概要

計測アプリケーションや監視アプリケーションでは、多くの場合、システムの精度を確保しつつ消費電力を低減することが求められます。本稿では、そのために必要なタイミングに関連する事柄とソリューションについて解説します。今回(Part 2)は、逐次比較型A/Dコンバータ(SAR ADC)を使用するケースに焦点を絞ります。SAR ADCを使用する場合、Part 1で取り上げたシグマ・デルタ(ΣΔ)型ADCとは異なるタイミング要因に注目する必要があります。いずれにせよ、シグナル・チェーンの中でも、アナログ・フロント・エンド(AFE)のタイミング、ADCのタイミング、デジタル・インターフェースのタイミングについて検討を実施する必要があります。

AFEのタイミングに関する検討事項

早速ですが、図1をご覧ください。まずは、左端のAFEについて検討することにしましょう。シグナル・チェーンごとにAFEにも違いがありますが、主要な構成要素には共通する部分があります。

図2に示したのは、SAR ADC「AD4696」に対応するAFEです。AFEとしては、外付けアンプ、ローパス・フィルタを使用しています。AD4696は、Easy Drive™機能を備えるマルチプレクスSAR ADCであり、16ビットの分解能、1MSPSのサンプル・レートに対応しています。外付けのセンサーとのインターフェースとしては、外付けのオペアンプ回路などが必要です。ただ、AD4696はEasy Drive機能として、アナログ入力部の高インピーダンス・モードやリファレンス入力部の高インピーダンス・モードなどを提供しています。そのため、外付け回路側から見れば、アナログ入力とリファレンス入力に関する駆動の要件が緩和されることになります。大きな電力を扱うアプリケーションでは、おそらくSAR ADC用のアンチエイリアシング(折返し誤差防止)フィルタ(AAF)に対しては厳しい要件が課せられることになります。それに対し、低消費電力のアプリケーションにおいて狭帯域の信号をサンプリングする場合には、フィルタの設計に対する要件はそれほど厳しくはありません。ΣΔ ADCを使用する場合、デジタル・フィルタが支配的な要因になって周波数特性が決まるので、外付けのAAFについては変調器の周波数を基にした簡素な設計を採用できます。これは、ΣΔ ADCがもたらすメリットの1つです。では、同ADCで使われるオーバーサンプリングや固有のフィルタ特性を利用できない場合にはどうなるのでしょうか。その場合、サンプル・レートを超える周波数の高い信号によって通過帯域にエイリアスが発生するのを防ぐために、性能の高い外付けのAAF(ローパス・フィルタ)が必要になります。そのAAFは、AFE回路からの広帯域のノイズを低減し、アナログ入力部で発生する非線形のキックバック電圧を抑制し、過電圧からアナログ入力部を保護できるように設計するべきです。同様に、タイミングについても詳細に検討する必要があります。AAFの設計については、Part 1の記事も参照してください。

SAR ADCの場合、サンプリングを実行する際にサンプル&ホールドのメカニズムが適用されます。それには、変換結果を収集するまで入力信号を保持しておくためのコンデンサとスイッチが使用されます。

図2のAFEを設計する際には、Part 1で説明したのと同様に、まずシグナル・コンディショニング用のオペアンプと外付けのAAFに関する選択を行います。外付けのドライバ・アンプは、ゲインによって決まる帯域幅を備えています。同アンプの選択にあたっては、消費電力と帯域幅の間にトレードオフが存在することに注意しなければなりません。このアンプは、シグナル・コンディショニング用回路の構成要素であるAAFの出力をバッファし、ADCの入力を駆動するために使用します。また、キックバックに対応するためのフィルタも設計しなければなりません。これについては、フィルタが対応する必要があるトータルの容量としてCEXT + CDACを使用します。

マルチプレクスSAR ADCでは、アナログ入力チャンネルを切り替える際にキックバックの問題が生じます。スイッチが閉じるとき、ADCの内蔵コンデンサCDACの電圧は、その時点でサンプリング・コンデンサCEXTを充電している電圧とは異なる値である可能性があります。その差によって、スイッチが閉じたときに電圧グリッチが発生します。このエネルギーは両コンデンサに分配され、コンデンサの端子間で測定される電圧は半分になります。CEXTとCDACの値はフィルタの設計に影響を及ぼすので、回路を設計する際に考慮すべき対象になります。キックバックとADC用のドライバの選択については、AD4696のデータシートに詳しく記載されています。また、Precision ADC Driver Tool(高精度ADCドライバ・ツール)やトレーニング用のビデオを活用することも可能です。

AD4696は、アナログ入力向けの高インピーダンス・モードを備えています。これを使用すれば、キックバック電圧を大幅に低減することができます(図3)。このモードをイネーブルにすると、AFEのアンプ回路とAD4696のアナログ入力部の間の直列抵抗に起因する性能の低下が抑制されます。その結果、従来のマルチプレクスSAR ADCを使用する場合と比べて、外付けRCフィルタで使用する抵抗REXTとして大きな値のものを選択することが可能になります。大きなREXTと小さなCEXTを使用することにより、歪み性能に大きな影響を及ぼすことなく、アンプの安定性に関する懸念を軽減することができます。ただ、過電圧保護のための内蔵クランプ機能がイネーブルである場合の安定性の問題を回避するためには、CEXTの値として最小500pFを確保することが推奨されます。こうした配慮を行うことにより、図3に示すように、必要な信号をより速くサンプリングし、システムのタイミングを高速化することができます。

ADCのタイミングに関する検討事項

ADC製品の選択は、システムにおいて何を重視するのかということに依存します。SAR型とΣΔ型の技術を比較し、性能の面からはどちらを選択すべきなのかということについて論じた記事は数多く存在します。低消費電力のアプリケーションについて言えば、同様の信号を測定する場合、SAR ADCでもΣΔ ADCでも、さほど差がない部分も数多く存在します。但し、明確な差として言えることが1つあります。それは、SAR ADCの方が、タイミングについて理解するのが容易であるということです。

SAR ADCによる入力信号のサンプリング動作は、アクイジション・フェーズと変換フェーズで構成されます(図5)。アクイジション・フェーズには、サンプル&ホールド回路または内部の容量性回路の充電が行われます(図2)。変換フェーズでは、スイッチによってコンデンサのアレイからコンパレータ回路への切り替えが実行されます。それにより、アナログ入力に対応するコードに達するまで内蔵DACへの重み付けが変更されます。

SAR ADC製品のデータシートを見ると、最大変換時間が規定されています。AD4696の場合、その値は415ナノ秒です。また、信号を取得(アクイジション)するための最小変換時間は1715ナノ秒です。これは、AD4696が500kSPSで動作している場合のアクイジション時間です。各変換の間隔がスループット・レートに相当します。

SAR ADCのタイミングについて主なトレードオフになるのは、消費電力とADCのサンプル・レートの関係です。SAR ADCには、サンプル・レートと電源電流の間に直接的な比例関係があります。これは1つの長所となります。つまり、対象とする信号の帯域幅に応じて電源電流を増減させられるということです。内部のADCコアは、変換処理と変換処理の間ではパワー・ダウンしています。そのため、AD4696の消費電力は、低いサンプル・レート(10kSPSなど)で動作する場合には0.17mW(公称値)程度まで低減できます。それに対し、1MSPSにおける消費電力は8mWです。つまり、AD4696は、サンプル・レートが低いバッテリ駆動のアプリケーションに適しています。

図6は、AD4696のVDDの電流について示したものです。同ADCのサンプル・レートを500kSPSという低い値に設定し、なおかつ100kSPS未満で動作させると、IDDは約2.5mAから0.5mAまで低下します。更にサンプル・レートを10kSPSまで下げると、IDDは42µA(公称値)まで減少します。電流の増減は線形に現れます。これは、デジタルとアナログの電源電流がすべて同様に直線的に増減するからです。そのため、使用する部品が同等という条件でDC/AC信号を測定する場合、SAR ADCは常に魅力的な選択肢になるはずです。

デジタル・インターフェースのタイミングに関する検討事項

AD4696は、従来のSAR ADCには存在していなかったいくつかの機能を備えています。それらは、低消費電力のシグナル・チェーンの電力を更に削減するために役立ちます。但し、タイミングについての考慮が必要です。

SAR ADCのスループット・レートについては、フィルタによる遅延を考慮する必要はありません。つまり、ΣΔ ADCを使用する場合と比べて計算はシンプルです(以下参照)。

ここで、CHsはイネーブルの状態にあるチャンネルの数です。

CNV信号は繰り返し遷移し、それに伴って立上がりエッジが繰り返し現れます。その間隔のことをサイクル時間と呼びます。通常、サイクル時間は、アクイジション・フェーズと変換フェーズを組み合わせた形で構成されます。ただ、両者の重なりを許容できる製品も存在します。つまり、変換フェーズの間に、信号のアクイジションを開始することができるということです。SAR ADCの各サンプルの間隔は、サイクル時間tCYCまたはサンプル・レート時間tSRという形で表現されます。タイミングに関する主なパラメータとしては以下のようなものがあります。

tCONVERT:変換時間

tACQ:アクイジション時間

tCYC = tSR:各サンプルの間隔。サンプリング周波数の逆数

変換を行う際、サンプリングの瞬間はCNV信号の立上がりエッジで制御されます。ほとんどのモードでは、CNVは外部信号として供給されます。一方、AD4696は自動サイクル・モードを備えています。このモードでは、変換開始信号を同ADCの内部で生成します。その信号によって変換が開始されるということです。また、AD4696では多くのシーケンサ・モードを使用できます。それらを使えば、ユーザは事前に定義した方法によって変換の順序と構成を選択することが可能です。あるいは、変換を中断することなく、シーケンス上の次の対象チャンネルをその場で制御するといったことも行えます。

デジタル・ホストは、次の変換が開始される前にデータを読み込む必要があります。信号が高速である場合、次のCNVの立上がりエッジ(または自動サイクル・モードにおける内部の変換開始信号)までに、AD4696のSPI(Serial Peripheral Interface)からデータを読み込めるよう、SCKの周波数を十分に高くする必要があります。サンプル・レートが高くなると、各変換の間隔が短くなるので、SCKの周波数をかなり高めなければなりません。

SCKの最低周波数は、サンプル・レート、SPIのフレームの長さ(ビット単位)、使用するシリアル・データの出力モードによって決まります。変換結果であるサンプル・データは、次の変換フェーズが開始するまで有効です。SCKの周波数は、次のCNVの立上がりエッジよりも前(または自動サイクル・モードにおける内部の変換開始信号よりも前)に、AD4696のSPIからデータを読み出せるよう、十分に高く設定しなければなりません。

複数のSDOによるデジタル出力

AD4696ファミリは、デュアルSDOモードとクワッドSDOモードを備えています。これらのモードでは、ADCによる変換結果がSDOからシフト出力されます。それと並行して、GPIOピンからデータをシフト出力することも可能です。これらのモードでは、SCKの1周期あたりに、SPIの出力ビット数が2倍または4倍になります。そのため、所定のサンプル・レートに必要なSCKの周波数を大幅に下げることができます。その結果、マイクロコントローラの要件が緩和されます。例えば、1MSPSで変換を行う場合に、必要なクロックを32MHzのSPIクロックから16MHzのSPIクロックに下げられるといった具合です。

変換モードの1フレームあたりに必要なSCKの周期の数NSCKは、次式のようになります。

ご覧のように、NSCKの値は、1フレームあたりのビット数NBITSとシリアル・データ出力の数NSDOによって決まります。ここで、NSDOの値はシングルSDOモードでは1、デュアルSDOモードでは2、クワッドSDOモードでは4になります。

変換モードにおいては、tCONVERTが経過するまでSPIフレームを開始してはなりません。また、最小tSCKCNVの仕様を遵守するよう十分に早く終了する必要もあります。変換モードにおいて、SPIフレームを完了するために必要な時間tFRAMEは、次式によって計算することができます。

tFRAME = tCYC – tCONVERT_max – tSCKCNV

ここで、tCYCはサンプル周期、tCONVERT_maxはtCONVERTの最大値、tSCKCNVはSCKの(最後の)立上がりエッジからCNVの立上がりエッジまでの遅延の仕様値です。

fSCKについては、tFRAMEとNSCKに応じて以下の条件を満たすようにします。

AD4696のデータシートには、何種類かのサンプル・レートに対するSCLKの最小周波数の例を示す表が掲載されています。

自動サイクル・モード

従来、電圧や電流のレベルを監視するアプリケーションでSAR ADCを使用する場合には、変換を実行するための変換信号をホスト・コントローラから連続的に出力する必要がありました。一方で、システムはデータが閾値を超えているかどうかを確認し、そのレベルに基づいて判断を行う必要があります。その際、ホストは連続的に変換を行わなければならないので電力効率がよくありません。そこで、AD4696は、ユーザがプログラムしたチャンネル・シーケンスで自律的に変換を行うように構成できるようになっています。

自動サイクル・モードは、アナログ入力を監視する場合に最適なモードです。変換周期としては、10マイクロ秒(100kSPSのサンプル・レート)から800マイクロ秒(1.25kSPSのサンプル・レート)までの範囲でいくつかのオプションが用意されています。このモードは、閾値の検出に関するアラートやヒステリシスの検出に関するアラートと組み合わせて使用することができます。これらのアラートは、チャンネルごとに設定することが可能です。そのため、デジタル・ホスト・システムのオーバーヘッドを削減することができます。その際には、ホスト・コントローラを低消費電力の状態に移行させられます。そして、あるレベルがトリガされ、AD4696からの割り込みを受け取った場合だけパワー・アップするという動作を実現できます。

オーバーサンプリング

Part 1で説明したとおり、オーバーサンプリングとデシメーションは、ΣΔのアーキテクチャに固有のものとして扱われてきました。しかし、SAR ADCであるAD4696は、オーバーサンプリングとデシメーション用のエンジンを備えています。それらを利用することで、ノイズをより低減することが可能です。その場合、ADCから連続して出力されるデータ(サンプル)を効果的に平均化することにより、高い実効分解能と低い実効ノイズでオーバーサンプリング・データを生成します。AD4696の場合、オーバーサンプリング比OSRが4倍になるごとに、実効ビット数が1ビットずつ増加します。

この機能は、温度のようにゆっくりと変化する事象に対応する信号を測定する場合に特に有用です。

そうしたシステムには、精度が高く低消費電力のシグナル・チェーンが求められます。サンプル周期をtSAMPLE、サイクル時間(サンプル・レートの逆数)をtCYC、オーバーサンプリング比(4~64の範囲で設定可能)をOSRとすると、以下の式が成り立ちます。

ΣΔ ADCと同様に、性能と速度の間にはトレードオフの関係があります。

| 項目 | タイミングに関する検討事項 | 低消費電力のシグナル・チェーンに対する影響 |

| AAF | 変換結果に影響を及ぼす遅延が生じる可能性がある | 高速シグナル・チェーンに比べて、さほど積極的なフィルタリングは必要ない |

| 高インピーダンス・モード | チャンネルを切り替える際のキックバック時間が短縮 | 消費電力がサンプル・レートに比例して増減。外部回路を簡素化できる |

| 電流 vs. サンプル・レート | 消費電力を低減するとサンプル・レートが低下 | サンプル・レートを低下させると消費電力が低減 |

| 自動サイクル・モード | 内部の変換開始をソフトウェアで制御できる | ホスト・コントローラを低消費電力の状態に移行させることが可能 |

| デュアルSDO、クワッドSDO | サンプル・レートが高くなると、単一のSDOでは全データの読み込みが不可能 | 回路の追加とデータ速度の間にトレードオフが存在 |

| オーバーサンプリング | サンプル間の間隔は、OSRが高くなるほど増加 | OSRを高めると、ノイズ性能と分解能が向上 |

低消費電力で高精度のプラットフォーム

エネルギー・コストは世界的に上昇傾向にあります。一方で、エネルギーを使用することが自然界に及ぼす影響についての理解も進んでいます。そうした状況下で、システム設計者は、電力バジェットを削減しつつ高い精度を達成すべく取り組みを行っています。しかし、入手が可能で最も消費電力の少ない製品を見つけだすのは簡単なことではありません。そこで、アナログ・デバイセズは、最も消費電力が少なく精度の高いデバイスをベースとし、すぐに使用できるシグナル・チェーンや回路をワンストップで提供するよう取り組みを進めています。それにより、設計プロセスの簡素化に貢献します。そうしたソリューションを利用することで、システム設計者は、高精度、低消費電力の最新製品を活用できるようになります。

SAR ADCを採用した低消費電力のシグナル・チェーン

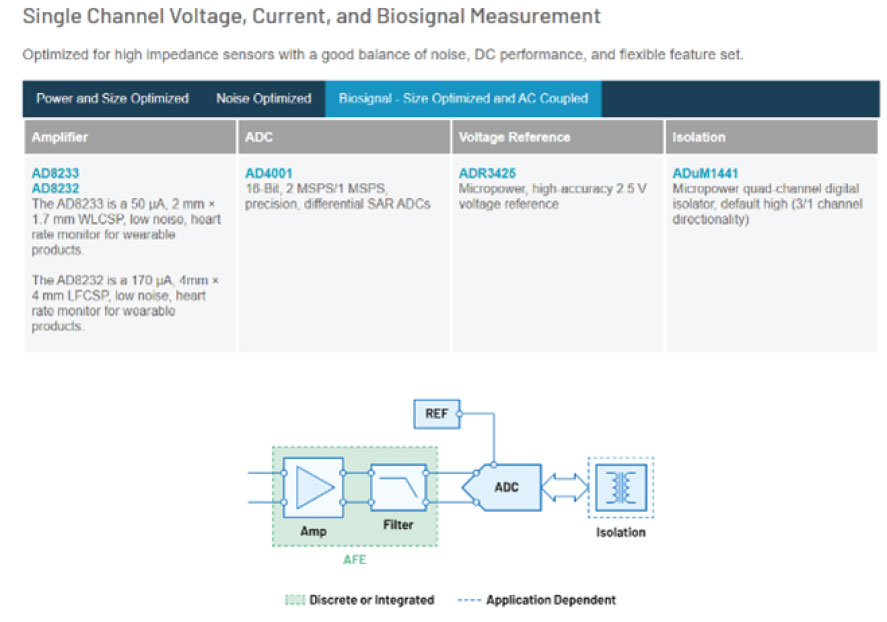

多くのアプリケーションでは、大きなDCオフセット/コモンモード電圧に重畳された小さな信号を測定しなければなりません。システムの用途が産業環境における流量監視や生体電位測定である場合、そのアプローチには共通する部分があります。すなわち、ACカップリングによって大きなオフセットを除去しつつ、ADCのダイナミック・レンジを最大限に活かせるよう信号にバイアスとゲインを適用することになります。

アナログ・デバイセズの低消費電力/高精度のシグナル・チェーンには、この種のアプリケーションに適したデバイスに関する提案が含まれています。

また、KWIK(Know-how with Integrated Knowledge)のページでは、より詳細な回路についての分析を示したり、選択すべき最新デバイスに関する提案を行ったりしています。

【具体例】流量測定用のシグナル・チェーン

ここでは具体的な例として、大規模なマルチ測定システムの設計を取り上げます(図9)。この例では、図10の回路を使用して流量測定機能を実現しています。図10の回路は、KWIKの回路例の一例です。

質問A:10個の流量センサーを1kSPSで動作させたいケースを考えます。その場合、SAR ADCとΣΔ ADCのうちどちらを選択すべきでしょうか?

質問B:AFEのタイミングについて検討すべき事柄としては、どのようなものがあるでしょう?

質問Aに対する答え:ここでは、SAR ADCであるAD4696を採用します。シグナル・コンディショニング用の回路は、計装アンプ「AD8235」とオペアンプ「ADA4505-2」を組み合わせて構成します。図9の回路は、外部の変換信号または自動サイクル・モードを使用することで、10個のチャンネルを10kSPSで動作させるための最良の選択肢となります。

質問Bに対する答え:この回路の場合、AAFの周波数特性ではなく、AD4505-2の周波数特性とゲインの関係から、被測定信号の帯域幅が決まります。AD4696の高インピーダンス・モードを使用すると、入力アンプの負担が軽減されます。そのため、より消費電力の少ないアンプを使用することが可能になります。図10で使用している製品は、主として消費電力が極めて少ないという理由で選択されました。

まとめ

高分解能、低消費電力のデータ・アクイジション・システムを設計する場合、入手可能な最も消費電力の少ない製品を見つけ出すのは容易ではありません。アナログ・デバイセズの高精度、低消費電力のシグナル・チェーンは、そうしたシステム設計の出発点としての役割を果たします。中核となるものとしてΣΔ ADCやSAR ADCを組み込んだシグナル・チェーンを構成する場合、トレードオフやタイミングの違いについて明確に理解しておく必要があります。

センサー(対象となる信号)とのインターフェースについて検討する際には、AFEのタイミングに注意しなければなりません。ICのレベルの起動、センサーに対するバイアス、外付けのフィルタ、部品の選択などについて考慮する必要があります。独特なアーキテクチャに基づいているΣΔ ADCとは異なり、SAR ADCのAAFについてはより厳格な要件が存在します。AFEについて言えば、ΣΔ ADCの場合、プログラマブル・ゲイン・アンプ(PGA)を内蔵しているものが少なくありません。これは、ΣΔ ADC製品がもたらすメリットの1つです。一方、高インピーダンス・モードのような機能を備えるSAR ADCであれば、外付けのアンプに求められる駆動関連の要件が緩和されます。

ΣΔ ADCでは、オーバーサンプリングとデシメーションという独特な処理が行われることに加え、フィルタによる遅延が生じます。特に、複数のチャンネルで変換を行う際には、その遅延によってスループット・レートに影響が及びます。一方、SAR ADCの場合、逐次比較方式であることからスループット・レートの計算はシンプルです。また、サンプリング速度が低いほど、変換時の消費電流が少なくなるというメリットも得られます。

ΣΔ ADCである「AD4130-8」では、デジタル的なタイミングについて複雑な検討が必要になります。そのことが契機となって、アナログ・デバイセズは分析/制御/評価用のタイミング・ツール「ACE(Analysis Control Evaluation):分析 ¦ 制御 ¦ 評価用 (ACE) ソフトウェア」を開発するに至りました。これを利用すれば、チャンネルのスループット・レートの計算が行えるだけでなく、タイミングに関する理解が容易になります。また、AD4130-8は、バッテリの寿命の延伸に役立つデューティ・サイクリング、FIFO(First In, First Out)、スタンバイ・モードといったタイミング機能を備えています。ただ、特定のスループット・レートを目標としている場合、達成できる実効分解能について注意を払わなければなりません。

AD4696のようなSAR ADCを採用すれば、より高い周波数でサンプリングを実施できます。そのこと自体はメリットになりますが、そうするとデジタル・タイムフレームtFRAMEが短くなります。それに伴い、SPIのクロック周波数を高く設定しなければならないので注意が必要です。

参考資料

Maithil Pachchigar「マルチプレクス・データ・アクイジション・システム設計におけるSARとシグマ・デルタ(Σ-Δ)コンバータのトレード・オフ」Analog Devices、2016年4月

Walt Kester「Which ADC Architecture Is Right for Your Application?(アプリケーションの種類に応じ、ADCのアーキテクチャを適切に選択する)」Analog Dialogue、Vol. 39、No. 9、2005年6月

Albert O'Grady「Transducer/Sensor Excitation and Measurement Techniques.(トランスデューサ/センサーの励起と測定)」Analog Dialogue、Vol. 34、No. 5、2000年8月

Alan Walsh「高精度SAR A/Dコンバータ(ADC)のフロントエンド・アンプとRCフィルタの設計」Analog Dialogue、Vol. 46、No. 12、2012年12月

Steven Xie「高精度ADC用のフィルタ設計における課題と検討事項」Analog Dialogue、Vol. 50、No. 4、2016年4月

Walt Kester「MT-021: ADC Architectures II: Successive Approximation ADCs(ADCのアーキテクチャII:逐次比較型のADC)」Analog Devices、2009年

Ke Li、Colm Slattery「電磁式流量計の設計――検討すべき事柄とソリューション」Analog Dialogue、Vol. 50、No. 6、2016年6月

「SPICE Model for a Platinum RTD Sensor(白金RTDセンサーのSPICEモデル)」Analog Devices、2022年

「MT-070 Tutorial: In-Amp Input RFI Protection(計装アンプの入力部をRFIから守る)」Analog Devices、2009年

Padraic O'Reilly「低消費電力/高精度のシグナル・チェーンで注意を払うべきタイミング要因【Part 1】」Analog Dialogue、Vol. 56、No. 3、2022年8月