はじめに

高精度のA/Dコンバータ(ADC)は、計装や測定、PLM、プロセス制御、モーター制御など、広範な分野で一般的に使用されています。現在のSAR(逐次比較)型ADCは18ビットまたはそれ以上の分解能を備え、サンプリング・レートも数MSPS(メガサンプル/秒)に達しています。また、ΣΔ型ADCの場合、分解能は24ビットや32ビット、サンプリング・レートは数百kSPS(キロサンプル/秒)にも達するものがあります。そうしたADCの能力に影響を及ぼすことなく、本来の実力を最大限に活用できるようにするのは容易なことではありません。例えば、シグナル・チェーンで使用するフィルタを、ノイズを抑えるよう実装するのはより困難な作業になっています。

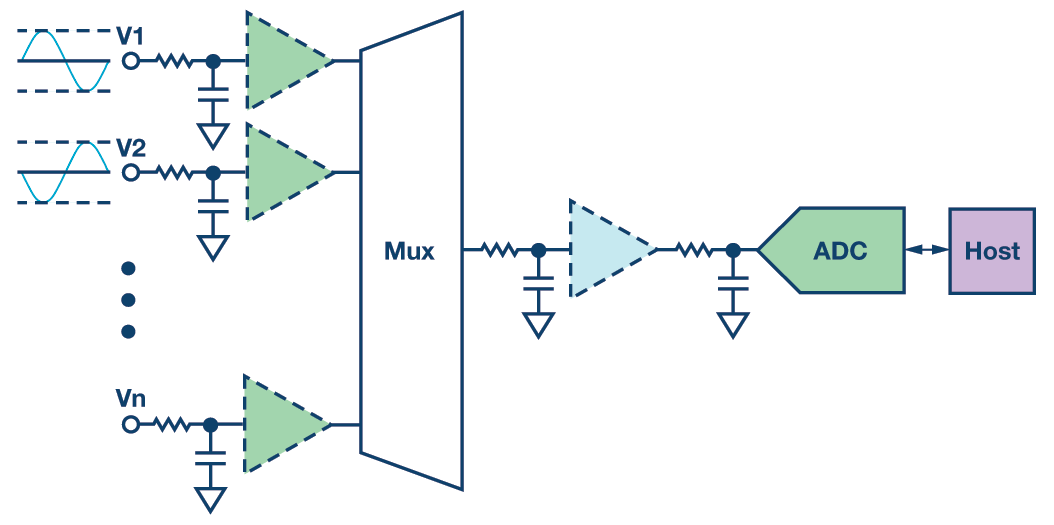

本稿では、シグナル・チェーンで使われるADC用のアナログ・フィルタとデジタル・フィルタの実装方法について説明します。具体的には、ADCの性能を最大限に引き出すためには、フィルタを設計するうえでどのような課題に取り組み、どのような事柄について検討すればよいのか解説します。図1に示したのは、データ・アクイジションに使用するシグナル・チェーンです。この種のシグナル・チェーンでは、アナログ・フィルタまたはデジタル・フィルタを単体で、あるいは両者を組み合わせて使用することができます。一般に、SAR型やΣΔ型の高精度ADCでは、第1ナイキスト・ゾーンをターゲットとしてサンプリングを実施します。そこで、本稿ではローパス・フィルタに関する話題を取り上げます。ただし、本稿の目的は、特定のローパス・フィルタの設計方法を紹介することではありません。ADCを含む回路において、ローパス・フィルタを適切に使用する方法を説明することを主目的とします。

理想的なフィルタ、現実のフィルタ

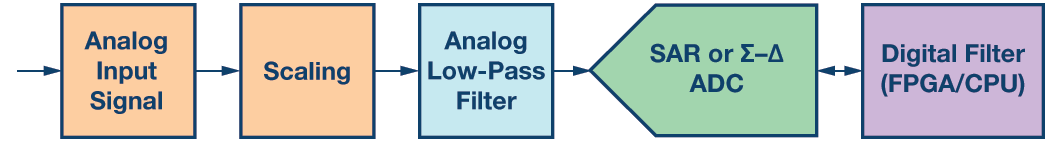

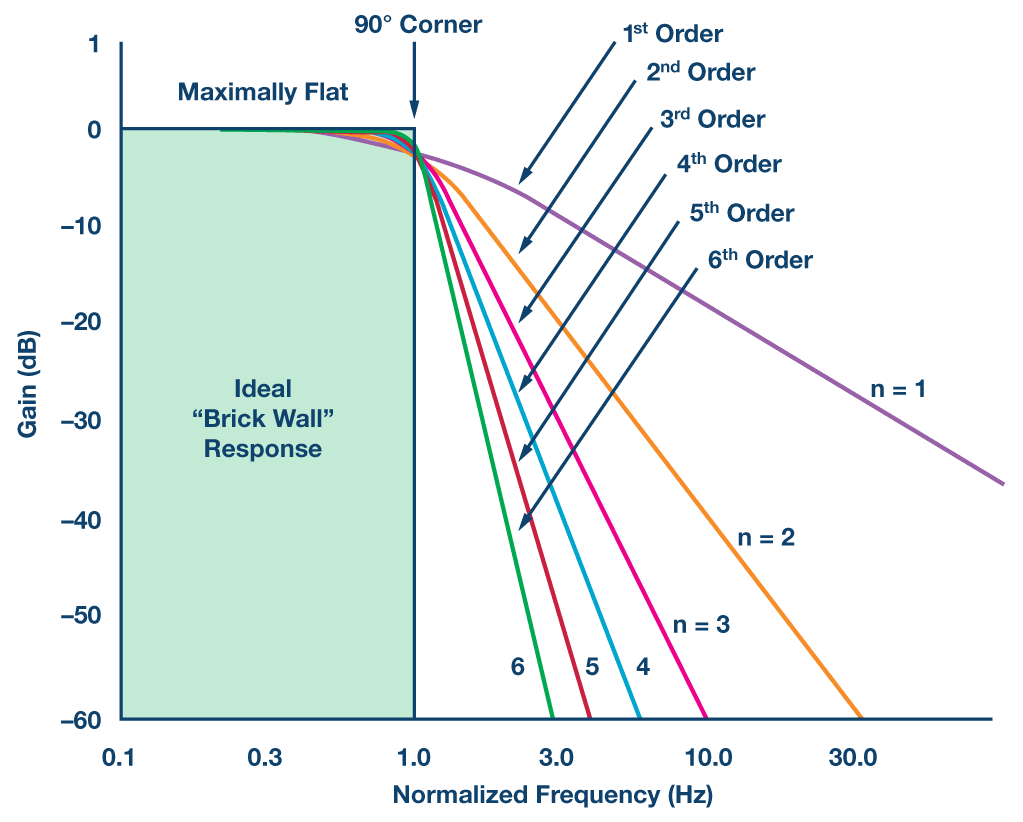

図2の太い破線は、理想的なローパス・フィルタの振幅応答です。ご覧のように、通過帯域のゲインは平坦性に優れており、遷移帯域は急峻な減衰特性を示しています。また、阻止帯域では大きな減衰量が得られ、帯域外の信号はすべてゼロに抑えられます。図2に示したそれ以外の曲線は、一般的に使用される現実のフィルタの振幅応答です。図のように、通過帯域のゲインが平坦ではなく、リップルが生じていたりすると、基本波の信号が意に反してスケーリングされてしまう可能性があります。また、阻止帯域の減衰量は無限ではなく、帯域外信号の除去能力には限界があります。加えて、遷移帯域は急峻ではなく、ある程度の幅を持ちます。そのため、カットオフ周波数の近くの周波数では減衰性能が不足します。さらに、現実のフィルタでは位相遅延や群遅延が生じます。

アナログ・フィルタとデジタル・フィルタ

アナログのローパス・フィルタは、ADCによるA/D変換の前の信号に適用します。それにより、折り返し(エイリアス)が発生するのを防止する役割を果たします。つまり、A/D変換の前の信号にシグナル・パスから混入する高周波ノイズや干渉を除去するということです。また、フィルタの帯域幅を超える信号の影響を除去し、ADCの変調器が飽和するのを防ぎます。加えて、入力電圧が高すぎる場合には、入力電流を制限して入力電圧を減衰させる役割も果たします。つまり、ADCの入力回路の保護にも役立つということです。ノイズのピークがフルスケールに近い信号に重なると、ADCのアナログ変調器が飽和する可能性があります。したがって、そのような信号もアナログ・フィルタによって減衰させる必要があります。

一方、デジタル・フィルタはA/D変換を実施する回路の後段に配置されます。それにより、A/D変換の過程で加わるノイズを除去することができます。ナイキストの定理では、対象とする最大信号周波数の2倍以上の周波数でサンプリングを行えばよいとされています。しかし、実際のアプリケーションでは、多くの場合、2倍よりもかなり高いサンプリング周波数(サンプリング・レート)が使用されます。そこで、デジタル・フィルタはA/D変換の過程で加わるさまざまなノイズの低減にも利用されます。例えば、信号帯域外の入力ノイズ、電源ノイズ、リファレンス・ノイズ、デジタル・インターフェースを介したフィード・スルー・ノイズ、ADCのチップから発生する熱ノイズ、量子化ノイズなどです。つまり、高い分解能に見合う高いS/N比を得るために、フィルタ技術を利用するということです。

表1に、アナログ・フィルタとデジタル・フィルタの利点と欠点を簡単にまとめました。

表1. アナログ・フィルタとデジタル・フィルタの比較

| アナログ・フィルタ | デジタル・フィルタ | |

| 設計の複雑さ |

高性能のフィルタは複雑になる |

比較的、簡素 |

| コスト |

高い (選択するアナログ部品に依存) |

低い(使用可能なCPU時間に影響) |

| 遅延 |

小さい | 大きい |

| 追加されるノイズ |

部品の熱ノイズが帯域内に追加される |

量子化によるデジタル・ノイズが加わる可能性がある |

| ADCの入力保護 |

保護に役立つ | 保護には寄与しない |

| プログラマブル化への対応 |

対応できない | 対応可能 |

| ドリフト誤差 |

発生する | 発生しない |

| 経年劣化 |

発生する |

発生しない |

| マルチチャンネルの場合のマッチング誤差 |

発生する |

発生しない |

アナログ・フィルタに関する検討事項

アンチエイリアシング( 折返し誤差防止) フィルタはADCの前段に配置します。したがって、アナログ・フィルタとして構成します。理想的なアンチエイリアシング・フィルタでは、通過帯域でゲインが増減することはなくユニティ・ゲインを示します。折り返しの減衰レベルは、データ変換システムの理論的なダイナミック・レンジに適合させます。

ADCの入力抵抗は、アーキテクチャによって異なります。入力部に配置するフィルタの設計は、その入力抵抗によって左右されることになります。以下では、ADCの入力部に配置するアナログ・フィルタについて、設計時に検討すべき事柄を示します。

ADCの入力部に接続するアンチエイリアス用RCフィルタに関する制約

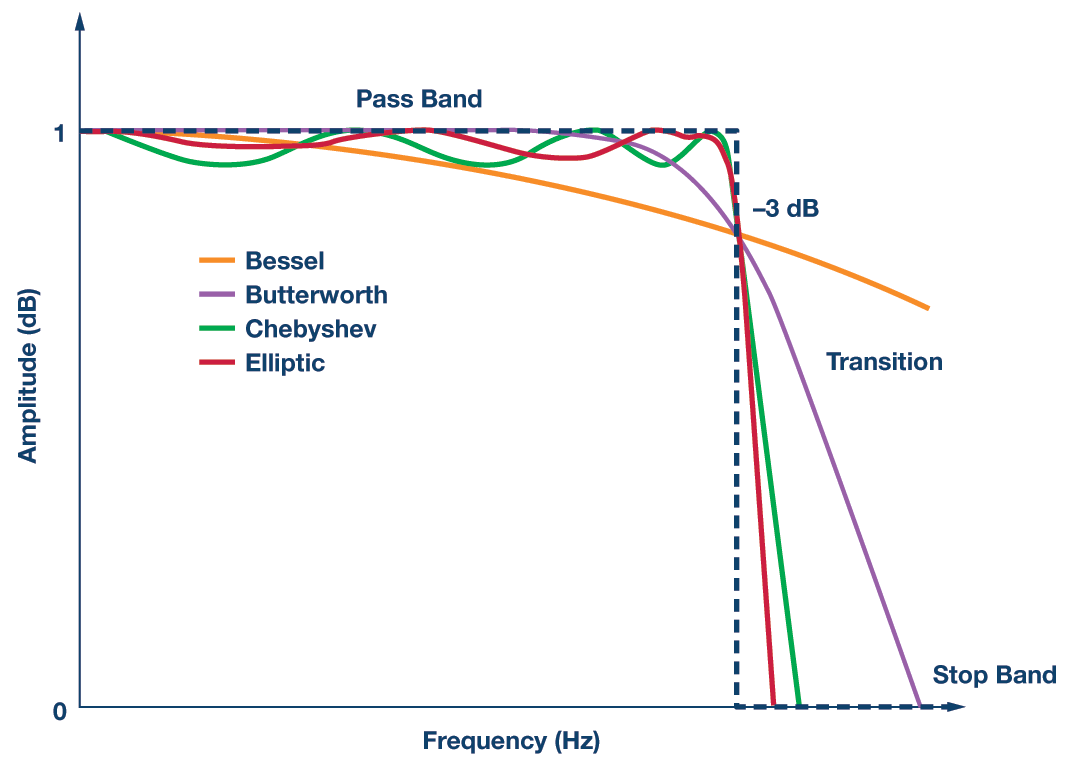

Analog Dialogueの「高精度SAR A/Dコンバータ(ADC)のフロントエンド・アンプとRCフィルタの設計」( 著者: Alan Walsh) という記事では、図3に示した回路を取り上げています。これはアナログ・デバイセズのADC「AD7980」に適用するRC(抵抗‐容量)フィルタの例です。

このRCフィルタは、カットオフ周波数が3 . 11MHzのローパス・フィルタです。100kHzの入力信号に対し、3.11MHzというのはかなり高い値です。そのため、このフィルタでは帯域外ノイズを効率的に低減できないのではないかと思われるかもしれません。実際、設計者の中には、ダイナミック・レンジを高めるために、抵抗の値を590Ωに変更し、-3dB帯域幅を100kHzにしようとする人もいるでしょう。しかし、この方法には2つの大きな問題があります。1つは通過帯域の減衰量が大きくなりすぎることです。この例の場合、100kHz付近の信号は振幅が30%減衰します。そのため、AD7980の性能とは関係なく、シグナル・チェーンとしての精度が大幅に低下します。また、帯域幅が狭いということはセトリング時間が長いということを意味します。この例の場合、AD7980が備えるサンプル&ホールド用のコンデンサは、規定のアクイジション時間内に次の変換に向けてフル充電することができなくなります。その結果、ADCの変換精度が低下します。

ADCの前段に配置するRCフィルタは、ターゲットとするアクイジション時間内に必ず完全にセトリングするように設計する必要があります。このことは、大きな入力電流が必要であったり、等価入力インピーダンスが小さかったりする高精度のADCでは特に重要です。一部のΣΔ型ADCでは、バッファなしの入力モードにおいて入力部のRCの値が最大であることが求められます。一般に、入力インピーダンスが高い入力アンプの前段には、大きな抵抗やコンデンサで構成した帯域幅が非常に狭いローパス・フィルタを付加することができます。入力インピーダンスが非常に高いADCを選択した場合にも同じことが言えます。例えば、「ADAS3022」であれば入力インピーダンスは500MΩにも達します。

1. 多重化されたシグナル・チェーンにおけるフィルタのセトリング時間

通常、入力信号を多重化する場合には、チャンネル間の切り替えを行った際に大きな遷移が生じます。最悪の場合、あるチャンネルが負のフルスケール、次のチャンネルが正のフルスケールということが起こります(図4)。その場合、マルチプレクサがチャンネルを切り替える際にはADCのフルレンジに相当する入力電圧の遷移が生じます。

この問題に対処するには、マルチプレクサの後段にフィルタを1つ配置します。これにより、すべてのチャンネルの信号に対してフィルタが適用されます。この方法であれば、設計は簡素化され、コストも抑えられます。上述したように、アナログ・フィルタには必ずセトリング時間が伴います。この回路では、マルチプレクサがチャンネルを切り替える度に、選択したチャンネルの出力電圧までフィルタを充電する必要があります。そのため、スループット・レートに制限が加わることになります。スループット・レートを高めるためには、マルチプレクサの前段において、チャンネルごとに1つのフィルタを配置することで対処できます。しかし、その場合にはコストが大きく増加します。

2. 通過帯域の平坦性と遷移帯域の制約、それらとノイズの関係

アプリケーションによっては、ノイズのレベルが高く、特に第1ナイキスト・ゾーンの境界近くで大きな干渉が生じるものがあります。その場合には、急峻なロールオフ特性を備えるフィルタが必要です。ご存じのとおり、アナログのローパス・フィルタでは周波数の増加に伴って振幅が低下し、遷移帯域を経て減衰域に達します。フィルタの段数、つまりは次数を増やすと、通過帯域の平坦性が高まり、遷移帯域が狭くなります。しかし、そのようなフィルタの設計は非常に複雑です。ゲインのマッチングに対してあまりにも敏感なので、実用化に向けたハードルはかなり高くなります。また、抵抗やアンプなどの部品をシグナル・チェーンに追加すると、帯域内には必ずノイズが生じます。

アプリケーションによって、アナログ・フィルタの設計の複雑さと性能の間でトレードオフが必要になります。例として、電力線保護用リレーの用途で「AD7606」を使用するケースを考えてみましょう。その場合、50Hz/60Hzの入力基本信号と最初の5つの高調波に対する保護チャンネルでは、測定チャンネルよりも精度の要件が緩くなります。例えば、測定チャンネルでは、帯域内の平坦性を高めて減衰域までの遷移を急峻にするために、2次のRCフィルタを使用します。これに対し、保護チャンネルでは1次のRCフィルタによって対応することが可能です。

3. 同時サンプリングを行う場合の位相遅延とマッチング誤差

フィルタの設計は、周波数だけに注目して行えばよいというものではありません。アナログ・フィルタについては、時間領域の特性と位相応答の検討も実施する必要があります。位相遅延は、一部のリアルタイム・アプリケーションでは重要な問題になる可能性があります。入力周波数に応じて位相が変化する場合には、位相の調整はさらに難しくなります。通常、フィルタにおける位相の変化は群遅延というかたちで計測されます。群遅延が一定でない場合には、信号が時間領域において分散し、インパルス応答の劣化につながります。

モーター制御や電力線監視における位相電流の測定など、マルチチャンネルの同時サンプリングを行うアプリケーションでは、位相遅延のマッチング誤差についても検討する必要があります。そうしたケースでは、複数のチャンネル間で、フィルタによる位相遅延のマッチング誤差が生じます。その誤差を無視してよいものなのかどうかを確認する必要があります。もしくは、動作温度範囲におけるシグナル・チェーンの許容誤差の範囲内にあるかどうかを確認してください。

4. 歪みとノイズの低減に向けた部品の選択

アプリケーションにおいて、高調波歪みとノイズを小さく抑えるためには、シグナル・チェーンの設計において適切な部品を選択しなければなりません。通常、アナログ系の電子部品には非線形性があり、そのことが高調波歪みの原因になります。上で紹介したAnalog Dialogueの記事では、歪みの少ないアンプの選定方法とアンプのノイズの計算方法を紹介しています。一般に、アンプなどの能動部品には、高いTHD+N(高調波歪み+ノイズ)性能が求められます。それに加えて、一般的な抵抗やコンデンサなどの受動部品についても歪みやノイズを考慮に入れる必要があります。

抵抗については、電圧係数と電力係数の2つの項目において非線形性が現れます。アプリケーションによっては、高性能のシグナル・チェーンを実現するために、薄膜抵抗や金属抵抗など、特定の技術によって製造された抵抗が必要になることがあります。入力フィルタ用のコンデンサも、適切なものを選定しなければ大きな歪みが生じてしまうかもしれません。予算に余裕がある場合には、ポリスチレン・コンデンサやNP0特性またはC0G特性のセラミック・コンデンサを選択することでTHD性能を向上させることができます。

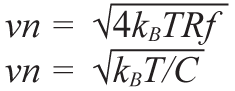

アンプだけでなく、抵抗やコンデンサもノイズ源になり得ます。平衡時の導電体内部における電荷キャリアの熱運動によって電子ノイズが生成されるからです。RC回路の熱ノイズは、簡単な式で表されます。抵抗値が大きいほどノイズが大きくなり、フィルタにおける要件が厳しくなります。RC回路のノイズ帯域幅は1/(4RC)で表されます。

抵抗と容量の小さいコンデンサの熱ノイズ(RMS値)は、次の2つの式で見積もることができます。

kB :ボルツマン定数。値は1.38065×10-23m2kgs-2K-1

T :温度。単位はK

f :ブリック・ウォール・フィルタの近似帯域幅

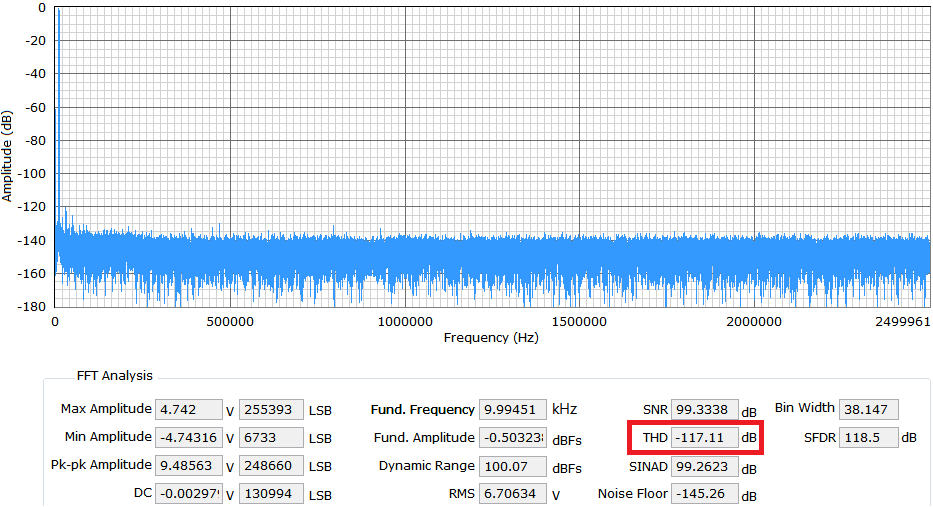

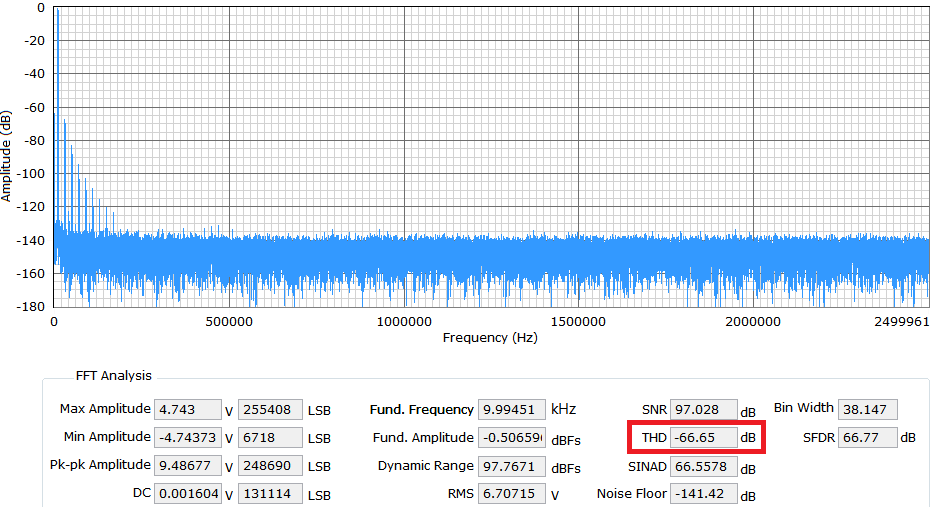

図6は、評価用ボード「EVAL-AD7960FMCZ」を使用し、10kHzのシングルトーンの正弦波を入力した場合のTHD性能の評価結果です。この測定は、NP0特性のコンデンサとX7R特性のコンデンサのそれぞれを使った場合を比較するために実施しました。図6(a)は、C76とC77として、値が1nFで0603サイズのNP0コンデンサを使用した結果です。一方、図6(b)では値が1nFで0603サイズのX7Rコンデンサを使用しました。

図6 . E VAL-AD7960FMCZでNP0コンデンサを使用した場合と

X7Rコンデンサを使用した場合のTHDの違い

アナログ・デバイセズの設計ツール「Analog Filter Wizard」を使用することで、ここまでに示した検討事項を踏まえてアクティブ・フィルタを設計することができます。同ツールを使えば、コンデンサと抵抗の値を計算し、アプリケーションに必要なアンプを選定することが可能です。

デジタル・フィルタに関する検討事項

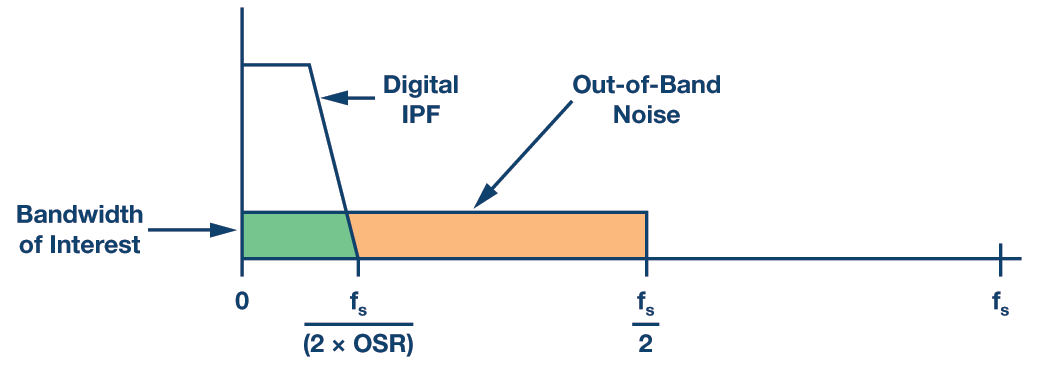

これまで、SAR型ADCとΣ Δ 型ADCでは、サンプル・レートと入力帯域幅の拡大が着実に進んできました。例えば、2倍のオーバーサンプリングを実施すれば、ADCの量子化ノイズの電力は2倍の周波数帯域に均等に分散されます。その場合、デジタル・データに変換された信号の帯域を制限するデジタル・フィルタを設計し、最終的に必要なサンプル・レートに適合するようデシメーション処理を適用することになります。この方法によって帯域内の量子化誤差が低減し、ADCのS/N比が向上します。また、フィルタにおけるロールオフの要件が緩和されるので、より簡易なアンチエイリアシング・フィルタを使用できます。オーバーサンプリングを適用すれば、フィルタの要件は緩和されます。しかし、サンプル・レートが高くなることに伴って、ADCではより高速なデジタル処理が行えるようにする必要があります。

1. オーバーサンプリングを適用した場合の実際のS/N比

オーバーサンプリングとデシメーション・フィルタを使用する場合、ADCのS/N比はどのようになるのでしょうか。分解能がNビットのADCの場合、その理論値は以下の式で求められます(単位はdB)。

[S/N比]=6.02×N+1.76+10×log10[OSR]

OSR=fs/(2×BW)

ただし、この式はノイズとしては量子化ノイズしか存在しない理想的なADCにだけ当てはまることに注意してください。

現実のADCでは、他にも多数のノイズ源からのノイズが加わり、それがA/D変換後のコードに反映されます。ノイズ源の例としては、信号源やシグナル・チェーンで使用する部品からのノイズ、ADCから発生する熱ノイズ、ショット・ノイズ、リファレンス電圧のノイズ、デジタル・フィードスルー・ノイズ、サンプリング・クロックのジッタに起因する位相ノイズなどが挙げられます。これらのノイズは、信号帯域に分布します。フリッカ・ノイズとして現れる場合もあります。したがって、現実のADCのS/N比は、一般的には上の式による計算結果よりも低くなります。

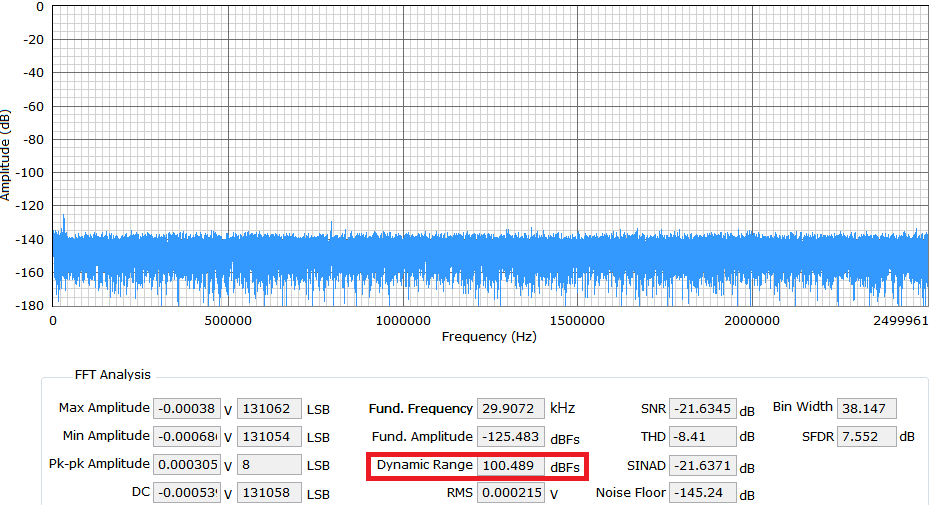

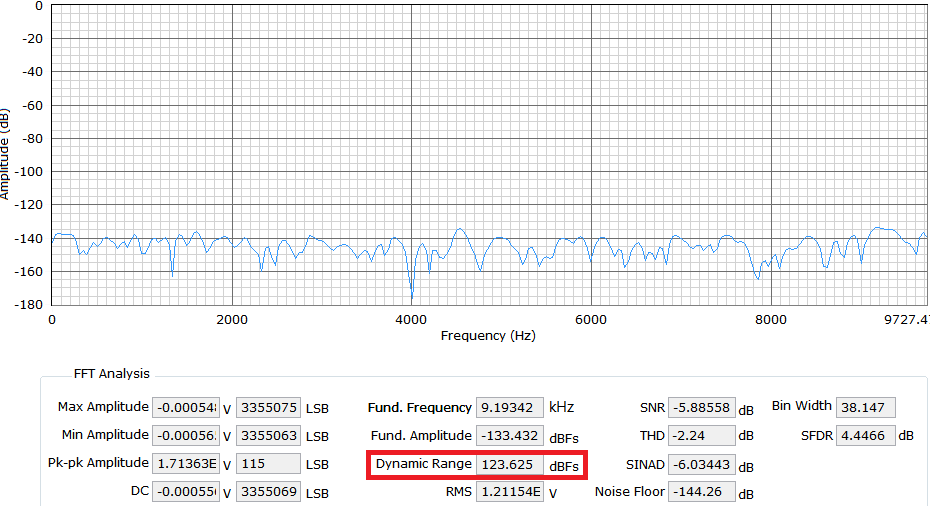

2. 評価用ボード上でのオーバーサンプリングによるダイナミック・レンジの向上

アプリケーション・ノート「AN-1279:5 MSPS、18 ビット/16 ビット高精度 SAR コンバータのオーバーサンプリングでダイナミック・レンジを拡大する方法」には、18ビットのADC「AD7960」で256倍のオーバーサンプリングを実施した場合にダイナミック・レンジの測定値は123dBであったと記されています。このような使い方は、分光法、MRI(核磁気共鳴画像法)、ガス・クロマトグラフィといった高性能のデータ・アクイジションを要するシステムのシグナル・チェーンや、振動、石油/ガス、地震の監視システムなどに適用されます。

図8に示すように、オーバーサンプリングを行う場合、ダイナミック・レンジの測定値はS/N比の理論値よりも1dB~2dB低くなります。シグナル・チェーンで使用する部品に起因する低周波ノイズによって、全体的なダイナミック・レンジが抑えられるためです。

図8 . 256倍のオーバーサンプリングによるダイナミック・レンジの向上

3. SAR型/ΣΔ型ADCの内蔵デジタル・フィルタがもたらすメリット

通常、デジタル・フィルタはFPGA、DSPまたはプロセッサによって実現します。アナログ・デバイセズはシステム設計を簡素化するために、A/D変換部の後段にデジタル・フィルタを内蔵する高精度ADCを提供しています。例えば、AD7606は、オーバーサンプリング用の1次のデジタル・フィルタ(sincフィルタ)を備えています。その設定は、OSピンにハイ/ローを入力するだけで簡単に行えます。Σ Δ 型ADCである「AD7175-x」は、従来のsinc3フィルタに加え、sinc5フィルタ、sinc1フィルタ、さらには50Hz/60Hzの成分を除去するためのフィルタを内蔵しています。また「AD7124-x」は、高速セトリング・モード機能(sinc4+sinc1フィルタまたはsinc3+sinc1フィルタ)を備えています。

4. 多重型ADCの遅延に関するトレードオフ

デジタル・フィルタには、比較的大きな遅延が生じるという欠点があります。遅延の大きさは、デジタル・フィルタの次数とマスター・クロック・レートに依存します。特に、リアルタイム・アプリケーションや高速なループ応答が必要なアプリケーションにおいては遅延を抑えることが重要になります。データシートに記載されている出力データレートは、単一のチャンネルで連続変換を行う場合の値です。チャンネルの切り替えを行う際には、ΣΔ変調器とデジタル・フィルタのセトリングのための時間が追加で必要になります。ここで言うセトリング時間とは、チャンネルの切り替えに伴う入力電圧の変化が出力データに反映されるまでの時間のことです。チャンネルの切り替え後のアナログ入力を正確に反映するには、デジタル・フィルタにおいて、前のアナログ入力に関連するデータをすべてクリアする必要があります。

以前のΣΔ型ADCでは、チャンネルの切り替え速度は出力データレートの数分の1程度でした。そのため、多重型のデータ・アクイジション・システムのようなスイッチングを伴うアプリケーションでは、単一のチャンネルで連続サンプリングする場合の数分の1程度の変換レートしか得られないことを理解しておく必要があります。

AD7175-xなど、アナログ・デバイセズの新しいΣ Δ型ADCの中には、チャンネルを切り替える際のセトリング時間を短縮するために最適化されたデジタル・フィルタを備えているものがあります。例えば。AD7175-xのsinc5+sinc1フィルタは、多重化アプリケーションをターゲットとしています。そのため、10kSPS以下の出力データレートに対して1サイクルでセトリングできるようになっています。

5. デジタル・フィルタのデシメーションによる折り返しの防止

多くの記事で論じられているように、オーバーサンプリング周波数が高いほど、ADCの前段に置くアナログ・フィルタの設計は容易になります。ナイキストの定理を満たすことはもちろん、それよりも高い周波数でサンプリングすれば、よりシンプルなアナログ・フィルタでも折り返しを防止することが可能です。歪みを生じさせることなく、急峻な減衰特性を備えるアナログ・フィルタを設計するのは困難です。これに対し、オーバーサンプリングを利用する場合、かなり高い周波数成分を除去できれば十分です。そのためのアナログ・フィルタを設計するのは難しいことではありません。併せて、A/D変換後の信号の帯域を制限するデジタル・フィルタを設計すれば、必要な情報を損なうことなく、求められる最終的なサンプル・レートにデシメーションすることができます。

デシメーションの処理を実装する際には、そのリサンプリングによって新たな折り返しの問題が生じないことを確認する必要があります。デシメーション後のサンプリング・レートに対し、入力信号がナイキストの定理に従っていることを確認してください。

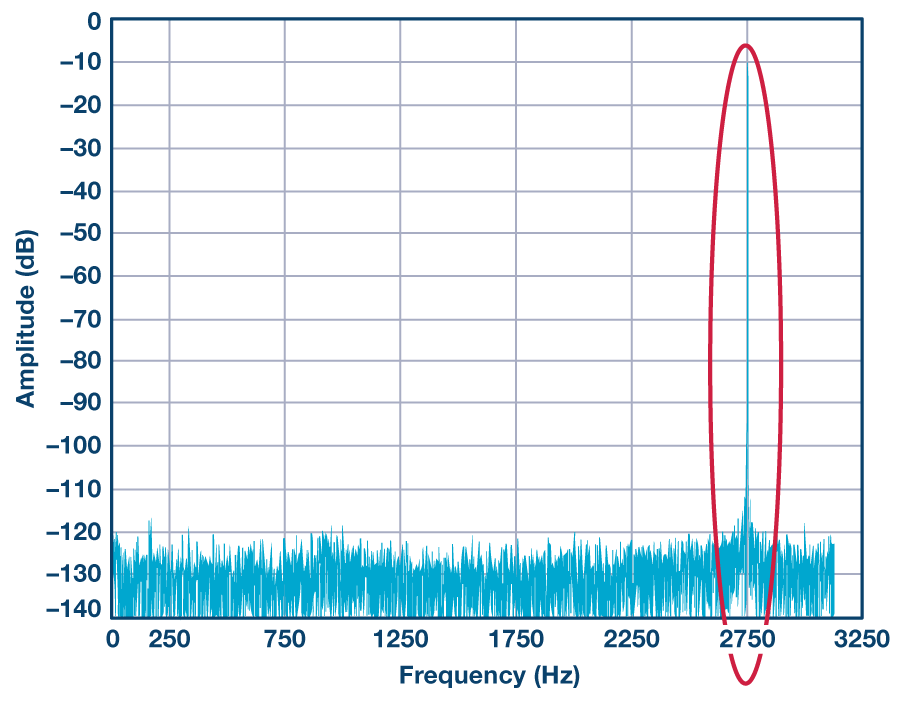

評価用ボード「EVAL-AD7606」、「EVAL-AD7607」、「EVAL-AD7608EDZ」では、各ADCをチャンネル当たり200kSPSで動作させることができます。図9に示す評価結果は、AD7606を6.25kSPSのサンプリング・レートに対し、32倍のオーバーサンプリング・レートで動作させた場合のものです。入力信号は、3.5kHz、-6dBFSの正弦波です。図9では、2.75kHz(6.25kHz-3.5kHz)の位置に-10dBFSの折り返しイメージが生じています。このように、適切なアンチエイリアシング・フィルタをADCの前段に配置していない場合、オーバーサンプリングとデシメーションを適用することで、デジタル・フィルタによる折り返しイメージが生成される可能性があります。アナログ信号帯域に重なるノイズを除去するために、アンチエイリアシング・フィルタを適切に使用しなければなりません。

ナイキスト周波数の2倍よりも低い場合に生じる折り返し

まとめ

高精度のADCを使用するアクイジション・システムにおいて目標を達成するには、フィルタの実装について解決すべき課題や検討すべき事柄があります。現実のSAR型ADCやΣΔ型ADCの入力部にアナログ・フィルタを接続する際には、システムの許容誤差の範囲を超えることがないよう注意しなければなりません。また、デジタル・フィルタを実装する際には、プロセッサ側に誤差を含んだ信号を引き渡すことがないよう考慮する必要があります。これらは決して簡単なことではありません。システムの仕様や応答時間、コスト、設計、リソースに関するトレードオフが必要になるため、非常に難易度の高い作業になります。

|

High for high performance filters |

参考資料

Mark Holdaway「Designing Antialias Filters for ADCs」EDN, 2006年

Alan Walsh「高精度SAR A/Dコンバータ(ADC)のフロントエンド・アンプとRCフィルタの設計」Analog Dialogue 46-12、2012年12月

Tim Wescott, Wescott Design Services「Sampling:What Nyquist Didn’t Say, and What to Do About It」Wescott Seminars、2015年