概要

設計リソース

設計/統合ファイル

- Schematic

- Bill of Materials

- Gerber Files

- PADS Files

- Assembly Drawing

評価用ボード

型番に"Z"が付いているものは、RoHS対応製品です。 本回路の評価には以下の評価用ボードが必要です。

- EVAL-CFTL-6V-PWRZ ($20.01) Wall Power Supply

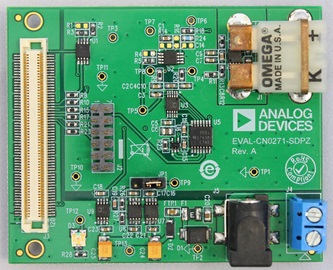

- EVAL-CN0271-SDPZ ($94.16) K-Type Thermocouple Measurement System with Integrated Cold Junction Compensation

- EVAL-SDP-CB1Z ($116.52) Eval Control Board

デバイス・ドライバ

コンポーネントのデジタル・インターフェースとを介して通信するために使用されるCコードやFPGAコードなどのソフトウェアです。

機能と利点

- 平均温度幅:-200 °C ~ +1200 °C

- K タイプ 熱電対計測システム

- 16 ビット ADC、 低温度ドリフト

- 冷接点補償機能集積

参考資料

-

CN-0271 Software User Guide2018/10/22WIKI

-

MT-068: Difference and Current Sense Amplifiers2016/05/13PDF244 kB

-

MT-101: Decoupling Techniques2015/02/14PDF954 kB

-

MT-035: Op Amp Inputs, Outputs, Single-Supply, and Rail-to-Rail Issues2015/02/14PDF115 kB

-

MT-031: データ・コンバータのグラウンディングと、「AGND」および「DGND」に関する疑問の解消2009/03/20PDF144 kB

-

MT-036: Op Amp Output Phase-Reversal and Input Over-Voltage Protection2008/12/11PDF653 kB

-

CN-0271: アンプベースの冷接点補償機能付き熱電対温度測定システム2012/06/20PDF565 kB

回路機能とその特長

図1に示す回路は、冷接点補償回路を含むフル機能の熱電対シグナル・コンディショニング回路であり、これに16ビットのシグマ・デルタ(Σ-Δ)A/Dコンバータ(ADC)を接続しています。AD8495 熱電対アンプは、Kタイプの熱電対温度を測定する、冷接点補償機能を備えたシンプルな低価格ソリューションを提供します。

AD8495に内蔵された固定ゲイン計装アンプは、小さい熱電対電圧を増幅して5 mV/°Cの出力を生成します。このアンプは同相ノイズ除去比が大きいので、長い熱電対リードに混入する恐れのある同相ノイズを阻止することができます。保護機能を追加する場合は、アンプの入力インピーダンスが高いため、フィルタ機能を容易に追加することができます。

AD8476差動アンプは、正確な信号レベルと同相電圧を提供してAD779016ビットΣ-Δ ADCを駆動します。

この回路は、熱電対シグナル・コンディショニングと高分解能のAD変換向けに小型で低価格のソリューションを提供します。

回路説明

熱電対は温度測定に幅広く使用されているシンプルな部品で、2本の異種金属線を接合したものでできています。これらの金属線の一端を接合した部分が測定接点で、温接点とも呼ばれます。熱電対のもう一端は、計測機器につながる金属線に接続されます。この接続により生じるもう1つの接点が基準接点で、冷接点とも呼ばれます。測定接点温度(TMJ)を得るには、熱電対が生じる差動電圧を知る必要があります。また、基準接点温度(TRJ)が生成する誤差電圧も知る必要があります。基準接点の誤差電圧を補償することを冷接点補償といいます。出力電圧が温接点の測定値を正確に反映するように、デバイスは基準(冷)接点温度のあらゆる変化を補償する必要があります。

この回路では、AD8495熱電対アンプを5V単電源で使用しています。AD8495の出力電圧は5mV/°Cに対して校正されています。5V単電源での出力は、15°C~950°Cの温度範囲に対応して、約75mV~4.75 Vの間で直線的に変化します。AD8495の出力がAD8476ユニティ・ゲイン差動アンプの非反転入力を駆動すると、シングルエンド入力が差動出力に変換されAD7790 16ビットΣ-Δ ADCを駆動します。

AD8495の入力の前に差動/同相ローパス・フィルタを使用することによりRF信号の発生を抑え、信号がAD8495に達した場合でも、整流して温度の変動のように見せることができます。2本の100Ω抵抗と1 µFのコンデンサで、カットオフ周波数が800Hzの差動フィルタを形成しています。また、2個の0.01µFコンデンサでカットオフ周波数が160kHzの同相フィルタを形成しています。AD7790 ADCに信号が入力される前段で、AD8476の出力に同様のフィルタを使用します。

AD8495の入力は、反対側の電源レールによる最大25Vの入力電圧変動から保護されます。たとえば、この回路では、5Vの正電源レールとGNDに接続された負電源レールにより、デバイスは−20V~+25Vの入力電圧に確実に耐えることができます。リファレンス・ピンと検出ピンの電圧は電源レールから0.3Vを超えてはなりません。アンプへの電源供給前に信号源がアクティブになる可能性のある電源シーケンスの問題を抱えるアプリケーションでは、この機能が特に重要です。

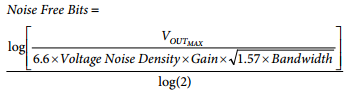

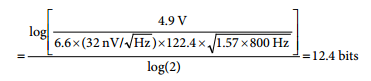

システムの理論上の分解能は、AD8495の帯域幅、電圧ノイズ密度、およびゲインから計算できます。ピークtoピーク(ノイズ・フリー・コード)分解能(ビット)は次のようになります。

AD8476は消費電力が非常に小さい完全差動の高精度アンプで、レーザ・トリミングしたユニティ・ゲイン用の10kΩ薄膜ゲイン抵抗を内蔵しています。このデバイスは、AD8495に対して比較的高い負荷インピーダンスを示すので、このアプリケーションには最適です。

AD7790は、低周波計測アプリケーション向けの低消費電力、フル機能アナログ・フロントエンドです。このデバイスには、バッファ付きまたはバッファなしを選択できる差動入力を1つ備えた低ノイズの16ビットΣ-Δ ADCが内蔵されています。

テスト結果

回路の性能を示す重要な指標が、直線性誤差の大きさです。AD8495の出力は、−25°C~+400°Cの範囲で2°C以内と高精度です。この範囲の内外を問わず出力動作時の精度をさらに高めるには、直線性補正アルゴリズムをソフトウェアに実装する必要があります。CN-0271の評価ソフトウェアは、NISTの熱電対電圧のルックアップ・テーブルを使用して、15°C~950°Cの範囲で1°C以内の出力誤差を実現します。

図2は、AD8495の性能を、CN-0271のシステムおよびそのADC出力に直線性補正を加えた結果と比較したものです。アルゴリズムのソフトウェアへの実装方法については、AN-1087アプリケーション・ノート「AD8494/AD8495/AD8496/AD8497を使用する際の熱電対の直線化」を参照してください。

システムのノイズ性能は回路の精度にとっても重要です。図3に1,000個の測定サンプルのヒストグラムを示します。このデータは評価ボードのEVAL-SDP-CB1Zシステム・デモ用プラットフォーム(SDP-B)に接続されたCN-0271の評価ボードを使って得られたものです。セットアップの詳細については「回路の評価とテスト」のセクションで説明します。

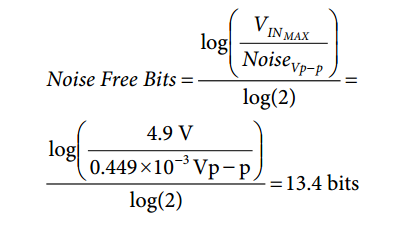

測定されたピークtoピーク・ノイズは約6LSB(1LSB = 4.9V ÷ 65536 = 74.8µV)で、0.449mVp-pとノイズ・フリー分解能の13.4ビットに対応しています。

熱電対の固定入力電圧の分解能測定値はAD8495の理論上の出力ノイズから予測されるノイズ・フリー・ビットとほぼ同じビット数になるので、上記からノイズ・フリー分解能がコンバータによって低下しないことがわかります。

この回路ノートに関する設計サポート・パッケージは、www.analog.com/CN0271-DesignSupport で入手できます。

バリエーション回路

負温度を測定するには、リファレンス・ピンに電圧を加えて0°Cでの出力電圧をオフセットさせます。AD8495の出力電圧は次のようになります。

VOUT = (TMJ × 5 mV/°C) + VREF

両電源で動作する回路に変更を加えることにより、Kタイプの熱電対の全温度範囲である−200°C~+1250°Cを測定することができます。AD8495を単電源で動作させると、周囲温度を下回る温度の測定値は、出力が電源レール付近で飽和し始めるため、非線形になります。低温で高精度を維持するには、両電源を使用するか、またはリファレンス・ピンに適切なオフセット電圧を加えることにより、出力をレベルシフトさせます。

AD8494はJタイプの熱電対向けに校正されています。また、AD8494とAD8495はともに0°C~50°Cの範囲の基準接点に対して最適化されています。

AD8496(Jタイプ)とAD8497(Kタイプ)は25°C~100°Cの範囲の基準接点に対して最適化されています。

この回路は、優れた安定性と精度で動作することが実証されています。

回路の評価とテスト

この回路は、EVAL-CN0271-SDPZ回路ボードとシステム・デモ用プラットフォーム(SDP-B)コントローラ・ボード(EVAL-SDP-CB1Z)を使用します。2枚のボードは120ピン・コネクタを備えているので、短時間で組み立てて回路の性能を評価することができます。EVAL-CN0271-SDPZボードには、この回路ノートで説明したように、評価対象の回路が含まれています。SDP-Bコントローラ・ボードは、EVAL-CN0271-SDPZ回路ボードからデータをキャプチャするためにCN-0271評価用ソフトウェアと併用します。

必要な装置

以下の装置類が必要になります。

- USBポート付きPCおよびWindows® XP、Windows Vista® (32ビット)またはWindows® 7 (32ビット)

- EVAL-CN0271-SDPZ回路評価ボード

- SDP-Bコントローラ・ボード(EVAL-SDP-CB1Z)またはSDP-Sコントローラ・ボード(EVAL-SDP-CS1Z)

- CN-0271 SDP評価用ソフトウェア

- 6V電源(EVAL-CFTL-6V-PWRZ)または同等DC電源

評価開始にあたって

CN-0271評価用ソフトウェアCDをPCのCDドライブにセットして評価用ソフトウェアをロードします。マイコンピュータから評価用ソフトウェアCDを挿入したドライブを探します。

機能ブロック図

回路ブロック図についてはこの回路ノートの図1を、回路図についてはファイルEVAL-CN0271-SDPZ-SCH-RevA.pdfをご覧ください。このファイルはCN-0271 設計サポート・パッケージに含まれています。

セットアップ

EVAL-CN0271-SDPZ回路基板の120ピン・コネクタをSDP-Bコントローラ・ボード(EVAL-SDP-CB1Z)のCON Aコネクタに接続します。120ピン・コネクタの両端にある穴を利用し、ナイロン製ハードウェアを使って2枚の基板をしっかり固定します。

電源を切って、EVAL-CFTL-6V-PWRZのプラグをボードのJ5と表示されたバレル・コネクタに差し込みます。これが使用できない場合は、+6VピンとGNDピンをボードのJ4にある2つのピン・スクリューに接続します。また、SDP-Bボードに付属しているUSBケーブルをPCのUSBポートに接続します。

次いで、Kタイプ熱電対コネクタの一端をボードのJ1に、もう一端をテスト装置に接続します。

テスト

評価用ソフトウェアを起動し、PCからのUSBケーブルをSDP-BボードのミニUSBコネクタに接続します。USBによる通信が確立すると、SDP-Bボードを使ってEVAL-CN0271-SDPZボードとの間のシリアル・データの送受信およびキャプチャを行うことができます。

図4に、CN-0271 SDP-B評価用ソフトウェアのインターフェースのスクリーンショットを図5にEVAL-CN0271-SDPZ評価ボードとSDP-Bボードの写真を示します。SDP-Bボードに関しては、UG-277ユーザー・ガイドを参照してください。