概要

設計リソース

設計/統合ファイル

- Schematic

- Bill of Materials

- Gerber Files

- Altium Files

- Assembly Drawing

評価用ボード

型番に"Z"が付いているものは、RoHS対応製品です。 本回路の評価には以下の評価用ボードが必要です。

- EVAL-CN0337-PMDZ ($47.08) 2-Bit, 300 kSPS, Single-Supply, Fully Isolated RTD Temperature Measurement System with 3-Wire Compensation

- EVAL-SDP-CB1Z ($116.52) Eval Control Board

- SDP-PMD-IB1Z ($64.74) PMOD to SDP Interposer Board

デバイス・ドライバ

コンポーネントのデジタル・インターフェースとを介して通信するために使用されるCコードやFPGAコードなどのソフトウェアです。

機能と利点

- フレキシブルなRTDコンディショニングと変換

- 温度補償

- 完全絶縁

参考資料

-

CN0337 Software User Guide2018/10/12WIKI

-

MT-101: Decoupling Techniques2015/02/14PDF954 kB

-

CN0337: 3 線補償機能を備えた 12 ビット、300kSPS、単電源、完全絶縁のRTD 温度計測システム2014/03/20PDF606 K

回路機能とその特長

図1の回路は、3個のアクティブ・デバイスのみを使用する、完全絶縁型12ビット、300kSPS RTD温度計測システムです。このシステムはPt100 RTDの出力を処理するもので、標準3線接続を使ってリード線補償を行うための先進的回路を搭載しています。この回路は3.3V単電源で動作します。室温でキャリブレーションを行った後の総合誤差は±10℃の温度変化に対して±0.24% FSR未満なので、各種工業用温度計測に最適です。

この組み合わせは回路のフットプリントが小さいので、精度、コスト、サイズが重要な温度計測に対する業界最先端のソリューションとなります。データと電源の両方が絶縁されているので、この回路は高電圧、さらには多くの場合過酷な産業分野の環境で発生するグラウンド・ループ干渉に対しても堅牢です。

この3線RTDリード線補償用の新しい回路は、ブルガリアのヴァルナにあるヴァルナ工科大学の電気電子工学部の准教授Hristo Ivanov Gigov博士と、技術者で博士課程の学生Stanimir Krasimirov Stankov氏によって開発されたものです。

回路説明

回路の入力段は、RTDに対する3線接続補償を使ったRTDシグナル・コンディショニング回路です。この回路は、RTDの入力抵抗の範囲(0°C~300°Cの温度範囲に対して100Ω~212.05Ω)をADCの入力範囲(0V~2.5V)に対応する電圧レベルに変換します。

RTDの励起電流は、AD8608クワッド・オペアンプの4つのうちの1つのオペアンプU1Cから供給されます。100mVのリファレンス電圧VRは、2.5VのADCリファレンスによって駆動されるR8/R9分圧器から生成されます。これにより、VR/(R1||R2)のRTD励起電流(約1.05mA)が発生します。

この励起電流により、0°Cから300°Cへの温度変化に対してRTD両端に約117.6mV(105mVから222.6mV)の電圧変化が生じます。オペアンプU1Aはこの電圧変化を19.6倍増幅し、2.3Vの出力スパンを生成します。オペアンプU1Aの出力が、直線性を維持するためのヘッドルームを100mVとした場合にADCの入力範囲(0V~2.5V)に一致する0.1V~2.4Vになるように、抵抗R1と並列に抵抗R2を接続して出力をシフトしています。この回路ノートで後述するように、抵抗値は他の一般的な温度範囲に合わせて変更することができます。

この回路は単一電源動作が可能な設計になっています。AD8608の最小出力電圧の仕様は、負荷電流を10mAとした場合、−40°C~+125°Cの全温度範囲に対して、2.7V電源では50mV、5V電源では290mVです。電源が3.3V、負荷電流が1mA未満で温度範囲がこれより狭い場合は、最小出力電圧は控えめに見積もって45mV~60mVになります。

部品の許容誤差を考慮し、安全マージンを確保するために最小出力電圧(範囲の下限)は100mVに設定されます。出力範囲の上限は、ADC入力の正側の振幅に対して100mVのヘッドルームを与えるため2.4Vに設定されます。したがって、オペアンプの公称出力電圧範囲は0.1V~2.4Vになります。

オペアンプU1Bは、AD7091R(U3)ADCの2.5Vの内部電圧リファレンスをバッファするために使用されています。

クワッドのAD8608オペアンプがこのアプリケーションに選択された理由は、低オフセット電圧(最大75μV)、低バイアス電流(最大1pA)、低ノイズ(最大12nV/√Hz)であるからです。消費電力は3.3V電源でわずか18.5mWです。

オペアンプU1Dは、リード線の抵抗r1とr2によって生じる誤差を補償する3線補正信号を備えています。ポイントAからTP1までのゲインは+19.6、ポイントBからTP1までのゲインは−39.2です。ポイントAの電圧には、r1とr2両端の電圧降下に等しい正の誤差項が含まれています。ポイントBの電圧には、r2両端の電圧降下に等しい正の誤差項が含まれており、r3両端の小さな電圧降下は無視できます。ポイントBからTP1までのゲインは負の値であり、ポイントAからTP1までのゲインの2倍になるので、r1 = r2と仮定すると、r1とr2両端の電圧降下による誤差はキャンセルされます。

帯域外ノイズを低減するため、オペアンプの出力段の後に単極RCフィルタ(R11/C9)が接続されます。RCフィルタのカットオフ周波数は664kHzに設定されます。産業分野における低周波数ノイズに備えて、フィルタのカットオフ周波数を下げるために追加の2次フィルタ(コンデンサC10とC11を追加したもの)が使用されます。この場合、AD7091Rは最大スループット・レートでは動作していません。変換速度を上げるためには、C10とC11を未実装のままにする必要があります。

AD7091R 12ビット1MSPS SAR ADCが選択された理由は、消費電力が3.3Vで349μA(1.2mW)ときわめて低いからです。これは市販のどの競合製品よりも大幅に低い値です。また、AD7091Rは標準的なドリフトが±4.5ppm/°Cの2.5Vリファレンスを内蔵しています。入力帯域幅は7.5MHzで、高速シリアル・インターフェースはSPI互換です。AD7091Rはフットプリントの小さな10ピンMSOPパッケージで供給されます。

この回路(ADuM5401アイソレータを除く)の総消費電力は、3.3V電源での動作時に約20 mWになります。

ADuM5401(Cグレード)クワッド・チャンネル・デジタル・アイソレータにより、ガルバニック絶縁が行われます。絶縁された出力データに加えて、ADuM5401は絶縁された+3.3Vも回路に供給します。絶縁が不要な場合には、通常の回路動作にADuM5401は必要ありません。DC/DCコンバータを内蔵した4チャンネル、2.5kVアイソレータのADuM5401は、小型16ピンSOICパッケージを採用しています。ADuM5401のクロックが7MHzのときの消費電力は約140mWです。

AD7091Rは、1MSPSのサンプリング・レートを実現するために50MHzのシリアル・クロック(SCLK)を必要とします。ただし、ADuM5401(Cグレード)アイソレータの最大データレートは25Mbpsで、12.5MHzの最大シリアル・クロック周波数に相当します。さらに、SPIポートではSCLKの立下がりエッジでデータをプロセッサにクロック出力する必要があるので、ADuM5401を介した総合往復伝搬遅延(最大120ns)によって上限のクロック周波数が1/120ns = 8.3MHzに制限されます。

AD7091Rは12ビットADCですが、プロセッサのシリアル・ポートの要件に対応させるため、シリアル・データは16ビット・ワードにフォーマットされています。したがって、サンプリング周期TSは、AD7091Rの650nsの変換時間、58ns(データシートから要求される予備時間のt1遅延+ tQUIET遅延)、SPIインターフェースのデータ転送用16クロック・サイクルで構成されます。

TS = 650 ns + 58 ns + 16 × 120 ns = 2628 ns

fS = 1/TS = 1/2628 ns = 380 kSPS

安全マージンを確保するため、7MHzの最大SCLKと300kSPSの最大サンプリング・レートを推奨します。デジタルSPIインターフェースは、12ピンPmod互換コネクタ(Digilent Pmod仕様)を使ってマイクロプロセッサの評価ボードに接続できます。

回路設計

図2に示す回路は、100Ω~212.05ΩのRTD抵抗の変化をADCの入力範囲に対応する0.1V~2.4Vの出力電圧変化に変換します。さらに、この回路は配線抵抗r1とr2に伴う誤差を除去します。

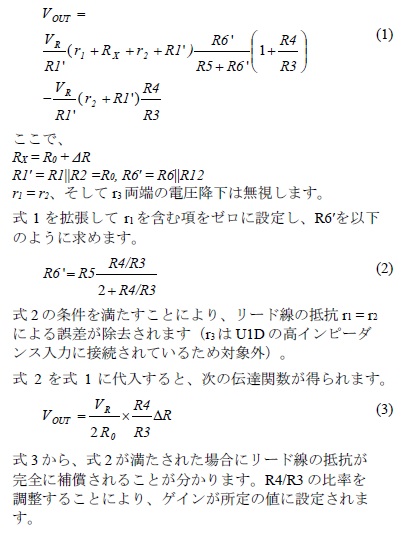

図2の回路の伝達関数は、重合わせの原理を使って次のように求められます。

ゲイン、出力オフセット、および抵抗の値と許容誤差の計算

0°C~300°Cの温度範囲では、RTDのPt100抵抗の範囲は100Ω~212.05Ω、図2の回路の入力抵抗の変化ΔRは0Ω~112.05Ωです。したがって、回路のゲインは式3から次のようになります。

この条件が満たされていると、0°CでR1′ = R0 = 100 Ω、VOUT = 0 Vになります。

ここでは回路の出力オフセットを0.1Vに設定する必要があります。出力をシフトさせる容易な方法は、抵抗R1′をR0よりわずかに小さくすることです。これによりゲインが比例して変わることに注意してください。0.1Vの出力オフセットは2.3Vの総合スパンの約4.35%なので、比率R1′/R0を0.9565未満にする必要があります。高出力レベルを2.4Vに等しい値に維持するため、比率R4/R3を比例して補正することができます。たとえば、R4 = 0.9565 × 41.06 × R3 = 39.27kΩとします。図1に示されているように標準抵抗値を使用することにより、この回路は必要なゲインと出力オフセットに対して妥当な近似値を得ています。抵抗R1′は、抵抗R2 = 1.91kΩを抵抗R1 = 100Ωと並列に接続することによって形成されます。

その他の温度範囲や温度センサー(たとえば、Pt200、Pt500、Pt1000、Pt2000)では、抵抗値を以下のように再計算する必要があります。

- R3の値(たとえば、1kΩ)を選択し、R5 = R6 = 2R3とします。

- センサーによる励起電流IRを選択し、VR = IR × RX_lowを計算します。

ここで、RX_lowは温度範囲の下限のRTDの抵抗です。 - R9の値(たとえば、R9 = 1kΩ)を選択し、R8を次のように計算します。

ここで、VREF = 2.5 VはADCのリファレンス電圧です。 - A = 0.0435 × (RX_high – RX_low) を計算します。ここで、 Aはこの計算手順に必要な暫定定数です。

RX_highは温度範囲の上限のRTDの抵抗です。 - R0 = RX_low – Aを計算します。

- R0 = R1 × R2/(R1 + R2) を計算し、R1とR2の値を選択します。

R1にはRX_lowに等しい標準値を選択し、R2を計算することを推奨します。 - 次式を計算します。

ここで、Bはこの計算手順に必要な暫定定数です。 - R4 = B × R3を計算し、R12 = R4となるようにします。

精度の解析

式1から、全ての抵抗が総合誤差に影響を与えることが分かります。これらの値を慎重に選択すると、標準値の抵抗に置き換えることによる全体の誤差を数パーセント未満にすることができます。ただし、必要なヘッドルームが確保されていることを確認するため、式1を使って100Ω入力と212.05Ω入力に対するオペアンプU1Aの出力を再計算します。実際の回路では、最も近い入手可能な標準抵抗値を選択します。抵抗Rl、R2、R8、R9は0.1%(25ppm/°C)のものとし、回路のその他の抵抗(R3、R4、R5、R6、R12)は1%(100 ppm/°C)のものとします。

このタイプの回路の絶対精度は主に抵抗によって決まるので、標準値への置換えと抵抗の許容誤差による誤差を除去するため、ゲインとオフセットのキャリブレーションをする必要があります。

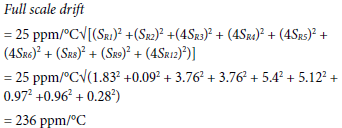

全体の誤差に対する抵抗の温度係数の影響

式1から、出力電圧が9本の抵抗(R1、R2、R3、R4、R5、R6、R8、R9、R12)の関数であることが分かります。

シミュレーション・プログラムを使って、9本の抵抗のそれぞれの小さな変化に対するTP1でのフルスケール出力電圧の感度を計算しました。回路へ入力したRTD抵抗は212Ωです。それぞれの感度を計算した結果、SR1 = 1.83、SR2 = 0.09、SR3 = 0.94、SR4 = 0.94、SR5 = 1.35、SR6 = 1.28、SR8 = 0.97、SR9 = 0.96、SR12 = 0.07となりました。各温度係数が2乗和平方根(RSS)法を使って結合されると仮定すると、R1、R2、R8、R9に25ppm/°Cの抵抗を、R3、R4、R5、R6、R12に100ppm/°Cの抵抗を使用した全体のフルスケール・ドリフトはほぼ次のようになります。

236ppm/°Cのフルスケール・ドリフトは0.024% FSR/°Cに相当します。±10°Cの温度変化に対する誤差は±0.24% FSRになります。 9本全ての抵抗に25ppm/°Cの抵抗を使用すると、フルスケール・ドリフトは約80ppm/°C、つまり0.008% FSR/°Cまで減少します。

抵抗の許容誤差、AD8608オペアンプのオフセット(75 μV)、AD7091Rのオフセットによって生じる誤差はキャリブレーション後に除去されます。ただし、オペアンプの出力が必要とする範囲内であることを、計算して検証する必要はあります。

全体の誤差に対する能動部品の温度係数の影響

AD8608オペアンプのDCオフセット(75 μV)とAD7091R ADCのDCオフセットは、キャリブレーションによって除去されます。

ADC AD7091Rの内部リファレンスのオフセット・ドリフトは、標準4.5ppm/°C、最大25ppm/°Cです。

AD8608オペアンプのオフセット・ドリフトは、標準1μV/°C、最大4.5μV/°Cです。

50 ppm/°Cまたは100ppm/°Cの抵抗を使用した場合、抵抗のドリフトが全体のドリフトに最も影響を与え、能動部品によるドリフトは無視できることに注意してください。

リード線の抵抗の補償

図1の回路では、リード線の抵抗(r1、r2、r3)は全て補償されています。ただし、式3に不整合が存在すると、リード線r1とr2の測定誤差が加わります。3本目のリード線r3はU1Dの高インピーダンス入力に接続されているため、回路に影響を与えません。

式3に不整合が存在しても、リード線r1とr2によって回路の直線性が影響されることはありません。

RTDのリニアライゼーション

図1の回路は、RTDの抵抗変化に対して直線的です。ただし、RTDの伝達関数(抵抗の温度特性)は非直線的です。したがって、RTDの非直線性誤差を除去するためにリニアライゼーションが必要です。マイクロコントローラが搭載されているシステムの場合、このリニアライゼーションは一般にソフトウェアで行われます。 アプリケーションノートAN-709 で、Pt100 RTDセンサーのリニアライゼーション技術について説明しています。CN0337評価用ソフトウェアでは、Pt100センサーの非直線性誤差を除去するために同様の技術が使用されています。

2ポイント・キャリブレーション前後のテストデータ

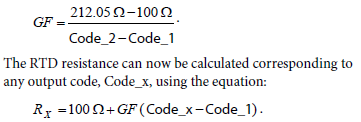

2ポイント・キャリブレーションを行うには、まず100Ωの高精度抵抗を入力に接続し、ADC出力コードをCode_1として記録します。次に212.05Ωの高精度抵抗を入力に接続し、ADC出力コードをCode_2として記録します。ゲイン係数を次式で計算します。

キャリブレーション前の誤差は、部品の公称値を使って計算した理論上の伝達関数とキャリブレーションなしの実際の回路の伝達関数を比較することによって得られます。テスト回路は±0.1%、±25ppm/°Cの抵抗R1、R2、R8、R9を除き±1%、±100ppm/°Cの抵抗を使って作成し、テストは室温でプリント回路ボード(PCB)を使って行いました。 いくつかのボードのキャリブレーション前後のテスト結果を図3のグラフに示します(温度変化はなし)。このグラフから分かるように、キャリブレーション前の最大誤差は約0.27% FSRです。キャリブレーション後、誤差はADCの1.5LSB誤差にほぼ相当する±0.037% FSRまで減少します。

PCBレイアウトに関する検討事項

高精度が不可欠な回路では、ボード上の電源とグラウンド・リターンのレイアウトを検討することが重要です。PCBでは、デジタル部とアナログ部をできるだけ分離する必要があります。このシステムのPCBはシンプルな2層構造ですが、4層構造にすると良好なEMSが得られます。レイアウトとグラウンディングの詳しい説明については チュートリアルMT-031を、デカップリング技術の情報についてはチュートリアルMT-101を参照してください。適切にノイズを抑え、リップルを下げるため、AD8608への電源を10μFと0.1μFのコンデンサでデカップリングします。これらのコンデンサはできるだけデバイスの近くに配置し、0.1μFコンデンサには低ESR値のものを使用します。全ての高周波数デカップリングにはセラミック・コンデンサを推奨します。電源ラインは、できるだけ幅の広いパターンの低インピーダンス経路とし、電源ライン上のグリッチによる影響を減らす必要があります。DC/DCコンバータを内蔵したisoPowerデバイスADuM5401は、入力と出力の電源ピンに電源バイパスを必要とします。ピン1とピン2の間およびピン15とピン16の間には、チップ・パッドのできるだけ近くに低ESRのバイパス・コンデンサを設置する必要があります。ノイズとリップルを抑えるときは、少なくとも2個のコンデンサの並列組み合わせが必要です。VDD1およびVISOのコンデンサの推奨値は0.1μFと10μFです。小さい方のコンデンサは低ESRでなければなりません。たとえば、セラミック・コンデンサを使用することを推奨します。低ESRコンデンサの両端と入力電源ピンの間の合計リード長は2mmを超えてはなりません。バイパス・コンデンサを2mmより長いパターンで設置すると、データ破損を生じることがあります。両方の共通グラウンド・ピンがパッケージの近くで相互接続されていない場合は、ピン1とピン8の間およびピン9とピン16の間のバイパスを検討します。詳細についてはADuM5401のデータシートを参照してください。

回路図、ボード・レイアウト、部品表(BOM)などが完備された文書パッケージについては、 www.analog.com/CN0337-DesignSupport をご覧ください。

高電圧耐性

このPCBは2500Vに対する基本的な絶縁方法に沿って設計されています。2500Vを超える高電圧テストは推奨しません。この評価ボードを高電圧で使用する際には適切な注意を払う必要があります。また、評価ボードは高電圧試験(hipot試験または絶縁耐圧試験としても知られている)も安全性の認定も行われていないため、安全機能に関してはこのボードに依存しないでください。

バリエーション回路

この回路は、図に示された部品の値を使うことで、優れた安定性と高精度を提供します。この構成で他のオペアンプやADCを使用して、抵抗変化の入力範囲をデジタル出力に変換したり、他のさまざまな応用が可能です。

0°C ~300°C以外の入力温度範囲に対応するには、図1の回路を「回路デザイン」のセクションで説明した推奨事項に従って設計変更します。Pt100 RTDセンサーを使用した場合の標準的な温度範囲の計算値をいくつか表1に示します。

| 温度範囲 |

R1 |

R2 |

R4, R12 |

| -50°C ~ 50°C |

79.4Ω |

7.82kΩ |

93.1kΩ |

| 0°C ~ 50°C |

100Ω |

11.7kΩ |

237kΩ |

| 0°C ~ 100°C |

100Ω |

5.83kΩ |

118kΩ |

| 0°C ~ 200°C |

100Ω |

2.91kΩ |

59kΩ |

| 0°C ~ 300°C |

100Ω |

1.91kΩ |

39.2kΩ |

| 0°C ~ 400°C |

100Ω |

1.45kΩ |

29.4kΩ |

| 0°C ~ 500°C |

100Ω |

1.17kΩ |

23.7kΩ |

| 0°C ~ 600°C |

100Ω |

976Ω |

19.6kΩ |

| 0°C ~ 700°C |

100Ω |

837Ω |

16.9kΩ |

| 0°C ~ 800°C |

100Ω |

723Ω |

14.7kΩ |

1 これ例外の抵抗値は図1に記載しています(R5 = R6 = 2kΩ、R3 = 1kΩ、R8 = 26.7kΩ、R9 = 1.1kΩ)

AD7091はAD7091Rの類似製品ですが、電圧リファレンスの出力を備えておらず、入力電圧範囲が電源電圧と同じです。AD7091はADR391 2.5 Vリファレンスと共に使用できます。ADR391はバッファリングが不要です。

ADR391は高精度の2.5Vバンドギャップ電圧リファレンスで、低消費電力と高精度(温度ドリフト9ppm/°C)を特長としており、小型TSOTパッケージに収容されています。

AD8605とAD8606は、AD8608クワッド・アンプのシングルおよびデュアル・バージョンです。異なる構成が必要な場合は、これらのデバイスをAD8608と置き換え可能です。

AD8601、AD8602、AD8604はそれぞれシングル/デュアル/クワッドのレールtoレール入力/出力の単電源アンプで、非常に低いオフセット電圧と広い信号帯域幅を特長としており、AD8605、AD8606、AD8608の代わりに使用できます。

AD7457は100kSPS、低消費電力の12ビットSAR ADCで、300kSPSのスループット・レートは必要ない場合に、ADR391電圧リファレンスと組み合わせてAD7091Rの代わりに使用できます。

回路の評価とテスト

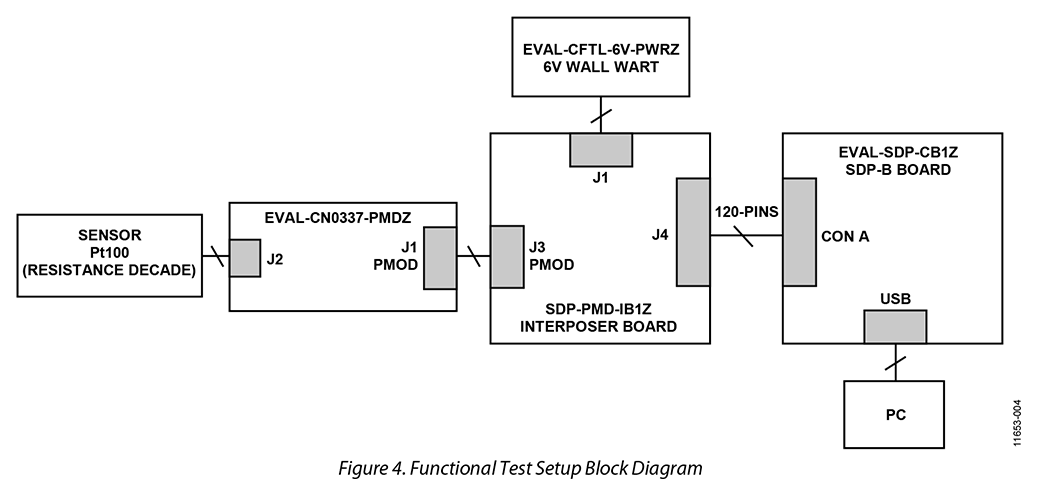

この回路には、EVAL-CN0337-PMDZ回路ボード、SDP-PMD-IB1Z、およびEVAL-SDP-CB1Zシステム・デモ用プラットフォーム(SDP)評価ボードが使用されています。SDP-PMD-IB1Zインターポーザ・ボードとEVAL-SDP-CB1Zボードは、120ピンのコネクタを備えています。このインターポーザ・ボードとEVAL-CN0337-PMDZボードは12ピンPmod対応コネクタを備えているので、短時間で組み立てて回路の性能を評価することができます。EVAL-CN0337-PMDZボードはこの回路ノートで説明したような評価ができる回路を備えています。SDP評価ボードはCN0337評価用ソフトウェアと共に使用して、EVAL-CN0337-PMDZ回路ボードからデータを取り込みます。

必要な装置

- USBポート付きPCおよびWindows® XP、Windows Vista® (32ビット)またはWindows® 7/8 (64ビットまたは32ビット)

- EVAL-CN0337-PMDZ回路評価ボード

- EVAL-SDP-CB1Z SDP 評価ボード

- SDP-PMD-IB1Z インターポーザ・ボード

- CN0337 評価用ソフトウェア

- 高精度の抵抗ディケード・ボックスまたはPt100センサー(抵抗ボックスを入手不可の場合、キャリブレーションを実行可能)

評価開始にあたって

CN0337評価用ソフトウェア・ディスクをPCのCDドライブにセットして、評価用ソフトウェアをロードします。CN0337評価用ソフトウェアページからこのソフトウェアの最新版のコピーをダウンロードすることもできます。[マイコンピュータ]を使用して、評価用ソフトウェアのディスクが置かれたドライブを探し、setup.exeファイルを開きます。画面上の指示に従ってインストールを終了します。全てのソフトウェア・コンポーネントをデフォルトの位置にインストールすることをお奨めします。

機能ブロック図

テスト・セットアップの機能ブロック図を図4に示します。

セットアップ

- EVAL-CFTL-6V-PWRZ(+6V DC電源)を、DCバレルジャックを使ってSDP-PMD-IB1Zインターポーザ・ボードに接続します

- SDP-PMD-IB1Z(インターポーザ・ボード)を、120ピンのコネクタ Aを使ってEVAL-SDP-CB1Z(SDPボード)に接続します

- EVAL-SDP-CB1Z(SDPボード)を、USBケーブルでPCに接続します

- EVAL-CN0337-PMDZ評価ボードを、12ピンのヘッダPmodコネクタを使ってSDP-PMD-IB1Zインターポーザ・ボードに接続します

- 抵抗ディケード・ボックス(Pt100センサー)を、端子ブロックJ2によりEVAL-CN0337-PMDZ評価ボードに接続します

テスト

評価用ソフトウェアを立ち上げます。アナログ・デバイセズのシステム開発プラットフォーム・ドライバがデバイス・マネージャに表示されていれば、ソフトウェアはSDPボードと通信を行うことができます。USB通信が確立すると、SDPボードを使ってEVAL-CN0337-PMDZボードとの間でシリアル・データの送受信およびキャプチャを行うことができます。さまざまな入力温度(抵抗値)でのデータをコンピュータに保存可能です。データ・キャプチャ用評価ソフトウェアの使用方法については、CN0337 Software User Guideに記載されています。