AD9635

新規設計に推奨A/Dコンバータ、12ビット、80MSPS / 125MSPS、デュアル、1、8V、シリアルLVDS出力

- 製品モデル

- 4

- 1Ku当たりの価格

- 最低価格:$24.00

製品の詳細

- 1.8V電源動作

- 低消費電力:チャンネルあたり115mW@125MSPS、スケーラブルな消費電力オプション付

- SNR=71dBFS(ナイキスト周波数まで)

- SFDR=93dBc@70MHz

- DNL誤差:

-0.1LSB~+0.2LSB(typ)、

INL誤差:±0.4LSB(typ)

- シリアルLVDS(ANSI-644、ディフォルト)、低消費、削減信号オプション(IEEE1596.3と同様)

- 650MHzのフル・パワー・アナログ帯域幅

- 入力電圧範囲:2V p-p

- 詳細はデータシートをご参照ください。

AD9635は、サンプル&ホールド回路内蔵のデュアル12ビット80MSPS / 125MSPSのA/Dコンバータ(ADC)であり、低価格、低消費電力、小型で使い易く設計されています。この製品は、最大125MSPSまでの変換レートで動作し、小型パッケージ・サイズを重要とするアプリケーション向けに、並外れたダイナミック性能と低消費電力化に関して最適化されています。

このADCは、フル性能動作のために1.8Vの単電源とLVPECL- / CMOS- / LVDS-互換のサンプル・クロック・レートを必要とします。ほとんどのアプリケーションでは、外付けのリファレンス電圧またはドライバ部品を必要としません。

このADCは、適切なLVDSシリアル・データ・レートを得るために、サンプル・レート・クロックを自動的に逓倍します。出力上のデータをキャプチャするためのデータ・クロック出力(DCO)と、新しい出力バイトを通知するためのフレーム・クロック出力(FCO)を備えています。各チャンネル独立したパワーダウン機能もサポートしており、AD9635、全チャンネル、フルパワー・ダウン時の消費電力は2 mW(typ)以下となります。このADCは、プログラマブルな出力クロック、データ・アライメントおよびデジタル・テスト・パターン発生器など、柔軟性を最大化しシステム・コストを最小化するような設計のための、いくつかの特長を備えています。デジタル・テスト・パターンとしては、決まった擬似乱数パターンを含んでおり、カスタムのユーザー定義のテスト・パターンもシリアル・ポート・インターフェース(SPI)を介して入力することも可能です。

AD9635はRoHS準拠、32ピンLFCSPパッケージを採用しています。仕様は工業温度範囲-40℃~+85℃にわたって規定されています。またこの製品はUS特許によって保護されています。

製品のハイライト

- 小型フットプリント:2個のADCを小型の省スペース・パッケージに収容

- 低消費電力:AD9635はチャンネルあたり115mW@125MSPS、スケーラブルな消費電力オプション付

- AD9645(14ビット、デュアルADC)とピン互換

- 使い易さ:最大500MHzの周波数で動作するデータ・クロック出力(DCO)とダブル・データ・レート(DDR)動作をサポート

- ユーザー・フレキシビリティ:SPI制御は、特別なシステムの要求に合致するための広範囲で柔軟な機能を提供

アプリケーション

- 通信関連

- ダイバーシティー無線システム

- マルチモード・デジタル・レシーバ:

GSM、EDGE、W-CDMA、LTE、

CDMA2000、WiMAX、TD-SCDMA - I/Q復調システム

- スマート・アンテナ・システム

- ブロードバンド・データ・アプリケーション

- バッテリ駆動の計測機器

- ハンドヘルド・スコープ・メータ

- ポータブル医用画像処理と超音波装置

- レーダ / LIDAR(レーザ光レーダ)

ドキュメント

データシート 2

ユーザ・ガイド 1

アプリケーション・ノート 7

技術記事 1

よく聞かれる質問 1

| 製品モデル | ピン/パッケージ図 | 資料 | CADシンボル、フットプリント、および3Dモデル |

|---|---|---|---|

| AD9635BCPZ-125 | 32-Lead LFCSP (5mm x 5mm x 0.75mm w/ EP) | ||

| AD9635BCPZ-80 | 32-Lead LFCSP (5mm x 5mm x 0.75mm w/ EP) | ||

| AD9635BCPZRL7-125 | 32-Lead LFCSP (5mm x 5mm x 0.75mm w/ EP) | ||

| AD9635BCPZRL7-80 | 32-Lead LFCSP (5mm x 5mm x 0.75mm w/ EP) |

| 製品モデル | 製品ライフサイクル | PCN |

|---|---|---|

|

5 11, 2014 - 13_0231 Assembly Transfer of Select 4x4 and 5x5mm LFCSP Products to STATS ChipPAC China. |

||

| AD9635BCPZ-125 | 製造中 | |

| AD9635BCPZ-80 | 製造中 | |

| AD9635BCPZRL7-125 | 製造中 | |

| AD9635BCPZRL7-80 | 製造中 | |

これは最新改訂バージョンのデータシートです。

ソフトウェア・リソース

必要なソフトウェア/ドライバが見つかりませんか?

ドライバ/ソフトウェアをリクエストハードウェア・エコシステム

| 製品モデル | 製品ライフサイクル | 詳細 |

|---|---|---|

| RFアンプ 1 | ||

| ADL5202 | 製造中止 | VGA(可変ゲイン・アンプ)、デジタル制御、広ダイナミック範囲、高速 |

| RF可変ゲイン・アンプ(VGA) 1 | ||

| AD8376 | 新規設計に推奨 | VGA、デュアル、超低歪 |

| クロックIC 6 | ||

| AD9516-4 | 新規設計に推奨 | 14出力のクロック発生器、1.6GHz VCO内蔵 |

| AD9517-4 | 新規設計に推奨 | クロック・ジェネレータ、12出力、1.6GHzのVCO内蔵 |

| AD9518-4 | 新規設計に推奨 | クロック・ジェネレータ、6出力、1.6GHzのVCO内蔵 |

| AD9520-4 | 新規設計に推奨 | 12 LVPECL/24 CMOS出力のクロック・ジェネレータ、1.6 GHZ VCO付き |

| AD9522-4 | 新規設計に推奨 | クロックジェネレータ、12 LVDS/24 CMOS出力、1.6 GHz VCO内蔵 |

| AD9528 | 新規設計に推奨 |

クロック・ジェネレータ、14 LVDS / HSTL出力、JESD204B対応 |

| ファンアウト・バッファ & スプリッタ 1 | ||

| AD9508 | 新規設計に推奨 | クロック・ファンアウト・バッファ、1.65GHz、出力デバイダおよび遅延調整機能付 |

| 差動アンプ 3 | ||

| ADA4927-2 | 新規設計に推奨 | 差動アンプ、ADC ドライバ、超低歪み、電流帰還型 |

| ADA4938-2 | 新規設計に推奨 | ADCドライバ、差動、超低歪み、デュアル |

| ADL5562 | 新規設計に推奨 | RF/IF用差動アンプ、超低歪み、3.3 GHz |

ツールおよびシミュレーション

Virtual Eval(仮想評価、 ベータ版)

Virtual Evalは、ADC、DAC、およびその応用製品評価を支援するウェブベースの設計ツールです。アナログ・デバイセズのサーバ上にあるモデルを使用して、重要な部品の性能特性をわずか数秒でシミュレートします。使用時は、入力トーンや外部ジッタなどの動作条件のほか、ゲインやデジタル・ダウンコンバージョンといったデバイス機能を設定してください。ノイズ、歪み、分解能、FFT、タイミング図、周波数応答プロット、その他さまざまな性能特性を確認することができます。

ツールを開くVisual Analog

VisualAnalog™は、高速ADCの選択や評価を行う設計者向けに、強力なシミュレーション/データ解析ツール・セットとユーザ・フレンドリなグラフィカル・インターフェースを組み合わせたソフトウェア・パッケージです。

ツールを開くAD9635 Simulink ADIsimADC Model

ツールを開くSパラメータ 1

AD9635 IBIS Model 1

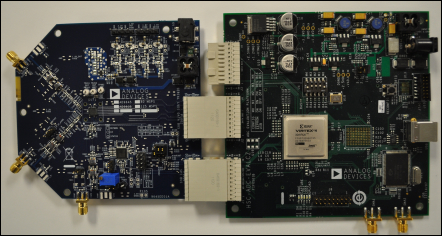

評価用キット

最新のディスカッション

AD9635に関するディスカッションはまだありません。意見を投稿しますか?

EngineerZone®でディスカッションを始める