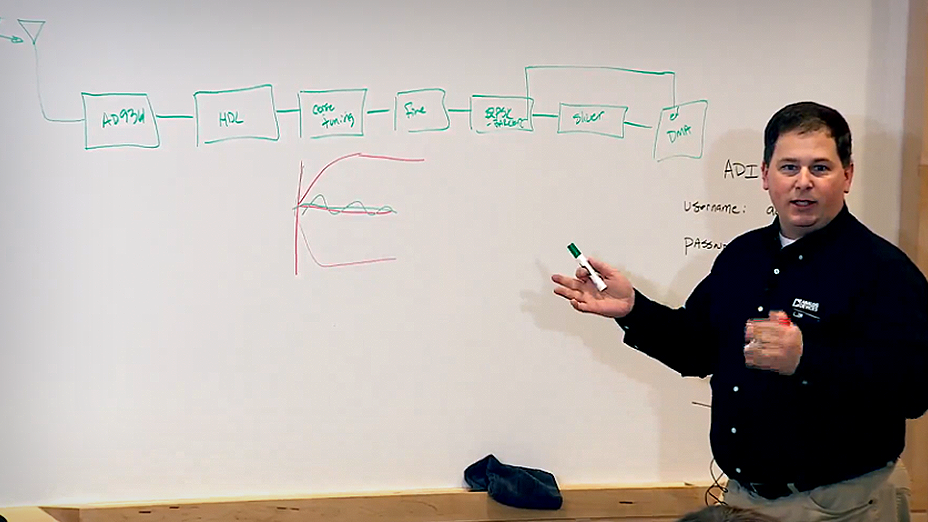

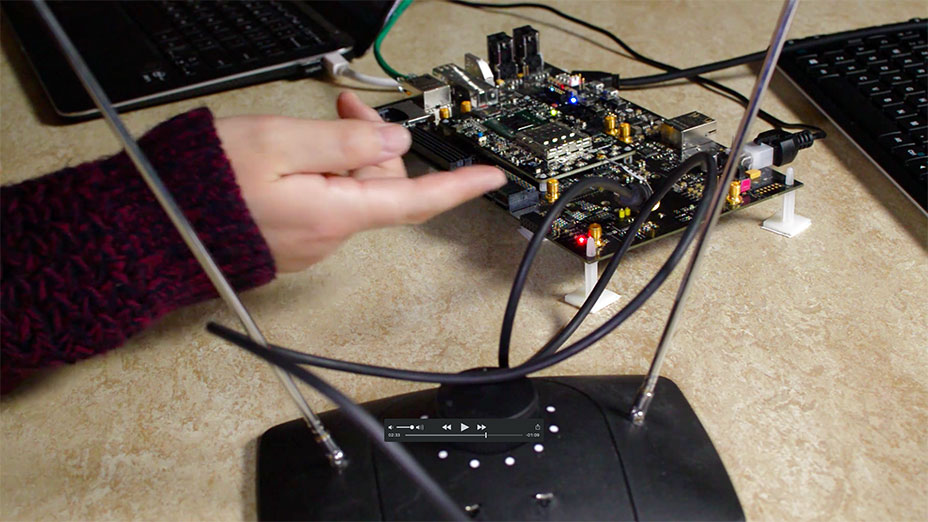

ADALM-PLUTOは、SDR(ソフトウェア無線)向けの完全なオープン・リファレンス・デザインで、アナログ・デバイセズのRF製品ベースの設計を短時間で検証し、製造までの期間を短縮する手助けとなります。このツールは、回路図、HDL、ファームウェア、組み込みLinux、ドライバ、アナログ・デバイセズのトランシーバー製品のホスト・ドライバを備えています。

設計を高速でトラッキングAD9361

新規設計に推奨RFアジャイル・トランシーバ

- 製品モデル

- 2

- 1Ku当たりの価格

- 最低価格:$224.70

製品の詳細

- 12ビットDACとADCを内蔵した、RF 2×2のトランシーバ

- トランスミッタ(TX)帯域: 47 MHz ~ 6.0 GHz

- レシ―バ(RX)帯域:70 MHz ~ 6.0 GHz

- TDDとFDD動作をサポート

- 調節可能チャンネル帯域幅(BW):200kHz以下~56MHz

- デュアルレシーバ:6つの差動または12つのシングルエンドの入力

- 優れたレシーバ感度: ノイズ指数2dB@800MHz LO

- RXゲイン制御

- リアルタイムのモニタとマニアル・ゲイン用の制御信号

- 独立した自動ゲイン制御

- デュアル・トランスミッタ: 4個の•差動出力

- 高直線性の広帯域トランスミッタ

- TX EVM:≤ 40 dB

- TX ノイズ: ノイズ・フロア ≤-157 dBm/Hz

- TX モニタ: 1 dB精度で≥66 dBのダイナミック・レンジ

- フラクショナルN シンセサイザを内蔵

- 局部発信器(LO)の最大ステップサイズ: 2.4 Hz

- 複数チップの同期

- CMOS/LVDS デジタル・インターフェース

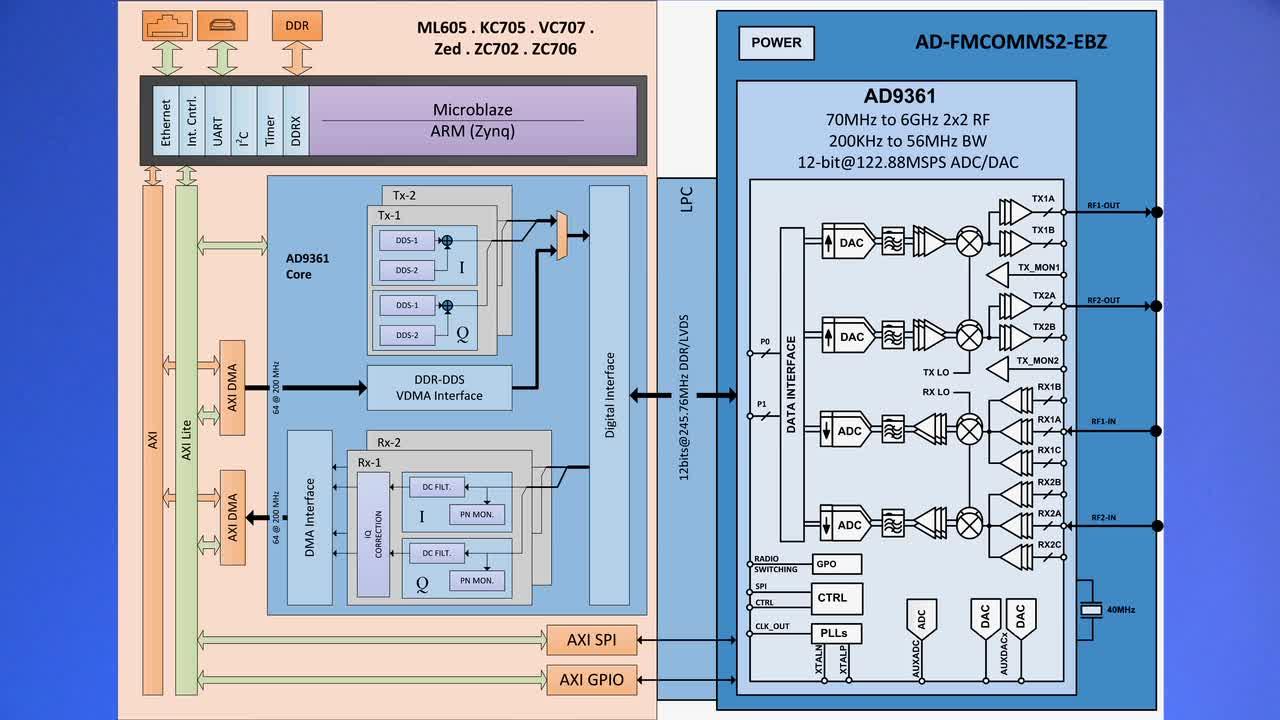

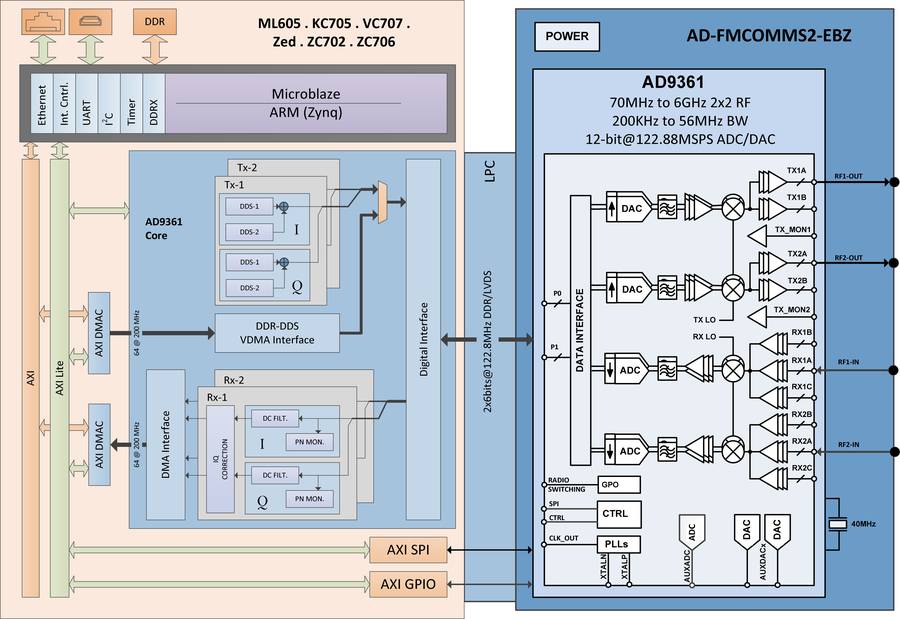

AD9361は、3G/4G基地局アプリケーションに使用できるように設計された高性能、高集積のRF Agile Transceiver™(RFアジャイル・トランシーバ)です。この製品は、そのプログラム性と広帯域により、幅広い範囲のトランシーバ・アプリケーションに最適となっています。このデバイスは、RFフロントエンドを柔軟なミックスド・シグナル・ベースバンド・セクションと内蔵の周波数シンセサイザと組み合わせており、プロセッサとのデジタル・インターフェースを設定可能にすることにより、回路設計を簡素化しています。AD9361のレシーバLOは、70MHz~6.0GHzの範囲で動作し、トランスミッタLOは47 MHz ~ 6.0 GHzの範囲で動作し、ほとんどの認可帯域と無認可帯域をカバーします。チャンネル帯域幅は200kHz以下~56MHzをサポートします。

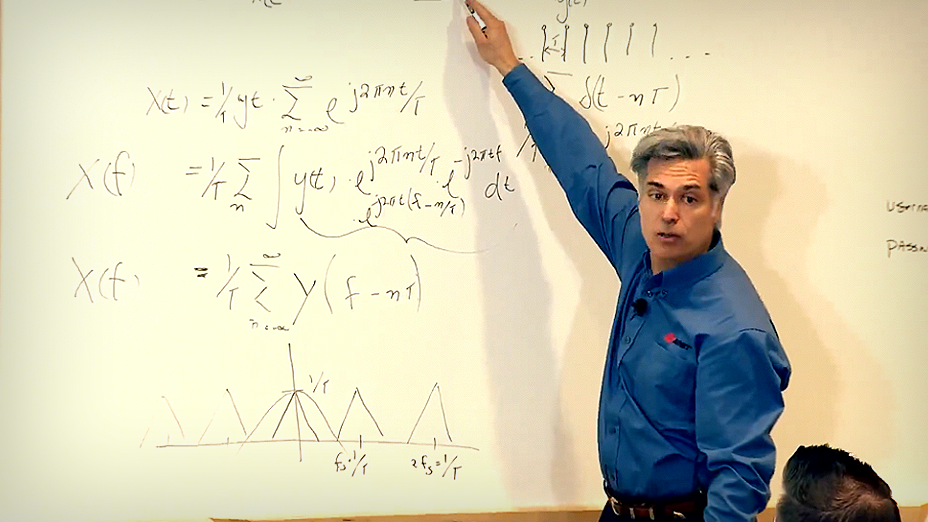

2つの独立したダイレクト・コンバージョン・レシーバは最高水準のノイズ指数と直線性を備えています。各レシーバ (RX)のサブシステムには独立の自動ゲイン制御 (AGC)、DCオフセット補正、直交補正、デジタル・フィルタリングが含まれているので、デジタル・ベースバンドにおいてこれらの機能は不要です。AD9361には又外部的に制御可能で柔軟な手動ゲイン・モードがあります。1チャンネルごとに内蔵されている2つの高ダイナミック・レンジA/D コンバータ(ADC) は受信したI 信号とQ信号をデジタル化します。そしてそれらのデジタル信号を設定可能なデシメーション・フィルタと128タップ有限インパルス応答 (FIR) フィルタを通して適切なサンプル・レートで12ビット出力信号を生成します。

トランスミッタは超低ノイズで高変調精度を実現する高ダイレクト・コンバージョン・アーキテクチャを使用します。このトランスミッタの設計は<−40 dBの最高級のTX誤差ベクトル振幅(EVM)が得られ、外部パワーアンプ(PA)の選択に大きなシステム余裕が得られます。内蔵トランスミッタ(TX) のパワー・モニタをパワー・ディテクタとして使用できるので高精度のTXパワー測定が可能です。

完全に集積化されたフェーズ・ロック・ループ(PLL)は、レシーバおよびトランスミッタの全チャンネルに、低消費電力のフラクショナル-N周波数合成を提供します。周波数分割デュープレックス(FDD)システムに要求されるチャンネル・アイソレーションは設計に組み込まれています。全てのVCOとループ・フィルターの部品は集積されています。AD9361のコアは直接1.3 Vレギュレーターから電源を供給できます。このICは標準4線シリアル・ポートと4本のリアルタイムI/O制御ピンを介して制御されます。通常の使用時における消費電力を最小化するための包括的なパワーダウン・モードが用意されています。AD9361は、10mm×10mm、144ボールのチップ・スケール・パッケージ・ボール・グリッド・アレイ(CSP_BGA)にパッケージされています。

アプリケーション

- ポイントtoポイント通信システム

- フェムトセル/ピコセル/マイクロセルの基地局

- 汎用無線システム

ユーザガイドを含む完全な設計ファイル資料パッケージを

ダウンロードしてください。

ドキュメント

データシート 1

ユーザ・ガイド 2

アプリケーション・ノート 2

技術記事 11

情報 1

ビデオ 32

ソリューション・カタログ 2

サードパーティ・ソリューション 1

Analog Dialogue 11

| 製品モデル | ピン/パッケージ図 | 資料 | CADシンボル、フットプリント、および3Dモデル |

|---|---|---|---|

| AD9361BBCZ | 144-Ball CSPBGA (10mm x 10mm x 1.7mm) | ||

| AD9361BBCZ-REEL | 144-Ball CSPBGA (10mm x 10mm x 1.7mm) |

これは最新改訂バージョンのデータシートです。

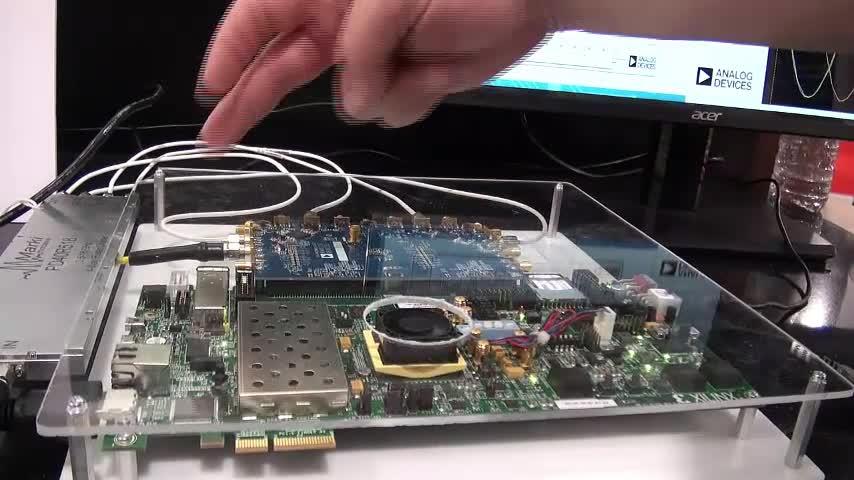

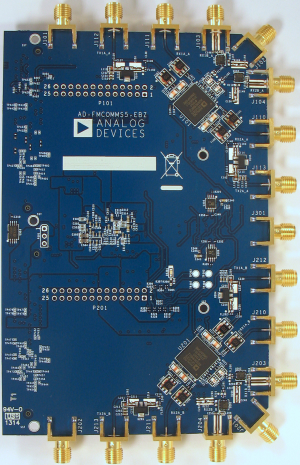

ハードウェア・エコシステム

| 製品モデル | 製品ライフサイクル | 詳細 |

|---|---|---|

| D/Aコンバータ(DAC) 1 | ||

| AD9548 | 新規設計に推奨 | クロック・ジェネレータ/シンクロナイザー、クワッド/オクタル入力ネットワーク |

| Linear Regulators 1 | ||

| ADP1755 | 製造中 | リニア・レギュレータ、ロー・ドロップアウト、調整機能付、1.2 A、低Vin |

| PLL Synthesizers 1 | ||

| ADF4351 | 新規設計に推奨 | 広帯域シンセサイザ、VCO内蔵 |

| スイッチング・レギュレータ 2 | ||

| ADP2164 | 新規設計に推奨 | ステップダウンDC-DCレギュレータ、6.5V、4A、高効率 |

| ADP5040 | 新規設計に推奨 | 1.2 Aの降圧レギュレータと2個の300 mA LDOを内蔵するMicro PMU |

| ロー・ノイズ・アンプ(LNA) & パワー・アンプ 6 | ||

| ADL5602 | 新規設計に推奨 | RF/IFゲイン・ブロック、50 MHz~4.0GHz |

| ADL5521 | 新規設計に推奨 | 低ノイズ・アンプ、400MHz~4GHz |

| ADL5523 | 新規設計に推奨 | 低ノイズ・アンプ、400MHz~4GHz |

| ADL5320 | 新規設計に推奨 | RFドライバ・アンプ、400MHz~2700MHz、¼W |

| ADL5321 | 新規設計に推奨 | RFドライバ・アンプ、2.3GHz~4.0GHz、1/4W |

| ADL5324 | 新規設計に推奨 | 400 MHz~4000 MHz、1/2 W、RFドライバ・アンプ |

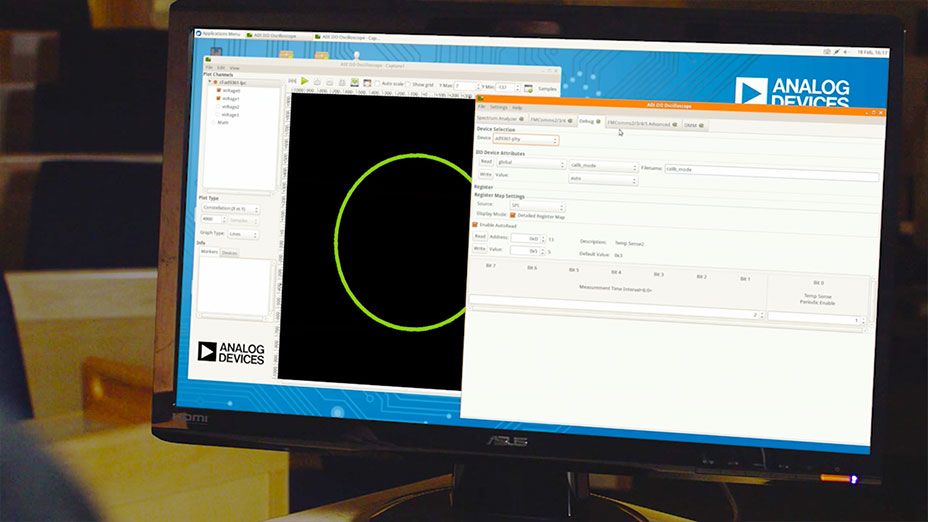

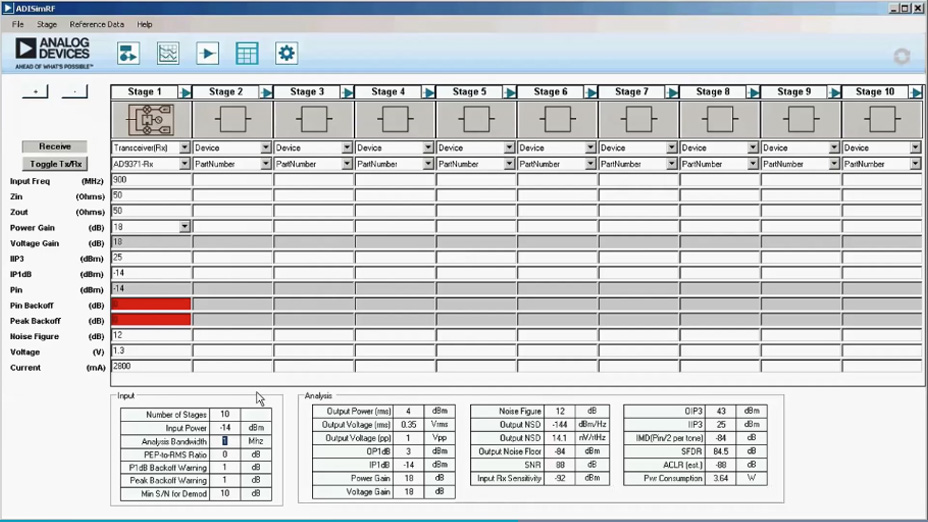

ツールおよびシミュレーション

評価用キット

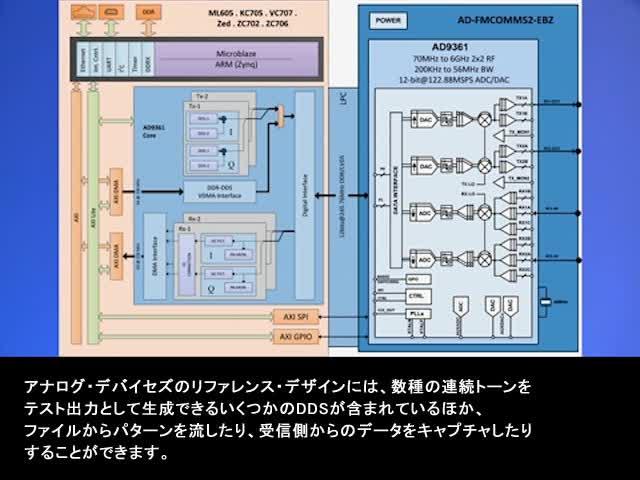

リファレンス・デザイン

最新のディスカッション

AD9361に関するディスカッションはまだありません。意見を投稿しますか?

EngineerZone®でディスカッションを始める