ADL5502

新規設計に推奨クレスト・ファクタ検出器、450~6000MHz

- 製品モデル

- 1

- 1Ku当たりの価格

- 最低価格:$7.66

製品の詳細

- 真のRMS検出器

- エンベロープピーク・ホールド出力

- 優れた温度安定性

- 温度対検出精度:±0.25dB rms

- 温度対エンベロープ検出精度:±0.25dB、入力範囲の上限25dBにわたって

- クレスト・ファクタを含めて、35dBを超える入力パワー・ダイナミック・レンジ

- RF帯域幅:450MHz~6GHz

- エンベロープ帯域幅:10MHz

- 入力インピーダンス:500Ω

- 単電源動作:2.5~3.3V

- 低消費電力:3V電源時で3mA

- RoHS準拠

ADL5502は、変調された信号のクレスト・ファクタを高精度に決定した上でエンベロープ検出を行う真のRMSパワー検出器です。このデバイスは、450MHz~6GHzの周波数範囲と10MHzを超えるエンベロープ帯域幅の高周波数受信および送信のシグナル・チェーンで利用できます。この検出器の動作に必要とされるのは2.5~3.3Vの単電源のみであり、その消費電流は3mAよりも低く抑えられます。入力は内部でAC結合され、入力インピーダンスの公称値は500Ωです。

RMS出力は直線的な応答のDC電圧であり、変換ゲインは900MHz時で1.8V/V rmsです。変換ゲインが1.2V/Vのピーク・エンベロープ出力は、1msに渡ってわずか1%未満のドループ電圧特性を備えたピーク・ホールド回路でトグルされます。

ADL5502は、複雑な波形のrms値とピーク平均値を高精度に決定する方法として、使いやすいデバイスです。単純な波形でも複雑な波形でもクレスト・ファクタ計測に利用できますが、CDMA2000、W-CDMA、QPSK/QAMベースのOFDM波形などのような、クレスト・ファクタの高い(ピーク対rms比の高い)信号の計測用として特に役立ちます。ピーク・ホールド機能により、サンプリング・レートが低いADCを使用して、エンベロープ内の短いピークを取り込むことができます。

このクレスト・ファクタ検出器は-40℃~+85℃の温度範囲で動作し、8ボール、1.5mm×1.5mmのWLCSP(ウェハーレベル・チップ・スケール・パッケージ)で提供されます。このデバイスは、高fTのシリコンBiCMOSプロセスで製造されています。

アプリケーション

- W-CDMA、CDMA2000、QPSK/QAMベースのOFDM波形、およびその他の複雑な変調

- 波形のパワーおよびエンベロープ計測

- RFトランスミッタまたはレシーバのパワーおよびエンベロープ計測

ドキュメント

データシート 1

評価用設計ファイル 1

製品選択ガイド 1

リファレンス設計 1

| 製品モデル | ピン/パッケージ図 | 資料 | CADシンボル、フットプリント、および3Dモデル |

|---|---|---|---|

| ADL5502ACBZ-P7 | 8-Ball WLCSP (1.5mm x 1.5mm) |

| 製品モデル | 製品ライフサイクル | PCN |

|---|---|---|

| 該当なし | ||

|

9 11, 2009 - 09_0191 Test transfer for ADL5502 from StatsChipPac Singapore (SCS) to ASE Kaohsiung Taiwan |

||

| ADL5502ACBZ-P7 | 製造中 | |

これは最新改訂バージョンのデータシートです。

ツールおよびシミュレーション

ADIsimRF

アナログ・デバイセズのADIsimRF設計ツールは、カスケード・ゲインやノイズ指数、IP3、P1dB、総合消費電力などRFシグナル・チェーン内の最も重要なパラメータの計算を行います。

ツールを開くADIsimPLL™

アナログ・デバイセズの新しい高性能PLL製品を迅速かつ確実に評価できるツールです。現在利用できるツールの中で、最も総合的なPLLシンセサイザーの設計/シミュレーション・ツールです。実施されるシミュレーションには、主要な非線形効果が含まれており、これはPLLの性能に大きく影響を及ぼします。ADIsimPLLによって、設計プロセスの繰り返し作業が1つ以上排除されるため、設計から製品の市場投入までの期間が大幅に短縮することができます。

ツールを開くSパラメータ 1

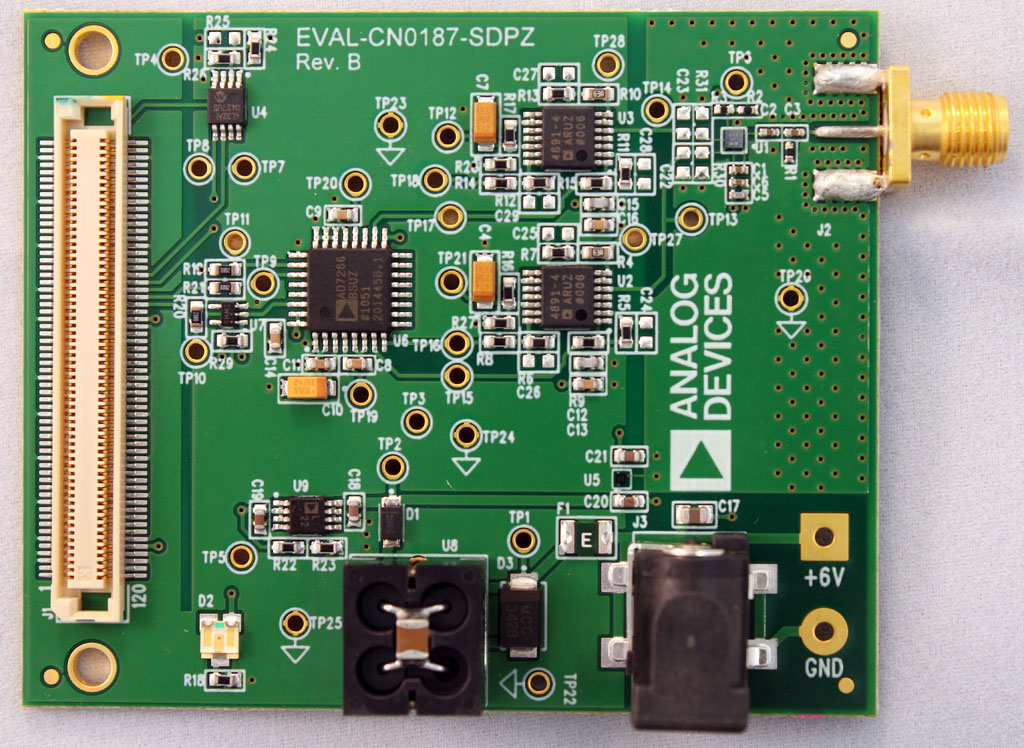

評価用キット

リファレンス・デザイン

最新のディスカッション

ADL5502に関するディスカッションはまだありません。意見を投稿しますか?

EngineerZoneでディスカッションを始める