The ADRF6612 is a dual radio frequency (RF) mixer and

intermediate frequency (IF) amplifier with an integrated phaselocked

loop (PLL) and voltage controlled oscillators (VCOs). The

ADRF6612 uses revolutionary broadband square wave limiting

local oscillator (LO) amplifiers to achieve an unprecedented RF

bandwidth of 700 MHz to 3000 MHz. Unlike narrow-band sine

wave LO amplifier solutions, the LO can be applied above or

below the RF input over an extremely wide bandwidth. Energy

storage elements are not utilized in the LO amplifier, thus dc

current consumption also decreases with decreasing LO

frequency.

The ADRF6612 utilizes highly linear, doubly balanced passive

mixer cores with integrated RF and LO balancing circuits to

allow single-ended operation. Integrated RF baluns allow optimal

performance over the 700 MHz to 3000 MHz RF input frequency.

The balanced passive mixer arrangement provides outstanding

LO to RF and LO to IF leakages, excellent RF to IF isolation,

and excellent intermodulation performance over the full RF

bandwidth.

The balanced mixer cores provide extremely high input

linearity, allowing the device to be used in demanding

wideband applications where in band blocking signals may

otherwise result in the degradation of dynamic range. Noise

performance under blocking is comparable to narrow-band

passive mixer designs. High linearity IF buffer amplifiers follow

the passive mixer cores, yielding typical power conversion gains

of 9 dB, and can be matched to a wide range of output

impedances.

The PLL architecture supports both integer-N and fractional-N

operation and can generate the entire LO frequency range of

200 MHz to 2700 MHz using an external reference input

frequency anywhere in the range of 12 MHz to 320 MHz. An

external loop filter provides flexibility in trading off phase noise

vs. acquisition time. To reduce fractional spurs in fractional-N

mode, a sigma-delta (Σ-Δ) modulator controls the post-VCO

programmable divider. The VCO consists of multiple VCO cores.

All features of the ADRF6612 are controlled via a 3-wire SPI

resulting in optimum performance and minimum external

components.

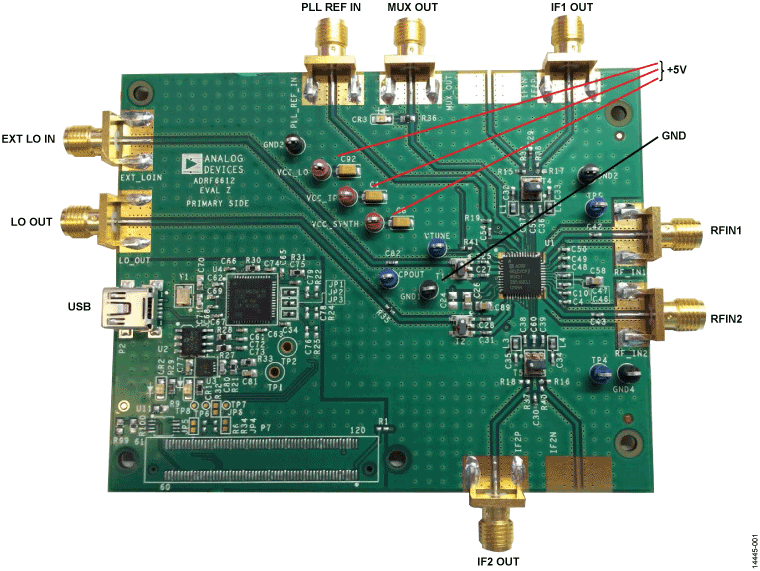

The ADRF6612 is fabricated using a BiCMOS, high

performance IC process. The device is available in a 7 mm × 7

mm, 48-lead LFCSP package and operates over a −40°C to +85°C

temperature range. An evaluation board is available.

Applications

- Multiband/multistandard cellular base station diversity

receivers

- Wideband radio link diversity downconverters

- Multimode cellular extenders and picocells