AD6672

RECOMMENDED FOR NEW DESIGNSIF Receiver

- Part Models

- 2

- 1ku List Price

- Starting From $56.75

Part Details

- 11-bit, 250MSPS output data rate

- Performance with NSR enabled

SNR: 75.2 dBFS in a 55 MHz band to 185 MHz at 250 MSPS

SNR: 72.8 dBFS in an 82 MHz band to 185 MHz at 250 MSPS - Performance with NSR disabled

SNR: 66.4 dBFS up to 185 MHz at 250 MSPS

SFDR: 87 dBc up to 185 MHz at 250 MSPS - Total power consumption: 358 mW at 250 MSPS

- 1.8 V supply voltages

- LVDS (ANSI-644 levels) outputs

- Integer 1-to-8 input clock divider (625 MHz maximum input)

- Internal ADC voltage reference

- Flexible analog input range

1.4 Vp-p to 2.0 Vp-p

(1.75 V p-p nominal) - Differential analog inputs with 350 MHz bandwidth

- Serial port control

- Energy saving power-down modes

- User-configurable, built-in self test (BIST) capability

The AD6672 is an 11-bit intermediate receiver with sampling speeds of up to 250 MSPS. The AD6672 is designed to support communications applications, where low cost, small size, wide bandwidth, and versatility are desired.

The ADC core features a multistage, differential pipelined architecture with integrated output error correction logic. The ADC features wide bandwidth inputs supporting a variety of user-selectable input ranges. An integrated voltage reference eases design considerations. A duty cycle stabilizer is provided to compensate for variations in the ADC clock duty cycle, allowing the converters to maintain excellent performance.

The ADC core output is connected internally to a noise shaping requantizer (NSR) block. The device supports two output modes that are selectable via the serial port interface (SPI). With the NSR feature enabled, the outputs of the ADCs are processed such that the AD6672 supports enhanced SNR performance within a limited region of the Nyquist bandwidth while maintaining an 11-bit output resolution. The NSR block is programmed to provide a bandwidth of up to 33% of the sample clock. For example, with a sample clock rate of 250 MSPS, the AD6672 can achieve up to 73.6 dBFS SNR for an 82 MHz bandwidth at 185 MHz fIN.

With the NSR block disabled, the ADC data is provided directly to the output with an output resolution of 11 bits. The AD6672 can achieve up to 66.6 dBFS SNR for the entire Nyquist bandwidth when operated in this mode.

APPLICATIONS

- Communications

- Diversity radio and smart antenna (MIMO) systems

- Multimode digital receivers (3G)

WCDMA, LTE, CDMA2000

WiMAX, TD-SCDMA - I/Q demodulation systems

- General-purpose software radios

Documentation

Data Sheet 1

User Guide 2

Application Note 10

Technical Articles 1

Evaluation Design File 1

Tutorial 4

Technical Book 1

ADI has always placed the highest emphasis on delivering products that meet the maximum levels of quality and reliability. We achieve this by incorporating quality and reliability checks in every scope of product and process design, and in the manufacturing process as well. "Zero defects" for shipped products is always our goal. View our quality and reliability program and certifications for more information.

| Part Model | Pin/Package Drawing | Documentation | CAD Symbols, Footprints, and 3D Models |

|---|---|---|---|

| AD6672BCPZ-250 | 32-Lead LFCSP (5mm x 5mm x 0.75mm w/ EP) | ||

| AD6672BCPZRL7-250 | 32-Lead LFCSP (5mm x 5mm x 0.75mm w/ EP) |

This is the most up-to-date revision of the Data Sheet.

Software Resources

Evaluation Software 1

JESD204x Frame Mapping Table Generator

The JESD204x Frame Mapping Table Generator tool consists of two Windows executables that will allow the user to input any valid combination of JESD204x parameters (L, M, F, S, NP) in order to output a .csv file that illustrates the frame mapping of the JESD204x mode in table format. There is an executable that allows the user to input a single JESD204x mode and another, that allows the user to input the parameters for multiple JESD204x modes in a specified .csv format in order to output a .csv file that illustrates the frame mapping of each of the JESD204x modes that were input into separate tables.

Can't find the software or driver you need?

Hardware Ecosystem

| Parts | Product Life Cycle | Description |

|---|---|---|

| Clock ICs 9 | ||

| AD9510 | RECOMMENDED FOR NEW DESIGNS | 1.2 GHz Clock Distribution IC, PLL Core, Dividers, Delay Adjust, Eight Outputs |

| AD9511 | RECOMMENDED FOR NEW DESIGNS | 1.2 GHz Clock Distribution IC, PLL Core, Dividers, Delay Adjust, Five Outputs |

| AD9512 | RECOMMENDED FOR NEW DESIGNS | 1.2 GHz Clock Distribution IC, Two 1.6 GHz Inputs, Dividers, Delay Adjust, Five Outputs |

| AD9513 | RECOMMENDED FOR NEW DESIGNS | 800 MHz Clock Distribution IC, Dividers, Delay Adjust, Three Outputs |

| AD9514 | RECOMMENDED FOR NEW DESIGNS | 1.6 GHz Clock Distribution IC, Dividers, Delay Adjust, Three Outputs |

| AD9515 | RECOMMENDED FOR NEW DESIGNS | 1.6 GHz Clock Distribution IC, Dividers, Delay Adjust, Two Outputs |

| AD9523 | NOT RECOMMENDED FOR NEW DESIGNS | 14-Output, Low Jitter Clock generator |

| AD9523-1 | RECOMMENDED FOR NEW DESIGNS | Low Jitter Clock Generator with 14 LVPECL/LVDS/HSTL/29 LVCMOS Outputs |

| AD9524 | NOT RECOMMENDED FOR NEW DESIGNS | 6 Output, Dual Loop Clock Generator |

| Differential Amplifiers 3 | ||

| ADA4927-1 | RECOMMENDED FOR NEW DESIGNS | Ultralow Distortion Current Feedback Differential ADC Driver |

| ADA4938-1 | RECOMMENDED FOR NEW DESIGNS | Ultralow Distortion Differential ADC Driver (Single) |

| ADL5562 | RECOMMENDED FOR NEW DESIGNS | 3.3 GHz Ultralow Distortion RF/IF Differential Amplifier |

| RF Amplifiers 1 | ||

| ADL5202 | Obsolete | Wide Dynamic Range, High Speed, Digitally Controlled VGA |

| RF VGAs (Variable Gain Amplifiers) 1 | ||

| AD8376 | RECOMMENDED FOR NEW DESIGNS | Ultralow Distortion IF Dual VGA |

Tools & Simulations

Virtual Eval - BETA

Virtual Eval is a web application to assist designers in product evaluation of ADCs, DACs, and other ADI products. Using detailed models on Analog’s servers, Virtual Eval simulates crucial part performance characteristics within seconds. Configure operating conditions such as input tones and external jitter, as well as device features like gain or digital down-conversion. Performance characteristics include noise, distortion, and resolution, FFTs, timing diagrams, response plots, and more.

Open ToolADC Companion Transport Layer RTL Code Generator Tool

This command line executable tool generates a Verilog module which implements the JESD204 receive transport layer. The user specifies in a configuration file one or more modes to be supported by the transport layer module. These modes are defined as a set of JESD204 parameter values: L, M, F, S, N', and CF. The transport layer converts JESD204 lane data output from a JESD204 link layer IP to a data bus with a fixed width, containing interleaved virtual converter samples. Both JESD204B and JESD204C link layers are supported.

Open ToolVisual Analog

For designers who are selecting or evaluating high speed ADCs, VisualAnalog™ is a software package that combines a powerful set of simulation and data analysis tools with a user-friendly graphical interface.

Open ToolS-Parameter 1

AD6672 IBIS Model 1

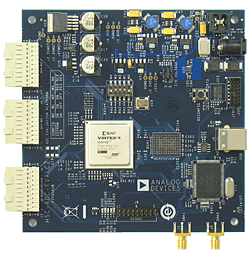

Evaluation Kits

Latest Discussions

No discussions on AD6672 yet. Have something to say?

Start a Discussion on EngineerZone®