DACを含むオープンループのシグナル・チェーンを補正する

はじめに

電子回路は、必ず誤差の発生源からの影響を受けます。通常、そうした発生源は複数存在します。それらにより、非常に高精度なコンポーネントであっても、データシートに記載されているレベルの性能を発揮できなくなる可能性があります。電子回路のシグナル・チェーンには、そうした誤差を補償するためのメカニズムが組み込まれているのが理想です。そうでない場合には、計測によって誤差の影響の度合いを明らかにし、体系的に補正を施す必要があるでしょう。それが、誤差の影響を最小限に抑えるための唯一の手段だと言えます。

本稿では、オープンループのシステムを例にとり、誤差の補償方法(キャリブレーション方法)を説明します。ここで言うオープンループのシステムとは、出力信号を利用して入力に対する適応制御動作を行うことなく、必要な性能を達成するシステムのことです。それに対し、クローズドループ・システムでは、システム内の制御動作に自身の出力信号を利用します。その場合、出力にもその制御動作の影響が現れることになります。そのような動作により、システムの性能を改善するための補正処理が自動的に行われます。ほとんどの場合、D/Aコンバータ(DAC)用のシグナル・チェーンは、一度設定したらその後に手を加えることはないタイプのシステムです。そして、そのシグナル・チェーンはおそらくオープンループのシステムであるはずです。シグナル・チェーンの出力の精度は、それを構成する各ブロックの精度に依存します。高い精度が求められるオープンループのシステムでは、ほぼ間違いなくキャリブレーションが必要になります。

本稿では、DAC用のシグナル・チェーンに適用できる2種類のキャリブレーション方法を紹介します。1つはTempCal(動作温度におけるキャリブレーション)、もう1つはSpecCal(仕様を利用したキャリブレーション)です(表1)。TempCalでは、最高のレベルで誤差を補償することができます。一方のSpecCalは、TempCalを適用できない場合の有効な代替策です。但し、TempCalほどの包括的な方法ではありません。

| TempCal | SpecCal | |

| DACの内在誤差 | ✓ | ✓ |

| 主要なコンポーネントの内在誤差 | ✓ | 補償できるものもある(VREFなど) |

| その他のシステム・レベル誤差 | ✓ | x |

DACの種類

DACには、正負いずれか一方の電圧しか出力しないタイプのものがあります。これをユニポーラ出力のDACと呼びます。本稿では、その例として「AD5676R」を取り上げます。そして、同DACを含むシグナル・チェーンのキャリブレーションを実施する方法を説明します。他の種類のDACを使用する場合にも、それと同じ方法によって必要な調整を施すことができます。

それ以外のDACについて簡単に触れておきましょう。「AD5766」のように正と負の両方の電圧を出力できるものは、バイポーラ出力のDACと呼ばれます。

電流出力型のDACは、可変ゲインを提供する乗算構成(MDAC)によく使用されます。通常は、固定抵抗に生成される電圧をバッファするための外付けアンプが必要になります。

「AD5770R」や「LTC2662」などは、新しいカテゴリの電流出力型DACです。外付け部品を追加することなく、あらかじめ定められた範囲内で出力電流を正確に設定することができます。

DACの伝達関数と誤差要因

DACは、入力されたデジタル・コードに正確に比例するアナログ出力(電圧または電流)を生成します。理想的なDACであれば、電源やリファレンスのばらつきといった望ましくない外的な要因には左右されないことになります。DACに入力されるデジタル・コードにおいて、1ステップに相当する最小ビットはLSB(Least Significant Bit)と呼ばれます。入力コードが1LSB増加すると、DACの出力はそれに伴って上昇します。電圧出力型の理想的なDACの場合、その出力電圧の増分は以下の式で表すことができます。

ここで、

上式の(VREF+)と(VREF-)は、それぞれ正と負のリファレンス電圧です。(VREF-)はグラウンド(0V)に等しい場合もあります。

nはDACの分解能であり、単位はビットです。

LSBSIZE(V)はDACの出力の最小増分であり、単位はVです。

上式から、LSBに対応する電圧がわかれば、任意のコードが入力された際のDACの出力電圧を正確に予測できるはずです(以下参照)。

実際には、DACの出力にはゲイン誤差とオフセット誤差が生じます。これらの誤差は、DACそのものから生じる誤差(以下、内在誤差)やシグナル・チェーンのその他の構成要素に起因する誤差(以下、システム・レベル誤差)によって発生します。DAC製品の中には、出力アンプを内蔵しているものがあります。そうではなく、アンプを外付けしなければならない場合には、それが潜在的な誤差の発生源になることもあります。

ICのデータシートを見ると、「用語の定義」というセクションに最も重要な仕様についての説明が記されています。DACの場合、そのセクションには、オフセット誤差、ゲイン誤差などのパラメータに関する説明があります。

ゼロ・スケール誤差は、ゼロ・コード(0x0000)をDACに入力したとき(内部レジスタに読み込まれます)に測定される出力誤差の値です。

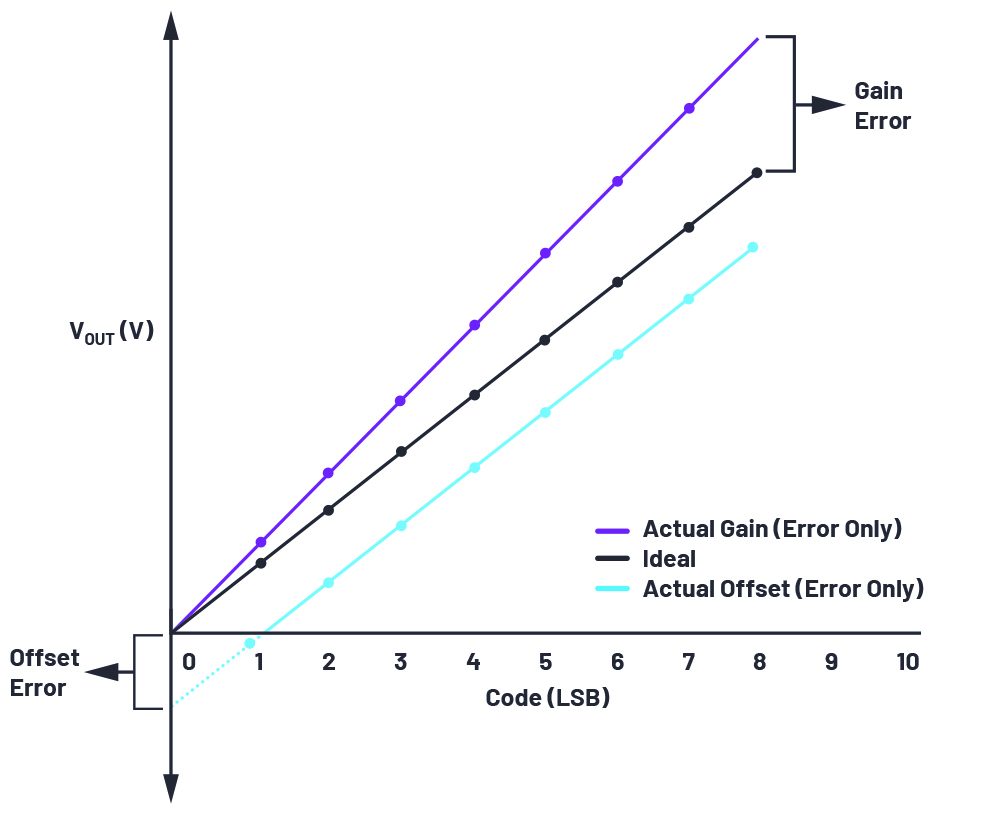

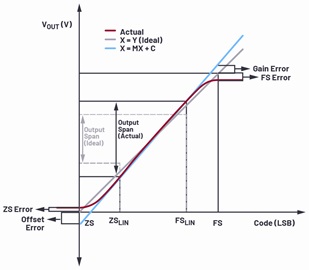

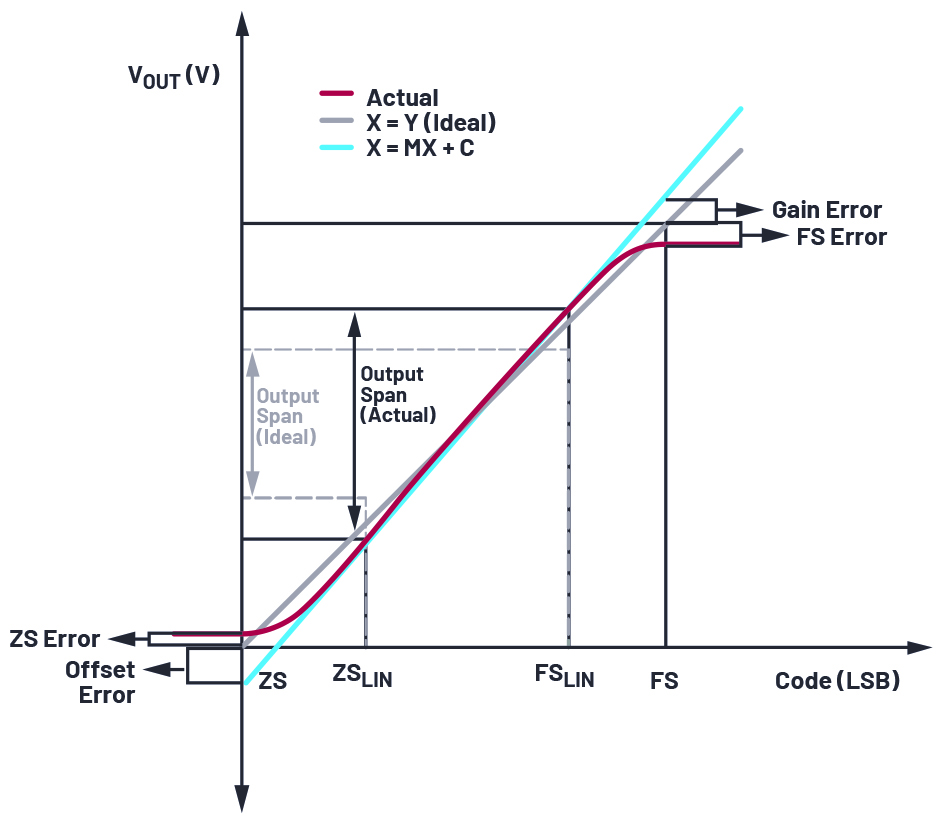

図1は、オフセット誤差とゲイン誤差がユニポーラのDACの伝達関数にどのような影響を及ぼすのかを示したものです。

ゲイン誤差は、DACのスパン誤差の測定値です。図1では紫色で示しています。黒色で示しているのが理想的なDACの伝達曲線です。図1を見ると、DACの実際の伝達曲線と理想的な伝達曲線の傾きにはずれがあります。このずれがゲイン誤差です。

オフセット誤差は、伝達関数においてDACが線形に動作する領域における実際の出力と理想的な出力の差です。青色で示した伝達関数は、オフセット誤差を求めるために、Y軸と交差するVOUTの値(負の値)を取得できるよう補完されていることに注意してください。

図1. ユニポーラDACのオフセット誤差とゲイン誤差

ゲイン誤差とオフセット誤差の影響は、後ほど示す図4の青色の曲線を見ることで確認できます。

これらのパラメータについては、それぞれの値が温度の変化に伴ってどのように変化(ドリフト)するのかということも問題になります。ドリフトについては、以下のような項目に注目する必要があります。

- ゼロ・コード誤差のドリフト:温度の変化に伴うゼロ・コード誤差の変化量

- ゲイン誤差の温度係数:温度の変化に伴うゲイン誤差の変化の割合

- オフセット誤差のドリフト:温度の変化に伴うオフセット誤差の変化量

温度の変化は電子システムの精度に大きな影響を及ぼします。通常、DACで生じるゲイン誤差とオフセット誤差については、温度に対して規定されています。ただ、システムの他の構成要素が、出力の全体的なオフセットとゲインに影響を与える可能性もあります。

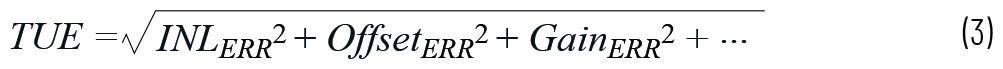

DACのINL(積分非直線性)性能とDNL(微分非直線性)性能が非常に高い場合でも、他の誤差について、特に温度と関連づけて検討しなければなりません。最新のDACでは、総合未調整誤差(TUE:Total Unadjusted Error)という指標が用いられています。これは、INL誤差、オフセット誤差、ゲイン誤差、電源と温度の変動に伴う出力ドリフトを考慮した出力誤差の指標です。その値は%FSR(フルスケールに対する割合)で表されます。

DACのデータシートにTUEの値が記載されていない場合には、RSS(二乗和平方根)を使ってその値を計算してもよいでしょう。RSSは、誤差を解析するために、相関のない各種の誤差を合算する方法です(以下参照)。

ここまでに説明した以外にも、出力ドリフトなど、影響がわずかであることから通常は考慮されない小さな誤差も存在します。

各種の性能指標については、必要に応じて単位の変換を行わなければなりません。その際に役立つ変換表を表2として示しておきます。

| LSB | V | %FSR | PPM | |

| LSB | LSB/2N × VREF | LSB/2N × 100 | LSB/2N × 106 | |

| V | (V × 2N)/VREF | V/VREF × 100 | V/VREF × 106 | |

| %FSR | (%FSR)/100 × 2N | %FSR/100 × VREF | %FSR × 104 | |

| PPM | PPM/106× 2N | PPM/106 × VREF | PPM/104 |

TUEは、すべての内在誤差の影響を考慮してDACのDC精度を簡潔に表現する優れた指標です。しかし、TUEには、DACを含めて構成されるシグナル・チェーンや動作環境によって生じるシステム・レベル誤差の影響は含まれていません。

なお、出力段にアンプ(バッファ)が付加されたDAC製品の場合、その影響は内在誤差としてデータシートに記載される仕様に反映されていることに注意してください。

システム・レベル誤差

特定のアプリケーションにおいて、DACを含むシグナル・チェーンの許容誤差について解析するケースを考えます。その場合、予想されるシステムの動作温度に注意を払いながら、様々な構成要素によってどの程度の誤差が生じるのかを考察/検証しなければなりません。アプリケーションによって、シグナル・チェーンには様々な回路ブロックが含まれる可能性があります。例えば、パワーIC、バッファ/アンプ、様々な能動的負荷などの回路ブロックです。それらは、システム・レベル誤差に影響を及ぼす可能性があります。

リファレンス電圧源

あらゆるDACには、変換動作の基準になるリファレンス電圧が必要です。リファレンス電圧源は、DACを含むシグナル・チェーン全体の精度に最も大きな影響を与える要素の1つです。

「ADR45xx」ファミリのようなスタンドアロンの電圧リファレンスを使用する場合、主要な仕様はデータシートを見ることで確認できます。リファレンス電圧源を内蔵するDACを使用する場合には、DACのデータシートを参照することになります。

ドロップアウト電圧は、例えば出力電圧を0.1%精度の範囲内に維持するために、入出力間で確保しなければならない最小の電圧差です。電源電圧のヘッドルームとも呼ばれます。

温度係数(TCまたはTCVOUT)は、周辺温度の変化に伴うデバイスの出力電圧の変化を、25°Cにおける出力電圧によって正規化したものです。「ADR4520/ADR4525/ADR4530/ADR4533/ADR4540/ADR4550」のAグレード品とBグレード品の場合、TCVOUTは-40°C、25°C、125°Cでテストされています。Cグレード品では、TCVOUTのテストは0°C、25°C、70°Cで行われています。このパラメータの値を規定する方法は2つあります。最も一般的なのはボックス法です。この方法であれば、全温度範囲の温度係数に対応できます。一方のボウタイ法では、25°Cからの、最も厳しい条件における傾きを算出するというものです。そのため、25°Cでキャリブレーションされるシステムに対してより有効な方法だと言えます。

DAC製品によっては、内蔵するリファレンス電圧源を使うよりも、外付けのリファレンス電圧源を使用した方が高い性能が得られることがあります。リファレンス電圧は、伝達関数に直接的な影響を及ぼします。同電圧が変化すると、それに比例する変化が伝達関数の傾きに現れます。これがゲインです。

バッファ付きのリファレンス電圧源を内蔵するDACも存在します。そうした製品では、それらの内蔵ブロックの影響が内在誤差としてデータシートに記載される仕様に反映されます。この点には注意が必要です。

ライン・レギュレーション

ライン・レギュレーションとは、与えられた入力の変化に対する出力の変化のことです。電圧源として機能するスタンドアロンのICに対しては必ず定義されています。そうしたICの例としては、入力に依存することなく安定した出力電圧を維持することが求められる電源IC、バッファ、リファレンスICが挙げられます。通常、ライン・レギュレーションについては、周辺温度における値がデータシートに記載されています。

負荷レギュレーション

負荷レギュレーションは、負荷電流の変化に対する出力電圧の変化量として定義されます。通常、電圧出力は、この変化の影響を抑えるためにバッファされます。一方で、リファレンス入力をバッファしないDACも存在します。その場合、入力コードが変化するとリファレンスの入力インピーダンスも変化し、リファレンス電圧が変動します。一般に、出力に対するその影響は大きくはありませんが、高精度のアプリケーションでは注意を払う必要があります。通常、負荷レギュレーションについては、周辺温度における値がデータシートに記載されます。

SHRシフト

SHR(Solder Heat Resistance)シフトは、特にリファレンス電圧源に関連する事象です。リフロー・ハンダ処理を行うと、リファレンス電圧源の出力電圧は永久的にシフトします。そのシフト量を、出力電圧に対する割合(%)で表します。詳細については、ADR45xxのデータシートをご覧ください。あらゆるICは、何らかの形でSHRシフトの影響を受けます。その影響は、必ずしも定量化できるものではありません。アプリケーションにおける具体的なシステム構成に大きく依存します。

長期安定性

長期安定性は、時間の経過に伴う出力電圧の変化によって定義します。変化量が1000時間あたりのppm値として規定されます。アプリケーションの長期安定性は、プリント基板のレベルでバーンインを実行することによって改善できます。

オープンループ・システムのキャリブレーションの理論

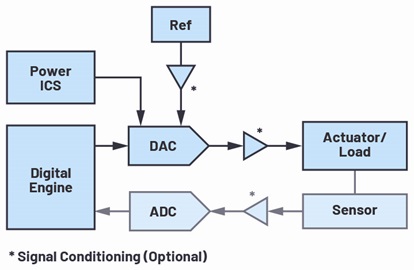

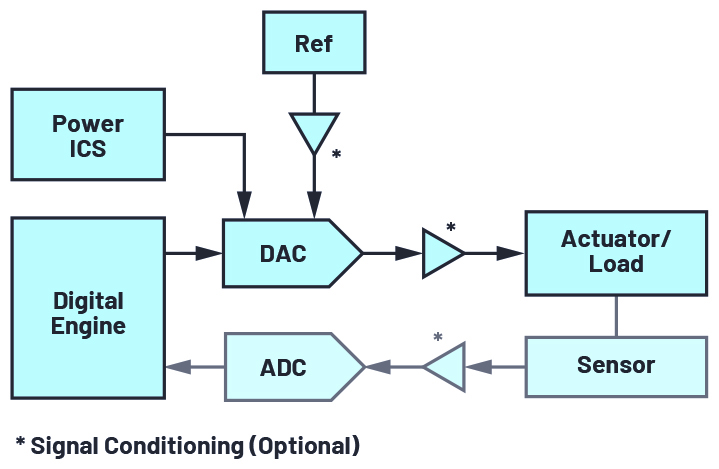

図2は、DACを含むシグナル・チェーンを簡略化して示したブロック図です。濃い黒で示した部分が、オープンループのシグナル・チェーンです。灰色で示した部分は、クローズドループのシグナル・チェーンを構成する場合に必要になります。

図2. DACを含むシグナル・チェーン

非常に正確な出力を得たいケースでは、コンポーネントを追加してクローズドループを構成すると共に、ソフトウェアによってデータにデジタル処理を加えることになるでしょう。ただ、コストやスペースなどの問題で、そうしたリソースを追加できないケースもあるはずです。そのような場合でも、オープンループのソリューションによって必要な精度を達成できる可能性があります。本稿では、そのようなケースを対象とし、オープンループのシステムにキャリブレーションを適用する方法を示します。

外的な影響がなく、ゲイン誤差とオフセット誤差が一定である場合、それらを補償するのは理論上は難しいことではありません。伝達関数においてDACが線形に動作する領域は、以下の式で表される直線でモデル化できます。

ここで、xはDACの入力、yはDACの出力です。

mは(図1で紫色で示した)ゲイン誤差を含む伝達関数の傾きです。

cは(図1で青色で示した)オフセット電圧です。

理想的なDACでは、mが1でcが0になります。現実のDACにはゲイン誤差とオフセット誤差が存在するので、いずれも異なる値になります。それらの値を知ることで、理想状態に近い出力が得られるようにDACの入力を補正することができます。ゲインは、DACのデジタル入力にゲイン誤差の逆数を乗じることによって補正できます。オフセット誤差は、DACのデジタル入力にオフセット誤差の測定値の符号を反転した値を加算することで除去できます。

以下の式は、DACによって必要な電圧を生成するための入力データを計算する方法を表しています。

ここで、ゲインとオフセット誤差はそれぞれ以下の式で表されます。

オフセット誤差の値は正にも負にもなることに注意してください。

上記の内容については、「Open-Loop Calibration Techniques for Digital-to-Analog Converters(D/Aコンバータのオープンループのキャリブレーション方法)」という記事も参考にしてください。

シグナル・チェーンに適切なキャリブレーションを施す方法

続いては、AD5676Rを例にとり、DACを含むシグナル・チェーンのオフセット誤差とゲイン誤差を補償する方法を説明します。すべての測定は、同DACの評価用ボード「EVAL-AD5676」を使用し、同DACが内蔵するリファレンス電圧源をイネーブルにした状態で実施しました。EVAL-AD5676を含む測定環境は、この例において測定の対象とするシグナル・チェーンの構成要素だと見なされます。シグナル・チェーンの各構成要素(ボード上のパワーIC、AD5676R、基板レイアウトやコネクタに伴う寄生要素など)は、すべてシステム・レベル誤差に影響を及ぼします。このような環境を例にとることで、任意のシステムに適用できるキャリブレーション方法を示すことにします。

EVAL-AD5676上のAD5676Rとの通信には、Blackfin® SDPコントローラ・ボード(SDP-B)である「EVAL-SDP-CB1Z」を使用します。また、出力電圧VOUT0の測定は、8ビットのDMM(Digital Multi Meter)で行います。更に、EVAL-SDP-CB1ZとEVAL-AD5676で構成されるシステム全体の温度を制御するために、気候チャンバを使用することにしました。

ユーザー・ガイドに記載されているとおりの方法で、EVAL-AD5676に電源を投入します。リンクの構成は表3に示したとおりです。

| リンク番号 | 位置 |

| LK1 | A |

| LK2 | A |

| LK3 | A |

| LK4 | A |

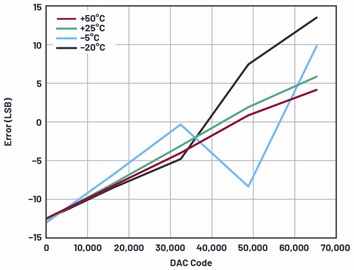

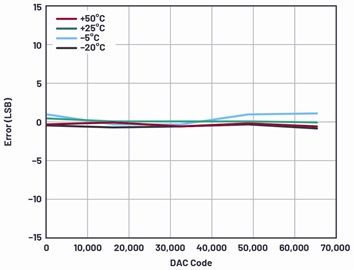

まず、キャリブレーションを施さない状態(以下、NoCal)で、シグナル・チェーンの誤差を様々な温度条件の下で測定しました。出力誤差は、特定の入力コードに対する理想値と実測値の差(LSB換算)を基に計算します。この誤差には、EVAL-AD5676に実装されたDACとシグナル・チェーンの内在誤差/システム・レベル誤差が含まれています。NoCalにおける出力誤差を図3に示しました。

図3. NoCalにおけるEVAL-AD5676の出力誤差(LSB換算)

オフセット誤差、ゲイン誤差、補償用のコードの計算に必要な情報は伝達関数に含まれています。必要なのは、DACが線形に動作する領域の上端、下端の値です。すなわち、ゼロ・スケールに近いデータ・ポイントZSLINとフル・スケールに近いデータ・ポイントFSLINに対応するコードの値が必要になります。通常、それらの情報はINLやDNLの仕様に関連して提供されています(多くの場合、表の備考欄に記載されています)。例えばAD5676Rの場合、線形に動作する領域はコードで言えば256~65280の範囲です。

図4は、DACが線形に動作する領域について説明したものです。

図4. ユニポーラのDACの伝達関数と誤差

ZSLINとFSLINのコードを把握すれば、キャリブレーションに必要な測定値を収集することができます。これら2つのコードに対するDACの出力電圧と、その間のいくつかのコード(例えば1/4スケール、1/2スケール、3/4スケール)に対応する出力電圧を測定します。

できれば、上記の測定はアプリケーションの動作温度で実施します。それができない場合には、まず周辺温度でZSLINとFSLINにおける測定を行います。その上で、シグナル・チェーンを構成するデバイスのデータシートを参照することにより、必要な情報を収集します。

先述したように、シグナル・チェーン内のすべてのデバイスは誤差に寄与する可能性があります。アプリケーションで使用するボードはそれぞれに異なるので、それぞれのボードに対してキャリブレーションを実施しなければなりません。

動作温度でのキャリブレーション

最高の精度が得られるようにキャリブレーションを実施するには、アプリケーションの稼働環境において実際の動作温度で誤差を測定します。その上で、得られた誤差を体系的に補正するためのデータをDACに書き込みます。これが、TempCalの概要です。

TempCalを実施するには、システムの実際の動作温度でZSLIN、FSLINのコードに対応するDACの出力を測定します。その上で、以下に示す一連の値を導出します。

各変数の意味は以下のとおりです。

VOE:オフセット誤差〔V〕

VFS,LIN,ACT:FSLINにおける出力の実測値

VZS,LIN,ACT:ZSLINにおける出力の実測値

VFS,LIN,IDEAL:FSLINにおける出力の理想値

VZS,LIN,IDEAL:ZSLINにおける出力の理想値

オフセット誤差の値は正にも負にもなり得ることに注意してください。

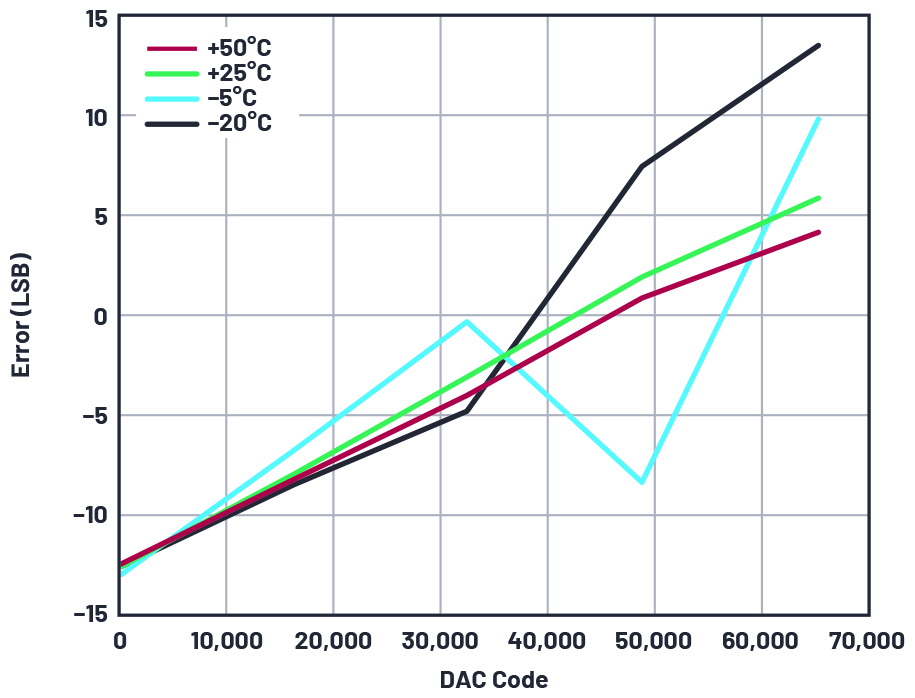

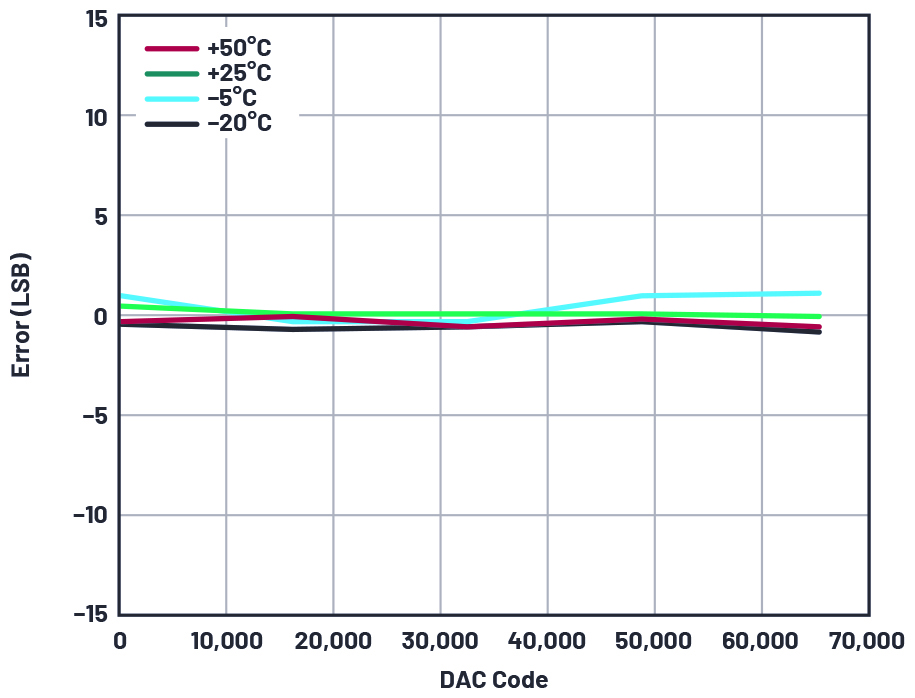

図5に、TempCalを適用してEVAL-AD5676の出力誤差を測定した結果を示しました。

図5. TempCalを適用した場合の出力誤差の測定結果。様々な温度における値(LSB換算)をプロットしました。

仕様を利用したキャリブレーション

アプリケーションの稼働環境において、実際の動作温度で誤差を測定することができないケースがあります。その場合でも、AD5676Rのデータシートと、周辺温度でキャリブレーションされたDACの伝達関数を使用すれば、高いレベルで補償を行うことが可能です。この方法をSpecCalと呼ぶことにします。

SpecCalでは、まず周辺温度でZSLINとFSLINのコードにおけるDACの出力を測定します。周辺温度におけるゲイン誤差とオフセット誤差を算出し、以下の式を使って、TempCalの場合と同様に伝達関数を導出します。

各変数の意味は以下のとおりです。

GEamb:周辺温度におけるゲイン誤差

VOE,amb:周辺温度におけるオフセット誤差(単位はV)

周辺温度において、DACを含むシグナル・チェーンのキャリブレーションを実施する際には、システム・レベル誤差も含まれることになります。しかし、温度の変化に伴うシステム・レベル誤差の変化は考慮されていません。そのため、SpecCalではTempCalほどの精度は得られません。

続いて、データシートを参照し、DACの内在誤差(オフセット誤差とゲイン誤差)のドリフトを確認します。ここでいうドリフトとは、動作温度の変化に伴うオフセット誤差とゲイン誤差の変動のことです。このような手順でキャリブレーションを行うことから、SpecCalと呼んでいます。AD5676Rのデータシートを見ると、オフセット誤差のドリフトの代表値が記載されています。オフセット誤差と代表的な性能(TPC:Typical Performance Characteristics)を確認すれば、周辺温度から上昇、下降することによって誤差がどちらの方向にドリフトするのかがわかります。オフセット誤差の変動量は、以下の式で算出できます。

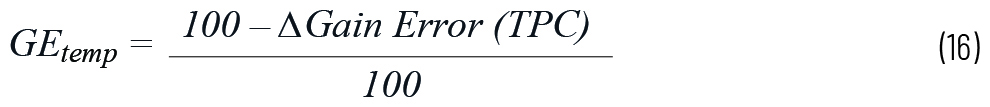

ゲイン誤差の温度変動は、ゲイン誤差とTPCから導き出せます。グラフから、フル・スケールに対するゲイン誤差の割合(単位は%FSR)を求めて以下の式を適用します。

動作温度におけるオフセット誤差とゲイン誤差の推定値が得られたところで、以下の式を使用して、SpecCalを適用した場合の入力コードを求めます。

ここで、

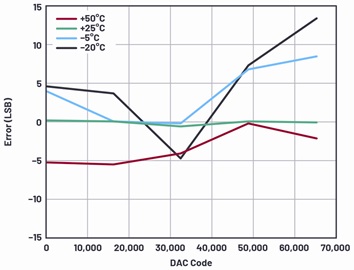

図6に、SpecCalを適用した場合のEVAL-AD5676の出力誤差を示しました。

図6. SpecCalを適用した場合の出力誤差の測定結果。様々な温度における値(LSB換算)をプロットしました。

この例では、DACが内蔵するリファレンス電圧源を使用しました。外付けのリファレンス電圧源を使用した場合、全体的な誤差が増大する可能性があります。リファレンス電圧源に起因する誤差は、リファレンスICのデータシートを参照し、対象温度におけるリファレンス電圧のドリフトを考慮することによって補償できます。なお、リファレンス電圧を変更すると、出力スパンとLSBの大きさも変化します。外付けのリファレンス電圧源を使用する場合には、これについて考慮する必要があります。温度と出力電圧のTPCを使用すれば、リファレンス電圧のドリフトによって変化した出力スパンを求めることができます(以下参照)。

ここで、VREFdriftは以下の式で表されます。

まとめ

本稿では、まずDACを含むシグナル・チェーンに存在する誤差の発生源について説明しました。DAC自体の内在誤差については、データシートに定義されています。一方、システム・レベル誤差の値はシステムごとに異なります。オープンループのアプリケーションでは、それら両方について考慮しなければなりません。

また、本稿では、2種類のキャリブレーション方法を示しました。TempCalは、システムの動作温度でDACを含むシグナル・チェーンのキャリブレーションを実施するというものです。もう一方のSpecCalは、動作温度でキャリブレーションを実施できない場合に、周辺温度における測定結果を基にして補償を行うというものです。SpecCalでは、シグナル・チェーンを構成するDACやその他のICのデータシートに記載されているTPCの値を利用します。具体的には、ゲイン誤差とオフセット誤差の温度ドリフトを考慮して補償を実施します。

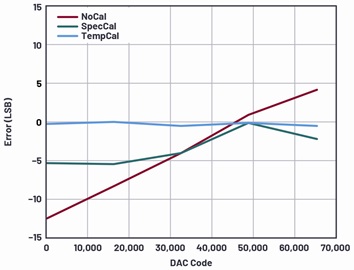

TempCalでは、SpecCalよりもはるかに高精度のキャリブレーションを実施できます。図7は、NoCal、TempCal、SpecCalの各場合における出力誤差を比較したものです。EVAL-AD5676を50°Cで動作させた場合、TempCalを適用することで、非常に理想に近い精度が得られることがわかります。また、SpecCalを適用することでも、NoCalの場合と比べて誤差を改善できることが見てとれます。

図7. NoCal、SpecCal、TempCalの比較。50°Cにおけるシステムの出力誤差(LSB換算)をプロットしました。

温度の変化は、電子システムの精度に大きな影響を与えます。システムの動作温度でキャリブレーションを実施すれば、ほとんどの誤差に対処することができます。動作温度でキャリブレーションを実施できない場合には、DACなどのデータシートに記載されている情報に基づいて温度の変化を考慮することにより、許容できるレベルの精度を得ることが可能です。