アプリケーション・ノート使用上の注意

本アプリケーションノートの英語以外の言語への翻訳はユーザの便宜のために提供されるものであり、リビジョンが古い場合があります。最新の内容については、必ず最新の英語版をご参照ください。

なお、日本語版のアプリケーションノートは基本的に「Rev.0」(リビジョン0)で作成されています。

AN-2582: 高VOUT 降圧DC/DC スイッチング・レギュレータの設計上の考慮事項

要約

システムがより複雑になり、より多くの電力を必要とするようになる中で、効率と実装密度が高いことから、高VOUT アプリケーション向けにDC/DC スイッチング・レギュレータの利用がますます広がっています。このアプリケーション・ノートでは、高VOUT 降圧スイッチング・レギュレータに関する実用に即した設計上の考慮事項や課題、例えばブートストラップ回路の通常動作を維持する方法などを示します。実用上の考慮事項と共に、扱いが難しいコーナー・ケース下でもスイッチング・レギュレータをスムーズに動作させるためのガイドラインも示します。

はじめに

降圧DC/DC スイッチング・レギュレータは電力変換アプリケーションで広く使用されます。リニア・レギュレータと比較すると、スイッチング・レギュレータには、出力電流能力、効率、ソリューション・サイズなど多くの面で優位性があります。これらの優位性は降圧比が高いほど大きくなります。パワーMOSFET を組み込んだモノリシック・パワー・マネージメントIC は、幅広いアプリケーションで降圧DC/DC(バック)スイッチング・レギュレータを利用するためのコンパクトで便利な手段を提供します。モノリシック降圧IC に関するデザイン・ノートやガイドはよく整備されていて、理解されています。

降圧スイッチング・レギュレータは、ポイント・オブ・ロード(POL)電源に適しているだけでなく、中間的なバス・レールでも重要な役割を果たします。これらの中間バス用のコンバータでは、一般的に、下流にある複数のレギュレータや負荷に電力を供給するために、高い電圧レベルと電力が要求されます。そのため、システム設計に降圧レギュレータをできるだけ多く組み入れる動きが広がっています。

システムが更に複雑で高度な機能を備えるようになると、消費電力は増加を続け、電力分配の損失も増加します。この問題への対応として、システム設計者は中間バスの電圧を12V から24V へ、そして現在では更に48V へと高くしています。高VOUTの降圧レギュレータでは、デューティ・サイクル、スイッチング損失、インダクタ・コア損失、パワーMOSFET へのストレスが全て大幅に上昇するため、設計は難しくなります。このアプリケーション・ノートは、高い出力電圧の降圧スイッチング・レギュレータの設計における主要な考慮事項を概説することを目的としています。.

ブートストラップ回路の考慮事項

N チャンネル上側FET を使用する降圧スイッチング・レギュレータでは、上側FET のソースがSW ノードにあり、電圧レベルが0V とVIN の間で振れるため、ゲート駆動電圧を得るために特別な電力スキームが必要になります。この問題の解決によく使用される方法は、単純な低コストのブートストラップ回路です[1]。一般的に、このブートストラップ回路はコンデンサCBSTとダイオード1 つずつの追加のみで実装できます。ブートストラップ・コンデンサCBST は、1 端がSW ノードに接続されており、SW の電圧がどのようなレベルになっても、上側FET やその他の補助回路に給電して駆動します[1]。

しかし、ブートストラップ回路で支持されるブートストラップ・コンデンサCBST は、理想的な電源とはほど遠く、制限(デューティ・サイクル、スイッチング周波数など)があるためスムーズな機能を保つことができません。VOUT が高いアプリケーションでは特に、CBST の電圧の維持は困難です。このセクションでは、高VOUT アプリケーションでのブートストラップ回路の概要と課題を述べ、ブートストラップ回路が正しく動作しないことを防止するためのガイドラインを示します。

ブートストラップ回路の概要

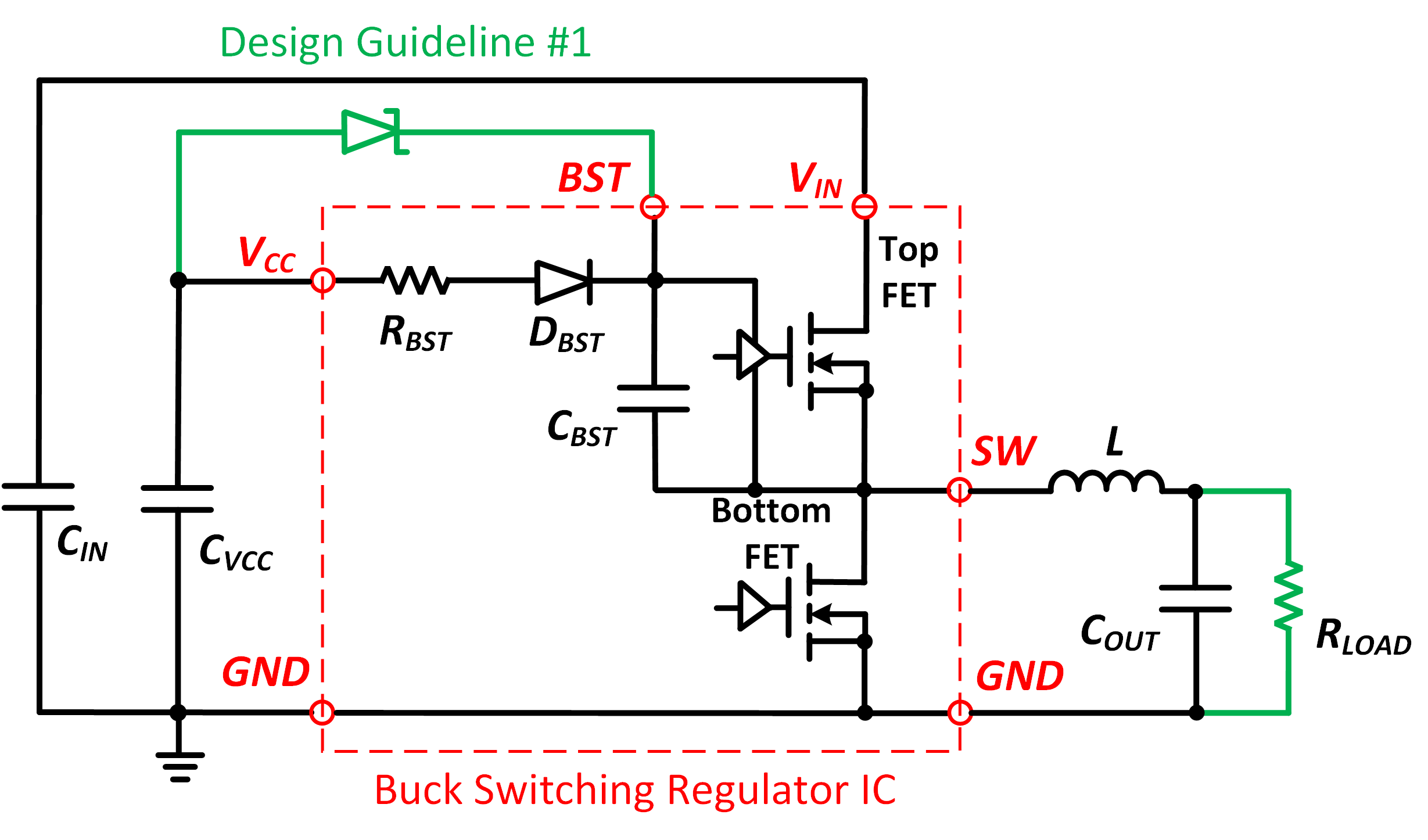

図1 は、ブートストラップ回路を備えた降圧スイッチング・レギュレータIC の簡略化した回路図です。CBST はブートストラップ・ダイオードDBST および寄生抵抗RBST と直列に接続されています。ブートストラップ・ダイオードDBST は、インピーダンスを下げるためにFET で実装する場合もあります。CBST のもう一方の端子は、多くの場合、BST ピンと呼ばれます。したがって、設計上BST ピンの電圧はSW ノードの電圧よりも一般に高くなります。CBST は、パッケージ内に組み込まれている場合も、SWピンとBST ピンの間に外付けすることが必要な場合もあります。

図1. 降圧スイッチング・レギュレータIC のブートストラップ回路の回路図

どのようにしてCBST が上側FET と補助回路を駆動するのに十分な電圧を常に保てるようにするかが問題になります。スイッチング・サイクルごとに、上側FET がオフでSW ノードの電圧がローの期間CBST が充電されます。VOUT が低くデューティ・サイクルが低い場合は、一般的に上側FET のオフ時間は、十分なCBST 電圧を得られるだけの長さがあります。上側FET がオンになると、CBST は徐々に放電し、上側FET を駆動する実効電源として機能します。起動プロセスでの充電後、CBST の電圧は定常状態に入り、上側FET と補助回路の通常動作を支えます。

高VOUT においてブートストラップ回路で発生し得る問題

VOUT が高くなり、高いデューティ・サイクルで動作するようになると、ブートストラップ回路の機能を確保できるようにCBSTを充電するのは難しくなります。VOUT が高くなると、VIN とスイッチング周波数が一定であれば、下側FET のオン時間が短くなります。このため、CBST の充電が行われる時間が次第に短くなります。極端な状況としては、VOUT がほぼVIN に等しくなるドロップアウト状態があります。理論的には、下側FET のオン時間がゼロになり、CBST を充電する時間がなくなる可能性があります。実際には、下側FET のオン時間はゼロまで下がることは許されていません。上側FET に最小オフタイムの要件があるため、SW ノードが最短時間だけローになって、ブートストラップ回路の動作を継続します。しかし、この最小オフ時間の要求(通常は150ns 未満)ではCBST の充電に十分な長い時間が常に確保されるわけではなく、条件によっては十分なCBST 電圧が得られない場合があります。ドロップアウト電圧下での性能を改善するために、レギュレータによっては、オフ時間のスイッチングをスキップし、周波数を下げて有効デューティ・サイクルを上げるものがあります。この動作では、CBST の充電状態を保つのが更に難しくなります。

高VOUT アプリケーションでは、軽負荷あるいは無負荷の条件ではCBST の充電条件が更に悪化し得ます。上側FET がオフになると、相当なインダクタ電流が流れ、SW の電圧が急激に引き下げられます。しかし、軽負荷条件では、インダクタ電流が少ないために、SWノード電圧がローに下がってCBSTの充電プロセスを開始するまでの時間が延び、実効的に充電時間が短縮されます。特にレギュレータが非常に高いデューティ・サイクルで動作し、オフ時間が最小になるとき、CBST の充電時間が大幅に短縮されます。入力電圧が高く、SW ノードの電圧降下時間が長くなると、CBST の充電時間は更に短くなります。

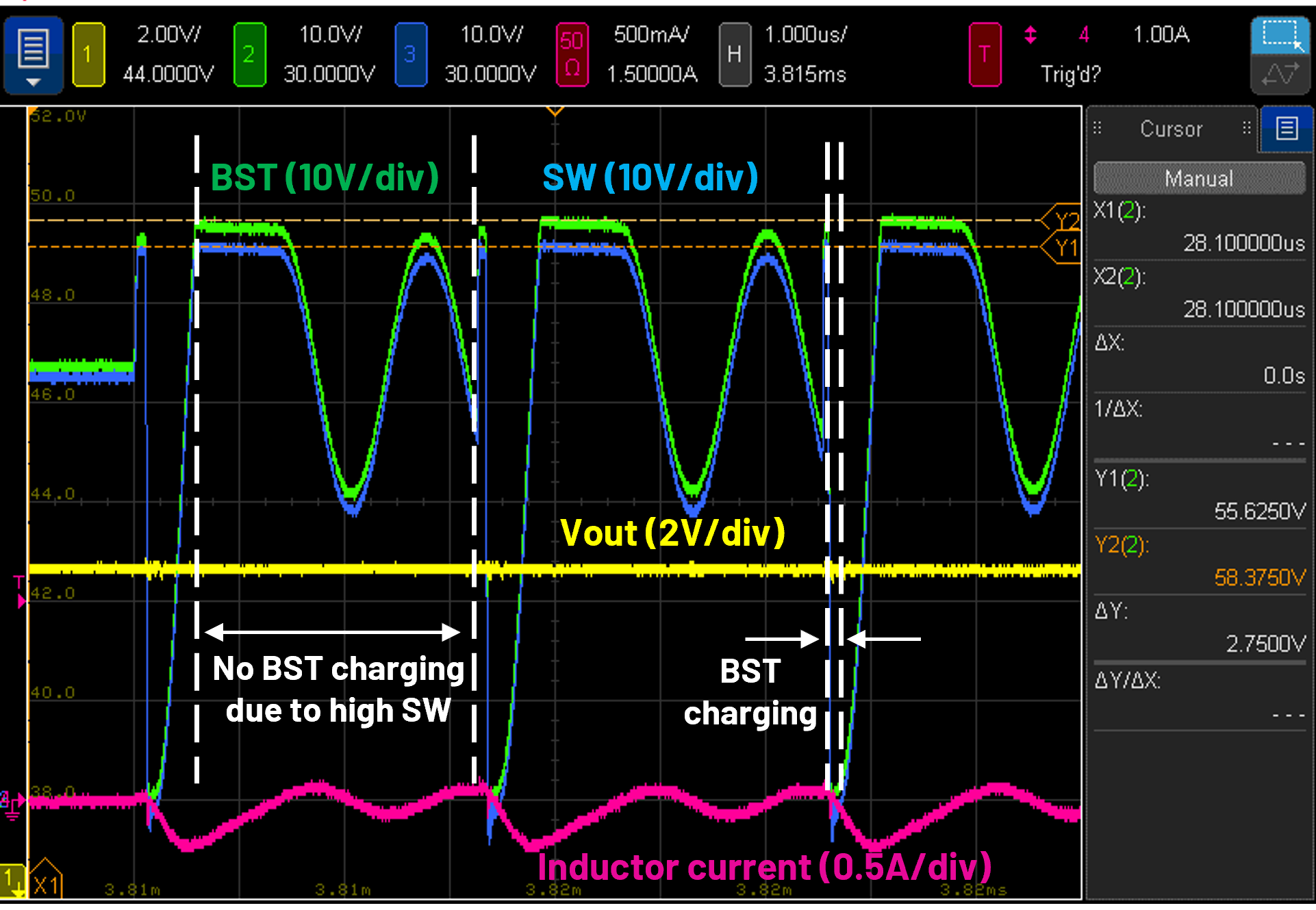

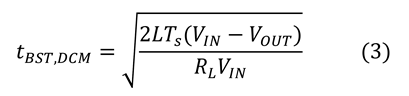

更に、軽負荷や無負荷の条件では、効率向上のために、スイッチング・レギュレータを不連続導通モード(DCM)で動作させる場合が多くなります。この場合には、下側FET がオンのとき、インダクタ電流が0A より下がるとチャンネルが切断されます。そして、DCM のリンギングによってSW の電圧が上昇し、CBSTの充電プロセスが終了します。図2 はVIN が55V、VOUT が43VにおけるDCM の波形を示しており、インダクタ電流が0A まで下がるとSW 電圧(青の波形)とBST 電圧(緑の波形)の両方が発振し急増しています。ブートストラップ・ダイオードは逆バイアスになり、次のスイッチング周期でSW がローに下げられるまでCBST の充電ができなくなります。発振が完全に減衰されたとしても、SW の電圧はVOUT のレベルを保ち、CBST の充電パスは成立しません。

図2. 降圧スイッチング・レギュレータIC のDCM 動作(パルス・スキッピング・モード)、55VIN、43VOUT、2mA 負荷

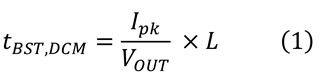

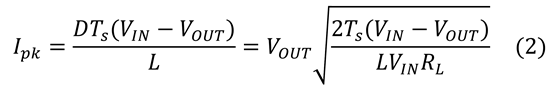

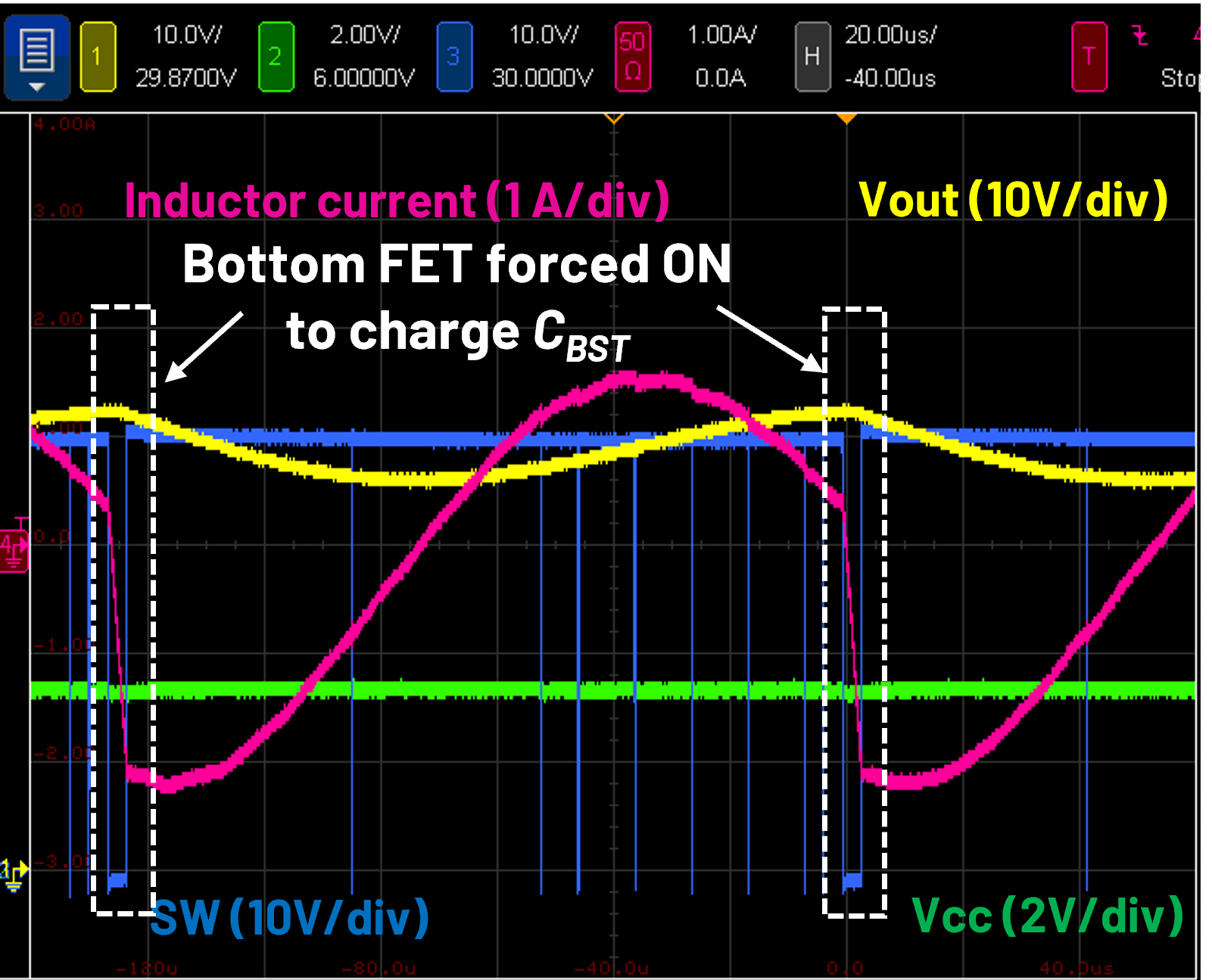

このため、DCM 動作時にインダクタ電流が0A に達するまでの時間が重要となります。この期間がCBST の実効充電時間で、このアプリケーション・ノートではtBST,DCM と呼びます。軽負荷時、無負荷時のピーク・インダクタ電流は非常に低いため、インダクタ電流は非常に短い時間で負になります。tBST,DCM は非常に短く、次式で計算できます。

この式で、IpkはDCM動作時のピーク・インダクタ電流です。Ipkが低ければ、CBST を充電するtBST,DCM が短くなります。多くのDCM動作例では、負荷電流の低下に伴ってIpkが低減し、以下のように計算できます。tBST,DCMの式も示します。

式2、式3 において、RLは負荷抵抗です。バースト・モードおよび一部のパルス周波数変調(PFM)モードにおけるDCMの例では、負荷が低い状態でも、Ipk が意図的にある一定のレベルに維持されます。そのため、これらのモードは、軽負荷時や無負荷時のCBST 充電の補充に有用です。

DCM ではVOUT が高くなると更にブートストラップ回路の通常動作が危うくなります。DCM でのCBST 充電時間は、出力電圧とインダクタンスにより大きく変化します。DCM の全てのケース(式1、式3)において、VOUT が高くなるとtBST,DCM は短くなります。高VOUT 時に高いインダクタンスを選択すると、tBST,DCM は長くなります。そのように選択したインダクタンスでも高VOUTアプリケーションでは小さすぎることが多く、これについてはこのアプリケーション・ノートの次のセクションで説明します。

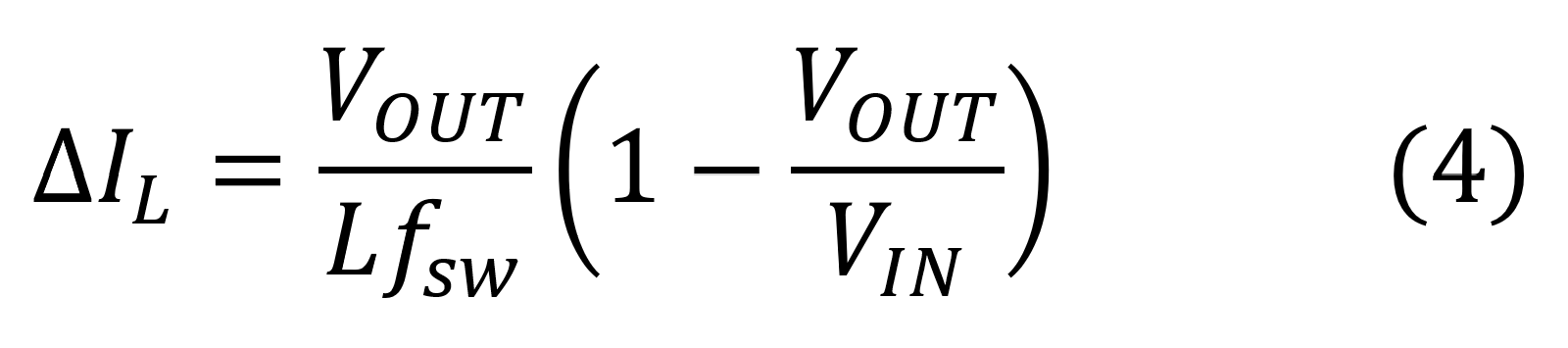

CBST 電圧が十分でなければ、降圧スイッチング・レギュレータの動作には重大な影響があります。上側FET がオンになるたびに、CBST の電圧をチェックし、問題なく上側FET を駆動できるかを確認します。CBST 電圧が低すぎれば、低電圧ロックアウト(UVLO)機能が動作して、上側FET をオフにし、下側FET を強制的にオンにして電流が導通するようにし、CBST の充電が継続できるようにします。この結果、CBST 充電の問題があればデューティ・サイクルは著しく変動し、VOUT の大きな発振を招きます。図3 は、CBST充電に起因する出力電圧振動の例を示しています。40V という高VOUT でのドロップアウト条件では、スイッチング・レギュレータが軽負荷時のCBST 電圧を維持するのは難しくなっています。スイッチング・レギュレータは、上側FET ゲート駆動回路のUVLO 機能を機能させて、下側FET がSW 電圧をプルダウンしてブートストラップ・コンデンサを充電するようにする必要があります。このため図3 で、下側FETの導通時間は通常のオン時間より大幅に長くなるときがあります。結果として、そのような異常な期間にはインダクタ電流は急速に−2A までランプ・ダウンします。負荷が2mA のみであれば、インダクタ電流は約3.8A のピークto ピーク・リップルで共振し、VOUT が大きく発振します。

図3. 降圧スイッチング・レギュレータIC のドロップアウト時動作、40VIN、40VOUT、2mA 負荷

回路が上述のコーナー・ケースに入る場合について、VOUT が高くデューティ・サイクルが高い状態でブートストラップ回路をスムーズに動作させられるよう、いくつかの設計ガイドラインを説明します。

設計ガイドライン#1

低インピーダンスの外付けBST ダイオードを実装すると、CBSTをより効率的に充電できます。内蔵のBST ダイオードもしくはFET と平行に外付けBST ダイオードを追加すると、スイッチング・レギュレータは限られた時間ウィンドウを利用してブートストラップ・コンデンサをより効果的に充電できます。SW 電圧が十分に低い限り、外付けのBST ダイオードはCBST に蓄積する電荷を補充する低インピーダンス・パスとして作用します。

順方向の電圧降下とインピーダンスが低いショットキー・ダイオードは、CBST充電ループに対して高い有効性があります。CBST充電プロセスが動作していないときには、外付けBST ダイオードは内蔵のBST ダイオードもしくはFET と同じ逆電圧に耐える必要があり、これはおおむねVIN に相当します。外付けBST ダイオードの選択にあたってのもう1 つの重要な要件は、リーク電流が低いことです。BST ダイオードがオフのとき、逆方向のリーク電流はCBST から流れます。このため、リーク電流が大きければ、外付けBST ダイオードの低いインピーダンスでもたらされるメリットを消してしまう可能性があります。選択するBST ダイオードは、高温でもリーク電流が低いものにします。

設計ガイドライン#2

最小限の負荷を維持することも、厳しい条件でのブートストラップ回路の動作を助けるソリューションとなります。このガイドラインは、軽負荷条件下でのCBST の充電時間を延長することに主眼を置いています。多くの場合、最小負荷によってピーク・インダクタ電流Ipk が増加し、CBST 充電時間が長くなります。SW電圧がより急速に低下するため、CBSTの充電プロセスはIpkが低い条件と比較して早く開始します。また、式1 に示すように、Ipkが高ければ、DCMにおけるCBST充電時間に大幅なメリットとなります。一般的には、十分に長いCBST 充電時間を得るためには、VOUT が高いほど最小負荷が高いことが必要になります。

以上をまとめると、これら2 つの設計ガイドラインでは、特に無負荷や軽負荷の場合について、限られたCBST の充電時間をより効率的に利用するだけでなく、CBST の充電時間を延長します。両方の設計ガイドラインは、高VOUT かつ高デューティ・サイクルのアプリケーションに同時に適用できます。

高VOUT アプリケーション用のインダクタの選択

インダクタは降圧スイッチング・レギュレータの必須部品の1つです。高VOUT アプリケーションに用いる降圧スイッチング・レギュレータの設計では、インダクタの選択が非常に重要です。前のセクションでの議論のとおり、デューティ・サイクルが高い高VOUT アプリケーション用のインダクタンスを選択する際には、CBST の充電について特別な考慮が必要です。

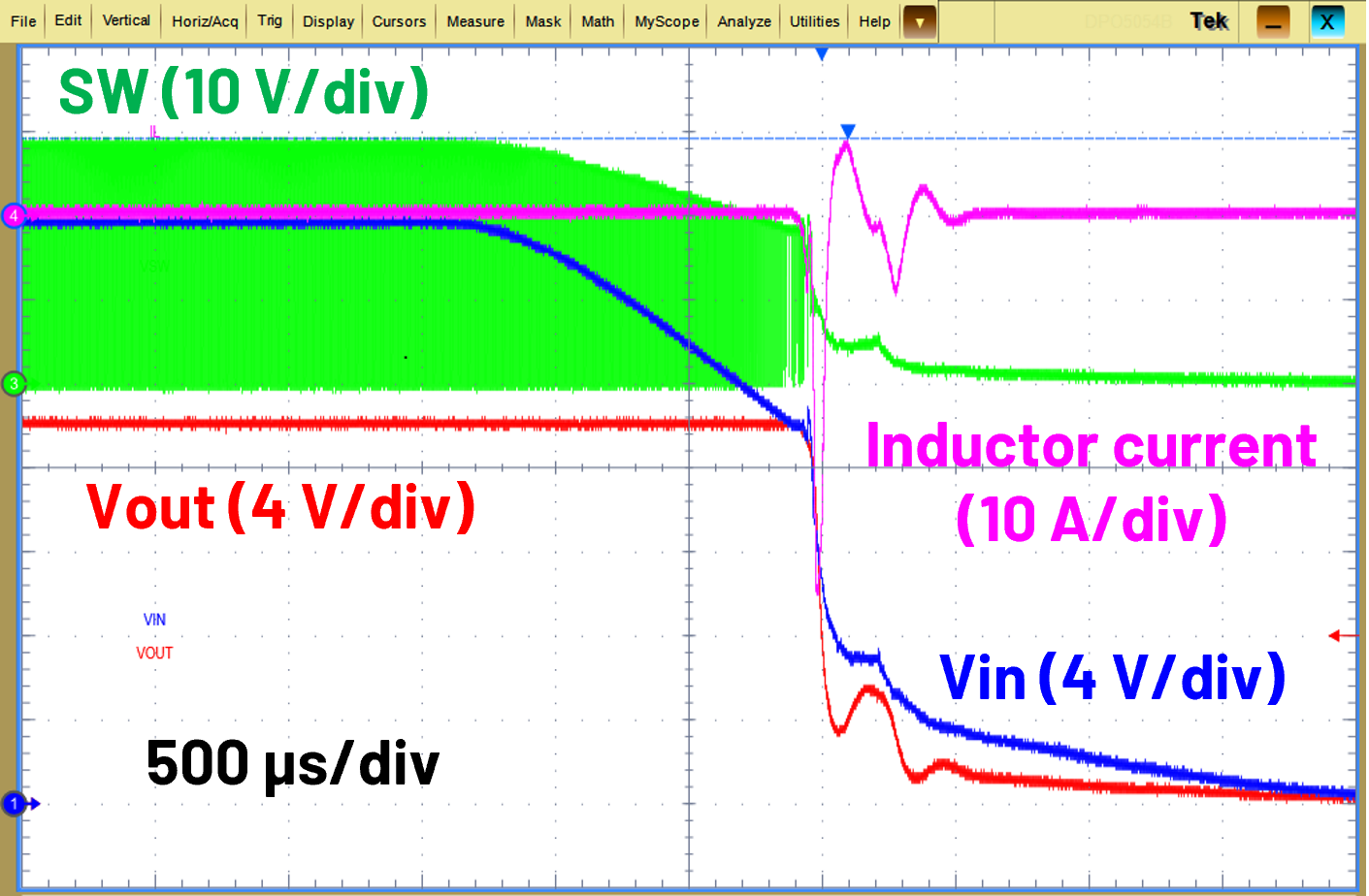

インダクタの選択においては、ピークto ピーク・インダクタ電流リップルを十分なレベルまでコントロールするという目安を置くことが多く、通常は負荷電流の30%~40%とします。インダクタのピークto ピーク電流リップルは次式で計算できます。

多くの場合、高VOUT アプリケーションでは50%を超える高いデューティ・サイクルが必要になり、ピーク電流モード制御で動作する降圧スイッチング・レギュレータで発生し得る低調波発振問題を解決するために最小インダクタンスの要件が必要となります。詳細については、AN19 - LT1070デザイン・マニュアルを参照してください。

式4 から、デューティ・サイクルが高いアプリケーションでは小さいインダクタンスを選択できることがわかります。インダクタ電流リップルはVOUT の増加に伴って単調には増加しません。インダクタ電流リップルΔIL はVOUT がVIN/2(50%デューティ・サイクル)に等しいときに最大になり、VOUTがVIN/2 を超えると(50%超のデューティ・サイクル)急激に減少します。例えば、定常的なVIN(24V)と負荷に対して、VOUT が18V から21V に上昇すると、選択されるインダクタンスは42%低下します。高い出力電圧と高い出力電流を要するアプリケーションでは、小さいインダクタンスでもインダクタの電流リップルを負荷の30%~40%に維持するのに十分です。

スイッチング・レギュレータが、定格のVOUT においては、小さいインダクタンスでインダクタ電流リップルが十分なレベルでスムーズに動作できていても、ソフト・スタート動作中には過度のインダクタ電流リップルが生じる可能性があります。VOUTが高くデューティ・サイクルが高い場合、VOUT が0V から目標のレベルまで上昇するとき、即ち起動時に低いデューティ・サイクルから高いデューティ・サイクルへとスイッチングするとき、インダクタのリップルは設計値の2 倍以上に達する可能性があります。軽負荷のDCM条件では、一時的な高いインダクタ電流リップルは上側FET がオフの間に負の値までアンダーシュートし、トライステート時の上側FET のボディ・ダイオードに電流が流れる可能性があります。高VOUT 条件で上側FET のボディ・ダイオードに意図しない逆電流が流れると、IC の損傷につながるおそれがありますが、これについては次のセクションで議論します。

軽負荷および無負荷条件でのCBST 充電の問題を解決するために、インダクタンスを高くするのは有効です。部品がDCMに入る場合、ピーク・インダクタ電流Ipk が一定かどうかにかかわらず、CBST の充電時間を延長するために高いインダクタンスが大きな役割を果たします。式1 および式3 で示されるように、同じCBST充電時間を維持するためには、インダクタンスはVOUT の上昇に伴って増加させる必要があります。

まとめると、軽負荷および無負荷の条件ではCBST の充電プロセスに対してインダクタンスを大きくすることは効果があり、これはDCMモードや強制連続モードでも同様です。デューティ・サイクルが高くなる高VOUT アプリケーションでは、全負荷時のリップル電流に基づいて小さいインダクタンスを選択することができますが、インダクタンスを大きくすると、起動プロセスや軽負荷時の動作について有利になります。このため、インダクタンスの選択においては、電流リップルと損失の要件に加えて、軽負荷時のCBST 充電時間に対する影響を考慮する必要があります。

逆電流に関する考慮事項

逆電流と発生し得る障害

降圧レギュレータでは、VIN は一般にVOUT より高く、電流は入力から出力負荷に向かって流れます。しかし、一定の特殊な条件では逆電流が発生する場合があり、出力から入力に向けて逆方向に意図しない電流が流れます。出力電圧が低い場合には、この逆電流によるリスクはありません。しかし、出力電圧が高い(10V を超える)場合、上側FET のボディ・ダイオードを流れる逆電流は部品の損傷を招くほど大きくなる可能性があります[2]。

設計上の考慮事項

このセクションでは、降圧レギュレータでの高VOUT 時の故障を防止するための設計上の考慮事項について説明します。多くの場合、逆電流は、VIN が意図せずにVOUT より低くなることがあるパワーダウン時に見られます。この条件では、逆電流が上側FET のボディ・ダイオードを流れる可能性があります。状況によっては、システム中の「意図せぬ出力ホールドアップ回路」や非常に大きい出力容量などの要因により、VOUT がVIN よりもゆっくりと下がります。

図4 はパワーダウン処理中の逆電流によるモノリシック降圧レギュレータの故障時の代表的な波形を示しています。この故障を発生させるため、降圧レギュレータIC には意図的に200μF という大きいCOUT を配し、負荷を与えていません。更に、VIN には大きいプルダウン電流を与え、入力レールに存在する他のシステム負荷を模しています。このため、パワーダウン時にVINは高速に低下する一方VOUT は高位のままとなり、最終的にVIN がVOUT より低くなります。逆方向のインダクタ電流が生成され、この電流が上側FET のボディ・ダイオードに流れます。逆電流は急速に上昇し、部品の損傷が発生します。

図4. パワーダウン処理中の逆電流による部品故障時の代表的波形

高出力電圧における逆電流による部品の故障を予防するための、アプリケーション回路用の推奨設計ガイドラインを2 つ紹介します。

設計ガイドライン#1

SW ノードとVIN の間にショットキー・ダイオードを追加して、エネルギーをシャントし、内部寄生ボディ・ダイオードに流れる電流を制限することができます。できるだけ多く逆電流をシャントするよう、外付けショットキー・ダイオードは低インピーダンスのものとし、IC の近くに配置してシャント・ループへのインピーダンス追加を最低限にします。ショットキー・ダイオードの選択においては、順方向電圧降下と電圧定格が小さくなるよう注意を払います。一般に、電圧定格が低いショットキー・ダイオードは、順方向電圧降下とインピーダンスが低い傾向があります。一方で、ショットキー・ダイオードは、アプリケーションの最大入力電圧に耐えられることが必要です。まとめると、外付けショットキー・ダイオードの逆電圧定格をまず決めた上で、低インピーダンスのショットキー・ダイオードを選択します。

例えば、アナログ・デバイセズの65V/8A モノリシック降圧レギュレータ(LT8645S、LT8646S)用に推奨するショットキー・ダイオードには、以下に挙げるようなものがあります。同様のインピーダンス特性であれば、他のダイオードを採用することもできます。

- RB058LAM-60(60V 定格)

- PMEG100T100ELPE(100V 定格)

- RB160MM-90(90V 定格)

設計ガイドライン#2

このガイドラインでは、VIN がVOUT より低くなるのを防止し、逆電流を完全に避けることに重点を置きます。適切なシーケンス方式を取り入れることで、これは容易に実現できます。システムがVIN レールをパワーダウンする前にVOUT が放電されるように、外部のEN 信号を利用して、適切なシーケンスで部品をディスエーブルすることができます。

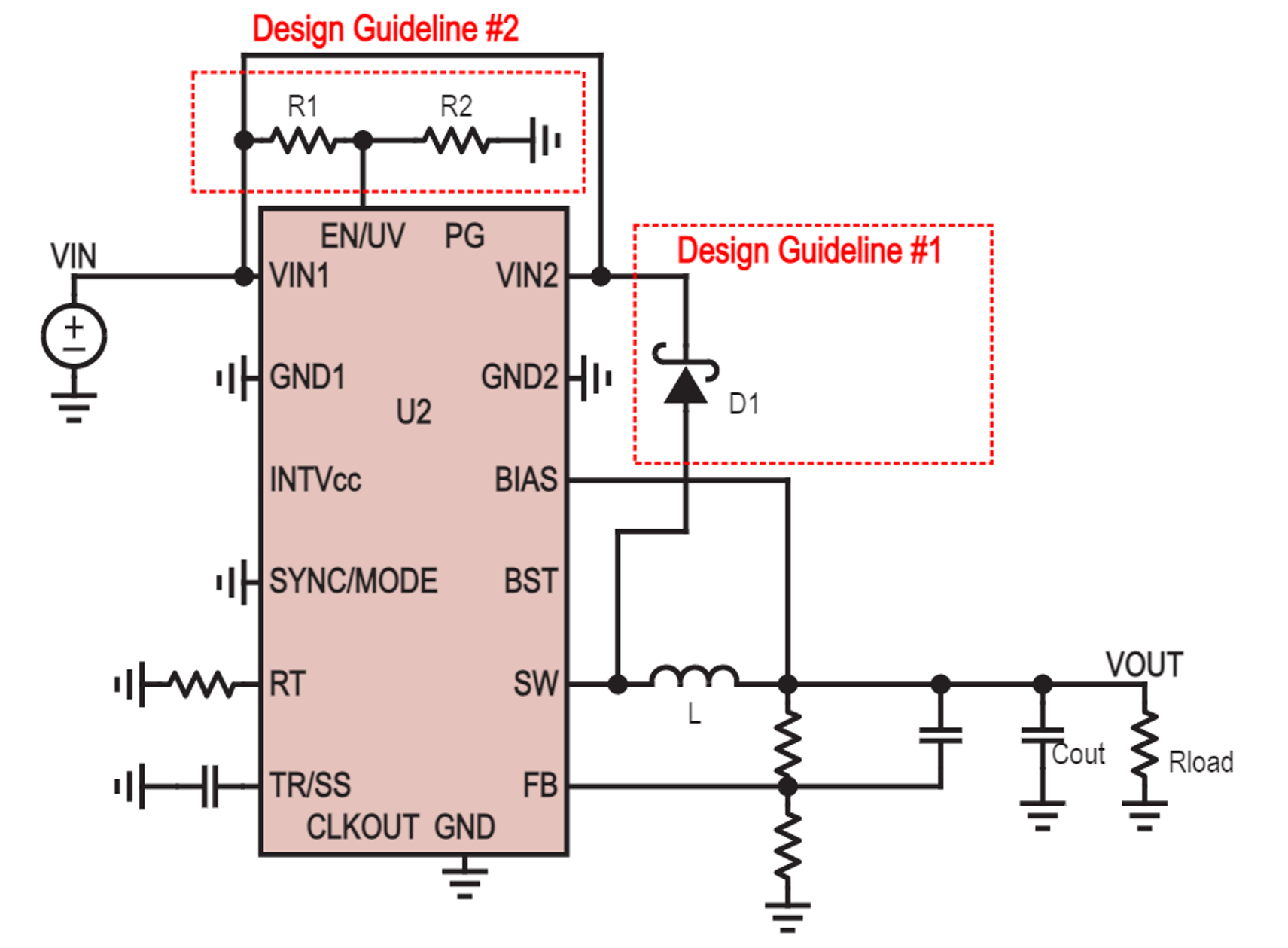

もう1 つのアプローチでは、外付けのEN/UVLO 抵抗分圧器(図5 のR1 とR2)を導入し、VIN がVOUT より十分に高いうちに部品をディスエーブルします。

図5. 設計ガイドライン#1 と#2 を実装したモノリシック降圧レギュレータIC の回路図.

このガイドラインでは、負荷がVOUT が放電し、確実にVOUT がVIN を超過しないようにすることを期待しています。このため、設計ガイドライン#2 は負荷がゼロに近くなると効果が弱くなります。信頼性の高いソリューションとするためには、システム中に両方のガイドラインを適用します。

更に、モノリシック降圧レギュレータIC の一部には、出力電圧が高い場合でも高い逆電流に耐えられるように設計されているものがあります。この例としては、LT8640A、LT8638S 、LT8648S が挙げられます。

まとめ

出力電圧が高いDC/DC 降圧スイッチング・レギュレータは、効率が高く大電流が得られ、ソリューション・サイズが小さいために、ますます広く使用されるようになっています。システムがより複雑になり、大電力を必要とするようになると、このようなレギュレータは幅広いアプリケーション(産業用、車載用など)に対して有用な選択肢となります。しかし、高VOUT のレギュレータの設計は、起動、パワーダウン、軽負荷時など考慮すべきユースケースが数多く存在するため、苦労の多い作業となる場合があります。このアプリケーション・ノートでは、高VOUT 時の設計課題に対処するための考慮事項やガイドラインを包括的に示しています。ブートストラップ回路に関する設計上の考慮事項とガイドラインを、VOUT が高くデューティ・サイクルが高いアプリケーションでのブートストラップ回路の動作を維持できるよう、詳細に記載しています。高VOUT におけるインダクタ選択のガイドラインについても再検討しています。逆電流への対処方法についても、詳細に解説しています。

参考資料

[1] Andrea Merello, “AN-1123, Bootstrap Network Analysis: Focusing on the Integrated Bootstrap Functionality.” Infineon Inc.

[2] Noora Wang, Ryan Hu, and Milo Zhu, “Methods to Eliminate Damage Caused by Reverse Current in Synchronous Buck Converters.”Texas Instruments Inc., May 2019