はじめに:進化の時代に技術者が直面する課題

プリント回路基板の設計において、電源の部分が後回しになるケースは少なくありません。そうするとスケジュールの面で余裕がなくなり、入力電圧や出力電圧、負荷といった基本的な要件以外の重要な部分が見落とされることになります。その結果、プリント基板の実装段階になって、見落とされた部分が、診断が難しい問題として顕在化するといったことが生じます。例えば、長い時間をかけてデバッグ作業を行った結果、スイッチング・ノイズなどによって回路の誤動作がランダムに発生することが判明するといった具合です。そうしたランダムな誤動作については、原因の特定が非常に困難になる可能性があります。

多くのアプリケーション・ボードでは、様々なロジック・レベルに対応するために、1つの電源回路によって複数の電源電圧を生成する必要があります。本稿では、そうしたマルチレール電源の設計時に見落とされがちないくつかの問題について2回に分けて解説します。そのPart 1となる今回は、設計上の戦略とトポロジについて説明します。再設計を繰り返さなくて済むようにするためには、最初から適切な戦略やトポロジを選択することが非常に重要です。なお、Part 2では、消費電力のバジェットや基板レイアウトの具体例を交えて、設計上のヒントや秘訣を紹介する予定です。

あまりにも多い選択肢

電源の設計を行う際には、採用候補となり得るソリューションが数多く存在することに気付かされるはずです。本稿では、1チップで複数の電圧レールに対応するICソリューションなど、様々な選択肢を取り上げます。それらについては、コストや性能といった面でのトレードオフについて評価する必要があります。また、LDO(低ドロップアウト)レギュレータとスイッチング・レギュレータ(以下、単に降圧レギュレータ、昇圧レギュレータと表記した場合、スイッチング方式であるものとします)の間にもトレードオフが存在します。VIOC(入出力間の電圧制御)機能を搭載するレギュレータをベースとしたソリューションなど、LDOレギュレータと降圧レギュレータを組み合わせるハイブリッド方式のソリューションも提供されています。

スイッチング・レギュレータには適切なフィルタリングを施し、スイッチング・ノイズを抑える必要があります。このフィルタリングが適切に行われていない場合、基板に実装された回路にどのような影響が及ぶ可能性があるのか把握しておかなければなりません。それ以外にも、トップレベル設計の観点から見たコスト、性能、実装方法、効率などについて検討する必要もあります。

何らかの電源ソースが与えられた場合に、マルチレール電源のトポロジとしてはどのようなものを選択するのが適切なのでしょうか。このような観点から、本稿では設計、ICのインターフェース、電圧の閾値レベル、回路に影響を及ぼす電源ノイズといった順に議論を進めていきます。TTL(Transistor-Transistor Logic)、CMOSといった基本的なロジック・レベル(5V、3.3V、2.5V、1.8Vなど)や、それぞれの閾値に関する要件についても解説を加えます。

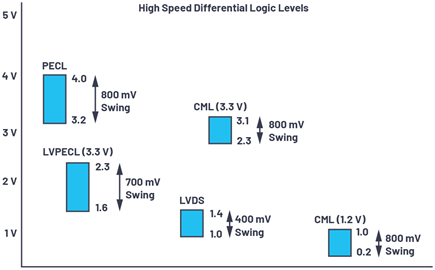

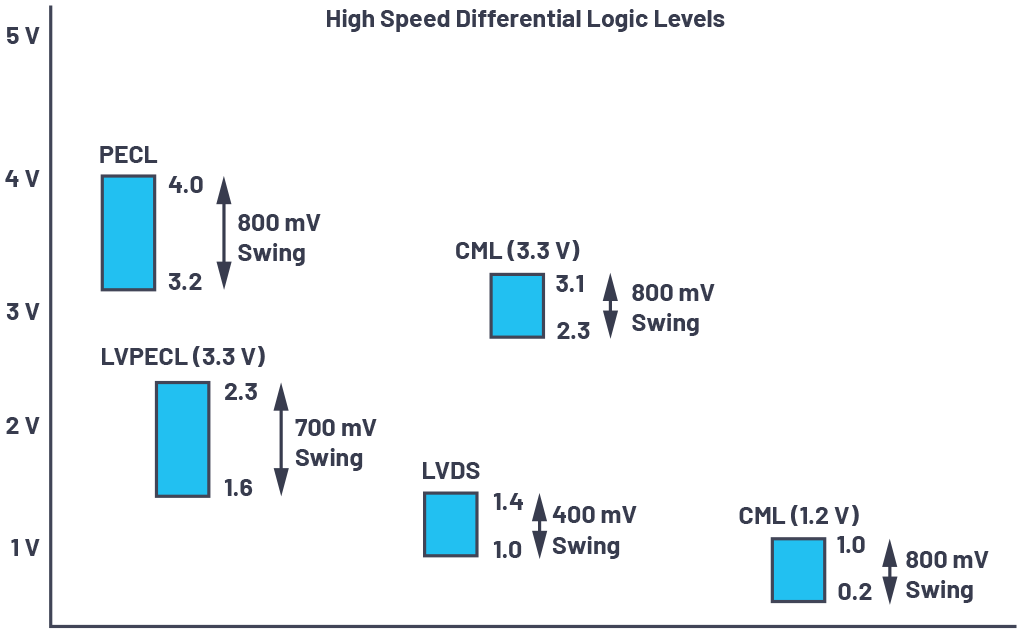

より高度なインターフェースとしては、PECL(Positive Emitter Coupled Logic)、LVPECL(Low-Voltage PECL)、CML(Current Mode Logic)といったものが挙げられます。ただ、本稿ではそれらについての詳細は割愛し、簡単に触れるにとどめます。こうした非常に高速なインターフェースを利用する場合には、ノイズ・レベルを低く抑えることが重要です。信号振幅に伴う問題をいかに回避するかということにも気を配らなければなりません。

電源の設計においては、多くの場合、コストと性能は比例します。クリーンな電源を供給するためには、ロジック・レベルなどの要件について慎重に検討する必要があります。堅牢性に配慮して設計を行い、許容誤差とノイズに対するマージンを適切に確保すれば、製造時に生じ得る問題を回避することができます。

電源の設計においては、様々なトレードオフについて理解しておかなければなりません。言い換えれば、達成できるレベルと許容できるレベルについて理解しておく必要があるということです。求められる性能を達成できなければ、他の選択肢を検討し、コストをかけてでも仕様を満たさなければなりません。例えば、「ADP5054」のようなマルチレール対応のレギュレータICを採用すれば、高いコスト効率を達成しつつ、求められる性能を満たせる可能性があります。

標準的な設計例

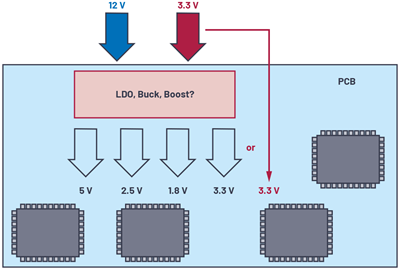

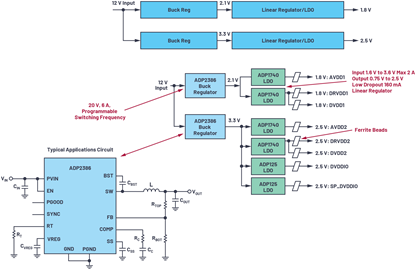

図1に示したのは、主電源として12Vと3.3Vの電圧を受け取る標準的なボードのブロック図です。基板上の各種デバイスに対しては、主電源を降圧して5V、2.5V、1.8Vを供給する必要があります。それに加え、おそらくは12Vの主電源を基に3.3Vも生成する必要があるはずです。仮に、3.3Vの主電源のノイズが十分に小さく、十分な電力が供給されるのであれば、それをそのまま使用できるかもしれません。その場合、12Vからの降圧機能が不要になるのでコストを抑えられます。しかし、上記の条件を満たさない場合には、12Vの主電源を3.3Vに降圧することで、ノイズを抑えつつ十分な電力を供給できるようにすることになるでしょう。

ロジック・インターフェースの概要

一般に、プリント基板上には複数の電源電圧が存在します。5Vだけを使用して動作するICもあれば、入出力インターフェース用に5Vと3.3V、内部ロジック用に2.5V、低消費電力のスリープ・モード用に1.8Vといった具合に、複数の電源電圧を必要とするICもあります。低消費電力のモードとしては、常時オンの状態でタイマー機能やハウスキーピング・ロジックが動作するというものがあります。あるいは、割込みやIRQピンによってICをイネーブルの状態として電力(5V、3.3V、2.5V)を供給するウェイクアップ・モードを備えているものもあります。ICの内部では、そうしたロジック・インターフェースが一般的に用いられています。

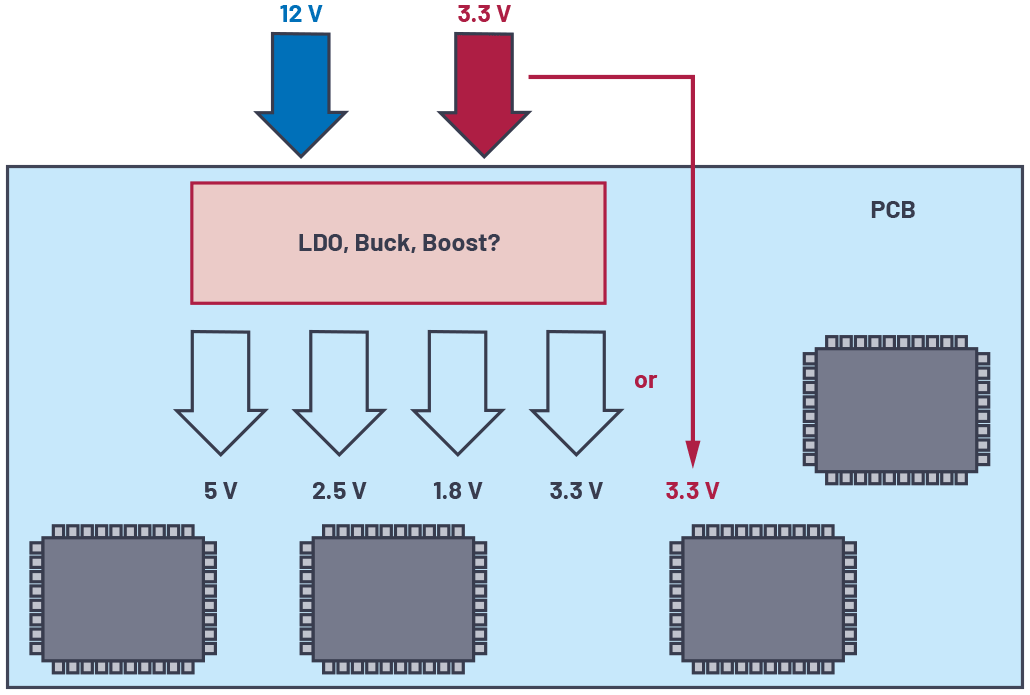

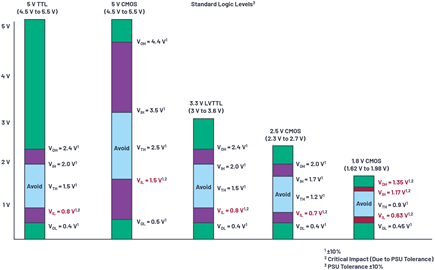

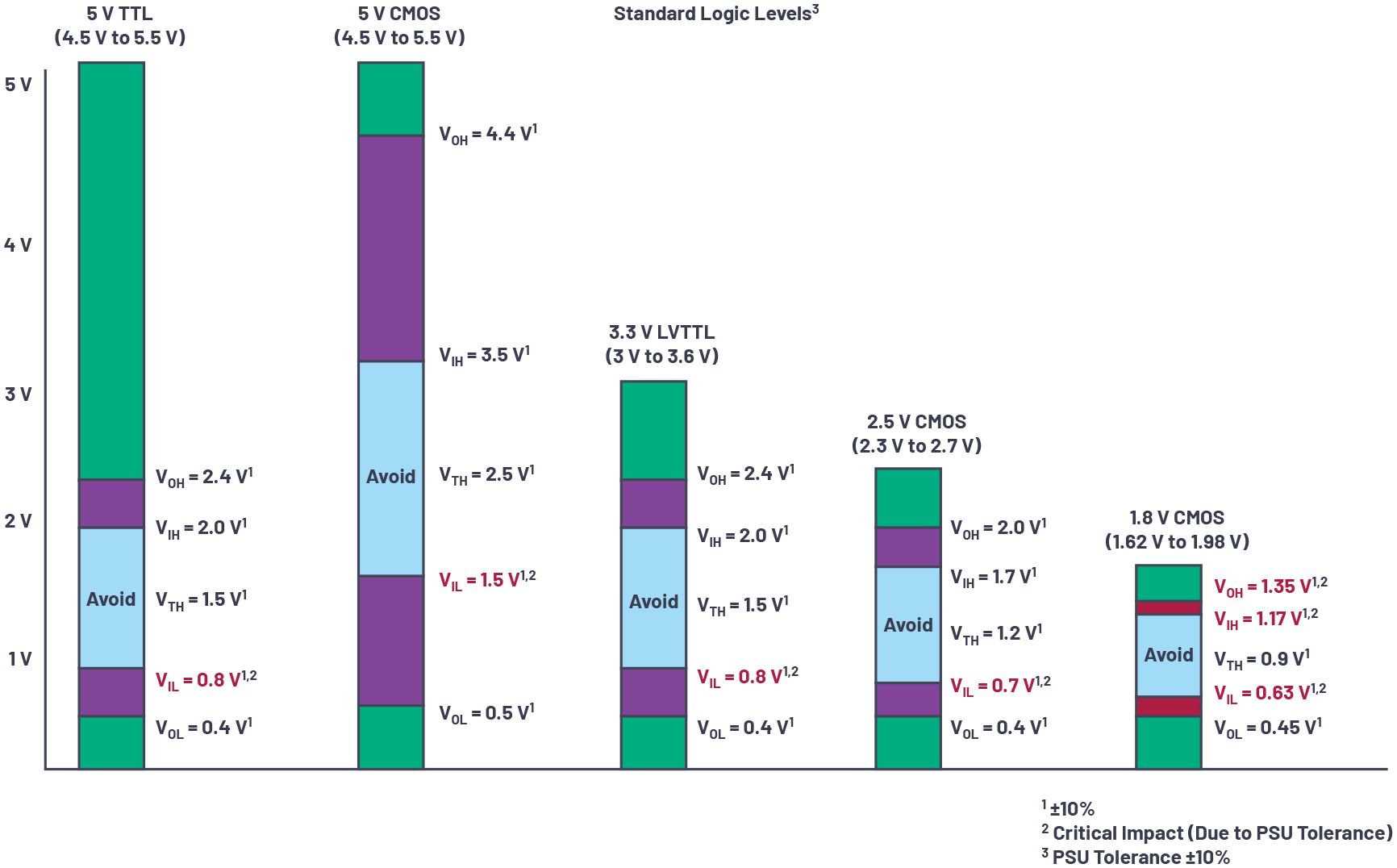

図2は、標準的なロジック・インターフェースで使用される電圧レベルについてまとめたものです。ここではTTLとCMOSを取り上げ、それぞれの閾値レベルと、許容される入出力電圧を示しています。本稿では、入力ロジックがどうなっていた場合にVILで示されるロー・レベルに駆動され、どうなっている場合にVIHで示されたハイ・レベルに駆動されるのかということに注目します。特に、図2において「無効」と記された閾値の不確定領域に焦点を絞ります。

あらゆるケースにおいて、電源については±10%の許容誤差を織り込む必要があります。図3は、図2と同様に、高速差動信号に対応するロジック・インターフェースのレベルについてまとめたものです。本稿では、図2で取り上げた標準ロジック・レベルを対象として解説を進めます。

スイッチング・ノイズ

スイッチング方式を採用した降圧/昇圧レギュレータには、適切にフィルタリングを施さなければなりません。さもなければ、数十mVから数百mVのスイッチング・ノイズが発生し、400mV~600mVに達するスパイクが生じる可能性があります。選択肢となるロジック・レベルとインターフェースに対し、スイッチング・ノイズによって問題になるレベルの影響が及ぶか否かを把握することが重要です。

セーフティ・マージン

堅牢な電源回路を実現するためには、適切なセーフティ・マージンを確保しなければなりません。設計上の経験則としては、最も厳しい条件を想定すると、-10%の誤差を許容できるようにする必要があります。例えば、5VのTTLではVILは0.8Vです。この場合、セーフティ・マージンを確保するとしたら、0.72Vに対応できるようにしなければなりません。同様に、1.8VのCMOSではVILが0.63Vなので、0.57Vに対応できるようにする必要があります。このようにマージンを確保することに伴い、閾値電圧VTHも低下します。5VのTTLではVTHが1.35V、1.8VのCMOSではVTHが0.81Vといった具合です。スイッチング・ノイズVNSは、数十mVから数百mVに達する可能性があります。また、ロジック回路からも信号ノイズVN(干渉ノイズ)が発生します。トータルのノイズ電圧VTNはVNとVNSの和になります。その値は、100mV~800mVに達する可能性があります。VTNを本来の信号VSIGに加えたものが、トータルの信号電圧VTSIGになります。つまり、VTSIG = VSIG + VTNです。このVTSIGが閾値電圧VTHに影響を及ぼし、無効領域は更に拡大します。この領域内にある信号のレベルは不確定なものとして扱われるので、ロジック回路はランダムにハイにもローにもなり得ます。論理が0であるはずの部分が誤って1と判定されてしまう可能性があるということです。

マルチレール電源に関する注意事項とヒント

閾値レベルについては、インターフェースの入力とIC内部のロジックの両方の観点から理解する必要があります。それにより、どれだけの電圧レベルを確保すればロジック・レベルが正しく判定されるのかを把握できます。逆に、どのようになったら、意に反して誤ったロジック・レベルで判定されるのかということもわかります。問題は、そうした閾値レベルを満たすためには、電源においてどれだけノイズを低く抑える必要があるのかということです。LDOレギュレータであれば発生するノイズはかなり小さいと言えます。しかし、降圧比が大きい場合には高い効率は得られません。スイッチング・レギュレータであれば効率的な降圧を実現できます。しかし、ある程度のノイズが発生することを覚悟しなければなりません。高効率で低ノイズの電源システムを実現するには、おそらくこれら2種類のレギュレータを何らかの形で組み合わせる必要があります。以下では、LDOレギュレータをスイッチング・レギュレータの後段に配置するハイブリッド方式をはじめ、様々な構成を紹介します。

効率を最大化しつつノイズを最小化するためのアプローチ

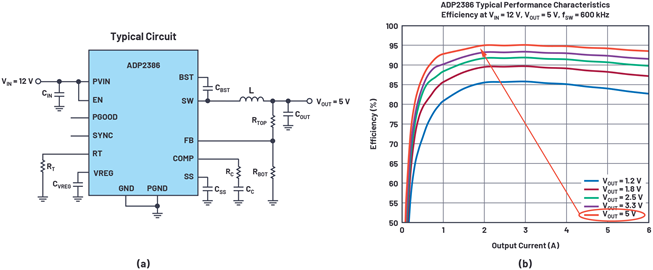

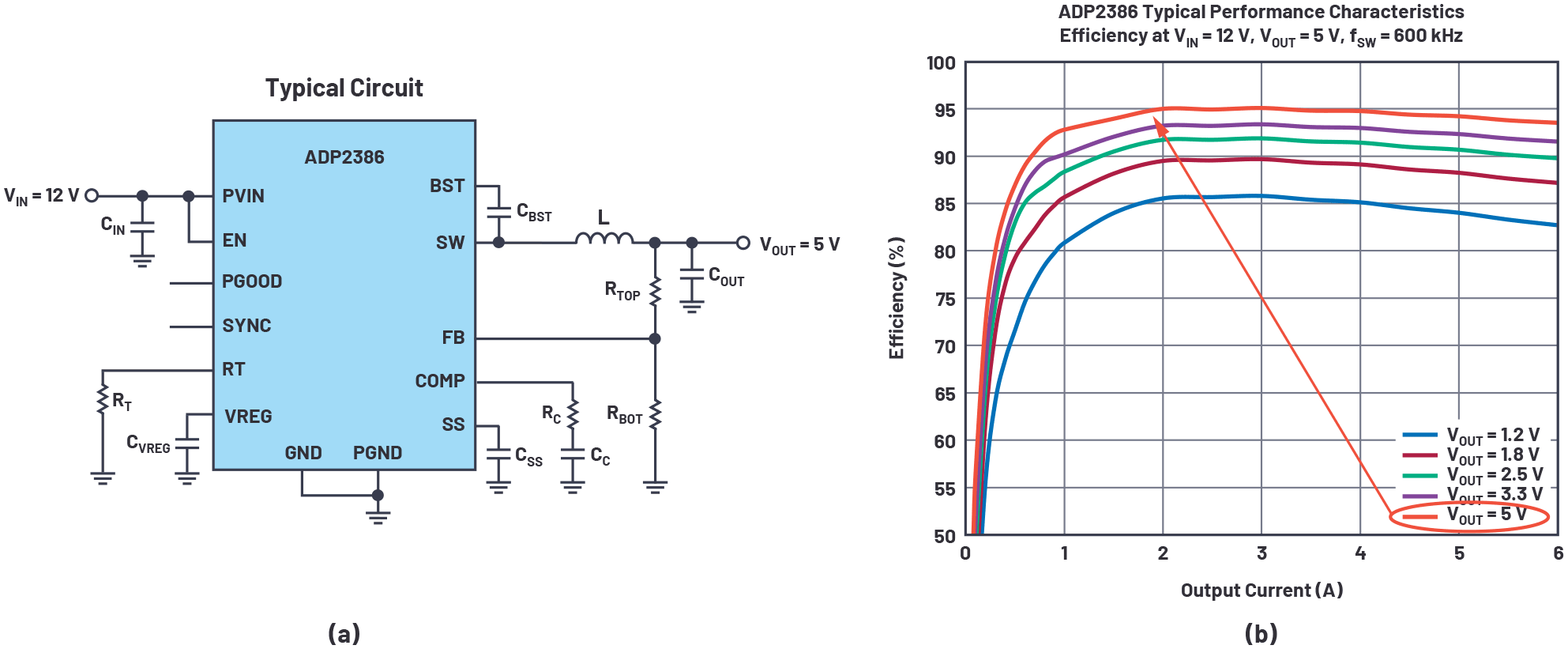

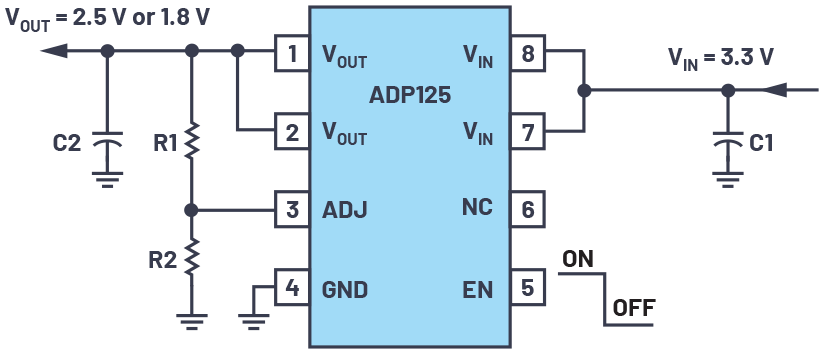

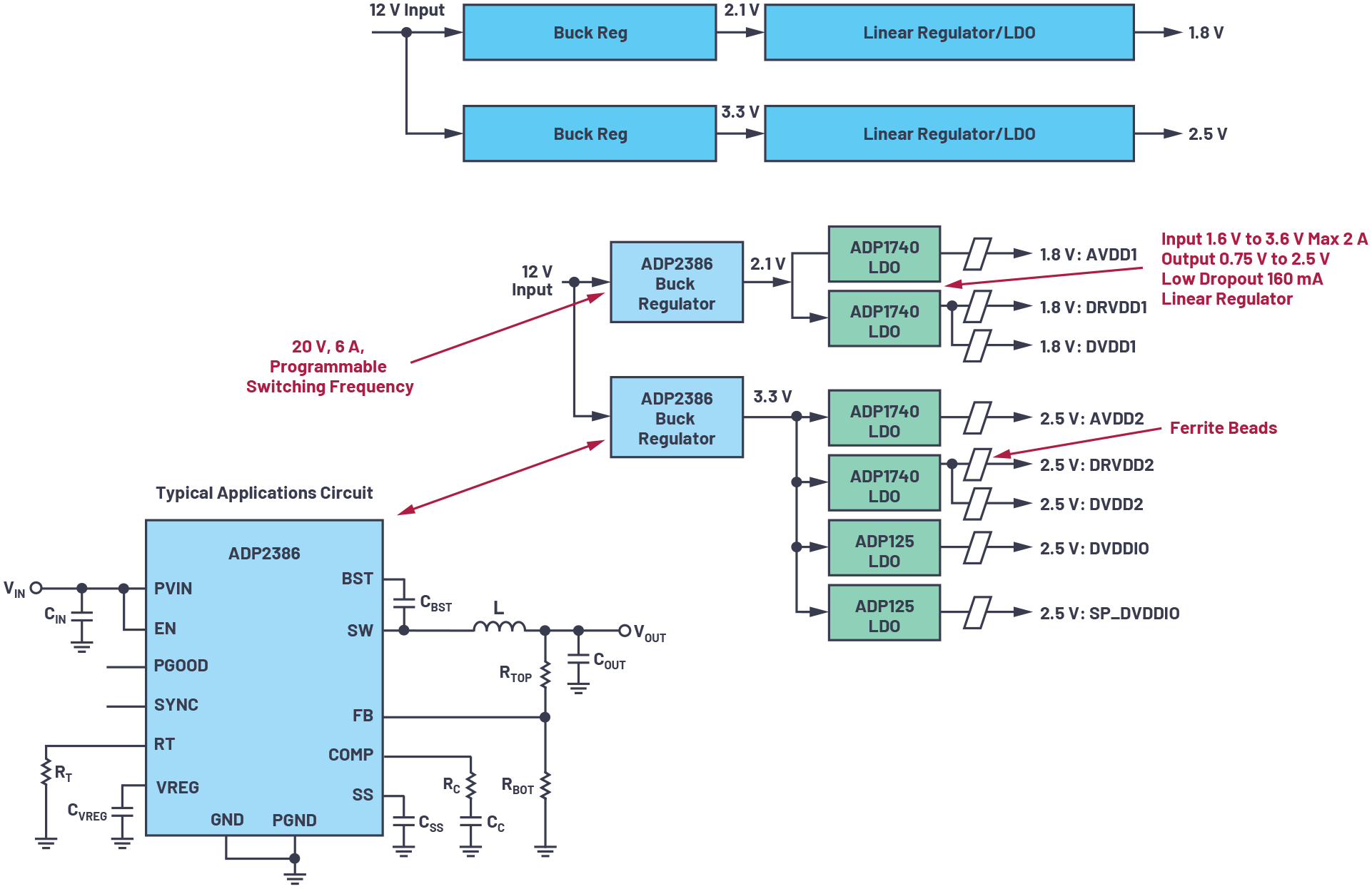

ここで再び図1のブロック図をご覧ください。このケースで、5Vのレギュレーションにおける効率を最大化しつつスイッチング・ノイズを最小化するには、どうすればよいでしょうか。1つの方法は、12Vの主電源と「ADP2386」などの降圧レギュレータを組み合わせることです。5VのTTL、5VのCMOSにおいて、VILはそれぞれ0.8Vと1.5Vです。こうした標準ロジックのインターフェース・レベルから考えると、許容マージンを満たすためには、スイッチング・レギュレータを選択しなければなりません。スイッチング方式の降圧トポロジを採用すれば、効率を最大化しつつ、5VのTTL/CMOSにおけるVIL未満にスイッチング・ノイズを抑えることができます。降圧レギュレータを活用する例として、図4(a)にADP2386の標準的な実用回路例を示しました。図4(b)には、この回路によって得られる効率を示しています。ご覧のように、最大95%の効率を達成できます。仮に、スイッチング方式の降圧レギュレータではなく、比較的低ノイズのLDOレギュレータを使用したとしたらどうなるでしょうか。その場合、入出力間で7Vの電圧降下が発生し、レギュレータの内部でかなりの電力が消費されることになります。その結果、効率が大幅に低下すると共に、多くの熱が発生します。コストを抑えつつ堅牢な設計を実現するためには、降圧レギュレータの後段にLDOレギュレータを配置して5Vを生成する方法が効果的です。

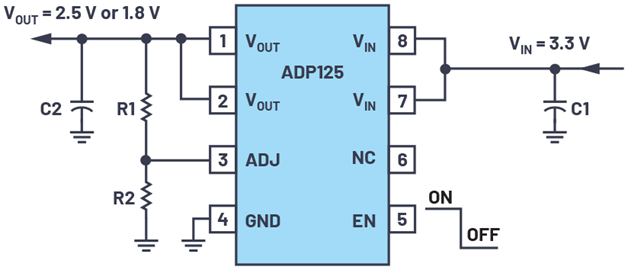

2.5Vと1.8VのCMOSでは、VILはそれぞれ0.7V、0.63Vとなります。残念ながら、スイッチング・ノイズが発生する状況では、このロジック・レベルにおいてセーフティ・マージンを確保することはできません。この問題を解決するには、3.3Vの主電源とリニア・レギュレータ(LDOレギュレータ)を組み合わせて回路を構成します。この方法は、図1に示した3.3Vの主電源が、十分な電力を供給可能でノイズも非常に小さい場合に適用できます。例えば、2.5Vの電源電圧の生成には「ADP125」(図5)、1.8Vの生成には「ADP1740」を使用できます。3.3Vから1.8Vに降圧する場合、1.5Vの電圧降下が生じます。この電圧降下が問題であれば、ハイブリッド構成にするとよいでしょう。セーフティ・マージンの問題には、もう1つの解決策があります。それは、12Vの主電源を入力とし、降圧レギュレータの後段にLDOレギュレータを配置することで、3.3V、2.5V、1.8Vを生成するというものです(図6)。3.3Vの主電源では十分な電力が供給できない場合や、ノイズが十分に小さいわけではない場合には、このようなハイブリッド方式が有効です。

LDOレギュレータを追加すると、コストと実装面積が少し増加します。放熱量もやや増えるでしょう。しかし、それはセーフティ・マージンを確保するために必要なトレードオフです。LDOレギュレータを使用すると、効率はやや低下します。ただ、入出力間の電圧降下を低く保つことにより、効率の低下を最小限に抑えることができます。3.3Vから1.8Vを生成するのであれば電圧降下は1.5Vですが、3.3Vから2.5Vを生成するのなら電圧降下を0.8Vに抑えられます。効率と遷移の特性は、VIOC機能を搭載するレギュレータを使用することで高められます。VIOC機能により、上流のスイッチング・レギュレータの出力が調整され、LDOレギュレータによる電圧降下が最適な値に維持されます。VIOC機能を搭載するレギュレータとしては、「LT3045」、「LT3042」、「LT3070-1」などが挙げられます。

LT3070-1は、5A出力で低ノイズのLDOレギュレータです。ドロップアウト電圧は85mVで、出力値はプログラムすることが可能です。LDOレギュレータを使用しなければならない場合には、放熱量が問題になります。消費電力はVDROP×Iで求められます。例えば、LT3070-1の出力電流を3Aとすると、このレギュレータによる消費電力の標準値は3A×85mV = 255mWになります。ドロップアウト電圧が400mVの一般的なLDOレギュレータの場合、出力電流を同じく3Aとすると、消費電力は1.2Wに達します。これは、LT3070-1を使用する場合のほぼ5倍にあたります。

ハイブリッド方式を採用すれば、コストと引き換えに効率を高めることができます。例えば、図6の構成であれば、効率と性能が最適化されます。まず降圧レギュレータ(ADP2386)によって最小許容電圧まで降圧することで、効率を最大限に高められます。その後にLDOレギュレータ(ADP1740/ADP125)によって必要な電圧を得ます。

なお、ここでは様々なトポロジや手法を紹介するために、一般的な設計例を示しました。実際には、電流の最大値、コスト、パッケージ、電圧降下などの項目について詳細に検討する必要があります。

また、なかにはノイズを小さく抑えた昇圧/降圧レギュレータも存在します。例えば、Silent Switcher ®レギュレータであれば、非常に高いノイズ性能とEMI性能が得られます。例えば、「LT8650S」や「LTC3310S」といった製品を採用したとします。そうすれば、性能、パッケージ、フットプリント、実装面積の面で高い費用対効果が得られます。

パッケージ、消費電力、コスト、効率、性能のトレードオフ

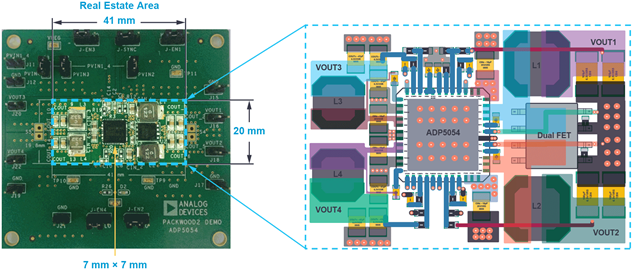

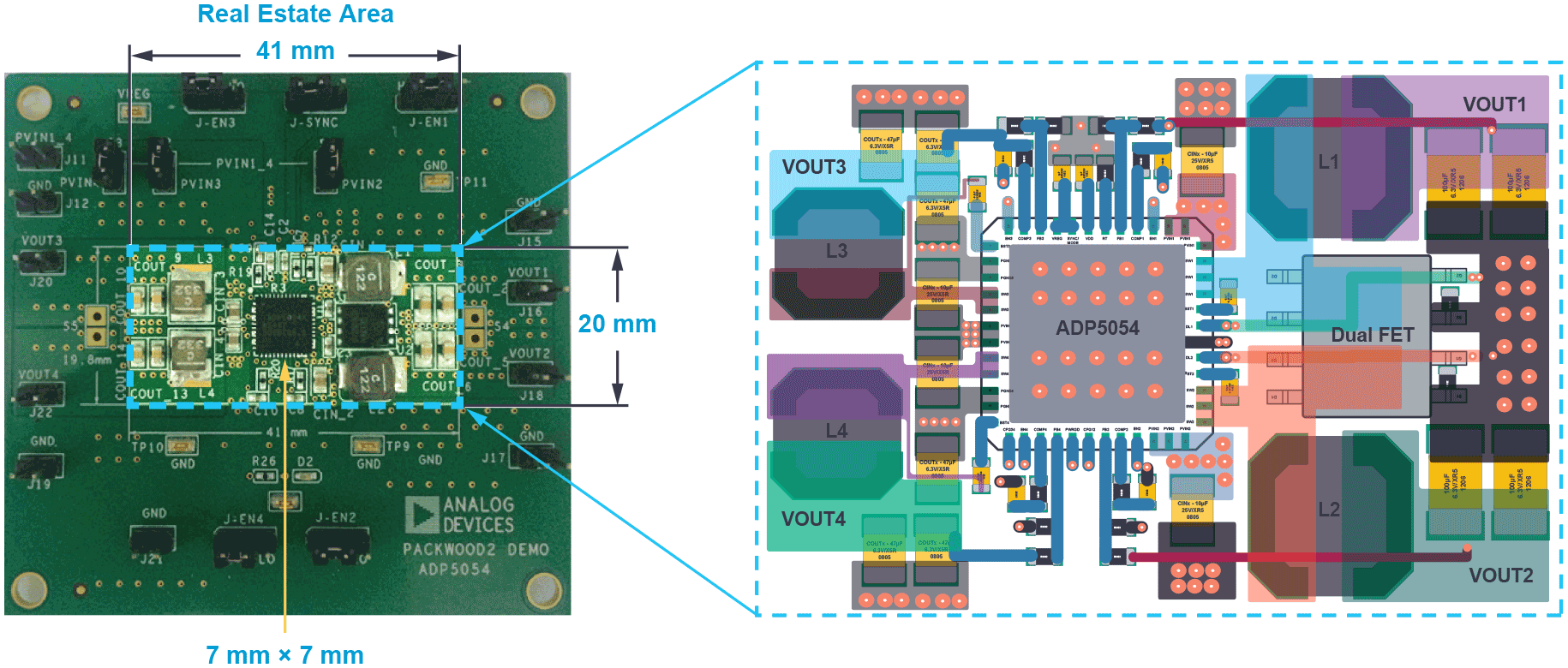

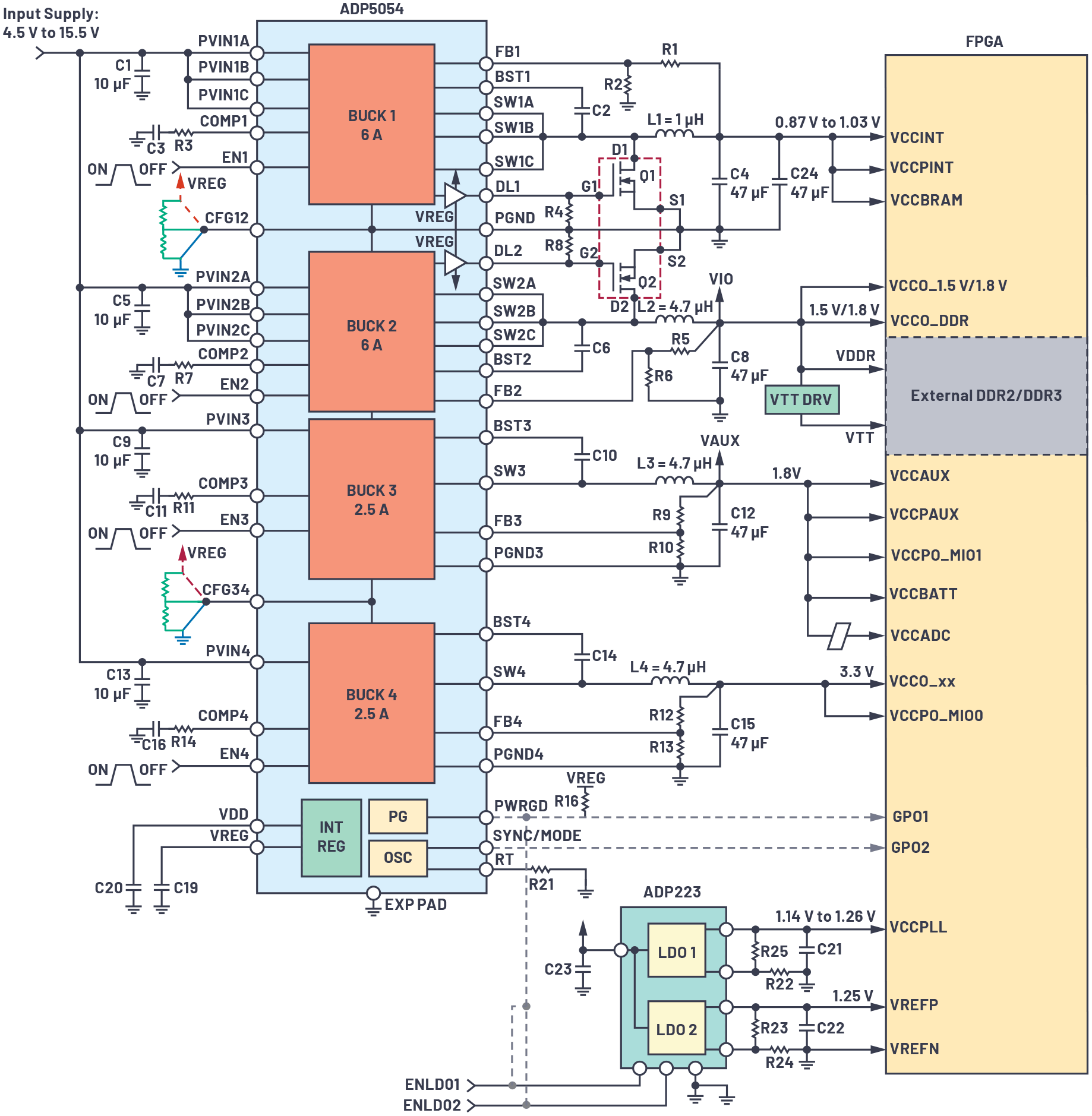

多くの場合、製品用のプリント回路基板を設計する際には、コンパクトなマルチレール電源によって大きな出力、高い効率、最大限の性能、ノイズの抑制を実現することが求められます。例えば、4つの降圧レギュレータを搭載するADP5054であれば、FPGAなどに対する大出力に対応可能なシングルチップのマルチレール電源ソリューションとして使用できます。図7に示すように、このソリューション全体の実装面積は約41mm×20mmに抑えられます。ADP5054そのもののフットプリントはわずか7mm×7mmです。しかも、計17Aの電流を供給できます。小さなスペースで非常に大きな電力を供給しなければならない場合には、μModule ®レギュレータの採用を検討してください。例えば「LTM4700」であれば、15mm×22mmのパッケージ・サイズで最大100Aの電流を供給できます。

次回の内容

次回(Part 2)では、ボードのレベルでカスケード方式を適用する方法について説明します。また、消費電力のバジェットとボードのレイアウトを考慮した上で適切なICを選択する方法など、設計上のヒントや秘訣を紹介します。

参考資料

「AD8045 Exposed Paddle Connection(AD8045の露出パドルの接続)」Analog Devices、2011年1月

「Header Pin(ヘッダ・ピン)」Digi-Key Electronics

Steve Knoth「超低ノイズLDOレギュレータによるクリーン電源の供給」Analog Devices、2018年9月

Christian Kueck「Application Note 139: Power Supply Layout and EMI(アプリケーション・ノート139:電源レイアウトとEMI)」 Linear Technology、2012年10月

「MT-093 Tutorial: Thermal Design Basics(MT-093 チュートリアル:熱設計の基本)」Analog Devices、2009年

Andy Radosevich「デジタルIC電源用のデュアル・リニア・レギュレータがオンザフライ出力調整と動的なヘッドルーム最適化を実現」Analog Devices、2020年4月

Henry J. Zhang「Application Note 136: PCB Layout Considerations for Nonisolated Switching Power Supplies(アプリケーション・ノート136:非絶縁型スイッチング電源のPCBレイアウトにおける考慮事項)」Linear Technology、2012年6月