ADSP-SC584

製造中デュアル・コアSHARC+とArm Cortex-A5 SOC、DDR、イーサネット、USB、349ボールcspBGA

- 製品モデル

- 9

- 1Ku当たりの価格

- 最低価格:$28.73

製品の詳細

-

SHARC+ コアの構造:

- 500 MHz(3.0GFLOPS)/コア

- パリティ付き5Mビット(640KB)L1メモリ/コア

- オプションのキャッシュ/SRAMモード

- 32ビット、40ビット、64ビット浮動小数点に対応

- 450 MHz ARM Cortex-A5(Neon/FPU付き)

- 32kByte/32kByteのL1命令/データ・キャッシュ

- 256kByteのL2キャッシュ

- ECC保護付き256KB L2 SRAM

- DDR3-900、DDR2-800、LPDDR(16ビット)

- FFT/iFFT(20 GFLOPS、1K-pt FFTあたり5usec)

- FIR/IIRフィルタとSINCフィルタ、ASRC

- OTP付きセキュリティ暗号化エンジン

- 19mm × 19mm BGA(0.8mmピッチ)

- 民生、工業、車載用

- ギガビット・イーサーネットMAC(RGMII)

- IEEE-1588 & AVBに対応(QoSとクロック再生)

- USB2.0 HS OTG/デバイス・コントローラ(MAC/PHY)

- 2x CAN2.0

- MLB 3/6ピン(車載用デバイスのみ)

- 最大8個のフルSPORTインターフェース(TDM & I2Sモード付き)

- S/PDIF Tx/Rx、8x ASRCペア、PCG

- 2x デュアルSPIと1x クワッドSPI(直接実行付き)

- 3x I2Cと3x UART(フロー・コントロール付き)

- 高度なパラレル・ペリフェラル・インターフェース

- ビデオI/O又はパラレル・コンバータ・インターフェース向け

- 2x リンク・ポート(双方向、8ビット、最大150MB/sec)

- 3x 改良型PWM、ADC制御モジュール(ACM)

- 8x GPタイマー、1x GP カウンター、WDTとRTC

- 最大80 GPIO(他のインターフェースとともにマルチプレックスされる)

- 8チャンネル、12ビット1MSPSハウスキーピングADC

- 熱センサー

ADSP-SC584プロセッサは新しい高性能、高電力効率、リアルタイム・シリーズの1つで、2個の高度なSHARC+®コアと高度なDSPアクセラレータ(FFT、FIR、IIR)を使用し毎秒最大24ギガ浮動小数点演算を行います。ADSP-SC58xとADSP-2158xのシリーズは消費電力が2ワット以下なので、この新しいプロセッサ・ラインアップは従来のSHARCプロセッサ製品と比べて5倍以上も電力効率が優れています。この利点により、温度管理の点で消費電力を制約しなければならないアプリケーションや、コストおよび信頼性の面で冷却ファンの追加ができないアプリケーションにおいても業界最先端のデジタル信号処理性能を提供します。応用分野としては、自動車、コンシューマおよびプロフェッショナル・オーディオ、多軸モーター制御、エネルギー供給システムなどがあります。

ADSP-SC58x製品は、SHARC+コアおよびDSPアクセラレータに加えてARM® Cortex-A5プロセッサ・コアを搭載しています。Cortex-A5が持つFPUおよびNeon® DSPによって、オーディオ、工業用クローズド・ループ・コントロール、工業用センシング・アプリケーションにおいて追加のリアルタイムタスク処理や、タイム・クリティカルなデータを扱うペリフェラルの制御を行なうことができます。ADSP-SC58xのインターフェースには、Gigabit Ethernet、高速USB、およびその他の柔軟で、かつシステム設計をシンプルにする多様な接続オプションがあります。

ADSP-2158xファミリーは主にDSPをコプロセッサとして必要とするアプリケーション向けに設計されており、2個のSHARC+コアとDSPコアに適合したペリフェラル・セットを内蔵しています。

コード互換性のある新しい高度なSHARC+コアはクロックレートと電力効率について改善されており、命令/データ・キャッシュ・オプション、ネイティブ倍精度の浮動小数点サポート、多数の他の新しい命令を追加しています。ADSP-SC58x/2158xファミリーは低消費電力用に設計され、低リークCMOSプロセスを採用しているので、105°C環境を念頭において500 MHzを実現し、将来より高性能で実施するためのロードマップを提供します。1.8 Mbytes以上の高速オンチップSRAMとDDR3/2/LPインターフェースは効率的なリアルタイム性能に役に立ち、メモリ・サブシステムは同時データ転送に主な強化機能となる高度なDMAエンジンを含んでいます。

高まる産業界のセキュリティに対する関心のソフトウェアIP保護に対しては、ARM® TrustZone®セキュリティや暗号化ハードウェア・アクセラレータを搭載しています。データの信頼性確保が必須の条件となっているアプリケーションには、メモリ・パリティおよびエラー訂正ハードウェアが、データの完全性を高めます。新しいADSP-SC58xおよびADSP-2158xシリーズは全体の機能が集積化されており、低消費電力なので、今日の複雑なアプリケーションに対して、BOM(部品材料)コストおよび基板面積を大幅に節減し、設計を簡素化し、市場投入時間を短縮します。

ADSP-SC58x/2158xはADIの受賞技術であるCrossCore® Embedded Studio開発ツール・スイートによってサポートされております。この統合開発環境は、システム設計を最適化し、市場投入までの時間短縮に貢献するインタラクティブかつリアルタイムな開発ツールを設計者に提供します。

アナログ・デバイセズはCrossCore Embedded Studio用のLinux Add-In(BuildrootをベースとするカスタムLinuxボード支援パッケージ)も提供します。このLinux Add-Inによってembedded Linux向けに用意されARM Cortex-A5コア上で動作する通信スタックやアプリケーション・パケッジの利用にご興味をいただけるようになります。Linuxの供給目標は2015年9月ですが、ご要求の際には、analog.com/srfのsoftware request formを完成し、追加コメント欄に「Linux SC58x Support」と特定してください。

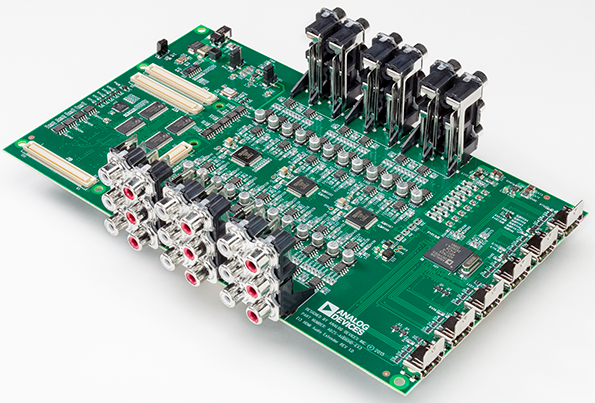

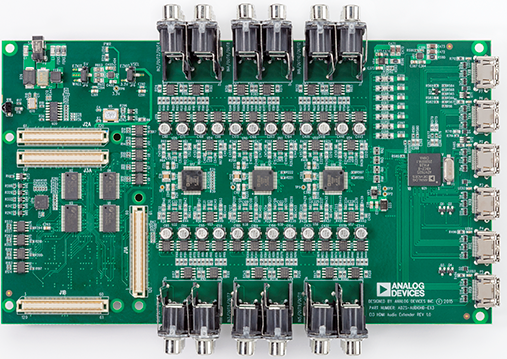

対応するADSP-SC584 EZ-KIT-Lite開発用ボードおよびICE-1000/2000エミュレータは先進的なアプリケーションの創造、テスト、およびデバッグを容易にします。エミュレータはCrossCore Embedded Studioとともに動作し、ARM社のCoreSight™を使用したJTAG準拠のすべてのアナログ・デバイセズプロセッサに対して最高水準のサポートを提供します。

ドキュメント

データシート 1

アプリケーション・ノート 17

プロセッサ・マニュアル 2

集積回路異常 1

情報 1

お客様の採用事例 1

珍問/難問集 1

| 製品モデル | ピン/パッケージ図 | 資料 | CADシンボル、フットプリント、および3Dモデル |

|---|---|---|---|

| ADSP-SC584BBCZ-3A | 349-Ball CSPBGA (19mm x 19mm) | ||

| ADSP-SC584BBCZ-4A | 349-Ball CSPBGA (19mm x 19mm) | ||

| ADSP-SC584BBCZ-5A | 349-Ball CSPBGA (19mm x 19mm) | ||

| ADSP-SC584CBCZ-3A | 349-Ball CSPBGA (19mm x 19mm) | ||

| ADSP-SC584CBCZ-4A | 349-Ball CSPBGA (19mm x 19mm) | ||

| ADSP-SC584CBCZ-5A | 349-Ball CSPBGA (19mm x 19mm) | ||

| ADSP-SC584KBCZ-3A | 349-Ball CSPBGA (19mm x 19mm) | ||

| ADSP-SC584KBCZ-4A | 349-Ball CSPBGA (19mm x 19mm) | ||

| ADSP-SC584KBCZ-5A | 349-Ball CSPBGA (19mm x 19mm) |

| 製品モデル | 製品ライフサイクル | PCN |

|---|---|---|

|

2 20, 2019 - 19_0030 Die Revision for ADSP-SC58x & ADSP-2158x SHARC Processors |

||

| ADSP-SC584BBCZ-3A | 製造中 | |

| ADSP-SC584BBCZ-4A | 製造中 | |

| ADSP-SC584BBCZ-5A | 製造中 | |

| ADSP-SC584CBCZ-3A | 製造中 | |

| ADSP-SC584CBCZ-4A | 製造中 | |

| ADSP-SC584CBCZ-5A | 製造中 | |

| ADSP-SC584KBCZ-3A | 製造中 | |

| ADSP-SC584KBCZ-4A | 製造中 | |

| ADSP-SC584KBCZ-5A | 製造中 | |

|

12 21, 2018 - 18_0142 Data sheet changes for ADSP-SC582,SC583,SC584,SC587,SC589,21583,21584,21587 |

||

| ADSP-SC584BBCZ-3A | 製造中 | |

| ADSP-SC584BBCZ-4A | 製造中 | |

| ADSP-SC584BBCZ-5A | 製造中 | |

| ADSP-SC584CBCZ-3A | 製造中 | |

| ADSP-SC584CBCZ-4A | 製造中 | |

| ADSP-SC584CBCZ-5A | 製造中 | |

| ADSP-SC584KBCZ-3A | 製造中 | |

| ADSP-SC584KBCZ-4A | 製造中 | |

| ADSP-SC584KBCZ-5A | 製造中 | |

|

7 20, 2017 - 17_0106 Data Sheet corrections for ADSP-2158x and ADSP-SC58x Products |

||

| ADSP-SC584BBCZ-3A | 製造中 | |

| ADSP-SC584BBCZ-4A | 製造中 | |

| ADSP-SC584CBCZ-3A | 製造中 | |

| ADSP-SC584CBCZ-4A | 製造中 | |

| ADSP-SC584KBCZ-3A | 製造中 | |

| ADSP-SC584KBCZ-4A | 製造中 | |

これは最新改訂バージョンのデータシートです。

ソフトウェア・リソース

ミドルウェア 2

- Operating Systems and Middleware

軽量TCP/IP(lwIP)スタック

CrossCore Embedded Studio向け軽量TCP/IP(lwIP)スタックは、組み込みプラットフォーム用に広く採用されているTCP/IPスタックの実装の1つで、TCP/IPセットの大半のネットワーキング・プロトコルに対応しています。

詳細を表示CrossCore®ユーティリティ

CrossCoreユーティリティは、Cortex-Mプロセッサで使用するための複数のユーティリティを提供します。これらのユーティリティは、以前はIARおよびKeilツールチェーン用にさまざまなボード・サポート・パッケージ内で配布されていましたが、現在はメンテナンス上の利便性を考慮してこの製品にまとめられています。

詳細を表示SigmaStudio®+

車載オーディオ、コネクティビティ、アルゴリズム/IPアプリケーション向けのシステム・レベル・ソリューション

詳細を表示CrossCore® Embedded Studio

CCESは、アナログ・デバイセズのBlackfin®、SHARC®、Arm®の各プロセッサ・ファミリ向けに用意された、世界トップクラスの統合開発環境(IDE)です。

詳細を表示SigmaStudio®

アナログ・デバイセズのDSPオーディオ・プロセッサおよびA2B®(オートモーティブ・オーディオ・バス)トランシーバー向けにプログラミング、開発、チューニングを行うソフトウェアのグラフィック開発ツール

詳細を表示評価用ソフトウェア 0

ツールおよびシミュレーション

評価用キット

最新のディスカッション

ADSP-SC584に関するディスカッションはまだありません。意見を投稿しますか?

EngineerZone®でディスカッションを始める