AD9209

新規設計に推奨12ビット、4GSPS、JESD204B/C、クワッドA/Dコンバータ

- 製品モデル

- 2

- 1Ku当たりの価格

- 最低価格:$1115.51

製品の詳細

- 柔軟性の高い再構成可能な共通プラットフォーム設計

- シングル、デュアル、クワッドバンドをサポート

- データパスおよびDSPブロックにより完全にバイパス可能

- マルチチップ同期機能搭載のオンチップPLL

- オフチップPLL用の外部RFクロック入力オプション

- 最大12GHzのクロック入力周波数に対応

- 最大4GSPSの最大ADCサンプル・レート

- JESD204C使用による最大4GSPSの最大データ・レート

- 8GHzのアナログ入力帯域幅(−3dB)

- ADCのAC性能(4GSPS時)

- 差動入力電圧:1.4Vp-p

- ノイズ密度:−151.5dBFS/Hz

- HD2:−69dBFS(2.7GHz、AIN = −1dBFS時)

- HD3:−76dBFS(2.7GHz、AIN = −1dBFS時)

- その他の最大高調波歪み(HD2とHD3を除く):2.7GHzで−79dBFS

- 補助機能

- 位相コヒーレント高速周波数ホッピング

- 分周比を選択可能なADCクロック・ドライバ

- 温度モニタリング・ユニット内蔵

- 柔軟性に優れたGPIOxピン

- 汎用デジタル機能

- 選択可能なデシメーション・フィルタ

- 設定可能なDDC

- 8つの微調整・複素DDCと4つの粗調整・複素DDC

- DDCあたり48ビットNCOを内蔵

- レシーバーのイコライゼーション用にプログラマブルな192タップPFIRフィルタ

- GPIOを介して4つの異なるプロファイル設定をロード可能

- データパスごとにプログラマブルな遅延

- AGC対応レシーバー

- 高速AGC制御用の低遅延・高速検出

- 低速AGC制御用の信号監視

- 専用のAGC対応ピン

- SERDES JESD204B/JESD204Cインターフェース、8レーン、最大24.75Gbps

- ADCあたり8レーン

- 8レーンJESD204B/JESD204C Tx(JTx)

- 実数または複素数のデジタル・データ(8、12、16、または24ビット)に対応

- 15mm × 15mm、0.8mmピッチ、324ボールBGA

AD9209は、クワッド12ビット、4GSPS A/Dコンバータ(ADC)です。ADC入力はオンチップの広帯域バッファと過負荷保護機能を使用しています。最大で8GHzの広帯域信号をダイレクト・サンプリングできるアプリケーションをサポートするように設計されています。オンチップ低位相ノイズのフェーズ・ロック・ループ(PLL)・クロック・シンセサイザは、ADCサンプリング・クロックを生成でき、高周波数クロック信号のプリント回路基板(PCB)分配を簡略化します。クロック出力バッファは、ADCサンプリング・クロックを他のデバイスに送信するために使用できます。

クワッドADCコアは1 × 10−20より良いコード誤差率(CER)を示します。低遅延高速検出および信号モニタリングは自動ゲイン制御(AGC)目的で使用できます。柔軟性に優れた192タップのプログラマブル有限インパルス応答(PFIR)フィルタはデジタル・フィルタリングやイコライゼーションで使用されます。プログラマブルなインテジャーおよびフラクショナルの遅延ブロックはアナログ遅延のミスマッチに対する補償をサポートします。

デジタル信号処理(DSP)ブロックは、1対のADCあたり2つの粗調整デジタル・ダウン・コンバータ(DDC)と4つの微調整DDCを備えています。各ADCはマルチバンド・アプリケーションに対応した1つまたは2つのメインDDC段で動作します。4つの追加微調整DDC段でADCあたり最大4つの帯域をサポートできます。各DDCと関連付けられた48ビット数値制御発振器(NCO)は、高速周波数ホッピング(FFH)をサポートすると同時に、汎用の入出力(GPIOx)ピンまたはシリアル・ポート・インターフェース(SPI)を介して選択された最大16の固有周波数の割り当てとの同期を維持します。

AD9209は、JESD204BまたはJESD204Cサブクラスの動作に合わせて構成可能な1つまたは2つのJTxリンクをサポートします。これにより、各ADCで異なるデータパス構成が可能になります。マルチデバイス同期は、SYSREF±入力ピンを通してサポートされています。

アプリケーション

- ワイヤレス通信インフラストラクチャ

- マイクロ波のポイントtoポイント、Eバンド、および5Gミリ波

- 広帯域通信システム

- DOCSIS 3.1および4.0 CMTS

- フェーズド・アレイ・レーダーおよび電子戦

- 電子テストおよび計測システム

ドキュメント

データシート 1

ユーザ・ガイド 1

アプリケーション・ノート 1

デザイン・ノート 1

技術記事 4

FPGA相互運用性レポート 1

デバイス・ドライバ 1

| 製品モデル | ピン/パッケージ図 | 資料 | CADシンボル、フットプリント、および3Dモデル |

|---|---|---|---|

| AD9209BBPZ-4G | 324-Ball BGA_ED (15mm x 15mm x 1.58mm) | ||

| AD9209BBPZRL-4G | 324-Ball BGA_ED (15mm x 15mm x 1.58mm) |

これは最新改訂バージョンのデータシートです。

ソフトウェア・リソース

デバイス・ドライバ 1

評価用ソフトウェア 1

JESD204x Frame Mapping Table Generator

The JESD204x Frame Mapping Table Generator tool consists of two Windows executables that will allow the user to input any valid combination of JESD204x parameters (L, M, F, S, NP) in order to output a .csv file that illustrates the frame mapping of the JESD204x mode in table format. There is an executable that allows the user to input a single JESD204x mode and another, that allows the user to input the parameters for multiple JESD204x modes in a specified .csv format in order to output a .csv file that illustrates the frame mapping of each of the JESD204x modes that were input into separate tables.

必要なソフトウェア/ドライバが見つかりませんか?

ハードウェア・エコシステム

| 製品モデル | 製品ライフサイクル | 詳細 |

|---|---|---|

| LTM4644 | 新規設計に推奨 | 構成可能な4A出力アレイを備えたクワッドDC/DC μModuleレギュレータ |

| ADP1765 | 新規設計に推奨 | 5 A、低VIN、低ノイズの CMOS リニア電圧レギュレータ |

| Clocks 1 | ||

| LTC6953 | 最終販売 | 11 の出力を備えた、JESD204B/JESD204C をサポートする超低ジッタ 4.5 GHz クロック分配器 |

| Fanout Buffers & Splitters 2 | ||

| HMC7043 | 新規設計に推奨 |

JESD204B/JESD204C 用機能付き、3.2 GHz、14 出力、高性能ファンアウト・バッファ |

| LTC6955 | 最終販売 | 超低ジッタ、7.5 GHz、11 出力ファンアウト・バッファ・ファミリー |

| Linear Regulators 3 | ||

| ADP7158 | 新規設計に推奨 | RF リニア電圧レギュレータ、2 A、固定出力、超低ノイズ、高 PSRR |

| ADM7172 | 新規設計に推奨 | 6.5V、2A、超低ノイズ、高PSRR、高速過渡応答CMOS LDO |

| ADM7150 | 新規設計に推奨 | リニア・レギュレータ(LDO)、800 m A、超低ノイズ/高PSRR |

| PLL Synthesizers 3 | ||

| ADF4377 | 新規設計に推奨 | VCO内蔵マイクロ波広帯域シンセサイザ |

| LTC6952 | 最終販売 | 11 の出力を備えた、JESD204B/JESD204C をサポートする超低ジッタ 4.5 GHz PLL |

| HMC7044 | 新規設計に推奨 |

JESD204B / JESD204 用機能付き、3.2 GHz、14 出力、高性能ジッター減衰器 |

| ステップダウン(降圧)レギュレータ 4 | ||

| LTM4633 | 新規設計に推奨 | トリプル10A降圧DC/DC μModuleレギュレータ |

| LTM8053 | 新規設計に推奨 | 40V入力、3.5A降圧Silent Switcher μModuleレギュレータ |

| LTM8063 | 新規設計に推奨 | 40VIN、2A Silent Switcher®(サイレント・スイッチャ)µモジュール・レギュレータ |

| LTM4616 | 新規設計に推奨 | デュアル8A/チャネル 低VIN、DC/DC μModuleレギュレータ |

| 完全差動アンプ 1 | ||

| ADL5580 | 新規設計に推奨 | 10dBゲインの完全差動10GHz ADCドライバ |

| 差動アンプおよびADC用ドライバ 1 | ||

| ADL5569 | 新規設計に推奨 | 6.5 GHz、超高感度ダイナミック・レンジ、差動アンプ |

ツールおよびシミュレーション

ADC Companion Transport Layer RTL Code Generator Tool

This command line executable tool generates a Verilog module which implements the JESD204 receive transport layer. The user specifies in a configuration file one or more modes to be supported by the transport layer module. These modes are defined as a set of JESD204 parameter values: L, M, F, S, N', and CF. The transport layer converts JESD204 lane data output from a JESD204 link layer IP to a data bus with a fixed width, containing interleaved virtual converter samples. Both JESD204B and JESD204C link layers are supported.

ツールを開くADIsimPLL™

アナログ・デバイセズの新しい高性能PLL製品を迅速かつ確実に評価できるツールです。現在利用できるツールの中で、最も総合的なPLLシンセサイザーの設計/シミュレーション・ツールです。実施されるシミュレーションには、主要な非線形効果が含まれており、これはPLLの性能に大きく影響を及ぼします。ADIsimPLLによって、設計プロセスの繰り返し作業が1つ以上排除されるため、設計から製品の市場投入までの期間が大幅に短縮することができます。

ツールを開くMxFE JESD204 Mode Selector Tool

The JESD204B/C Mode Selector Tool is a simple command line-based Windows executable that can be used to narrow down the number of JESD204x modes to only include those modes that support the user’s specific application use case. The tool guides the user through a use case description flow chart and gives the user a small list of applicable transmit and/or receive modes to choose from. This tool is applicable to the AD9081, AD9082, AD9177, AD9207, AD9209, AD9986, and AD9988.

ツールを開くSパラメータ 2

熱モデル 1

High Speed Converter Toolbox for MATLAB

ツールを開くAD9207/AD9209 AMI Model

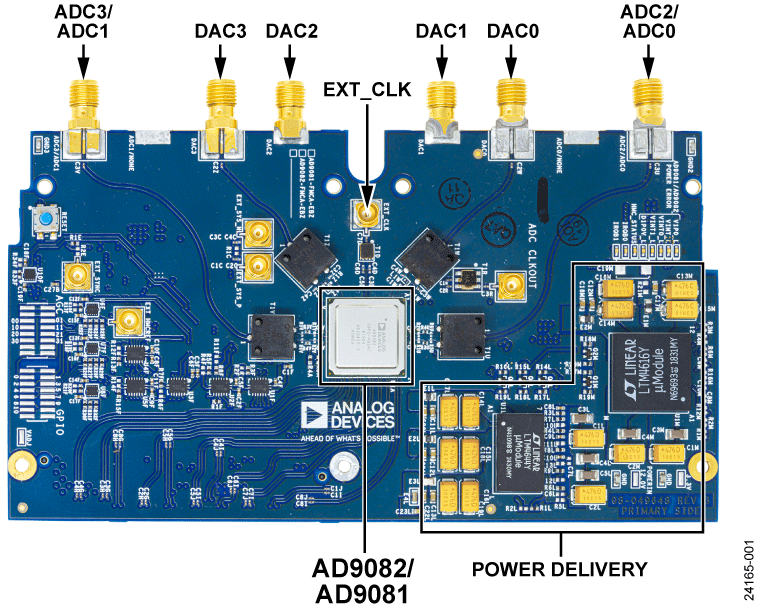

ツールを開く評価用キット

最新のディスカッション

AD9209に関するディスカッションはまだありません。意見を投稿しますか?

EngineerZoneでディスカッションを始める