ADRV9010

RECOMMENDED FOR NEW DESIGNSIntegrated, Quad RF Transceiver with Observation Path

- Part Models

- 3

- 1ku List Price

- Starting From $1020.78

Part Details

- 4 differential transmitters

- 4 differential receivers

- 2 observation receivers with 2 inputs each

- Center frequency

- 650 MHz to 3800 MHz (ADRV9010BBCZ)

- 650 MHz to 6000 MHz (ADRV9010BBCZ-A)

- Maximum receiver bandwidth: 200 MHz

- Maximum transmitter bandwidth: 200 MHz

- Maximum transmitter synthesis bandwidth: 450 MHz

- Maximum observation receiver bandwidth: 450 MHz

- Fully integrated independent fractional-N radio frequency synthesizers

- Fully integrated clock synthesizer

- Multichip phase synchronization for all local oscillators and baseband clocks

- JESD204B/JESD204C digital interface

The ADRV9010 is a highly integrated, radio frequency (RF) agile transceiver that offers four independently controlled transmitters, dedicated observation receiver inputs for monitoring each transmitter channel, four independently controlled receivers, integrated synthesizers, and digital signal processing functions to provide a complete transceiver solution. The device provides the high radio performance and low power consumption demanded by cellular infrastructure applications such as TDD-based small cell base station radios, macro 3G/4G/5G TDD systems, and TDD based massive multiple in/multiple out (MIMO) base stations. The ADRV9010BBCZ operates from 650 MHz to 3800 MHz, covering most of the licensed and unlicensed cellular bands. The ADRV9010BBCZ-A operates from 650 MHz to 6000 MHz.

The receiver subsystem consists of four independent, wide bandwidth, direct conversion receivers with state-of-the-art dynamic range. The four independent transmitters use an innovative direct conversion modulator that achieves high modulation accuracy with exceptionally low noise. The ADRV9010 device also includes two wide bandwidth, time shared observation path receivers with two inputs each for monitoring transmitter outputs.

The complete transceiver subsystem includes automatic and manual attenuation control, dc offset correction, quadrature error correction (QEC), and digital filtering, eliminating the need for these functions in the digital baseband. Other auxiliary functions such as analog-to-digital converters (ADCs), digital-to-analog converters (DACs), and general-purpose input/outputs (GPIOs) that provide an array of digital control options are also integrated.

To achieve a high level of RF performance, the transceiver includes five fully integrated phase-locked loops (PLLs). Two PLLs provide high performance, low power fractional-N RF synthesis for the transmitter and receiver signal paths. One fully integrated PLL also supports an independent local oscillator (LO) mode for the observation receiver. Another PLL generates the clocks needed for the converters and digital circuits and a fifth PLL provides the clock for the serial data interface. A multichip synchronization mechanism synchronizes the phases of all LOs and baseband clocks between multiple ADRV9010 chips. All voltage controlled oscillators (VCOs) and loop filter components are integrated and adjustable through the digital control interface.

The serial data interface consists of eight serializer lanes and eight deserializer lanes. The interface supports both the JESD204B and JESD204C standards, operating at data rates up to 16.22016 Gbps. The interface also supports interleaved mode for lower bandwidths, thus reducing the number of high speed data interface lanes to one. Both fixed and floating-point data formats are supported. The floating-point format allows internal automatic gain control (AGC) to be invisible to the demodulator device.

The ADRV9010 is powered directly from 1.0 V, 1.3 V, and 1.8 V regulators and is controlled via a standard serial peripheral interface (SPI). Comprehensive power-down modes are included to minimize power consumption in normal use. The ADRV9010 is packaged in a 14 mm × 14 mm, 289-ball chip scale ball grid array (CSP_BGA).

APPLICATIONS

- 3G/4G/5G TDD macro and small cell base stations

- TDD active antenna systems for advanced LTE and 5G

For technical support, please post questions directly on the ADRV9010 EngineerZone® forum or email adrv9010_support@analog.com. Please note the questions sent through email will be answered on the ADRV9010 EngineerZone® forum.

Documentation

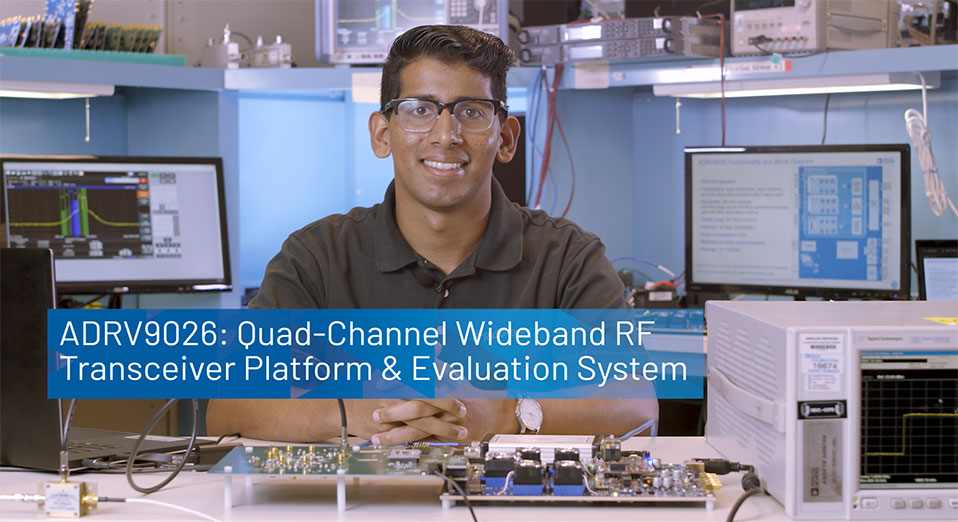

Video 1

Product Selection Guide 1

ADI has always placed the highest emphasis on delivering products that meet the maximum levels of quality and reliability. We achieve this by incorporating quality and reliability checks in every scope of product and process design, and in the manufacturing process as well. "Zero defects" for shipped products is always our goal. View our quality and reliability program and certifications for more information.

| Part Model | Pin/Package Drawing | Documentation | CAD Symbols, Footprints, and 3D Models |

|---|---|---|---|

| ADRV9010BBCZ | 289-Ball CSPBGA (14 mm x 14 mm x 1.34 mm) | ||

| ADRV9010BBCZ-A | 289-Ball CSPBGA (14 mm x 14 mm x 1.34 mm) | ||

| ADRV9010BBCZ-REEL | 289-Ball CSPBGA (14 mm x 14 mm x 1.34 mm) |

This is the most up-to-date revision of the Data Sheet.

Software Resources

Evaluation Software 2

ADRV9010 Release Build Software Release Notes (PDF) SW4.1.0.84

The SW4.1.0.84 release build provides ARM firmware, stream files, API, and GUI software to support the ADRV9010.

ADRV9010 Released Software SW4.1.0.84

The ADRV9010 software package contains the GUI software, the API source code, the firmware file, and the gain tables. The GUI software enables transceiver testing using the evaluation board and the Windows GUI. The API source code is intended for use in a customer system and can be integrated with the rest of the customer code and compiled for the target system. The firmware file in binary format is used by the ARM® processor on the transceivers. The gain tables include the receiver gain tables and transmitter attenuation table. Note that the files within the zip must be used together. For example, the ARM files from one zip file cannot be used with the API files from another version.

Tools & Simulations

Design Tool 1

ADIsimRF

ADIsimRF is an easy-to-use RF signal chain calculator. Cascaded gain, noise, distortion and power consumption can be calculated, plotted and exported for signal chains with up to 50 stages. ADIsimRF also includes an extensive data base of device models for ADI’s RF and mixed signal components.

Open ToolLatest Discussions

No discussions on ADRV9010 yet. Have something to say?

Start a Discussion on EngineerZone®