AD9278

RECOMMENDED FOR NEW DESIGNSOctal LNA/VGA/AAF/ADC and CW I/Q Demodulator

- Part Models

- 1

- 1ku List Price

- Starting From $61.63

Part Details

- Low power: 88 mW per channel, TGC mode, 40 MSPS;

32 mW per channel, CW mode - 10 mm × 10 mm, 144-ball CSP-BGA

- TGC channel input-referred noise: 1.3 nV/√Hz, max gain

- Flexible power-down modes

- Fast recovery from low power standby mode: <2 μs

- Overload recovery: <10 ns

- Input-referred noise: 1.25 nV/√Hz, gain = 21.3 dB

- Programmable gain: 15.6 dB/17.9 dB/21.3 dB

- 0.1 dB compression: 1000 mV p-p/750 mV p-p/450 mV p-p

- Dual-mode active input impedance matching

- Bandwidth (BW): >50 MHz

- Programmable second-order LPF from 8 MHz to 18 MHz

- Programmable HPF

- Attenuator range: −45 dB to 0 dB

- Postamp gain (PGA): 21 dB/24 dB/27 dB/30 dB

- Linear-in-dB gain control

- SNR: 70 dB, 12 bits up to 65 MSPS

- Serial LVDS (ANSI-644, low power/reduced signal)

- Individual programmable phase rotation

- Output dynamic range per channel: >158 dBc/√Hz

- Output-referred SNR: 153 dBc/√Hz, 1 kHz offset, −3dBFS

The AD9278 is designed for low cost, low power, small size, and ease of use. It contains eight channels of a variable gain amplifier (VGA) with a low noise preamplifier (LNA); an anti-aliasing filter (AAF); a 12-bit, 10 MSPS to 65 MSPS analog-to-digital converter (ADC); and an I/Q demodulator with programmable phase rotation.

Each channel features a variable gain range of 45 dB, a fully differential signal path, an active input preamplifier termination, a maximum gain of up to 51 dB, and an ADC with a conversion rate of up to 65 MSPS. The channel is optimized for dynamic performance and low power in applications where a small package size is critical.

The LNA has a single-ended-to-differential gain that is selectable through the SPI. The LNA input noise is typically 1.3 nV/√Hz at a gain of 21.3 dB, and the combined input-referred noise of the entire channel is 1.3 nV/√Hz at maximum gain. Assuming a 15 MHz noise bandwidth (NBW) and a 21.3 dB LNA gain, the input SNR is roughly 88 dB. In CW Doppler mode, each LNA output drives an I/Q demodulator. Each demodulator has independently programmable phase rotation through the SPI with 16 phase settings.

The AD9278 requires a LVPECL-/CMOS-/LVDS-compatible sample rate clock for full performance operation. No external reference or driver components are required for many applications.

The ADC automatically multiplies the sample rate clock for the appropriate LVDS serial data rate. A data clock (DCO±) for capturing data on the output and a frame clock (FCO±) trigger for signaling a new output byte are provided.

Powering down individual channels is supported to increase battery life for portable applications. A standby mode option allows quick power-up for power cycling. In CW Doppler operation, the VGA, AAF, and ADC are powered down. The power of the TGC path scales with selectable ADC speed power modes.

The ADC contains several features designed to maximize flexibility and minimize system cost, such as a programmable clock, data alignment, and programmable digital test pattern generation. The digital test patterns include built-in fixed patterns, built-in pseudo-random patterns, and custom user-defined test patterns entered via the serial port interface.

Fabricated in an advanced BiCMOS process, the AD9278 is available in a 10 mm × 10 mm, RoHS compliant, 144-lead BGA. It is specified over the industrial temperature range of −40°C to +85°C.

Documentation

Data Sheet 1

Technical Articles 1

ADI has always placed the highest emphasis on delivering products that meet the maximum levels of quality and reliability. We achieve this by incorporating quality and reliability checks in every scope of product and process design, and in the manufacturing process as well. "Zero defects" for shipped products is always our goal. View our quality and reliability program and certifications for more information.

| Part Model | Pin/Package Drawing | Documentation | CAD Symbols, Footprints, and 3D Models |

|---|---|---|---|

| AD9278BBCZ | 144-Ball CSPBGA (10mm x 10mm x 1.4mm) |

| Part Models | Product Lifecycle | PCN |

|---|---|---|

|

Jun 29, 2012 - 12_0139 AD9278 Silicon Revision |

||

| AD9278BBCZ | PRODUCTION | |

This is the most up-to-date revision of the Data Sheet.

Software Resources

Can't find the software or driver you need?

Request a Driver/SoftwareHardware Ecosystem

| Parts | Product Life Cycle | Description |

|---|---|---|

| Analog-to-Digital Converters (ADCs) 1 | ||

| AD7982 | PRODUCTION | 18-Bit, 1 MSPS PulSAR ADC in MSOP/LFCSP |

| Clock ICs 6 | ||

| AD9510 | RECOMMENDED FOR NEW DESIGNS | 1.2 GHz Clock Distribution IC, PLL Core, Dividers, Delay Adjust, Eight Outputs |

| AD9511 | RECOMMENDED FOR NEW DESIGNS | 1.2 GHz Clock Distribution IC, PLL Core, Dividers, Delay Adjust, Five Outputs |

| AD9512 | RECOMMENDED FOR NEW DESIGNS | 1.2 GHz Clock Distribution IC, Two 1.6 GHz Inputs, Dividers, Delay Adjust, Five Outputs |

| AD9513 | RECOMMENDED FOR NEW DESIGNS | 800 MHz Clock Distribution IC, Dividers, Delay Adjust, Three Outputs |

| AD9514 | RECOMMENDED FOR NEW DESIGNS | 1.6 GHz Clock Distribution IC, Dividers, Delay Adjust, Three Outputs |

| AD9515 | RECOMMENDED FOR NEW DESIGNS | 1.6 GHz Clock Distribution IC, Dividers, Delay Adjust, Two Outputs |

| Differential Amplifiers 2 | ||

| AD8138 | PRODUCTION | Low Distortion Differential ADC Driver |

| ADA4932-1 | RECOMMENDED FOR NEW DESIGNS | Low Power Differential ADC Driver |

| Fanout Buffers & Splitters 2 | ||

| ADCLK846 | RECOMMENDED FOR NEW DESIGNS | 1.8 V, 6 LVDS/12 CMOS Outputs Low Power Clock Fanout Buffer |

| ADCLK946 | RECOMMENDED FOR NEW DESIGNS | Six LVPECL Outputs, SiGe Clock Fanout Buffer |

| Operational Amplifiers 2 | ||

| ADA4896-2 | RECOMMENDED FOR NEW DESIGNS | 1 nV/√Hz, Low Power, Rail-to-Rail Output Amplifiers |

| ADA4897-2 | RECOMMENDED FOR NEW DESIGNS | 1 nV/√Hz, Low Power Operational Amplifier |

Tools & Simulations

Visual Analog

For designers who are selecting or evaluating high speed ADCs, VisualAnalog™ is a software package that combines a powerful set of simulation and data analysis tools with a user-friendly graphical interface.

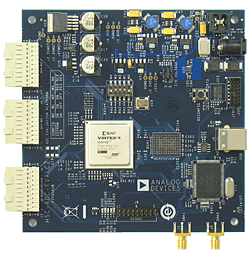

Open ToolEvaluation Kits

Latest Discussions

No discussions on AD9278 yet. Have something to say?

Start a Discussion on EngineerZone®