AD6676

RECOMMENDED FOR NEW DESIGNSWideband IF Receiver Subsystem

- Part Models

- 1

- 1ku List Price

- Starting From $186.18

Part Details

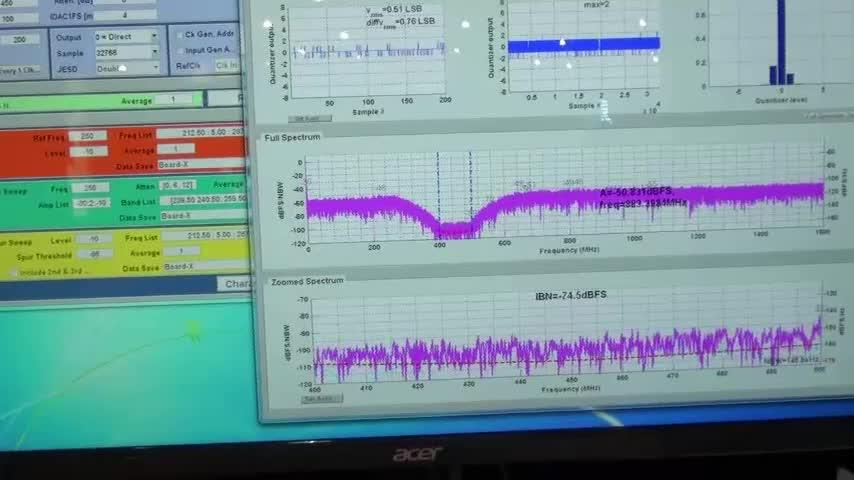

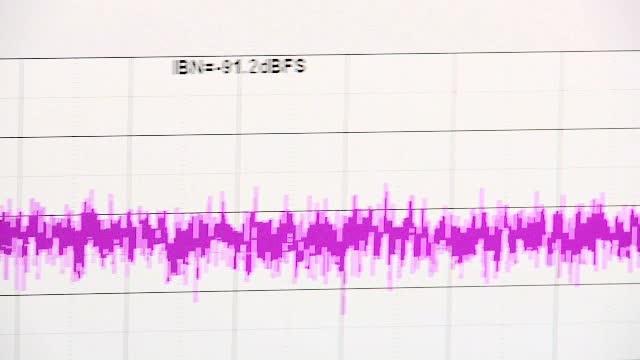

- High instantaneous dynamic range

- Noise figure (NF) as low as 13 dB

- Noise spectral density (NSD) as low as −159 dBFS/Hz

- IIP3 up to 36.9 dBm with spurious tones <−99 dBFS

- Tunable band-pass Σ-Δ analog-to-digital converter (ADC)

- 20 MHz to 160 MHz signal bandwidth

- 70 MHz to 450 MHz IF center frequency

- Configurable input full-scale level of −2 dBm to −14 dBm

- Easy to drive resistive IF input

- Gain flatness of 1 dB with under 0.5 dB out-of-band peaking

- Alias rejection greater than 50 dB

- 2.0 GSPS to 3.2 GSPS ADC clock rate

- On-chip PLL clock multiplier

- 16-bit I/Q rate up to 266 MSPS

- On-chip digital signal processing

- NCO and quadrature digital downconverter (QDDC)

- Selectable decimation factor of 12, 16, 24, and 32

- Automatic gain control (AGC) support

- On-chip attenuator with 27 dB span in 1 dB steps

- Fast attenuator control via configurable AGC data port

- Peak detection flags with programmable thresholds

- Single or dual lane, JESD204B capable

- Low power consumption: 1.20 W

- 1.1 V and 2.5 V supply voltage

- TDD power saving up to 60%

- 4.3 mm × 5.0 mm WLCSP

The AD6676 is a highly integrated IF subsystem that can digitize radio frequency (RF) bands up to 160 MHz in width centered on an intermediate frequency (IF) of 70 MHz to 450 MHz. Unlike traditional Nyquist IF sampling ADCs, the AD6676 relies on a tunable band-pass Σ-Δ ADC with a high oversampling ratio to eliminate the need for band specific IF SAW filters and gain stages, resulting in significant simplification of the wideband radio receiver architecture. On-chip quadrature digital downconversion followed by selectable decimation filters reduces the complex data rate to a manageable rate between 62.5 MSPS to 266.7 MSPS. The 16-bit complex output data is transferred to the host via a single or dual lane JESD204B interface supporting line rates of up to 5.333 Gbps.

Applications

- Wideband cellular infrastructure equipment and repeaters

- Point-to-point microwave equipment

- Instrumentation

- Spectrum and communication analyzers

- Software defined radio

Sample orders for small quantities may be coordinated by contacting highspeed.converters@analog.com.

Documentation

Data Sheet 1

User Guide 1

Technical Articles 4

Informational 1

Video 3

FPGA Interoperability Reports 2

Device Drivers 2

Webcast 3

ADI has always placed the highest emphasis on delivering products that meet the maximum levels of quality and reliability. We achieve this by incorporating quality and reliability checks in every scope of product and process design, and in the manufacturing process as well. "Zero defects" for shipped products is always our goal. View our quality and reliability program and certifications for more information.

| Part Model | Pin/Package Drawing | Documentation | CAD Symbols, Footprints, and 3D Models |

|---|---|---|---|

| AD6676BCBZRL | 80-Ball WLCSP (4.29mm x 5.04mm) |

| Part Models | Product Lifecycle | PCN |

|---|---|---|

|

Mar 13, 2018 - 18_0042 AD6676 Assembly Bumping Site Transfer from Amkor to TSMC |

||

| AD6676BCBZRL | PRODUCTION | |

This is the most up-to-date revision of the Data Sheet.

Software Resources

Evaluation Software 2

JESD204x Frame Mapping Table Generator

The JESD204x Frame Mapping Table Generator tool consists of two Windows executables that will allow the user to input any valid combination of JESD204x parameters (L, M, F, S, NP) in order to output a .csv file that illustrates the frame mapping of the JESD204x mode in table format. There is an executable that allows the user to input a single JESD204x mode and another, that allows the user to input the parameters for multiple JESD204x modes in a specified .csv format in order to output a .csv file that illustrates the frame mapping of each of the JESD204x modes that were input into separate tables.

JESD204 Interface Framework

Integrated JESD204 software framework for rapid system-level development and optimization

Can't find the software or driver you need?

Hardware Ecosystem

| Parts | Product Life Cycle | Description |

|---|---|---|

| LDO Linear Regulators 2 | ||

| ADP223 | RECOMMENDED FOR NEW DESIGNS | Dual, 300 mA Adjustable Output, Low Noise, High PSRR Voltage Regulator |

| ADP1752 | PRODUCTION | 800mA Low-Vin LDO Regulator |

| Low-Noise Amplifiers (LNAs) & Power Amplifiers 2 | ||

| ADL5541 | PRODUCTION |

20 MHz to 6 GHz RF/IF Gain Block, Fixed Gain of 15 dB |

| ADL5542 | PRODUCTION |

20 MHz to 6 GHz RF/IF Gain Block, Fixed Gain of 20 dB |

| Phase-Locked Loop (PLL) Synthesizers 1 | ||

| ADF4355-2 | RECOMMENDED FOR NEW DESIGNS | Microwave Wideband Synthesizer with Integrated VCO |

| RF Mixers 2 | ||

| ADRF6620 | Obsolete | 700 MHz to 2700 MHz RX Mixer with Integrated IF DGA, Fractional-N PLL, and VCO |

| ADL5801 | RECOMMENDED FOR NEW DESIGNS | High IP3, 10 MHz TO 6 GHz, Active Mixer |

Tools & Simulations

ADC Companion Transport Layer RTL Code Generator Tool

This command line executable tool generates a Verilog module which implements the JESD204 receive transport layer. The user specifies in a configuration file one or more modes to be supported by the transport layer module. These modes are defined as a set of JESD204 parameter values: L, M, F, S, N', and CF. The transport layer converts JESD204 lane data output from a JESD204 link layer IP to a data bus with a fixed width, containing interleaved virtual converter samples. Both JESD204B and JESD204C link layers are supported.

Open ToolAD6676 AMI Model

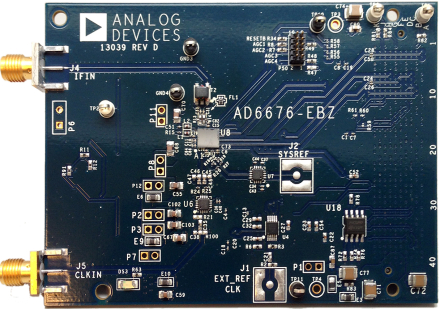

Open ToolEvaluation Kits

Latest Discussions

No discussions on AD6676 yet. Have something to say?

Start a Discussion on EngineerZone®