はじめに

自動試験装置(ATE)やマシン・オートメーション、産業用/医療用の計測機器などのアプリケーションには、高精度のデータ・アクイジション・システムが必要になります。物理的な情報、アナログの情報を正確にデジタル化し、解析できるようにしなければならないからです。そうしたシステムでは、分解能/精度が高い逐次比較型のA/D コンバータ(SAR ADC)が使用されます。ただ、その種の ADC を使用する際、データシートに記載されているとおりの性能を引き出すのは容易なことではありません。従来型の SAR ADC を使用する場合、スイッチド・キャパシタ入力を駆動するために、出力能力が高く高速な専用のアンプを使用しなければならなくなることがよくあります。これは、高精度なデータ・アクイジション・システム向けのシグナル・チェーンを設計する際に遭遇する、一般的な課題の 1 つです。本稿では、この問題を解決することが可能なピン互換の ADC ファミリー「AD4000」を紹介します。このファミリーは、分解能が16/18/20 ビットの製品から成ります。各製品は、アナログ・デバイセズの先進的な技術と最先端のアーキテクチャを採用して設計されています。いずれも使いやすい機能を備えており、シグナル・チェーンの消費電力を抑えつつ複雑さを緩和したり、性能を大きく損なうことなくチャンネルの密度を高めたりすることが可能なシステム・レベルのメリットを数多く提供します。AD4000 ファミリーの特徴の 1 つは、ハイ Z モード(入力が高インピーダンスのモード)、少ない入力電流、長いアクイジション・フェーズが組み合わせられていることです。それにより、ADC の駆動に関する問題が軽減され、ドライバに対するセトリングの要件が緩和されます。結果として、駆動に使用できるアンプの選択肢が増加します。例えば、DC や低周波信号(10 kHz 未満)を扱うアプリケーションに対し、消費電力が少ないものの帯域幅の狭い JFET 入力のアンプや、精度の高い計装アンプなどを適用できるようになります。本稿は、以前アナログ・ダイアログに掲載された記事1の続編です。今回の記事では、カットオフ周波数の低い RC フィルタとともに使用可能な高精度のアンプをいくつか紹介します。いずれも、最適な性能を達成しつつ、AD4000 ファミリーの製品を直接駆動することができます。それらを利用することにより、ADC 専用のドライバ段が不要になり、システムの消費電力、基板面積、部品コストを大幅に削減することが可能になります。

従来型SAR ADCの入力の駆動

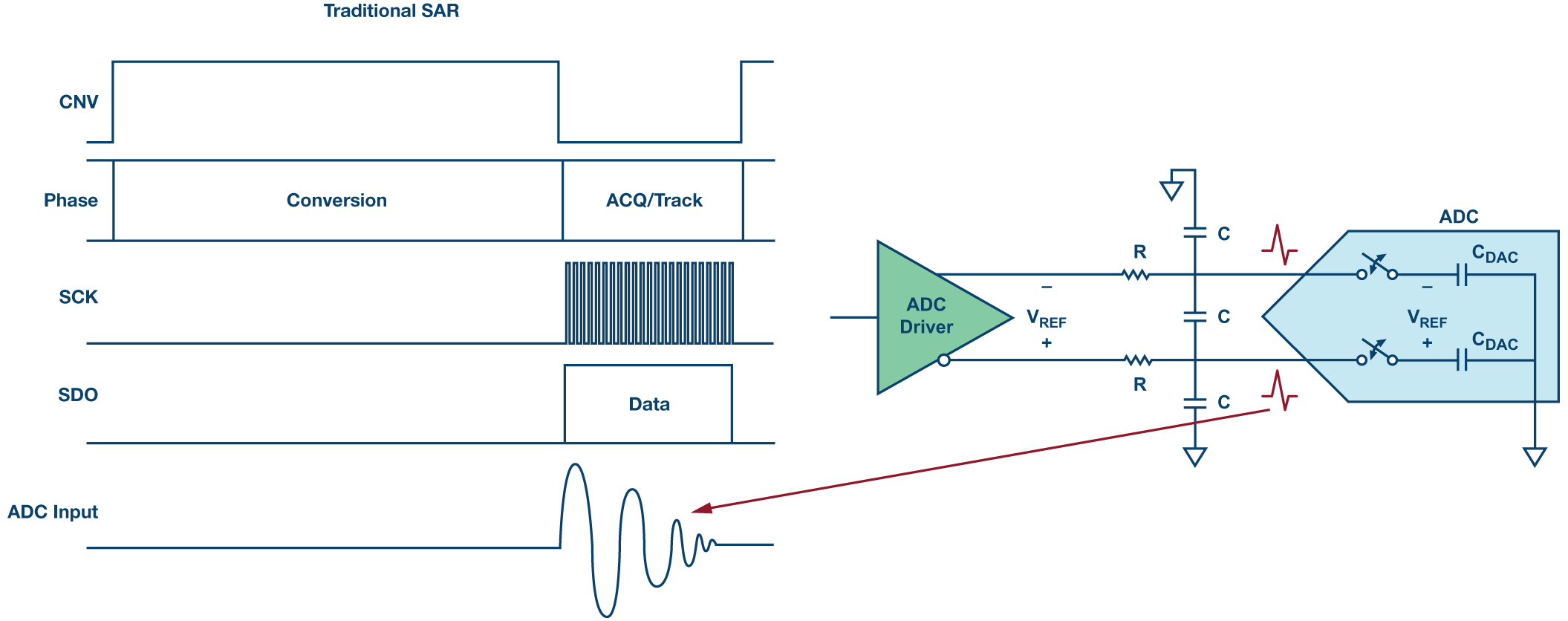

図 1 は、高精度のデータ・アクイジション・システムを構築する際に使用される一般的なシグナル・チェーンです。分解能/精度の高い SAR ADC では、入力部にスイッチド・キャパシタが使用されます。そのため、この種の SAR ADC を駆動する方法は、システム設計における主要な課題の 1 つになっていました。

システム設計者は、ADC 用ドライバのデータシートを注意深く読み込まなければなりません。ノイズや歪み、入出力電圧のヘッドルーム/フットルーム、帯域幅、セトリング時間などの仕様を確認する必要があるからです。一般に、高速 ADC 用のドライバには、帯域幅が広く、ノイズが少なく、出力能力が高いことが求められます。SARADC の入力部にあるスイッチド・キャパシタのキックバックを、アクイジション時間内にセトリングしなければならないからです。このことから、アンプの選択肢は非常に少なくなり、性能、消費電力、実装面積の面でトレードオフを強いられることになります。また、ドライバと ADC の入力の間に配置する RC フィルタも適切に選択しなければならず、それに伴ってアンプの性能や選択肢についてはさらに制約が増します。RC フィルタには、広い帯域にわたるノイズを抑え、電荷のキックバックの影響を低減することが求められます。システム設計者は、選択した ADC 用ドライバと RC フィルタによって、望ましい性能が得られることを確認しなければなりません。そのためには、かなりの時間を費やしてシグナル・チェーンを評価する必要があります。

図 2 の動作タイミング図に示すように、SAR ADC のスループット(サイクル・タイムの逆数)は、変換フェーズとアクイジション・フェーズから成ります。ADC からのデータは、アクイジション・フェーズに SPI(SerialPeripheral Interface)を介して出力されます。一般に、従来型 SAR ADC のアーキテクチャでは、変換フェーズは長く、アクイジション・フェーズは短くなります。変換フェーズの間、ADC が内蔵する容量性の D/A コンバータ(DAC)は、A/D 変換を実行する際には ADC の入力部から切り離されます。そして、アクイジション・フェーズになると再接続されます。ADC 用のドライバは、次の変換フェーズが開始するまでに、入力部に現れる非線形性のキックバックを適切な電圧にセトリングしなければなりません。ここで、カットオフ周波数が低い RC フィルタによって積極的にフィルタリングを行うと、ADC用のドライバによって、従来型の SAR ADC のキックバックをアクイジション時間内にセトリングすることができなくなります。その結果、ADC の歪み性能や直線性が低下することになります。

より長いアクイジション・フェーズ

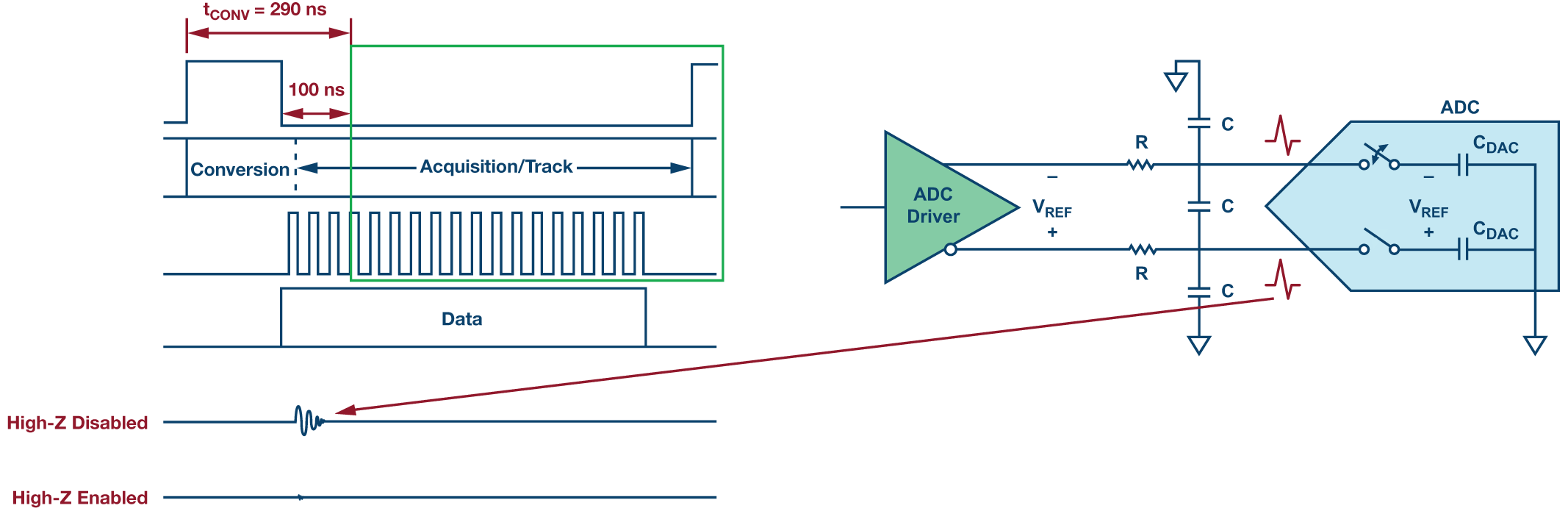

AD4000 ファミリーは、変換時間がわずか 290 ns という高速な製品です。同ファミリーの製品では、進行中の変換プロセスが終了する 100 ns 前には、アクイジション・フェーズに戻ります。そのため、図 3 に示すように、アクイジション・フェーズをより長くとることができます。SAR ADC の入力で観測されるキックバックは、直線性を損なう原因になります。それが、AD4000 ファミリーでは、ハイ Z モードが無効(ディスエーブル)の場合でも良好なレベルに抑えられます。そして、同モードを有効(イネーブル)にした場合には、ほぼ無視できるレベルになります。それにより、ADC 用のドライバに対するセトリング時間の要件が緩和されます。その結果、RC フィルタのカットオフ周波数を下げられるようになり、抵抗値を高く設定することが可能になります。これは、よりノイズの大きいアンプや、より出力能力が低く、帯域幅の狭いアンプを使用できるということを意味します。つまり、ADC 用のドライバ・アンプや RC フィルタを、入力部のスイッチド・キャパシタのセトリングに関する要件ではなく、対象とする信号の帯域幅に基づいて選択できるようになるということです。RC フィルタの抵抗値を高く設定し、それに応じて容量値を小さくすれば、歪み性能にそれほど影響を及ぼすことなく、アンプの安定性の問題を軽減することができます。また、抵抗値を高めることは、ADC の入力部を過電圧から保護することにつながり、アンプの動的な消費電力が削減されます。さらに、アクイジション・フェーズが長ければ、SPI のクロック・レートを引き下げて入出力で消費される電力を抑えることができます。それにより、プロセッサや FPGA の選択肢が増えます。加えて、ADC のスループットを損なうことなく、デジタル信号の絶縁に関する要件を簡素化できるというメリットも得られます。

ハイ Z モード

ここまでにも何度か触れたように、AD4000 ファミリーは、ハイ Z モードを備えています。これは、アクイジションの開始時に、容量性 DAC を入力に再接続することで生じる電荷のキックバックを低減するためのものです。このモードを有効にすると、変換の終了時に、直前にサンプリングした電圧を保持するために容量性 DACがチャージされます。次のサンプリングを行う際、ADCの入力部で取得される電圧に対しては、変換プロセスによって生じる電荷の影響が及びます。その非線形性の影響が、容量性 DAC に対するチャージの処理によって抑えられるということです。ハイ Z モードを利用すれば、高速 ADC 専用のドライバは不要になります。また、DCや低周波信号(10 kHz 未満)に対して、JFET 入力のアンプや計装アンプなど、消費電力が少なく帯域幅の狭い高精度のアンプを選択できるようになるというメリットが得られます。

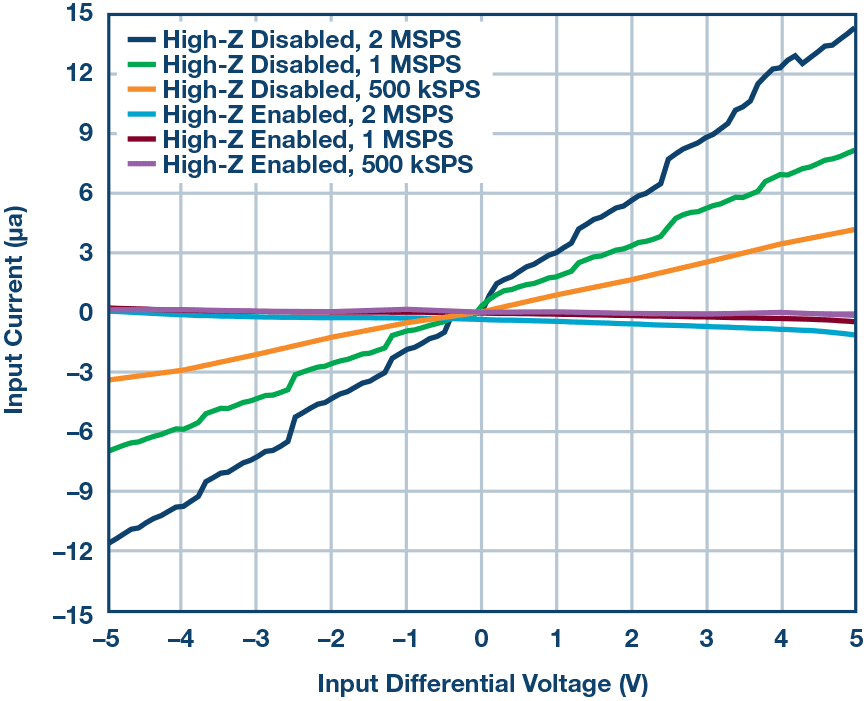

図 4 は、ハイ Z モードを有効/ 無効にした場合の「AD4003」、「AD4007」、「AD4011」の入力電流を示したものです。入力電流が少ないことから、ハイ Z モードを無効にした場合でも、市場で提供されている従来型の SAR ADC よりも、はるかに容易に駆動できます。1 世代前の製品である「AD7982」と比較すると、AD4007 では、ハイ Z モードを無効にした場合でも、1 MSPS における入力電流が 1/4 に抑えられています。なお、ハイ Z モードを有効にすると、入力電流は 1 µ A 未満になります。

AD4000 ファミリーは入力電流が少なく、従来型の SARADC よりもはるかに高いソース・インピーダンスで駆動できます。そのため、従来型の SAR ADC を使用する場合よりも、RC フィルタの抵抗値を 10 倍大きく設定することが可能です。

高精度のアンプによる直接駆動

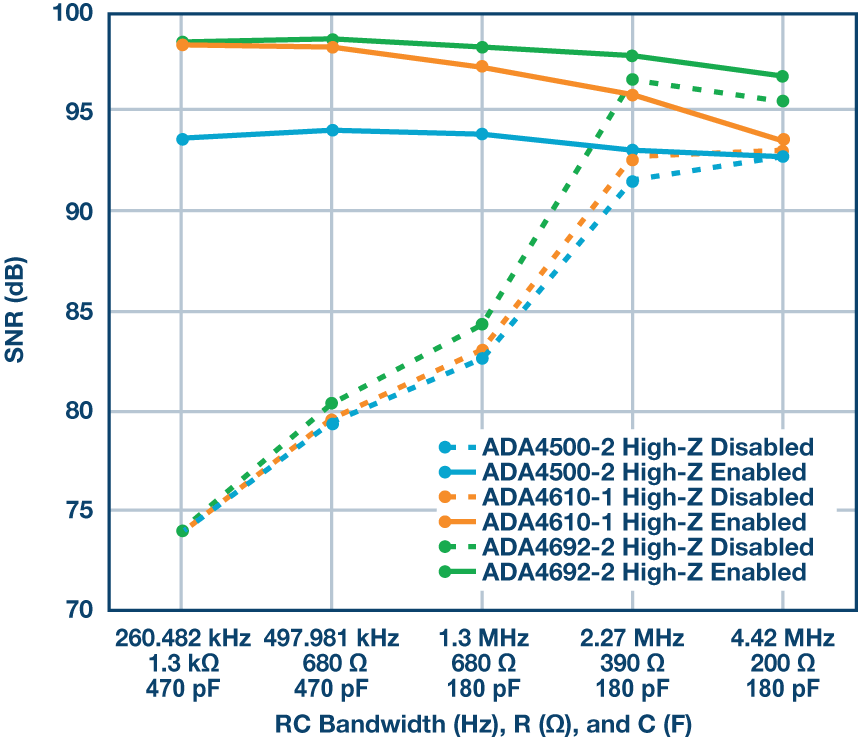

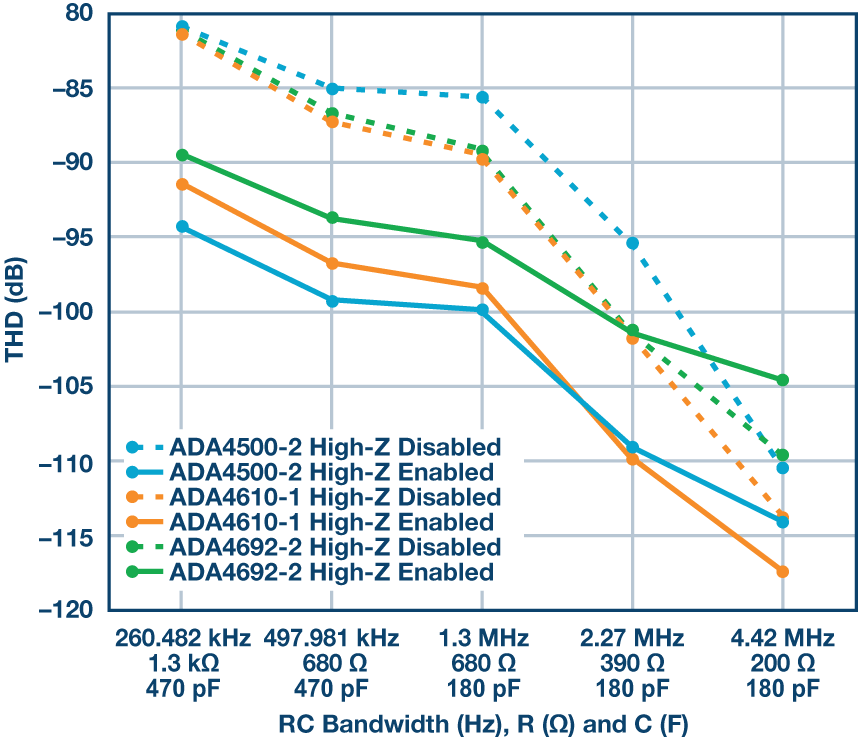

ほとんどのシステムでは、シグナル・チェーンの AC/DC性能は、ADC ではなく、フロントエンドによって制限されます。実際、アンプのノイズと歪みの性能が、特定の入力周波数における S/N 比と THD を決める要素になります。このことは、図 5 と図 6 に示した高精度アンプのデータ(各製品のデータシートからの抜粋)を見れば明らかです。しかし、ハイ Z モードを備える AD4000 ファミリーを採用すれば、シグナル・コンディショニング段で使用する高精度のアンプを含めて、ドライバ・アンプの選択の幅は大きく広がります。また、選んだアンプで最適な性能を達成しつつ、RC フィルタについても柔軟な選択が行えるようになります。

図 5 と図 6 は、AD4003、「AD4020」の S/N 比と THDを表しています。入力の駆動には、3 種類の高精度アンプを使用しています。1 つは、アンプ当たりの静止電流を 1 8 0 µ A に抑えた低消費電力の製品「ADA4692-2」です。もう 1 つは、アンプ当たりの静止電流が 1.5 mAで入力バイアス電流も少なく抑えた JFET 入力アンプ「ADA4610-1」です。最後の1つは、アンプ当たりの静止電流が 1.55 mAでクロスオーバー歪みが生じない「ADA4500-2」です。最大のスループット、5 V のリファレンス、1 kHz の入力トーンを使用し、ハイ Z モードを有効/無効にした場合の AD4004/AD4020 の性能をRC フィルタの値を変えて測定しました。ADA4692-2 とADA4610-1 を使用すると、ハイ Z モードが有効で、RCフィルタの帯域幅が 260 kHz または 498 kHz と低い場合に 98 dB(代表値)以上の S/N 比が得られます。これらの使い方は、対象とする信号の帯域が低い場合に、シグナル・チェーン上流の部品からの広帯域にわたるノイズを除去するうえで役に立ちます。AD4000 ファミリーであれば、アプリケーションの要件に応じて適切な高精度のアンプを選択することが可能です。例えば、レール toレール・アンプである ADA4692-2 は、消費電力が重視される携帯型のアプリケーションに適しています。AD4000ファミリーの製品を直接駆動しつつ、最適な性能を達成することができます。

ハイ Z モードを有効にすると、AD4003/AD4020 の S/N比は、RC フィルタの帯域幅が 1.3 MHz 未満で抵抗値が390 Ωよりも大きい場合でも 10 dB 以上改善されます。また、THD は RC フィルタのカットオフ周波数が 4.42MHz の場合で -104 dB 以下になります。AD4000 ファミリーの製品は、最大のスループットで使用する場合、オーバーサンプリングを活用できます。それにより、RCフィルタのカットオフ周波数が低い場合の S/N 比を高めることができます。

ハイ Z モードを有効にした場合、AD4003/AD4020 の消費電力は 2 ~ 2.5 mW/MSPS 増加します。それでも、「ADA4807-1」のような ADC 専用のドライバを使用する場合よりもはるかに少なく抑えられることになります。また、プリント回路基板の面積と部品点数も削減されます。消費電力が ADA4807 の 1/5.5 の ADA4692-2を、ADC 用ドライバとして使用することも可能です。その場合でも、ハイ Z モードが無効で、RC フィルタの帯域幅が 2.27 MHz または 4.47 MHz という条件下でも、約 96 dB(代表値)の 信号/ノイズ + 歪み(SINAD)が得られます。ハイ Z モードを有効にした場合、ADC 用ドライバを使用する方が ADC の S/N 比と THD は良好です。ハイ Z モードを無効にした場合には、ADC の S/N比、THD と RC フィルタのカットオフ周波数の間にトレードオフが生じます。

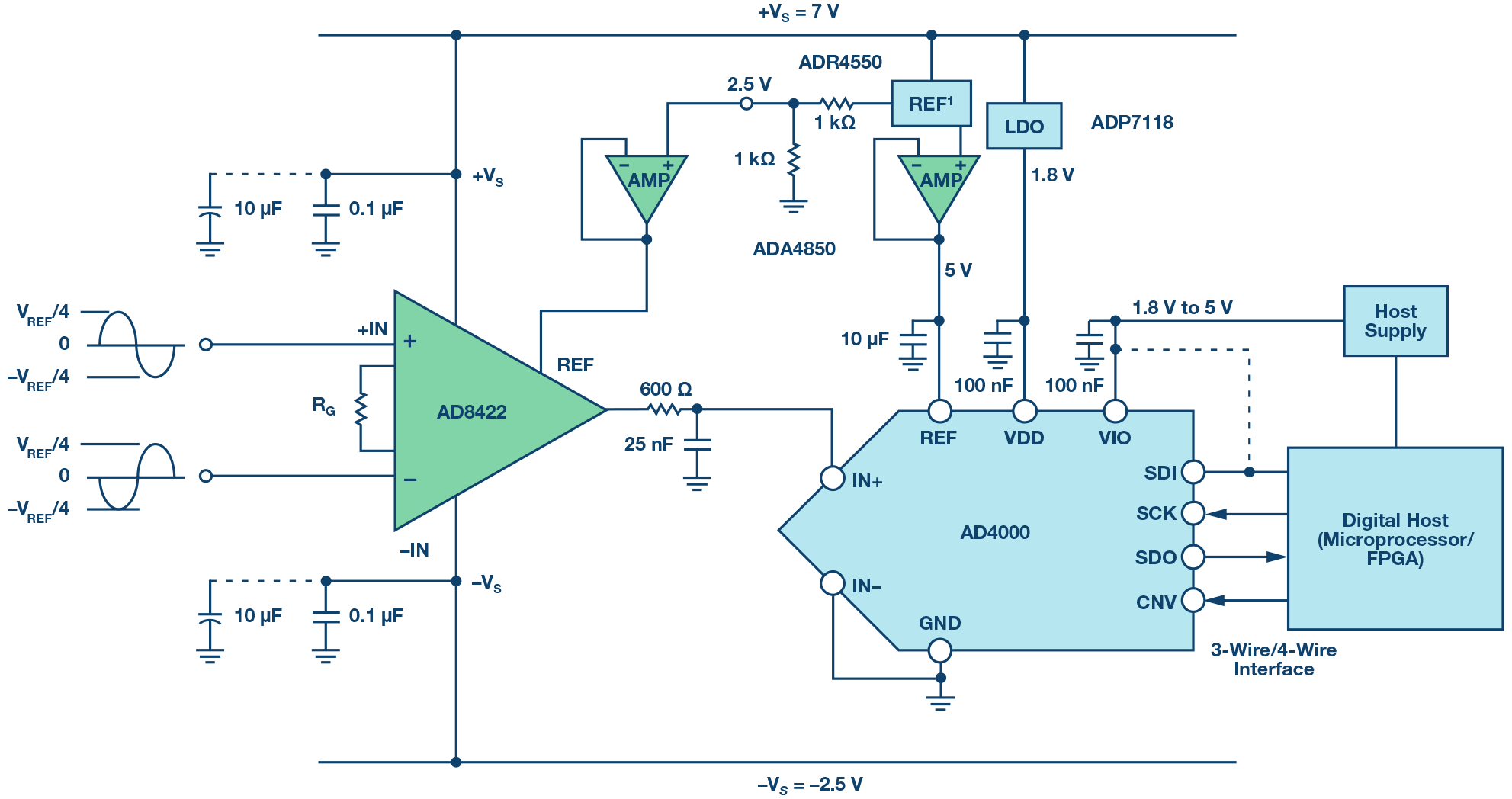

計装アンプによる直接駆動

計装アンプは、優れた精度と同相ノイズ除去性能、高い入力インピーダンスを備えています。センサーに直接接続できますが、一般に信号帯域幅は狭くなります(10 MHz未満)。通常、SAR ADC と計装アンプを組み合わせて、(例えば ATE や医療機器用に)高精度のシグナル・チェーンを設計する場合、ADC の入力部の前段に、信号のレベル変換やキックバックのセトリングを行うためのシグナル・コンディショニング段やドライバ段を適用します。

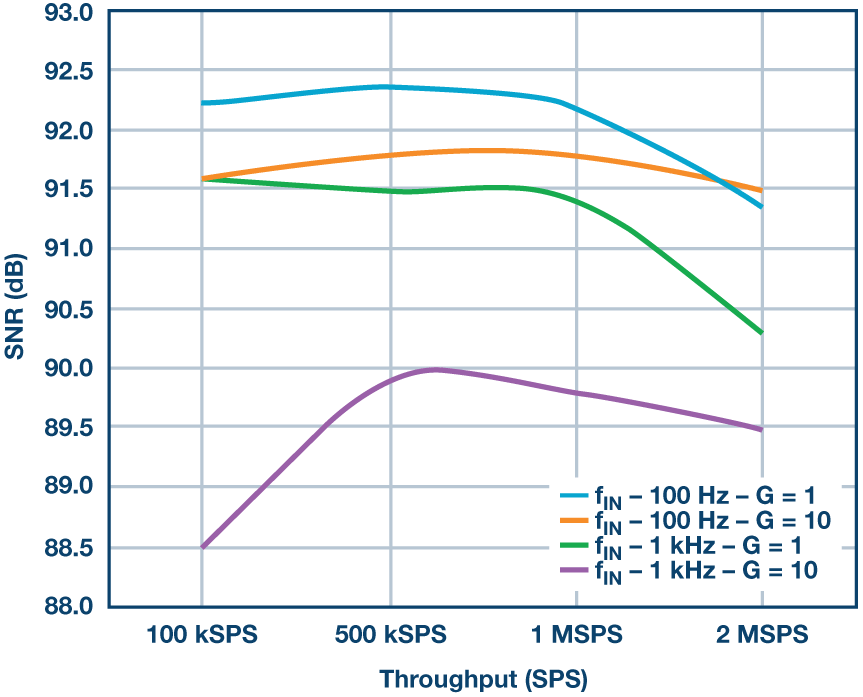

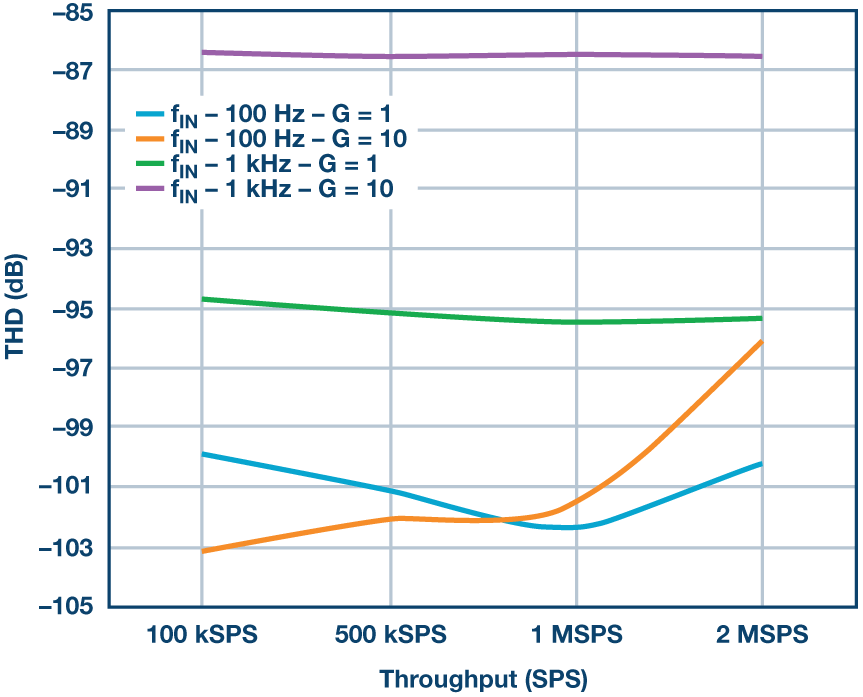

図 7 は、ハイ Z モードを有効にして AD4000 を計装アンプ「AD8422」で直接駆動する場合の簡略化したブロック図です。ドライバ段が不要になるため、基板面積を削減できます。対象とする帯域に基づき、10 kHz を超える広帯域ノイズの除去に最適な RC フィルタを構成するために、600 Ωの抵抗と 25 nF のコンデンサを選択しています。最適な性能を達成するために、AD8422 の REFピンは「ADA4850」でバッファされた VREF/2 でバイアスされています。このシグナル・チェーンにより、RGで設定されるゲインが 1(RG なし)の場合と 10(RG が2.2 kΩ)の場合に、100 Hz と1 kHz の入力信号に対する最適な S/N 比と THD が得られます。図 8 と図 9 は、ハイ Z モードが有効でゲインが 1、10 である場合に、2MSPS までのすべてのスループットにおいて、100 Hz の入力信号に対し、91 dB を超える S/N 比と -96 dB 以下のTHD が得られることを示しています。これらの図からわかるように、ADC のスループットを下げると、入力キックバックをセトリングするためのアクイジション時間を長くとることができ、S/N 比と THD はやや向上します。

まとめ

AD4000 ファミリーは、低消費電力、ピン互換で、分解能が 16/18/20 ビットの高精度 SAR ADC です。表 1 に、同ファミリーの製品を変換速度と分解能/入力形式で分類して示しました。使いやすさと高い精度を併せ持つこれらの ADC を使用することで、システム・レベルの技術的な課題を解決することができます。

| 変換速度 | 16 ビット、シングルエンド | 16 ビット、差動 | 18 ビット、シングルエンド | 18 ビット、差動 | 20 ビット、差動 |

| 2MSPS | AD4000 | AD4001 | AD4002 | AD4003 | AD4020 |

| 1MSPS | AD4004 | AD4005 | AD4006 | AD4007 | |

| 500kSPS | AD4008 | AD4010 | AD4011 |

AD4000 ファミリーは、ハイ Z モード、少ない入力電流、長いアクイジション・フェーズという特有の組み合わせによって駆動に関する要件を緩和します。また、同ファミリーの製品を使えば、高速 ADC 専用のドライバ段が不要になるので、基板面積、消費電力、部品コストを削減することができます。その結果、ADC 用ドライバの選択の幅が広がります。また、対象とする帯域幅に基づいて RC フィルタの設計を最適化できるようになり、広帯域にわたるノイズの低減、アンプの安定性の向上、ADCの入力保護、動的消費電力の削減といった問題が緩和されます。本稿では、この ADC ファミリーの製品を高精度アンプや計装アンプによって直接駆動する方法を紹介しました。この ADC ファミリーを採用することによって、精度を大きく損なうことなく、一般的なシステム・レベルの問題を解決することができます。