概要:

フェーズ・ロック・ループ(PLL)は、実に様々な高周波アプリケーションで使用されています。例えば、クロックのシンプルなクリーンアップ用回路、高性能の無線通信リンク用の局部発振器(LO)、ベクトル・ネットワーク・アナライザに搭載されるスイッチング周波数が極めて高いシンセサイザなどが、そうしたアプリケーションの例です。本稿では、それらのアプリケーションを念頭に置きながら、PLLの主要な構成要素について説明します。それにより、PLLを初めて扱う人にとっても、既に長く扱ってきた人にとっても、部品の選定や、各種アプリケーションにおけるトレードオフについて検討する上で役立つ指針を提供します。本稿では、アナログ・デバイセズのPLLと電圧制御発振器(VCO)の製品ファミリである「ADF4xxx」および「HMCxxx」を実例として取り上げます。その上で、アナログ・デバイセズのPLL回路シミュレータ「ADIsimPLL」を活用し、各製品の特性も示していきます。

基本構成:クロックのクリーンアップ用回路

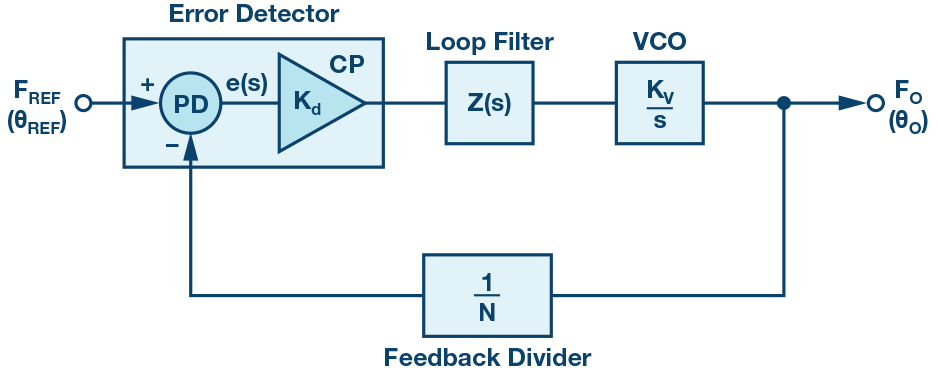

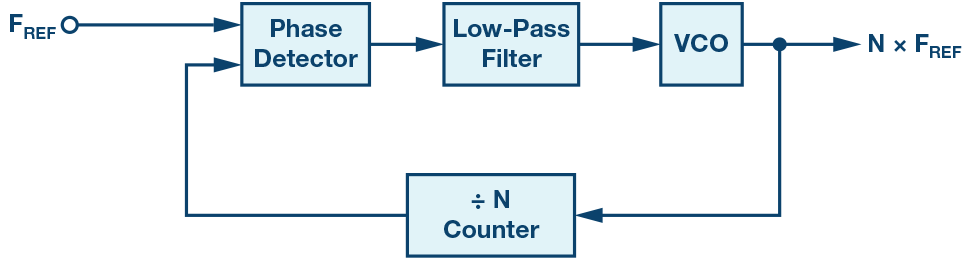

図1 に、最も基本的なPLLのブロック図を示しました。PLLでは、リファレンス信号FREFの位相と調整可能なフィードバック信号RFIN(出力FOの分周信号)の位相を比較します。図2には、周波数領域で動作する負のフィードバック制御ループを示しました。比較結果が安定した状態にあり、出力の周波数と位相がエラー検出器の入力の周波数と位相に一致しているとき、PLLはロックしていると表現します。本稿では、ADF4xxxに実装されているような従来型のデジタルPLLのアーキテクチャのみを対象とします。

この回路の1 つ目の基本要素は、位相周波数検出器(PFD) です。PFDは、REFINに入力される信号の周波数と位相を、RFINに入力されるフィードバック信号の周波数と位相と比較します。「ADF4002」は、スタンドアロンのPFD(帰還分周比はN = 1)として構成可能なPLLです。高精度の電圧制御水晶発振器(VCXO)と狭帯域のローパス・フィルタと共に使用することで、ノイズの大きいREFIN( クロック信号) をクリーンアップすることができます。

位相周波数検出器

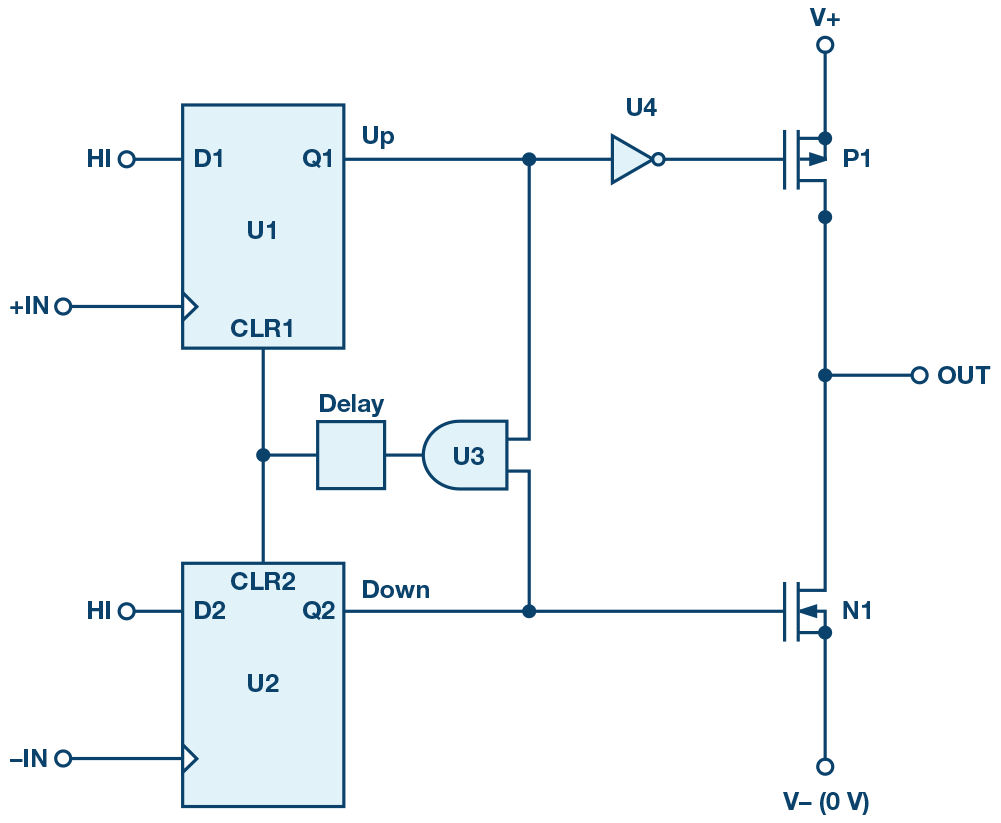

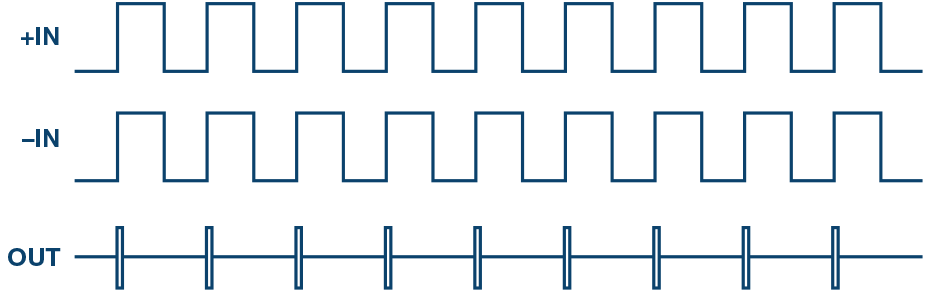

図3の位相周波数検出器は、+INに入力されるFREF信号と-INに入力されるフィードバック信号を比較します。2個のD型フリップフロップが、遅延素子と共に使用されています。一方のQ出力を使用して正の電流源を実現し、もう一方のQ出力を使用して負の電流源を実現しています。これらの電流源は、チャージ・ポンプとして知られるものです。PFDの詳しい動作については、Phase-LockedLoops for High Frequency Receivers and Transmitters -Part 1(高周波レシーバー/トランスミッタ用のPLL - パート1)をご覧ください。

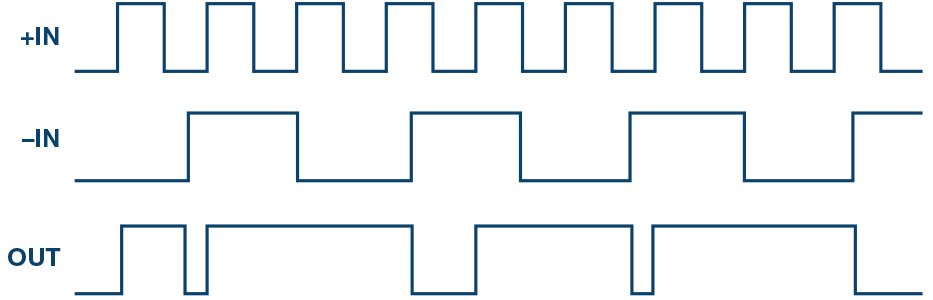

この回路により、+INの入力周波数が-INよりも高いと( 図4) 、チャージ・ポンプはハイ側の電流を出力します。それがPLLのローパス・フィルタに供給され、VCOへの入力電圧が引き上げられます。それに伴い、-INへの入力周波数が増加します。-INの周波数が+INよりも高ければ、逆の動作が生じます。このような仕組みにより、PFDの2つの入力周波数はやがて同じ値に収束(ロック)します(図5)。

先ほど、ノイズの多いクロックをクリーンアップするという用途を挙げました。それについては、ADIsimPLLにより、クロックの位相ノイズのプロファイル、自走状態のVCXO、クローズドループのPLLをモデル化できます。

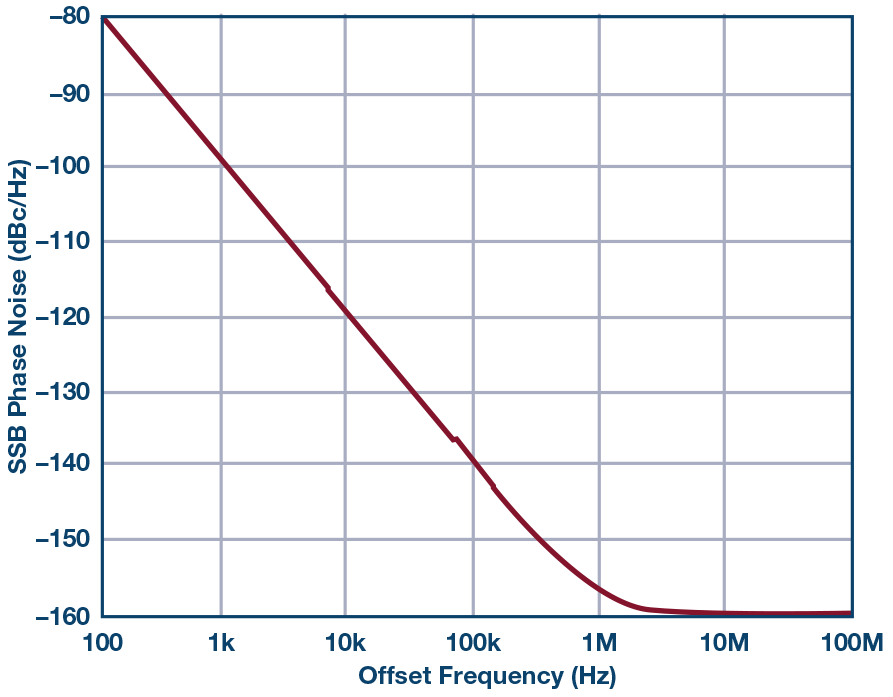

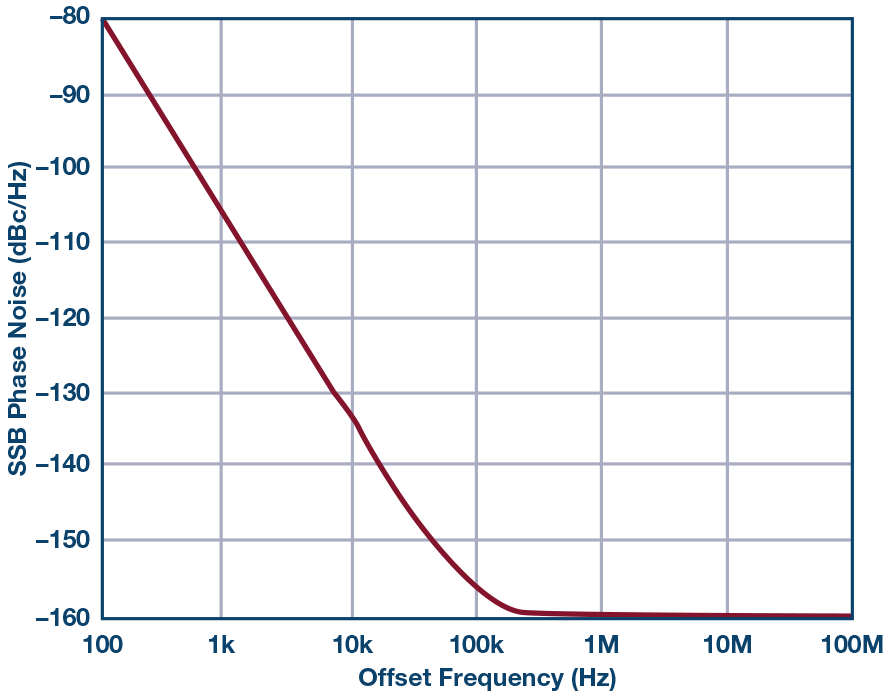

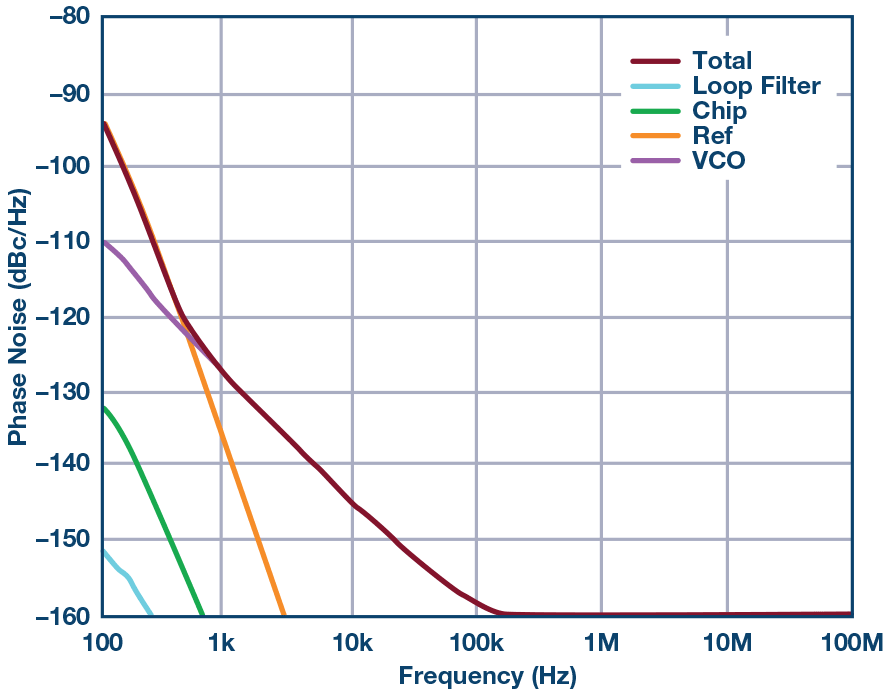

図6~図8は、ADIsimPLLで得たグラフです。図6には、ノイズの大きいREFINの位相ノイズのプロファイルを示しました。それが、ローパス・フィルタによってフィルタリングされます。PLLのリファレンスとPFD回路に起因するすべての帯域内ノイズは、ローパス・フィルタによって除去されます。その結果、ループ帯域の外側に、それよりもはるかに小さいVCXOのノイズ(図7)だけが残ります。最終的には、図8のような結果が得られます。最もシンプルな構成のPLLでは、出力周波数が入力周波数と等しくなります。このようなPLLは、クロックのクリーンアップ用PLLと呼ばれます。この用途では、狭帯域(1kHz未満)のローパス・フィルタが推奨されます。

高周波向けのインテジャーN型アーキテクチャ

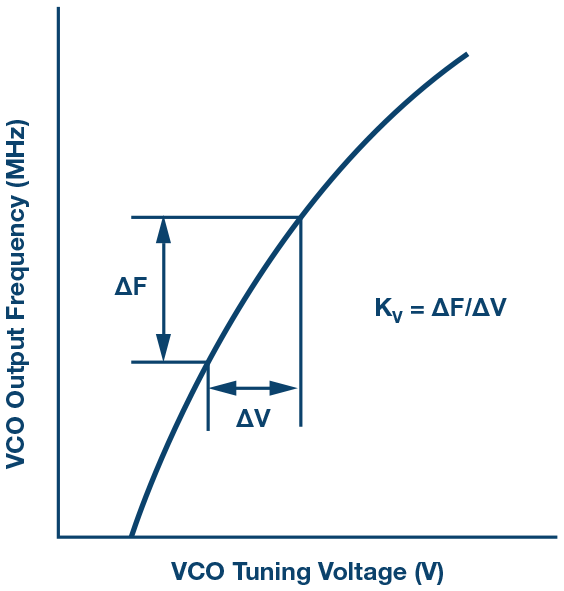

周波数の高い信号を生成するにはVCOを使用します。VCOは、VCXOよりも広い範囲でチューニングが可能であり、周波数ホッピングや周波数ホッピング・スペクトラム拡散(FHSS:Frequency Hopping Spread Spectrum)といった用途に一般的に使用されています。この種のPLLでは、出力がリファレンス周波数の倍数(比較的大きな値)になります。通常、VCOは調整が可能な可変の要素を備えています。例えば、バラクタ・ダイオードは、入力電圧に応じて容量が変化します。これを利用すれば、調整が可能な共振回路を構成し、所望の周波数を生成することができます(図9)。PLLは、このVCOを制御するためのシステムだと見なせます。

帰還分周器は、VCOの周波数をPFDの周波数で除算する役割を果たします。それにより、PLLはPFDの周波数の倍数となる周波数の信号を出力できるようになります。分周器は、リファレンスのパスに配置されるケースもあります。その場合、PFDの周波数よりも高い周波数リファレンスを使用できます。この種の製品としては、アナログ・デバイセズの「ADF4108」が挙げられます。本稿で2つ目の基本要素として取り上げるのは、PLLのカウンタです。

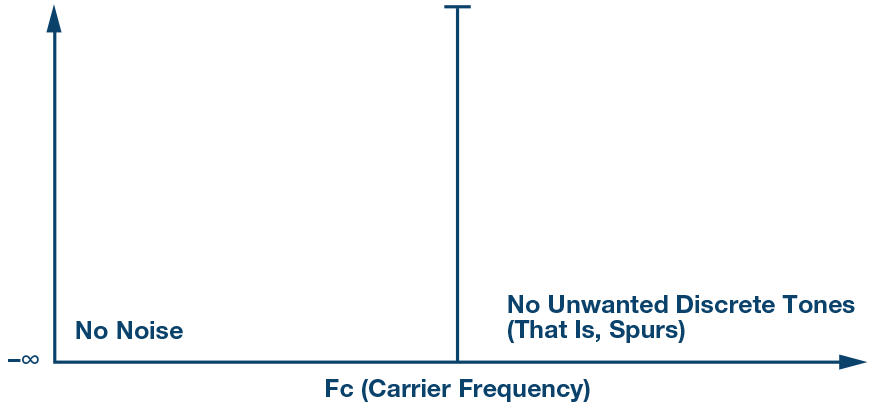

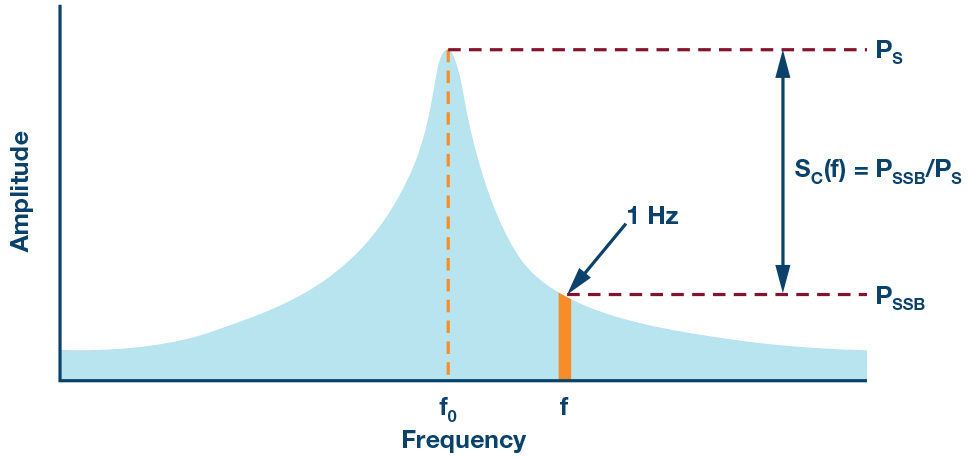

PLLの主要な性能パラメータは、周波数の合成に伴って生成される望ましくない成分である位相ノイズや周波数スプリアスです。インテジャーN型のPLLの場合、周波数スプリアスはPFDの周波数を基に生成されます。VCOのチューニング・ポートは、チャージ・ポンプからのリーク電流によって変調されます。その影響はローパス・フィルタによって緩和されます。ローパス・フィルタが狭帯域であるほど、周波数スプリアスの除去性能は高くなります。理想的なトーンはノイズや周波数スプリアスを含みません(図10)。しかし、実際には図11に示すように、搬送波を中心としてスカート状に位相ノイズが生じます。単側波帯の位相ノイズは、搬送波からの周波数オフセットとして規定される1Hzの帯域幅における、搬送波を基準としたノイズのパワーであると定義することができます。

インテジャーN型とフラクショナルN型の分周器

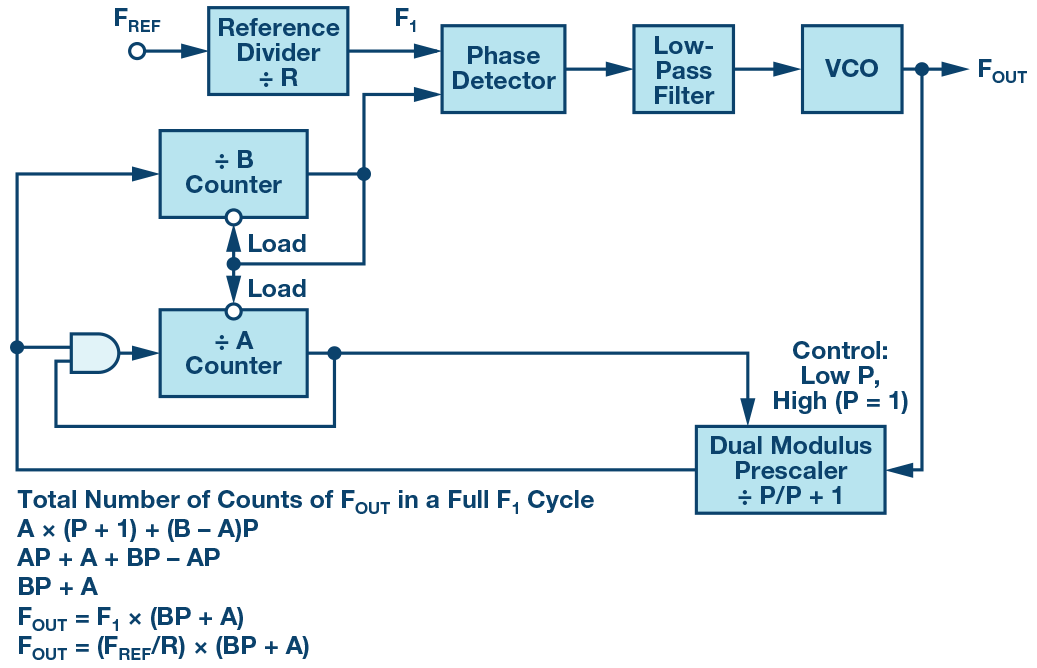

狭帯域のアプリケーションの場合、チャンネル間隔は狭く(一般に5MHz未満)、帰還カウンタNの値は大きくなります。小さな回路でNとして大きな値を取れるようにするには、図12に示すようにP/P + 1のデュアル係数を備えるプリスケーラを使用します。それにより、N = PB + AによってNの値を計算できるようにします。例えば、係数が8/9のプリスケーラにおいてNが90であるなら、Bは11、Aは2です。このデュアル係数プリスケーラは、表1に示すように、A(つまり2サイクル)の間、9で除算を行い、残りのサイクル(B - Aの9サイクル)の間、8で除算を行います。一般に、プリスケーラはバイポーラをベースとするエミッタ結合論理(ECL)回路など、高周波回路技術を使用して設計されます。ただ、図のAとBのカウンタは、プリスケーラからの低い周波数の出力を受け取ることができ、低速のCMOS回路でも製造できます。そうすれば、回路の実装面積と消費電力を抑えることが可能になります。ADF4002のような低い周波数に対応するクリーンアップ用PLLには、この種のプリスケーラは含まれていません。

| Nの値 | P/P + 1 | Bの値 | Aの値 |

| 90 | 9 | 11 | 2 |

| 81 | 9 | 10 | 1 |

| 72 | 8 | 9 | 0 |

| 64 | 8 | 8 | 0 |

| 56 | 8 | 7 | 0 |

| 48 | 8 | 6 | 0 |

| 40 | 8 | 5 | 0 |

| 32 | 8 | 4 | 0 |

| 24 | 8 | 3 | 0 |

| 16 | 8 | 2 | 0 |

| 8 | 8 | 1 | 0 |

| 0 | 8 | 0 | 0 |

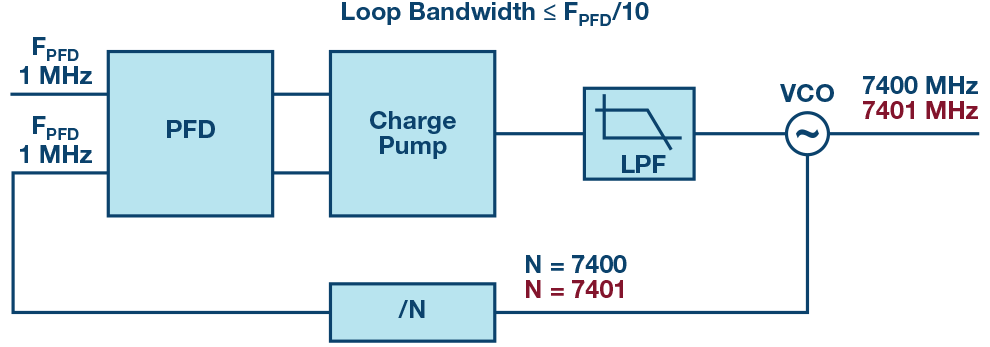

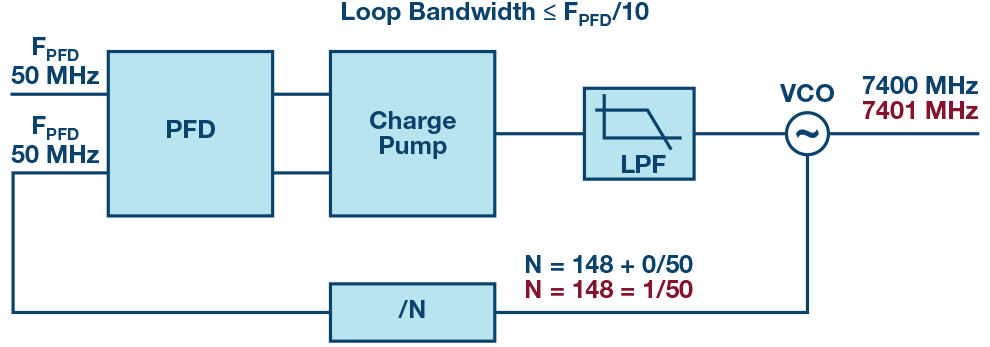

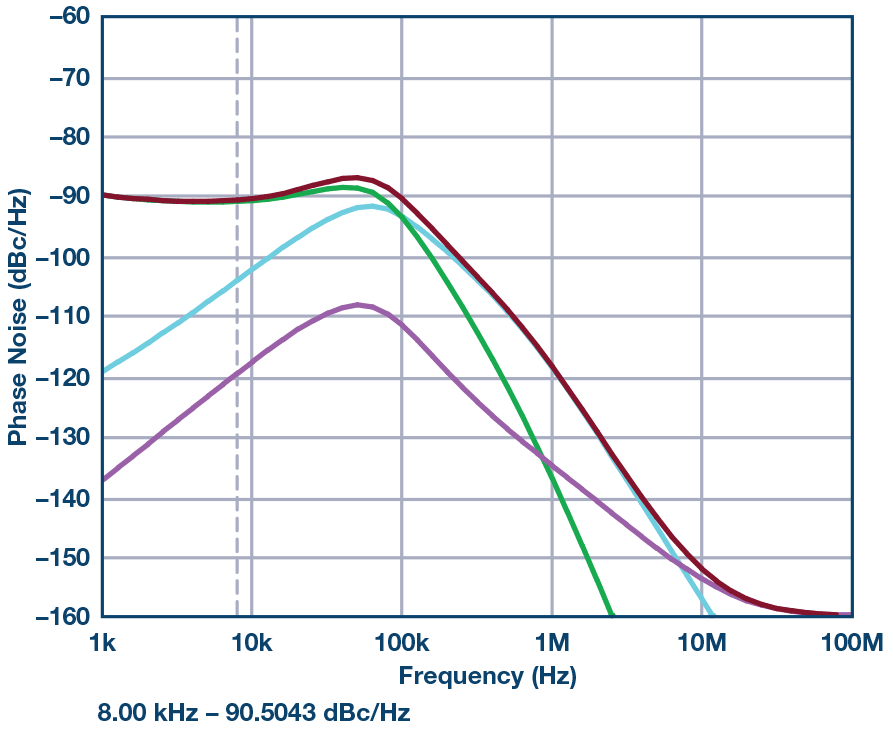

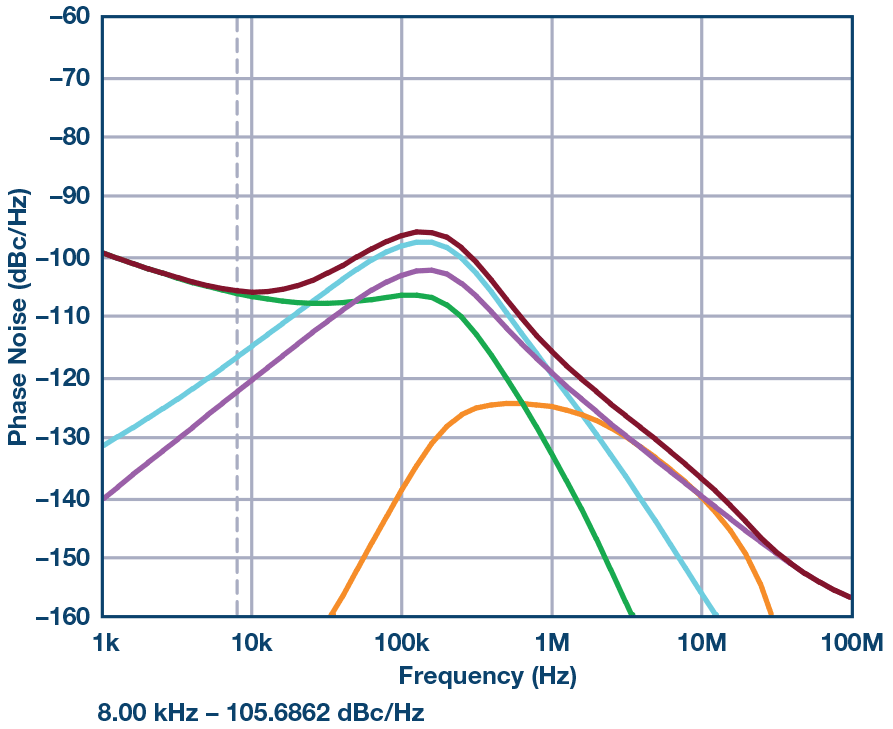

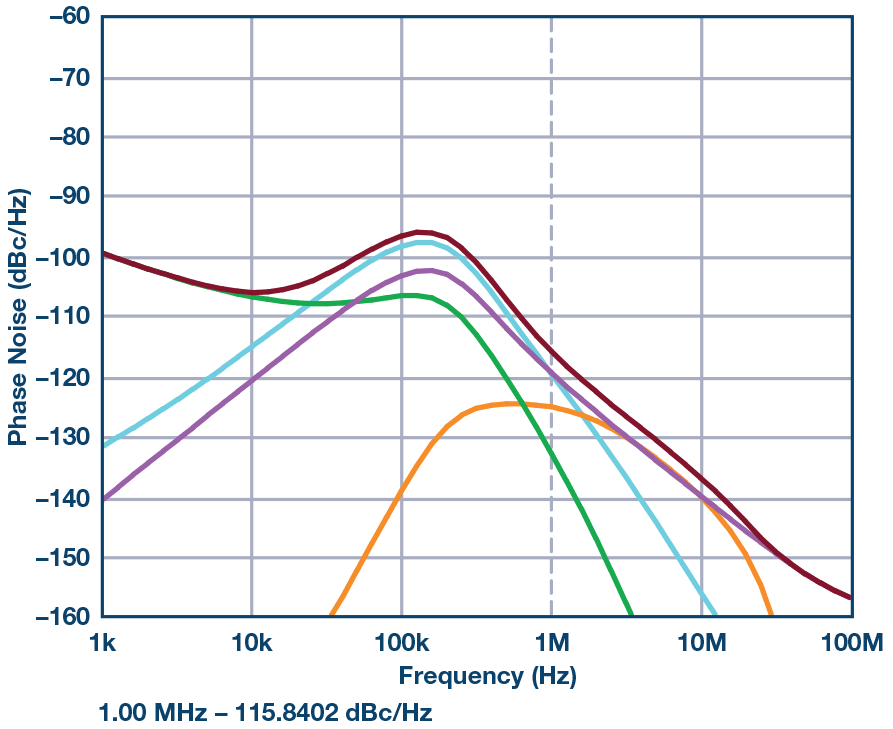

帯域内(PLLのループ・フィルタの帯域幅内)の位相ノイズは、Nの値から直接影響を受けます。帯域内ノイズは20log(N)に比例して増加します。したがって、Nの値が高い狭帯域のアプリケーションの場合、帯域内ノイズはほぼNの値によって決まります。「ADF4159」や「HMC704」などのフラクショナルN型のシンセサイザであれば、高い分解能を維持しつつ、システムのNの値をかなり低く設定することができます。それによって、帯域内の位相ノイズを大幅に抑えることが可能になります。図13~16に、ADF4108とHMC704による実現方法/性能の例を示しました。それぞれのPLLを使用し、5Gシステム( 第5世代移動通信システム) のLOに適した7.4GHz~7.6GHzの周波数を1MHzのチャンネル分解能で生成しています。ADF4108はインテジャーNの構成(図13)で使用され、HMC704はフラクショナルNの構成で使用されます。HMC704を使用する図14の例では、PFDの周波数を50MHzにしています。そのため、Nの値、ひいては帯域内ノイズを低下させつつ、1MHz(またはそれ以下)の周波数ステップ・サイズを実現することができます。図15と図16を比較すると、(8kHzのオフセット周波数で)15dBの改善が見られます。一方、ADF4108では、それと同等の分解能を達成するには、PFDの周波数を1MHzにする必要があります。

スプリアスによってシステムの性能が決して低下しないようにするには、フラクショナルN型のPLLを慎重に扱う必要があります。HMC704などのPLLにおける最大の問題は、整数境界のスプリアスです。これはNの値の小数部分が0または1に近い場合に生成されます。例えば、147.98や148.02は、148という整数値に非常に近いと言えます。VCOの出力とRF入力の間にバッファを設けるか、慎重な周波数プランニングによって問題となる周波数(整数値に近い周波数)を避けるようにREFINを変更することによって、この問題を緩和することができます。

ほとんどのPLLでは、帯域内ノイズはNの値とPFDの周波数に大きく依存します。帯域内の位相ノイズの測定値において、平坦な部分から20log(N)と10log(FPFD)を差し引くと、性能指数(FOM)が得られます。PLLを選択するための一般的な方法は、FOMを比較することです。帯域内ノイズに影響を及ぼすもう1つの要因に、1/fノイズがあります。1/fノイズは、デバイスの出力周波数に依存します。FOM、1/fノイズ、リファレンス・ノイズが、PLLシステムの帯域内ノイズの大部分を占めます。

5G通信用の狭帯域LO

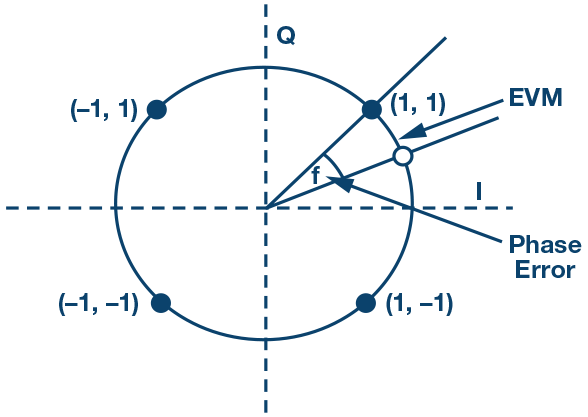

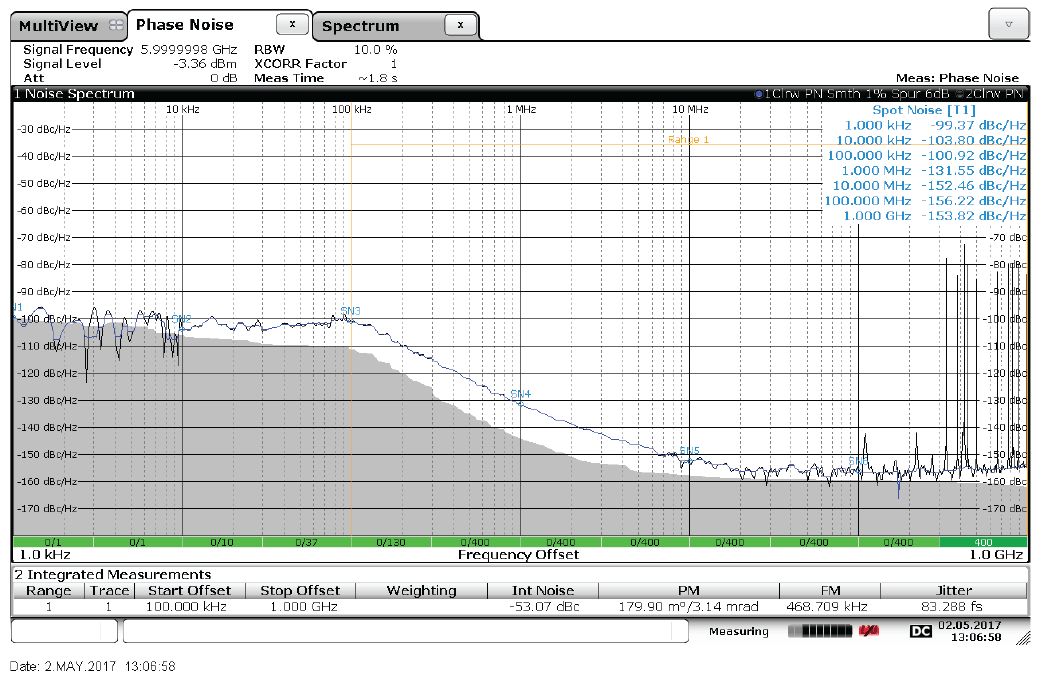

通信システムにおいて、PLLの観点からの主要な仕様は、エラー・ベクトル振幅(EVM) とVCOのブロッキング仕様です。EVMの範囲は、各オフセット位置におけるノイズの寄与分を表す積分位相ノイズと同様です。先述した5Gシステムの場合、積分範囲はかなり広く、1kHzから100MHzにまで及びます。EVMは、完全な変調信号に対応する理想のポイントからの劣化の度合いを百分率で表したものだと考えることができます(図17)。同様に、積分位相ノイズは、搬送波からの各オフセット位置におけるノイズ・パワーを積分したものです。それを基に、EVM、積分位相ノイズ、rms位相誤差とジッタを計算することができます。最新式のシグナル・ソース・アナライザでは、ボタンを押すだけでそうした数値が表示されます(図18)。変調密度が高い方式を使うほど、EVMの重要性は増します。ETSI(欧州電気通信標準化機構)の仕様である3GPP TS 36.104によると、16QAMの必要最小EVMは12.5%で、64QAMでは8%です。しかしEVMは、パワー・アンプの歪みや、ミキサーからの望ましくない生成物に起因する、非理想的な様々なパラメータで構成されます。そのため、通常、積分ノイズ(単位はdBc)はそれとは独立して定義されます。

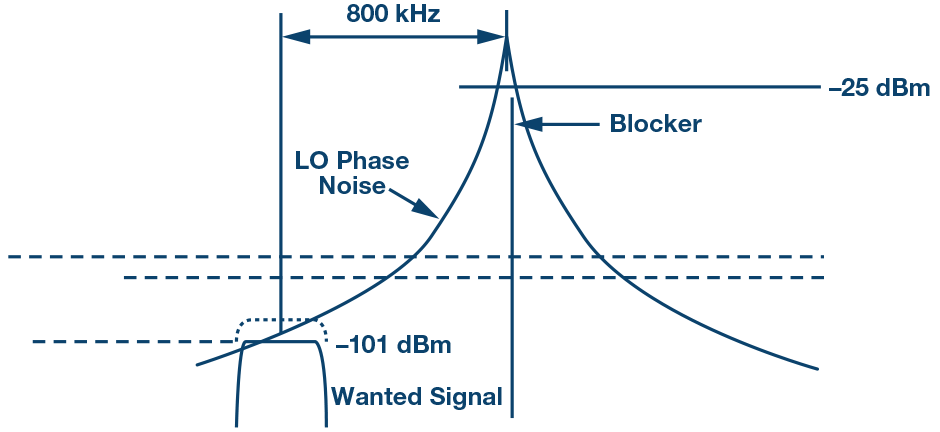

VCOのブロッキング仕様は、強力な伝送信号の存在を考慮する必要のあるセルラ式携帯電話システムにおいて、非常に重要です。レシーバーの信号が弱く、VCOのノイズがあまりにも大きい場合には、近くのトランスミッタの信号が混入して対象となる信号をかき消してしまう恐れがあります。図19は、レシーバーのVCOのノイズが大きい場合に、近くにある送信パワーが-25dBmのトランスミッタ( 周波数は800kHz離れています) によって、対象とする-101dBmの信号が埋もれてしまう様子を表したものです。これらの仕様はワイヤレス通信規格の一部です。ブロッキング仕様は、VCOの性能要件に直接的な影響を及ぼします。

VCO

PLLのもう1つの基本要素はVCOです。VCOでは、位相ノイズ、周波数範囲、消費電力の間の基本的なトレードオフが必要になります。発振器のQ値が高いほど、VCOの位相ノイズは小さくなります。しかし、Q値が高い回路ほど、周波数範囲は狭くなります。電源電圧の向上は、位相ノイズの低下につながります。アナログ・デバイセズのVCO製品ファミリを見てみると、「HMC507」は6650MHz~7650MHzの範囲に対応します。100kHzにおけるこのVCOのノイズは約-115dBc/Hzです。一方、「HMC586」は4000MHz~8000MHzのフル・オクターブに対応しますが、位相ノイズは-100dBc/Hzまで劣化します。このようなVCOの位相ノイズを最小限に抑える1つの手段は、VTUNEによるVCOの電圧のチューニング範囲を(最大20Vまたはそれ以上に)引き上げることです。ただ、そうするとPLL回路は複雑なものになります。多くのPLLでは、チャージ・ポンプは5Vまでしかチューニングできません。そのため、オペアンプを使用するアクティブ・フィルタによって、PLL回路のチューニング電圧を引き上げる必要があります。

マルチバンド対応のPLLとVCO

VCOの位相ノイズを劣化させることなく、周波数範囲を拡大する方法は、もう1つあります。それは、マルチバンドに対応するVCOを使用することです。マルチバンド対応のVCOでは、周波数範囲が少しずつ重なり合う複数のVCOを組み合わせて、1オクターブの周波数範囲をカバーします。低い周波数は、VCOの出力に周波数分割器を適用することによって生成します。そのような製品の例が「ADF4356」です。このICは、メインのVCOコアを4個内蔵しています。各コアは256の重なり合う周波数範囲をサポートします。内部リファレンスとフィードバック周波数分割器によって、VCOの帯域が適切に選択されます。この処理をVCOバンド選択または自動キャリブレーションと呼びます。

マルチバンド対応のVCOはチューニング範囲が広いので、広範にわたる周波数の生成が求められる広帯域対応の計測器に適しています。そうしたアプリケーションでは、フラクショナルN型で高い分解能(39ビット)が求められるため、その点でも理想的です。ベクトル・ネットワーク・アナライザなどの計測器では、超高速のスイッチング速度が不可欠です。それは、非常に帯域の広いローパス・フィルタによって、最終周波数を素早くチューニングすることで達成可能です。また、各周波数向けに直接プログラムされた周波数の値から成るルックアップ・テーブルを使用することにより、それらのアプリケーションにおける自動周波数キャリブレーションのルーチンを省くことができます。「HMC733」のような、シングルコアで広帯域に対応するVCOを使用すれば、複雑さを抑えることも可能です。

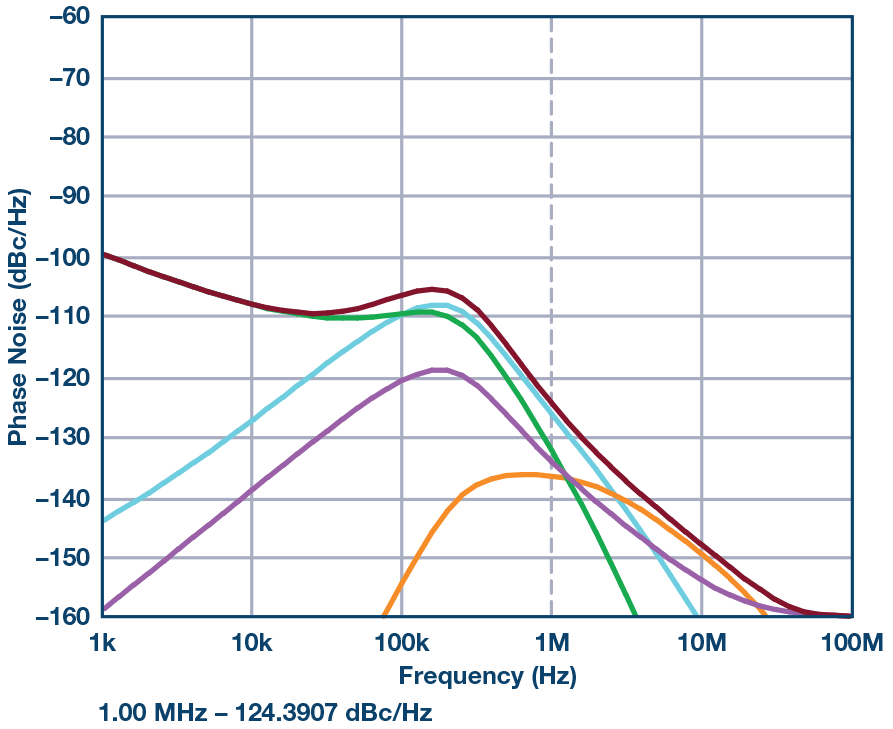

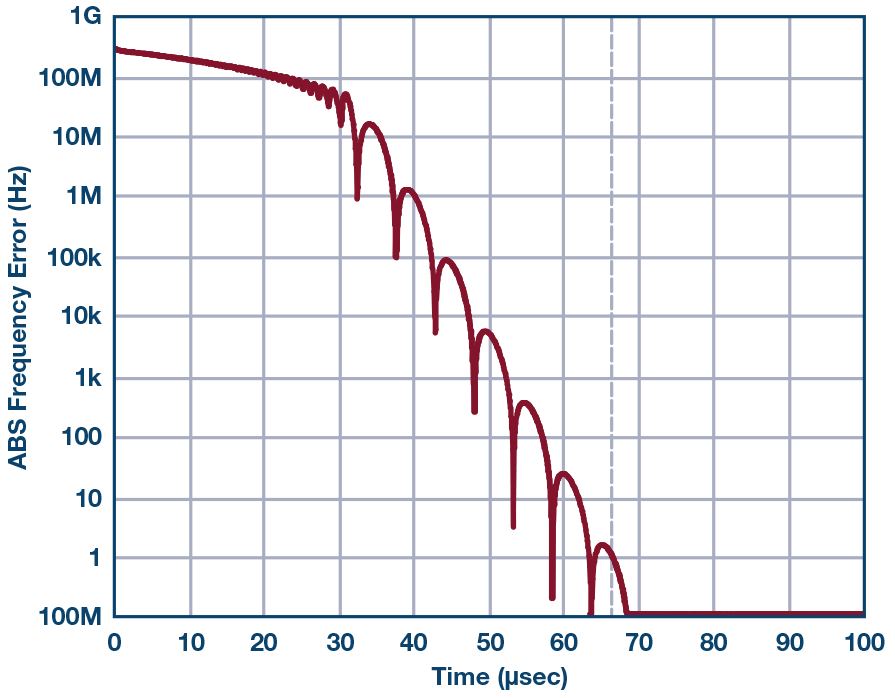

本稿で最後に取り上げるPLL回路の基本要素は、ローパス・フィルタです。ローパス・フィルタの帯域幅は、システムのセトリング時間に直接影響を与えます。セトリング時間が重要であるケースでは、ループ帯域幅を、安定したロック状態と、位相ノイズとスプリアスに関する目標を達成できる最大限の値に設定します。通信リンクにおいて狭い帯域が求められる場合に、HMC507を使用して(30kHz~100MHzの範囲の)積分ノイズを最小に抑えたいとします。その場合、ローパス・フィルタの最適な帯域幅は約207kHzになります(図20)。この場合、積分ノイズは約-51dBcとなり、約51マイクロ秒で1kHzの誤差範囲内に周波数をロックすることができます(図22)。

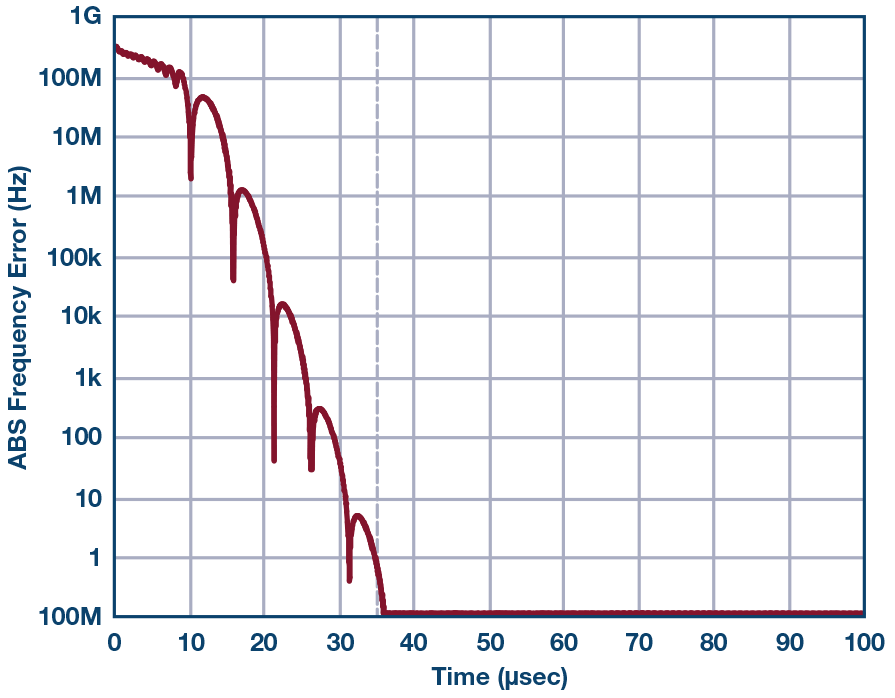

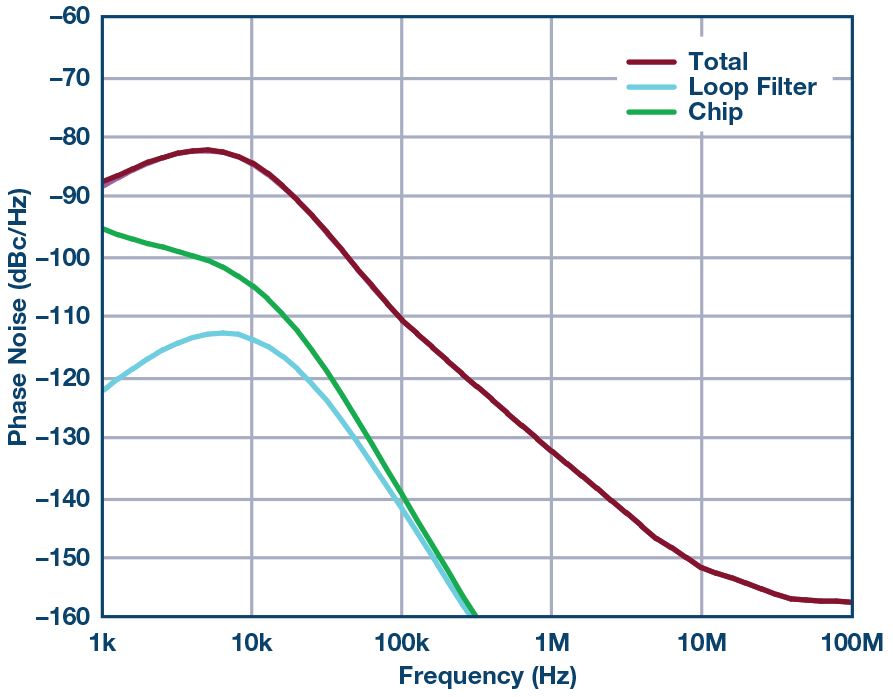

一方、広帯域に対応するHMC586(4GHz~8GHzに対応)は、300kHz弱という広い帯域幅で最適なrms位相ノイズを達成します(図21)。積分ノイズは-44dBcです。周波数は、27マイクロ秒以内に先ほどと同じ範囲内にロックすることができます(図23)。各アプリケーションにおいて最良の結果を得るためには、部品を適切に選定することと、周辺回路をあらゆる面で適切に設計することが非常に重要です。

低ジッタのクロッキング

高速なD/AコンバータやA/Dコンバータでは、クリーンでジッタの小さいサンプリング・クロックが必要不可欠です。帯域内のノイズを最小限に抑えるには、Nの値は小さい方が望ましいと言えます。スプリアスを抑えるには、インテジャーN型のPLLが適しています。クロックは固定周波数であるケースが多いので、REFINの周波数が入力周波数のちょうど整数倍になるように周波数を選択することができます。それによって、帯域内のPLLのノイズを最小限に抑えられます。VCO(集積されているかどうかにかかわらず)については、アプリケーションに対して十分に低ノイズであるものを選択します。特に、広帯域ノイズには注意を払う必要があります。更に、ローパス・フィルタを、帯域内のPLLのノイズがVCOのノイズを横断するように慎重に配置することで、rmsジッタを最小限に抑えることができます。位相マージンが60°のローパス・フィルタを使用すれば、フィルタのピーキングが最小になり、ジッタも最小限に抑えられます。低ジッタのクロッキングは、本稿の最初に示したクロックのクリーンアップの用途と、最後に示した回路の高速スイッチング機能の用途の中間に位置します。

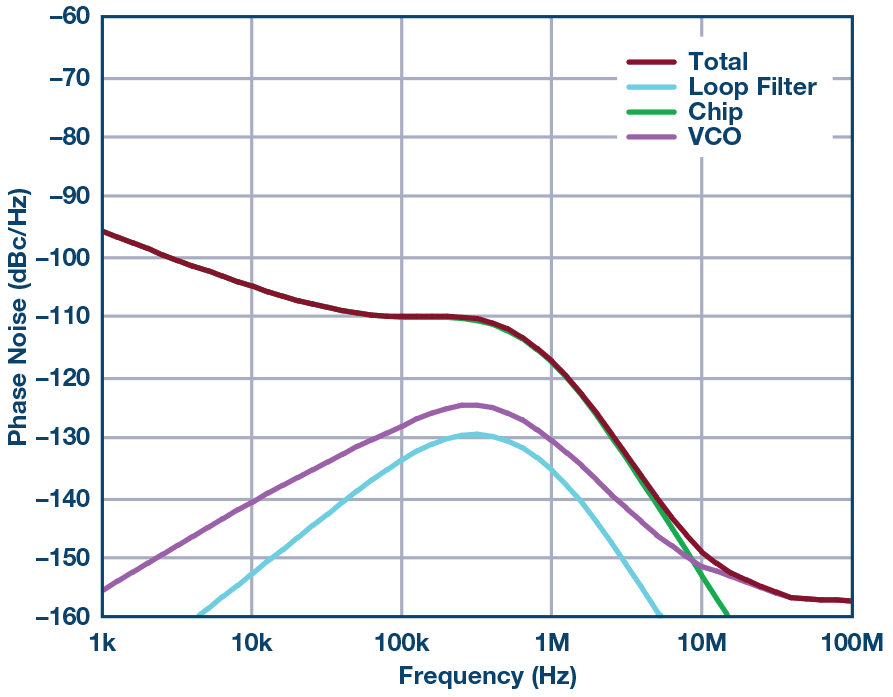

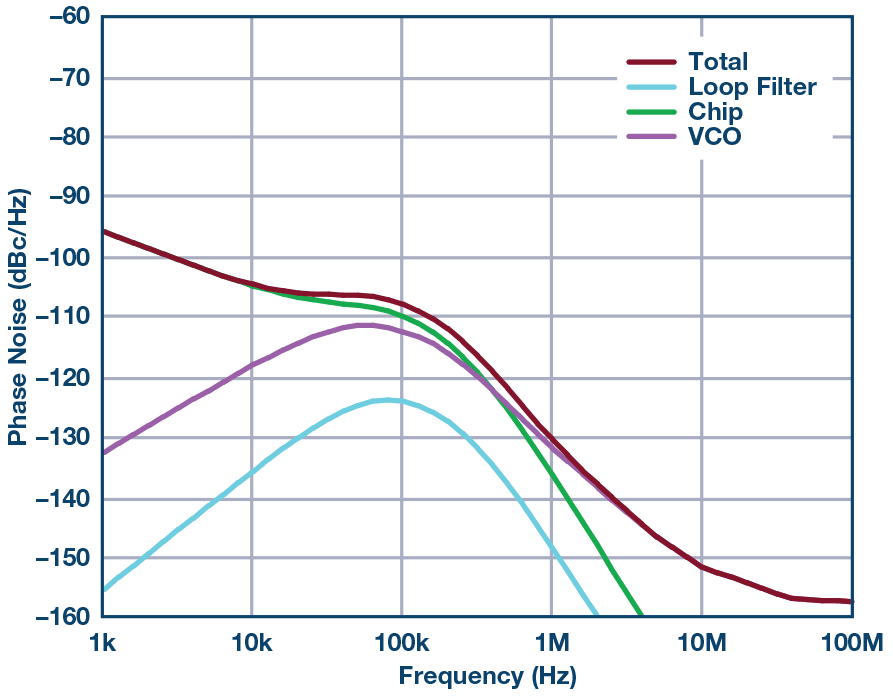

クロック回路においては、クロックのrmsジッタが主要な性能パラメータとなります。このパラメータは、ADIsim-PLLを使用すれば見積もることができます。もちろん、シグナル・ソース・アナライザを使えば実測することも可能です。「ADF5356」のような高性能のPLLを使用すれば、132kHzという比較的広いローパス・フィルタの帯域幅と、Wenzel Associatesが提供するOCXO(恒温槽付水晶発振器)のような、REFINが非常に低いクロック源によって、rmsジッタを90フェムト秒未満に抑えたクロックを生成することができます(図26)。PLLのループ・フィルタの帯域幅(LBW)を調整する際、それをあまりに小さくすると、帯域内のPLLのノイズが小さくなる近傍のオフセット位置において、VCOのノイズが支配的になります(図24)。逆にあまりにも大きくすると、VCOのノイズがかなり小さくなるオフセット位置において、帯域内のノイズが支配的になることがわかります(図25)。

参考資料

Ian Collins「Integrated PLLs and VCOs for WirelessApplications(ワイヤレス・アプリケーション用のPLL/VCO)」Radio Electronics、2010年

Mike Curtin、Paul O’Brien「Phase-Locked Loops forHigh Frequency Receivers and Transmitters - Part 1(高周波レシーバー/トランスミッタ用のPLL - パート1)」Analog Dialogue、AD33-03