Maxim > 設計サポート > 技術資料 > チュートリアル > A/D変換とD/A変換、サンプリング回路 > APP 641

キーワード:用語集、ADC、DAC、A/Dコンバータ、D/Aコンバータ、A/D変換、D/A変換、コンバータ、定義

チュートリアル 641

# ADC/DACに関する用語集

2002年7月22日

#### 概要

本稿では、A/D コンバータ(ADC)と D/A コンバータ(DAC)に関連してよく使われる技術用語の意味を説明します。

#### アクイジション・タイム

アクイジション・タイムとは、ADCのホールド状態(トラック&ホールド機能を実現する入力回路による)が解除されてから、サンプリング用のコンデンサの電圧が新たな入力電圧の 1LSB 以内に相当する値に収まるまでにかかる時間のことです。アクイジション・タイム(Taco)は以下の式で表されます。

#### $T_{acq} = In (2^N) \times (R_{SOURCE} \times C_{SAMPLE})$

ここで、 $R_{SOURCE}$  はソース・インピーダンス、 $C_{SAMPLE}$  はサンプリング用のコンデンサの容量、N は ADC の分解能(ビット数)です。

#### エイリアシング

エイリアシングとは、サンプリング定理に関連する用語です。ADCに入力される信号にナイキスト周波数よりも高い周波数の成分が存在していた場合、A/D 変換に伴って生じるエイリアシングが生じます。 周波数スペクトルで見ると、その高い周波数の成分がナイキスト周波数より高い位置と低い位置に現れます。この事象については「折り返す」、「複製される」などと表現され、特にナイキスト周波数より低い成分によって問題が生じる可能性があります。

エイリアシングを防ぐためには、入力信号にフィルタリングを施して不要な信号成分をあらかじめ除去しておきます。それにより、ADCがそれらの成分をデジタル化しないようにします。ただ、アンダーサンプリングを用いるアプリケーションでは、意図的にエイリアシングを生じさせ、その結果を活用するということが行われます(「アンダーサンプリング」の項も参照)。

エイリアシングについては、「Filter Basics: Anti-Aliasing(フィルタの基礎:アンチエイリアシング)」 も参照してください。

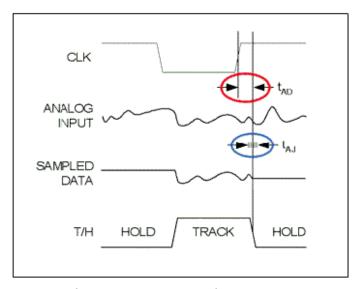

### アパーチャ遅延

ADC のアパーチャ遅延( $t_{AD}$ )とは、クロック信号のサンプリング・エッジ(**図 1** のクロック信号の立上がりエッジ)からサンプルが取得される瞬間までの時間のことです。ADCのトラック&ホールド回路がホールド状態になると、サンプルが取得されます。

図 1. アパーチャ遅延(赤)とアパーチャ・ジッタ(青)

# アパーチャ・ジッタ

ADC では、サンプリングを繰り返し実施するたびに、アパーチャ遅延が変動します(**図 1**)。その変動をアパーチャ・ジッタ( $t_{AJ}$ )と呼びます。一般的な ADC では、アパーチャ・ジッタの値はアパーチャ遅延の値よりもはるかに小さくなります。

# バイナリ・コーディング (ユニポーラ)

通常、ユニポーラの信号のコーディング方式としてはストレート・バイナリが使用されます。バイナリ・コードの範囲は、ゼロ・スケールに相当するオール・ゼロ(00…000)から、正のフル・スケールの値に相当するオール 1(11…111)までです。ミッド・スケールは、1 つの 1(MSB)に続くオール・ゼロ(10…000)で表されます。このコーディング方法は、バイポーラの伝達関数の正/負の値に対応可能なオフセット・バイナリ方式に似ています。

#### バイポーラ入力

バイポーラというのは、あるリファレンス・レベルに対して信号が上下に振れることを意味しています。 シングルエンドのシステムでは、通常、入力はアナログ・グラウンドを基準とします。つまり、グラウンド・レベルに対して上下に振れるバイポーラ信号が使われます。一方、差動システムでは、入力信号はグラウンドを基準とするのではなく、正の入力は負の入力を基準にします。バイポーラの信号は、正の入力が負の入力に対して上下に振れる信号になります。

#### 同相モード除去(CMR)

同相モード除去 (CMR: Common-Mode Rejection) とは、2 つの入力に共通する信号成分を除去する能力のことです。同相モードの信号としては、AC 信号、DC 信号、あるいは両者を組み合わせた信号が存在し得ます。CMR に関連する用語に、同相モード除去比 (CMRR: Common-mode Rejection Ratio) があります。これは、同相モードの信号のゲインに対する差動信号のゲインの比のことです。多くの場合、CMRR は dB 単位の値として表されます。

#### クロストーク

クロストークは、各アナログ入力が他のアナログ入力からどの程度隔離されているのかを表す尺度です。 複数の入力チャンネルを備える ADC の場合、クロストークは、1 つのアナログ入力から他のアナログ 入力に結合する信号の量を表します。通常、その値は dB 単位で規定されます。複数の出力チャンネル を備える DAC の場合、クロストークは、他のチャンネルの出力信号が更新されたときに 1 つの出力チャンネルに現れるノイズの量を表します。

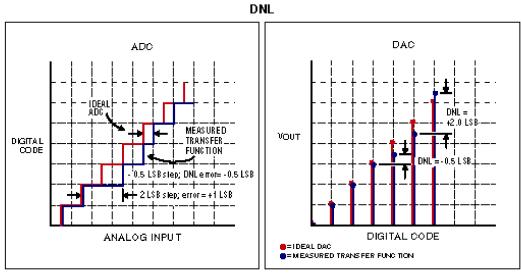

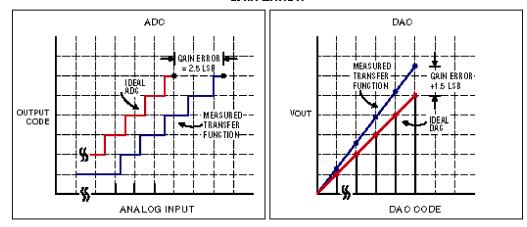

# 微分非直線性(DNL)誤差

ADC の場合、連続する 2 つの出力コードをトリガするアナログ入力のレベルは、理想的には 1LSB に相当する分だけ異なっているはずです。これが微分非直線性(DNL: Differential Nonlinearity)誤差がゼロの状態です。1LSB からの偏差があれば、それは DNL 誤差と呼ばれます。DAC の場合、DNL 誤差は連続する入力コードに対する理想的な出力応答と実測された出力応答の差を表します。理想的な DAC の応答では、アナログ出力の値は正確に 1 コード(LSB)に相当する分だけ離れています(DNL = 0)。

なお、DNLの仕様が1LSBに等しいかそれ未満であれば、単調性が保証されていることになります(「単調性」の項も参照してください)。

DNL については「INL/DNL Measurements for High-Speed Analog-to-Digital Converters (ADCs) (高速アナログ-ディジタルコンバータ(ADC)の INL/DNL 測定)」も参考にしてください。

図 2. ADC と DAC の DNL

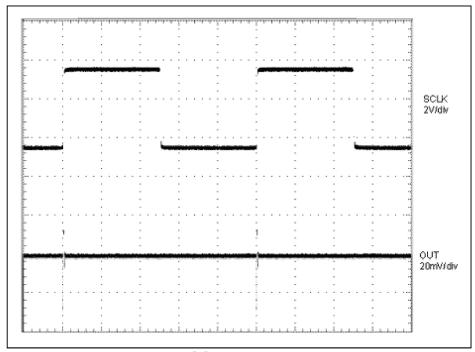

# デジタル・フィードスルー

デジタル・フィードスルーとは、デジタル制御ラインがトグルした際に DAC の出力に現れるノイズのことです。図3に示した DAC の出力には、シリアル・クロック信号からのノイズが原因でデジタル・フィードスルーが現れています。

図 3. デジタル・フィードスルー

#### ダイナミック・レンジ

ダイナミック・レンジは、デバイスの仕様で規定されている信号の最大レベルとノイズ・フロアの間に どれだけの差があるのかを表します。通常は dB 単位の値として定義されます。ADC の場合、ダイナミック・レンジはその ADC によって適切に解釈できる信号振幅の範囲を表します。例えば、ダイナミック・レンジが 60dB の ADC は、x から 1000x までの信号振幅を適切に解釈できるということになります。通信アプリケーションのように、信号の強度が大きく変化する場合には特にダイナミック・レンジが重要です。信号が大きすぎると、ADC が許容できる入力範囲をオーバーしてしまいます。一方、小さすぎる信号は、ADC の量子化ノイズに埋もれてしまいます。

### 有効ビット数(ENOB)

有効ビット数(ENOB: Effective Number of Bits)は、特定の入力周波数とサンプリング・レートを対象とした ADC の動的性能を規定するものです。理想的な ADC では、誤差として存在するのは量子化ノイズだけです。しかし、現実の ADC では入力周波数が高くなるにつれて全体的なノイズ(特に歪み成分)が増加します。その結果、ENOB が低下することになります。なお、その際には SINAD も低下します(「SINAD」の項も参照)。この SINAD に基づけば、フル・スケールの正弦波を入力した場合のENOB は次式で表すことができます。

$$ENOB = \frac{SINAD - 1.76}{6.02}$$

#### フォース・センス出力

フォース・センス出力とは、回路内の遠隔点に電圧(または電流)を強制的に印加し(フォース)、その結果生じる電流(または電圧)を測定(センス)する技術のことです。例えば、出力アンプを内蔵している DAC の中には、フォース・センス出力を備えているものがあります。その場合、出力アンプの反転入力が外部に接続できるようになっているはずなので、外部でフィードバック・パスを閉じて使用してください。

# フルパワー帯域幅 (FPBW)

ADCに、仕様で規定されたフル・スケールの振幅またはそれに近い振幅のアナログ入力を印加して動作させるとします。その入力信号の周波数を高めていくと、デジタル化された変換結果の振幅は低下していきます。その低下レベルが-3dBに達する入力周波数をフルパワー帯域幅(FPBW: Full-Power Bandwidth)と呼びます。

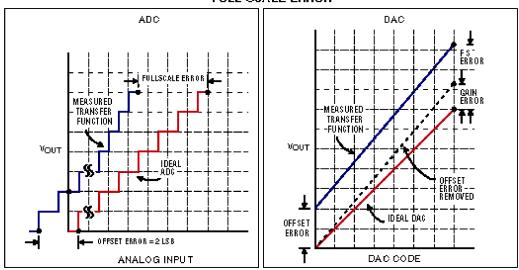

# フル・スケール(FS)誤差

フル・スケール誤差とは、フル・スケール(FS: Full Scale)への遷移をトリガする実際の値と理想的な値の差のことです。フル・スケール誤差の値は、 $\mathbf Z$  (に示すように、オフセット誤差とゲイン誤差の値の和になります。

#### FULL-SCALE ERROR

図 4. ADC と DAC のフル・スケール誤差

### DAC のフル・スケール・ゲイン誤差

DACのフル・スケール・ゲイン誤差とは、実際の出力スパンと理想的な出力スパンの差のことです。実際の出力スパンは、すべての入力を 1 に設定した場合の出力値から、すべての入力を 0 に設定した場合の出力値を引くことで求められます。ADC/DAC のフル・スケール・ゲイン誤差は、ゲイン誤差の測定に使用するリファレンスの影響を受ける可能性があります。

# ゲイン誤差

ADC/DAC のゲイン誤差は、実際の伝達関数の傾きが理想的な伝達関数の傾きとどれくらい一致しているのかを表します(図5)。フル・スケール誤差からオフセット誤差を引いた値がゲイン誤差です。通常、その値は、LSB 単位か、フル・スケール範囲に対する割合(%FSR)として表します。なお、ゲイン誤差は、ハードウェアまたはソフトウェアを利用することによって補正することが可能です。

#### GAIN ERROR

図 5. ADC と DAC のゲイン誤差

#### ゲイン誤差のドリフト

ゲイン誤差の値は、周囲温度の変化に応じて変動します。その変動量をゲイン誤差のドリフトと呼びます。通常、その値は ppm/℃単位で表されます。

#### ゲイン・マッチング

ゲイン・マッチングは、複数のチャンネルを備える ADC の全チャンネルのゲインが互いにどの程度一致しているのかを表します。ゲイン・マッチングの値は、すべてのチャンネルに同じ信号を入力し、ゲインの最大偏差(通常は dB 単位)を求めることによって測定します。

# グリッチ・インパルス

グリッチ・インパルスとは、メジャー・キャリー遷移が発生したときに DAC の出力に現れる電圧トランジェントのことです(「メジャー・キャリー遷移」の項も参照)。電圧対時間のグラフを作成した場合、得られる曲線より下の部分の面積に相当します。通常は単位が nV・s の値として測定されます。

#### 高調波

対象とする信号が、周期性を持つ信号であるとします。通常、その信号には歪みがあり、周波数が基本 周波数の整数倍の成分が含まれています。それらの周波数成分(正弦波)を高調波と呼びます。

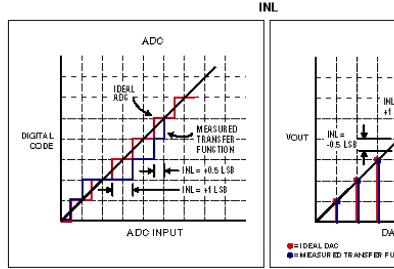

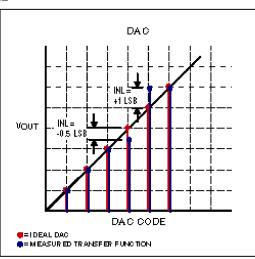

# 積分非直線性(INL)誤差

ADC/DAC の積分非直線性(INL: Integral Nonlinearity)誤差とは、実際の伝達関数(直線)に対する偏差のことを指します(図 6)。オフセット誤差とゲイン誤差をヌルにした後の直線は、ベストフィットの直線か伝達関数の両端を結ぶ直線となります。INLは「相対精度」とも呼ばれます。

図 6. ADC と DAC の INL

INL については「INL/DNL Measurements for High-Speed Analog-to-Digital Converters (ADCs) (高速アナログ-ディジタルコンバータ(ADC)の INL/DNL 測定)」も参考にしてください。

### 相互変調歪み (IMD)

相互変調歪み(IMD: Intermodulation Distortion)とは、回路やデバイスの非直線性が原因で生じる、元の信号には含まれていない周波数成分のことです。IMDには、高調波歪みと 2 トーン歪みの影響が現れます。これらは、2 つの入力信号 f1 と f2 の総電力に対する、2 次から 5 次までの相互変調積の総電力の比として測定します。f1 と f2 としては、振幅が等しく、周波数が互いに非常に近い信号を選択します。f1 2 次から f1 3 次までの相互変調積(f1 2 次から f1 3 次までの相互変調積(f1 3 次)は、以下のような成分になります。

- · 2 次の相互変調積 (IM2): f1 + f2、f2 f1

- ・3 次の相互変調積 (IM3): 2×f1 f2、2×f2 f1、2×f1 + f2、2×f2 + f1

- · 4次の相互変調積 (IM4): 3×f1 f2、3×f2 f1、3×f1 + f2、3×f2 + f1

- ・5 次の相互変調積 (IM5): 3×f1 2×f2、3×f2 2×f1、3×f1 + 2×f2、3×f2 + 2×f1

#### 最下位ビット(LSB)

最下位ビット(LSB: Least Significant Bit)とは、2 進数の値を表すビット列の中で最も重みが小さい ビットのことです。通常、いちばん右のビットが LSB になります。ADC/DAC の場合、LSB の重みは、フル・スケールの電圧範囲を  $2^N$  で割った値になります。ここで、N は ADC/DAC の分解能です。例えば、ユニポーラ、フル・スケール電圧が 2.5V、分解能が 12 ビットの ADC の場合、 $1LSB = (2.5V/2^{12}) = 610 \,\mu$ V となります。

### メジャー・キャリー遷移

ミッド・スケールの付近では、次の 2 種類の遷移が生じます。1 つは、MSB がローからハイに変化し、他のすべてのビットがハイからローに変化するというものです。もう 1 つの遷移では、MSB がハイからローに変化し、他のすべてのビットがローからハイに変化します。これらをメジャー・キャリー遷移と呼びます。例えば、01111111 から 10000000 に変化する場合がそれにあたります。多くの場合、メジャー・キャリー遷移が生じる際には、最悪のスイッチング・ノイズが発生します(「グリッチ・インパルス」の項も参照)。

#### 単調性

ある数列において、すべての n に対して  $P_{n+1}$  の値が  $P_n$  の値より大きい(または等しい)場合、P の値は単調に増加すると表現します。同様に、ある数列において、すべての n に対して  $P_{n+1}$  の値が  $P_n$  の値より小さい(または等しい)場合、P の値は単調に減少していることになります。ある DAC において、入力コードの値が大きくなるにつれてアナログ出力の値が常に上昇するとします。この場合、その DAC は単調性を備えると表現します。一方、ある ADC において、アナログ入力の値が上昇するにつれてデジタル出力コードの値が常に大きくなるとします。この場合、その ADC は単調性を備えることになり

ます。ADC/DACでは、DNL 誤差が±1LSB以下である場合、単調性を備えることが保証されます。

### 最上位ビット (MSB)

最上位ビット(MSB: Most Significant Bit)とは、2 進数の値を表すビット列の中で最も重みが大きいビットのことです。通常、いちばん左のビットが MSB となります。

#### 乗算型 DAC(MDAC)

DACには、抵抗ストリング型、電流加算型、デルタ・シグマ型などの方式があります。乗算型もそうした方式のうちの 1 つです。乗算型 DAC (MDAC: Multiplying DAC) のリファレンス入力には、AC 信号を印加することができます。この性質を利用すれば、対象とする信号をリファレンス入力に印加し、DACの入力コードを使用してその信号をスケーリングすることが可能になります。つまり、デジタル減衰器の機能を実現できます。

#### ノー・ミッシング・コード

ADCのアナログ入力としてランプ信号を印加したとします。その応答としてすべてのデジタル・コードが生成できる場合、その ADC ではノー・ミッシング・コードが実現されていると表現されます。

#### ナイキスト周波数

ADC/DAC は、サンプリング定理に基づいて実現されます。同定理によれば、エイリアシングの影響を受けずにアナログ信号を完全に再現できるようにするためには、ADCのサンプリング・レートを信号の最大帯域幅(最高周波数)の 2 倍以上に設定しなければなりません。この最高周波数をナイキスト周波数と呼びます。

# オフセット・バイナリ

オフセット・バイナリは、バイポーラの信号に対してよく使用されるコーディング方式です。オフセット・バイナリ方式では、最も小さい負の値(負のフル・スケール)をオール・ゼロ(00…00)で表します。そして、最も大きい正の値(正のフル・スケール)をオール 1(11…111)で表現します。ゼロ・スケールは、MSB が 1 でそれ以外がすべてゼロになります(10…000)。この方式は、ユニポーラの信号に対してよく使用されるストレート・バイナリに似ています。「バイナリ・コーディング(ユニポーラ)」、「ユニポーラ」の項も参考にしてください。

# オフセット誤差(バイポーラ ADC/DAC の場合)

バイポーラに対応する ADC/DAC のオフセット誤差は、ユニポーラに対応する ADC/DAC のオフセット誤差と同様の方法で測定します。但し、ゼロ・スケールで測定される誤差は、バイポーラの伝達関数におけるミッド・ポイントの誤差に相当します。「オフセット誤差(ユニポーラ ADC/DAC の場合)」の項も参照してください。

# オフセット誤差(ユニポーラ ADC/DAC の場合)

オフセット誤差は、「ゼロ・スケール誤差」とも呼ばれます。これは、実際の伝達関数が、ある 1 点で理想的な伝達関数とどのくらい一致しているのかを表します(**図 7**)。理想的な ADC の場合、最初の遷移は入力がゼロから 0.5LSB に相当するレベルに変化する際に生じます。ADC のオフセット誤差は、ゼロ・スケールの電圧をアナログ入力に印加し、最初の遷移が起こるまでその電圧を高めていくことによって測定します。DACの場合、オール・ゼロの入力コードに対するアナログ出力を測定することで、オフセット誤差の値を取得できます。

#### OFFSET ERROR DAO ADC IDEAL Hill: idéal dác νοσ OUTPUT **TEANSFER** MEASURED TROMSER FIING HIN JEPSET Er role - OFFSET EFROR - 12 JSB -2 LSB ANATOMINPHE DAD DODE

図 7. ADC と DAC のオフセット誤差

#### オフセット誤差のドリフト

オフセット誤差の値は、周囲温度の変化に応じて変動します。その変動量をオフセット誤差のドリフトと呼びます。通常、その値は ppm/℃単位で表されます。

#### オーバーサンプリング

ADCにおいて、ナイキスト周波数よりもはるかに高い周波数(サンプリング・レート)でアナログ入力信号をサンプリングすることをオーバーサンプリングと呼びます。オーバーサンプリングを実施すれば、ノイズ・フロアを効果的に低減することができます。それにより、ADCの動的性能が向上し、実質的な分解能が高くなります。デルタ・シグマ型の ADC では、オーバーサンプリングが基盤技術として使用されます。

「Demystifying Sigma-Delta ADCs(デルタ・シグマ型 ADC の謎を解き明かす)」という記事も参考にしてください。

#### 位相マッチング

位相マッチングは、マルチチャンネルの ADC の全チャンネルに同一の信号を印加した場合に、それぞ

れの位相がどの程度一致しているのかを表す指標です。全チャンネルの位相偏差の中で最大の値が位相マッチングの値として扱われます。通常、その単位としては度(゜)が使用されます。

### 電源電圧変動除去比(PSRR)

ADC/DAC では、電源電圧が変動すると、性能に変化が現れます。電源電圧変動除去比(PSRR: Power Supply Rejection Ratio)とは、DC 電源電圧の変動に対するフル・スケール誤差の比のことです。その値は dB 単位で表します。

### 量子化誤差

ADCにおいて、量子化誤差は、アナログ入力の実際の値と、その値に対応するデジタル表現の差として 定義されます。

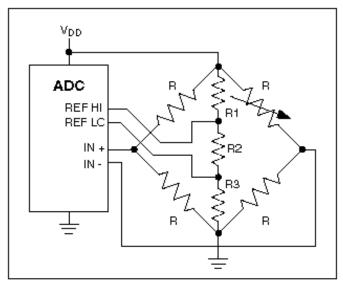

#### レシオメトリック測定

レシオメトリック測定を使用すれば、ADCのリファレンス電圧の変動によって生じる誤差を除去することができます。具体的には、ADCに対してリファレンス電圧を固定値として入力する代わりに、トランスデューサ(ロードセルやブリッジなど)に印加される信号の一部を入力します。抵抗ブリッジ回路を利用したレシオメトリック測定の例を図8に示しました。

図 8. 抵抗ブリッジ回路を利用したレシオメトリック測定

# 分解能

ADCの分解能とは、アナログ入力信号をデジタル・データとして表現するために使用するビット数のことです。アナログ信号をより正確に再現するためには、分解能が高くなければなりません。分解能の高い ADC を使用すれば、量子化誤差が小さくなります。DAC についても、分解能は ADC と似たような

意味を持ちます。分解能の高い DAC を使用した場合、入力するコードをインクリメントしたときに、より小さいステップ・サイズのアナログ出力が得られます。

### 二乗平均平方根(RMS)

AC 信号の二乗平均平方根(RMS:Root Mean Square)の値は、その信号の実効 DC 値または DC 等価値に相当します。その値は、AC 信号の振幅を 2 乗した値の時間平均をとり、その平方根を求めることで得られます。正弦波の場合、RMS 値はピーク値の $\sqrt{2}/2$  倍(0.707 倍)になります。これはピーク to ピーク値の 0.354 倍に相当します。

### サンプリング・レート/サンプリング周波数

サンプリング・レートまたはサンプリング周波数とは、ADC がアナログ入力信号を取得(サンプリング)するレートのことです。通常は、サンプル/秒(sps)の単位で表現します。1回のサンプリングに対して1回の変換結果を出力する ADC の場合、サンプリング・レートの代わりにスループット・レートという用語が使われることもあります。その種の ADC としては、逐次比較レジスタ(SAR)型のADC、フラッシュ型のADC、パイプライン型のADC などが挙げられます。それに対し、デルタ・シグマ型のADC では通常はオーバーサンプリングが行われます。そのため、サンプリング・レートは出力データ・レートよりもはるかに高くなります。

### セトリング時間

DAC のセトリング時間とは、出力値を更新(変更)するコマンドが実行されてから、DAC の出力が最終値に到達するまでの時間のことです。実際には、最終値を対象とするのではなく、最終値の数%以内に収まるまでの時間が使用されます。セトリング時間は、出力アンプのスルー・レートやリンギング、信号のオーバーシュートなどの影響を受けます。

ADC のセトリング時間とは、サンプリング用のコンデンサの電圧が 1LSB 以内に相当する電圧に到達するまでにかかる時間のことです。ADC のセトリング時間は、アクイジション時間より短いことが不可欠です。

### 信号/ノイズ+歪み(SINAD)

信号/ノイズ + 歪み(SINAD: Signal-to-Noise and Distortion Ratio)とは、正弦波(ADC の場合はアナログ入力、DAC の場合はアナログ出力)の RMS 値に対する、ADC/DAC のノイズと歪みの和の RMS 値の比のことです。RMS ノイズと歪みの和には、基本波と DC オフセットを除く、ナイキスト周波数までのすべてのスペクトル成分が含まれます。通常、SINAD の値は dB 単位で表されます。

# S/N比 (SNR)

S/N 比(SNR: Signal-to-Noise Ratio)とは、ある時点におけるノイズ信号の振幅に対する対象信号の

振幅の比のことです。デジタル・データを基に完全なアナログ波形を再生できる場合(理想的な ADC/DAC を使用できる場合)、理論上の最大 S/N 比は量子化誤差(残留誤差)の RMS 値に対するフル・スケールのアナログ信号の RMS 値の比になります。理想的な ADC で生じるノイズは量子化誤差だけです。その S/N 比は、以下に示す式のように ADC の分解能(N ビット)によって決まります。

$SNR_{dB[MAX]} = 6.02_{dB} \cdot N + 1.76_{dB}$

現実の ADC の S/N 比は、量子化雑音だけでなく、熱ノイズ、リファレンス・ノイズ、クロック・ジッタなどの影響を受けます。

#### 符号付き 2 進数

符号付き 2 進数とは、MSB が正または負の符号を表すコーディング方式のことです。例えば、-2 を 8 ビットで表現すると 10000010 になります。+2 の場合、00000010 と表現します。

#### スルー・レート

DACが電圧を出力するケースを考えます。その電圧出力は入力コードに応じて変化しますが、その変化にはある程度の時間がかかります。その最小時間に対応する最大レートのことをスルー・レートと呼びます。出力アンプを備える DAC の場合、通常、その DAC のスルー・レートは出力アンプのスルー・レートによって決まります。

ADC の場合、入力信号があまりにも高速に変化すると、デジタル化された出力データに誤差が生じます。そのような誤差が生じない最大レートのことをスルー・レートと呼びます。

# 小信号帯域幅(SSBW)

小信号帯域幅(SSBW: Small-signal Bandwidth)を測定する際には、まずADCに小振幅のアナログ信号を入力します。その信号の振幅は、スルー・レートがADCの性能を制限しないレベルまで小さく抑える必要があります。次に、デジタル化された変換結果の振幅が-3dB減衰する点まで入力信号の周波数を掃引します。多くの場合、SSBWは、ADCのトラック&ホールド回路で使用するアンプの性能によって決まります。

# スプリアスフリー・ダイナミック・レンジ (SFDR)

スプリアスフリー・ダイナミック・レンジ(SFDR: Spurious Free Dynamic Range)とは、基本波(最大の信号成分)の振幅の RMS 値と、最大のスプリアス成分(DC オフセットは除く)の RMS 値の比のことです。SFDR は、キャリアに対するデシベル値(単位は dBc)として規定されます。

# 全高調波歪み (THD)

全高調波歪み(THD: Total Harmonic Distortion)は、信号にどの程度の大きさの歪み成分が含まれ

ているのかを表します。多くの場合、キャリアに対するデシベル値(単位は dBc)として規定されます。 ADC の場合、THD は基本波と高調波の RMS 和の比を表します。その際、高調波については、どれを対象にするのかを選択することになります。THD を測定する際には、ナイキスト周波数までの高調波だけを対象とします。

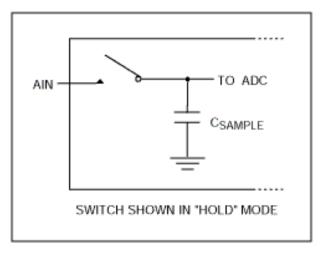

### トラック&ホールド回路

トラック&ホールド回路とは、ADC の入力部にあるサンプリング回路のことを指します。「サンプル&ホールド回路」とも呼ばれます。トラック&ホールド回路を最も基本的な形で表現すると、**図9**のようになります。ご覧のように、アナログ・スイッチとコンデンサによって構成されています。トラック・モードでは、この回路はスイッチが閉じている状態になります。ホールド・モードに移行するとスイッチが開き、最後の瞬間の入力の電圧がサンプリング用のコンデンサに保持されます。

図 9. トラック&ホールド回路の概念図

### 遷移ノイズ

理想的な ADC は、アナログ入力電圧を高めていくと、遷移領域に到達するまで一定のコードを出力します。しかし、現実の ADC では、遷移ノイズが原因で、隣接するコードの間で出力がトグルしてしまうことがあります。この現象は、入力電圧がある範囲内にあるときに発生します。各コードの遷移が発生する場所(コード・エッジ)は理論的には入力電圧の値で定義されます。しかし、遷移ノイズが原因で、その値は不確実なものになります。

#### 2 の補数

2 の補数とは、正負の数に対応するデジタル・コーディング方式の一種です。2 の補数を使用すると、加算と減算の計算が簡素化されます。例えば、-2 を 8 ビットの 2 の補数で表現すると 11111110 になります。+2 は 00000010 で表されます。

# アンダーサンプリング

アンダーサンプリングとは、ADCにおいて、サンプリング定理を満たさない低いサンプリング周波数でサンプリングを行う手法のことです。つまり、アンダーサンプリングでは、意図的にエイリアシングが発生するようにします。その場合、サンプリング定理を満たしていないことから、信号の情報が失われることが予想されます。しかし、アナログ入力とサンプリング周波数を適切に選択すると共に、アナログ入力に適切にフィルタリングを施せば、必要な情報を含むエイリアシングの成分を高い周波数から低い周波数にシフトしてから変換することができます。つまり、ADCをダウンコンバータとして効果的に使用し、広帯域幅の信号を所望の帯域にシフトしているということです。この手法を適切に機能させるには、ADCのトラック&ホールド回路の帯域幅が重要になります。つまり、想定される最高周波数の信号を処理できるだけの帯域幅を備えていなければなりません。

#### ユニポーラ

アナログ入力がシングルエンドの ADC では、ユニポーラの信号の入力範囲は、ゼロ・スケール(通常はグラウンド)からフル・スケール(通常はリファレンス電圧)までとなります。差動入力を備える ADC の場合も、ユニポーラの信号の入力範囲は、ゼロ・スケールからフル・スケールまでです。但し、入力は負の入力を基準とする正の入力として測定されます。

## ゼロ・スケール誤差

「オフセット誤差(ユニポーラ ADC/DAC の場合)」の項を参照してください。

#### 詳細については、以下をご覧ください。

技術サポートに関するお問い合わせ: https://www.analog.com/jp/support.html サンプルのご依頼: https://www.analog.com/jp/support/sample-products.html

その他のご質問やご意見: https://www.analog.com/jp/contact-us.html

アプリケーション・ノート 641: https://www.analog.com/media/en/technical-documentation/application-notes/2698536550528608457AN641\_0.pdf チュートリアル 641, AN641, AN 641, APP641, Appnote 641

© 2002 Analog Devices, Inc. All rights reserved.

本ウェブページに掲載されているコンテンツは、米国およびその他の国の著作権法によって保護されています。

このコンテンツのコピーをご希望される方は、弊社までお問い合わせください

その他の法的注意事項: https://www.analog.com/jp/who-we-are/legal-and-risk-oversight.html