# RFトランシーバーICにより、デジタル・ ビームフォーミング方式のフェーズド・ アレイにおけるスプリアスの相関を排除

著者: Peter Delos、Michael Jones、Mark Robertson Analog Devices, Inc.

## はじめに

デジタル・ビームフォーミング方式を採用した大規模なアンテ ナでは、多くの波形発生器からの信号、あるいは多くのレシー バーからの信号を結合する処理が行われます。このビームフォ ーミング処理によって、ダイナミック・レンジを改善するとい うことです。仮に、各種の差要因に相関関係がなければ、ノイ ズ性能とスプリアス性能の両方について、ダイナミック・レン ジの数値が10logNだけ高まります。ここでNは、波形発生器ま たはレシーバーのチャンネル数です。ノイズは本質的に極めて ランダムな性質のものです。そのため、相関のあるノイズ源と 相関のないノイズ源を区別するのは比較的容易です。それに対 し、スプリアス信号の相関を強制的に排除するのは容易ではあ りません。この排除の処理を実現することができれば、フェー ズド・アレイ・システムのアーキテクチャに対して、大きなメ リットがもたらされることになります。

実は、スプリアス信号の相関を排除する手法は、既に公開 されています。それは、LO(局部発振器)の周波数にオフ セットを加え、そのオフセットをデジタル的に補償するとい うものです。本稿では、まずこの手法の概念について解説し ます。次に、アナログ・デバイセズの最新のトランシーバー IC「ADRV9009」が備える機能を使うことで、その概念を具現 化する方法を説明します。最後に、この手法の効果を確認する ための実測データを示すことにします。

## スプリアスの相関を排除するための既知の手法

フェーズド・アレイにおけるスプリアスの相関を排除する方法 は、かなり以前からいくつも考案されてきました。筆者らが 入手した中で最も古い文献は、2002年に公開されたものです1 その文献には、レシーバーのスプリアスの相関を確実に排除 するための一般的な手法について記されています。その手法で は、まず、各レシーバーの信号に対して、既知の方法で変更処 理を加えます。各信号は、レシーバーの非線形部品の影響で歪 んでいきます。次に、レシーバーの出力において、それまでに 加えられた変更処理の反転を意味する処理を適用します。対象 となる信号はコヒーレントになり相関を持ちますが、歪みの成 分は復元されません。この手法の実証テストでは、変更処理と して次のようなものが使われました。それは、各LOシンセサイ ザが異なる周波数を出力するように設定し、デジタル処理によ って数値制御発振器(NCO)を制御することで、変更処理に対 する補正を加えるというものです。なお、これ以外にも複数の 手法が既に公開されています<sup>2、3</sup>。

歳月を経て、半導体技術は大きく進化しました。その結果、ト ランシーバーのサブシステム全体を1つのモノリシックなチップ 上に集積できるようになりました。

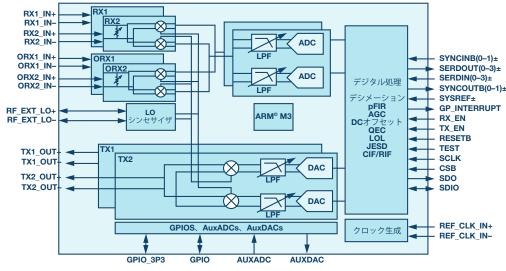

図1. ADRV9009の機能ブロック図

また、細心のトランシーバーIC製品は、非常に高度でプログラマブルな機能を搭載するようになりました。それらの機能を使えば、「Correlation of Nonlinear Distortion in Digital Phased Arrays: Measurement and Mitigation」「に記されている、スプリアスの相関を排除するための手法を実現できます。

# トランシーバーICの機能により スプリアスの相関を排除

図1に、ADRV9009の機能ブロック図を示しました。

各波形発生器またはレシーバーは、ダイレクト・コンバージョンのアーキテクチャに基づいて実装されています。ダイレクト・コンバージョンのアーキテクチャについては、Daniel Rabinkin氏による文献「Front-End Nonlinear Distortion and Array Beamforming」をで覧ください⁴。LOの周波数は、各IC上でそれぞれ個別にプログラムすることができます。デジタル処理部には、NCOを使用したデジタル・アップ・コンバージョンとデジタル・ダウン・コンバージョンの処理が含まれています。NCOも各ICでそれぞれ個別にプログラムすることが可能です。デジタル・ダウン・コンバージョンについては、Peter Delos氏による文献「広帯域RFレシーバー・アーキテクチャ・オプションの検討」をで覧ください⁵。

続いて、複数のトランシーバーにわたってスプリアスの相関を排除する方法について説明します。まず、オンボードのフェーズ・ロック・ループ(PLL)をプログラムすることにより、LOの周波数にオフセットを加えます。続いて、そのオフセットをデジタル的に補償するように、NCOの周波数を設定します。両方の機能の調整をトランシーバーICの内部で行うことにより、トランシーバーに入出力されるデジタル・データの周波数にオフセットを加える必要がなくなります。トランシーバーICには、周波数を変換する機能とスプリアスの相関を排除する機能の全体が組み込まれることになります。

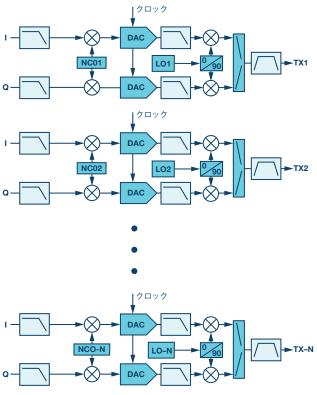

図2. 波形発生器のアレイ。このアレイ全体を対象として LOの周波数とNCOの周波数をプログラムすることにより、 スプリアスの相関を排除します。

図2に示したのは、波形発生器のアレイを表すブロック図です。 以下では、この波形発生器を前提とし、相関を排除する手法 について説明したり、データを示したりすることにします。なお、この手法は、レシーバーのアレイにも同じように適用できます。

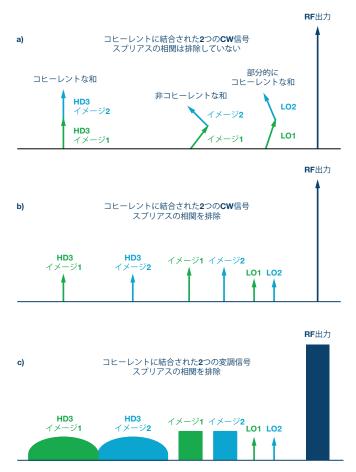

図3は、周波数の観点から相関を排除する方法を説明するための概念図です。これは、ダイレクト・コンバージョンのアーキテクチャから送信された2つの信号を表しています。ご覧のように、RF出力がLOよりも高い周波数に存在します。ダイレクト・コンバージョンのアーキテクチャにおいて、イメージと3次高調波は、LOの周波数よりも低い周波数に現れます。LOの周波数をすべてのチャンネルで同じ周波数に設定すると、図3 (a)に示すように、スプリアスの周波数も同じになります。図3 (b)に示したのは、LO2の周波数をLO1よりも高く設定した場合の例です。デジタルで制御されるNCOは、RF信号がコヒーレントなゲインを得るように、同じようにオフセットを与えます。イメージと3次高調波歪みとでは、周波数が異なります。したがって、両者に相関関係はありません。図3 (c) は、図3 (b) と同じ構成でRF搬送波に変調を加えた場合の様子を表しています。

図3. スプリアスの周波数スペクトル。(a)は、結合された2つの CW (連続波) 信号を使用した場合の例です。スプリアスの 相関を排除する処理は適用していません。(b)は、結合された 2つのCW信号に対し、スプリアスの相関を排除する処理を 適用した結果です。(c) は、結合された2つの変調信号に対し、スプリアスの相関を排除する処理を適用した結果です。

## 測定結果

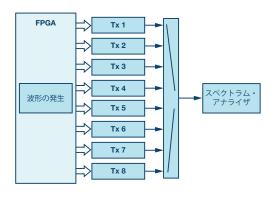

筆者らは、8チャンネルのトランシーバーをベースとするRFテスト環境を構築しました。それにより、フェーズド・アレイのアプリケーションでの使用を前提として、トランシーバーICの評価を行いました。図4に示したのは、波形発生器を評価するための構成です。評価にあたっては、すべての波形発生器に同じデジタル・データを適用します。

また、NCOの位相を調整することにより、すべてのチャンネルに対するキャリブレーションを実施します。8つの信号を結合するコンバイナにおいて、RF信号が同相で、コヒーレントに結合されるようにします。

図4. 波形発生器のスプリアスをテストするための構成

次に、LOとNCOをすべて同じ周波数に設定した場合と、LOとNCOの周波数にオフセットを加えた場合のスプリアスを比較するためのテスト・データを示します。使用したトランシーバーICは、2つのチャンネルで1つのLOを共有します(図1)。そのため、8個のRFチャンネルに対し、LOの周波数が4種類存在することになります。

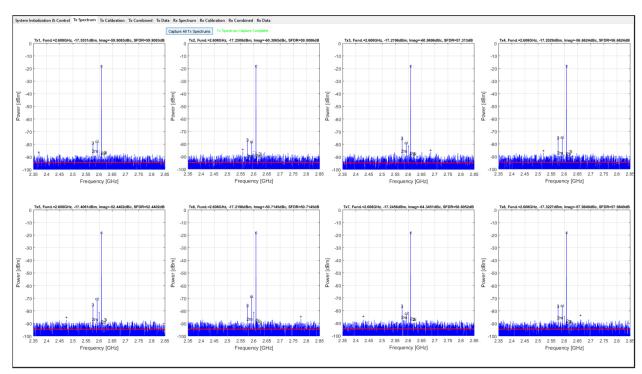

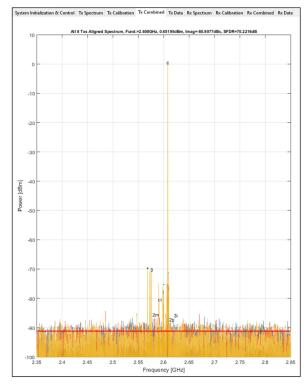

図5と図6は、トランシーバーのNCOとLOをすべて同じ周波数に設定して取得したものです。この場合、イメージ、LOリーク、3次高調波から生成されるスプリアスは、すべてのチャンネルで同じ周波数になります。図5は、個々の送信出力をスペクトラム・アナライザで測定したものです。一方、図6は結合後の出力を測定した結果です。このテストでは、搬送波を基準とするdBcを単位として測定を行っています。測定結果を見ると、イメージとLOリークのスプリアスには改善が見られます。しかし、3次高調波は改善されていません。一連のテストの結果から、3次高調波はチャンネル間で必ず相関を持つ、イメージは必ず相関を持たない、LOリークについては起動時の条件によって相関の状態が異なる、ということがわかりました。図3(a)では、これらを反映して、3次高調波に対してはコヒーレントな

和、イメージに対しては非コヒーレントな和、LOリークに対しては部分的にコヒーレントな和と表現しています。

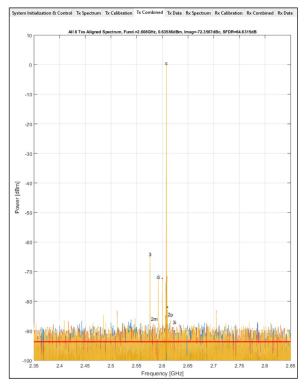

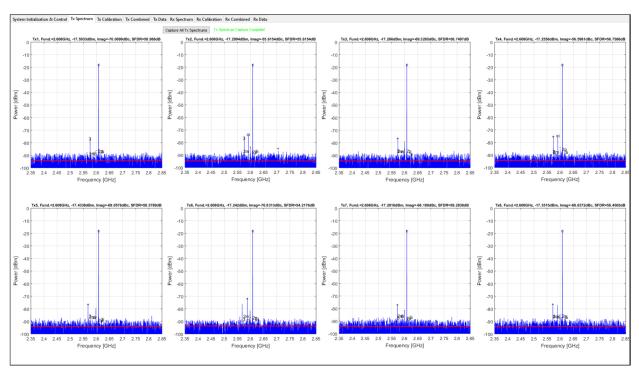

次に、トランシーバーのLOをすべて異なる周波数に設定しました。また、NCOについては、信号がコヒーレントに結合されるように、周波数と位相の調整を行いました。そのようにして得られたのが、図7と図8に示したスペクトルです。この場合、イメージ、LOリーク、3次高調波から生成されるスプリアスはすべて異なる周波数になります。図7は、個々の送信出力をスペクトラム・アナライザで測定したものです。一方の図8は、結合後の出力を測定した結果です。このテストでも、搬送波を基準とするdBcを単位として測定を行っています。イメージ、LOリーク、3次高調波がノイズとして拡散されるようになり、チャンネルの結合時にはすべてのスプリアスに改善が見られます。

この例のように、ごく少数のチャンネルを結合する場合、ス プリアスは相対レベルで20log(N)だけ改善します。これは、ス プリアスは全く結合されず、信号成分がコヒーレントに結合さ れて20log(N)だけ改善されるからです。実用的なアレイは大規 模で、はるかに多数のチャンネルが結合されるはずです。その 場合の改善量は10log(N)に近づくと考えられます。その理由は 2つあります。1つは、多数の信号を結合する場合、現実的に は、各スプリアスが分離していると見なせるほど十分に拡散す ることはできないからです。例えば、変調帯域幅が1MHzであ るとします。また、仕様では、1MHzの帯域幅でスプリアスの 放射を測定すると定められているとしましょう。その場合、ス プリアスを1MHz以上離して拡散するのが理想的です。それが できない場合、1MHzの各測定帯域幅には、複数のスプリアス 成分が含まれることになります。それぞれ周波数が異なるの で、それらは非コヒーレントに結合し、1MHzの各帯域幅で測 定されるスプリアス電力は10log(N)だけ増加します。しかし、 どの1MHz帯域幅にも、すべてのスプリアスが含まれるという わけではありません。そのため、ここでのNは信号数のNよりも 小さくなります。つまり、改善量は10log(N)ですが、Nが十分 に大きく、測定帯域幅内に複数のスプリアスが配置されるなら ば、スプリアスの相関を排除しないシステムに対する絶対的な 改善量は、10log(N)よりもさらに高くなります。つまり、dB単 位で10log(N)と20log(N)の間の改善量が見込めるということで

図5. 各チャンネルの波形発生器の出力。LOとNCOを同じ周波数に設定した場合の結果です。

図6. 結合後の出力。LOとNCOを同じ周波数に設定した場合の結果です。この場合、3次高調波には改善が見られません。

図7. 各チャンネルの波形発生器の出力。LOとNCOの周波数にオフセットを加えた場合の結果です。

もう1つの理由は、このテストでCW(連続波)信号を使用したことに起因します。現実の信号は変調されるので、信号の拡散が生じます。そのため、多数のチャンネルを結合するときに、スプリアスが重ならないようにするのは不可能です。重なったスプリアス信号には相関関係はなく、重複している領域において非コヒーレントに10log(N)だけ加算されます。

LOの周波数をすべてのチャンネルで同じ値に設定した場合、LOリークの成分については特筆すべきことがあります。LOリークは、2つの信号を加算する際に、アナログ変調器におけるLOのキャンセルが不完全であることに起因して発生します。振幅と位相の不均衡がランダムな誤差として現れる場

合、LOリークの残余成分の位相もランダムになります。多数の異なるトランシーバーのLOリークは、周波数が全く同じであったとしても、非コヒーレントに10log(N)だけ加算されます。同じことは変調器のイメージ成分にも当てはまりますが、変調器の3次高調波には必ずしも当てはまりません。少数のチャンネルがコヒーレントに結合される場合、LOの位相が完全にランダムになる可能性は低いはずです。実際、測定結果からは相関の部分的な排除が行われたことが見てとれます。チャンネル数が非常に多い場合には、LOの位相はチャンネル間ではるかにランダムに分布するようになり、相関がない状態で加算されることが期待できます。

図8. 結合後の出力。LOとNCOの周波数にオフセットを加えた場合の結果です。この場合、スプリアスは周波数軸上で拡散されます。 そのため、個々のチャンネルで見た場合と比べて、SFDRが明らかに改善されています。

## まとめ

LOとNCOの周波数にオフセットを加えた場合、SFDRの測定結果には、生成されたスプリアスがすべて異なる周波数にあることがはっきりと現れます。それらはコヒーレントには結合されず、チャンネルの結合時のSFDRは必ず改善されます。アナログ・デバイセズの最新のトランシーバーICでは、プログラミングによってLOとNCOの周波数制御が行えます。本稿で紹介した評価結果は、それらの機能をフェーズド・アレイのアプリケーションに適用できること、また、アレイのレベルのSFDRはシングルチャンネルの場合よりも確実に改善されることを示しています。

#### 参考資料

- <sup>1</sup> Lincoln Cole Howard、Daniel Rabideau「Correlation of Nonlinear Distortion in Digital Phased Arrays: Measurement and Mitigation (デジタル・フェーズド・アレイにおける非線形歪みの相関: 測定と低減) 」2002 IEEE MTT-S International Microwave Symposium Digest

- <sup>2</sup> Salvador Talisa、Kenneth O'Haever、Thomas Comberiate、 Matthew Sharp、Oscar Somerlock「Benefits of Digital Phased Arrays (デジタル・フェーズド・アレイのメリット)」 Proceeding of the IEEE、Vol. 104、No. 3、2016年3月

- <sup>3</sup> Keir Lauritzen「Correlation of Signals, Noise, and Harmonics in Parallel Analog-to-Digital Converter Arrays (A/Dコンバータの並列アレイにおける信号、ノイズ、高調波の相関)」Ph.D. Dissertation、University of Maryland、2009年

- <sup>4</sup>Rabinkin、Song、「Front-End Nonlinear Distortion and Array Beamforming (フロント・エンドの非線形歪みとアレイ・ビームフォーミング)」Radio and Wireless Symposium (RWS) 2015 IEEE

- <sup>5</sup>Peter Delos「広帯域RFレシーバー・アーキテクチャ・オプションの検討」 Analog Devices、2017年2月

Peter Delos「Can Phased Arrays Calibrate on Noise? (フェーズド・アレイはノイズのキャリブレーションを実現できるのか?)」 Microwave Journal、2018年3月

Jonathan Harris「デジタル・ダウンコンバータを理解する【Part1】」 Analog Dialogue AD50-07

Jonathan Harris「デジタル・ダウンコンバータを理解する【Part2】」 Analog Dialogue AD50-11

Howard、Lincoln、Nina Simon、Daniel Rabideau「Mitigation of Correlated Nonlinearities in Digital Phased Arrays Using Channel-Dependent Phase Shifts. (チャンネルに依存する位相シフトにより、デジタル・フェーズド・アレイにおける非線形な相関を緩和)」 2003 EEE MTT-S Digest

## 著者について

Peter Delos (peter.delos@analog.com) は、アナログ・デバイセズ(米国ノースカロライナ州グリーンズボロ)の航空宇宙/防衛グループに所属するテクニカル・リードです。1990年にバージニア工科大学で電気工学の学士号を、2004年にニュージャージー工科大学で電気工学の修士号を取得しています。エレクトロニクス業界で25年以上の経験を積んでおり、そのうちのほとんどの期間は、アーキテクチャのレベル、プリント基板のレベル、ICのレベルで先進的なRF/アナログ・システムの設計に携わってきました。現在は、フェーズド・アレイ・アプリケーション用の高性能レシーバー、波形発生器、シンセサイザの小型化を図るための設計に注力しています。

Mark Robertson (mark.robertson@analog.com) は、1990年に英国ケンブリッジ大学を卒業し、電気/情報科学の学位を取得しました。テスト/計測、携帯電話、セルラー基地局などを対象とするRF/アナログ回路の設計技術者として、様々な企業で経験を積みました。2012年にシステム・エンジニアとして、アナログ・デバイセズ(英国バース)に入社しました。現在でも、可能な範囲で回路設計に携わっています。

Mike Jones (michael.jones@analog.com) は、アナログ・デバイセズ(ノースカロライナ州グリーンズボロ)の航空宇宙/防衛事業部門に所属するプリンシパル電気設計エンジニアです。2016年にアナログ・デバイセズに入社しました。2007年から2016年までは、General Electric(ノースカロライナ州ウィルミントン)に勤務し、マイクロ波フォトニクスを専門とする設計技術者として、原子力事業向けのマイクロ波/光学ソリューションの開発に従事していました。ノースカロライナ州立大学で、2004年に電気工学の学士号とコンピュータ工学の学士号、2006年に電気工学の修士号を取得しています。

# オンライン・ サポート・ コミュニティ

アナログ・デバイセズのオンライン・サポート・コミュニティに参加すれば、各種の分野を専門とする技術者との連携を図ることができます。難易度の高い設計上の問題について問い合わせを行ったり、FAQを参照したり、ディスカッションに参加したりすることが可能です。

#### ez.analog.com にアクセス

\*英語版技術記事はこちらよりご覧いただけます。

# アナログ・デバイセズ株式会社

本 社 〒105-6891 東京都港区海岸1-16-1 ニューピア竹芝サウスタワービル10F 大阪営業所 〒532-0003 大阪府大阪市淀川区宮原3-5-36 新大阪トラストタワー10F 名古屋営業所 〒451-6040 愛知県名古屋市西区牛島町6-1 名古屋ルーセントタワー40F