# 高電圧高容量バッテリ・システム向けの低コストの isoSPI結合回路

Jon Munson

LTC6804 バッテリ・スタック・モニタに組み込まれているisoSPI™ 機能は、LTC6820のisoSPI通信インタフェースと組み合わせること で、絶縁障壁を越える安全で信頼性の高い情報伝達を可能にします。 isoSPIは特に、人体への危険を最小限に抑えるために完全な絶縁層 分離を必要とする、直列セルから数百Vを取り出すエネルギ貯蔵シス テムで有益です。

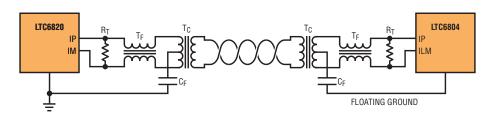

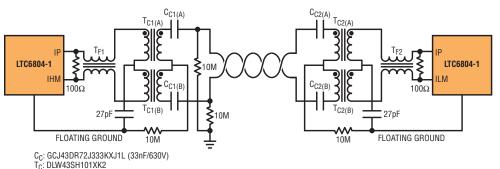

isoSPIの代表的応用例(図1)のパルス・トラン スは、絶縁層分離を備えており、配線の影響で 発生する可能性のある同相干渉を排除します。 isoSPI機能は、すぐに使用可能で低コストのイー サネットLAN用トランスで動作します。これら のトランスには通常、同相ライン・ノイズを改善 する同相チョーク・セクション(図1)、一般的な 100Ωライン終端抵抗、および同相デカップリン グ・コンデンサが含まれます。

イーサネットおよびゲート・ドライバのタイプを 含む通常の信号トランスの巻線にはエナメル被 覆線が使用されており、ピンホール大の絶縁欠 陥がある場合があります。この欠陥は導線を大 気に曝すので、認定されるそのようなトランスに ついて巻線間バイアスが本質的に制限されま す。このようなユニットは製造過程で高電位 (通 常1.5kV) を使用して試験され(「高電位選別」 と呼ばれる)、全体的な絶縁問題が特定されま す。これは、60Vの長期間バイアスの安全設計 マージンとして確立されています。これは、微小 な腐食部分が巻線間に伝導路を形成するには 60Vを超える電圧を必要とする傾向があるから です。

#### 図1. 一般化したisoSPIポイント・ツー・ポイント・リンク

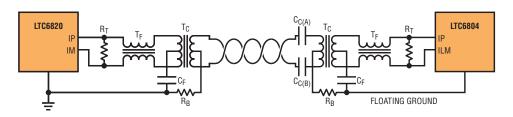

### 図2. 高電圧用のACカップリングisoSPIポイント・ツー・ポイント・リンク

#### 問題:高電圧 = 高コスト

400V範囲のバッテリ・スタック電圧の場合、優 れた設計方法は、強化(2倍)絶縁をもつトラン ス、および3750V以上の高電位試験を指定す ることです。このようなトランスを見つけること は小型部品と同様に困難です。 クリープ (表面距 離) とクリアランス (空間距離) の寸法が必要で あり、比較的高コストです。isoSPIは、最大1kV のバッテリ・システムに適用されますが、このよ うなバッテリ・システムでは、安全な設計マージ ンを持つには5kVで高電位試験を行ったトラン スが必要です。この段階で、絶縁部品が大型で 高コストになったり、パルスの忠実度が低下した りすることがあります。

## 解決策:分割により問題を解決

強化絶縁トランスを使用する方法に置き換わる 方法の1つは、追加の絶縁をカップリング・コン デンサに移動することにより、電磁部品のバイア ス要件を切り離すことです。コンデンサ単体は一 見して、総合的な絶縁オプションのように思われ ますが、トランスが備えている同相除去や耐衝 撃絶縁の特性をもたないので、実際にはL-C手 法が最適です。この方法では、コンデンサはDC バイアスの公称値まで充電し、トランスに過渡を 処理させます。この場合、通常のユニットも適切 に使用できます。

カップリング・コンデンサは、高い値をもつ抵抗 によりバイアスされます。この抵抗は通常、図2 に示すように、トランスのセンタータップ接続部 に接続されます。さらに、バイアス抵抗のDC電 流を監視する場合、絶縁破壊をフォルトとして検 出可能です。抵抗には10MΩのような高い値が 選択されるため、フォルト電流はトランスの良好 な配線の定格範囲内にあり、人体への感電の危 険が最小限に抑えられます。

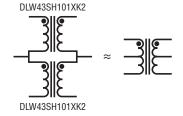

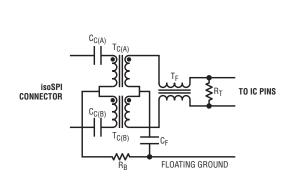

図3.2つの同相チョークをセンタータップ付きのisoSPIトランスとして使用

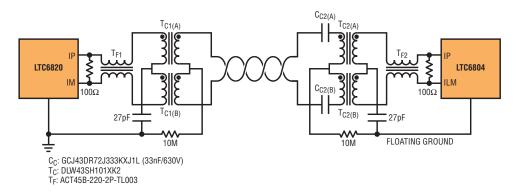

図4. 高電圧isoSPIポイント・ツー・ポイント・リンクの全体図

トランスの磁気設計から高電圧要件を取り除い たことにより、比較的低コストの多数のオプショ ンを使用できます。その1つは単純に、認証済 みイーサネット・トランスを適切に使用すること です。もう1つの方法は、他のすぐに使用できる 低プロファイルの磁性製品を使用して、部品の 高さと重量を低減し、はんだ接続の疲労問題を 減少することです。これらは、他の部品と同様に、 表面実装自動組み立て方法で取り付けることが でき、製造コストが低減されます。これらの機能 をもつ優れた候補は、個別同相チョーク(CMC) というトランス構造で、通常はフィルタ要素と して使用されています。このような部品は最大 100µHで使用可能であり、車載システムでの使 用が承認されているので、isoSPIの構成でも推 奨されます。

適切なCMCは低コストです。これらのCMC は、チップサイズのフェライト上に機械巻の配線 ペアを配置した形状として、短時間で簡単に製 造できます。isoSPIの設計には、長いパルス波 形を効果的に流すためにある程度高いインダク タンスが必要ですが、直列の巻線をもち200uH を発生するチョークを2つ使用して、適切なイン ダクタンスを達成できます。この設計の他の利点 として、仮想センタータップ接続が形成されるこ とがあります。この接続は、同相バイアスおよび デカップリング機能に有益です。

図3に、2つのCMCで実現される同等のトラン ス・モデルを示します。 図示のチョークは 1812 SMTの実装面積とバイファイラ巻き (製造時に 配線をペアにする)をもつので、1次と2次が密 接に一致します。これにより、漏れインダクタン スが最小になり、高周波数性能が維持されます。 物理的に巻線が分離されているタイプは、過剰 な漏れインダクタンスによりパルスの忠実度が 低下します。図に示すユニットは、50V DC連 続定格です。

#### 設計図の完成

図4に、L-C手法を使用し、トランスとして CMCを使用した全体の回路を示します。一般 的なisoSPIのアプリケーションには、役に立つ CMCフィルタ処理セクションが含まれているの で(標準のLAN部品の場合に内蔵)、この回路 にはその機能を保持するための推奨離散部品 が含まれます。カップリング・コンデンサは高品 質の10nF~33nFの部品で、実装面積は1812 です(定格630Vまたは1kV)。ここで、シャー シがグランド電位でLTC6820が動作している と仮定すると、ツイスト・ペアのバイアスは安全 レベルです。

デイジー・チェーン接続されたLTC6804-1モ ジュール間のリンク内にある場合のように、ツ イスト・ペアの両端がフロート電位である場合、 図5に示すように、リンクの両端にコンデンサを 使用し、各ラインに高い値の抵抗を接続して、 ツイスト・ペア自体を接地電位にバイアスできま す。この場合、コンデンサは直列なので、22nF 以上を推奨します(33nF/630Vタイプを図示)。

図5. 絶縁配線をもつ高電圧のデイジー・チェーンisoSPIリンク

T<sub>F</sub>: ACT45B-220-2P-TL003

高電圧isoSPIシステムのコストへの影響を緩和するために、ACカップリング方法を使用して、 磁気部品の2倍の絶縁要件を解消します。特殊トロイダル・トランスの磁気部品を低コストの ボビン巻同相チョーク (CMC) 部品に置き換えることで、コストをさらに削減できます。コンデ ンサとCMCは両方とも、比較的低プロファイルの表面実装チップ部品です。

> LTC6804-1 LTC6804-1 **≥**100Ω IHN 27pF FLOATING GROUND FLOATING GROUND T<sub>C</sub>: DLW43SH101XK2

図6. 同一基板上の相互接続用デイジー・チェーンisoSPIリンク

同一基板上にデイジー・チェーン接続された LTC6804-1の間にあるリンクでは、電位が通 常 50V 未満なので、コンデンサのカップリング は不要です。通常は、トランス・セクションが1 つのみ必要ですが(図6)、これは、通常は、ケー ブルなしで流入するノイズが非常に小さいため です。

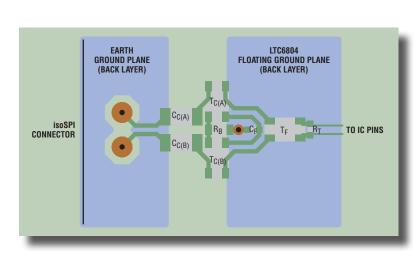

## 高電圧のレイアウト

プロント回路のレイアウトでは、メインの絶縁障 壁、つまりコンデンサの両端に広い絶縁空間が 必要です。図7に、良好な高電圧性能が得られ る配置例を示します。青の領域はそれぞれ、フ レーム・グランド(左側、ツイスト・ペア・コネク タ付き)とIC同相(右側)を表します。

トランスはHVの過渡電位に耐える必要がある ので、サイズが1206のバイアス抵抗を使用して、 間隔も維持します。HFデカップリング・コンデン サとインピーダンス終端抵抗には、小型部品を 使用できます(0602のサイズを図示)。

HV障壁の両端での漏れ電流を防止するもう 1つの優れた方法は、HV部品(グランド間の 「ギャップ」の上にある部品)の領域内で半田 マスクの使用を少なくすることです。これにより、 部品の下にある残留フラックスを効果的に洗浄 でき、多孔性の半田マスク層に水分が残ること を防止します。

## isoSPIバスに関する特別な検討事項

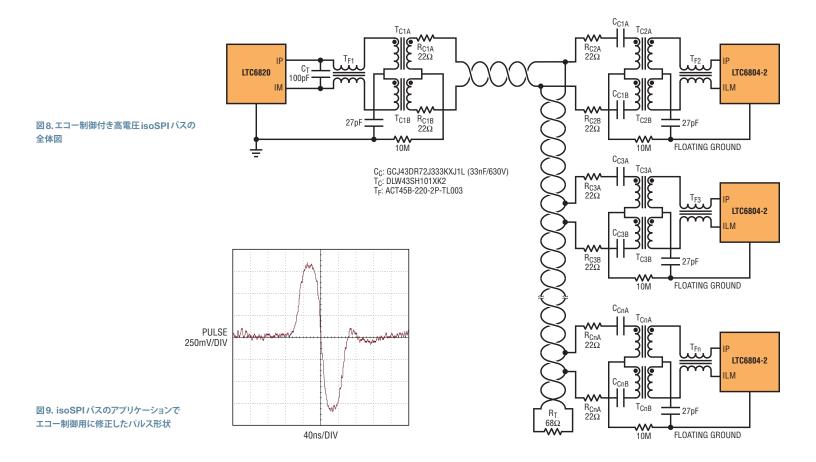

前述の各回路はポイント・ツー・ポイントの isoSPIリンクに適用されますが、高電圧ソリュー ションを提供する重要な事例の1つは、バス接 続され、アドレス指定可能なLTC6804-2です。 これは、図8に示すように、ツイスト・ペアのリン クが各「タップ」接続を通過しています。バスの

図7. isoSPIインタフェースでの高電圧性能を目的としたプリント回路レイアウトの提案

アプリケーションでは、各トランスに高電圧の要 件を課しています。これは、同じツイスト・ペア の電位とフロートのセル・スタックの任意の電圧 とのインタフェースをとる必要があるからです。

絶縁を追加するためにCMCとACカップリング・ コンデンサを使用することは、前述の回路と同様 ですが、ネットワーク内の物理的な位置とは無関 係に、通信デバイスの反射強度を低減し、一貫 した波形を提供するために、少し異なる結合回 路を提案します。3つの異なる点があります。

- LTC6820の終端を100pFコンデンサ(C<sub>T</sub>) に変更する。

- ・遠い側の終端のみを通電バス(R<sub>T</sub>)に適用し、 68Ωに設定する(いずれのLTC6804-2でも 終端なし)。

- 浮遊容量負荷をデカップリングするために、 すべてのバス接続に22Ωのカップリング抵抗 (R<sub>c</sub>)を使用する。

これらを図8の回路に示します。繰り返します が、この回路では、LTC6820が安全な接地電 位で動作することを前提にしています。変更され た波形は反射からの歪みを制御するために帯域 が制限されているので、ICピンで受信するパル スは図9に示すように丸くなっています。しかし、 isoSPIのパルス識別回路がこのフィルタ処理さ れた形状に良好に機能し、16個すべてのアドレ スをもつバスをサポートします。最適な動作を得 るためには、システム内で発生する実際の損失 に合わせて、パルス検出しきい値を下げる必要 がある場合があります(しきい値を作動信号の ピーク値の40%~50%に設定する)。

アドレスが5個以下のネットワークでは、反射は 通常大きな問題ではないため、標準の抵抗をも つ終端を保持できます(図8のC<sub>TERM</sub>とR<sub>TERM</sub> の位置に $100\Omega$ の抵抗があり、 $R_c$ を省略する)。

#### まとめ

高電圧isoSPIシステムのコストへの影響を緩和 するために、ACカップリング方法を使用して、 磁気部品の2倍の絶縁要件を解消します。特殊 トロイダル・トランスの磁気部品を低コストのボ ビン巻同相チョーク(CMC)部品に置き換える ことで、コストをさらに削減できます。コンデンサ とCMCは両方とも、比較的低プロファイルの 表面実装チップ部品であり、価格競争が激しく、 信頼性の高い車載用に承認された部品が使用 できます。ACカップリング用のバイアス抵抗は、 システムの絶縁の保全性を監視する有効な手段 です。