# O-RANを採用した ワイヤレス・ソリューション のための5G対応デバイス

著者: Brad Brannon、システム・エンジニア

### 概要

O-RANとは、オープンな無線アクセス・ネットワークを実現 するための仕様です。その背景には、3GPP (3rd Generation Partnership Project) が掲げる5G関連の目標があります<sup>1</sup>。 その達成に向けて、ワイヤレス・コミュニティを変革し、ワイ ヤレス装置の新たな構築スタイルを導入して、イノベーション を実現するための触媒としてO-RANは策定されました。高い 費用対効果を実現しつつ成功に結び付けるには、オープン・ ソース化された無線装置や最適化された5G対応デバイスを利 用できるようにする必要があります。本稿では、電力効率に優 れたソリューションを設計/構築するための方法を紹介します。

#### 5Gが抱える課題

無線技術者やネットワーク技術者は、5Gに関連して掲げられて いる目標を達成するために複数の手法を取り入れています。例 えば、データ・サービスをネットワークのエッジに移したり、 Massive MIMOとスモール・セルを活用したりすることで、 通信容量とスループットの両方を高めるといった具合です。 Massive MIMOでは、アレイ状に配置された多数のアンテナを 使用します。それにより、通信容量を増加させるだけでなく、中 央のロケーションにとってのカバレッジの拡大に貢献します。ま た、従来のマクロセルと同様に、中央のロケーションを中心とし て比較的広い範囲をカバーします。但し、Massive MIMOでは、 2.6GHz以上といったより高い周波数を使用します。そのため、 電波がうまく建物を通過することができません。そこで、到達が 難しい屋外のエリアや屋内をカバーするためにスモール・セルが 使用されます。一般家庭や企業の施設、商業施設、競技場など、 屋内外には、果たしてどれだけ多くのエリアが存在するのでしょ うか。そのように考えれば、5Gを成功に導くには、スモール・ セルの活用が不可欠であることがわかります。ただ、このことは、 1つのネットワークに膨大な数のスモール・セルが含まれるとい うことを意味します。また、多様な配備方法も用意しなければな りません。そのため、そうした設備を低コストで導入/運用でき るか否かが成功の鍵を握ることになります。

#### 利用可能な技術

ここ数年の間に、5G向けのソリューションを実現する方向で様々 な技術が進化しました。まず、ベースバンドの領域では、引き 続きムーアの法則に従ってゲートあたりのコストが低下していま す。それだけでなく、より複雑な機能を無線技術に組み込めるよ うになっています。現在では、デジタル・プリディストーション (DPD: Digital Predistortion) のような機能を含む制御アルゴ リズムの多くを、無線システムに直接組み込むことができます。 新世代の無線の利用が進めば、それ以外にも多くの可能性が生ま

もう1つ、強力な動きを見せているのがO-RAN<sup>2</sup>などの業界団体 です。そうした団体は、スケール・メリットを活かしてコストの 低減を実現しようとしています。また、サプライ・チェーンのセ キュリティを高め、ワイヤレス・ネットワークによる新たなマネ タイズの方法を提供することを目指して、ワイヤレス業界全体で 連携して取り組みを進めています。稿末に示した参考資料3には、 「O-RAN Allianceは要件を明確に定義し、目標の達成に必要なエ コシステム/サプライ・チェーンの構築を支援するために、事業 者によって設立されました。O-RAN Allianceは、目標の達成に 向けて(オープン化とインテリジェンス化という原則の)具現化 に取り組みます」と記されています。同アライアンスは、3GPP の仕様に対応する物理インターフェースの定義を行っています。 それにより、業界全体で相互運用が可能なホワイト・ボックス・ ソリューションとしてそのインターフェースを標準化/実装でき るようにすることに焦点を絞って活動を行っています。また、同 アライアンスは、ハードウェアに関する要件の定義や、O-CU/ O-DU/O-RU (O-RANの定義に基づく、オープンな集約ユニット、 オープンな分散ユニット、オープンな無線ユニット)のリファレ ンス設計の提供も行っています。そうしたすべての活動によって、 フロントホールとベースバンド・プロセッサの標準化が可能にな り、ソリューションの更なるコスト低減を実現しようとしていま す。それらに、無線ICをはじめとする5G対応のICを組み合わせ ることで、スモール・セルのあるべき姿が定まり、標準規格に対 応する実装が可能になります。このような業界団体の取り組みは 非常に重要です。

加えて、ここ数年の間に無線技術も急速に進化しました。現在 では、3GPPが38.104仕様や稿末の参考資料1の中で定めてい る性能の要件を満たす無線技術が複数の形態で提供されていま す。そうした技術は高度に統合された状態で製品化されており、 アナログ部品やRF部品だけでなく、DPD、CFR (Crest Factor Reduction) といった重要なアルゴリズムも備えています。そう したデバイスはCMOSの微細プロセスで製造されますが、RFフ ロント・エンドについても技術の進化が見てとれます。低コスト のRF向けプロセス (SiGe、SOI、GaN、GaAsなど) によって、 上記の標準規格で定められた要件を満たす集積度の高いLNA(低 ノイズ・アンプ)や大出力/高性能のPA(パワー・アンプ)が 実現されています。

もう1つ、大きな進化を遂げているのが、集積度が高く効率的な パワー・ソリューションです。そうしたソリューションは、サイ ズを抑えて電力を供給できるPoE (Power over Ethernet) や、 標準的なパワー・デバイス、監視機能、保護機能などに対応して います。無線環境において非常に高い効率やノイズ性能を実現し つつ、PAなどの主要なデバイスを保護するためのオプションも 備えているということです。

これらの技術を組み合わせることによって、高性能/低コストの スモール・セル向けプラットフォームを実現できます。そうした プラットフォームは、小電力/大電力のシステムの両方に対応で きるので、通信事業者のネットワーク全体にわたって効率的に配 備することが可能です。

## システムの概要

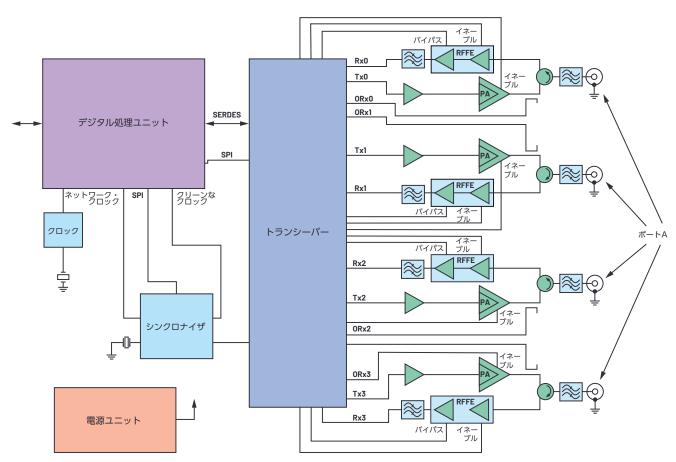

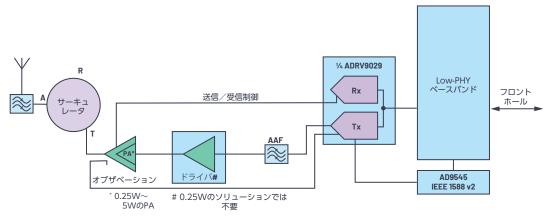

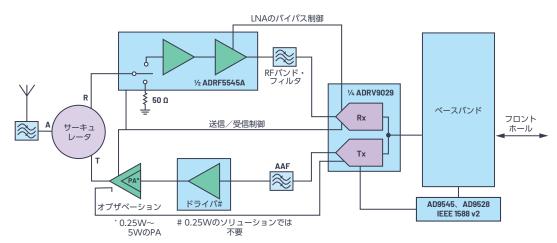

図1は、5Gに対応するスモール・セルのブロック図です。ここ では、4T4R(4つのトランスミッタ、4つのレシーバー)という 標準的な構成を例にとっています。実際には、2T2Rの構成をと ることもできますし、24dBm以上の電力クラスに対応すること も可能です。以下では、この図を基に、オープンな無線ユニット (O-RU) で扱う様々な帯域や電力レベルに応じて簡単にスケーリ ングできる5G対応デバイスについて説明します。

図 1. スモール・セルのブロック図

## 無線の主要な要素

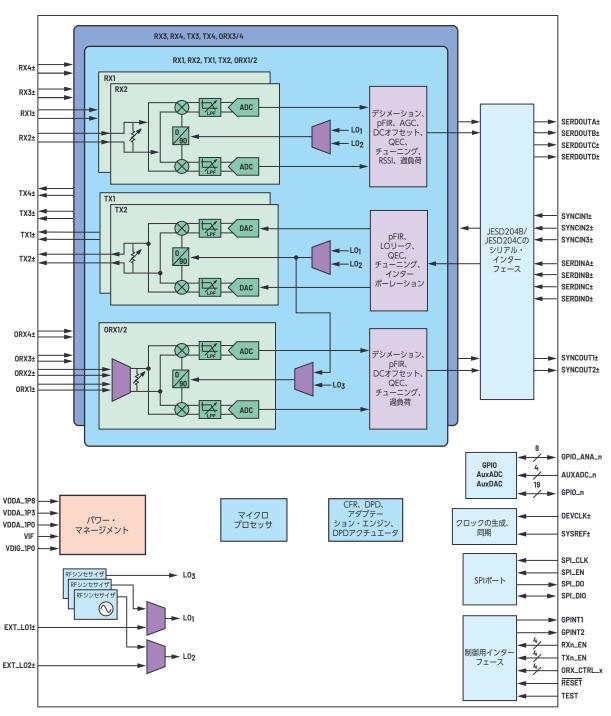

ここ10年の間に、トランシーバーICは高性能なプラット フォームへと進化しました。例えば、アナログ・デバイセズの RadioVerse<sup>TM</sup>ファミリには、最高200MHzの占有帯域幅をサ ポートし、DPDなどの高度な機能を搭載するものなど、多様な トランシーバーICが含まれています。また、この製品ファミリは、 5Gに対応するデバイスに求められるニーズを満たすだけではあ りません。これまでどおり、LTEやマルチキャリアGSM (Global System for Mobile Communications)の要件にも対応します。 このような製品については、絶えず新世代品が開発されています。 その最新製品の1つが、4T4R構成の「ADRV9029」です(図2)。 これ以外にも、DPDを搭載するものや搭載しないもの、2T2Rの 構成のものなど、多様な製品が提供されています。

図 2. ADRV9029のブロック図

各RadioVerse製品には、LNAとPAを除き、無線システム全体 を構築するために必要なあらゆるものが含まれています。例え ば、送受信に必要なすべての回路、シンセサイザ、クロックなど を網羅しています。また、AGC(自動利得制御)とゲイン制御ア ンプの実行に必要なステート・マシン、VGA(可変ゲイン・アン プ)も内蔵しています。RadioVerse製品は、最高6GHzの広い 帯域に対応します。LNAとPAについては、そのような仕様に対 応する高性能品は存在せず、必要な帯域または周波数範囲に応じ て適切な製品を選択しなければなりません。そのため、システム を完成させるためには、RadioVerse製品とLNA/PAを組み合わ せる必要があります。以下では、5G NR (New Radio) に対応 するスモール・セルの設計において送受信に使用するシグナル・ チェーンについて説明します。また、その構成要素となるデバイ スの選択に関する知見を提供します。

## レシーバーのシグナル・チェーン

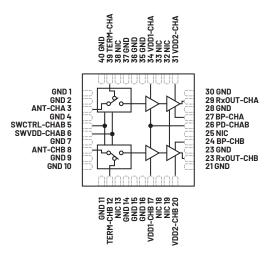

ADRV9029とレシーバー用のフロント・エンド・モジュール 「ADRF5545A」(図3)を組み合わせれば、それら2つのICだけ でほぼレシーバーを構築できることになります。ADRF5545Aの 代わりに、ピン互換の「ADRF5515」を使用することも可能です。 わずかな数の受動部品を追加することにより、図4のようなシグ ナル・チェーンを構成できます。結果として、非常にコンパクト で高性能なレシーバーが実現されます。このアーキテクチャがも たらす最大のメリットは、高い集積度によって得られます。すな わち、非常に少ないコストで実装できるだけでなく、消費電力も 最小限に抑えられます<sup>4</sup>。

RadioVerseファミリのアーキテクチャによって、従来のレシー バーの設計に必要だった多くの要素を排除することが可能になり ます。一部のRF信号を増幅/フィルタリングするためのコンポー ネントに加え、チャンネル・フィルタ(アナログ、デジタル)や ベースバンド・アンプなど、多くの無線機能が不要になるのです。 一般に、それらはシステムの中でサイズと消費電力が最も大きい 要素だと言えます。そのため、ダイレクトRFサンプリングなど のアーキテクチャを採用する場合と比べて、占有面積と消費電力 が大幅に削減されます。

#### ADRF5545A

図3. ADRF5545Aの内部構造。TDDに対応する デュアルチャンネルのレシーバー用フロント・エンドです。

図4に示すように、このスモール・セル用のレシーバーは、主 にTDD (Time Division Duplex) 向けのサーキュレータ、 ADRF5545A、SAW/BAW(表面弾性波/バルク弾性波)フィ ルタまたはモノブロック・フィルタ、バラン、トランシーバーか ら成ります。ADRV9029をはじめとするRadioVerse製品は、 ノイズ性能が高く、入力1dB圧縮ポイントが小さいので、アン プやVGAを追加する必要はありません。このシグナル・チェー ンを使用すれば、アンテナからビットまで(RF信号からデジタ ル・データまで)に至るシステム全体のノイズ指数 (NF: Noise Figure)を2dBにまでに抑えることができます。この設計では、 ADRF5545Aという集積型のRFフロント・エンド・モジュール (FEM)を採用しています。ただ、ディスクリート構成の回路を 採用することによってメリットが得られる設計も少なくありませ ん。FEMでは高い集積度が得られるわけですが、それと引き換え に、アンテナ用のフィルタの要件がやや厳しくなるというトレー ドオフがあるからです。それでも、Massive MIMOやその他の TDDシステムなどを設計する際には、集積度の高いソリューショ ンは魅力的な選択肢になります。一般に、ディスクリート構成の フロント・エンドは、FDD (Frequency Division Duplex) シス テムの設計に適しています。

図4. レシーバーのシグナル・チェーンの構成要素

ここで、LNAまでの損失が約0.5dB、バンド・フィルタにおける 損失が1dBであると仮定しましょう。そうすると、2つのアクティ ブ・デバイスのデータシートに記載された値から、レシーバー のシグナル・チェーン全体の公称NFは約2dBになるはずです。 信号/ノイズ + 歪み (SINAD) がMCS-4と同じくOdBである と仮定すると、5GのG-FR1-A1-1の搬送波(約5MHz)に対す るリファレンスの感度は約-104.3dBmとなります。これだけの 感度があれば、38.104のセクション7.2.2に定められているワ イド・エリアの伝導要件も、マージンを十分に確保して満たすこ とができます。ここで、表1をご覧ください。同じ条件下でロー カル・エリア/スモール・セルの設計に求められる感度は-93.7 dBmです。こちらに対しては、十分すぎるほどの余裕がありま す。性能が高くない一部のスモール・セル・アプリケーションに 対しては、「GRF2093」(Guerrilla RF製) といった1段構成の LNAとSAWフィルタを組み合わせることで対応できる可能性も あります。

表 1. 38.104 におけるレシーバーの分類

|                    | ワイド・エリア<br>(dBm) | ミッドレンジ<br>(dBm) | ローカル・エリア<br>(dBm) |

|--------------------|------------------|-----------------|-------------------|

| 5MHz<br>BW/15kHz   | -101.7           | -96.7           | -93.7             |

| 20MHz<br>BW/15kHz  | -95.3            | -90.3           | -87.3             |

| 50MHz<br>BW/30kHz  | -95.6            | -90.6           | -87.6             |

| 100MHz<br>BW/30kHz | -95.6            | -90.6           | -87.6             |

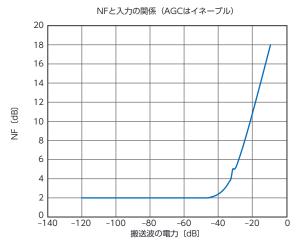

また、38.104のセクション7.4.1では、(ワイド・エリアにおい て)-52dBmの干渉信号の下で、レシーバーの感度の低下を6dB 以下に抑えるACS (Adjacent Channel Selectivity) ブロッキ ング性能を求めています。図5に示したNFと入力レベルの関係 から、-52dBmにおいては、それよりも低いレベルと比べてノイ ズはほとんど増加しません。実際、ノイズ・フロアは-40dBmの 手前まで上昇していないことが見てとれます。ACSの要件として -44dBmが求められるローカル・エリアに対しても理想的です。

一般的なブロッキングの要件(7.4.2)としては、(ローカル・エ リアにおいて)-35dBmの干渉信号を、±7.5MHzのオフセット で帯域内のレシーバーに印加した場合に、感度の低下を6dB以 下に抑えることが求められます。図5に示したように、アナログ・ デバイセズの製品で構成したシグナル・チェーンでは、感度は約 0.9dBしか低下しません。挟帯域のブロッキングは、やや電力の 小さいCWに似たスティミュラスになりますが、それについても 問題はありません。

図5. レシーバーにおける NF と入力レベルの関係

更に興味深い課題は、セクション7.5.2の帯域外ブロッキングで す。ここでは、-15dBmの干渉信号がアンテナの入力に印加され るケースを想定します。動作帯域幅が200MHz未満のスモール・ セルの場合、この信号とその帯域端との周波数の差は、最も近 い場合で20MHzとなります。このテストでは、動作周波数から 20MHz以内の帯域を除いて、1MHz~12.75GHzの掃引を実施 することが求められます。このような条件に対し、図4のシグナ ル・チェーンには有利な点が複数存在します。

まず、サーキュレータの帯域幅が有限であり、帯域外の信号の 多くが除去されるということが挙げられます。但し、動作帯域 に近い信号に対しては大きな効果は働きません。もう1つは、 ADRF5545Aの後段のフィルタによって、いくらかのフィルタリ ングが行われることです。一般的には、20MHzの帯域外信号に 対して、約20dBの除去性能が得られます。更に、アナログ・デ バイセズのトランシーバー・ファミリは、そのアーキテクチャに 固有で、なおかつ非常に有効な独自機能として、帯域外成分の除 去機能を内蔵しています。アプリケーション・ノート [AN-1354] の図20を見れば、その本質的な帯域外除去性能を確認できます。 具体的には、感度の低下については、通過帯域からどちらの方向 に周波数を掃引しても、より大きな信号を許容できることがわか ります。帯域端の近くでは、6dBの感度の低下に対して約10dB に対応できます。それ以上離れると、内蔵するフィルタによって 帯域外の信号が大きく減衰します。その信号は、帯域内に折り返 す (エイリアス) ことなく、オンチップのフィルタと外付けのフィ ルタによってほぼ減衰されます。

シグナル・チェーン全体で見ると、20MHzの除外帯域までは、 -15dBmの帯域外信号が約-40dBm~-45dBmに抑えられます。 それ以上離れた場合には、除去性能は更に高くなるでしょう。図 5から、このレベルであれば、感度はほとんど低下しないと考え られます。

おそらく、より大きな問題になるのはFEMの直線性です。この レベルでは、3次相互変調歪み (IM3) がかなり大きくなると予 想されます。使用するFEMによっては、帯域選択フィルタを2つ 目のLNAの前に移動し、一般的に大きな相互変調歪みを生成す る帯域外信号から保護することが望ましいかもしれません。一方、 ここで採用しているタイプのFEMでは、2つの段の間にフィルタ を配置するのは不可能です。そのため、代替策を講じることにな ります。

図3に示したように、標準的なFEMには、2段目のLNAをバイ パスするためのスイッチが用意されています。これは、帯域外に 大きな干渉信号が存在する場合に、相互変調歪みの影響を抑え るために使われます。ゲインを抑えることで、2段目のLNAが、 非直線性が増す方向に駆動されないように保護するということで す。LNAのゲインの切り替えによって、シグナル・チェーンのS/ N比は1dB低下します。しかし、大きな干渉信号によって引き起 こされる相互変調歪みを抑えることにより、全体的なダイナミッ ク・レンジは維持されます。つまり、ノイズ性能の損失を上回る 効果が得られるということです。それによってワーストケースの NFは約5.7dBとなりますが、それでもまだローカル・エリア(ス モール・セル)におけるリファレンスの感度の要件の範囲内に収 まります。それ以外のフィルタリングの要件には、アンテナ部の フィルタによって対応します。干渉信号の除去性能は、レシー バー用のFEMのゲイン圧縮ポイントと3次インターセプト・ポイ ントによって決まります。

#### トランスミッタのシグナル・チェーン

ADRV9029に、RF対応の適切なドライバ(駆動アンプ)または VGA (選択肢については analog.com/jp/rf を参照) と適切な PAを組み合わせれば、屋内向けのピコセル、屋外向けのピコセ ル、屋外向けのマイクロセルを簡単に構築できます<sup>5</sup>。それらに 加え、わずかな数の受動部品を使用するだけで、非常にコンパク トで効率的なトランスミッタを構成することが可能です。そのシ グナル・チェーンは図6のようになります。このアーキテクチャ の最大のメリットは、高い集積度が実現されていることです。言 い換えれば、非常に低いコストで実装できます。また、アナログ・ デバイセズの一部のトランシーバー製品が備えるDPD機能を活 用すれば、消費電力も最小限に抑えることが可能です。

図6に示したスモール・セル向けのトランスミッタは、主にサー キュレータ、PA、フィルタ、トランシーバーで構成されていま す。また、PAの出力部にカプラを付加しています。このカプラ は、出力の歪みのモニタリングに使用します(アンテナのVSWR [電圧定在波比] とフォワード電力のモニタリングにも使用でき ます)。これをDPDと組み合わせて使用すれば、送信機能の動 作効率とスプリアス性能を向上させることが可能です。外付けの DPD機能(FPGAなど)も利用できますが、アナログ・デバイセ ズのトランシーバーが備えるDPD機能を使用する場合、同機能 を動作させても消費電力は最大で350mWしか増加しません。 なお、消費電力の増加量は、PAに必要な補正量に依存します。 低消費電力のPAを選択した場合、必要な補正量も小さく抑えら れるので、DPD機能による消費電力も少なくなります。また、 DPD機能を内蔵している場合、オブザベーション・レシーバー のSERDES (Serializer/Deserializer) のレーンが完全に不要に なります。そのため、SERDESのレーン数は、外付けのベースバ ンドICを使用する場合の半分になります。加えて、DPDの帯域 幅の拡張が完全にトランシーバー内で処理されるので、トラン シーバーのペイロードが低減されます。仮に、同等のDPD機能 をFPGAに実装したとすると、消費電力は約10倍になります。 つまり、その方法は、低消費電力であることが求められるスモー ル・セルやMassive MIMOに対しては、電力効率が低くすぎて 適切ではありません。一方、トランシーバーが内蔵するDPD機 能であれば、非常に少ない消費電力でコスト効率良くスモール・ セルに適用することができます。つまり、効率の面でメリットが あることに加え、外付けのコンポーネントに大きな演算負荷をか けることなく、送信側の直線性を高めることができます。

図6. トランスミッタのシグナル・チェーンの構成要素

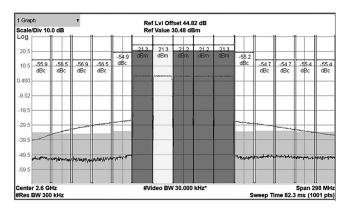

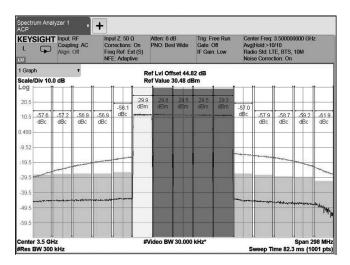

図7、図8は、消費電力が少ないスモール・セルと中程度のスモー ル・セルの評価結果です。アナログ・デバイセズのトランシーバー が内蔵するDPD機能をアプリケーションに適用した場合の例を 表しています。ご覧のように、5つの隣接する20MHzのLTE搬 送波(合計100MHz)に対するスティミュラスが示されていま す。一般に、LTEでは最小45dBのACLR(Adjacent Channel Leakage Ratio:隣接チャンネル漏洩電力比)が必要になります。 実際、多くの実装ではそれ以上の性能が求められます。アナロ グ・デバイセズのテスト用の施設では、あらゆる電力クラスの新 たなPAの試験が常に行われています。アナログ・デバイセズが 提供するDPD技術の最新情報とPA製品の最新のリストについて は、「Power Amplifier Test Report」をご覧ください。

図7. DPDあり/なしの場合のPAのスペクトル (合計RFは26dBm)

図8. DPDあり/なしの場合のPAのスペクトル (合計RFは37dBm)

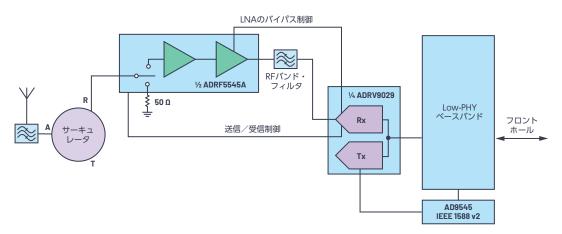

#### 全体の構成

図9に示したのは、シグナル・チェーンの全体像です。この図に は、送信/受信制御に必要な信号の一部が含まれています。そ れらの信号は、電力効率を高めるために、TDD方式に対応して アンプをそれぞれのサイクルで有効/無効にするために使用し ます。また、この回路をFDD方式で使用する場合には、未使用 のスロットの電源をオフにすることで消費電力を削減できます。 LNAには、送信電力がコア・アンプの入力ではなく終端に返って くることを防ぐための入力スイッチが必要です。そうした様々な 信号を、ASIC、FPGA、トランシーバーなどによって生成し、制 御を実現します。

図9. トランシーバーのシグナル・チェーンの全体像

レシーバーのシグナル・チェーンには、アナログ信号のゲインの 低下に応じてデジタル・データのストリームに変更を加える機能 が含まれています。それにより、Low-PHYを経て下流のベース バンドに引き渡される信号の絶対レベルが維持されます。

ここで示したアプリケーションは、シングル・バンドに対応する ものです。トランシーバーは広帯域に対応しており、6GHzまで のあらゆる周波数を使用できます。しかし、シグナル・チェーン を構成するすべてのデバイスがそのような特質を備えているわけ ではありません。前述したように、LNAやPAなどのデバイスは、 一般的に対応可能な帯域が限定されており、使用する帯域に基 づいて製品の選定を行う必要があります。通常は、ピン互換の複 数の製品によって6GHz以下の一般的な帯域全体が網羅されてお り、簡単に置換できるようになっています。つまり、5Gの帯域 やO-RANで提案されている帯域を含めて、TDD/FDDの一般的 な帯域全体がサポートされています。

## クロック・ツリー

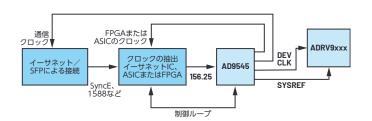

クロック・ツリーについては、システムに応じて複数の異なる構 成を適用できます。タイミングの正確なアライメントが求められ る場合には、2段構成のクロック合成が必要になります。最初の 段は、無線信号をデジタル化する際のタイミング調整を正確に行 うASIC、FPGA、またはコントローラを介してベースバンド・ブ ロックに接続しなければなりません。本稿のアプリケーション例 では、フロントホールまたはローカルのGPSレシーバーから供給 されるPTP (Precision Time Protocol) 情報の処理が必要にな ります。それによって、無線システムとベースバンド・プロセッ サは、無線フレームがいつ処理されるべきなのかを正確に把握し ます。

「AD9545」は、メイン・クロックの周波数、位相、時間を、無 線システムに対応させて正確に調整する処理に最適な製品です。 この製品ファミリは、リファレンスを使用することなく一時的 に動作するように構成することができます。この使い方には、 TCXO (Temperature Compensated Crystal Oscillator:温 度補償水晶発振器)またはOCXO (Oven Controlled Crystal Oscillator: 恒温槽付水晶発振器)を併用する場合、リファレン ス・クロックに障害や中断が生じても精度を維持できるというメ リットがあります。

タイミングのアライメントに高い精度が求められない構成、 または正確なアライメントが必要な構成の2つ目の段には、ク ロック分配デバイスが必要です。同デバイスの役割は、無線 システム全体で使用する一連のクロックを生成することです。 それには、JESD204、eCPRI (Enhanced Common Public Radio Interface)、イーサネット、SFP (Small Form-factor Pluggable) や、無線システム全体にわたるその他の主要な信号 に必要なクロックが含まれます。「AD9528」は、最大14の異な るレートに対応して低ジッタのクロックを供給可能なクロック・ ジェネレータです。JESD204B/JESD204Cのデバイス・クロッ クやSYSREF信号などをサポートします。

2段構成のクロック回路のブロック図を図10に示しました。 タイミングについて高い精度のアライメントが求められないア プリケーションについては、AD9545を削除/バイパスし、 AD9528だけで対応しても構いません。システムに対する入力ク ロックは、ネットワークの基本的なタイミングに基づき、イーサ ネット機能を実現するブロックまたはFPGA内(アーキテクチャ によって異なります)のベースバンド/ネットワーク機能によっ て再生されます。無線システムの具体的な要件に応じ、これ以外 にも多くの構成が可能です。図10に示したのは、代表的な構成 例にすぎません。

図10. クロック・ツリーの例

#### 消費電力

消費電力には多くの要素が寄与します。例えば、選択するFPGA や実装する機能、使用するトランシーバー、有効にするオプショ ン、必要なクロック・ツリー、生成されるRF電力などによって 消費電力は決まります。

標準的なミッドレンジのFPGA (SoC) に、O-RANのCUS-Plane/M-Planeの処理とIEEE 1588 v2 PTPのスタックの同期 処理を実装したとします。その場合の消費電力は約15Wです。 TDD/FDDのうちどちらかの方式を採用してADRV9029を動作 させた場合、消費電力は、どのようなDFE機能をイネーブルに するかによって、5W~8Wの範囲で変動します。システムの消 費電力については、これにクロッキング、レシーバー、トランス ミッタ、その他の消費電力を加算する必要があります。表2に示 したのは、トランスミッタ側のシグナル・チェーンを除いたシス テムの消費電力の例です。トランスミッタのシグナル・チェーン の消費電力は、出力電力のクラスに応じて大きく異なります。

表 2. 消費電力の概算

| デバイス                  | 必要な個数 | TDD、70:30の標準的な<br>消費電力(4T4R) |

|-----------------------|-------|------------------------------|

| ミッドレンジの<br>FPGA (SoC) | 1     | 約15W                         |

| ADRV9xxx              | 1     | 約5W                          |

| ADRF5545A             | 2     | 0.6 W                        |

| AD9545                | 1     | 0.7 W                        |

| AD9528                | 1     | 1.4 W                        |

| PA用のドライバ              | 4     | 1.2 W                        |

| その他                   | 1     | 2 W                          |

| 合計                    | 14    | 26W~29W                      |

この無線システムにおいて、Tx:Rxのデューティ・サイクルが 70:30であったとします。そのトータルの消費電力は、(正確 な構成によって異なりますが)PAに伴う電力を除くと26W~ 29Wとなります。表3には、PAの消費電力の例を示しました。 クラスABの一部のPAは、主にトランジスタの線形領域で動作 します。そのため、効率は20%~50%になると考えられます。 ここで大きな効果を発揮するのが、トランシーバーICが内蔵する DPD機能です。帯域幅が狭く消費電力の少ないPAであっても、 DPDを利用すれば効率を高めることが可能です。DPDによって 数十mWの電力が消費されますが、それを十分に相殺できるだ けのメリットが得られます。

## 表3. PAの消費電力

| デバイス                   | 必要な個数 | TDD、70:30の標準的な<br>消費電力(4T4R) |

|------------------------|-------|------------------------------|

| PA (アンテナあたり<br>+24dBm) | 4     | 約2.5W                        |

| PA (アンテナあたり<br>+37dBm) | 4     | 約47W                         |

低消費電力のスモール・セルの場合、約2.5Wの消費電力が追加 されると、トータルの消費電力は約30Wに達します。しかし、 PoEソリューションによって給電される受動冷却式の屋内向けス モール・セルにとっては問題のない数値です。

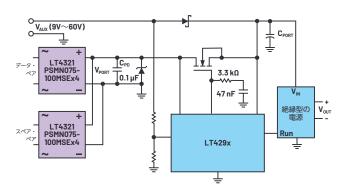

PoEソリューションの1つの実装例を図11に示しました。この ソリューションでは、ブリッジ・コントローラ [LT4321] を使 用しています。同ICを使えば、整流器の代わりにMOSトランジ スタを理想ダイオードとして使用することが可能になります。そ の結果、効率が大幅に改善されます。LT4321の後段には、IEEE 802.3bt に準拠する PD (受電装置) インターフェース [LT4295] を配置しています。同ICの後段には、ここまでに示した消費電力 の要件を満たすローカルのレギュレータを配置します。必要に応 じて、最大90W超の電力を供給することになります。

図11. スモール・セル向けのPoEソリューション。 絶縁型電源を採用しています。

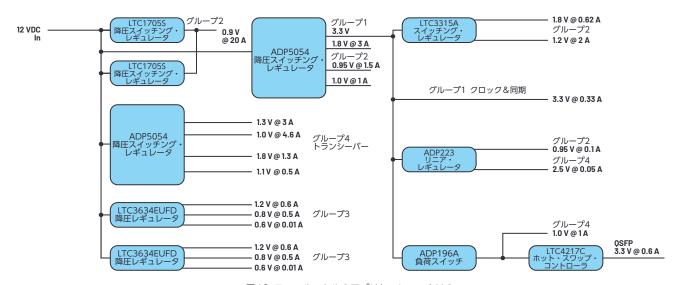

PoE向けの変換デバイス以外にも、スモール・セルのリファ レンス設計に使用できる製品は数多く存在します。例えば、 「ADP5054」ファミリは、アナログ・デバイセズ製のトランシー バーへの給電を対象として特別に設計された統合型の電源ICで す。それ以外にも、多くの降圧コンバータや低ノイズのLDO(低 ドロップアウト) レギュレータを提供しています (図12)。

#### オプション

本稿で紹介した無線アーキテクチャには、柔軟性が高いという長 所があります。つまり、様々な市場の要件に対応できるというこ とです。このアーキテクチャは、FDDとTDDの両方を含む様々 なアプリケーションに対して最適化されています。ロー・バン ド、ミッド・バンド、ハイ・バンドに対して同等に優れた性能を 示し、スモール・セルにもMassive MIMOにも対応できるプラッ トフォームとして利用できます。また、トランスミッタとレシー バーの両方の回路において、様々なトレードオフにより、コスト、 サイズ、重量、消費電力を最適化できます。本稿では、性能と集 積度の高さに焦点を絞って解説を行いました。しかし、少し異な る選択によってコストを削減するといった、シンプルなトレード オフを行うことも可能です。

図12. スモール・セルのアプリケーション向けの 標準的なパワー・ツリー

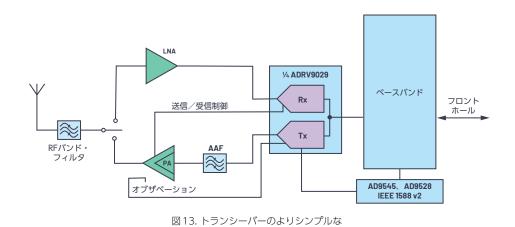

例えば、一部の低消費電力のPAについてはドライバは必要なく、 削除しても構わないはずです。また、スモール・セルのアプリケー ションの多くは、小さなRF電力しか扱いません。そのため、サー キュレータをシンプルなTRスイッチに置き換えられる可能性が あります。更に、ローカル・エリアにおける性能だけが求められ る場合には、2段のLNAをシンプルな1段のLNAに置き換える ことが可能です。そうすれば、良好な無線性能を提供しつつ、コ ストを抑えることができます(図13)。それ以外にも、広範な周 波数と電力に関するオプションを様々に組み合わせることで、多 様なケースに対応することが可能になります。

#### まとめ

本稿で紹介した5G対応のデバイスは、通信アプリケーションを 対象として提供されています。特に、O-RANのO-RUに適した 低コストの実装を可能にします。具体的には、RadioVerseファ ミリの製品や、RFアンプ、クロックの再生/同期、PoE、POL (Point of Load) レギュレータなどを紹介しました。このような 集積度の高いデバイスを組み合わせることで、5Gに対応するス モール・セル、マクロセル、マイクロセル、Massive MIMOな どのアプリケーションを実現できます。

FPGA、eASIC (ストラクチャードASIC)、ASICで提供される適 切な物理層とソフトウェアを組み合わせることにより、O-RU向 けのソリューションを開発することができます(図14)。このソ リューションは、Intel®、Comcores、Whizz Systems との連携 によって開発しました。

こうしたソリューションは、RF特性に関する要件だけでなく、高 性能なO-RANプラットフォームを配備するために必要なコスト や消費電力の要件も満たします。

シグナル・チェーン

図14.5G向けのプロトタイピング用プラットフォーム。 帯域の変更が可能なRFフロント・エンドを採用しています。

## 参考資料

<sup>1</sup> ftp://ftp.3gpp.org/specs/latest/Rel-15/38\_series/

<sup>2</sup> O-RAN Alliance

<sup>3</sup> [O-RAN: Towards an Open and Smart RAN (O-RAN: オー プンでスマートなRANを目指す)」O-RAN Alliance、2018年 10月

<sup>4</sup> Brad Brannon 「ゼロIFアーキテクチャがもたらすメリット、 実装面積は50%に、コストは1/3に Analog Dialogue、Vol. 50、No. 3、2016年9月

#### 著者について

Brad Brannon (brad.brannon@analog.com) は、アナ ログ・デバイセズのシステム・エンジニアです。ノースカ ロライナ州立大学を卒業後、37年間にわたり、設計、テス ト、アプリケーション開発、システム・エンジニアリング を担当してきました。現在は、O-RANに対応するリファレ ンス設計の開発、それを利用する顧客のサポートに従事。 A/DコンバータやD/Aコンバータのクロック処理、無線設 計、ADCのテストなどに関する記事やアプリケーション・ ノートの執筆も担当しています。

# EngineerZone® オンライン・サポート・コミュニティ

アナログ・デバイセズのオンライン・サポート・コミュ ニティに参加すれば、各種の分野を専門とする技術者と の連携を図ることができます。難易度の高い設計上の問 題について問い合わせを行ったり、FAQを参照したり、 ディスカッションに参加したりすることが可能です。

SUPPORT COMMUNITY

Visit ez.analog.com

VISIT ANALOG.COM/JP

<sup>&</sup>lt;sup>5</sup> Specifications (仕様)、O-RAN Alliance

<sup>\*</sup>英語版技術記事はこちらよりご覧いただけます。