### MAX98388/MAX98389

#### 概要

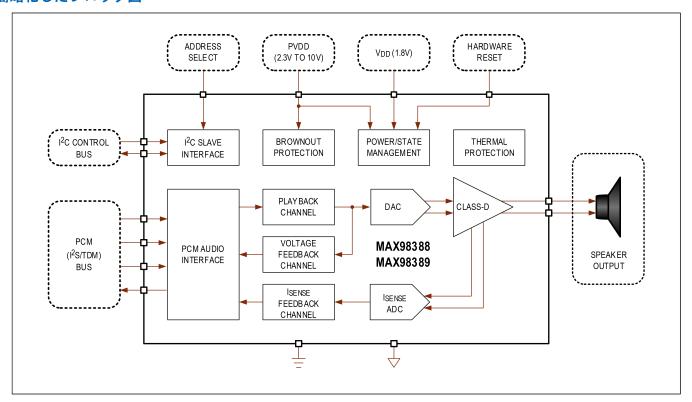

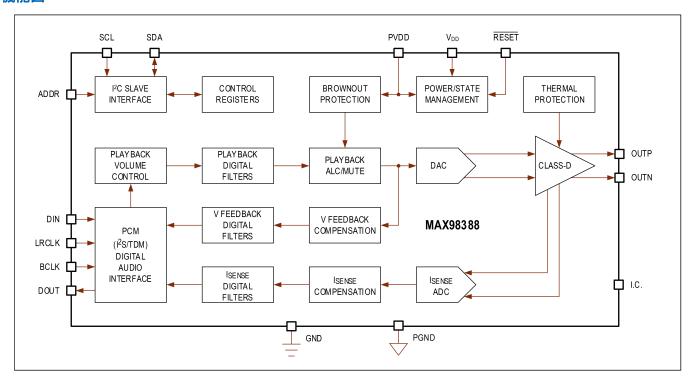

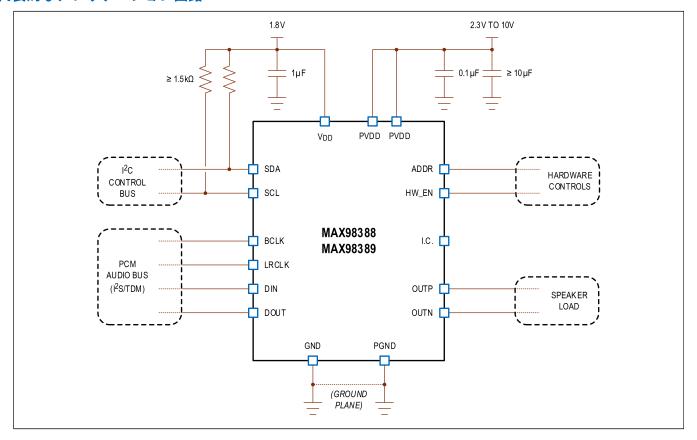

MAX98388/MAX98389 は、IV 帰還を内蔵した小型でコスト効率 に優れたモノラル・デジタル入力アンプです。本デバイスは、 2.3V~10V の広い電源電圧範囲で動作します。この電源範囲で は、両バージョンとも1セル、2セル、外部レギュレーション/ ブースト型のポータブル・アプリケーションをサポートしてい ます。MAX98388 は最大 5.5V のアプリケーション (1 セル)、 MAX98389 は 5V~10V のアプリケーション (2 セル) に最適化 されています。

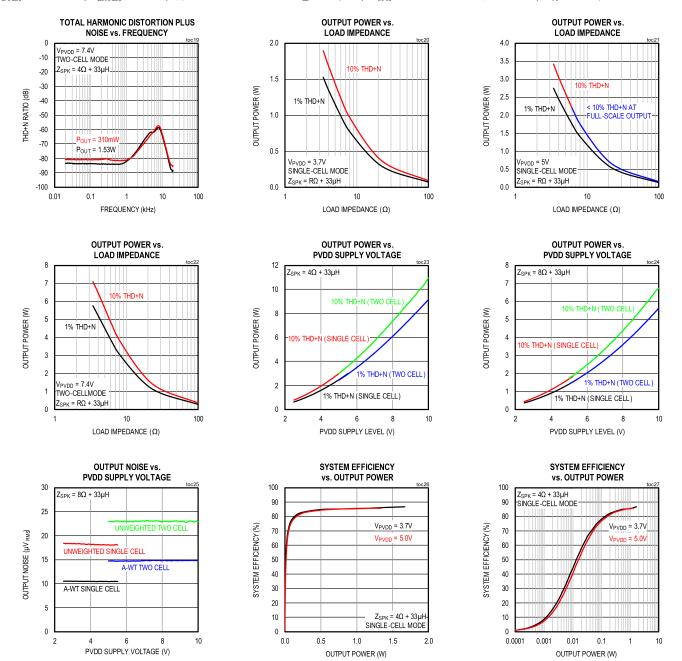

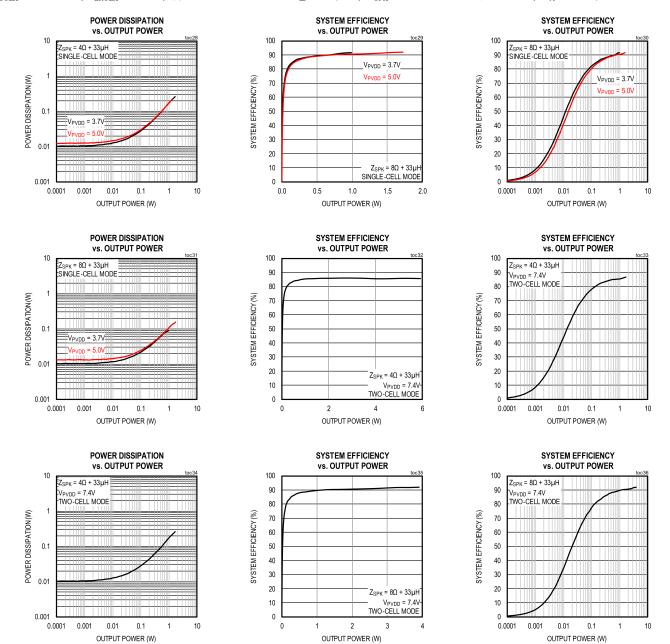

D級再生アンプは、AB級レベルのオーディオ性能と、ポータブ ル・アプリケーション用のバッテリー長寿命化に必要な効率を 共に備えています。アクティブ・エミッション制限回路 (AEL) とエッジ・レート制限回路をスペクトラム拡散変調(SSM)方 式と組み合わせることで、EMI を低減し、従来の D級アンプに 必要とされていた出力フィルタ処理を不要にしました。

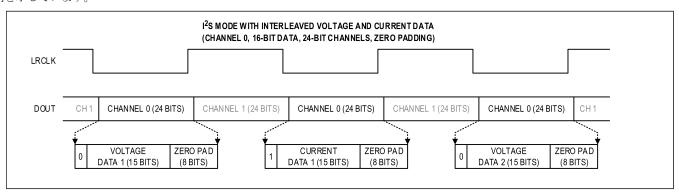

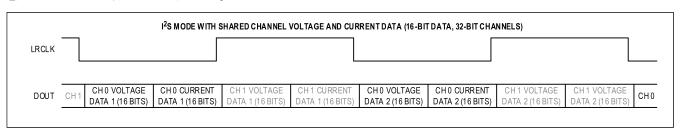

本デバイスは、高精度出力電流検出チャンネルと出力電圧帰還 チャンネルを備えています。これらのチャンネルで収集された データは、オーディオ・データ出力で伝送することができ、 オーディオ・エンハンスメント、バス・ブースト、スピーカ保 護、ハプティック機能などのアルゴリズムをホストのオーディ オ DSP で実行することができます。

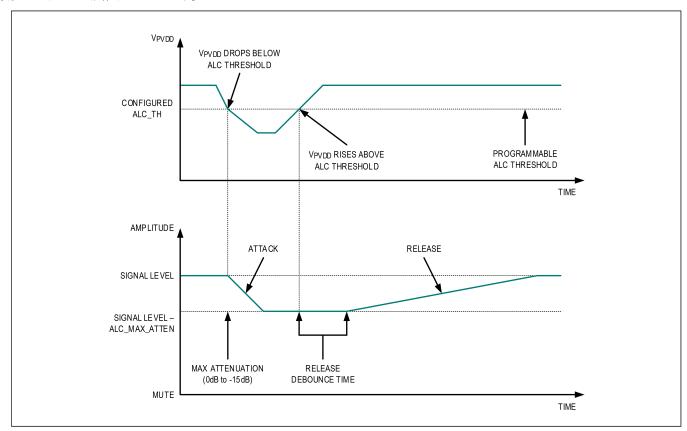

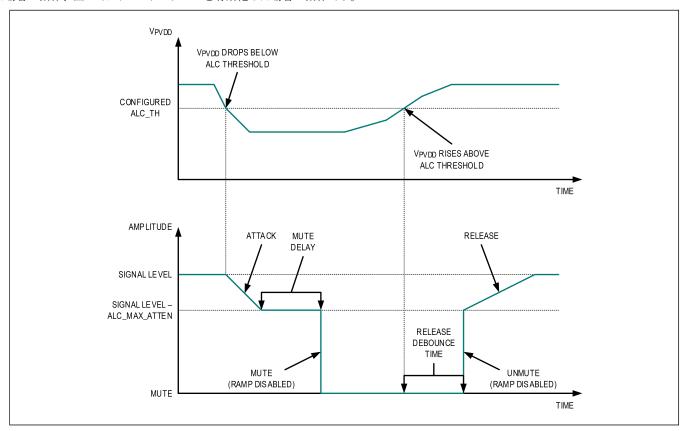

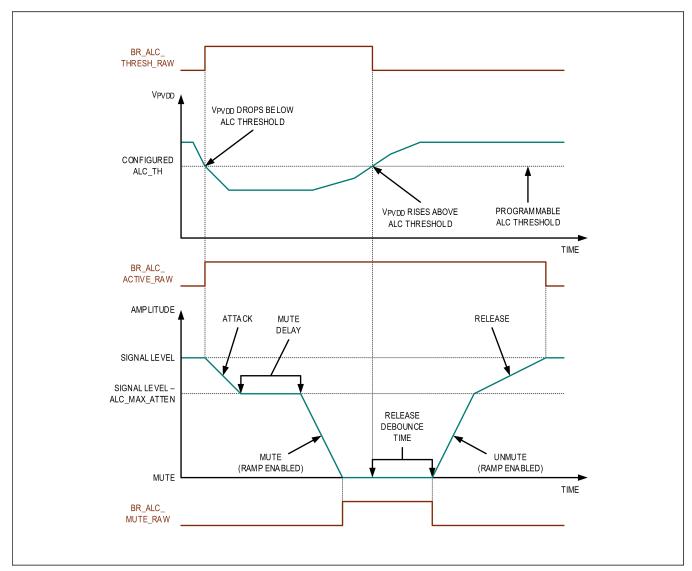

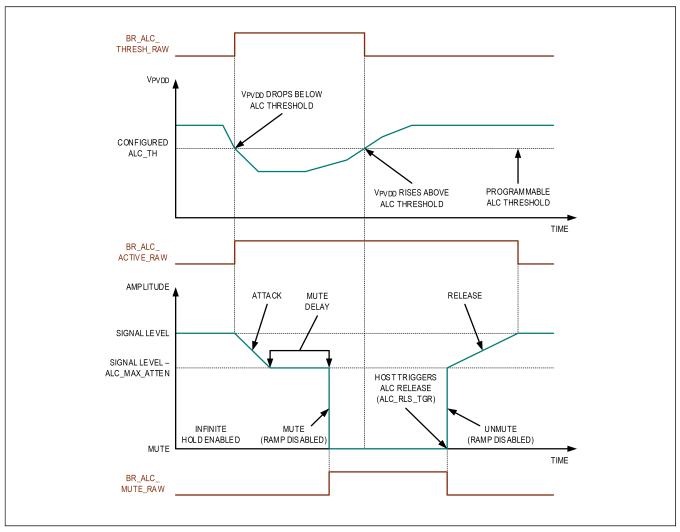

本デバイスはスレッショルドが設定可能な再生チャンネル ALC を搭載しており、ポータブル・システムのバッテリーにブラウ ンアウト保護を提供すると共に、デバイスの損傷を防ぐための 堅牢な過熱および過電流保護を提供しています。

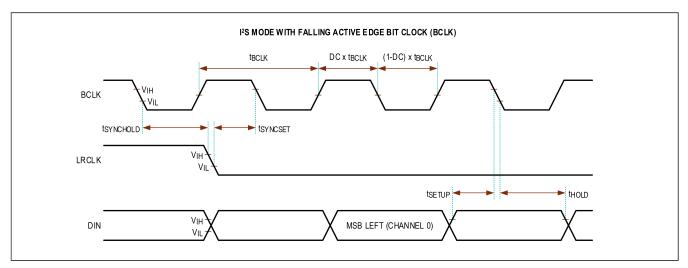

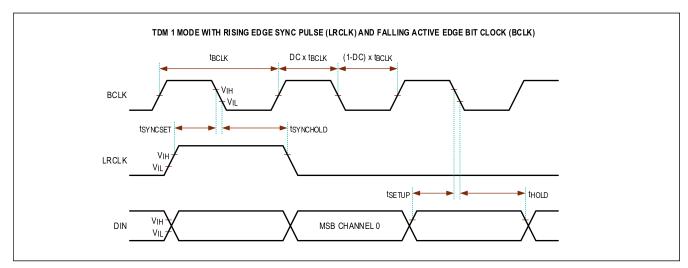

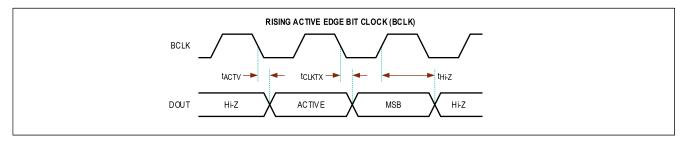

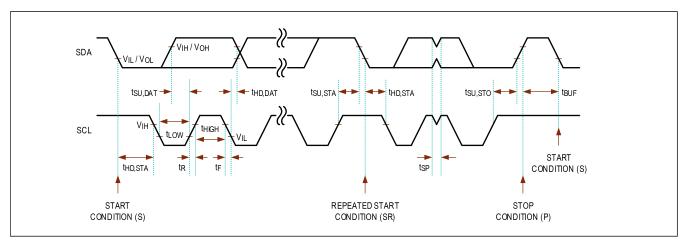

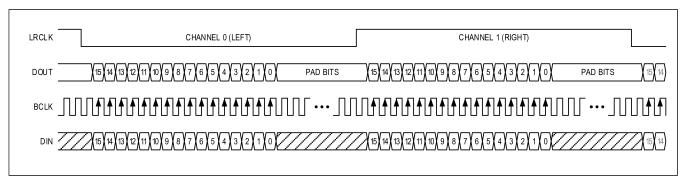

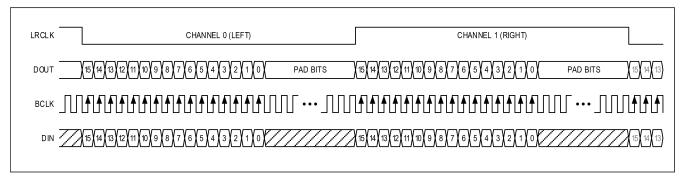

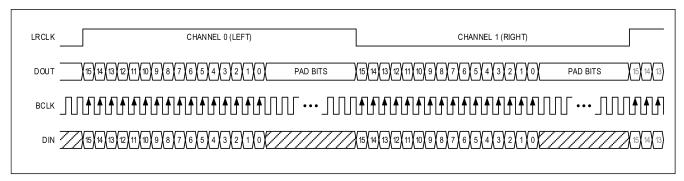

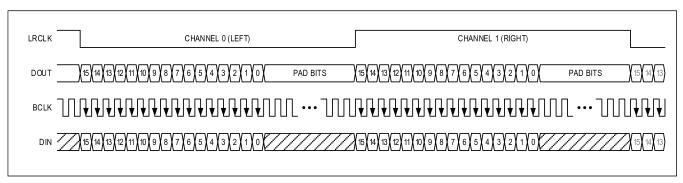

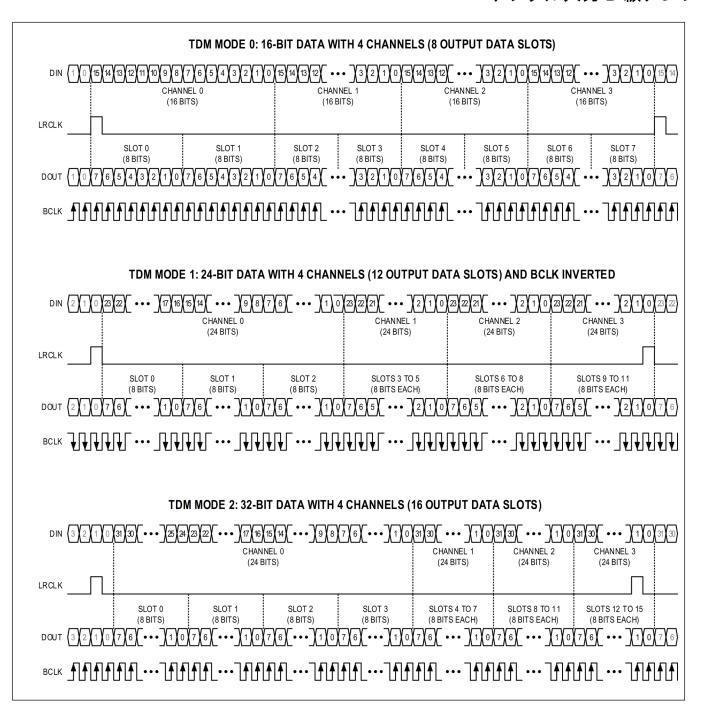

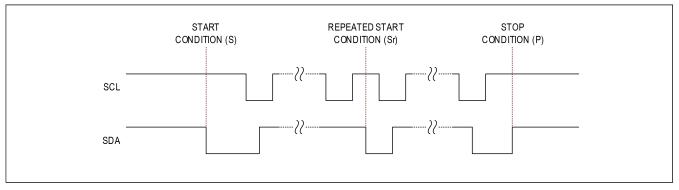

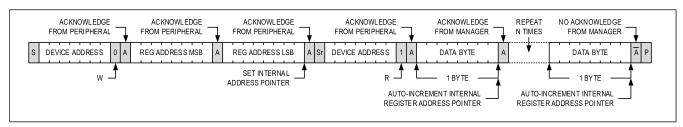

また、オーディオ再生と IV 帰還データ用の PCM インター フェースと、デバイス制御とステータス読出し用の標準I<sup>2</sup>Cイン ターフェースを備えています。PCM インターフェースは、I<sup>2</sup>S、 左詰め、および TDM タイミングなどの一般的なオーディオ・ データフォーマットをサポートしています。独自のクロッキン グ構成により、外付けの高周波リファレンス・クロックが不要 です。このクロックを不要とすることで、デバイスのサイズと 端子数を削減するだけでなく、高速スイッチングによる EMI の リスクや潜在的な基板カップリングの問題を軽減しながら、イ ンターフェースの電力を節約できます。

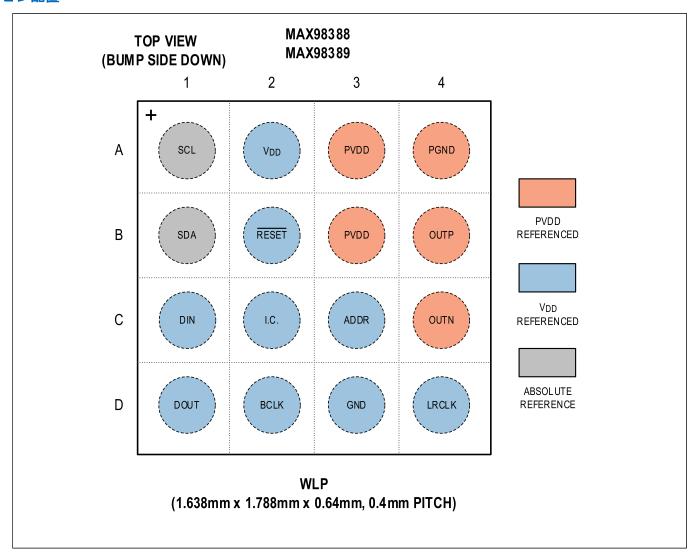

パッケージの接続はエッジ配線だけで済むように設計されてい るため、高価なバンプ・ビアを必要とせず、コスト効率の高い ウェーハレベル・パッケージ (WLP) が使用可能となっていま す。本デバイスは、0.4mm ピッチの 16 バンプ WLP パッケージ で提供され、-40℃~+85℃ の拡張温度範囲で仕様規定されてい ます。

SMBus は、Intel Corp.の商標です。

#### 機能と利点

- ・ 広いアンプ電源範囲: 2.3V~10V ・ 1 セルと 2 セルの両方をサポート

- 高性能 D 級アンプ

- ダイナミックレンジ:最大 111dB(A 特性周波数重み付け)

- 出力ノイズ: 10µV<sub>RMS</sub> (1セル・モード)

- 出力ノイズ: 14.5µV<sub>RMS</sub> (2 セル・モード)

- 高出カパワー(THD+N≤1%)

- 4Ωに対する出力パワー: 1.32W (V<sub>PVDD</sub> = 3.7V)

- 4Ωに対する出力パワー: 2.4W (V<sub>PVDD</sub> = 5V)

- 4Ωに対する出力パワー: 5.15W (V<sub>PVDD</sub> = 7.4V)

- 4Ωに対する出力パワー: 9.1W (V<sub>PVDD</sub> = 10V)

- 高いアンプ効率(再生専用パワー)

- 4Ωに対する 0.1W での効率: 76%(V<sub>PVDD</sub> = 5V)

- 4Ωに対する 1W での効率: 85.5% (V<sub>PVDD</sub> = 5V)

- 8Ωに対する 1W での効率:90%(V<sub>PVDD</sub> = 5V)

- ピーク THD+N: -83dB 以下(1kHz 時)

- 低い総自己消費電力

- 9.3mW (V<sub>PVDD</sub> = 3.7V、IV 帰還ディスエーブル時)

- 13.9mW (V<sub>PVDD</sub> = 3.7V、IV 帰還イネーブル時)

- 16.1mW (V<sub>PVDD</sub> = 5V、IV 帰還イネーブル時)

- 22.5mW (V<sub>PVDD</sub> = 7.4V、IV 帰還イネーブル時)

- 低いソフトウェア・シャットダウン電力:5µW 未満

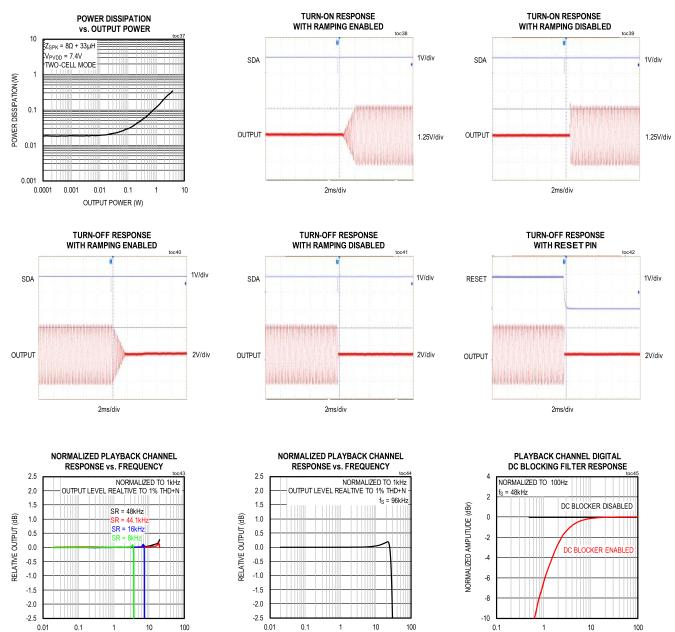

- ターンオン時間: 1ms (f<sub>s</sub> = 48kHz、ランプをディスエーブル

- 再生遅延:5サンプル(f<sub>S</sub> < 50kHz、f<sub>IN</sub> = 1kHz)

- 外部のリファレンス・クロックが不要

- 再生サンプル・レート: 8kHz~96kHz

- EMI対策として D級スイッチング周波数をトリミング

- 強力なクリック/ポップ抑制回路

- ブラウンアウト保護用プログラマブル ALC

- 堅牢な短絡および過熱保護

- 省スペース・パッケージでの提供:

- 2.93mm<sup>2</sup>、16 ピン WLP(0.4mm ピッチ)

### アプリケーション

- AR/VR ウェアラブル

- LRA ハプティック・ドライブ

- スマート・ウォッチおよび IoT デバイス

- ゲーミング・デバイス

- ノートブック・コンピュータおよびタブレット

オーダー情報はデータシート末尾に記載されています。

©2023 Analog Devices, Inc. All rights reserved. 商標および登録商標は各社の所有に属します。

社/〒105-6891 東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 10F

電話 03(5402)8200

大 阪営業所/〒532-0003 大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 10F

電話 06(6350)6868

名古屋営業所/〒451-6038 愛知県名古屋市西区牛島町 6-1 名古屋ルーセントタワー 38F 電話 052 (569) 6300

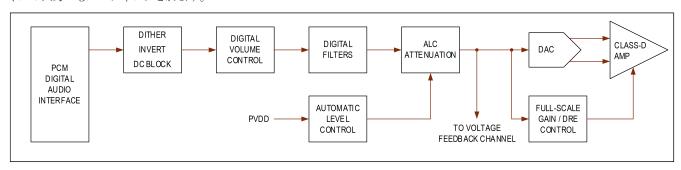

### 簡略化したブロック図

### MAX98388/MAX98389

## IV 帰還およびブラウンアウト保護内蔵 デジタル入力 D 級アンプ

### 絶対最大定格

| GND~PGND                | −0.1V~+0.1V                                  | (OUTP または OI |

|-------------------------|----------------------------------------------|--------------|

| V <sub>PVDD</sub> ~PGND | −0.3V~+12V                                   | 短絡持続時間       |

| V <sub>DD</sub> ~GND    | −0.3V~+2.2V                                  | 連続消費電力(TA    |

| OUTP、OUTN~PGND          | $-0.3V \sim V_{PVDD} + 0.3V$                 | ディレーティング     |

| BCLK, LRCLK, DIN, DOUT? | $\sim$ GND0.3V $\sim$ V <sub>DD</sub> + 0.3V | ジャンクション温     |

| ADDR、I.C.~GND           | $-0.3V \sim V_{DD} + 0.3V$                   | 動作温度範囲       |

| 他の全端子~GND               | 0.3V~+2.2V                                   | 保存温度範囲       |

| OUTP~OUTN の短絡持続時間       | 連続                                           | けんだ処理温度(     |

| (OUTP $\pm$ $\pm$ $\pm$ $\pm$ OUTN) $\sim$ (PGND、PVDD $\pm$ $\pm$ $\pm$ $\pm$ $\pm$ $\pm$ $\pm$ $\pm$ $\pm$ |

|-------------------------------------------------------------------------------------------------------------|

| 短絡持続時間連続                                                                                                    |

| 連続消費電力(TA=+70℃、+70℃ 超では 13.7mW/℃で                                                                           |

| ディレーティング)1.38W                                                                                              |

| ジャンクション温度+150°C                                                                                             |

| 動作温度範囲40℃~+85℃                                                                                              |

| 保存温度範囲65℃~+150℃                                                                                             |

| はんだ処理温度 (リフロー)+260℃                                                                                         |

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。これらの規定はストレス定格のみを定めたものであり、この仕様の動作セクションに記載する 規定値以上でデバイスが正常に動作することを意味するものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

### パッケージ情報

#### **WLP**

| Package code                                        | W161P1Z+1                      |

|-----------------------------------------------------|--------------------------------|

| Outline Number                                      | 21-100636                      |

| Land Pattern Number                                 | Refer to Application Note 1891 |

| Thermal Resistance, Four-Layer Board:               |                                |

| Junction to Ambient $(\theta_{JA})$                 | 57.93°C/W                      |

| Junction-to-Case Thermal Resistance $(\theta_{JC})$ | N/A                            |

最新のパッケージ外形図とランド・パターン(フットプリント)に関しては、www.maximintegrated.com/packages で確認してください。パッケージ・コードの「+」、「#」、「-」は RoHS 対応状況のみを示します。パッケージ図面は異なる末尾記号が示されている場合がありますが、図面は RoHS 状況に関わらず該当のパッケージについて図示しています。

パッケージの熱抵抗は、JEDEC 規格 JESD51-7 に記載の方法で 4 層基板を使用して求めたものです。パッケージの熱に対する考慮事項の詳細については、www.maxim-ic.com/thermal-tutorial を参照してください。

### 電気的特性

$(V_{PVDD}=5V~(1~\text{セル・モード})$  または 7.4V (2~セル・モード) 、 $V_{DD}=1.8V$ 、 $V_{GND}=V_{PGND}=0V$ 、 $C_{PVDD}=10\mu F+0.1\mu F$ 、 $C_{VDD}=1\mu F$ 、 $f_{BCLK}=3.072MHz$ 、 $f_{LRCLK}=48kHz$ 、 $Z_{SPK}=\infty$  (OUTP $\sim$ OUTN) 、1~セル・モード、AC 測定帯域幅 $=20Hz\sim20kHz$ 、 $T_A=T_{MIN}\sim T_{MAX}$ 、代表値は  $T_A=+25\%$  での値)(Note 1)

| PARAMETER                               | SYMBOL                    | CONE                                | DITIONS                                              | MIN                                 | TYP  | MAX  | UNITS     |    |

|-----------------------------------------|---------------------------|-------------------------------------|------------------------------------------------------|-------------------------------------|------|------|-----------|----|

| SYSTEM-LEVEL                            |                           |                                     | <u>.</u>                                             |                                     |      |      |           |    |

|                                         |                           | Guaranteed by PSRR test             | Two-cell/ boosted mode                               | 5                                   |      | 10   |           |    |

| PVDD Supply Voltage                     | $V_{PVDD}$                | test                                | Single-cell mode                                     | 3.0                                 |      | 5.5  | $_{ m V}$ |    |

| Range                                   | V PVDD                    |                                     | est, single-cell mode, the parametric performance is | 2.3                                 |      |      | V         |    |

| V <sub>DD</sub> Supply Voltage<br>Range | $V_{DD}$                  | Guaranteed by PSRR te               | Guaranteed by PSRR test                              |                                     | 1.8  | 1.89 | V         |    |

| PVDD Undervoltage                       | 37                        | Single-cell mode                    | V <sub>PVDD</sub> falling                            | 1.9                                 |      | 2.2  | V         |    |

| Lockout                                 | $V_{ m UVLO\_PVDD}$       | Two-cell mode                       | V <sub>PVDD</sub> falling                            | 4.4                                 |      | 4.7  | 7 ·       |    |

| PVDD UVLO                               |                           | Single-cell mode (Note              | 4)                                                   | 150                                 | 200  |      | **        |    |

| Hysteresis                              |                           | Two-cell mode (Note 4)              | )                                                    | 120                                 | 150  |      | mV        |    |

| V <sub>DD</sub> Undervoltage<br>Lockout | $V_{\text{UVLO\_VDD}}$    | V <sub>DD</sub> falling             |                                                      | 1.3                                 |      | 1.6  | V         |    |

| V <sub>DD</sub> UVLO Hysteresis         |                           | Note 4                              |                                                      | 20                                  | 40   |      | mV        |    |

| V <sub>DD</sub> Supply Ramp Rate        |                           |                                     |                                                      | 0.1                                 |      |      | V/ms      |    |

| Thermal Shutdown<br>Temperature         |                           | THERMSHDN_THRES                     | S = 0x2                                              |                                     | 155  |      | °C        |    |

| Thermal Shutdown<br>Hysteresis          |                           |                                     |                                                      |                                     |      |      | °C        |    |

| Thermal Warning<br>Temperature          |                           | THERMWARN_THRE                      | THERMWARN_THRES = 0x2                                |                                     | 115  |      | °C        |    |

| Thermal Warning<br>Hysteresis           |                           |                                     |                                                      |                                     | 15   |      | °C        |    |

| POWER CONSUMPTION                       | N / QUIESCEN              | T POWER CONSUMPT                    | TON                                                  |                                     |      |      |           |    |

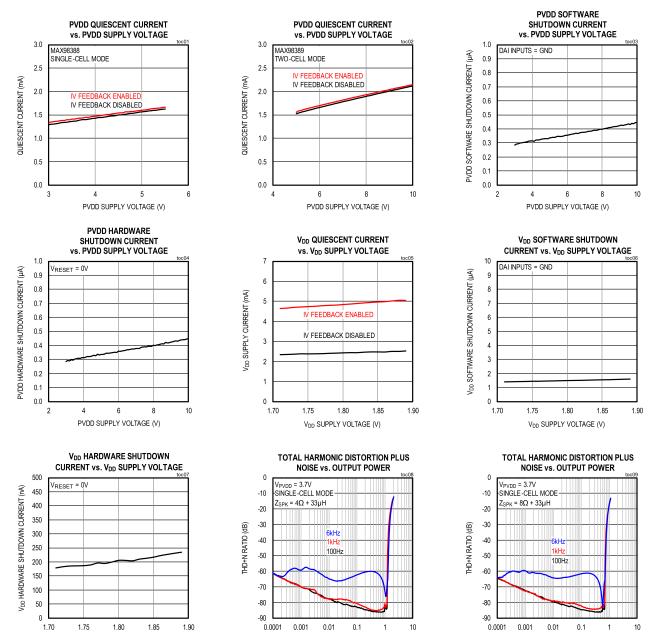

|                                         |                           | Both supplies, IV feedback disabled | $V_{PVDD} = 3.7V$                                    |                                     | 9.3  |      |           |    |

| Total Quiescent Power                   |                           |                                     | $V_{PVDD} = 3.7V$                                    |                                     | 13.9 |      | mW        |    |

| *                                       |                           | Both supplies, IV feedback enabled  | $V_{PVDD} = 5V$                                      |                                     | 16.1 |      | 1         |    |

|                                         |                           | leedback enabled                    | $V_{PVDD} = 7.4V$                                    |                                     | 22.5 |      |           |    |

| PVDD Quiescent<br>Current               |                           | IV feedback disabled                | $V_{PVDD} = 3.7V$                                    |                                     | 1.37 |      | mA        |    |

| V <sub>DD</sub> Quiescent Current       |                           | IV feedback disabled                |                                                      |                                     | 2.38 |      | mA        |    |

|                                         |                           |                                     | $V_{PVDD} = 3.7V$                                    |                                     | 1.42 | 2    |           |    |

| PVDD Quiescent<br>Current               |                           | IV feedback enabled                 | $V_{PVDD} = 5V$                                      |                                     | 1.59 | 2.2  | mA        |    |

| Current                                 |                           |                                     | $V_{PVDD} = 7.4V$                                    |                                     | 1.86 | 2.5  | 1         |    |

| V <sub>DD</sub> Quiescent Current       |                           | IV feedback enabled                 | ,                                                    |                                     | 4.83 | 6.8  | mA        |    |

| POWER CONSUMPTION                       | N / SOFTWARE              | SHUTDOWN POWER                      | CONSUMPTION                                          |                                     |      |      |           |    |

| PVDD Software                           | _                         | No toggling on PCM                  | V <sub>PVDD</sub> = 3.7V,<br>single-cell mode        |                                     | 0.3  | 4    |           |    |

| Shutdown Current                        | nt I <sub>PVDD_SWSD</sub> |                                     | interface pins,<br>$T_A = +25$ °C                    | $V_{PVDD} = 7.4V,$<br>two-cell mode |      | 0.4  | 5         | μΑ |

$(V_{PVDD}=5V~(1~\text{セル・モード})$  または 7.4V~(2~セル・モード) 、 $V_{DD}=1.8V$ 、 $V_{GND}=V_{PGND}=0V$ 、 $C_{PVDD}=10\mu F+0.1\mu F$ 、 $C_{VDD}=1\mu F$ 、 $f_{BCLK}=3.072MHz$ 、 $f_{LRCLK}=48kHz$ 、 $Z_{SPK}=\infty$  (OUTP $\sim$ OUTN) 、1~セル・モード、AC 測定帯域幅 $=20Hz\sim20kHz$ 、 $T_A=T_{MIN}\sim T_{MAX}$ 、代表値は  $T_A=+25\%$  での値)(Note 1)

| PARAMETER                                    | SYMBOL                    | COND                                                                                                          | ITIONS                                                                                           | MIN                         | TYP     | MAX               | UNITS |

|----------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------|---------|-------------------|-------|

| V <sub>DD</sub> Software Shutdown<br>Current | $I_{VDD\_SWSD}$           | No toggling on PCM interface pins, $T_A = +25$ °C                                                             |                                                                                                  |                             | 1.5     | 6                 | μΑ    |

| POWER CONSUMPTION                            | ON / HARDWAR              | E SHUTDOWN POWER                                                                                              | CONSUMPTION                                                                                      |                             |         |                   |       |

| PVDD Hardware                                |                           | $T_A = +25$ °C                                                                                                | $V_{PVDD} = 3.7V$ , single-cell mode                                                             |                             | 0.3     | 4                 | 4     |

| Shutdown Current                             | I <sub>PVDD_HWSD</sub>    | 1 <sub>A</sub> = +23 C                                                                                        | $V_{PVDD} = 7.4V$ , two-cell mode                                                                |                             | 0.4     | 5                 | μΑ    |

| V <sub>DD</sub> Hardware<br>Shutdown Current | $I_{VDD\_HWSD}$           | $T_A = +25$ °C                                                                                                |                                                                                                  |                             | 0.2     | 1                 | μΑ    |

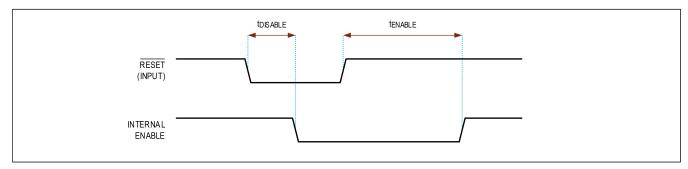

| ENABLE / DISABLE TIM                         | ИING                      |                                                                                                               |                                                                                                  |                             |         |                   |       |

|                                              |                           |                                                                                                               | Volume ramp disabled, $f_S \ge 44.1 kHz$                                                         |                             | 0.6     | 1                 |       |

| T. O. T.                                     |                           | Software-shutdown state to active state                                                                       | Volume ramp disabled,<br>f <sub>S</sub> < 44.1kHz (Note 4)                                       |                             | 1.1     | 2.3               |       |

| Turn-On Time                                 | t <sub>ON</sub> (device t | (device ready to receive audio data)                                                                          | Volume ramp enabled, $f_S \ge 44.1 kHz$                                                          |                             | 2.3     | 2.7               | ms    |

|                                              |                           |                                                                                                               | Volume ramp enabled,<br>f <sub>S</sub> < 44.1kHz (Note 4)                                        |                             | 2.9     | 4.2               |       |

|                                              | t <sub>OFF</sub> ope      | From full-active state<br>operation to software-<br>shutdown state (power<br>down done status)                | Volume ramp disabled                                                                             |                             | 70      | 100               | μs    |

| Turn-Off Time                                |                           |                                                                                                               | Volume ramp enabled, $f_S \ge 44.1 \text{kHz}$                                                   |                             | 4.3     | 4.6               |       |

|                                              |                           |                                                                                                               | Volume ramp enabled,<br>f <sub>S</sub> < 44.1kHz                                                 |                             | 6.7     | 8                 | ms    |

| Hardware Enable Time                         | t <sub>HW_EN</sub>        |                                                                                                               | hardware- shutdown state<br>to the software-shutdown                                             |                             |         | 1.5               | ms    |

| Hardware Reset Time                          | t <sub>HW_RES</sub>       | software reset bit) until                                                                                     | tware reset (write 1 to the<br>the device is reset and<br>nutdown state (I <sup>2</sup> C ready) |                             |         | 0.4               | ms    |

| Hardware Disable<br>Assert Time              | $t_{ m HW\_DIS}$          | Minimum time RESET input must be asserted low to ensure the device transitions to the hardware-shutdown state |                                                                                                  |                             | 1       |                   | μs    |

| SPEAKER DIGITAL AU                           | DIO CHANNEL               | / DAC DIGITAL FILTER                                                                                          | CHARACTERISTICS (fL                                                                              | <sub>RCLK</sub> < 50kHz) (N | Note 2) |                   |       |

| Passband Cutoff                              | f                         | Ripple $\leq \delta_P$                                                                                        |                                                                                                  | $0.452 \times f_S$          |         |                   | Hz    |

| Frequency                                    | $f_{PLP}$                 | Droop < -3dB                                                                                                  |                                                                                                  | $0.457 \times f_S$          |         |                   | IIZ   |

| Passband Ripple                              | $\delta_{\mathrm{P}}$     | $f_{IN} < f_{PLP}$ , referenced to significant response only                                                  | gnal level at 1kHz, digital                                                                      | -0.1                        |         | +0.1              | dB    |

| Stopband Cutoff<br>Frequency                 | $f_{\mathrm{SLP}}$        | Attenuation $> \delta_S$                                                                                      |                                                                                                  |                             |         | $0.49 \times f_S$ | Hz    |

$(V_{PVDD}=5V~(1~\text{セル・モード})$  または 7.4V~(2~セル・モード) 、 $V_{DD}=1.8V$ 、 $V_{GND}=V_{PGND}=0V$ 、 $C_{PVDD}=10\mu F+0.1\mu F$ 、 $C_{VDD}=1\mu F$ 、 $f_{BCLK}=3.072MHz$ 、 $f_{LRCLK}=48kHz$ 、 $Z_{SPK}=\infty$  (OUTP $\sim$ OUTN) 、1~セル・モード、AC 測定帯域幅 $=20Hz\sim20kHz$ 、 $T_A=T_{MIN}\sim T_{MAX}$ 、代表値は  $T_A=+25\%$  での値)(Note 1)

| PARAMETER                    | SYMBOL                                                                                                                                                                        | COND                                                       | ITIONS                                  | MIN                         | TYP   | MAX                        | UNITS   |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------|-----------------------------|-------|----------------------------|---------|

| Stopband Attenuation         | $\delta_{S}$                                                                                                                                                                  | $f_{IN} > f_{SLP}$                                         | 75                                      |                             |       | dB                         |         |

| Group Delay                  |                                                                                                                                                                               | $f_{IN} = 1kHz$                                            |                                         | 5                           |       | samples                    |         |

| SPEAKER DIGITAL AU           | DIO CHANNEL                                                                                                                                                                   | DAC DIGITAL FILTER                                         | CHARACTERISTICS (fL                     | <sub>RCLK</sub> ≥ 50kHz) (N |       |                            |         |

| Passband Cutoff              | $f_{PLP}$                                                                                                                                                                     | Ripple $< \delta_P$                                        |                                         | $0.227 \times f_S$          |       |                            | Hz      |

| Frequency                    |                                                                                                                                                                               | Droop < -3dB                                               |                                         | $0.314 \times f_S$          |       |                            | пх      |

| Passband Ripple              | $\delta_{	ext{P}}$                                                                                                                                                            | $f_{IN} < f_{PLP}$ , referenced to si filter response only | gnal level at 1kHz, digital             | -0.1                        |       | +0.1                       | dB      |

| Stopband Cutoff<br>Frequency | $f_{\mathrm{SLP}}$                                                                                                                                                            | Attenuation $< \delta_S$                                   |                                         |                             |       | $0.49 \times f_{\text{S}}$ | Hz      |

| Stopband Attenuation         | $\delta_{\mathrm{S}}$                                                                                                                                                         | $f_{IN} \ge f_{SLP}$                                       |                                         | 80                          |       |                            | dB      |

| Group Delay                  |                                                                                                                                                                               | $f_{IN} = 1kHz$                                            |                                         |                             | 5.5   |                            | samples |

| SPEAKER DIGITAL AU           | DIO CHANNEL                                                                                                                                                                   | DC BLOCKING DIGITA                                         | AL FILTER CHARACTER                     | RISTICS (Note 2             | 2)    |                            |         |

| DC Attenuation               |                                                                                                                                                                               |                                                            |                                         | 80                          |       |                            | dB      |

| DC Blocking Filter           | £                                                                                                                                                                             | $f_S = 8kHz$ , $16kHz$ , $32kHz$                           | z, 48kHz, and 96kHz                     |                             | 1.872 |                            | Ша      |

| -3dB Cutoff Frequency        | $ m f_{C}$                                                                                                                                                                    | $f_S = 44.1 \text{kHz}, 88.2 \text{kHz}$                   |                                         |                             | 1.72  |                            | Hz      |

| SPEAKER CLASS-D A            | MPLIFIER                                                                                                                                                                      |                                                            |                                         |                             |       |                            |         |

| Output Offset Voltage        | $V_{OS}$                                                                                                                                                                      | $T_A = +25$ °C                                             |                                         | -3                          | ±0.3  | +3                         | mV      |

|                              | $\begin{array}{c c} & & Aweighte \\ 32 \ sample \\ digital \ sil \\ input \ sign \end{array}$                                                                                 | Peak voltage,<br>Aweighted,                                | Amp output power down, single-cell mode |                             | -77   |                            |         |

| Click and Dan Laval          |                                                                                                                                                                               |                                                            | Amp output power down, two-cell mode    |                             | -71   |                            | dBV     |

| Click-and-Pop Level          |                                                                                                                                                                               | input signal,<br>$Z_{SPK} = 8\Omega + 33\mu H$ or          | Amp output powerup, single-cell mode    |                             | -76   |                            | db v    |

|                              |                                                                                                                                                                               | $4\Omega + 33\mu H$                                        | Amp output powerup, two-cell mode       |                             | -70   |                            |         |

|                              |                                                                                                                                                                               | A waighted 24 hit or                                       | Single-cell mode, DAC low-power mode    |                             | 10    |                            |         |

| Output Noise                 | e <sub>N</sub> A-weighted, 24-bit, or 32-bit data                                                                                                                             | Two-cell mode, DAC high-performance mode                   |                                         | 14.5                        |       | $\mu V_{ m RMS}$           |         |

|                              |                                                                                                                                                                               | A-weighted, 24-bit or                                      | $Z_{SPK} = 4\Omega + 33\mu H$           |                             | 110   |                            |         |

|                              | DR  32-bit data, single-cell mode, DAC low power mode (Note 3)  A-weighted, 24-bit or 32-bit data, two-cell mode, V <sub>PVDD</sub> = 7.4V, DAC highperformance mode (Note 3) | mode, DAC low power                                        | $Z_{SPK} = 8\Omega + 33\mu H$           |                             | 110.5 |                            |         |

| Dynamic Range                |                                                                                                                                                                               | $Z_{SPK} = 8\Omega + 33\mu H$                              |                                         | 111                         |       | dB                         |         |

### MAX98388/MAX98389

# Ⅳ 帰還およびブラウンアウト保護内蔵 デジタル入力 D 級アンプ

$(V_{PVDD}=5V~(1~\text{セル・モード})$  または 7.4V~(2~セル・モード) 、 $V_{DD}=1.8V$ 、 $V_{GND}=V_{PGND}=0V$ 、 $C_{PVDD}=10\mu F+0.1\mu F$ 、 $C_{VDD}=1\mu F$ 、 $f_{BCLK}=3.072MHz$ 、 $f_{LRCLK}=48kHz$ 、 $Z_{SPK}=\infty$  (OUTP $\sim$ OUTN) 、1~セル・モード、AC 測定帯域幅 $=20Hz\sim20kHz$ 、 $T_A=T_{MIN}\sim T_{MAX}$ 、代表値は  $T_A=+25\%$  での値)(Note 1)

| PARAMETER                         | SYMBOL    | CON                                                                                                                                                                                                                                              | DITIONS                                                                     | MIN                                                                            | TYP  | MAX  | UNITS |    |

|-----------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------|------|------|-------|----|

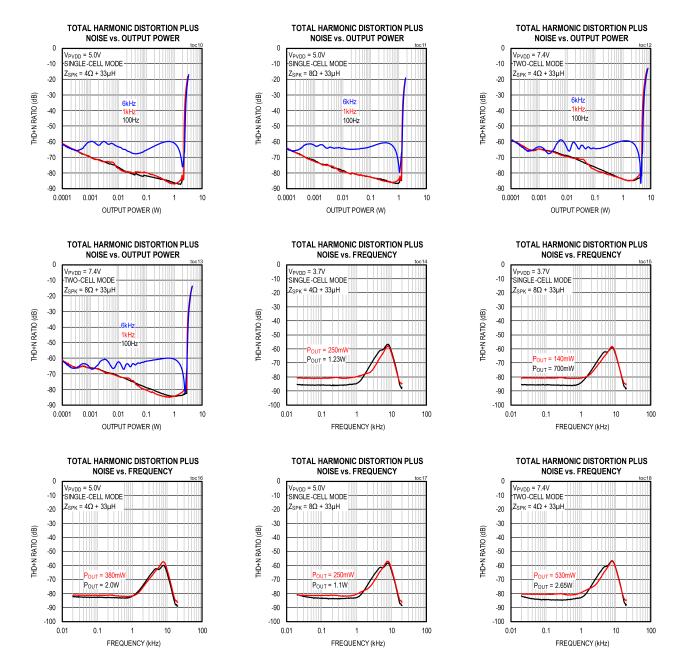

|                                   |           | $f_{IN} = 1 \text{kHz},$<br>$T_A = +25 \text{°C},$                                                                                                                                                                                               | $\begin{split} P_{OUT} &= 1W, \\ Z_{SPK} &= 4\Omega + 33 \mu H \end{split}$ |                                                                                | -87  |      |       |    |

| Total Harmonic Distortion + Noise | THD+N     | THD+N V <sub>rv</sub>                                                                                                                                                                                                                            | single-cell mode,<br>$V_{PVDD} = 5V$                                        | $\begin{split} P_{OUT} &= 0.7 W, \\ Z_{SPK} &= 8\Omega + 33 \mu H \end{split}$ |      | -85  | -73   | dB |

|                                   |           | $f_{IN} = 1 \text{kHz}, T_A = +25 \text{°C}$<br>$V_{PVDD} = 7.4 \text{V}, POUT = \text{(Note 4)}$                                                                                                                                                | C, two-cell mode,<br>= 1.4W, $Z_{SPK} = 8\Omega + 33\mu H$                  |                                                                                | -83  | -74  |       |    |

| Full-Scale Output                 | EC        | Single-cell mode, +12d                                                                                                                                                                                                                           | lB gain                                                                     |                                                                                | 12.4 |      | 4DV   |    |

| Voltage                           | FS        | Two-cell mode, +18dE                                                                                                                                                                                                                             | gain                                                                        |                                                                                | 18.4 |      | dBV   |    |

|                                   |           |                                                                                                                                                                                                                                                  | THD+N = 10%                                                                 |                                                                                | 92   |      |       |    |

|                                   |           | $f_{IN} = 1 \text{kHz},$                                                                                                                                                                                                                         | $P_{OUT} = 1W$                                                              |                                                                                | 90   |      | 1     |    |

|                                   |           | $Z_{SPK} = 8\Omega + 33\mu H,$<br>$V_{PVDD} = 5V$                                                                                                                                                                                                | $P_{OUT} = 0.1 W$                                                           |                                                                                | 80   |      | 1     |    |

| Efficiency                        | η         | V PVDD 3 V                                                                                                                                                                                                                                       | $P_{OUT} = 0.05W$                                                           |                                                                                | 72   |      | %     |    |

|                                   |           | $f_{IN} = 1 \text{kHz},$                                                                                                                                                                                                                         | $P_{OUT} = 1W$                                                              |                                                                                | 85.5 |      | 1     |    |

|                                   |           | $Z_{SPK} = 4\Omega + 33\mu H$                                                                                                                                                                                                                    | $P_{OUT} = 0.1 W$                                                           |                                                                                | 76   |      | 1     |    |

|                                   |           | $V_{PVDD} = 5V$                                                                                                                                                                                                                                  | $P_{OUT} = 0.05W$                                                           |                                                                                | 69   |      | 1     |    |

|                                   |           |                                                                                                                                                                                                                                                  | V <sub>PVDD</sub> = 3.7V,<br>single-cell mode                               |                                                                                | 1.32 |      |       |    |

|                                   |           | $\begin{split} f_{\rm IN} &= 1 \text{kHz}, \\ THD+N &\leq 1\%, \\ Z_{\rm SPK} &= 4\Omega + 33 \mu \text{H} \end{split}$ $\begin{split} f_{\rm IN} &= 1 \text{kHz}, \\ THD+N &\leq 10\%, \\ Z_{\rm SPK} &= 4\Omega + 33 \mu \text{H} \end{split}$ | V <sub>PVDD</sub> = 5V,<br>single-cell mode                                 |                                                                                | 2.4  |      |       |    |

|                                   |           |                                                                                                                                                                                                                                                  | $V_{PVDD} = 7.4V$ , two-cell mode                                           |                                                                                | 5.15 |      |       |    |

|                                   |           |                                                                                                                                                                                                                                                  | V <sub>PVDD</sub> = 8.4V,<br>two-cell mode                                  |                                                                                | 6.54 |      |       |    |

|                                   |           |                                                                                                                                                                                                                                                  | $V_{PVDD} = 3.7V$ , single-cell mode                                        |                                                                                | 1.65 |      |       |    |

|                                   |           |                                                                                                                                                                                                                                                  | $V_{PVDD} = 5V$ , single-cell mode                                          |                                                                                | 3.0  |      |       |    |

|                                   |           |                                                                                                                                                                                                                                                  | $V_{PVDD} = 7.4V$ , two-cell mode                                           |                                                                                | 6.35 |      |       |    |

| 0                                 |           |                                                                                                                                                                                                                                                  | $V_{PVDD} = 8.4V,$<br>two-cell mode                                         |                                                                                | 8.02 |      | Ī     |    |

| Output Power                      | $P_{OUT}$ | Power P <sub>OUT</sub>                                                                                                                                                                                                                           |                                                                             | V <sub>PVDD</sub> = 3.7V,<br>single-cell mode                                  |      | 0.77 |       | W  |

|                                   |           | $f_{IN} = 1kHz$ ,                                                                                                                                                                                                                                | $V_{PVDD} = 5V$ , single-cell mode                                          |                                                                                | 1.4  |      |       |    |

|                                   |           | THD+N $\leq$ 1%,<br>$Z_{SPK} = 8\Omega + 33\mu H$                                                                                                                                                                                                | $V_{PVDD} = 7.4V$ , two-cell mode                                           |                                                                                | 3.05 |      |       |    |

|                                   |           |                                                                                                                                                                                                                                                  | $V_{PVDD} = 8.4V,$<br>two-cell mode                                         |                                                                                | 3.87 |      |       |    |

|                                   |           |                                                                                                                                                                                                                                                  | $V_{PVDD} = 3.7V$ , single-cell mode                                        |                                                                                | 0.95 |      |       |    |

|                                   |           | $\begin{split} f_{\text{IN}} &= 1 \text{kHz}, \\ THD+N &\leq 10\%, \\ Z_{\text{SPK}} &= 8\Omega + 33 \mu \text{H} \end{split}$                                                                                                                   | $V_{PVDD} = 5V$ , single-cell mode                                          |                                                                                | 1.72 |      |       |    |

|                                   |           |                                                                                                                                                                                                                                                  | $V_{PVDD} = 7.4V$ , two-cell mode                                           |                                                                                | 3.75 |      |       |    |

|                                   |           |                                                                                                                                                                                                                                                  | $V_{PVDD} = 8.4V,$<br>two-cell mode                                         |                                                                                | 4.84 |      |       |    |

$(V_{PVDD}=5V~(1~\text{セル・モード})$  または 7.4V~(2~セル・モード) 、 $V_{DD}=1.8V$ 、 $V_{GND}=V_{PGND}=0V$ 、 $C_{PVDD}=10\mu F+0.1\mu F$ 、 $C_{VDD}=1\mu F$ 、 $f_{BCLK}=3.072MHz$ 、 $f_{LRCLK}=48kHz$ 、 $Z_{SPK}=\infty$  (OUTP $\sim$ OUTN) 、1~セル・モード、AC 測定帯域幅 $=20Hz\sim20kHz$ 、 $T_A=T_{MIN}\sim T_{MAX}$ 、代表値は  $T_A=+25\%$  での値)(Note 1)

| PARAMETER                                                      | SYMBOL                                                                                                                | COND                                                                                        | ITIONS                                                                                                                             | MIN   | TYP  | MAX   | UNITS |

|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| Class-D Switching<br>Frequency                                 | $f_{\rm SW}$                                                                                                          |                                                                                             |                                                                                                                                    | 285   | 300  | 315   | kHz   |

| Spread-Spectrum<br>Bandwidth                                   | $f_{\rm SSM}$                                                                                                         |                                                                                             |                                                                                                                                    |       | ±14  |       | kHz   |

| Intermodulation Distortion                                     | IMD                                                                                                                   | ITU-R, $19kHz/20kHz$ , $12kHz = 8\Omega + 33\mu H$                                          | ITU-R, $19kHz/20kHz$ , $1:1$ , $V_{IN} = -3dBFS$ , $Z_{SPK} = 8\Omega + 33\mu H$                                                   |       | -70  |       | dB    |

| Frequency Response                                             |                                                                                                                       | Full response from digitathe amplifier output                                               | al audio interface input to                                                                                                        | -0.25 |      | +0.25 | dB    |

| Output Stage<br>On-Resistance                                  | R <sub>ON</sub>                                                                                                       | PMOS + NMOS (Full H                                                                         | -Bridge), $T_A = +25$ °C                                                                                                           |       | 0.38 |       | Ω     |

| Output Current Limit                                           | $I_{LIM}$                                                                                                             |                                                                                             |                                                                                                                                    | 3.5   |      |       | A     |

| Output Current Limit<br>Auto-Restart Time                      |                                                                                                                       |                                                                                             |                                                                                                                                    |       | 20   |       | ms    |

| Minimum Load<br>Resistance                                     | $R_{\rm L}$                                                                                                           | Nominal $4\Omega$ load minus                                                                | 25%                                                                                                                                |       | 3    |       | Ω     |

| Maximum Device-to-<br>Device Speaker Channel<br>Phase Mismatch |                                                                                                                       |                                                                                             | een multiple devices from all sample rates and DAI                                                                                 |       | 1.5  |       | deg   |

| Minimum Load<br>Inductance                                     |                                                                                                                       | In series with a $4\Omega$ load                                                             |                                                                                                                                    |       | 0    |       | μН    |

| Maximum Load<br>Inductance                                     |                                                                                                                       | In series with a $4\Omega$ load                                                             |                                                                                                                                    |       | 100  |       | μН    |

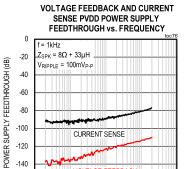

| SPEAKER CLASS-D A                                              | MPLIFIER / POV                                                                                                        | VER-SUPPLY REJECTION                                                                        | ON                                                                                                                                 |       |      |       |       |

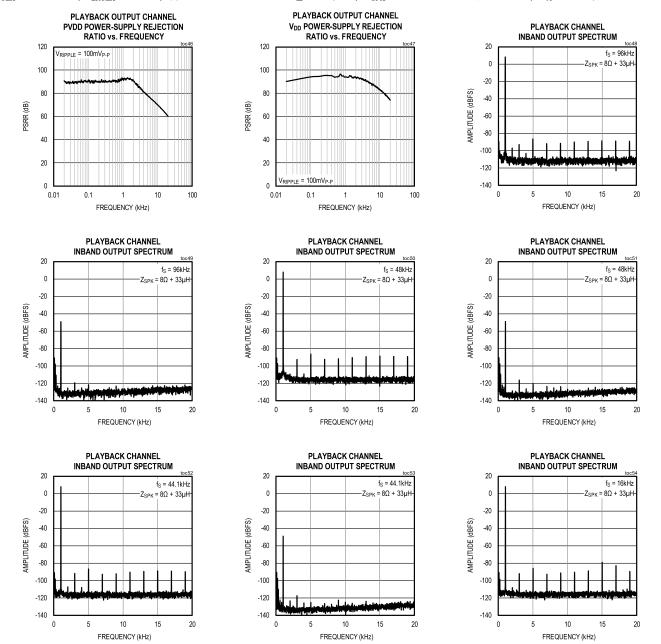

| PVDD DC Power<br>Supply Rejection Ratio                        | PSRR                                                                                                                  | DC level, $V_{PVDD} = 2.3V$<br>digital silence used for in                                  |                                                                                                                                    | 70    | 85   |       | dB    |

|                                                                |                                                                                                                       | $V_{RIPPLE} = 200 \text{mV}_{PP},$                                                          | $f_{RIPPLE} = 217Hz$                                                                                                               |       | 85   |       |       |

| PVDD AC Power                                                  |                                                                                                                       | $T_A = +25^{\circ}C,$                                                                       | $f_{RIPPLE} = 1kHz$                                                                                                                |       | 85   |       |       |

| Supply Rejection Ratio                                         | PSRR                                                                                                                  | digital silence used for input signal, $Z_{SPK} = 8\Omega + 33\mu H$ or $4\Omega + 33\mu H$ | $f_{RIPPLE} = 10kHz$                                                                                                               |       | 70   |       | dB    |

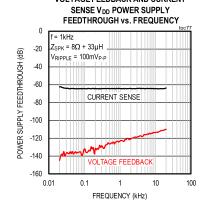

| V <sub>DD</sub> DC Power Supply<br>Rejection Ratio             | PSRR                                                                                                                  | DC level, $V_{DD} = 1.71 \text{V t}$<br>digital silence used for in                         |                                                                                                                                    | 70    | 85   |       | dB    |

|                                                                |                                                                                                                       | $V_{RIPPLE} = 100 \text{mV}_{PP},$                                                          | $f_{RIPPLE} = 217Hz$                                                                                                               |       | 90   |       |       |

| V <sub>DD</sub> AC Power Supply                                | DCDD                                                                                                                  | $T_A = +25$ °C, digital                                                                     | $f_{RIPPLE} = 1kHz$                                                                                                                |       | 90   |       |       |

| Rejection Ratio                                                | PSRR                                                                                                                  | silence used for input<br>signal, $Z_{SPK} = 8\Omega +$<br>$33\mu H$ or $4\Omega + 33\mu H$ | $f_{RIPPLE} = 10kHz$                                                                                                               | 80    |      |       | dB    |

| SPEAKER CLASS-D AN                                             | MPLIFIER / POV                                                                                                        | VER-SUPPLY INTERMO                                                                          | DULATION                                                                                                                           |       |      |       | •     |

| Power-Supply                                                   |                                                                                                                       | $T_A = +25^{\circ}\text{C},$<br>$f_{IN} = 1 \text{kHz},$<br>$P_{OUT} = 400 \text{mW}$       | $\begin{aligned} P_{\mathrm{VDD}} & supply, \\ f_{\mathrm{RIPPLE}} &= 217 Hz, \\ V_{\mathrm{RIPPLE}} &= 200 mV_{PP} \end{aligned}$ | -80   |      |       | dB    |

| Intermodulation                                                | $\begin{aligned} P_{OUT} &= 400 mW, \\ Z_{SPK} &= 8\Omega + 33 \mu H \text{ or } \\ 4\Omega + 33 \mu H \end{aligned}$ |                                                                                             | $\begin{split} &V_{DD} \text{ supply,} \\ &f_{RIPPLE} = 217 Hz, \\ &V_{RIPPLE} = 100 mV_{PP} \end{split}$                          |       | -80  |       | ub    |

$(V_{PVDD}=5V~(1~\text{セル・モード})$  または 7.4V~(2~セル・モード) 、 $V_{DD}=1.8V$ 、 $V_{GND}=V_{PGND}=0V$ 、 $C_{PVDD}=10\mu F+0.1\mu F$ 、 $C_{VDD}=1\mu F$ 、 $f_{BCLK}=3.072MHz$ 、 $f_{LRCLK}=48kHz$ 、 $Z_{SPK}=\infty$  (OUTP $\sim$ OUTN) 、1~セル・モード、AC 測定帯域幅 $=20Hz\sim20kHz$ 、 $T_A=T_{MIN}\sim T_{MAX}$ 、代表値は  $T_A=+25\%$  での値)(Note 1)

| PARAMETER                                                             | SYMBOL           | CONDITIONS                                                                                       | MIN                            | TYP  | MAX                        | UNITS   |

|-----------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------|--------------------------------|------|----------------------------|---------|

| SPEAKER OUTPUT VO                                                     | OLTAGE FEEDE     | BACK (Note 2)                                                                                    |                                |      |                            |         |

| Resolution                                                            |                  |                                                                                                  |                                | 16   |                            | Bits    |

| Sample Rate                                                           | $f_{S\_VFB}$     |                                                                                                  | 8                              |      | 96                         | kHz     |

| V-14 D                                                                | 37               | Single-cell mode                                                                                 | ±5.5                           |      |                            | V       |

| Voltage Range                                                         | $V_{SPK}$        | Two-cell mode                                                                                    |                                | ±11  |                            | v       |

| Power Supply<br>Feedthrough                                           | PSF              | No input signal, AC relative to PVDD or $V_{DD}$ , $f_{RIPPLE} = 1kHz$ , $V_{RIPPLE} = 100mVP-P$ |                                | -100 |                            | dB      |

| Max Device to Device<br>Voltage Feedback<br>Channel Phase<br>Mismatch |                  | $f_{IN} = 1 \text{kHz}$                                                                          |                                | 0.05 |                            | Samples |

| SPEAKER OUTPUT VO                                                     | OLTAGE FEEDE     | BACK / DIGITAL FILTER CHARACTERISTICS (1                                                         | $t_s$ < 50kHz) (Note           | e 2) |                            |         |

| Passband Ripple                                                       |                  | $f_{IN} < f_{PLP}$ , referenced to the signal level at 1kHz                                      | -0.225                         |      | +0.225                     | dB      |

| Lowpass Filter Cutoff                                                 | $f_{PLP}$        | Ripple $< \delta_P$                                                                              | $0.44 \times f_S$              |      |                            | Hz      |

| Frequency                                                             |                  | Droop < -3dB                                                                                     | $0.45 \times f_{S}$            |      |                            | 112     |

| Lowpass Filter<br>Stopband Frequency                                  | $f_{SLP}$        | -40dB limit                                                                                      |                                |      | $0.58 \times f_{\text{S}}$ | Hz      |

| Lowpass Filter<br>Stopband Attenuation                                |                  |                                                                                                  | 40                             |      |                            | dB      |

| Group Delay                                                           |                  | $f_{IN} = 1kHz$                                                                                  |                                | 8    |                            | Samples |

| SPEAKER OUTPUT VO                                                     | OLTAGE FEEDE     | BACK / DIGITAL FILTER CHARACTERISTIC S (                                                         | $f_S \ge 50 \text{kHz}$ ) (Not | e 2) |                            |         |

| Passband Ripple                                                       |                  | $f_{IN} \le f_{PLP}$ , referenced to the signal level at 1kHz                                    | -0.225                         |      | +0.225                     | dB      |

| Lowpass Filter Cutoff                                                 | $f_{PLP}$        | Ripple $< \delta_P$ , $88.2kHz \le f_S \le 96kHz$                                                | $0.235 \times f_S$             |      |                            | 11-     |

| Frequency                                                             |                  | Droop $< -3$ dB, $88.2$ kHz $\le f_S \le 96$ kHz                                                 | $0.29 \times f_S$              |      |                            | Hz      |

| Lowpass Filter<br>Stopband Frequency                                  | $f_{SLP}$        | -40dB limit                                                                                      |                                |      | $0.58 \times f_S$          | Hz      |

| Lowpass Filter<br>Stopband Attenuation                                |                  |                                                                                                  | 40                             |      |                            | dB      |

| Group Delay                                                           |                  | $f_{IN} = 1kHz$                                                                                  |                                | 9    |                            | Samples |

| SPEAKER OUTPUT CO                                                     | JRRENT SENS      | E ADC (Note 2)                                                                                   |                                |      |                            |         |

| Resolution                                                            |                  |                                                                                                  |                                | 16   |                            | Bits    |

| Sample Rate                                                           | $f_{S\_ISNS}$    |                                                                                                  | 8                              |      | 96                         | kHz     |

| Current Range                                                         | I <sub>SPK</sub> |                                                                                                  |                                | ±3   |                            | A       |

$(V_{PVDD}=5V~(1~\text{セル・モード})$  または 7.4V (2~セル・モード) 、 $V_{DD}=1.8V$ 、 $V_{GND}=V_{PGND}=0V$ 、 $C_{PVDD}=10\mu F+0.1\mu F$ 、 $C_{VDD}=1\mu F$ 、 $f_{BCLK}=3.072MHz$ 、 $f_{LRCLK}=48kHz$ 、 $Z_{SPK}=\infty$  (OUTP $\sim$ OUTN) 、1~セル・モード、AC 測定帯域幅 $=20Hz\sim20kHz$ 、 $T_A=T_{MIN}\sim T_{MAX}$ 、代表値は  $T_A=+25\%$  での値)(Note 1)

| PARAMETER                                                             | SYMBOL       | COND                                                                  | ITIONS                                                            | MIN                                                                                                                           | TYP  | MAX    | UNITS   |  |

|-----------------------------------------------------------------------|--------------|-----------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------|--------|---------|--|

| Dynamic Range                                                         | DNR          | $f_{IN} = 1$ kHz, unweighted                                          |                                                                   |                                                                                                                               | 73   |        | dB      |  |

|                                                                       |              | $f_{\mathrm{IN}} = 1 \mathrm{kHz},$                                   |                                                                   | $\begin{aligned} & \text{Single-cell mode,} \\ & V_{\text{PVDD}} = 5V, \\ & I_{\text{SPK}} = 0.6A_{\text{RMS}} \end{aligned}$ |      | -59    |         |  |

| Total Harmonic                                                        | THEAT        | $Z_{LOAD} = 4\Omega + 33\mu H$                                        | $Two\text{-cell mode}, \\ V_{PVDD} = 7.4V, \\ I_{SPK} = 1A_{RMS}$ |                                                                                                                               | -63  |        | - dB    |  |

| Distortion + Noise                                                    | THD⊤N        | THD+N $f_{IN} = 1kHz,$                                                | Single-cell mode,<br>$V_{PVDD} = 5V$ ,<br>$I_{SPK} = 0.3A_{RMS}$  |                                                                                                                               | -54  |        | ав      |  |

|                                                                       |              | $Z_{LOAD} = 8\Omega + 33\mu H$                                        | Two-cell mode,<br>$V_{PVDD} = 7.4V$ ,<br>$I_{SPK} = 0.5A_{RMS}$   |                                                                                                                               | -59  |        |         |  |

| Differential Mode Gain                                                |              | Open loop current sense                                               | channel response                                                  | 0.98                                                                                                                          |      | 1.02   |         |  |

| Differential Mode Gain<br>Variability                                 |              | Across supply, $T_A = -40$                                            | )°C to +85°C (Note 4)                                             | -2.5                                                                                                                          |      | +2.5   | %       |  |

| Maximum Common<br>Mode Gain                                           |              |                                                                       |                                                                   |                                                                                                                               | -60  |        | dB      |  |

| Highpass Cutoff<br>Frequency                                          |              | -3dB limit, across all sa                                             | mple rates                                                        | 2                                                                                                                             |      |        | Hz      |  |

|                                                                       |              | DC blocking filter enabl                                              | DC blocking filter enabled, $T_A = +25$ °C                        |                                                                                                                               |      | +0.12  |         |  |

| DC Offset Current                                                     |              | DC blocking filter disabled, $T_A = +25$ °C                           | $MAX98388, V_{PVDD} = 3.7V, single-cell mode$                     | -2                                                                                                                            |      | +2     | mA      |  |

|                                                                       |              | DC blocking filter disabled, T <sub>A</sub> = +25°C                   | $MAX98389, V_{PVDD} = 7.4V, two-cell mode$                        | -4                                                                                                                            |      | +4     |         |  |

| Voltage and Current<br>Accuracy Drift Tracking                        |              | $T_A = 0$ °C to +85°C, rela                                           | tive to +25°C                                                     |                                                                                                                               | 0.4  |        | %       |  |

| Speaker Amplifier Voltage to Current                                  |              | MAX98388,<br>f <sub>IN</sub> = 1kHz                                   | Single-cell mode                                                  |                                                                                                                               | -80  |        | dB      |  |

| Sense Crosstalk                                                       |              | $MAX98389,$ $f_{IN} = 1kHz$                                           | Two-cell mode                                                     |                                                                                                                               | -75  |        | ав      |  |

| Power Supply<br>Feedthrough                                           | PSF          | No input signal, AC rela $f_{RIPPLE} = 1 \text{kHz}$ , $V_{RIPPLE} =$ |                                                                   |                                                                                                                               | 65   |        | dB      |  |

| Max Current Sense to<br>Voltage Feedback<br>Channel Phase<br>Mismatch |              | $f_{IN} = 1 \text{kHz}$                                               |                                                                   |                                                                                                                               | 0.05 |        | Samples |  |

| Max Device to Device<br>Current Sense Channel<br>Phase Mismatch       |              | $f_{IN} = 1kHz$                                                       |                                                                   |                                                                                                                               | 0.05 |        | Samples |  |

| SPEAKER OUTPUT CU                                                     | IRRENT ADC / | DIGITAL FILTER CHAR                                                   | ACTERISTICS (f <sub>s</sub> < 50                                  | kHz) (Note 2)                                                                                                                 |      |        |         |  |

| Passband Ripple                                                       |              | $f_{IN} \leq f_{PLP}$                                                 |                                                                   | -0.225                                                                                                                        |      | +0.225 | dB      |  |

| Lowpass Filter Cutoff<br>Frequency                                    | $f_{PLP}$    | −3dB limit                                                            |                                                                   | $0.44 \times f_S$                                                                                                             |      |        | Hz      |  |

$(V_{PVDD}=5V~(1~\text{セル・モード})$  または 7.4V~(2~セル・モード) 、 $V_{DD}=1.8V$ 、 $V_{GND}=V_{PGND}=0V$ 、 $C_{PVDD}=10\mu F+0.1\mu F$ 、 $C_{VDD}=1\mu F$ 、 $f_{BCLK}=3.072MHz$ 、 $f_{LRCLK}=48kHz$ 、 $Z_{SPK}=\infty$  (OUTP $\sim$ OUTN) 、1~セル・モード、AC 測定帯域幅 $=20Hz\sim20kHz$ 、 $T_A=T_{MIN}\sim T_{MAX}$ 、代表値は  $T_A=+25\%$  での値)(Note 1)

| PARAMETER                              | SYMBOL            | COND                                | ITIONS                             | MIN                   | TYP   | MAX                        | UNITS   |  |

|----------------------------------------|-------------------|-------------------------------------|------------------------------------|-----------------------|-------|----------------------------|---------|--|

| Lowpass Filter<br>Stopband Frequency   | $ m f_{SLP}$      | -40dB limit                         |                                    |                       |       | $0.58 \times f_{\text{S}}$ | Hz      |  |

| Lowpass Filter<br>Stopband Attenuation |                   |                                     |                                    | 40                    |       |                            | dB      |  |

| Max Group Delay                        |                   | $f_{IN} = 1kHz$                     |                                    |                       | 8     |                            | Samples |  |

| SPEAKER OUTPUT CU                      | JRRENT ADC / I    | DIGITAL FILTER CHAR                 | ACTERISTICS (f <sub>S</sub> ≥ 50kł | Hz) (Note 2)          |       |                            |         |  |

| Passband Ripple                        |                   | $f_{\text{IN}} \leq f_{\text{PLP}}$ |                                    | -0.225                |       | +0.225                     | dB      |  |

| Lowpass Filter Cutoff<br>Frequency     | $f_{	ext{PLP}}$   | Droop < -3dB, 88.2kHz               | $z \le f_S \le 96 \text{kHz}$      | $0.23 \times f_s$     |       |                            | Hz      |  |

| Lowpass Filter<br>Stopband Frequency   | $ m f_{SLP}$      | -40dB limit                         |                                    |                       |       | $0.58 \times f_S$          | Hz      |  |

| Lowpass Filter<br>Stopband Attenuation |                   |                                     |                                    | 40                    |       |                            | dB      |  |

| Max Group Delay                        |                   | $f_{IN} = 1kHz$                     |                                    |                       | 9     |                            | Samples |  |