# **GaN FET 向け低 IQ、デュアル、** 2 相同期整流式降圧コントローラ

#### 特長

- ▶ GaN FET 向けに全面的に最適化された GaN 駆動テクノロジ

- ▶ 広い V<sub>IN</sub> 範囲: 4V~100V

- ▶ 広い出力電圧範囲: 0.8V ≤ V<sub>OUT</sub> ≤ 60V

- ▶ キャッチ/クランプ/ブートストラップ・ダイオード不要

- ▶ 内蔵のスマート・ブートストラップ・スイッチにより、 ハイサイド・ドライバ用電源の過充電を防止

- ▶ ほぼゼロになるよう内部で最適化されたスマート・デッド・ タイム、または抵抗により調整可能なデッド・タイム

- ▶ ゲート・ドライバの分割出力により、ドライバ強度設定の オン/オフが調整可能

- ▶ 調整可能で正確なドライバ電圧と UVLO

- ▶ 低 I<sub>Q</sub>: 5µA(48V<sub>IN</sub>から5V<sub>OUT</sub>まで、Ch1がオンの時)

- ▶ 設定可能周波数(100kHz~3MHz)

- ▶ 同期可能周波数(100kHz~3MHz)

- ▶ スペクトラム拡散周波数変調

- ▶ 40 ピン(6mm × 6mm)、サイド・ウェッタブル、 QFN パッケージ

# アプリケーション

- ▶ 産業用電源システム

- ▶ 防衛アビオニクス (航空電子機器) および医療用システム

- ▶ 電気通信用電源システム

#### 概要

LTC7890 は高性能のデュアル降圧 DC/DC スイッチング・レギュレータ・コントローラで、あらゆる N チャンネル同期窒化ガリウム (GaN) 電界効果トランジスタ (FET) のパワー段を入力電圧から最大 100V まで駆動できます。LTC7890 により、GaN FET 使用時に直面していた従来の課題の多くが解決されます。LTC7890 を使用すると、シリコン金属酸化膜半導体電界効果トランジスタ (MOSFET) ソリューションと比べてアプリケーション設計が簡素化すると同時に、保護ダイオードやその他の追加外付け部品が不要になります。

内蔵のスマート・ブートストラップ・スイッチにより、デッド・タイム時のBOOSTx ピンから SWx ピンのハイサイド・ドライバ電源への過充電を防止して、上側 GaN FET のゲートを保護できます。LTC7890 では、両方のスイッチング・エッジでゲート・ドライバのタイミングを内部で最適化して、デッド・タイムをほぼゼロにするスマート・ニア・ゼロ機能を実現しています。そのため、効率が大幅に向上し、入力電圧が大きい場合でも高周波数動作が可能になります。または、外付け抵抗を使用してデッド・タイムを調整し、マージンを確保したり、アプリケーションに適合させたりすることもできます。

LTC7890 のゲート駆動電圧を  $4V\sim5.5V$  の間で正確に調節できるため、性能を最適化でき、また、様々な GaN FET またはロジック・レベルの MOSFET を使用できます。

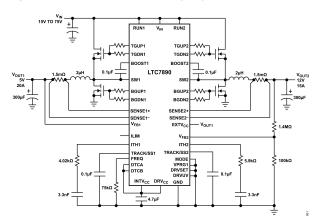

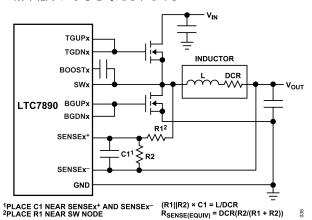

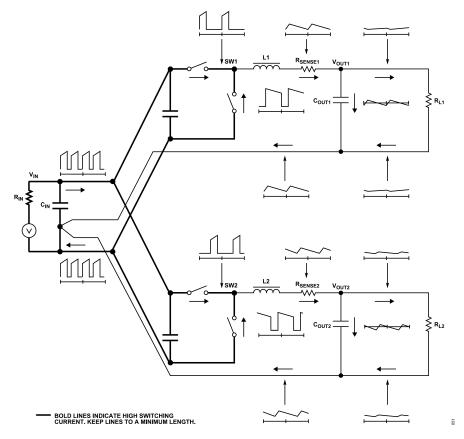

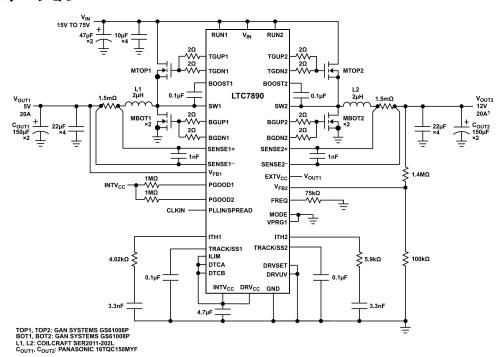

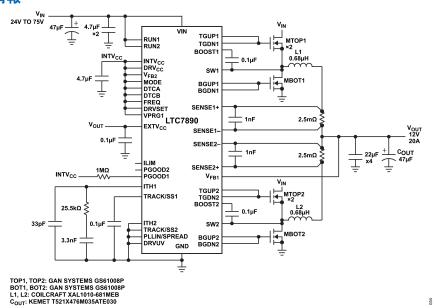

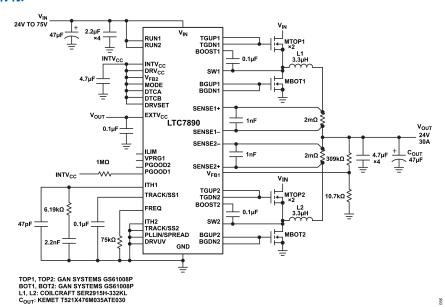

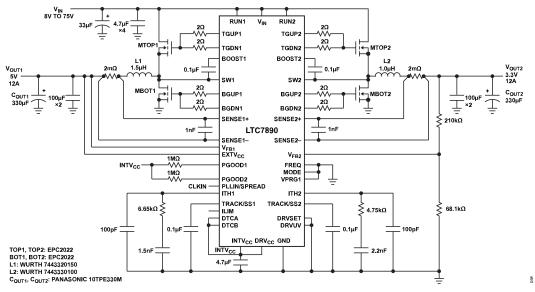

# 代表的なアプリケーション回路

図 1. 代表的なアプリケーション回路

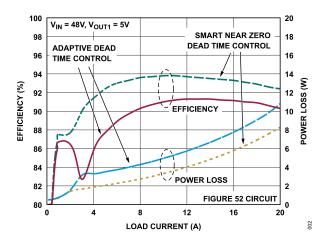

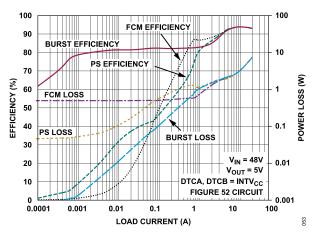

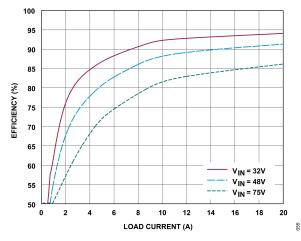

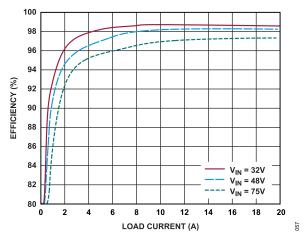

図 2. 効率および電力損失と負荷電流の関係

このデータシートでは、PLLIN/SPREAD などの多機能ピンについてはすべてのピン名を表記しますが、特定の機能のみが該当するような説明箇所では、PLLIN のように 1 つのピン機能だけを表記しています。

Rev 0

# 目次

| 特長1                                                        |

|------------------------------------------------------------|

| アプリケーション1                                                  |

| 代表的なアプリケーション回路1                                            |

| 概要1                                                        |

| 仕様                                                         |

| 電気的特性3                                                     |

| 絶対最大定格                                                     |

| ESD に関する注意                                                 |

| ピン配置およびピン機能の説明                                             |

| 代表的な性能特性10                                                 |

| 動作原理16                                                     |

| 機能図16                                                      |

| メイン制御ループ16                                                 |

| 電源とバイアス電源(V <sub>IN、EXTVcc、DRVcc、INTVcc) 16</sub>          |

| ハイサイド・ブートストラップ・コンデンサ17                                     |

| デッド・タイム制御(DTCA および DTCB ピン)17                              |

| 起動とシャットダウン(RUNx および TRACK/SSx ピン) 17                       |

| 軽負荷時の動作:バースト・モード動作、パルス・<br>スキップ・モード、強制連続モード(MODE ピン)18     |

| 周波数の選択、スペクトラム拡散、フェーズ・ロック・<br>ループ(FREQ および PLLIN/SPREAD ピン) |

| 出力過電圧保護19                                                  |

| フォールドバック電流19                                               |

| パワーグッド19                                                   |

| アプリケーション情報20                                               |

| インダクタ値の計算20                                                |

| インダクタ・コアの選択20                                              |

|                                                            |

|   | 電流検出方式の選択                              | 20 |

|---|----------------------------------------|----|

|   | 小さな値の抵抗による電流検出                         | 21 |

|   | インダクタの DCR による電流検出                     | 21 |

|   | 動作周波数の設定                               | 22 |

|   | 軽負荷時動作モードの選択                           | 22 |

|   | デッド・タイム制御(DTCA および DTCB ピン)            | 23 |

|   | パワーFET の選択                             | 24 |

|   | C <sub>IN</sub> と C <sub>OUT</sub> の選択 | 25 |

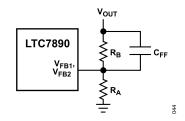

|   | 出力電圧の設定                                | 26 |

|   | RUNx ピンと低電圧ロックアウト                      | 26 |

|   | ソフト・スタートとトラッキング(TRACK/SSx ピン)          | 26 |

|   | 2 相単出力動作                               | 27 |

|   | INTV <sub>CC</sub> レギュレータ (OPTI-DRIVE) | 27 |

|   | 上側 FET ドライバ電源(C <sub>B</sub> )         | 29 |

|   | 最小オン時間に関する考慮事項                         | 29 |

|   | フォールト状態:電流制限とフォールドバック                  | 29 |

|   | フォールト状態:過電圧保護                          | 29 |

|   | フォールト状態: 過熱保護                          | 29 |

|   | フェーズ・ロック・ループと周波数同期                     | 29 |

|   | 効率に関する考慮事項                             | 30 |

|   | 過渡応答の確認                                | 30 |

|   | 設計例                                    | 31 |

|   | PCB レイアウトのチェックリスト                      | 32 |

|   | PCB レイアウトのデバッグ                         | 34 |

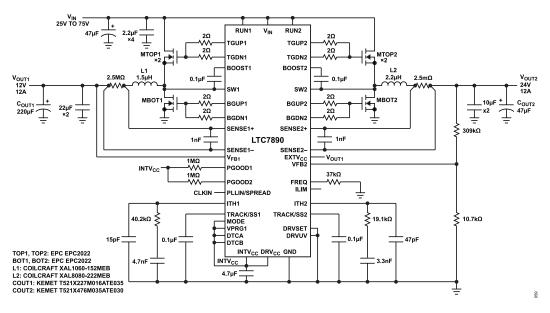

|   | 代表的なアプリケーション                           | 35 |

|   | 関連製品                                   | 39 |

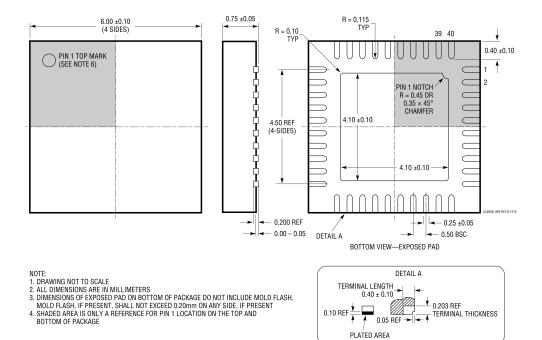

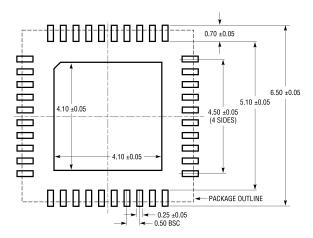

| 外 | 形寸法                                    | 40 |

|   | オーダー・ガイド                               | 40 |

|   | 評価用ボード                                 | 41 |

# 改訂履歴

4/2023—Revision 0: Initial Version

analog.com.jp Rev. 0 | 2 of 41

# 仕様

# 電気的特性

特に指定のない限り、 $T_J = -40^{\circ}\text{C} \sim +150^{\circ}\text{C}$ (最小値および最大値の場合)、 $T_A = 25^{\circ}\text{C}$ (代表値の場合)、 $V_{IN} = 12V$ 、RUN1 および RUN2 = 12V、VPRG1 = 7 ロート状態、EXTV $_{CC} = 0V$ 、DRVSET = 0V、DRVUV = 0V、TGUP1 = TGDN1 = TGxx1、BGUP1 = BGDN1 = BGxx1、TGUP2 = TGDN2 = TGxx2、BGUP2 = BGDN2 = BGxx2、DTCA および DTCB = 0V。

表 1. 電気的特性

| Parameter                                                      | Symbol                                | Test Conditions/Comments                                                   | Min   | Тур  | Max   | Unit |

|----------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------------|-------|------|-------|------|

| INPUT SUPPLY                                                   |                                       |                                                                            |       |      |       |      |

| Input Supply Operating Range                                   | V <sub>IN</sub>                       |                                                                            | 4     |      | 100   | V    |

| Total Quiescent Supply Current in Regulation                   | lQ                                    | 48 V to 5 V, no load, RUN2 = 0 V <sup>1</sup>                              |       | 5    |       | μA   |

|                                                                |                                       | 14 V to 3.3 V, no load, RUN2 = 0 V <sup>1</sup>                            |       | 14   |       | μA   |

| CONTROLLER OPERATION                                           |                                       |                                                                            |       |      |       |      |

| Regulated Output Voltage Set Point                             | V <sub>OUT1</sub> , V <sub>OUT2</sub> |                                                                            | 0.8   |      | 60    | V    |

| Channel 1 Regulated Feedback Voltage <sup>2</sup>              | V <sub>FB1</sub>                      | V <sub>IN</sub> = 4 V to 100 V, ITH1 voltage = 0.6 V to 1.2 V              |       |      |       |      |

|                                                                |                                       | VPRG1 = floating, T <sub>A</sub> = 25°C                                    | 0.792 | 8.0  | 0.808 | V    |

|                                                                |                                       | VPRG1 = floating                                                           | 0.788 | 8.0  | 0.812 | V    |

|                                                                |                                       | VPRG1 = 0 V                                                                | 4.925 | 5.0  | 5.075 | V    |

|                                                                |                                       | VPRG1 = INTV <sub>CC</sub>                                                 | 11.82 | 12   | 12.18 | V    |

| Channel 2 Regulated Feedback Voltage <sup>2</sup>              | V <sub>FB2</sub>                      | V <sub>IN</sub> = 4 V to 100 V, ITH2 voltage = 0.6 V to 1.2 V              |       |      |       |      |

|                                                                |                                       | T <sub>A</sub> = 25°C                                                      | 0.792 | 8.0  | 0.808 | V    |

|                                                                |                                       |                                                                            | 0.788 | 8.0  | 0.812 | V    |

| Channel 1 Feedback Current <sup>2</sup>                        |                                       | VPRG1 = floating, T <sub>A</sub> = 25°C                                    | -50   | 0    | +50   | nA   |

|                                                                |                                       | VPRG1 = 0 V or INTV <sub>CC</sub> , T <sub>A</sub> = 25°C                  |       | 1    | 2     | μA   |

| Channel 2 Feedback Current <sup>2</sup>                        |                                       | T <sub>A</sub> = 25°C                                                      | -50   | 0    | +50   | nA   |

| Feedback Overvoltage Threshold (Relative to V <sub>FBx</sub> ) |                                       | T <sub>A</sub> = 25°C                                                      | 7     | 10   | 13    | %    |

| Transconductance Amplifier <sup>2</sup>                        | g <sub>м1</sub> , g <sub>м2</sub>     | ITH1 and ITH2 = 1.2 V, sink and source current = 5 μA                      |       | 1.8  |       | mMho |

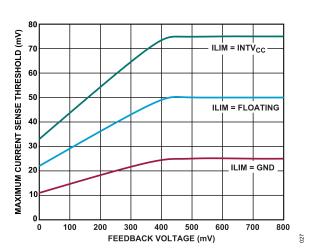

| Maximum Current Sense Threshold                                | V <sub>SENSE(MAX)</sub>               | V <sub>FBx</sub> = 0.7 V, SENSEx <sup>-</sup> = 3.3 V                      |       |      |       |      |

|                                                                |                                       | ILIM = 0 V                                                                 | 21    | 26   | 31    | mV   |

|                                                                |                                       | ILIM = floating                                                            | 45    | 50   | 55    | mV   |

|                                                                |                                       | ILIM = INTV <sub>CC</sub>                                                  | 67    | 75   | 83    | mV   |

| SENSE1 <sup>+</sup> and SENSE2 <sup>+</sup> Pin Current        | I <sub>SENSE1</sub> +,                | SENSE1 <sup>+</sup> and SENSE2 <sup>+</sup> = 3.3 V, T <sub>A</sub> = 25°C | -1    |      | +1    | μA   |

| SENSE1 <sup>-</sup> Pin Current                                | I <sub>SENSE1</sub> -                 | SENSE1 <sup>-</sup> < 3 V                                                  |       | 1    |       | μA   |

|                                                                |                                       | $3.2 \text{ V} \le \text{SENSE1}^- < \text{INTV}_{CC} - 0.5 \text{ V}$     |       | 75   |       | μA   |

|                                                                |                                       | SENSE1 <sup>-</sup> > INTV <sub>CC</sub> + 0.5 V                           |       | 725  |       | μA   |

| SENSE2 <sup>-</sup> Pin Current                                |                                       | SENSE2 <sup>-</sup> < INTV <sub>CC</sub> - 0.5 V                           | -2    |      | +2    | μA   |

|                                                                |                                       | SENSE2 <sup>-</sup> > INTV <sub>CC</sub> + 0.5 V                           |       | 650  |       | μA   |

| Soft Start Charge Current                                      |                                       | TRACK/SS1 and TRACK/SS2 = 0 V                                              | 9.5   | 12   | 14.5  | μA   |

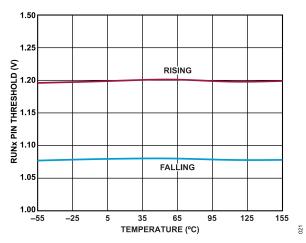

| RUNx Pin On Threshold                                          |                                       | RUNx rising                                                                | 1.15  | 1.20 | 1.25  | V    |

| RUNx Pin Hysteresis                                            |                                       |                                                                            |       | 120  |       | mV   |

| DC SUPPLY CURRENT                                              |                                       |                                                                            |       |      |       |      |

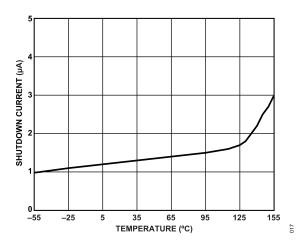

| V <sub>IN</sub> Shutdown Current                               |                                       | RUN1 and RUN2 = 0 V                                                        |       | 1    |       | μA   |

| V <sub>IN</sub> Sleep Mode Current                             |                                       | SENSE1 <sup>-</sup> < 3.2 V, EXTV <sub>CC</sub> = 0 V                      |       |      |       |      |

| One Channel On                                                 |                                       |                                                                            |       | 15   |       | μA   |

| Both Channels On                                               |                                       |                                                                            |       | 19   |       | μA   |

| Sleep Mode Current <sup>3</sup> , Only Channel 1 On            |                                       | SENSE1⁻≥3.2 V                                                              |       |      |       |      |

| V <sub>IN</sub> Current                                        |                                       | EXTV <sub>CC</sub> = 0 V                                                   |       | 5    |       | μA   |

| V <sub>IN</sub> Current                                        |                                       | EXTV <sub>CC</sub> ≥ 4.8 V                                                 |       | 1    |       | μA   |

| EXTV <sub>CC</sub> Current                                     |                                       | EXTV <sub>CC</sub> ≥ 4.8 V                                                 |       | 6    |       | μA   |

| SENSE1 <sup>-</sup> Current                                    |                                       |                                                                            |       | 10   |       | μA   |

analog.com.jp Rev. 0 | 3 of 41

# 仕様

# 表 1. 電気的特性(続き)

| Parameter                                                                  | Symbol               | Test Conditions/Comments                                                          | Min  | Тур  | Max  | Unit  |

|----------------------------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------|------|------|------|-------|

| Sleep Mode Current <sup>3</sup> , Both Channels On                         |                      | SENSE1 <sup>-</sup> ≥ 3.2 V, EXTV <sub>CC</sub> ≥ 4.8 V                           |      |      |      |       |

| V <sub>IN</sub> Current                                                    |                      |                                                                                   |      | 1    |      | μA    |

| EXTV <sub>CC</sub> Current                                                 |                      |                                                                                   |      | 7    |      | μA    |

| SENSE1 <sup>-</sup> Current                                                |                      |                                                                                   |      | 12   |      | μA    |

| Pulse Skipping (PS) or Forced Continuous Mode                              |                      |                                                                                   |      |      |      |       |

| (FCM), V <sub>IN</sub> or EXTV <sub>CC</sub> Current <sup>3</sup>          |                      |                                                                                   |      |      |      |       |

| One Channel On                                                             |                      |                                                                                   |      | 2    |      | mA    |

| Both Channels On                                                           |                      |                                                                                   |      | 3    |      | mA    |

| GATE DRIVERS                                                               |                      |                                                                                   |      |      |      | 11151 |

| TGxxx or BGxxx On Resistance                                               |                      | DRVSET = INTV <sub>CC</sub>                                                       |      |      |      |       |

| Pull-Up                                                                    |                      | DICOULT - HALAGO                                                                  |      | 2.0  |      | Ω     |

| Pull-Down                                                                  |                      |                                                                                   |      | 1.0  |      |       |

|                                                                            |                      | DDVCET - INTV                                                                     |      |      |      | Ω     |

| BOOSTx to DRV <sub>CC</sub> Switch On Resistance                           |                      | DRVSET = INTV <sub>CC</sub>                                                       |      | 7    |      | Ω     |

| TGxxx or BGxxx Transition Time <sup>4</sup>                                |                      |                                                                                   |      |      |      |       |

| Rise Time                                                                  |                      |                                                                                   |      | 25   |      | ns    |

| Fall Time                                                                  |                      |                                                                                   |      | 15   |      | ns    |

| TGxxx Off to BGxxx On Delay <sup>4</sup>                                   |                      | DTCA = 0 V                                                                        |      |      |      |       |

| Synchronous Switch On Delay Time                                           |                      |                                                                                   |      | 20   |      | ns    |

| BGxxx Off to TGxxx On Delay <sup>4</sup>                                   |                      | DTCB = 0 V                                                                        |      |      |      |       |

| Top Switch On Delay Time                                                   |                      |                                                                                   |      | 20   |      | ns    |

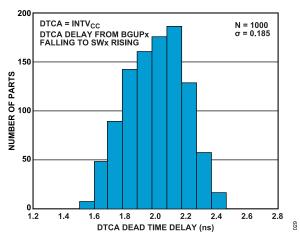

| BGxxx Falling to SWx Rising Delay <sup>5</sup>                             |                      | DTCB = INTV <sub>CC</sub> or resistor                                             |      |      |      |       |

|                                                                            |                      | DTCA = INTV <sub>CC</sub>                                                         |      | 2    |      | ns    |

|                                                                            |                      | DTCA = 50 kΩ                                                                      |      | 25   |      | ns    |

|                                                                            |                      | DTCA = 100 kΩ                                                                     |      | 40   |      | ns    |

| SWx Falling to BGxxx Rising Delay <sup>5</sup>                             |                      | DTCA = INTV <sub>CC</sub> or resistor                                             |      |      |      |       |

| 0 0,                                                                       |                      | DTCB = INTV <sub>CC</sub>                                                         |      | 0.5  |      | ns    |

|                                                                            |                      | DTCB = 50 kΩ                                                                      |      | 25   |      | ns    |

|                                                                            |                      | DTCB = 100 kΩ                                                                     |      | 40   |      | ns    |

| TGxxx Minimum On-Time <sup>6</sup>                                         | tonann               | 5105 100 N2                                                                       |      | 40   |      | ns    |

| Maximum Duty Cycle                                                         | t <sub>ON(MIN)</sub> | Output in dropout, FREQ = 0 V                                                     |      | 99   |      | %     |

| OW DROPOUT (LDO) LINEAR REGULATORS                                         |                      | Output in diopout, TNEQ = 0 V                                                     |      |      |      | 70    |

| INTV <sub>CC</sub> Voltage for V <sub>IN</sub> and EXTV <sub>CC</sub> LDOs |                      | EVTV = 0.V for V IDO 13.V for EVTV IDO                                            |      |      |      |       |

| INTIVES Approach of AIV and EVIACE FDO2                                    |                      | EXTV <sub>CC</sub> = 0 V for V <sub>IN</sub> LDO, 12 V for EXTV <sub>CC</sub> LDO | F 0  |      | F 7  | ,     |

|                                                                            |                      | DRVSET = INTV <sub>CC</sub>                                                       | 5.2  | 5.5  | 5.7  | V     |

|                                                                            |                      | DRVSET = 0 V                                                                      | 4.8  | 5.0  | 5.2  | V     |

|                                                                            |                      | DRVSET= 64.9 kΩ                                                                   | 4.5  | 4.75 | 5.0  | V     |

| DRV <sub>CC</sub> Load Regulation                                          |                      | DRV <sub>CC</sub> load current = 0 mA to 100 mA, T <sub>A</sub> = 25°C            |      | 1    | 3    | %     |

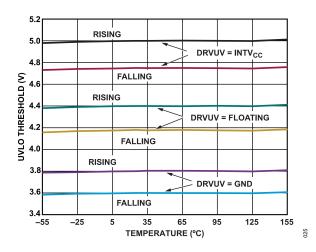

| Undervoltage Lockout                                                       | UVLO                 |                                                                                   |      |      |      |       |

| DRV <sub>CC</sub> Rising                                                   |                      | DRVUV = INTV <sub>CC</sub>                                                        | 4.8  | 5.0  | 5.2  | V     |

|                                                                            |                      | DRVUV = 0 V                                                                       | 3.6  | 3.8  | 4.0  | V     |

|                                                                            |                      | DRVUV = floating                                                                  | 4.2  | 4.4  | 4.6  | V     |

| DRV <sub>CC</sub> Falling                                                  |                      | DRVUV = INTV <sub>CC</sub>                                                        | 4.55 | 4.75 | 4.95 | V     |

|                                                                            |                      | DRVUV = 0 V                                                                       | 3.4  | 3.6  | 3.8  | V     |

|                                                                            |                      | DRVUV = floating                                                                  | 4.0  | 4.18 | 4.4  | V     |

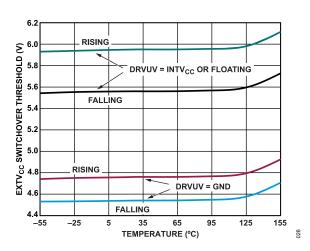

| EXTV <sub>CC</sub> LDO Switchover Voltage                                  |                      |                                                                                   |      |      |      |       |

| EXTV <sub>CC</sub> Rising                                                  |                      | DRVUV = INTV <sub>CC</sub> or floating, T <sub>A</sub> = 25°C                     | 5.75 | 5.95 | 6.15 | V     |

|                                                                            |                      | DRVUV = 0 V, T <sub>A</sub> = 25°C                                                | 4.6  | 4.76 | 4.9  | V     |

| EXTV <sub>CC</sub> Switchover Hysteresis                                   |                      | 5.11.5 V V, 1 <sub>A</sub> 20 0                                                   | 7.0  | 7.70 | 7.0  | *     |

|                                                                            |                      | DDV/IV/ = INTV/ or floating                                                       |      | 200  |      | m\/   |

| EXTV <sub>CC</sub> Falling                                                 |                      | DRVUV = INTV <sub>CC</sub> or floating                                            |      | 390  |      | mV    |

|                                                                            |                      | DRVUV = 0 V                                                                       |      | 220  |      | mV    |

analog.com.jp Rev. 0 | 4 of 41

# 仕様

表 1. 電気的特性(続き)

| Parameter                                                       | Symbol            | Test Conditions/Comments                     | Min | Тур  | Max        | Unit |

|-----------------------------------------------------------------|-------------------|----------------------------------------------|-----|------|------------|------|

| SPREAD SPECTRUM OSCILLATOR AND PHASE-LOCKED LOOP (PLL)          |                   |                                              |     |      |            |      |

| Fixed Frequency                                                 | fosc              | PLLIN/SPREAD = 0 V                           |     |      |            |      |

| Low Fixed Frequency                                             |                   | FREQ = 0 V, T <sub>A</sub> = 25°C            | 320 | 370  | 420        | kHz  |

| High Fixed Frequency                                            |                   | FREQ = INTV <sub>CC</sub>                    | 2.0 | 2.25 | 2.5        | MHz  |

| Programmable Frequency                                          |                   | FREQ = 374 kΩ                                |     | 100  |            | kHz  |

|                                                                 |                   | FREQ = 75 k $\Omega$ , T <sub>A</sub> = 25°C | 450 | 500  | 550        | kHz  |

|                                                                 |                   | FREQ = $12.5 \text{ k}\Omega$                |     | 3    |            | MHz  |

| Synchronizable Frequency Range                                  | f <sub>SYNC</sub> | PLLIN/SPREAD = external clock                | 0.1 |      | 3          | MHz  |

| PLLIN Input High Level                                          |                   |                                              | 2.2 |      |            | V    |

| PLLIN Input Low Level                                           |                   |                                              |     |      | 0.5        | V    |

| Spread Spectrum Frequency Range (Relative to f <sub>OSC</sub> ) |                   | PLLIN/SPREAD = INTV <sub>CC</sub>            |     |      |            |      |

| Minimum Frequency                                               |                   |                                              |     | 0    |            | %    |

| Maximum Frequency                                               |                   |                                              |     | 20   |            | %    |

| PGOODx OUTPUTS                                                  |                   |                                              |     |      |            |      |

| PGOODx Voltage Low                                              |                   | PGOODx = 2 mA, T <sub>A</sub> = 25°C         |     | 0.2  | 0.4        | V    |

| PGOODx Leakage Current                                          |                   | PGOODx = 5 V, T <sub>A</sub> = 25°C          |     |      | ±1         | μA   |

| PGOODx Trip Level (V <sub>FBx</sub> with Respect to Set         |                   | T <sub>A</sub> = 25°C                        |     |      |            |      |

| Regulated Voltage)                                              |                   |                                              |     |      |            | %    |

| V <sub>FBx</sub> Rising                                         |                   |                                              | 7   | 10   | 13         |      |

| Hysteresis                                                      |                   |                                              |     | 1.6  |            | %    |

| V <sub>FBx</sub> Falling                                        |                   |                                              | –13 | -10  | <b>–</b> 7 | %    |

| Hysteresis                                                      |                   |                                              |     | 1.6  |            | %    |

| PGOODx Delay for Reporting a Fault                              |                   |                                              |     | 25   |            | μs   |

<sup>「</sup>本仕様については出荷テストは行っていません。

analog.com.jp Rev. 0 | 5 of 41

$<sup>^2</sup>$  LTC7890 は帰還ループでテストされています。このループでは ITHx 電圧  $(V_{\rm ITHx})$  を仕様規定された電圧にサーボ制御して、得られた帰還電圧  $(V_{\rm FBx})$  を 測定しています。

$<sup>^3</sup>$  SENSEI-のバイアス電流は、 $I_{VIN}=I_{SENSEI}- imes V_{OUTI}/(V_{IN} imes\eta)$ ( $\eta$  は効率)の式に従って入力電源に反映されます。

<sup>4</sup>立上がり時間と立下がり時間は、10%と90%のレベルで測定しています。遅延時間は50%レベルで測定しています。

$<sup>^5</sup>$  SWx の立下がりから BGxxx の立上がりまで、および BGxxx の立下がりから SWx の立上がりまでの遅延時間は、SWx と BGxxx の立上がり関値と立下がり 関値が約 1V の時に測定しています。 図 41 と図 42 を参照してください。

$<sup>^6</sup>$ インダクタのピーク to ピーク・リップル電流に対して仕様規定される最小オン時間条件は、最大負荷電流( $I_{MAX}$ )の 40%以上です(最小オン時間に関する考慮事項のセクションを参照)。

# 絶対最大定格

#### 表 2. 絶対最大定格

| Parameter                                                                                    | Rating             |

|----------------------------------------------------------------------------------------------|--------------------|

| Input Supply (V <sub>IN</sub> )                                                              | -0.3 V to +100 V   |

| RUN1 and RUN2                                                                                | –0.3 V to +100 V   |

| BOOST1 and BOOST2                                                                            | –0.3 V to +106 V   |

| SW1 and SW2                                                                                  | –5 V to +100 V     |

| BOOST1 to SW1 and BOOST2 to SW2                                                              | –0.3 V to +6 V     |

| BGUP1, BGDN1, BGUP2, and BGDN2 <sup>1</sup>                                                  | Not applicable     |

| TGUP1, TGDN1, TGUP2, and TGDN2 <sup>1</sup>                                                  | Not applicable     |

| EXTV <sub>CC</sub>                                                                           | –0.3 V to +30 V    |

| $DRV_CC$ and $INTV_CC$                                                                       | –0.3 V to +6 V     |

| $V_{FB1}$                                                                                    | –0.3 V to +15 V    |

| $V_{FB2}$                                                                                    | –0.3 V to +6 V     |

| PLLIN/SPREAD and FREQ                                                                        | –0.3 V to +6 V     |

| TRACK/SS1, TRACK/SS2, ITH1, and ITH2                                                         | -0.3 V to +6 V     |

| DRVSET and DRVUV                                                                             | –0.3 V to +6 V     |

| MODE, ILIM, and VPRG1                                                                        | –0.3 V to +6 V     |

| PGOOD1 and PGOOD2                                                                            | –0.3 V to +6 V     |

| DTCA and DTCB                                                                                | –0.3 V to +6 V     |

| SENSE1 <sup>+</sup> , SENSE2 <sup>+</sup> , SENSE1 <sup>-</sup> , and SENSE2 <sup>-</sup>    | –0.3 V to +65 V    |

| SENSE1 <sup>+</sup> to SENSE1 <sup>-</sup> and SENSE2 <sup>+</sup> to<br>SENSE2 <sup>-</sup> |                    |

| Continuous                                                                                   | –0.3 V to +0.3 V   |

| <1 ms                                                                                        | -100 mA to +100 mA |

| Operating Junction Temperature Range <sup>2</sup>                                            | -40°C to +150°C    |

| Storage Temperature Range                                                                    | -65°C to +150°C    |

<sup>「</sup>これらのピンには電圧も電流も印加しないでください。 容量性負荷に のみ接続してください。これを行わない場合、恒久的な損傷が生じる おそれがあります。

上記の絶対最大定格を超えるストレスを加えると、デバイスに 恒久的な損傷を与えることがあります。この規定はストレス定 格のみを指定するものであり、この仕様の動作のセクションに 記載する規定値以上でのデバイス動作を定めたものではありま せん。デバイスを長時間にわたり絶対最大定格状態に置くと、 デバイスの信頼性に影響を与えることがあります。

# ESD に関する注意

ESD(静電放電)の影響を受けやすいデバイスです。

電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術であるESD保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

analog.com.jp Rev. 0 | 6 of 41

<sup>&</sup>lt;sup>2</sup> LTC7890 は、 $-40^{\circ}$ C~ $150^{\circ}$ C の動作ジャンクション温度範囲で仕様規定されています。 ジャンクション温度が高い場合は動作寿命が低下します。ここに示す仕様に見合った最大周囲温度は、具体的な動作条件と、ボード・レイアウト、パッケージの熱抵抗定格値、およびその他の環境条件の組み合わせによって決まります。ジャンクション温度 ( $T_J$ 、 $^{\circ}$ C 単位) は、次式により周囲温度 ( $T_A$   $^{\circ}$ C 単位) と消費電力 ( $P_D$ 、ワット単位) から計算します。 $T_J = T_A + (P_D \times \theta_{JA})$ 。ここで、 $\theta_{JA}$ はパッケージの熱抵抗で、40 ピン( $6mm \times 6mm$ )、サイド・ウェッタブル、クワッド・フラット・ノー・リード(QFN)パッケージの場合、 $34^{\circ}$ C/W に相当します。

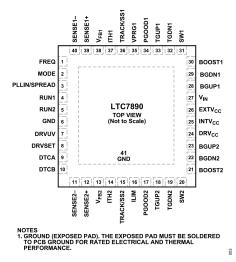

# ピン配置およびピン機能の説明

図 3. ピン配置

表 3. ピン機能の説明

| ピン <b>番号</b> | 記号                  | 説明                                                                                                                                                                                                                                                                                                                                                                           |

|--------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

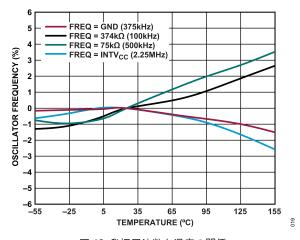

| 1            | FREQ                | 内部電圧制御発振器(VCO)の周波数制御ピン。FREQ を GND に接続すると、370kHz の周波数に固定されます。FREQ を INTVcc に接続すると、2.25MHz の周波数に固定されます。FREQ と GND の間に抵抗を接続すると、100kHz~3MHz の範囲で周波数を設定できます。FREQ の容量は最小限に抑えてください。                                                                                                                                                                                                 |

| 2            | MODE                | モード・セレクト入力。この入力により、LTC7890の軽負荷時の動作が決まります。MODE を GND に接続すると、Burst Mode®の動作が選択されます。MODE がフロート状態の場合、GND に接続された 100kΩ の内部抵抗によって、バースト・モード動作が選択されます。MODE を INTVcc に接続すると、連続インダクタ電流動作になります。MODE を 100kΩ の抵抗を介して INTVcc に接続すると、パルス・スキッピング動作が選択されます。                                                                                                                                  |

| 3            | PLLIN/SPREAD        | 位相検出器/スペクトラム拡散への外部同期入力イネーブル。外部クロックを PLLIN/SPREAD に印加すると、PLL は TGxx1 信号の立上がりを外部クロックの立上がりエッジに強制的に同期させます。外部クロックに同期させない場合、この 入力を INTVcc に接続すると、発振器のスペクトラム拡散ディザリングが有効になり、GND に接続すると、スペクトラム拡散が無効になります。                                                                                                                                                                             |

| 4            | RUN1                | チャンネル 1 の実行制御入力。RUN1 を 1.08V 未満にすると、コントローラのスイッチングがディスエーブルされます。<br>RUN1 と RUN2 を 0.7V 未満にすると、LTC7890 がシャットダウンし、Io が約 1μA に低下します。RUN1 ピンを VIN に接続すると常時オン動作になります。                                                                                                                                                                                                               |

| 5            | RUN2                | チャンネル 2 の実行制御入力。RUN2 を 1.08V 未満にすると、コントローラのスイッチングがディスエーブルされます。 RUN1 と RUN2 を 0.7V 未満にすると、LTC7890 がシャットダウンし、 $I_0$ が約 1 $\mu$ A に低下します。RUN2 ピンを $V_{IN}$ に接続すると常時オン動作になります。                                                                                                                                                                                                   |

| 6            | GND                 | グラウンド。定格の電気的および熱的性能を得るには、GNDピンと露出パッドをPCBのグラウンドにハンダ付けする必要があります。                                                                                                                                                                                                                                                                                                               |

| 7            | DRVUV               | DRVcc UVLO および EXTVcc の切替え設定ピン。DRVUV は、表 1 に示すように、INTVcc UVLO および EXTVcc の立上がり および立下がりの切替え閾値を指定します。                                                                                                                                                                                                                                                                          |

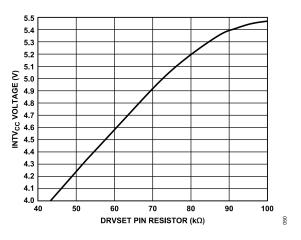

| 8            | DRVSET              | $INTV_{CC}$ のレギュレーション設定ピン。 $DRVSET$ は、 $INTV_{CC}$ LDO リニア電圧レギュレータのレギュレーション・ポイントを設定します。 $DRVSET$ を $GND$ に接続すると、 $INTV_{CC}$ は 5V に設定されます。 $DRVSET$ を $INTV_{CC}$ に接続すると、 $INTV_{CC}$ は 5.5V に設定されます。 $DRVSET$ と $GND$ の間に抵抗( $50k\Omega\sim110k\Omega$ )を配置すると、 $4V\sim5.5V$ の電圧を設定できます。この抵抗と $20\mu A$ の内部ソース電流により、 $INTV_{CC}$ LDO レギュレータがレギュレーション・ポイントを設定するための電圧が生成されます。 |

| 9            | DTCA                | 下側 FET のオフから上側 FET のオンまでの遅延用デッド・タイム制御ピン。DTCA を GND に接続すると、約 20ns の適応型デッド・タイム遅延が設定されます。DTCA を INTV $_{\rm CC}$ に接続すると、BGUPx の立下がりから SWx の立上がりまでの遅延にスマート・ニア・ゼロ遅延が設定されます。DTCA と GND の間に $10k\Omega\sim200k\Omega$ の抵抗を接続すると、BGUPx の立下がりから SWx の立上がりまでの間に更に遅延( $7ns\sim60ns$ )が追加されます。この設定は両チャンネルに適用されます。                                                                        |

| 10           | DTCB                | 上側 FET のオフから下側 FET のオンまでの遅延用デッド・タイム制御ピン。DTCB を GND に接続すると、約 20ns の適応型デッド・タイム遅延が設定されます。DTCB を INTV $_{\rm CC}$ に接続すると、SWx の立下がりから BGDNx の立上がりまでの間の遅延にスマート・ニア・ゼロ遅延が設定されます。DTCB と GND の間に $10k\Omega\sim200k\Omega$ の抵抗を接続すると、SWx の立下がりから BGDNx の立上がりまでの間に更に遅延( $7ns\sim60ns$ )が追加されます。この設定は両チャンネルに適用されます。                                                                      |

| 11           | SENSE2 <sup>-</sup> | チャンネル2の差動電流コンパレータへの負入力。SENSE2⁻ピンは、SENSE2⁻が INTVccより大きい時に、チャンネル2の<br>電流コンパレータに電流を供給します。                                                                                                                                                                                                                                                                                       |

| 12           | SENSE2 <sup>+</sup> | チャンネル 2 の差動電流コンパレータへの正入力。ITH2 ピンの電圧および SENSE2 <sup>-</sup> ピンと SENSE2 <sup>-</sup> ピンの間の制御されたオフセットは、電流検出抵抗(R <sub>SENSE</sub> )と組み合わせて電流トリップ閾値を設定します。                                                                                                                                                                                                                        |

analog.com.jp Rev. 0 | 7 of 41

# ピン配置およびピン機能の説明

# 表 3. ピン機能の説明(続き)

| ピン番号 | 記号              | 説明                                                                                                                                                                                                                                                                                                                                  |

|------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13   | $V_{FB2}$       | チャンネル2のエラー・アンプ帰還入力。 $V_{FB2}$ は、リモートセンシングされたチャンネル2の帰還電圧を、出力両端に接続された外付け抵抗分圧器から受け取ります。両チャンネルが $V_{FB1}$ 、ITH1、および TRACK/SS1 を共有する 2 相単出力アプリケーションの場合は、 $V_{FB2}$ を INT $V_{CC}$ に接続します。                                                                                                                                                |

| 14   | ITH2            | チャンネル2のエラー・アンプ出力とスイッチング・レギュレータの補償ポイント。電流コンパレータのトリップ・ポイントは、この制御電圧に応じて増加します。                                                                                                                                                                                                                                                          |

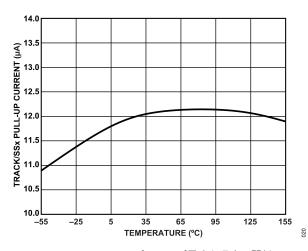

| 15   | TRACK/SS2       | チャンネル 2 の外部トラッキング/ソフト・スタート入力。TRACK/SS2 は、V <sub>FB2</sub> 電圧を 0.8V または TRACK/SS2 ピンの電圧のいずれか低い方にレギュレーションします。TRACK/SS2 には 12μA の内部プルアップ電流源が接続されています。TRACK/SS2 と GND の間に接続するコンデンサにより、最終のレギュレーション出力電圧までの立上がり時間が設定されます。立上がり時間は、12.5nF の静電容量ごとに 1ms です。または、TRACK/SS2 に他の電源の抵抗分圧器を接続すると、起動時に出力が他の電源に追従します。                                 |

| 16   | ILIM            | 電流コンパレータの検出電圧範囲入力。ILIM を GND または INTVcc に接続するか、ILIM をフロート状態にすることで、最大電流検出閾値を 3 つのレベル(それぞれ 25mV、75mV、50mV)のいずれかに設定します。                                                                                                                                                                                                                |

| 17   | PGOOD2          | チャンネル2のパワーグッド・オープンドレイン・ロジック出力。PGOOD2は、V <sub>FB2</sub> 電圧が設定値の±10%以内にない場合、GNDにプルダウンされます。                                                                                                                                                                                                                                            |

| 18   | TGUP2           | チャンネル2の上側 FET 用高電流ゲート・ドライバ・プルアップ。TGUP2 は BOOST2 にプルアップします。TGUP2 を上側 FET のゲートに直接接続すると、ゲートの立上がりエッジでゲート駆動の遷移速度が最大になります。TGUP2 と上側 FET ゲートの間に抵抗を接続すると、ゲートの立上がりスルー・レートを調整できます。                                                                                                                                                            |

| 19   | TGDN2           | チャンネル2の上側 FET 用高電流ゲート・ドライバ・プルダウン。TGDN2 は SW2 にプルダウンします。TGDN2 を上側 FET のゲートに直接接続すると、ゲートの立下がりエッジでゲート駆動の遷移速度が最大になります。TGDN2 と上側 FET ゲートの間に抵抗を接続すると、ゲートの立下がりスルー・レートを調整できます。                                                                                                                                                               |

| 20   | SW2             | チャンネル2のインダクタへのスイッチ・ノード接続。                                                                                                                                                                                                                                                                                                           |

| 21   | BOOST2          | チャンネル 2 の上側フローティング・ドライバへのブートストラップ電源。BOOST2 ピンと SW2 ピンの間にコンデンサを接続します。下側 FET がオンになると、内部スイッチが DRVcc から BOOST2 ピンに電源を供給します。BOOST2 ピンの電圧振幅は DRVcc から(V <sub>IN</sub> + DRVcc)までです。                                                                                                                                                       |

| 22   | BGDN2           | チャンネル2の下側 FET 用高電流ゲート・ドライバ・プルダウン。BGDN2 は GND にプルダウンします。BGDN2 を下側 FET のゲートに直接接続すると、ゲートの立下がりエッジでゲート駆動の遷移速度が最大になります。BGDN2 と下側 FET ゲートの間に抵抗を接続すると、ゲートの立下がりスルー・レートを調整できます。BGDN2 は、ターンオン時における下側 FET ゲートのケルビン検出としても機能します。                                                                                                                  |

| 23   | BGUP2           | チャンネル2の下側 FET 用高電流ゲート・ドライバ・プルアップ。BGUP2 は DRVcc にプルアップします。BGUP2 を下側 FET のゲートに直接接続すると、ゲートの立上がりエッジでゲート駆動の遷移速度が最大になります。BGUP2 と下側 FET ゲートの間に抵抗を接続すると、ゲートの立上がりスルー・レートを調整できます。BGUP2 は、ターンオフ時における下側 FET ゲートのケルビン検出としても機能します。                                                                                                                |

| 24   | DRVcc           | ゲート・ドライバ電源ピン。ゲート・ドライバは DRV <sub>CC</sub> から給電されます。DRV <sub>CC</sub> を INTV <sub>CC</sub> まで、INTV <sub>CC</sub> バイパス・コンデンサへのパターンとは別のパターンで接続します。                                                                                                                                                                                      |

| 25   | INTVcc          | 内部 LDO レギュレータの出力。INTVccの電圧レギュレーション・ポイントは DRVSET ピンで設定します。INTVccは、4.7μF~10μF のセラミック・コンデンサまたは他の等価直列抵抗(ESR)の低いコンデンサで GND にデカップリングする必要があります。                                                                                                                                                                                            |

| 26   | EXTVcc          | DRVCC に接続されている内部 LDO レギュレータへの外部電源入力。この LDO レギュレータは INTVcc に電力を供給し、EXTVcc が EXTVcc 切替え電圧より高い時は常に内部の V <sub>IN</sub> LDO レギュレータをバイパスします。電源とバイアス電源 (V <sub>IN、EXTVcc、DRVcc、INTVcc)</sub> のセクションと INTVcc レギュレータ (OPTI-DRIVE) のセクションにおける EXTVcc の接続を参照してください。EXTVcc は 30V を超えないようにしてください。EXTVcc LDO レギュレータを使用しない場合は、EXTVcc を GND に接続します。 |

| 27   | V <sub>IN</sub> | 主電源ピン。V <sub>IN</sub> と GND の間にバイパス・コンデンサを接続する必要があります。                                                                                                                                                                                                                                                                              |

| 28   | BGUP1           | チャンネル1の下側 FET 用高電流ゲート・ドライバ・プルアップ。BGUP1 は DRVcc にプルアップします。BGUP1 を下側 FET のゲートに直接接続すると、ゲートの立上がりエッジでゲート駆動の遷移速度が最大になります。BGUP1 とボトム FET ゲートの間に抵抗を接続すると、ゲートの立上がりスルー・レートを調整できます。BGUP1 は、ターンオフ時におけるボトム FET ゲートのケルビン検出としても機能します。                                                                                                              |

| 29   | BGDN1           | チャンネル 1 の下側 FET 用高電流ゲート・ドライバ・プルダウン。BGDN1 は GND にプルダウンします。BGDN1 を下側 FET のゲートに直接接続すると、ゲートの立下がりエッジでゲート駆動の遷移速度が最大になります。BGDN1 と下側 FET ゲートの間に抵抗を接続すると、ゲートの立下がりスルー・レートを調整できます。BGDN1 は、ターンオン時における下側 FET ゲートのケルビン検出としても機能します。                                                                                                                |

| 30   | BOOST1          | チャンネル1の上側フローティング・ドライバへのブートストラップ電源。BOOST1 ピンと SW1 ピンの間にコンデンサを接続します。下側 FET がオンになると、内部スイッチが DRVcc から BOOST1 ピンに電源を供給します。BOOST1 ピンの電圧振幅は DRVcc から(V <sub>IN</sub> + DRVcc)までです。                                                                                                                                                         |

| 31   | SW1             | チャンネル1のインダクタへのスイッチ・ノード接続。                                                                                                                                                                                                                                                                                                           |

| 32   | TGDN1           | チャンネル1の上側 FET 用高電流ゲート・ドライバ・プルダウン。TGDN1 は SW1 にプルダウンします。TGDN1 を上側 FET のゲートに直接接続すると、ゲートの立下がりエッジでゲート駆動の遷移速度が最大になります。TGDN1 と上側 FET ゲートの間に抵抗を接続すると、ゲートの立下がりスルー・レートを調整できます。                                                                                                                                                               |

| 33   | TGUP1           | チャンネル1の上側 FET 用高電流ゲート・ドライバ・プルアップ。TGUP1 は BOOST1 にプルアップします。TGUP1 を上側 FET のゲートに直接接続すると、ゲートの立上がりエッジでゲート駆動の遷移速度が最大になります。TGUP1 と上側 FET ゲートの間に抵抗を接続すると、ゲートの立上がりスルー・レートを調整できます。                                                                                                                                                            |

| 34   | PGOOD1          | チャンネル 1 のパワーグッド・オープンドレイン・ロジック出力。PGOOD1 は、V <sub>FB1</sub> 電圧が設定値の±10%以内にないとき、GND にプルダウンされます。                                                                                                                                                                                                                                        |

analog.com.jp Rev. 0 | 8 of 41

# ピン配置およびピン機能の説明

# 表 3. ピン機能の説明(続き)

| ピン番号 | 記 <del>号</del>      | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

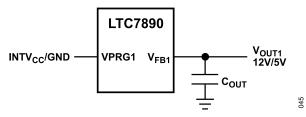

| 35   | VPRG1               | チャンネル 1 の出力電圧制御ビン。VPRG1 は、チャンネル 1 を外付け帰還抵抗で調整可能な出力モードにするか、12V または 5V の固定出力モードにするかを設定します。VPRG1 をフロート状態にすると、外付けの抵抗分圧器で出力が 0.8V~60V の範囲に設定され、VFB1が 0.8V にレギュレーションされます。VPRG1 を INTVcc または GND に接続すると、VFB1 の内部抵抗分圧器を介して、出力がそれぞれ 12V または 5V に設定されます。                                                                                                                                                                                                                                                                                                  |

| 36   | TRACK/SS1           | チャンネル 1 の外部トラッキング/ソフト・スタート入力。TRACK/SS1 は、 $V_{FB1}$ 電圧を $0.8V$ または TRACK/SS1 ピンの電圧のいずれか低い方にレギュレーションします。TRACK/SS1 には $12\mu$ A の内部プルアップ電流源が接続されています。 TRACK/SS1 と GND の間に接続するコンデンサにより、最終のレギュレーション出力電圧までの立上がり時間が設定されます。立上がり時間は、 $12.5$ nF の静電容量ごとに $1$ ms です。または、 $12.5$ nF の静電容量ごとに $15.5$ nF の音源の抵抗分圧器を接続すると、起動時に出力が他の電源に追従します。 |

| 37   | ITH1                | チャンネル 1 のエラー・アンプ出力とスイッチング・レギュレータの補償ポイント。電流コンパレータのトリップ・ポイントは、この制御電圧に応じて増加します。                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 38   | V <sub>FB1</sub>    | チャンネル1のエラー・アンプ帰還入力。VPRG1がフロート状態の場合、VFB1は、リモートセンシングされたチャンネル1のフィードバック電圧を、出力端子間に接続された外付け抵抗分圧器から受け取ります。VPRG1を GND または INTVcc に接続した場合、VFB1はリモートセンシングされた出力電圧を直接受け取ります。                                                                                                                                                                                                                                                                                                                                                                                |

| 39   | SENSE1⁺             | チャンネル 1 の差動電流コンパレータへの正入力。ITH1 ピン電圧と SENSE1 <sup>-</sup> ピンと SENSE1 <sup>+</sup> ピンの間の制御オフセットにより、R <sub>SENSE</sub> と連動して電流トリップ閾値が設定されます。                                                                                                                                                                                                                                                                                                                                                                                                        |

| 40   | SENSE1 <sup>-</sup> | チャンネル 1 の差動電流コンパレータへの負入力。SENSE1⁻ピンは、SENSE1⁻が INTVcc より大きい時に、チャンネル 1 の電流コンパレータに電流を供給します。SENSE1⁻が 3.2V 以上の場合、このピンは V <sub>IN</sub> の代わりにスリープ・モードでの I <sub>Q</sub> の大部分を供給し、入力換算の I <sub>Q</sub> を更に減少させます。                                                                                                                                                                                                                                                                                                                                        |

| 41   | GND (EPAD)          | グラウンド(露出パッド)。定格の電気的性能および熱性能を得るため、露出パッドは PCB のグラウンドにハンダ処理する必要があります。                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

analog.com.jp Rev. 0 | 9 of 41

# 代表的な性能特性

図 4. 効率および電力損失と負荷電流の関係

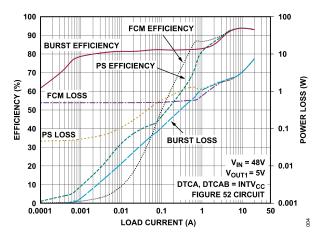

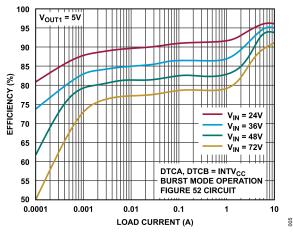

図 5. 効率と負荷電流の関係

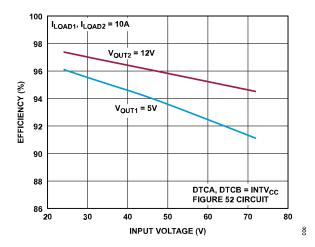

図 6. 効率と入力電圧の関係(I<sub>LOAD1</sub>、I<sub>LOAD2</sub>は負荷電流)

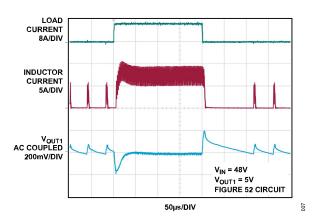

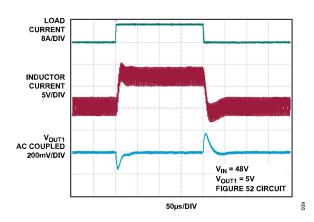

図7. 負荷ステップ (バースト・モード動作)

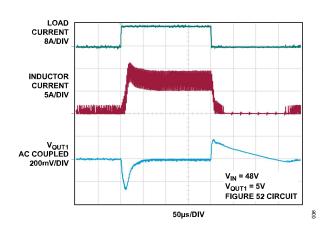

図 8. 負荷ステップ (パルス・スキッピング・モード)

図 9. 負荷ステップ(強制連続モード)

analog.com.jp Rev. 0 | 10 of 41

# 代表的な性能特性

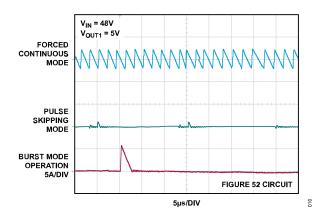

図 10. 軽負荷時のインダクタ電流

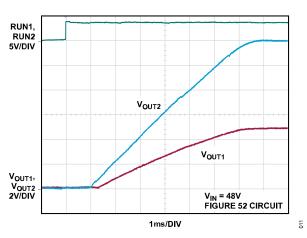

図 11. ソフト・スタートアップ

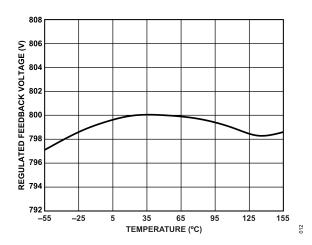

図 12. レギュレーション帰還電圧と温度の関係

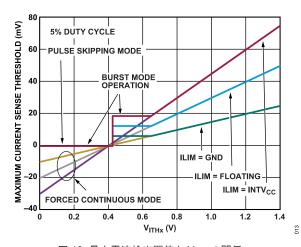

図 13. 最大電流検出閾値と V<sub>ITHx</sub>の関係

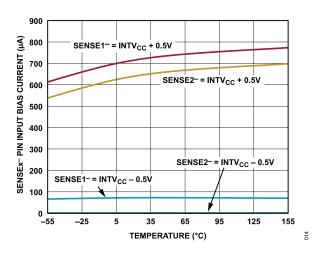

図 14. SENSEx<sup>-</sup>ピン入力バイアス電流と温度の関係

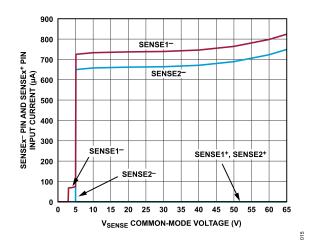

図 15. SENSEx<sup>-</sup>ピンおよび SENSEx<sup>+</sup>ピンの入力電流と V<sub>SENSE</sub> コモンモード電圧の関係

analog.com.jp Rev. 0 | 11 of 41

# 代表的な性能特性

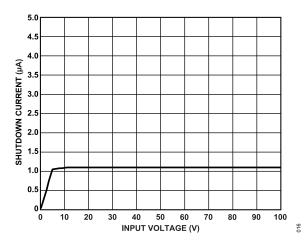

図 16. シャットダウン電流と入力電圧の関係

図 17. シャットダウン電流と温度の関係

図 18. 静止電流と温度の関係

図 19. 発振周波数と温度の関係

図 20. TRACK/SSx プルアップ電流と温度の関係

図 21. RUNx ピン閾値と温度の関係

analog.com.jp Rev. 0 | 12 of 41

# 代表的な性能特性

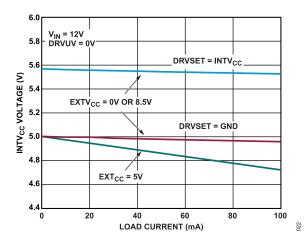

図 22. INTVcc 電圧と負荷電流の関係

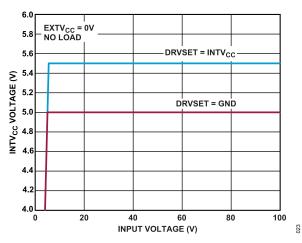

図 23. INTV<sub>CC</sub>電圧と入力電圧の関係

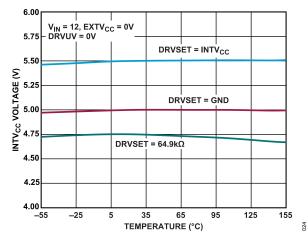

図 24. INTVcc 電圧と温度の関係

図 25. UVLO 閾値と温度の関係

図 26. EXTV<sub>CC</sub> 切替え閾値と温度の関係

図 27. 最大電流検出閾値と帰還電圧の関係

analog.com.jp Rev. 0 | 13 of 41

# 代表的な性能特性

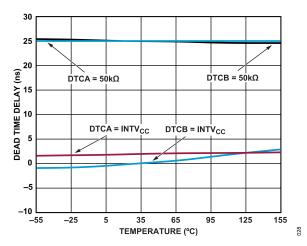

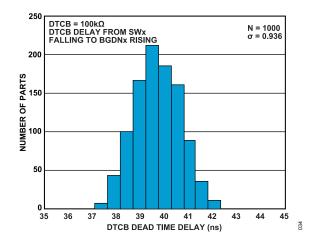

図 28. デッド・タイム遅延と温度の関係

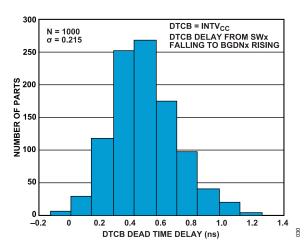

図 29. スマート・ニア・ゼロ DTCA デッド・タイム遅延の ヒストグラム ( $\delta$ はデッド・タイム遅延の標準偏差)

図 30. スマート・ニア・ゼロ DTCB デッド・タイム遅延の ヒストグラム

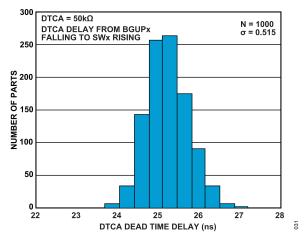

図 31. DTCA =  $50k\Omega$ 、デッド・タイム遅延のヒストグラム

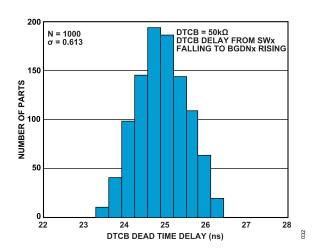

図 32. DTCB =  $50k\Omega$ 、デッド・タイム遅延のヒストグラム

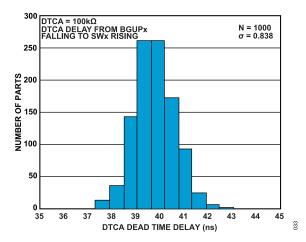

図 33. DTCA =  $100k\Omega$ 、デッド・タイム遅延のヒストグラム

analog.com.jp Rev. 0 | 14 of 41

# 代表的な性能特性

図 34. DTCB =  $100k\Omega$ 、デッド・タイム遅延のヒストグラム

analog.com.jp Rev. 0 | 15 of 41

#### 動作原理

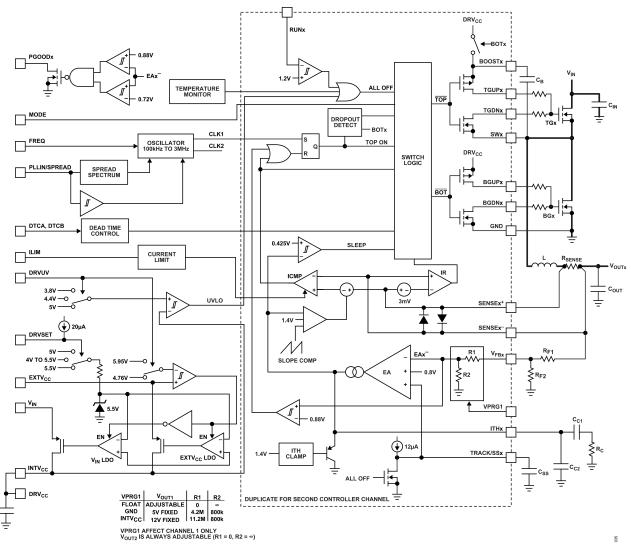

# 機能図

図 35. 機能図

#### メイン制御ループ

LTC7890 はデュアル同期整流式コントローラで、固定周波数のピーク電流モード・アーキテクチャを採用しています。2 つのコントローラ・チャンネルは 180°位相がずれて動作するため、必要な入力静電容量と電源に起因するノイズが減少します。通常動作時、クロックがセット/リセット (SR) ラッチをセットすると外付けの上側 FET がオンになり、インダクタ電流が増加します。メインの電流コンパレータ ICMP が SR ラッチをリセットすると、メイン・スイッチがオフになります。各サイクルで上側 FET がターンオフした後、下側 FET がターンオンします。これにより、インダクタ電流が反転し始めて電流コンパレータIR それを検出するか、次のクロック・サイクルが始まるまで、インダクタ電流が減少します。

ICMPがトリップしてラッチがリセットされるインダクタ電流のピークは、エラー・アンプの出力である ITH ピンの電圧によって制御されます。エラー・アンプは、 $V_{FBx}$ ピンの出力電圧帰還信号(出力電圧 $V_{OUTx}$ とグラウンドの間に接続した外付け抵抗分圧器で生成)を 0.8V の内部リファレンス電圧と比較します。負

荷電流が増加するとリファレンス電圧に対して V<sub>FBx</sub> がわずかに 低くなるので、平均インダクタ電流が新しい負荷電流に見合った値となるまで、エラー・アンプが ITHx 電圧を上昇させます。

# 電源とバイアス電源(V<sub>IN</sub>、EXTV<sub>CC</sub>、DRV<sub>CC</sub>、INTV<sub>CC</sub>)

INTVccピンは、上側および下側のFETドライバとほとんどの内部回路に電力を供給します。FETドライバ用の電源は DRVccピンから供給されます。このピンはゲート・ドライバに電源を供給するために INTVccピンに接続する必要があります。LDOリニア電圧レギュレータは  $V_{\rm IN}$ ピンと EXTVccピンの両方から利用可能で、INTVccに電力を供給します。INTVccは、DRVSETピンの制御により  $4V\sim5.5V$  の範囲で設定できます。EXTVccピンをその切替え電圧より低い電圧に接続した場合、 $V_{\rm IN}$  LDOレギュレータが INTVccに電力を供給します。EXTVccがその切替え電圧を超えると、 $V_{\rm IN}$  LDOレギュレータがオフになり、EXTVcc LDOレギュレータがオンになります。

analog.com.jp Rev. 0 | 16 of 41

#### 動作原理

EXTVcc LDO レギュレータは、イネーブルにした場合に INTVcc に電力を供給します。 EXTVcc ピンを使用することで、LTC7890 スイッチング・レギュレータの出力のような高効率の外部電源 から INTVcc の電力を供給できます。

# ハイサイド・ブートストラップ・コンデンサ

各上側 FET ドライバは、フローティング・ブートストラップ・コンデンサ ( $C_B$ ) からバイアスされます。このコンデンサは通常、下側 FET がオンになるたびに、BOOSTx と DRV $c_C$ の間の内部スイッチを介して充電されます。この内部スイッチは、下側 FET がオフの時は常時ハイ・インピーダンスであり、デッド・タイム中に SWx が GND より低い値を示す時は常に、ブートストラップ・コンデンサの過充電を防止します。

入力電圧がその出力に近い電圧まで低下すると、ループがドロップアウト状態に入り、上側 FET を連続的にオンにしようとする可能性があります。ドロップアウト検出器はこのイベントを検出し、 $C_{Bx}$ を再充電できるように、10 サイクルごとに上側 FET を強制的にオフ、下側 FET を短時間オンさせるため、370kHz 動作時のデューティ・サイクルは 99%、2MHz 動作時のデューティ・サイクルは約 98%となります。ブートストラップ・コンデンサの電圧が INTV  $_{Cc}$ 電圧の約 75%未満まで低下すると、ブースト・リフレッシュ・パルスが 4 サイクルごとに増加し、 $C_{Bx}$ により多くの電荷を供給するため、ドロップアウト時のデューティ・サイクルがわずかに低下します。

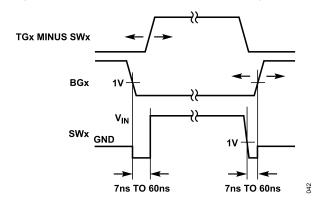

# デッド・タイム制御(DTCA および DTCB ピン)

LTC7890 のデッド・タイム遅延は、DTCA ピンと DTCB ピンを設定することで、ほぼゼロから 60ns まで設定できます。DTCA ピンは、下側 FET のターンオフと上側 FET のターンオンに関連するデッド・タイムを設定します。DTCB ピンは、上側 FET のターンオフと下側 FET のターンオンに関連するデッド・タイムを設定します。本セクションでは、TGx は上側 FET のゲートで検出された電圧を表し、BGx は下側 FET のゲートで検出された電圧を表します。

DTCAピンを GND に接続すると、適応型デッド・タイム制御が設定され、ドライバ・ロジックは、下側 FET がターンオフするのを待ってから上側 FET をターンオンします。適応型デッド・タイム制御により、BGx の立下がりから TGx の立上がりまでのデッド・タイムは約 20ns となります。

DTCBピンを GND に接続すると、適応型デッド・タイム制御が設定され、ドライバ・ロジックは、上側 FET がターンオフするのを待ってから下側 FET をターンオンします。適応型デッド・タイム制御により、TGx の立下がりから BGx の立上がりまでのデッド・タイムは約 20ns となります。

DTCA ピンを INTVccに接続すると、SWx の立上がりエッジから BGx の立下がりエッジまでの遅延をほぼゼロにする、スマート・ニア・ゼロのデッド・タイム制御を設定できます。DTCA ピンと GND の間に抵抗を配置すると、SWx の立上がりから BGx の立下がりまでの遅延が 7ns~60ns 追加されます。詳細については、デッド・タイム制御(DTCA および DTCB ピン)のセクションを参照してください。

DTCB ピンを INTV<sub>CC</sub>に接続すると、SWx の立下がりエッジから BGx の立上がりエッジまでの遅延をほぼゼロにする、スマート・ニア・ゼロのデッド・タイム制御を設定できます。 DTCB ピンと GND の間に抵抗を配置すると、SWx の立下がりから BGx の立上がりまでの遅延が 7ns $\sim$ 60ns 追加されます。 詳細については、デッド・タイム制御(DTCA および DTCB ピン)のセクションを参照してください。

# 起動とシャットダウン(RUNx および TRACK/SSx ピン)

LTC7890 の 2 つのチャンネルは、RUN1 ピンと RUN2 ピンを用いて個別にシャットダウンできます。RUNx ピンを 1.08V 未満にすると、そのチャンネルのメイン制御ループがシャットダウンします。両方の RUNx ピンを 0.7V 未満にすると、コントローラと、INTV $_{\rm CC}$  LDO を含むほとんどの内部回路の両方がディスエーブルされます。このシャットダウン状態では、LTC7890 に流れる  $I_{\rm B}$  はわずか  $1\mu{\rm A}$  です。

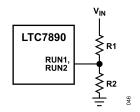

RUNx ピンは、外部でプルアップするか、ロジックで直接駆動する必要があります。各 RUNx ピンは最大 100V (絶対最大)まで許容できます。したがって、一方または両方のコントローラが連続的にイネーブルされて、シャットダウンされることのない常時オンのアプリケーションでは、RUNx ピンを  $V_{\rm IN}$  に接続できます。更に、 $V_{\rm IN}$  ピンと RUNx ピンの間に抵抗分圧器を挿入して高精度の入力 UVLO を設定し、調整可能なレベル未満では電源が動作しないようにすることもできます。

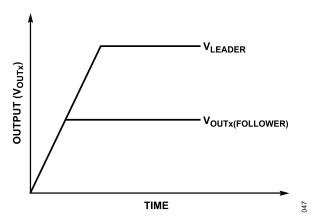

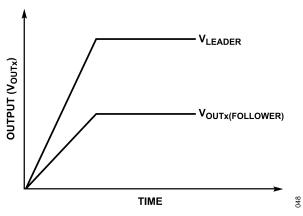

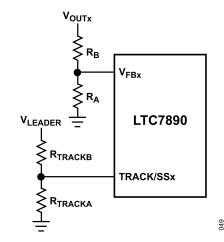

各チャンネルの  $V_{OUTx}$  の起動は、対応する TRACK/SSx ピンの電圧によって制御します。 TRACK/SSx ピンの電圧が 0.8V の内部 リファレンス電圧よりも低い場合、LTC7890 は  $V_{FBx}$  電圧を 0.8V のリファレンス電圧ではなく TRACK/SSx ピンの電圧にレギュレーションします。この方法により、TRACK/SSx ピンをソフト・スタートとして使用することができるので、起動時に出力電圧を滑らかに上昇させ、入力電源の突入電流を制限できます。 TRACK/SSx ピンと GND の間の外付けコンデンサは、 $12\mu A$  の内部プルアップ電流によって充電され、TRACK/SSx ピンの電圧に電圧ランプが発生します。 TRACK/SSx 電圧が TRACK/SSx 電が TRACK/SSx 電流 TRACK/SSx での TRACK/SSx

あるいは、TRACK/SSx ピンを用いて、Voutx の立上がりを他の電源の立上がりに追従させることもできます。通常、このトラッキングを行うには、他の電源と GND の間の外付け抵抗分圧器を介して TRACK/SSx ピンに接続する必要があります (RUNxピンと低電圧ロックアウトのセクションとソフト・スタートとトラッキング(TRACK/SSx ピン)のセクションを参照)。

#### 動作原理

# 軽負荷時の動作:バースト・モード動作、 パルス・スキップ・モード、強制連続モード (MODE ピン)

LTC7890 は、軽負荷電流時に、高効率のバースト・モード動作、固定周波数パルス・スキッピング・モード、または強制連続動作モードのいずれかに設定できます。

バースト・モード動作を選択するには、MODE ピンを GND に接続します。強制連続動作を選択するには、MODE ピンを INTVcc に接続します。パルス・スキッピング・モードを選択するには、MODE ピンを 1.2V 以上 INTVcc -1.3V 未満の直流電圧に接続します。内部の 100k $\Omega$  抵抗が GND に接続されているので、MODE ピンがフロート状態の時はバースト・モード動作になり、MODE ピンが外部 100k $\Omega$  抵抗を介して INTVcc に接続されている時はパルス・スキッピング・モードになります。

コントローラでバースト・モード動作が有効化されている場合、ITHx ピンの電圧が低い値を示している場合でも、インダクタの最小ピーク電流は最大値の約25%に設定されます。平均インダクタ電流が負荷電流より大きい場合、エラー・アンプはITHxピンの電圧を低下させます。ITHx電圧が0.425Vを下回ると、内部スリープ信号がハイになり(スリープ・モードが有効化され)、両方の外付けFETがオフになります。すると、ITHxピンがエラー・アンプの出力から遮断され、0.45Vを維持します。

スリープ・モードでは内部回路のほとんどがオフになるため、LTC7890 に流れる  $I_Q$  が減少します。一方のチャンネルがスリープ・モードで、もう一方のチャンネルがシャットダウンされている場合、LTC7890 に流れる  $I_Q$  はわずか  $15\mu A$  です。両方のチャンネルがスリープ・モードの場合、LTC7890 に流れる  $I_Q$  はわずか  $20\mu A$  です。チャンネル 1 の  $V_{OUT}$  が 3.2V 以上の時、この  $I_Q$  の大部分は SENSE1 ピンから供給され、 $V_{IN}/V_{OUT}$  の比に効率を乗じた分だけ入力換算の  $I_Q$  が更に減少します。

スリープ・モードでは、負荷電流が出力コンデンサから供給されます。出力電圧が低下するにつれて、エラー・アンプの出力が上昇します。出力電圧が十分に低下すると、ITHx ピンがエラー・アンプの出力に再接続され、スリープ信号がローになり、コントローラは内部発振器の次のサイクルで上側 FET をオンにして通常動作を再開します。

コントローラのバースト・モード動作が有効化されていると、インダクタ電流は反転することができません。インダクタ電流がゼロに達する直前に、逆電流コンパレータ (IR) が下側 FETをオフにし、インダクタ電流が反転して負になるのを防ぎます。したがって、コントローラは不連続動作状態で動作します。

強制連続動作の場合、軽負荷時または大きなトランジェント状態時にはインダクタ電流を反転させることができます。ピーク・インダクタ電流は、通常動作時と同様にITHxピンの電圧によって決まります。このモードでは、軽負荷時の効率がバースト・モード動作の場合よりも低下します。ただし、連続動作には出力電圧リップルが小さく、オーディオ回路への干渉が少ないという利点があります。強制連続モードでは、出力リップルは負荷電流に依存しません。

パルス・スキッピング・モードになるように MODE ピンを接続すると、LTC7890 は軽負荷時にパルス幅変調(PWM)のパルス・スキッピング・モードで動作します。このモードでは、出力電流が最大設計値の約1%になるまで固定周波数動作が維持されます。軽負荷時には、ICMP は数サイクルの間トリップ状態を維持し、同じサイクル数の間上側 FET をオフしたままにする(つまり、パルスをスキップする)ことがあります。インダクタ電流は反転できません(不連続動作)。強制連続動作と同様、このモードでは、バースト・モード動作と比較して、出力リップル、オーディオ・ノイズ、およびRF干渉が低減します。パルス・スキッピング・モードでは、低電流での効率が強制連続モードより高くなりますが、バースト・モード動作ほど高くはありません。

強制連続モードやパルス・スキッピング・モードとは異なり、バースト・モード動作は外部クロックに同期できません。そのため、バースト・モードを選択し、スイッチング周波数がPLLIN/SPREAD ピンに印加された外部クロックに同期している場合、LTC7890 はバースト・モードから強制連続モードに切り替わります。

# 周波数の選択、スペクトラム拡散、フェーズ・ロック・ループ(FREQ および PLLIN/SPREAD ピン)

LTC7890 コントローラの自走スイッチング周波数は、FREQ ピンで選択します。FREQ を GND に接続すると 370kHz が選択され、FREQ を INTVcc に接続すると 2.25MHz が選択されます。FREQ と GND の間に抵抗を接続すると、周波数を 100kHz~3MHz の範囲で設定できます。

スイッチング・レギュレータは、電磁干渉(EMI)が懸念されるアプリケーションでは特に問題を生じることがあります。 EMI 性能を向上するために、LTC7890 はスペクトラム拡散モードで動作できます。このモードは、PLLIN/SPREAD ピンをINTVcc に接続することで有効化できます。この機能により、スイッチング周波数は FREQ ピンで設定した周波数~+20%(代表値)の範囲内で変化します。

LTC7890 ではフェーズ・ロック・ループ (PLL) が使用可能で、PLLIN/SPREAD ピンに接続された外部クロック信号源に内部発振器を同期させることができます。LTC7890 の PLL は、チャンネル 1 の外付け上側 FET のターンオンを同期信号の立上がりエッジに一致させます。チャンネル 2 の外付け上側 FET のターンオンは、外部クロック源の立上がりエッジに対して 180° 位相がずれます。

PLL の周波数は、外部クロックが入力される前に FREQ ピンで設定した自走周波数にプリバイアスされます。外部クロックの周波数付近にプリバイアスしておくと、PLL をわずかに変化させるだけで、外部クロックの立上がりエッジを TG1 の立上がりエッジに同期させることができます。より高速に外部クロックにロックインするには、FREQ ピンを使用して、内部発振器の周波数を外部クロックの周波数にほぼ等しい値に設定します。LTC7890の PLL は、周波数が 100kHz~3MHz の外部クロック源に確実にロックするよう設計されています。

analog.com.jp Rev. 0 | 18 of 41

# 動作原理

PLLIN/SPREAD ピンはトランジスタ・トランジスタ・ロジック (TTL) 互換で、閾値が 1.6V (立上がり) および 1.1V (立下がり) であるため、クロック信号の振幅が  $0.5V\sim2.2V$  での動作が確保されています。

# 出力過電圧保護

LTC7890 は各チャンネルに過電圧コンパレータを備えており、トランジェント・オーバーシュートや、出力過電圧の原因となるその他の深刻な状態から保護します。 $V_{FBx}$  ピンがレギュレーション・ポイントである 0.8V を 10%以上超えると、上側 FET がオフになり、インダクタ電流は逆転できなくなります。

# フォールドバック電流

出力電圧が公称レベルの 70%未満に低下すると、フォールドバック電流制限機能が有効になり、過電流または短絡状態の深刻度に比例してピーク電流制限値が徐々に低下します。ソフト・スタート期間中は、  $(V_{FBx}$ 電圧が TRACK/SSx電圧に追従している限り) フォールドバック電流制限機能は無効化されます。

# パワーグッド

LTC7890 には各チャンネルに PGOODx ピンがあり、内部 N チャンネル MOSFET のオープン・ドレインに接続されています。  $V_{FBx}$ 電圧が 0.8V リファレンスの $\pm 10\%$ 以内にない場合、MOSFET がオンになり、PGOODx ピンがローになります。PGOODx ピンは、RUNx ピンがロー(シャットダウン)の時にもローになります。  $V_{FBx}$ 電圧が $\pm 10\%$ の条件以内になると、MOSFET がオフになるため、PGOODx ピンを外付け抵抗によって INTV $_{CC}$  などの 6V を超えない電源にプルアップできます。

analog.com.jp Rev. 0 | 19 of 41

# アプリケーション情報

図 1 は、LTC7890 の基本的なアプリケーション回路を示しています。外付け部品の選択は負荷条件によって大きく左右されますが、まずは、インダクタ、電流検出部品、動作周波数、軽負荷動作モードの選択から始めます。次に、入力コンデンサと出力コンデンサ、およびパワーFET で構成される残りのパワー段コンポーネントを選択します。次に、必要な出力電圧を設定するための帰還抵抗を選択します。更に、ソフト・スタート、バイアス、ループ補償など、残りの外付け部品を選択します。

# インダクタ値の計算

動作周波数が高いほど小さな値のインダクタとコンデンサを使用できるという点で、動作周波数とインダクタの選択には相関関係があります。周波数が高くなるほど、FETのスイッチング損失とゲート電荷損失が発生するため、一般に効率が低下します。このトレードオフに加えて、リップル電流と低電流動作に対するインダクタ値の影響も考慮しなければなりません。インダクタの値は、リップル電流に直接影響します。

最大平均インダクタ電流( $I_{L(MAX)}$ )は、最大出力電流に等しくなります。ピーク電流は、平均インダクタ電流にインダクタ・リップル電流( $\Delta I_L$ )の半分を加えたものに等しくなります。このリップル電流は式1に示すように、インダクタンス(L)または周波数(f)が高くなるほど減少し、 $V_{IN}$ が高くなるほど増加します。

$$\Delta I_L = \frac{1}{(f)(L)} V_{OUT} \left( 1 - \frac{V_{OUT}}{V_{IN}} \right) \tag{1}$$

$\Delta I_L$  が大きな値でもよければ、低い値のインダクタンスを使用できますが、出力電圧リップルが大きくなり、コア損失が大きくなります。リップル電流を設定するための妥当な出発点は、  $\Delta I_L=0.3 \times I_{L(MAX)}$ です。 $\Delta I_L$  が最大になるのは、最大入力電圧の時です。

インダクタの値は、2次的な影響も与えます。必要な平均インダクタ電流が減少すると、ピーク電流が  $R_{SENSE}$  によって決定される電流制限の 25%未満になった時点でバースト・モード動作への移行が開始されます。インダクタ値を低くする( $\Delta I_L$  を高くする)と、この遷移はより低い負荷電流で起こるため、低電流動作の値の高い範囲では効率が低下する可能性があります。バースト・モード動作では、インダクタンス値が小さくなるとバースト周波数が低下します。

#### インダクタ・コアの選択

Lの値が定まったら、インダクタの種類を選択します。高効率 レギュレータは一般に、低価格の鉄粉コアで生じるコア損失を 許容できないため、より高価なフェライトまたはモリパーマロ イのコアを使わざるを得ません。インダクタ値が同じ場合、実 際のコア損失はコア・サイズではなく、選択するインダクタン ス値に大きく依存します。インダクタンスが大きくなると、コ ア損失は減少します。しかし、インダクタンスを増加させるに は巻き線数を増やす必要があるため、銅損失が増加します。

フェライトを使った設計ではコア損失が小さくなるので、ス イッチング周波数が高い場合に適しています。したがって、設 計目標を銅損と飽和防止に集中できます。フェライト・コア材は飽和しやすいため、設計電流のピークを超えるとインダクタンスが急激に低下します。その結果、インダクタのリップル電流が急激に増加し、それに伴い出力電圧リップルも増加します。コアを飽和させないようにしてください。

# 電流検出方式の選択

LTC7890 はインダクタ DC 抵抗 (DCR) による検出または低抵抗値による検出のいずれかを使うように構成できます。2 つの電流検出方式のどちらを選択するかは、コスト、消費電力、精度のいずれを設計で主に重視するかで決まります。DCR による検出が普及したのは、高価な電流検出抵抗が不要で、特に大電流のアプリケーションで電力効率が向上するためです。一方、電流検出抵抗では、最も正確な電流制限値をコントローラに提供できます。他の外付け部品の選択は負荷条件によって決まり、RSENSE (RSENSE を使用する場合)とインダクタの値の選択から始めます。

SENSEx<sup>+</sup>ピンと SENSEx<sup>-</sup>ピンは、電流コンパレータへの入力と なります。これらのピンのコモンモード電圧範囲は 0V~65V (絶対最大値) であるため、LTC7890 は最大 60V の出力電圧を レギュレーションできます。SENSEx<sup>+</sup>ピンは高インピーダンス で、電流は約 1µA 未満です。このように高インピーダンスなの で、電流コンパレータをインダクタの DCR による検出に使用で きます。SENSEx<sup>-</sup>ピンのインピーダンスは、コモンモード雷圧 に応じて変化します。INTV<sub>CC</sub> - 0.5V 未満の時、SENSEx<sup>-</sup>ピンは 比較的高インピーダンスとなり、SENSE1では約 75uA、 SENSE2<sup>-</sup>には約 1µA の電流が流れます。SENSEx<sup>-</sup>ピンが INTVcc + 0.5V を超えると、このピンにはより大きな電流(約 700μA) が流れます。INTVcc - 0.5V から INTVcc + 0.5V までの 間では、電流は小さい方の電流から大きい方の電流に流れます。 SENSE1<sup>-</sup>ピンの電圧が 3.2V を超えると、V<sub>IN</sub>ではなく V<sub>OUTI</sub> から 内部回路にバイアスがかかるため、SENSE1<sup>-</sup>ピンには更に約 75µA の電流が流れ、入力換算電源電流が減少します。

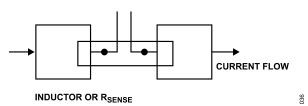

検出ラインに共通するフィルタ部品は LTC7890 の近くに配置し、検出ラインは電流検出素子の下のケルビン接続点まで互いに近づけて配線します(図 36 を参照)。他の場所で電流を検出すると、電流検出素子に寄生インダクタンスと静電容量が加わり、検出端子の情報が劣化して、電流制限の設定値が予測できなくなることがあります。DCR による検出を使用する場合は(図 38を参照)、R1 をスイッチング・ノードの近くに配置して、高感度の小信号ノードにノイズが結合しないようにします。

# TO SENSE FILTER NEXT TO THE CONTROLLER

図 36. インダクタまたは検出抵抗を使用した検出ラインの配置

# アプリケーション情報

# 小さな値の抵抗による電流検出

図 37 に、ディスクリート抵抗を使用した代表的な検出回路を示します。 $R_{SENSE}$  は必要な出力電流に基づいて選択します。 コントローラの電流コンパレータの  $V_{SENSE(MAX)}$ は 50 mV、 25 mV 、または 75 mV で、これは ILIM ピンの状態によって決まります。電流コンパレータの閾値電圧により、インダクタのピーク電流が設定されます。

最大インダクタ電流( $I_{L(MAX)}$ )およびリップル電流( $\Delta I_L$ )を用いて(インダクタ値の計算のセクションを参照)、目標とする検出抵抗値は式 2 で与えられます。

$$R_{SENSE} = \frac{V_{SENSE(MAX)}}{I_{L(MAX)} + \frac{\Delta I_L}{2}}$$

(2)

アプリケーションが全動作温度範囲にわたって全負荷電流を確実に供給するには、表 1 に示す  $V_{SENSE(MAX)}$ の最小値を選択します。

検出抵抗に寄生インダクタンス(ESL)があると、低インダクタ値( $<3\mu$ H)または高電流(>5A)アプリケーションの場合、電流検出信号に大きな誤差が生じます。この誤差は入力電圧に比例し、ライン・レギュレーションを劣化させたり、ループを不安定化させたりすることがあります。図37に示すように、RCフィルタ(フィルタ抵抗  $R_F$  とフィルタ・コンデンサ  $C_F$ )をSENSEx+ピンと SENSEx-ピンの間に配置することで、この誤差を補正できます。ESLを最も適切に抑えるには、RCフィルタの時定数を  $R_F$  ×  $C_F$  = ESL/ $R_{SENSE}$  となるように設定します。一般に、 $1nF\sim10nF$  の範囲内になるように  $C_F$  を選択し、それに応じて  $R_F$  を計算します。この誤差を最小限に抑えるため、低 ESL でフットプリントの広い形状の表面実装型検出抵抗を推奨します。メーカーのデータシートで仕様規定されていない場合、ESL は、1206 フットプリントの抵抗器では 0.4nH、1225 フットプリントの抵抗器では 0.2nH と概算できます。

図 37. 抵抗を使用した電流検出

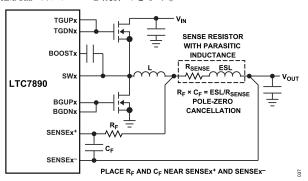

#### インダクタの DCR による電流検出

大負荷電流時に可能な限り高い効率を必要とするアプリケーションの場合、図 38 に示すように、LTC7890 はインダクタの DCR 両端の電圧降下を検出できます。インダクタの DCR とは、 銅巻線の DC 抵抗の小さな値を表し、値の小さい大電流インダクタでは  $1m\Omega$  未満になることがあります。このようなインダクタを必要とする大電流アプリケーションでは、検出抵抗による

電力損失は、インダクタの DCR による検出に比べると数ポイントの効率低下になると考えられます。

図 38. インダクタの DCR を用いた電流検出 (R<sub>SENSE(EQUIV)</sub>は等価検出抵抗)

外付けの(R1||R2) × C1 の時定数が L/DCR の時定数に等しくなるように選択すると、外付けコンデンサ両端の電圧降下はインダクタの DCR 両端の電圧降下に R2/(R1 + R2)を掛けたものに等しくなります。R2 は、目標とする検出抵抗値よりも DCR が大きいアプリケーションに対して、検出端子両端の電圧を調整する抵抗です。外部フィルタ部品の寸法を適切に決めるには、インダクタの DCR を知る必要があります。DCR は、インダクタンス、容量、抵抗(LCR)メーターを用いて測定できます。ただし、DCR の許容差は常に同じではなく、温度によって変化します。詳細については、メーカーのデータシートを参照してください。

$I_{L(MAX)}$ および  $\Delta I_L$  を用いて(インダクタ値の計算のセクションを参照)、目標とする検出抵抗値は式 3 で与えられます。

$$R_{SENSE(EQUIV)} = \frac{V_{SENSE(MAX)}}{I_{L(MAX)} + \frac{\Delta I_L}{2}}$$

(3)

アプリケーションが全動作温度範囲にわたって全負荷電流を確実に供給するには、表 1 に示す  $V_{SENSE(MAX)}$ の最小値を選択します。

次に、インダクタの DCR を決めます。メーカーから仕様が提供されている場合は、通常は  $20^{\circ}$ C で規定されている最大値を使用します。銅抵抗の温度係数(約  $0.4\%^{\circ}$ C)を考慮して、この値を増加させます。最大インダクタ温度( $T_{L(MAX)}$ )の値は控え目に見て  $100^{\circ}$ C です。最大インダクタ DCR( $DCR_{MAX}$ )を検出抵抗の目標値( $R_D$ )に調整するには、式 4 で与えられる分圧比を使用します。

$$R_D = \frac{R_{SENSE(EQUIV)}}{DCR_{MAX} \text{ at } T_{L(MAX)}} \tag{4}$$

C1 は通常、 $0.1\mu$ F $\sim$ 0.47 $\mu$ F の範囲内になるように選択します。この範囲では、等価抵抗( $R1\parallel$ R2)が約  $2k\Omega$  になるため、 $SENSEx^+$ ピンの約  $1\mu$ A の電流に起因する誤差が低減します。

analog.com.jp Rev. 0 | 21 of 41

# アプリケーション情報

R1||R2 は、室温のインダクタンスと最大 DCR によって式 5 で求められます。

$$R1 \parallel R2 = \frac{L}{(DCR \text{ at } 20^{\circ}C) \times C1}$$

(5)

検出抵抗値は、式6と式7で与えられます。

$$R1 = \frac{R1 \parallel R2}{R_D} \tag{6}$$

$$R2 = \frac{R1 \times R_D}{1 - R_D} \tag{7}$$

R1 の最大電力損失 ( $P_{LOSS}$ ) はデューティ・サイクルに関連して、連続モード時の最大入力電圧 ( $V_{IN(MAX)}$ ) で発生し、式 8 で与えられます。

$$P_{LOSS} in R1 = \frac{\left(V_{IN(MAX)} - V_{OUT}\right) \times V_{OUT}}{R1}$$

(8)

RIの電力定格が RIの PLOSSより大きくなるようにします。軽負荷時に高い効率が必要な場合、DCR 検出と検出抵抗のどちらを使用するかを決定する際には、この電力損失を検討します。軽負荷時の電力損失は、RI によって余分のスイッチング損失が生じるため、検出抵抗の場合より DCR ネットワークの方がわずかに大きくなることがあります。ただし、DCR による検出では検出抵抗が不要になるため、伝導損失が減少し、重負荷時の効率が高くなります。ピーク効率はどちらの方法でもほぼ同じです。

# 動作周波数の設定

動作周波数の選択では、効率と部品サイズの間にトレードオフがあります。動作周波数が高いと、小型のインダクタと値の小さいコンデンサを使用できます。低い周波数で動作させるとゲート電荷と遷移損失が減るので効率が改善されますが、出力リップル電圧を低く維持するには、インダクタンスの値や出力容量を大きくする必要があります。

高電圧アプリケーションでは、遷移損失が電力損失に大きく影響し、300kHz~900kHzのスイッチング周波数の時にサイズと効率の間で良好なバランスをとることができます。低電圧アプリケーションは、スイッチング損失が低いという利点があるため、必要に応じて最大 3MHz のスイッチング周波数で動作させることができます。スイッチング周波数は、表 4 に示すように、FREQ ピンと PLLIN/SPREAD ピンで設定します。

表 4. FREQ と PLLIN/SPREAD によるスイッチング周波数の設定

| FREQ Pin                                   | PLLIN/SPREAD Pin                 | Frequency                                              |

|--------------------------------------------|----------------------------------|--------------------------------------------------------|

| 0 V                                        | 0 V                              | 370 kHz                                                |

| INTV <sub>CC</sub>                         | 0 V                              | 2.25 MHz                                               |

| Resistor to GND                            | 0 V                              | 100 kHz to 3 MHz                                       |

| 0 V, $INTV_{CC}$ , or Resistor to $GND$    | External clock, 100 kHz to 3 MHz | Phase-locked to external clock                         |

| 0 V, INTV $_{\rm CC}$ , or Resistor to GND | INTV <sub>CC</sub>               | Spread spectrum, f <sub>OSC</sub> modulated 0% to +20% |

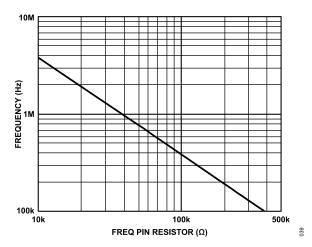

FREQ ピンを GND に接続すると 370kHz が選択され、FREQ を INTV $_{\rm CC}$  に接続すると 2.25MHz が選択されます。FREQ と GND の間に抵抗を接続すると、周波数を 100kHz $\sim$ 3MHz の範囲内で 任意に設定できます。FREQ ピンの抵抗( $R_{\rm FREQ}$ )は、図 39 または式 9 により選択します。

$$R_{FREQ}(\text{in k}\Omega) = 37 \text{ MHz}/f_{OSC}$$

(9)

図 39. 発振器周波数と FREQ ピンの抵抗値の関係

EMI性能を向上させるため、PLLIN/SPREADピンをINTVccに接続してスペクトラム拡散モードを選択できます。スペクトラム拡散機能を有効化した場合、スイッチング周波数は、FREQピンで選択した周波数から+20%までの範囲内で調整されます。スペクトラム拡散モードは、MODEピンで選択した任意の動作モード(バースト・モード、パルス・スキッピング、強制連続モード)で使用できます。

また、LTC7890ではPLLが使用可能で、PLLIN/SPREADピンに接続された外部クロック信号源に内部発振器を同期させることができます。PLLがロックした後、TGxx1は外部クロック信号の立上がりエッジに同期し、TGxx2は位相がTGxx1から180°ずれます。詳細については、フェーズ・ロック・ループと周波数同期のセクションを参照してください。

# 軽負荷時動作モードの選択

LTC7890 は、軽負荷電流時に、高効率のバースト・モード動作、固定周波数パルス・スキッピング・モード、または強制連続動作モードのいずれかに設定できます。バースト・モード動作を選択するには、MODEピンをGNDに接続します。強制連続動作

# アプリケーション情報

を選択するには、MODE ピンを INTVccに接続します。パルス・スキッピング・モードを選択するには、MODE ピンを  $100k\Omega$  の 抵抗を介して INTVccに接続します。MODE ピンがフロート状態 の場合、MODE ピンとグラウンドの間にある  $100k\Omega$  の内部抵抗により、バースト・モードが選択されます。PLLIN/SPREAD ピンを介して外部クロックに同期させた場合、パルス・スキッピング・モードが選択されていれば、LTC7890 はそのモードで動作します。それ以外の場合、LTC7890 は強制連続モードで動作します。MODE ピンを用いて軽負荷時動作モードを選択する方法を表 5 に示します。

表 5. MODE ピンを使用した軽負荷時動作モードの選択

| MODE Pin                                   | Light Load Operating Mode | Mode When Synchronized |

|--------------------------------------------|---------------------------|------------------------|

| 0 V or Floating                            | Burst Mode                | Forced continuous      |

| 100 $k\Omega$ to $\text{INTV}_{\text{CC}}$ | Pulse skipping            | Pulse skipping         |

| INTV <sub>CC</sub>                         | Forced continuous         | Forced continuous      |

どの軽負荷時動作モードを選択するのが適切かは、それぞれのアプリケーションの条件によって決まります。バースト・モード動作では、インダクタ電流は反転できません。インダクタ電流がゼロに達する前に、逆電流コンパレータが下側 FET をオフにし、インダクタ電流が反転して負になるのを防ぎます。したがって、レギュレータは不連続動作状態で動作します。更に、負荷電流が少ないと、インダクタ電流はスイッチング間波数より低い周波数でバースト動作を開始し、スイッチングが停止している時は低消費電流のスリープ・モードに入ります。その結果、軽負荷時にはバースト・モード動作の効率が最も高くなります。

強制連続モードでは、インダクタ電流は軽負荷時に反転が可能となり、負荷に関係なく同じ周波数でスイッチングします。このモードでは、軽負荷時の効率がバースト・モード動作よりもかなり低下します。ただし、連続動作には出力電圧リップルが小さく、オーディオ回路への干渉が少ないという利点があります。強制連続モードでは、出力リップルは負荷電流に依存しません。

パルス・スキッピング・モードでは、出力電流が設計上の最大 値の約1%になるまで固定周波数動作が維持されます。非常に軽 い負荷時には、PWM コンパレータは数サイクル間トリップ状態 を維持し、同じサイクル数の間上側 FET をオフにしたままにす る(つまり、パルスをスキップする)ことがあります。インダ クタ電流は反転できません (不連続動作)。強制連続動作と同 様、このモードでは、バースト・モード動作に比べて出力リッ プルとオーディオ・ノイズが小さくなり、RF 干渉が減少します。 パルス・スキッピング・モードでは、軽負荷時の効率が強制連 続モードより高くなりますが、バースト・モード動作ほど高く はありません。したがって、パルス・スキッピング・モードは 軽負荷時の効率、出力リップル、EMI の間の妥協点となります。 アプリケーションによっては、システム内の条件に応じて軽負 荷時の動作モードを変更することが望ましい場合があります。 例えば、システムが非アクティブの場合、MODEピンを 0V に設 定しておくことで、高効率のバースト・モード動作を選択でき ます。システムが起動した時、外部クロックを PLLIN/SPREAD に供給するか、MODEをINTVccに接続すれば低ノイズの強制連 続モードに切り替えることができます。このようなモード変更 を行うと、個々のアプリケーションでそれぞれの軽負荷時動作 モードの利点が得られます。

# デッド・タイム制御 (DTCA および DTCB ピン)

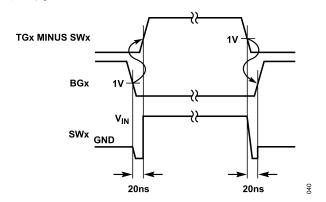

LTC7890 のデッド・タイム遅延は、DTCA ピンと DTCB ピンの 設定により、ほぼゼロから 60ns まで調整できます。図 40、図 41、 図 42 に、各 DTCx ピンの設定に対する TGx - SWx、BGx、SWx の各波形を示します。DTCx ピンを GND に接続(適応型デッ ド・タイム制御)、DTCx ピンを INTVcc に接続(スマート・ニ ア・ゼロ型デッド・タイム制御)、および DTCx ピンを抵抗を 介して GND に接続の各セクションでは、TGx は上側 FET ゲート で検出される電圧(TGxの立下がり閾値はTGUPxピンで検出) を、BGx は下側 FET ゲートで検出される電圧 (BGx の立上がり 閾値は BGDNx ピンで、立下がり閾値は BGUPx ピンで検出)を 表します。SWx 波形は、正のインダクタ電流による連続導通 モードでの動作を表します。DTCA ピンは、下側 FET のターン オフと上側 FET のターンオン (SWx がローからハイに遷移) に 関連するデッド・タイムを設定します。DTCB ピンは、上側 FET のターンオフと下側 FET のターンオン (SWx がハイから ローに遷移)に関連するデッド・タイムを設定します。

#### DTCx ピンを GND に接続(適応型デッド・タイム制御)

DTCA ピンと DTCB ピンを GND に接続すると、適応型デッド・タイム制御が設定されます。適応型制御(図 40 を参照)では、一方の FET がオフになってから他方の FET がオンになるまでのデッド・タイムが測定されます。 DTCA ピンを GND に接続すると、BGx の立下がりから TGx - SWx の立上がりまでの遅延が約 20ns に固定されます。 DTCB ピンを GND に接続すると、TGx - SWx の立下がりから BGx の立上がりまでの遅延が約 20ns に固定されます。

図 40. DTCx ピンを GND に接続(適応型デッド・タイム制御)

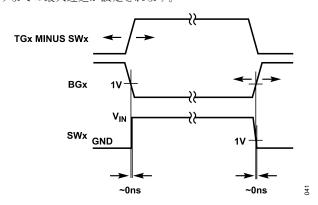

# DTCx ピンを INTVcc に接続(スマート・ニア・ゼロ型 デッド・タイム制御)

図 41 に、DTCx ピンを INTVcc に接続した場合のタイミング波形を示します。DTCA ピンを INTVcc に接続すると、BGx の立下がりから SWx の立上がりまでの遅延がほぼゼロになります。DTCB ピンを INTVcc に接続すると、SWx の立下がりから BGx の立上がりまでの遅延がほぼゼロになります(上側 FET のターンオフ時にインダクタ電流が正)。BGx (BGDN ピンで検出)および SWx の立上がりエッジが定義されるのは、その電圧が(GND を基準として)約 1V まで上昇した時点であることに注意してください。同様に、BGx (BGUP ピンで検出)および SWx の立下がりエッジは、その電圧が約 1V まで低下した時点です。

# アプリケーション情報

DTCB の遷移の場合、上側 FET がターンオフしてから約 20ns 後に SWx ノードが 1V に低下しない場合(インダクタ電流が小さいか負)、下側 FET が自動的にターンオンします。この 20ns のタイムアウトにより、TGx-SWx の立下がりから BGx の立上がりまでの最大遅延が設定されます。

図 41. DTCx ピンを INTV<sub>CC</sub> に接続 (スマート・ニア・ゼロ型デッド・タイム制御)

# DTCx ピンを抵抗を介して GND に接続

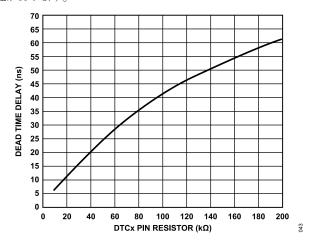

DTCx ピンと GND の間に抵抗を接続すると、SWx と BGx のエッジ間に  $7ns\sim60ns$  の遅延が追加されます(図 42 を参照)。 DTCA ピンに抵抗を接続すると、BGx の立下がりから SWx の立上がりまでの間に遅延が追加されます。 DTCB ピンと GND の間に抵抗を接続すると、SWx の立下がりから BGx の立上がりまでの間に 遅延が追加されます。 図 43 は、DTCx ピンの抵抗値と BGx エッジから SWx エッジまでの間に設定される遅延の関係を示しています。この抵抗は  $10k\Omega$  以上にする必要があります。

図 42. DTCx ピンを抵抗を介して GND に接続 (調整型デッド・タイム制御)

DTCx ピンに抵抗を使用した場合、一方の FET がオフしてから 他方の FET がオンするまでの最大遅延時間は、設定済み遅延時間を約 30ns 超えるように設定されます。DTCA 遷移(SWx がローからハイ)において、下側 FET がターンオフした直後に SWx がハイになるような負のインダクタ電流(例えば、強制連続モードでの軽負荷時電流)で下側 FET がターンオフすると、このタイムアウトに達する可能性があります。

DTCx ピンの一方を抵抗で設定している場合、もう一方の DTCx ピンは抵抗で設定するか INTVcc に接続していなければ、適切なデッド・タイム制御動作はできません。一方の DTCx ピンを抵抗で設定するか INTVcc に接続し、もう一方の DTCx ピンを GND に接続すると、予期しないデッド・タイム遅延が発生する可能性があります。

図 43. デッド・タイム遅延と DTCx ピン抵抗値の関係

# パワーFET の選択

LTC7890 では 2 つの外付けパワーFET を選択する必要があります。1 つは上側(メイン)スイッチ用の N チャンネル FET で、もう 1 つは下側(同期)スイッチ用の N チャンネル FET です。ピーク to ピークのゲート駆動レベルは、INTVcc のレギュレーション・ポイント( $4V\sim5.5V$ )によって設定されます。ほとんどの GaN FET は、この INTVcc レギュレーション・ウィンドウ内で十分に駆動できます。シリコン MOSFET を使用する場合、ほとんどのアプリケーションでは、ロジック・レベル関値の MOSFET を使用する必要があります。FET のブレークダウン電圧( $BVD_{SS}$ )仕様にも十分注意を払ってください。

パワーFET の選択基準には、オン抵抗( $R_{DS(ON)}$ )、ミラー容量( $C_{MILLER}$ )、入力電圧、および最大出力電流などがあります。  $C_{MILLER}$  は、FET メーカーのデータシートに一般に記載されているゲート電荷曲線から概算できます。  $C_{MILLER}$  は、曲線がほぼ平らな区間の水平軸に沿ったゲート電荷の増分を、FET のドレイン端子とソース端子間の電圧差( $V_{DS}$ )の仕様規定されている変化量で割ったものに等しくなります。この結果に、アプリケーションで印加される  $V_{DS}$  とゲート電荷曲線で規定された  $V_{DS}$  との比率を乗じます。連続モードで動作している時の上側 FET と下側 FET のデューティ・サイクルは式 10 と式 11 で与えられます。

$$Main Switch Duty Cycle = V_{OUT}/V_{IN}$$

(10)

Synchronous Switch Duty Cycle =

$$(V_{IN} - V_{OUT})/V_{IN}$$

(11)

最大出力電流時における FET の消費電力は、式 12 と式 13 で与えられます。

analog.com.jp Rev. 0 | 24 of 41

# アプリケーション情報

$$P_{MAIN} = \frac{V_{OUT}}{V_{IN}} (I_{MAX})^2 (1+\delta) R_{DS(ON)} +$$

$$(V_{IN})^2 \left(\frac{I_{MAX}}{2}\right) (R_{DR}) (C_{MILLER}) \times$$

$$\left(\frac{1}{V_{INTCC} - V_{THMIN}} + \frac{1}{V_{THMIN}}\right) (f)$$

(12)