## 正誤表

この製品のデータシートに間違いがありましたので、お詫びして訂正いたします。 この正誤表は、2021年1月20日現在、アナログ・デバイセズ株式会社で確認した誤りを 記したものです。

なお、英語のデータシート改版時に、これらの誤りが訂正される場合があります。

正誤表作成年月日: 2021年1月20日

製品名:LT8698S/LT8698S-1

対象となるデータシートのリビジョン(Rev): Rev.0

訂正箇所:40ページ

スペック表内 Related Parts の表 LT8611 の機能説明の内容

#### 【誤】

· · 効率 946% · ·

#### 【正】

· · 効率 94.6% · ·

社/〒105-6891 東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル

電話 03 (5402) 8200

大阪営業所/〒532-0003 大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 電話 06(6350)6868

アナログ・デバイセズ株式会社

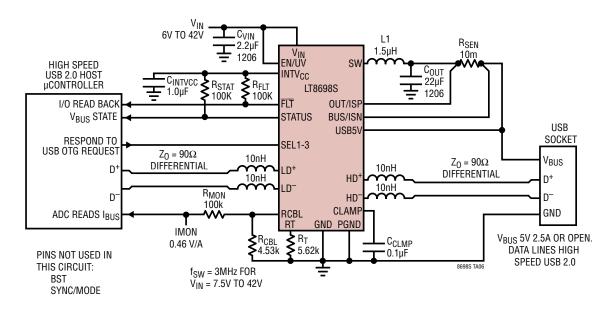

# ケーブル電圧降下補償機能とデータライン保護機能を備える 5V 3A 出力、42V 入力 USB チャージャ

## 特長

- 広い入力電圧範囲:最大42V

- プログラマブルなケーブル電圧降下補償機能により、 リモート USB ソケットに対する高精度の 5V レギュレー ションを提供

- High Speed USB 2.0 準拠のデータライン・スイッチ

- 大手メーカーおよび USB BC 1.2 のプロファイルを含む 選択可能なチャージャ・プロファイル

- Silent Switcher®2技術と選択可能なスペクトラム拡散周波数変調機能によって超低EMIを実現

- 堅牢なデータライン保護

- 最大20Vの短絡状態に対する耐性

- 最大8kVの接触放電および15kVの空気放電に対する IEC61000-4-2 ESD 保護

- ステータスおよび障害出力ピンが使用可能

- プログラマブルで同期可能なスイッチング周波数: 300kHz~3MHz

- 強制連続モードまたはパルス・スキップ・モードを 選択可能

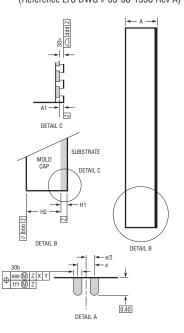

- V<sub>IN</sub>ピンとGNDピンの間隔が0.75mmの 小型4mm×6mm×0.94mm LQFNパッケージ

- AEC-Q100認定進行中

## アプリケーション

- オートモーティブ USB

- 産業用USB

#### 概要

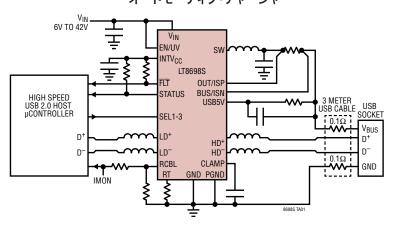

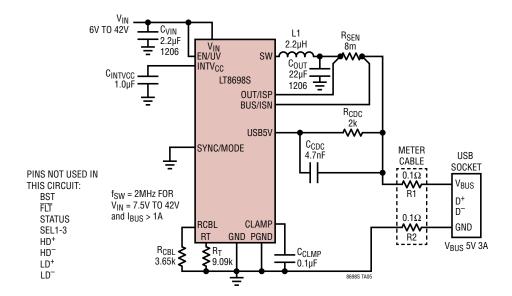

LT®8698S は、5VのUSB V<sub>BUS</sub>レールに最大42Vの入力電圧から最大3Aの電力を供給する目的で設計された、小型で高効率の同期整流式モノリシック降圧スイッチング・レギュレータです。プログラマブルなケーブル電圧降下補償機能により、USBソケットとLT8698Sが自動車の配線ハーネスのような長いケーブルで接続されている場合でも、高精度の5V V<sub>BUS</sub>レギュレーションを維持します。Silent Switcher® (サイレント・スイッチャ)技術と選択可能なスペクトラム拡散周波数変調機能により、超低EMI/EMCを実現しています。

LT8698S は、USB BC 1.2 CDP、DCP、SDPや一般的な独自 規格のプロファイルなど、ポータブル・デバイス用チャージャ の各種プロファイルをサポートします。内蔵された  $V_{BUS}$  リセット機能と  $V_{BUS}$  レギュレータ・ディスエーブル機能により、 USB OTG 機能をサポートします。

LT8698Sの堅牢な High Speed USB 2.0 データ・ライン・スイッチは、最大 20V の短絡状態と最大 8kV の接触放電および 15kV の空気放電レベルの IEC61000-4-2 ESD イベントに対して、上流の USB ホスト・マイクロコントローラを保護します。更に、 $V_{BUS}$  モニタおよび障害保護機能により、USB パワー・スイッチを不要にしています。LT8698Sは、 $V_{IN}$  とPGND の間に 2 個の並列 10nF コンデンサを内蔵し、EMI/EMC性能を改善しています。LT8698S-1 はこれらのコンデンサを内蔵していません。

全ての登録商標および商標の所有権は、それぞれの所有者に帰属します。

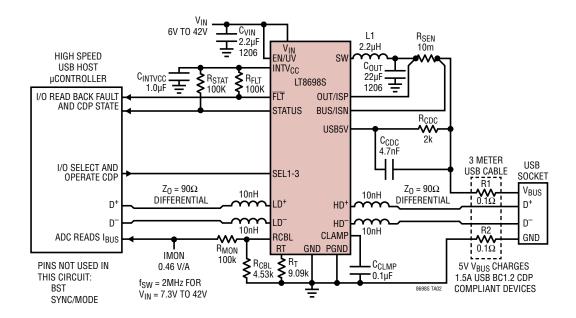

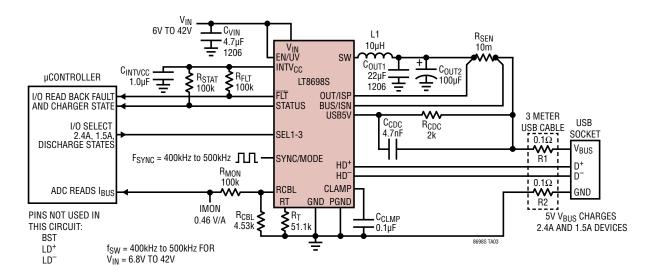

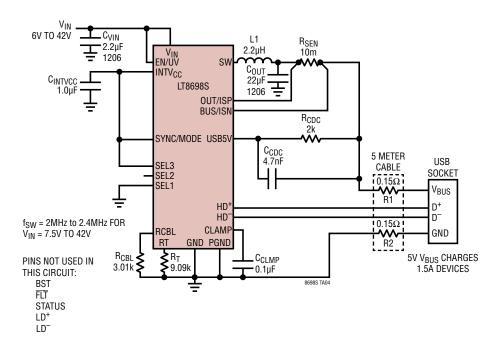

#### 標準的応用例

高速データライン保護機能とケーブル電圧降下補償機能を備える オートモーティブ・チャージャ

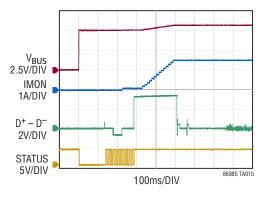

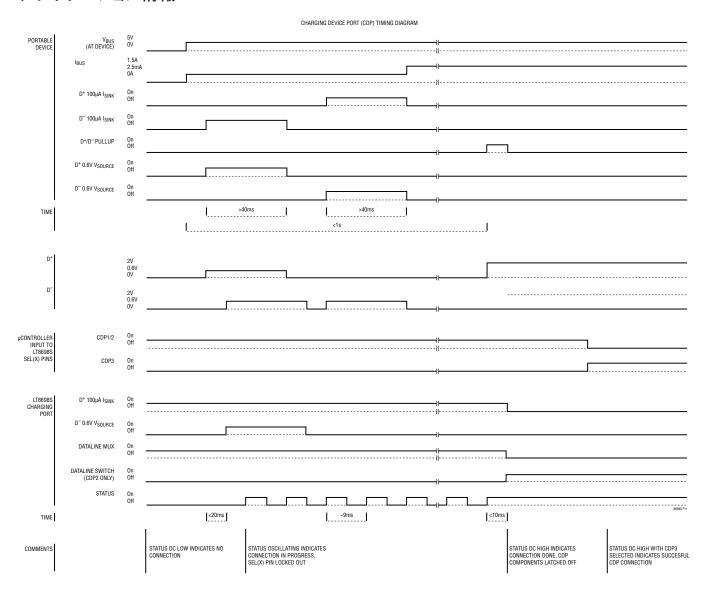

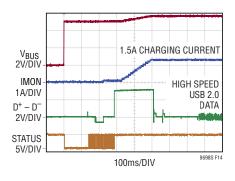

#### USB BC1.2 CDP セッション

Rev.0

1

文書に関するご意見 詳細:www.analog.com

#### 絶対最大定格

#### (Note 1)

| V <sub>IN</sub> 、EN/UV、OUT/ISP、BUS/ISN、USB5V42    | ۷۷ |

|---------------------------------------------------|----|

| HD <sup>+</sup> 、HD <sup>-</sup> 、CLAMP20         | )V |

| SYNC/MODE, FLT, STATUS,                           |    |

| SEL1、SEL2、SEL3、LD <sup>+</sup> 、LD <sup>-</sup> 6 | ٥V |

| RCBL, RT2                                         | 2V |

| 動作ジャンクション温度範囲(Note 2)                             |    |

| LT8698SE40°C ~ 125°                               | ,C |

| LT8698SJ40°C~150°                                 | ,C |

| 保存温度範囲65°C~150°                                   | ,C |

| ピーク・パッケージ・ボディ・リフロー温度                              | ,C |

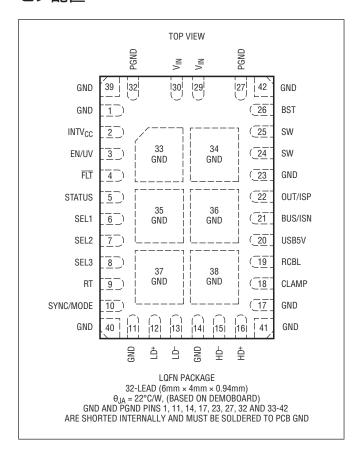

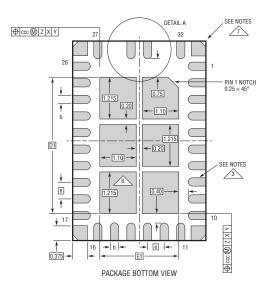

## ピン配置

## 発注情報

|                  |            | 製品マ    | ーキング   | パッケージ・                                        |       |                |

|------------------|------------|--------|--------|-----------------------------------------------|-------|----------------|

| 製品番号             | パッド/ボール仕上げ | デバイス   | 仕上げコード | タイプ                                           | MSL定格 | 温度範囲(Note 2参照) |

| LT8698SEV#PBF    |            | 8698V  |        |                                               |       | -40°C to 125°C |

| LT8698SJV#PBF    | Au (RoHS)  | 00900  | -4     | LQFN (Laminate Package<br>with QFN Footprint) | 3     | -40°C to 150°C |

| LT8698SEV-1#PBF  |            | 000001 | e4     |                                               |       | -40°C to 125°C |

| LT8698SJV-1#PBF  |            | 8698S1 |        |                                               |       | -40°C to 150°C |

| オートモーティブ製品**     |            |        |        |                                               |       |                |

| LT8698SEV#WPBF   |            | 8698V  |        | LQFN (Laminate Package<br>with QFN Footprint) | 3     | -40°C to 125°C |

| LT8698SJV#WPBF   | Au (PoUC)  | 80987  | e4     |                                               |       | -40°C to 150°C |

| LT8698SEV-1#WPBF | Au (RoHS)  | 000001 |        |                                               |       | -40°C to 125°C |

| LT8698SJV-1#WPBF |            | 8698S1 |        |                                               |       | -40°C to 150°C |

- デバイスの温度グレードは出荷時のコンテナのラベルで示してあります。

- パッドまたはボールの仕上げコードはIPC/JEDEC J-STD-609 に準拠しています。

- 推奨のPCBアセンブリ手順および製造手順についての参照先

- パッケージおよびトレイの図面の参照先

<sup>\*\*</sup> このデバイス・バージョンは、オートモーティブ・アプリケーションの品質と信頼性の条件に対応するため、管理の行き届いた製造工程により供給されます。これらのモデルは#W接尾部 により指定されます。オートモーティブ・アプリケーション向けには、上記のオートモーティブ・グレード製品のみを提供しています。特定製品のオーダー情報とこれらのモデルに特有の オートモーティブ信頼性レポートについては、最寄りのアナログ・デバイセズ代理店までお問い合わせください。

# 電気的特性 ●は全動作温度範囲での規格値を意味する。それ以外はT<sub>A</sub> = 25°Cでの値(Note 2)。

| SYMBOL                  | PARAMETER                                                                                       | CONDITIONS                                                                                                                                                                                              |   | MIN                   | ТҮР                  | MAX                    | UNITS             |

|-------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------------|----------------------|------------------------|-------------------|

|                         | V <sub>IN</sub> Shutdown Current                                                                | V <sub>EN/UV</sub> = 0.25V, V <sub>IN</sub> = 12V                                                                                                                                                       |   |                       | 0.1                  | 1                      | μА                |

|                         | V <sub>IN</sub> Current in Regulation                                                           |                                                                                                                                                                                                         | • |                       | 2.5<br>23            | 4<br>36                | mA<br>mA          |

| V <sub>CHG</sub>        | Regulator Output Voltage at BUS/ISN                                                             | $\begin{split} I_{LOAD} &= 0\text{A, R}_{CBL} = 3.57\text{k (Note 4)} \\ I_{LOAD} &= 2.4\text{A, R}_{CBL} = 3.57\text{k (Note 4)} \\ I_{LOAD} &= 0\text{A, V}_{USB5V} = 0\text{V (Note 4)} \end{split}$ | • | 4.925<br>5.52<br>5.93 | 5.00<br>5.61<br>6.05 | 5.063<br>5.680<br>6.13 | V<br>V<br>V       |

|                         | USB5V Voltage                                                                                   | V <sub>IN</sub> = 5V to 42V                                                                                                                                                                             | • | 4.915                 | 4.99                 | 5.053                  | V                 |

|                         | Upper FLT Threshold Offset                                                                      | Percentage of V <sub>USB5V</sub> , V <sub>USB5V</sub> Falling                                                                                                                                           | • | 4                     | 7                    | 10                     | %                 |

|                         | Lower FLT Threshold Offset                                                                      | Percentage of V <sub>USB5V</sub> , V <sub>USB5V</sub> Rising                                                                                                                                            | • | 4                     | 7                    | 10                     | %                 |

|                         | FLT Threshold Hysteresis                                                                        | Percentage of V <sub>USB5V</sub>                                                                                                                                                                        |   |                       | 3                    |                        | %                 |

| I <sub>CDP</sub>        | Regulator Output Current Limit                                                                  | $V_{BUS/ISN} = 4.5V$ , $R_{SEN} = 10 m \Omega$                                                                                                                                                          |   | 2.55                  | 2.65                 | 2.75                   | А                 |

|                         | Latch-On Time in Current Limit                                                                  | $V_{BUS/ISN} = 0.2V$                                                                                                                                                                                    |   | 3.4                   | 4.2                  | 5                      | ms                |

| T <sub>SHTDWN_REC</sub> | Latch-Off Time in Current Limit                                                                 | $V_{BUS/ISN} = 0.2V$                                                                                                                                                                                    |   | 48                    | 59                   | 70                     | ms                |

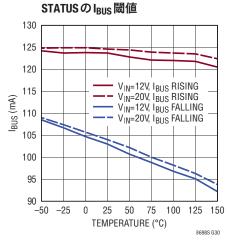

|                         | Regulator Output Current STATUS $I_{BUS/ISN}$ Falling, $R_{SEN} = 10 \text{m} \Omega$ Threshold |                                                                                                                                                                                                         |   |                       | 100                  | 180                    | mA                |

|                         | Regulator Output Current STATUS $R_{SEN} = 10 m \Omega$ Threshold Hysteresis                    |                                                                                                                                                                                                         |   |                       | 20                   |                        | mA                |

|                         | Regulator Output Sink Current V <sub>BUS/ISN</sub> = 6.3V (Note 4)                              |                                                                                                                                                                                                         |   |                       | -2.3                 | -1.7                   | А                 |

|                         | R <sub>CBL</sub> Monitor Voltage                                                                | $I_{LOAD} = 0A, R_{SEN} = 10m\Omega$ $I_{LOAD} = 2.4A, R_{SEN} = 10m\Omega$                                                                                                                             |   |                       | 2<br>1.10            | 50<br>1.15             | mV<br>V           |

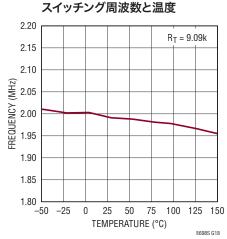

|                         | Oscillator Frequency                                                                            | $R_T = 9.09k$<br>$R_T = 66.5k$<br>$R_T = 5.76k$                                                                                                                                                         | • | 1.8<br>255<br>2.7     | 2<br>300<br>3        | 2.2<br>345<br>3.3      | MHz<br>kHz<br>MHz |

|                         | SYNC/MODE Low Threshold for Pulse-<br>Skip Operation                                            | V <sub>SYNC/MODE</sub> Rising                                                                                                                                                                           | • | 0.3                   | 0.7                  | 1.1                    | V                 |

|                         | SYNC/MODE Input High for Synced Operation                                                       |                                                                                                                                                                                                         | • | 1.5                   |                      |                        | V                 |

|                         | SYNC/MODE Input Low for Synced Operation                                                        |                                                                                                                                                                                                         | • |                       |                      | 0.4                    | V                 |

|                         | SYNC/MODE High Threshold for Spread Spectrum Operation                                          | V <sub>SYNC/MODE</sub> Rising                                                                                                                                                                           | • | 2.7                   | 3.2                  | 3.7                    | V                 |

|                         | SYNC/MODE Pull Up Current for Forced Continuous Operation                                       | V <sub>SYNC/MODE</sub> = 2V                                                                                                                                                                             | • | 2                     | 4.25                 | 6.5                    | μА                |

|                         | Top Switch Max Current Limit                                                                    |                                                                                                                                                                                                         |   | 5                     | 6                    | 7                      | А                 |

|                         | Top Switch On Resistance                                                                        | I <sub>SW</sub> = 1A                                                                                                                                                                                    |   |                       | 75                   |                        | mΩ                |

|                         | Bottom Switch On Resistance                                                                     | I <sub>SW</sub> = 1A                                                                                                                                                                                    |   |                       | 75                   |                        | mΩ                |

|                         | SW Leakage Current                                                                              |                                                                                                                                                                                                         |   | -1                    | 0                    | 1                      | μA                |

|                         | EN/UV Threshold                                                                                 | V <sub>EN/UV</sub> Falling                                                                                                                                                                              | • | 1.17                  | 1.31                 | 1.45                   | V                 |

|                         | EN/UV Threshold Hysteresis                                                                      |                                                                                                                                                                                                         |   |                       | 150                  |                        | mV                |

|                         | EN/UV Current                                                                                   | V <sub>EN/UV</sub> = 2V                                                                                                                                                                                 |   | -100                  |                      | 100                    | nA                |

|                         |                                                                                                 |                                                                                                                                                                                                         |   |                       |                      |                        |                   |

## LT8698S/LT8698S-1

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外はT<sub>A</sub> = 25°Cでの値(Note 2)。

| SYMBOL                  | PARAMETER                                                                                                                                                                | CONDITIONS                                                                                                  |   | MIN      | TYP        | MAX    | UNITS                    |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---|----------|------------|--------|--------------------------|

|                         | FLT Pull Down Resistance                                                                                                                                                 | $V_{FLT} = 0.1V$                                                                                            | • |          | 150        | 300    | Ω                        |

|                         | FLT Leakage                                                                                                                                                              | V <sub>FLT</sub> = 4V                                                                                       |   |          |            | 1      | μA                       |

|                         | STATUS Pull Down Resistance                                                                                                                                              | V <sub>STATUS</sub> = 0.1V                                                                                  | • |          | 150        | 300    | Ω                        |

|                         | STATUS Leakage                                                                                                                                                           | V <sub>STATUS</sub> = 4V                                                                                    |   |          |            | 1      | μА                       |

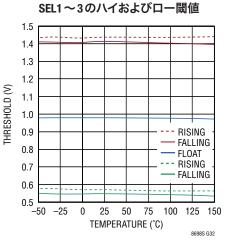

|                         | SEL1-3 Low Threshold                                                                                                                                                     | V <sub>SEL</sub> Rising                                                                                     | • | 0.48     | 0.58       | 0.68   | V                        |

|                         | SEL1-3 Low Threshold Hysteresis                                                                                                                                          |                                                                                                             |   |          | 35         |        | mV                       |

|                         | SEL1-3 High Threshold                                                                                                                                                    | V <sub>SEL</sub> Falling                                                                                    | • | 1.31     | 1.41       | 1.51   | V                        |

|                         | SEL1-3 High Threshold Hysteresis                                                                                                                                         |                                                                                                             |   |          | 35         |        | mV                       |

|                         | SEL1-3 Float Voltage                                                                                                                                                     |                                                                                                             | • | 0.9      | 1.0        | 1.1    | V                        |

|                         | SEL1-3 Input Current                                                                                                                                                     | $V_{SEL} = 4V$ $V_{SEL} = 0V$                                                                               |   |          | 45<br>–15  |        | μ <b>Α</b><br>μ <b>Α</b> |

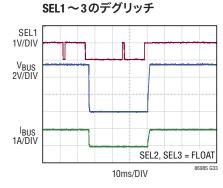

|                         | SEL1-3 De-bounce Time                                                                                                                                                    |                                                                                                             |   | 1.25     | 1.5        | 1.75   | ms                       |

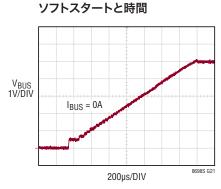

|                         | Soft Start Time                                                                                                                                                          |                                                                                                             |   | 0.7      | 1.1        | 1.6    | ms                       |

| データライン                  | ・スイッチ                                                                                                                                                                    |                                                                                                             |   |          |            |        |                          |

| $V_{OL}, V_{OH}$        | Signal Range                                                                                                                                                             |                                                                                                             | • | 0        |            | 3.6    | V                        |

|                         | Off HD <sup>+</sup> , HD <sup>-</sup> Current $V_{HD}^+$ , $V_{HD}^- = 3.6V$ , $V_{LD}^+$ , $V_{LD}^- = 0V$ $V_{HD}^+$ , $V_{HD}^- = 20V$ , $V_{LD}^+$ , $V_{LD}^- = 0V$ |                                                                                                             |   | -1       | 0<br>0.75  | 1<br>1 | μA<br>mA                 |

|                         | Off LD <sup>+</sup> , LD <sup>-</sup> Current                                                                                                                            | $V_{HD}^+, V_{HD}^- = 0V, V_{LD}^+, V_{LD}^- = 3.6V$<br>$V_{HD}^+, V_{HD}^- = 20V, V_{LD}^+, V_{LD}^- = 0V$ |   | -1<br>-1 | 0          | 1      | μ <b>Α</b><br>μ <b>Α</b> |

|                         | On Leakage Current                                                                                                                                                       | $V_{HD}^+, V_{HD}^- = 3.6V, 0V$                                                                             |   | -100     | 0          | 100    | nA                       |

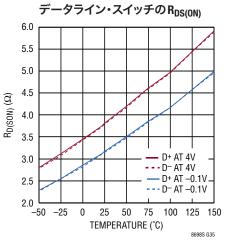

|                         | On Resistance                                                                                                                                                            | $V_{HD}^+$ , $V_{HD}^- = 0V$ , 3.6V, $I_{LD}^+$ , $I_{LD}^- = 20$ mA                                        |   |          | 3          |        | Ω                        |

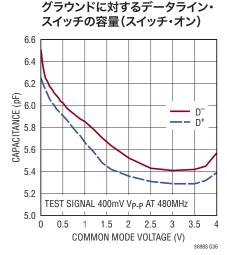

|                         | On Capacitance to Ground                                                                                                                                                 | $V_{HD}^+$ , $V_{HD}^- = 200 \text{mV}_{DC}$ , $400 \text{mV}_{P-P}$ , $480 \text{MHz}$ (Note 5)            |   |          | 6.1        |        | pF                       |

| V <sub>BUS</sub> 放電     |                                                                                                                                                                          |                                                                                                             |   |          |            |        |                          |

|                         | BUS/ISN Discharge Current Sink                                                                                                                                           | $V_{BUS/ISN} = 5V$                                                                                          |   | 6        | 9          | 12     | mA                       |

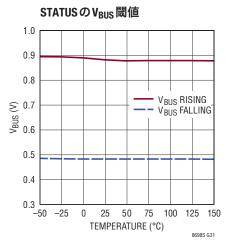

| V <sub>BUS_LKG</sub>    | BUS/ISN Discharge Status Threshold                                                                                                                                       | V <sub>BUS/ISN</sub> Falling                                                                                |   |          | 0.5        | 0.7    | V                        |

|                         | BUS/ISN Discharge Status Threshold<br>Hysteresis                                                                                                                         |                                                                                                             |   |          | 0.35       |        | V                        |

| T <sub>VLD_VLKG</sub>   | Maximum BUS/ISN Discharge Time                                                                                                                                           | V <sub>BUS/ISN</sub> = 1V                                                                                   |   |          | 400        | 500    | ms                       |

| T <sub>VBUS_REAPP</sub> | Minimum BUS/ISN Low Time                                                                                                                                                 | $V_{BUS/ISN} = 1V$                                                                                          |   | 100      | 120        |        | ms                       |

|                         | STATUS Oscillation Period                                                                                                                                                |                                                                                                             |   | 7.5      | 9          | 10.5   | ms                       |

| V <sub>BUS</sub> オフ     |                                                                                                                                                                          |                                                                                                             |   |          |            |        |                          |

| IVBUS_LKG_SRC           | Regulator Output Leakage Current                                                                                                                                         | $V_{BUS/ISN} = 0V$<br>$V_{BUS/ISN} = 5V$                                                                    |   | -70      | -0.1<br>15 | 80     | μΑ<br>μΑ                 |

| R <sub>OTG_VBUS</sub>   | Regulator Output Resistance                                                                                                                                              | V <sub>BUS/ISN</sub> = 0.75V                                                                                |   | 10       | 350        |        | kΩ                       |

# 電気的特性 ●は全動作温度範囲での規格値を意味する。それ以外はT<sub>A</sub> = 25°Cでの値(Note 2)。

| SYMBOL                                       | PARAMETER                                                                                   | CONDITIONS                                       |   | MIN   | TYP  | MAX  | UNITS |

|----------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------|---|-------|------|------|-------|

| USB BCS 1.2 7                                | ・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・ | ・(CDP)のプロファイル                                    |   |       |      |      |       |

| V <sub>DAT_REF</sub>                         | HD <sup>+</sup> Data Detect Voltage                                                         | V <sub>HD</sub> <sup>+</sup> Rising              |   | 0.25  | 0.32 | 0.40 | V     |

|                                              | HD <sup>+</sup> Data Detect Hysteresis                                                      |                                                  |   |       | 45   |      | mV    |

| V <sub>IH</sub>                              | HD <sup>+</sup> , HD <sup>-</sup> Logic High                                                |                                                  |   | 2.0   |      |      | V     |

| V <sub>IL</sub>                              | HD <sup>+</sup> , HD <sup>-</sup> Logic Low                                                 |                                                  |   |       |      | 0.8  | V     |

| V <sub>LGC</sub>                             | HD <sup>+</sup> , HD <sup>-</sup> Logic Threshold                                           |                                                  |   | 0.8   | 1.4  | 2.0  | V     |

| V <sub>DM_SRC</sub>                          | HD <sup>-</sup> Voltage Source                                                              | $I_{HD}^- = -100\mu A, V_{HD}^+ = 0.6V$          |   | 0.5   | 0.6  | 0.7  | V     |

| I <sub>DP_SINK</sub>                         | $HD^+$ Current Source $V_{HD}^+ = 0.6V$                                                     |                                                  |   | 25    | 100  | 175  | μА    |

| V <sub>DAT_SINK</sub>                        | HD <sup>+</sup> Data Sink Voltage                                                           | $I_{HD}^+ = 25\mu A$                             |   |       | 0.06 | 0.15 | V     |

| T <sub>VDMSRC_EN</sub>                       | HD <sup>-</sup> Voltage Source Enable Time                                                  | $V_{HD}^{+} = 0.6V$                              |   |       | 0.5  | 20   | ms    |

| T <sub>CON_IDPSNK_</sub>                     | HD <sup>+</sup> Current Source Connect Disable<br>Time                                      | $V_{HD}^+ = 2V$                                  |   |       | 0.75 | 10   | ms    |

| T <sub>VDPSRC_ON</sub>                       | Minimum Accepted HD <sup>+</sup> Voltage Source<br>On Time                                  | $V_{HD}^{+}=0.6V$                                |   |       | 32   | 40   | ms    |

| T <sub>VDMSRC_DIS</sub>                      | HD <sup>-</sup> Voltage Source Disable Time                                                 | $V_{HD}^+ = 0V$                                  |   |       | 0.5  | 20   | ms    |

|                                              | Minimum Accepted HD <sup>+</sup> Source Voltage Off Time                                    | $V_{HD}^+ = 0V$                                  |   |       | 32   | 40   | ms    |

| T <sub>SVLD_CON_PWD</sub>                    | Maximum Accepted USB Connect Time                                                           | $V_{HD}^+, H_D^- = 0V$                           |   | 1     | 1.15 |      | S     |

| USB BCS 1.2 専                                | 専用チャージング・ポート(DCP)のプロ                                                                        |                                                  | · |       |      |      |       |

| R <sub>DCP_DAT</sub>                         | Dataline Short Resistance                                                                   | $V_{HD}^{+} = 0.6V, I_{HD}^{-} = -2.5 \text{mA}$ |   |       | 85   | 200  | Ω     |

| R <sub>DAT_LKG</sub>                         | Dataline Short Pull Down Resistance                                                         |                                                  |   | 300   | 500  |      | kΩ    |

| USB BCS 1.2核                                 | 票準ダウンストリーム・ポート(SDP)のこ                                                                       | プロファイル                                           |   |       |      |      |       |

| R <sub>DP_DWN</sub> ,<br>R <sub>DM_DWN</sub> | Dataline Termination Resistor                                                               |                                                  |   | 14.25 | 20   | 24.8 | kΩ    |

| 2.4A チャージ                                    | アのプロファイル                                                                                    |                                                  |   |       |      |      |       |

|                                              | HD <sup>+</sup> Voltage                                                                     | V <sub>BUS/ISN</sub> = 5V                        |   | 2.60  | 2.68 | 2.76 | V     |

|                                              | HD <sup>+</sup> Output Resistance                                                           |                                                  |   |       | 23   |      | kΩ    |

|                                              | HD <sup>-</sup> Voltage                                                                     | V <sub>BUS/ISN</sub> = 5V                        |   | 2.60  | 2.68 | 2.76 | V     |

|                                              | HD <sup>-</sup> Output Resistance                                                           |                                                  |   |       | 23   |      | kΩ    |

| 2.1Aチャージ                                     | ・<br>マのプロファイル                                                                               |                                                  | · |       |      |      |       |

|                                              | HD <sup>+</sup> Voltage                                                                     | V <sub>BUS/ISN</sub> = 5V                        |   | 2.60  | 2.68 | 2.76 | V     |

|                                              | HD <sup>+</sup> Output Resistance                                                           |                                                  |   |       | 23   |      | kΩ    |

|                                              | HD <sup>-</sup> Voltage                                                                     | V <sub>BUS/ISN</sub> = 5V                        |   | 1.94  | 2.00 | 2.06 | V     |

|                                              | HD <sup>-</sup> Output Resistance                                                           |                                                  |   |       | 30   |      | kΩ    |

## LT8698S/LT8698S-1

### 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外はTA=25°Cでの値(Note 2)。

| SYMBOL | PARAMETER                                           | CONDITIONS                | MIN  | TYP  | MAX  | UNITS |

|--------|-----------------------------------------------------|---------------------------|------|------|------|-------|

| 1Aチャーシ | <b>ジャのプロファイル</b>                                    |                           |      |      |      |       |

|        | HD <sup>+</sup> Voltage                             | $V_{BUS/ISN} = 5V$        | 1.94 | 2.00 | 2.06 | V     |

|        | HD <sup>+</sup> Output Resistance                   |                           |      | 30   |      | kΩ    |

|        | HD <sup>-</sup> Voltage                             | V <sub>BUS/ISN</sub> = 5V | 2.60 | 2.68 | 2.76 | V     |

|        | HD <sup>-</sup> Output Resistance                   |                           |      | 23   |      | kΩ    |

| 2Aチャーシ | <b>ジャのプロファイル</b>                                    | •                         | •    |      |      |       |

|        | HD <sup>+</sup> , HD <sup>-</sup> Voltage           | $V_{BUS/ISN} = 5V$        | 1.2  | 1.25 | 1.35 | V     |

|        | HD <sup>+</sup> , HD <sup>-</sup> Output Resistance |                           |      | 7.5  |      | kΩ    |

Note 1: 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。また、長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える恐れがある。

Note 2: LT8698SE およびLT8698SE-1は、 $0^{\circ}$ C~125 $^{\circ}$ Cのジャンクション温度で性能仕様に適合することが確認されている。 $-40^{\circ}$ C~125 $^{\circ}$ Cの動作ジャンクション温度範囲での仕様は、設計、特性評価および統計学的なプロセス・コントロールとの相関で確認されている。LT8698SJ およびLT8698SJ-1は、 $-40^{\circ}$ C~150 $^{\circ}$ Cの全動作温度範囲で動作することが確認されている。ジャンクション温度が高いと、動作寿命は短くなる。125 $^{\circ}$ Cを超えるジャンクショ

ン温度では動作寿命がディレーティングされる。ジャンクション温度  $(T_J(^\circ C))$  は周囲温度  $(T_A(^\circ C))$  および消費電力 (PD(W)) から次式に従って計算される。

$$T_J = T_A + (P_D \bullet \theta_{JA})$$

ここで、 $\theta_{JA}$ (°C/W)はパッケージの熱抵抗である。

Note 3: このデバイスには過負荷状態の間デバイスを保護するための過熱保護機能が備わっている。過熱保護機能がアクティブなときジャンクション温度は150°Cを超える。規定されている最大動作ジャンクション温度を超えた状態で動作が継続すると、寿命が短くなる。

Note 4: DUT は36ページの CDP チャージャ・アプリケーションの回路によく似たクローズドループ・テスト回路内に構成される。

Note 5:パラメータは製造プロセスではテストされない。

**Note 6:**  $\theta$ の値はJESD51 の条件に従ってシミュレーションによって決定されるが、 $\theta$ <sub>JA</sub>の値だけはデモ・ボードを使ったシミュレーションによって決定される。PCB レイアウトに関する検討事項と熱データの例については、アプリケーション情報のセクションを参照。

Rev.0

詳細:www.analog.com

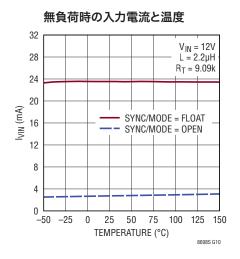

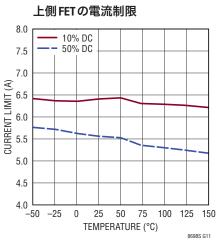

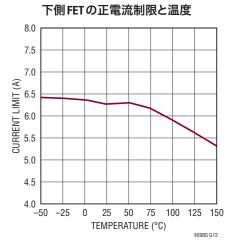

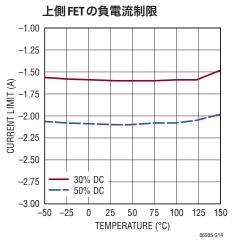

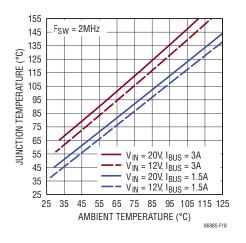

## 代表的な性能特性 注記がない限り、TA = 25°C、VIN = 12V。

出力電流の負荷曲線

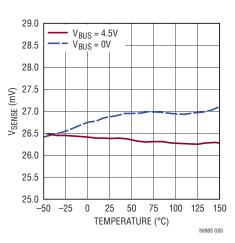

検出電圧(V<sub>ISP</sub> - V<sub>ISN</sub>)と温度

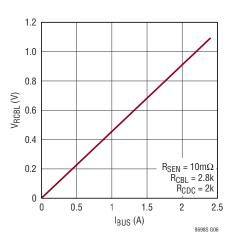

RCBLの電圧と負荷

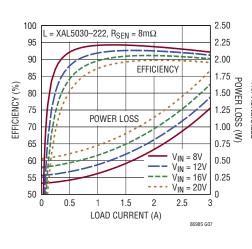

T<sub>A</sub> = 25°Cでの効率

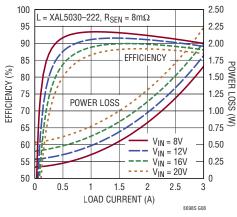

T<sub>A</sub> = 90°Cでの効率

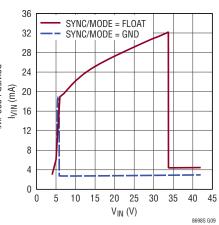

無負荷時の入力電流とVIN

## 代表的な性能特性 注記がない限り、T<sub>A</sub> = 25°C、V<sub>IN</sub> = 12V。

Rev.0

8

詳細:www.analog.com

## 代表的な性能特性 注記がない限り、TA = 25°C、VIN = 12V。

スイッチング周波数 と負荷電流

2.40

(WHZ)

1.60

1.20

0.40

SYNC/MODE = FLOAT SYNC/MODE = LOW SYNC/MODE = LOW

**起動/ドロップアウト**Igus = 0A

V<sub>IN</sub>

10ms/DIV

8698S G22

2MHzでの最大周波数

## 代表的な性能特性 注記がない限り、T<sub>A</sub> = 25°C、V<sub>IN</sub> = 12V。

VUSBSV 2V/DIV GLITCH APPLIED TO USBSV PIN FAULT LATCH-OFF 2ms/DIV

Rev.0

10

詳細:www.analog.com

## 代表的な性能特性 注記がない限り、T<sub>A</sub> = 25°C、V<sub>IN</sub> = 12V。

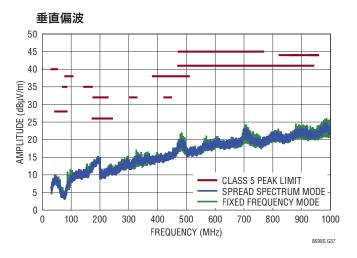

放射 EMI 性能 (ピーク検出器およびクラス5ピーク限度値での CISPR25 放射エミッション) EMI フィルタを取り付けた DC2688A デモ・ボード、 $V_{\rm IN}$  = 14V、 $I_{\rm VBUS}$  = 2.5A、 $f_{\rm SW}$  = 2MHz、 L = XFL4020-222、 $C_{\rm VIN2}$  および  $C_{\rm VIN3}$  を実装、LT8698S のみ

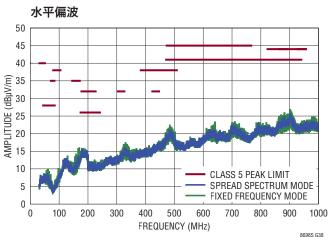

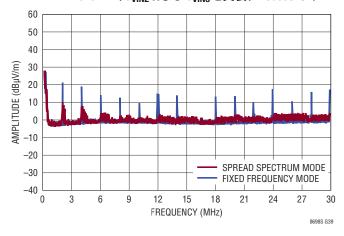

#### 伝導 EMI 性能 EM フィルタを取り付けた DC2688A デモ・ボード、V<sub>IN</sub> = 14V、I<sub>VBUS</sub> = 2.5A、f<sub>SW</sub> = 2MHz、 L = XFL4020-222、C<sub>VIN2</sub> および C<sub>VIN3</sub>を実装、LT8698S のみ

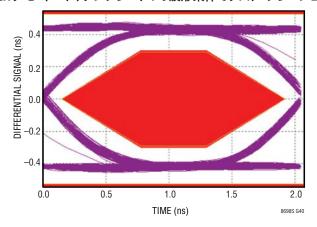

High Speed USB 2.0 のアイ・ダイアグラム DC2688A デモ・ボード、テンプレート1 の波形条件でテスト・プレーン2 で測定

#### ピン機能

**GND(1、11、14、17、23番ピン)**: GNDピンは内部制御回路の帰還側であり、グラウンドに接続する必要があります。すべての GND ピンと PGND ピンは、内部で互いに短絡されます。

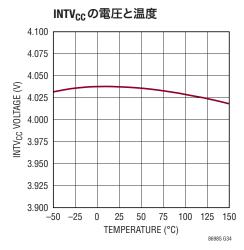

INTV<sub>CC</sub> (2番ピン): INTV<sub>CC</sub> は、内部 4Vリニア電圧レギュレータのバイパス・ピンです。このピンは、内部パワー・スイッチのゲート・ドライバと制御回路に電力を供給します。 INTV<sub>CC</sub>には、外付け終端抵抗によって最大 1mA の負荷をかけることができます。INTV<sub>CC</sub>に過度の負荷をかけると、動作の信頼性を損ないます。このピンは、LT8698S の近くに配置される 1 $\mu$ Fの低ESR セラミック・コンデンサでグラウンドにバイパスします。

EN/UV (3番ピン): EN/UV は、イネーブル/プログラマブル低電圧ロックアウト・ピンです。EN/UV ピンの電圧が閾値より低くなると、LT8698S はシャットダウンし、閾値より高くなると、イネーブルになります。EN/UV の閾値電圧は、上昇時1.46V、下降時1.31Vです。EN/UVが0.25Vより低くなると、 $V_{IN}$ の電流は $1\mu A$ 未満まで低減されます。 $V_{IN}$ からの外付け抵抗分圧器を使用して、LT8698Sのシャットダウンをトリガする低電圧ロックアウト閾値を設定できます。詳細については、アプリケーション情報のセクションを参照してください。EN/UVを使用しない場合は、 $V_{IN}$ に接続します。

FLT (4番ピン): FLT は、内部障害ロジックのオープンドレイン出力です。FLT は、出力電圧がレギュレーション状態ではない障害状態が4.2ms続いた後にローになります。INTV<sub>CC</sub>が3.6Vより低くなるか、または内部サーマル・シャットダウン機能が作動した場合、FLT は直ちにローになります。障害がない状態が4.2ms続いた後、FLT は高インピーダンスに移行します。FLT が有効なのは、V<sub>IN</sub>が4.5Vより高く、EN/UVが1.46Vより高い場合です。FLT を使用しない場合は、フロート状態にします。

**STATUS (5番ピン)**: STATUS はオープンドレイン出力インジケータです。STATUSピンの機能は、SEL1~3ピンで選択したステートによって決まります。詳細については、表6を参照してください。STATUS は4.2ms の間デバウンスされます。このピンが有効なのは、 $V_{IN}$ が4.5Vより高く、EN/UVが1.46Vより高い場合です。STATUS を使用しない場合は、フロート状態にします。

**SEL1、SEL2、SEL3(6~8番ピン)**: SEL1~3は、LT8698S の USB 機能の選択に使用するトライステート入力ピンです。詳 細については、アプリケーション情報のセクションの表6を 参照してください。0.58V より低い電圧に接続するとロジック・ロー、1.41V より高い電圧に接続するとロジック・ハイ、フロート状態にするとトライステートになります。トライステートを確実に検出できるように、もれ電流は1μA以下に抑えてください。USBステート間の確実な移行のために、SEL1~3ピンは1.5msの間デバウンスされます。

RT(9番ピン): RTは、スイッチング周波数設定ピンです。RTとグラウンドの間に抵抗を接続して、スイッチング周波数を選択します。詳細については、アプリケーション情報のセクションを参照してください。

SYNC/MODE(10番ピン): SYNC/MODEは、クロック同期/モード選択入力ピンです。SYNC/MODEピンをグラウンドに接続すると、パルス・スキップ・モードになります。クロック源に接続すると外部クロックの周波数に同期し、強制連続モードになります。フロート状態にすると強制連続モードになり、RTピンでスイッチング周波数を設定します。INTV<sub>CC</sub>に接続すると強制連続モードになり、スイッチング周波数のスペクトラム拡散周波数変調によってEMI/EMC性能を向上させます。

**LD<sup>+</sup>(12番ピン)**: LD<sup>+</sup>は、内部 USB D<sup>+</sup>データライン・スイッチの低電圧ホスト側です。このピンを使用しない場合は、フロート状態にします。

**LD**<sup>-</sup>(**13番ピン**): LD<sup>-</sup>は、内部 USB D<sup>-</sup>データライン・スイッチの低電圧ホスト側です。このピンを使用しない場合は、フロート状態にします。

**HD**<sup>-</sup>(15番ピン): HD<sup>-</sup>は、内部USB D<sup>-</sup>データライン・スイッチ の高電圧 USB ケーブルおよびデバイス側です。 HD<sup>-</sup> > 4.5V の場合、両方のデータライン・スイッチが遮断されます。 この ピンを使用しない場合は、フロート状態にします。

**HD+(16番ピン)**: HD+は、内部 USB D+データライン・スイッチの高電圧 USB ケーブルおよびデバイス側です。HD+> 4.5Vの場合、両方のデータライン・スイッチが遮断されます。 このピンを使用しない場合は、フロート状態にします。

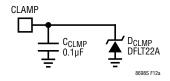

**CLAMP(18番ピン)**:CLAMPは、20V以上の0.1µF低ESRコンデンサでグラウンドにバイパスします。

RCBL(19番ピン): RCBLは、ケーブル電圧降下補償設定ピンです。RCBLとグラウンドの間に接続される抵抗R<sub>CBL</sub>を使って、USB5V入力電流を設定することにより、ケーブル電圧降下補償を設定します。RCBLは2mAをソースできます。RCBLに過度の容量性負荷がかかると、負荷過渡応答が低下することがあります。RCBLと容量性負荷の間に100kの抵抗を接続することにより、このピンの負荷容量を分離します。LT8698Sがイネーブルの場合、RCBLの負荷モニタ出力は有効です。イネーブルでない場合、出力はローになります。詳細については、アプリケーション情報のセクションを参照してください。

#### ピン機能

USB5V (20番ピン): USB5V は、5Vレギュレータ帰還ピンです。ケーブル電圧降下補償では、USB5Vピンの入力電流は検出される出力電流に比例します。 USB5VとBUS/ISN出力の間にR<sub>CDC</sub>を接続して、5Vのレギュレーションに加えてケーブル電圧降下補償を実行します。 USB5VとBUS/ISNの間にC<sub>CDC</sub>を接続して、ケーブル電圧降下補償ループの帯域幅を制限します。ケーブル電圧降下補償機能を使用しない場合は、USB5VをVBUSに短絡させます。

BUS/ISN(21番ピン): BUS/ISNは、USB VBUS出力/負電流検出入力ピンです。BUS/ISNは、エラーアンプに追加の入力を供給し、最大出力レギュレーション電圧が6.05Vを超えないようにします。また、BUS/ISNは、内部電流検出アンプに負の入力を提供します。ケーブル電圧降下補償と出力電流制限を使用する場合、BUS/ISNはR<sub>SEN</sub>検出抵抗に接続する必要があります。BUS/ISNピンは検出抵抗にケルビン接続し、BUS/ISNのPCBパターンからレギュレータの出力電流を分離します。その他の動作とPCBレイアウトについては、アプリケーション情報のセクションを参照してください。

OUT/ISP(22番ピン): OUT/ISPは、スイッチング・レギュレータの出力です。OUT/ISPは、SWの反対側のインダクタ端子に接続し、出力コンデンサによってバイパスする必要があります。また、OUT/ISPピンは電流検出アンプへの非反転入力であり、ケーブル電圧降下補償と出力電流制限を使用する場合、R<sub>SEN</sub>検出抵抗に接続する必要があります。OUT/ISPピンは検出抵抗にケルビン接続し、OUT/ISPパターンからレギュレータの出力電流を分離します。詳細については、アプリケーション情報のセクションを参照してください。

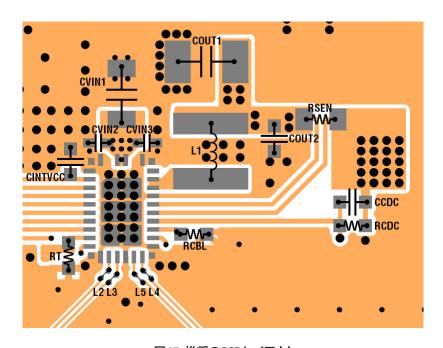

**SW(24、25番ピン)**: SW は、内蔵の上側および下側パワー・スイッチの出力ノードです。スイッチング・レギュレータのイン

ダクタに接続します。優れた性能を得るため、プリント回路基板上でのこのノードの面積は小さくなるようにしてください。

BST (26番ピン): BST は、(入力電圧より高い)駆動電圧を 上側パワー・スイッチに供給します。BSTはフロート状態のま まにしてください。

PGND(27、32番ピン): PGNDピンは内蔵の下側パワー・スイッチの帰還経路であり、互いに接続する必要があります。 PGNDピンのできるだけ近くに、入力コンデンサの負端子を配置してください。レイアウト例については、アプリケーション情報のセクションを参照してください。すべてのGNDピンとPGNDピンは、内部で互いに短絡されます。

$V_{IN}$  (29、30番ピン):  $V_{IN}$ ピンは内蔵の上側パワー・スイッチの入力経路であり、互いに接続する必要があります。 LT8698S は、最小  $2\mu$ Fのローカル入力バイパス・コンデンサを PGNDに接続する必要があります。 $V_{IN}$ と PGNDの間に、1個の2.2 $\mu$ Fコンデンサを配置できます。低EMI/EMCのためのベスト・プラクティスとして、2個の追加の0.1 $\mu$ F入力バイパス・コンデンサを  $V_{IN}$  に接続できます。1つの0.1 $\mu$ Fコンデンサは、 $V_{IN}$ と27番ピン PGNDの間に配置します。もう1つの同じ値の0.1 $\mu$ Fコンデンサは、 $V_{IN}$ と32番ピン PGNDの間に配置します。これらのコンデンサは、できるだけLT8698Sの近くに配置してください。レイアウト例については、アプリケーション情報のセクションを参照してください。

露出パッド(33~38番ピン):露出パッドはグラウンドに接続する必要があります。LT8698Sパッケージから周辺への熱抵抗を低減するため、これらのピンはPCB表面層の広い銅箔面積へ接続します。詳しい推奨事項については、アプリケーション情報のセクションを参照してください。

コーナ・サポート・パッド (39~42番ピン):パッケージの各コーナの4つのパッドは、ボード・レベルの機械的信頼性を向上させるためのサポート・パッドです。これらのパッドは、LT8698S内部でグラウンドに接続されます。パッドはPCBグラウンドに接続する必要があります。

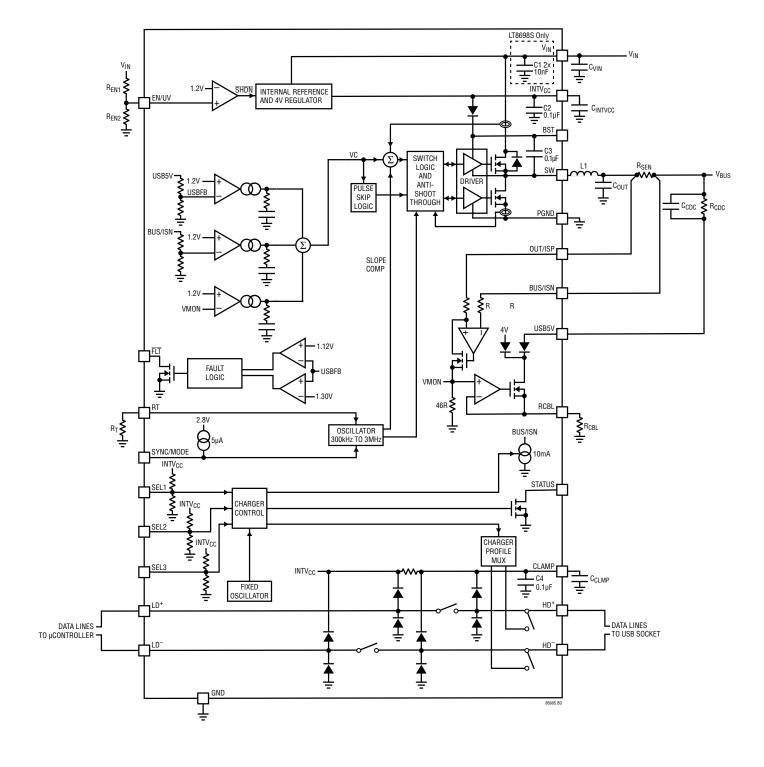

## ブロック図

#### 動作

LT8698Sは、ケーブル電圧降下補償機能と堅牢なUSBデータライン保護機能を備える、高効率の同期整流式モノリシックUSBチャージャです。LT8698Sは、5V USB V<sub>BUS</sub>レールへの電力供給用に最適化されたスイッチング・レギュレータと、High Speed USB 2.0データラインに接続され、上流のUSBホストICに障害保護およびESD保護を提供する、2個のアナログ・スイッチを搭載しています。更に、LT8698Sは多数のUSBチャージャ・プロファイルをサポートしており、大電流によるポータブル・デバイスの充電が可能です。

LT8698Sレギュレータは、モノリシック、固定周波数、ピーク 電流モードの降圧DC/DCコンバータです。RTピンに接続す る抵抗を使用して周波数を設定する発振器により、各クロッ ク・サイクルの開始時に内蔵の上側パワー・スイッチがオン します。次に、インダクタを流れる電流が増加して上側スイッ チの電流コンパレータが作動し、上側のパワー・スイッチが オフします。上側スイッチがオフするときのピーク・インダクタ 電流は、Vcノードの電圧によって制御されます。エラーアン プは、内部抵抗分圧器を通るUSB5Vピンの出力電圧と内 部リファレンスを比較し、Vcノードをサーボ制御してUSB5V ピンを5Vに調整します。負荷電流が増加すると、リファレン スと比較して帰還電圧が低くなるため、エラーアンプによっ てVcの電圧が上昇し、平均インダクタ電流が新たな負荷 電流に釣り合うまで上昇し続けます。強制連続モードでな い場合、上側パワー・スイッチがオフすると、下側の同期パ ワー・スイッチがオンし、次のクロック・サイクルが始まるか、 インダクタ電流が0に減少するまでオンのままになります。 過負荷状態によって下側スイッチの電流制限値を超える電 流が下側スイッチに流れると、スイッチャ電流が安全なレベ ルに戻るまで、次のクロック・サイクルは遅延します。また、 USB5Vがグラウンドに短絡する障害状態の間、BUS/ISNの 電圧は6.05Vに安定化され、接続されたデバイスにとって安 全なレベルに出力電圧を制限します。更に、出力障害状態 の間、LT8698Sは、OUT/ISPピンとBUS/ISNピンに接続され る外付け検出抵抗を使用して、高精度の平均出力電流制 限を提供します。

LT8698S はケーブル電圧降下補償機能を搭載しており、高負荷電流でも、長い抵抗性ケーブルの端で $V_{BUS}$ レールの5Vレギュレーションを提供します。ケーブル電圧降下補償を実現するために、LT8698S はRCBLピンを46・( $V_{OUT/ISP}$  -  $V_{BUS/ISN}$ )に駆動します。RCBLピンから $R_{CBL}$ 抵抗を通してソースされる電流はUSB5Vピンから得られるため、 $R_{CDC}/R_{CBL}$ の抵抗比に比例する出力オフセットが $R_{CDC}$ 抵抗の両端に発生し、5VのUSB5Vピン電圧に上乗せされます。

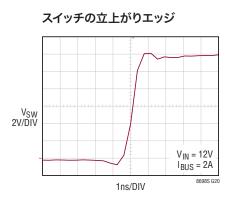

製品名LT8698Sの「S」は、第2世代のSilent Switcher 技術を表しています。この技術は、高スイッチング周波数で高いスイッチング・レギュレータ効率を実現するための高速スイッチング・エッジを可能にすると同時に、良好なEMI性能を実現します。この技術には、 $V_{IN}$ 、 $INTV_{CC}$ 、およびBST用のセラミック・コンデンサ(ブロック図のC1~C4)をパッケージに統合することが含まれています。これらのコンデンサは、すべてのAC電流ループを小さく保ち、EMI性能を改善します。LT8698S-1 は、 $V_{IN}$ に接続されるセラミック・コンデンサを内蔵していません。

EN/UVピンの電圧が1.46Vを超えると、スイッチング・レギュレータ、データライン・スイッチおよび関連する回路がイネーブルになります。 EN/UVピンの電圧が1.31Vを下回ると、スイッチングが停止し、データライン・スイッチが開きます。 EN/UVピンの電圧が0.25Vを下回ると、 $V_{\rm IN}$ の電流は $1\mu A$ 未満に低下します。

LT8698Sは主に強制連続モード(FCM)で動作し、広い負 荷範囲にわたって高速過渡応答と最大周波数での動作を 実現します。軽負荷時のレギュレータの効率を改善するに は、LT8698Sをパルス・スキップ・モード(PSK)で動作させ ます。パルス・スキップ・モードでは、軽負荷電流時のスイッ チング周波数を下げて、パルス間のVIN静止電流を減らし ます。パルス・スキップ・モードで動作させる場合は、SYNC/ MODEピンをグラウンドに接続します。強制連続モードで 動作させる場合は、SYNC/MODEピンをフロート状態にし ます。強制連続モードでスペクトラム拡散変調機能(SSM) を使用する場合は、SYNC/MODEピンに3.2Vより高いDC 電圧を印加します。SYNC/MODEピンにクロックを入力する と、内部発振器が外部クロックの周波数に同期し、強制連 続モードで動作します。強制連続モードの間は発振器が連 続して動作し、スイッチング波形の立上がり遷移がクロック に揃えられます。軽負荷時には、インダクタ電流を負の方向 に流して、設定スイッチング周波数を維持できます。LT8698S は、出力から電流をシンクして、負荷ステップ応答を改善で きます。負のインダクタ電流が大量に流れて入力に戻ること がないように、両方のパワー・スイッチに対して最小電流制 限が適用されます。スペクトラム拡散変調機能(SSM)は、RT ピンで設定された設定値より最大20%高い周波数でスイッ チング周波数のディザリングを実行し、スイッチング・エネル ギーを周波数領域で拡散させます。

出力電圧が設定値から±7% (標準)より大きく変化する場合や、電源障害状態が存在する場合は、USB5Vピンの電圧をモニタするコンパレータによってFLTピンはローになります。

### 動作

データライン・アナログ・スイッチにより、 $HD^+$ ピンと $LD^+$ ピン の間、および $HD^-$ ピンと $LD^-$ ピンの間の接続と遮断が可能です。接続時に、これらのスイッチは $OV \sim 3.6V$ の全同相電圧範囲にわたって小さい値の抵抗を提供し、 $HD^+$ /側では $OV \sim 20V$ 、 $LD^+$ /側では $OV \sim 20V$ 、 $OV \sim 20V$ 、 $OV \sim 20V$  をブロックできます。 $OV \sim 20V$  に関きまたは $OV \sim 20V$  をブロックできます。 $OV \sim 20V$  に関かる によってスイッチは遮断されます。

LT8698Sは、USB BC 1.2 CDP、DCP、SDPや一般的な独自規格のプロファイルなど、多数のチャージャ・プロファイルをサポートします。それぞれのプロファイルでは、様々な部品がデータラインに接続されます。これには抵抗分圧器、データライン間の短絡回路、電圧源および電流源などがあります。これらのプロファイルには、パッシブ方式のものと、USBソ

ケットに接続されたデバイスに何らかのアクティブ方式で反応するものがあります。USBソケットに接続されたデバイスは、プロファイルによって大電流チャージャを認識し、標準のUSB 2.0ソケットで通常許される0.5Aより多くの電流がV<sub>BUS</sub>から供給されます。

SEL1~3ピンは、ホスト・マイクロコントローラがLT8698Sの動作を制御するためのトライステート入力です。高インピーダンス入力が印加されると、内部抵抗分圧器はこれらのピンを1Vにバイアスします。SEL1~3ピンは、LT8698Sにステートの変更を許可する前に1.5msの間デバウンスされます。

STATUS ピンは、SEL1~3ピンで選択されるステートによって機能が決定されるオープンドレイン出力です。このピンは、ハイまたはローを出力するか、9ms 周期で発振します。

## アプリケーション情報

#### ケーブル電圧降下補償

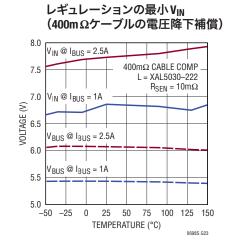

LT8698Sは、ケーブル電圧降下補償に必要な回路を内蔵しています。ケーブル電圧降下補償により、このレギュレータは、ケーブル抵抗が大きい場合でも、USBのVBUSレール上で5Vのレギュレーションを維持できます。LT8698Sは、負荷の増加に応じて、レギュレータ側の出力電圧(VBUS/ISN)を5Vを超えて上昇させることにより、VBUSの5Vへの安定化を維持します。この補償方式では、レギュレータと負荷の間に追加のケルビン検出線対は必要ありませんが、LT8698Sはケーブル抵抗RCABLEの値を検出しないため、システム設計者がケーブル抵抗の値を知っている必要があります。

式1の比を使用して、ケーブル電圧降下補償を設定します。

$$R_{CBL} = 46 \cdot \left( \frac{R_{SEN} \cdot R_{CDC}}{R_{CABLF}} \right)$$

(1)

ここで、 $R_{CDC}$ はレギュレータの出力とUSB5Vピンの間に接続される抵抗、 $R_{CBL}$ はRCBLピンとGNDの間に接続される抵抗、 $R_{SEN}$ はレギュレータ出力と負荷の間で直列に、OUT/ISPピンとBUS/ISNピンの間に接続される検出抵抗、 $R_{CABLE}$ はケーブルの抵抗です。LT8698Sが正常に動作するには、 $R_{SEN}$ の値を、2.4Aアプリケーションでは $10m\Omega$ 、3Aアプリケーションでは $8m\Omega$ にする必要があります。

$R_{CDC}$ を通ってUSB5Vピンに流れ込む電流は、 $R_{CBL}$ を流れる電流と同じです。これらの2つの抵抗の比は、上記の式に従って選択する必要があります。これらの抵抗の絶対値は、最大負荷電流でこの電流が30 $\mu$ A~1200 $\mu$ Aの範囲に保たれるように選択してください。この制約により、 $R_{CBL}$ と $R_{CDC}$ の値は1k~40.2kの範囲内になります。 $I_{USB5V}$ が小さすぎる場合、 $R_{CBL}$ ピンに容量性負荷が加わると、レギュレータの負荷ステップ・トランジェント性能が低下します。 $I_{USB5V}$ が大きすぎる場合、 $R_{CBL}$ ピンが電流制限に達し、ケーブル電圧降下補償は機能しなくなります。

R<sub>SEN</sub>の下流にあるリモート負荷からグラウンドまでの容量によって、ケーブル電圧降下補償に起因する、LT8698Sデバイスにおける帰還ループ系の4象限平面の左側にゼロが現れます。このゼロは、通常はC<sub>BUS</sub>と、USBソケットに接続されたポータブル・デバイスの入力容量によって形成されます。C<sub>CDC</sub>は、高周波数でのケーブル電圧降下補償ゲインを減らします。LT8698Sの出力の安定性を維持するには、4.7nFのC<sub>CDC</sub>コンデンサを2kのR<sub>CDC</sub>の両端に接続する必要があります。R<sub>CDC</sub>を変更する場合は、C<sub>CDC</sub>も変更して、RC時定数をほぼ同じ10µsに保つ必要があります。LT8698Sの出力コンデンサC<sub>OUT</sub>およびC<sub>BUS</sub>の容量と比較してリモート負荷の容量の方が大きい場合は、安定性を維持するために、ケーブル電圧降下補償の大きさに応じてR<sub>CDC</sub>・C<sub>CDC</sub>の時定数を大きくしなければならない場合があります。出力の安定性は、必ず最終アプリケーション回路で検証してください。

ケーブル電圧降下補償を使用しない場合は、USB5Vを VBUS出力に短絡させます。

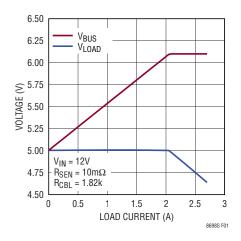

LT8698S は、BUS/ISNピンの電圧を最大 6.05V までに制限することにより、 $V_{BUS}$ の最大電圧を制限します。 $I_{BUS}$  が最大のときにケーブル電圧降下を1.05V より大きく補償するようにケーブル電圧降下補償量を設定すると、この制限により、 $V_{BUS/ISN}$  が6.05V より高い値に上昇するのを防ぐことができ、負荷直近の $V_{BUS}$  は5V 以下に低下します。式2に、LT8698S の出力電圧の計算方法を示します。

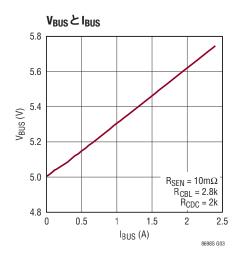

$$V_{OUT} = 5V + \frac{46 \cdot I_{BUS} \cdot R_{SEN} \cdot R_{CDC}}{R_{CBL}}$$

(2)

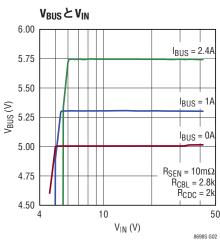

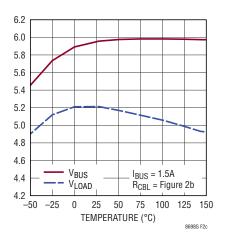

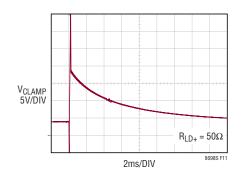

ケーブル電圧降下補償がどのように作用するかについては、図1のV<sub>BUS/ISN</sub>とV<sub>BUS</sub>の負荷曲線を参照してください。

図1. ケーブル電圧降下補償の負荷曲線の例

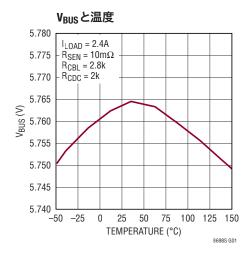

#### 広い温度範囲にわたるケーブル電圧降下補償

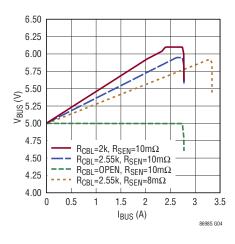

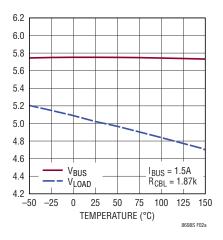

多くのアプリケーションでは、温度変動のないケーブル電圧降下補償を使用できます(図2a、b、cを参照)。ただし、ケーブル電圧降下補償の温度変動をケーブル抵抗の温度変動と一致させると、広い動作温度範囲で全体的な出力電圧精度の向上につながります。例えば、配線抵抗が $0.49\Omega$ で最大出力電流が1.5Aのアプリケーションでは、配線抵抗を完全に補償するために、ケーブル電圧降下補償によって最大負荷時には出力に $25^\circ$ Cで0.735Vが加わります。この例の線材

(a)  $3m \cap AWG 24$  ツイスト・ペア・ケーブル  $(490m \Omega) \cap$ ケーブル電圧降下補償 (温度補償なし)

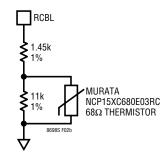

(b) 銅線の温度係数とのマッチング用の R<sub>CBL</sub>抵抗回路網

(c) 3mのAWG 24ツイスト・ペア・ケーブル(490Ω)の ケーブル電圧降下補償(NTC R<sub>CBL</sub>を使用した温度補償あり)

図2. ケーブル電圧降下補償のアプリケーション

が銅の場合、銅抵抗の温度係数は約4000ppm/°Cであるため、出力電圧誤差は125°Cで294mV、-40°Cで191mVになります。この挙動を図2aに示します。

ゲージごとの銅線抵抗については、表1を参照してください。

表 1. 銅線抵抗とワイヤ・ゲージ

| AWG | RESISTANCE OF CU WIRE AT 20°C (m $\Omega$ /m) |

|-----|-----------------------------------------------|

| 15  | 10.4                                          |

| 16  | 13.2                                          |

| 17  | 16.6                                          |

| 18  | 21.0                                          |

| 19  | 26.4                                          |

| 20  | 33.3                                          |

| 21  | 42.0                                          |

| 22  | 53.0                                          |

| 23  | 66.8                                          |

| 24  | 84.2                                          |

| 25  | 106                                           |

| 26  | 134                                           |

| 27  | 169                                           |

| 28  | 213                                           |

| 29  | 268                                           |

| 30  | 339                                           |

| 31  | 427                                           |

| 32  | 538                                           |

| 33  | 679                                           |

| 34  | 856                                           |

| 35  | 1080                                          |

| 36  | 1360                                          |

| 37  | 1720                                          |

| 38  | 2160                                          |

| 39  | 2730                                          |

| 40  | 3440                                          |

ケーブル電圧降下補償は、 $R_{CBL}$ 抵抗の一部として負の温度係数(NTC)抵抗を追加することにより、温度に対して正に変化するように設定できます。この回路の考え方は、NTC抵抗がケーブルと同じ温度であることを前提としています。 $-40^{\circ}\mathrm{C} \sim 150^{\circ}\mathrm{C}$ の広い温度範囲で銅線抵抗の変化に一致する $R_{CBL}$ の抵抗回路網の例を図2bに示します。負の温度変化を示す抵抗を $R_{CBL}$ に使用して、数種類の温度で得られたケーブル電圧降下補償出力を図2cに示します。

NTC抵抗は、温度に対して完全に線形の伝達関数特性を示しません。ここで、部品の値が標準的な場合、最も厳しい場合の誤差はケーブル電圧降下補償出力の20%未満、つまり全出力電圧精度の4%未満です。R<sub>CBL</sub>抵抗の値を、より狭い温度範囲用に最適化すれば、温度に対する出力電圧の精度を向上させることができます。

#### 負荷ステップ過渡応答に対する ケーブル・インダクタンスの影響

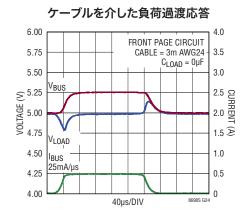

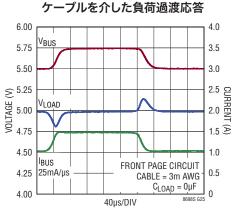

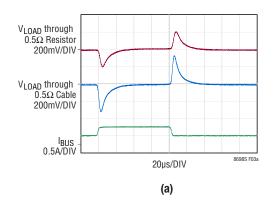

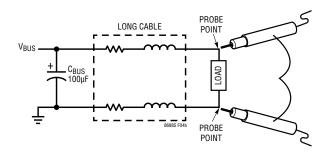

ケーブル配線が長い場合、ケーブルのインダクタンスにより、高速負荷ステップに対する2線式検出レギュレータのピークtoピーク過渡応答性能が制限されます(図3を参照)。LT8698Sなどの2線式検出レギュレータは、負荷直近ではなくレギュレータのローカル出力で出力電圧を検出するため、ケーブルの抵抗を補償した場合でも、ケーブルのインダクタンスによる負荷ステップ応答の性能低下が生じます。ローカル・レギュレータの出力コンデンサとリモート負荷の入力コンデンサは、コンデンサ間の誘導性ケーブル配線によってLCタンク回路を形成します。高速負荷ステップが長いケーブル配線を通過すると、大きなピークtoピーク過渡応答を示し、LCタンク回路の共振周波数でリンギングを示します。このリンギングはLCタンク回路の特性であり、レギュレータの不安定性を示すものではありません。

125mA/us、0.5Aの負荷ステップに対するLT8698Sの負荷ス テップ過渡応答を図3aに示します。抵抗性インピーダンス のみの場合と、抵抗性 + 誘導性インピーダンスの場合の2 種類のケーブル・インピーダンスを比較します。まず、0.5Ωの 表面実装抵抗をLT8698Sの出力と負荷ステップ発生器の 間に接続します。この抵抗は純粋な抵抗性「ケーブル」の代 わりになります。次に、長さが3メートル、全抵抗値が0.5Ω、 インダクタンスが約0.8μHのAWG24ツイスト・ペア・ケーブ ルをLT8698Sの出力と負荷ステップ発生器の間に接続しま す。これら2つの回路の抵抗が同じ場合でも、インダクタンス があるため、ケーブルでのトランジェント負荷ステップ応答 の方が劣ります。ケーブルのインダクタンスによってLT8698S の負荷過渡応答性能がどの程度低下するかは、ケーブルの インダクタンスと負荷ステップの速度によって異なります。長 いケーブルは短いケーブルよりインダクタンスが大きくなりま す。電源導線と戻り導線の間隔が狭いケーブルは、間隔が 広い導線と比較して、単位長さあたりのインダクタンスが小 さくなります。負荷ステップの速度が速いと、負荷ステップ応 答に対するインダクタンスの影響は大きくなります。

図3. 負荷ステップ過渡応答に対するケーブル・ インダクタンスの影響

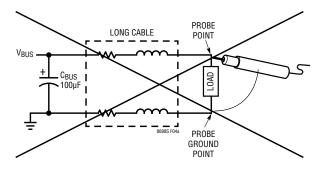

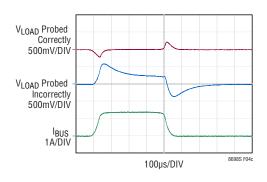

#### リモート出力の適切なプロービング

LT8698Sのリモート出力にプローブを当てるときは、正しい結果が得られるように注意してください。ケーブル電圧降下補償を使用する場合、ケーブルの抵抗と大きな負荷電流が原因で、ローカル・レギュレータの出力電圧とケーブルの端のリモート出力電圧は一致しません。抵抗があって出力と同

じ電流が流れるグラウンド戻り線についても同じことが言えます。LT8698Sのローカル・グラウンドと負荷直近のリモート・グラウンドは通電ケーブルによって分離されているため、これらの2つの場所ではグラウンド基準ポイントが異なります。

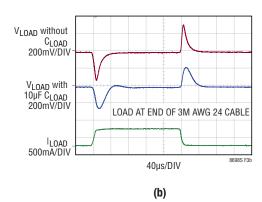

図4bに示すように、ケーブルの端の位置でリモート出力の両 端に差動プローブを当てて、そのポイントで出力電圧を測定 します。図4aに示すように、LT8698Sのローカル・グラウンド と負荷直近のリモート・グラウンドの両方に、オシロスコープ のプローブのグラウンド・リード線を同時につながないでく ださい。これを行うと、プローブのグラウンド線に大きな電流 が流れ、異常で不正確な測定結果が得られます。この異常 な挙動を図4cに示します。3メートルのAWG 24ツイスト・ペ ア・ケーブルを通して、1.3Aの負荷ステップをLT8698Sの出 力に加えています。1本の曲線では、差動プローブを負荷直 近の両端に当てることにより、出力電圧の結果が正しく測定 されています。もう1本の曲線では、オシロスコープのグラウ ンド・リード線がリモート・グラウンドにつながれています。こ の誤った方法でのプロービングは、グラウンドの戻り抵抗が 低いことによるDC誤差と、オーバーシュートの増大を示す AC誤差の両方の原因になります。LT8698Sのリモート出力 の測定には、オシロスコープ、実験台、入力電源のグラウンド 線を追加しないでください。

#### 出力オーバーシュートの低減

ケーブル電圧降下補償を使用すると、その結果として、LT8698SのBUS/ISNピンのローカル出力電圧は、負荷直近のリモート出力より高い電圧に調整されます。これら2つの出力は数百mΩのケーブル抵抗によって分離されることがあります。このため、負荷電流が2Aの場合、VBUS/ISNは負荷直近の公称5Vの出力より最大1.05V高くなる可能性があります。LT8698Sの出力に接続されるすべての部品が、この電圧上昇に耐えられることを確認してください。

LT8698Sは、ケーブル電圧降下補償機能による出力電圧上昇の影響を軽減する目的で設計された各種の機能を備えています。まず、LT8698Sのエラーアンプは、USB5Vピンの電圧を一次出力の5Vに安定化するのに加えて、BUS/ISNピンの電圧を6.05Vより低い電圧に安定化します。BUS/ISBの最大電圧が6.05Vに制限されることで、LT8698Sの出力に接続されるポータブル・デバイスなどの部品は過電圧状態から保護されますが、ケーブル電圧降下補償の大きさは1.05Vまでに制限されます。

(a) リモート出力の誤ったプロービング

(b) リモート出力の適切なプロービング

(c) リモート出力の誤ったプロービングの影響

図4. リモート出力の適切なプロービング

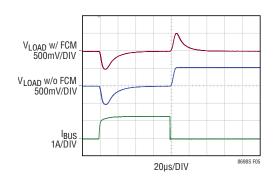

更に、LT8698Sは、強制連続モード(FCM)時に出力から電流をシンクできます。この機能により、重負荷から軽負荷への負荷ステップに対するステップ応答が改善されます。ケーブル電圧降下補償機能は、重負荷時にケーブル抵抗の両端に生じる電圧降下を補償するために、出力に電圧を追加します。ほとんどのDC/DCコンバータは電流をソースすることしかできないため、電流が大きな値からゼロ付近まで減少する負荷ステップでは、出力電圧は高いままになり、レギュレーションされません。LT8698Sは、USB5Vの電圧が

高すぎる場合、レギュレータが強制連続モードで出力から 電流をシンクできるようにすることにより、この問題を解決し ます。最初のページのアプリケーション回路で3mのケーブ ルを介して1.3Aの高速負荷ステップに応答する場合の強制 連続モードとパルス・スキップ・モードの出力電圧を図5に 示します。パルス・スキップ・モードでは、電流が高い値から 0に低下したときの負荷ステップ応答は極めて低速になり、 OUT/ISP、BUS/ISN、およびUSB5Vピンのバイアス電流に よって制限されます。しかし、強制連続モードをイネーブル にすると、出力は迅速にレギュレーション状態に戻ります。

図5. 強制連続モードを使用した場合と使用しない場合の負荷ステップ応答

最後に、LT8698Sの正のスイッチ・ピーク電流と負のバレー電流の制限値は、2.65Aの正の出力電流の制限値を超えています。このように電流範囲が広いため、LT8698Sは、過渡負荷ステップ中のケーブル電圧降下補償のために出力コンデンサを迅速に充電できます。

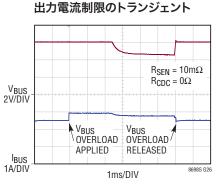

#### 出力電流制限

LT8698Sは、出力電圧のレギュレーションに加えて、電流レギュレーション・ループによって平均出力電流を制限します。出力電流レギュレーションは、USBケーブルの障害やUSBソケットに接続されたデバイスの障害が発生した場合に、消費電力を制限します。LT8698Sは、OUT/ISPピンとBUS/ISNピンを使用して、外付け検出抵抗R<sub>SEN</sub>の両端の電圧降下を測定します。この抵抗は、出力コンデンサC<sub>OUT</sub>の負荷側に、負荷に対して直列に接続する必要があります。LT8698Sの制御ループは、OUT/ISPピンとBUS/ISNピン間の平均電圧がレギュレーション点を超えないように、スイッチの電流制限値をサイクルごとに調整します。電流レギュレーションがアクティブのときに負荷電流が出力電流制限値を超えると、出力電圧はレギュレーション点より低い電圧に低下します。

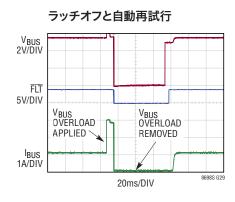

LT8698Sは、出力電流レギュレーション・ループのラッチオフおよび自動再試行機能を備えています。出力電圧が少なくと

も4.2msにわたってレギュレーション点より7%低くなると、LT8698Sは59msの間スイッチングを停止します。59msの経過後、LT8698Sはスイッチングを開始します。スイッチングの開始後4.2ms以内に出力が公称レギュレーション点に戻れば、通常動作を再開します。出力が4.2ms以内に公称レギュレーション点まで戻らず、レギュレーション点より7%以上低いままの場合、LT8698Sは再び59msの間スイッチングを停止し、このシーケンスが繰り返されます。このラッチオフおよび自動再試行機能により、障害状態での消費電力は、この機能を使用しない場合のデューティ・サイクルの約7%に低減されます。

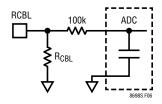

#### 出力電流モニタとしてのRCBLの使用

RCBLピンの主要な機能は、ケーブル電圧降下補償のセクションで説明したように、ケーブル電圧降下補償機能を設定することです。RCBLピンの第2の機能は、出力負荷電流に比例した出力電圧を発生することです。このため、RCBLピンは出力負荷モニタとして使用できます。RCBLピンの電圧とUSBの負荷電流の関係は、式3に従います。

$$V_{RCBL} = I_{LOAD} \bullet R_{SEN} \bullet 46 \tag{3}$$

この式は、LT8698Sがイネーブルのときに有効です。

RCBLピンの電流はケーブル電圧降下補償制御ループの一部であるため、RCBLピンに過剰な容量性負荷が加わると、負荷ステップが生じたときにUSB出力電圧にオーバーシュートが発生する原因になります。RCBLピンの容量性負荷を100pFより小さい値に抑えるか、または図6に示すように、RCBLピンとその駆動先の入力の間に100kΩを直列に接続して負荷の容量を分離してください。

図6. 出力電流モニタとしてのRCBLピンの使用

#### スイッチング周波数の設定

LT8698Sは固定周波数のPWMアーキテクチャを採用しており、RTピンとグラウンドの間に接続した1個の抵抗を使用して、300kHz~3MHzの範囲でスイッチングするように設定で

きます。目的のスイッチング周波数を得るのに最適な $R_T$ の値を表2に示します。

表2. スイッチング周波数とRTの値

| Switching Frequency (MHz) | $R_{T}(k\Omega)$ |

|---------------------------|------------------|

| 3                         | 5.76             |

| 2.8                       | 6.19             |

| 2.6                       | 6.81             |

| 2.4                       | 7.5              |

| 2.2                       | 8.25             |

| 2                         | 9.09             |

| 1.8                       | 10.2             |

| 1.6                       | 11.5             |

| 1.5                       | 12.4             |

| 1.4                       | 13.3             |

| 1.3                       | 14.7             |

| 1.2                       | 15.8             |

| 1.1                       | 17.4             |

| 1                         | 19.1             |

| 0.9                       | 21.5             |

| 0.8                       | 24.3             |

| 0.7                       | 28               |

| 0.6                       | 32.4             |

| 0.5                       | 39.2             |

| 0.4                       | 49.9             |

| 0.3                       | 66.5             |

目的のスイッチング周波数を得るのに必要な $R_T$ の値は、式4を使用して計算することもできます。ここで、fの単位はMHzです。

$$R_T = \frac{20.25}{f} - 1.013k \tag{4}$$

#### 動作周波数の選択と交換条件

動作周波数の選択は、効率、部品サイズ、入力電圧範囲の間の兼ね合いによって決まります。高周波数動作の利点は、小さな値のインダクタとコンデンサを使用できることです。欠点は、効率が低くなることと入力電圧範囲が狭くなることです。

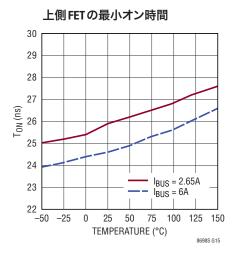

与えられたアプリケーションでの、最小オン・タイムによる制限が掛かる直前までの最大スイッチング周波数(f<sub>SW(MAX)</sub>)は、式5を用いて計算できます。

$$f_{SW(MAX)} = \frac{V_{OUT/ISP}}{t_{ON(MIN)} \bullet V_{IN(MAX)}} \bullet 1000$$

(5)

ここで、 $V_{IN(MAX)}$ はサイクルをスキップしない場合の最大入力電圧、 $V_{OUT/ISP}$ はOUT/ISPの出力電圧、 $t_{ON(MIN)}$ は上側スイッチの最小オン時間(約30ns)です。この式は、高い $V_{IN}/V_{OUT/ISP}$ 比に対応するには、スイッチング周波数を下げる必要があることを示しています。

トランジェント動作では、 $R_T$ の値に関係なく、 $V_{IN}$ が42Vの絶対最大定格まで上昇する可能性がありますが、LT8698Sは、必要に応じてスイッチング周波数を下げることにより、インダクタ電流の制御を維持して安全な動作を確保します。

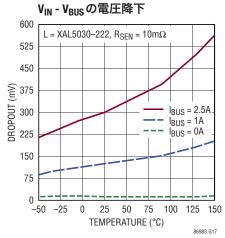

LT8698S は99%を超える最大デューティ・サイクルでの動作が可能です。 $V_{IN}$ と $V_{BUS/ISN}$ 間のドロップアウト電圧は、上側スイッチの $R_{DS(ON)}$ によって制限されます。この領域で動作すると、スイッチング周波数が低下します。

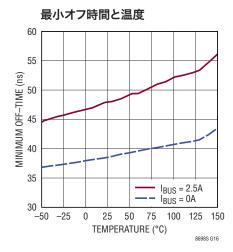

与えられたアプリケーションの制限付き最小オフ時間の前の最大スイッチング周波数  $(f_{SW(MAX)})$  は、式6を使用して計算できます。

$$f_{SW(MAX)} = \left(\frac{1}{t_{OFF(MIN)}} - \frac{V_{OUT/ISP}}{t_{OFF(MIN)} \bullet V_{IN(MIN)}}\right) \bullet 1000 \tag{6}$$

ここで、 $V_{IN(MIN)}$ はサイクルをスキップしない場合の最小入力電圧、 $V_{OUT/ISP}$ はOUT/ISPの出力電圧、 $t_{OFF(MIN)}$ は40nsの最小スイッチ・オフ時間です。スイッチング周波数を高くするほど、最大周波数動作での最小入力電圧が高くなることに注意してください。

#### インダクタの選択と最大出力電流

LT8698S は、アプリケーションの出力負荷条件に基づいてインダクタを選択できるため、ソリューションのサイズを最小限に抑えることができます。LT8698S は、高速ピーク電流モード・アーキテクチャを採用しているため、過負荷状態または短絡状態の間、インダクタが飽和した状態での動作に支障なく耐えられます。

LT8698Sのインダクタは、目的のスイッチング周波数に基づいて、表3に従って選択してください。

表3にインダクタの公称値を示します。インダクタは、通常は 電流と温度に対してディレーティングされ、許容誤差の仕様 があります。この表では、最も厳しい条件と許容誤差の場合 でも、アプリケーションのインダクタンスが公称値の60%未 満にならないことを前提としています。 安定した動作のために、表3に示した値以上のインダクタを 使用してください。

表3. インダクタの値とスイッチング周波数

| SWITCHING FREQUENCY (MHz) | MINIMUM NOMINAL INDUCTOR VALUE (μH) |

|---------------------------|-------------------------------------|

| 2.4 – 3.0                 | 1.5                                 |

| 1.9 – 2.4                 | 2.2                                 |

| 1.3 – 1.9                 | 3.3                                 |

| 0.89 – 1.3                | 4.7                                 |

| 0.61 - 0.89               | 6.8                                 |

| 0.51 - 0.61               | 8.2                                 |

| 0.30 - 0.51               | 10                                  |

表4に、LT8698S用に推奨するインダクタ・メーカーと関連するインダクタ製品シリーズ名を示します。

表4. インダクタのメーカー

| VENDOR    | SERIES                 | WEBSITE           |

|-----------|------------------------|-------------------|

| TDK       | SLF, VLC, VLF          | www.tdk.com       |

| Sumida    | CRH, CDR, CDMC         | www.sumida.com    |

| Coilcraft | XAL, XFL, MSS          | www.coilcraft.com |

| NIC       | NPIM, NPIS             | www.niccomp.com   |

| Würth     | TPC, SPC, PD, PDF, PD3 | www.we-online.com |

#### 入力コンデンサ

適切な温度定格および電圧定格のセラミック・コンデンサを $V_{IN}$ およびPGNDピンのできるだけ近くに配置して、LT8698S回路の入力をバイパスします。Y5V型は、温度や印加される電圧が変化すると性能が低下するので使用しないでください。LT8698Sをバイパスするには $2.2\mu$ F~ $4.7\mu$ Fのセラミック・コンデンサが適しており、リップル電流を容易に処理できます。低いスイッチング周波数を使用すると、大きな入力容量が必要になることに注意してください。入力ソース・インピーダンスが高かったり、長い配線やケーブルによる大きなインダクタンスが存在する場合、追加のバルク容量が必要になることがあります。これには性能の高くない電解コンデンサを使用することができます。

降圧レギュレータには、立上がりと立下がりが非常に高速なパルス電流が入力電源から流れます。その結果として生じるLT8698Sでの電圧リップルを減らし、周波数が非常に高いこのスイッチング電流を狭い範囲のループに押し込め

Rev.0

22

てEMIを最小限に抑えるためには、入力コンデンサが必要です。セラミック入力コンデンサに関する2つ目の注意点は、LT8698Sの最大入力電圧定格に関することです。セラミック入力コンデンサは、パターンやケーブルのインダクタンスと結合して、質の良い(減衰の小さな)タンク回路を形成します。LT8698Sの回路を通電中の電源に差し込むと、入力電圧に公称値の2倍のリンギングが生じて、LT8698Sの電圧定格を超える恐れがあります。この状況は簡単に回避できます(アナログ・デバイセズのアプリケーション・ノート88を参照)。

#### 出力コンデンサと出力リップル

OUT/ISPピンとグラウンドの間に接続される出力コンデンサ Coutには、2つの基本的な機能があります。出力コンデンサは、インダクタと共に、LT8698Sが発生する方形波をフィルタに通してDC出力を生成します。この機能では出力コンデンサが出力リップルを決定するので、スイッチング周波数でのインピーダンスが低いことが重要です。2番目の機能は、トランジェント負荷を満たしてLT8698Sの制御ループを安定化するためにエネルギーを蓄えることです。セラミック・コンデンサは、等価直列抵抗(ESR)が非常に小さいので最良のリップル性能が得られます。初期値に適した値については、標準的応用例のセクションを参照してください。

固定出力電圧のスイッチング・レギュレータでは、大きい値の出力コンデンサを使用すると、通常はトランジェント性能が向上します。ただし、LT8698Sのケーブル電圧降下補償機能により、レギュレータ側の出力電圧は負荷ステップに応答して変化します。トランジェント負荷ステップが生じると、LT8698SはCOUTを充電しなければならないため、COUTが大きいと、過渡応答が低下することがあります。トランジェント応答を改善できるのは、USBソケットの近くでケーブルの端に接続されるリモート容量だけです。LT8698Sのループの安定性と出力電圧リップルの条件を満たすのに必要な最小ローカル出力容量が、COUTの最善の選択肢になります。コンデンサの推奨値については、このデータシートの標準的応用例のセクションを参照してください。

USB 2.0仕様は、ハブの $V_{BUS}$ とグラウンドの間に最小120 $\mu$ F の低 ESR コンデンサを接続することを要求しています。 ダウンストリーム・デバイスの固定 $V_{BUS}$ 容量は最大10 $\mu$ Fに制限されるため、この最小120 $\mu$ Fの $V_{BUS}$ 容量により、1つのダウンストリーム・デバイスの活線挿入によって $V_{BUS}$ のグリッチが発生し、もう1つの接続デバイスの動作を中断するのを防ぐことができます。LT8698Sがハブの $V_{BUS}$ に電力供給している場合、OUT/ISPとグラウンドの間に追加の $V_{OUT}$ を接続す

ることにより、この条件を満たすことができます。OUT/ISPとグラウンドの間には、常に最小22μFの容量が接続されている必要があります。

BUS/ISNノードに接続される容量は、OUT/ISPノードに接続される容量より小さくなるようにします。グラウンドに対するBUS/ISNノードの容量が大きいと、レギュレータのループ位相余裕が低下し、ケーブル電圧低下補償の過渡応答が低速になります。22µFよりはるかに大きな出力容量が必要な場合は、BUS/ISNノードではなく、OUT/ISPノードにコンデンサを接続してください。

コンデンサを選択する際は、電圧バイアスと温度の該当する 動作条件での実効容量に特に注意してください。物理的に 大きなコンデンサ、または電圧定格が大きいコンデンサが必 要になる場合があります。

#### セラミック・コンデンサ

セラミック・コンデンサは小さく堅牢で、ESRが非常に小さいコンデンサです。ただし、セラミック・コンデンサには圧電特性があるため、LT8698Sに使用すると問題を生じることがあります。パルス・スキップ・モードの動作では、LT8698Sのスイッチング周波数は負荷電流に依存します。非常に軽い負荷では、LT8698Sはセラミック・コンデンサを可聴周波数で励起し、可聴ノイズを発生することがあります。LT8698Sはパルス・スキップ動作では低い電流制限値で動作するので、通常は非常に静かでノイズが気になることはありません。これが許容できない場合は、高性能のタンタル・コンデンサまたは電解コンデンサを出力に使用してください。低ノイズのセラミック・コンデンサも使用できます。

表5. セラミック・コンデンサのメーカー

| VENDOR      | WEBSITE         |

|-------------|-----------------|

| Taiyo Yuden | www.ty-top.com  |

| AVX         | www.avxcorp.com |

| Murata      | www.murata.com  |

| TDK         | www.tdk.com     |

#### EN/UVピン

LT8698S は、EN/UVピンの電圧が0.25V未満のときシャットダウン状態になり、EN/UVピンがハイのときアクティブになります。EN/UVコンパレータの下降時閾値は1.31Vで、150mVのヒステリシスがあります。シャットダウン機能を使用しない場合は、EN/UVピンを $V_{IN}$ に接続できます。シャットダウン制御が必要な場合は、ピンを目的のロジック・レベル

に駆動できます。LT8698SのEN/UVピンには、約1M $\Omega$ の抵抗に対して直列に配置される内部5.5V クランプがあります。

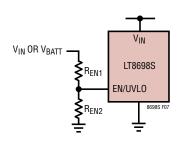

$V_{\rm IN}$ とEN/UVピンの間に抵抗分圧器を追加すると、LT8698Sは、 $V_{\rm IN}$ が目的の電圧より高くなった場合にのみ動作するように設定されます。通常、この閾値( $V_{\rm IN(EN)}$ )は、入力電源が電流制限されているか、または入力電源のソース抵抗が比較的高い状況で使用されます。この閾値は、式7を満たすように $R_{\rm EN1}$ と $R_{\rm EN2}$ の値を設定することにより調整できます。

$$V_{IN(EN)} = \left(\frac{R_{EN1}}{R_{EN2}} - 1\right) \cdot 1.46V \tag{7}$$

図7.UVL0分圧器

この場合は、 $V_{IN}$ が $V_{IN(EN)}$ を超えるまでLT8698Sはオフのままになります。コンパレータのヒステリシスのため、入力が $V_{IN(EN)}$ よりわずかに低くなるまでスイッチングは停止しません。

#### INTVccレギュレータ

内部低ドロップアウト(LDO)レギュレータは、 $V_{IN}$ を基にして、ドライバと内部バイアス回路に電力を供給する4V電源を生成します。 $INTV_{CC}$ のLDOは、LT8698Sの回路に十分な電流を供給できます。COLDOは、 $LO\mu$ Fのセラミック・コンデンサを使用してグラウンドにバイパスする必要があります。パワーMOSFETのゲート・ドライバが必要とする大量の過渡電流を供給するには、十分なバイパスが必要です。

入力電圧が高く、スイッチング周波数が高いアプリケーションでは、LDOの消費電力が大きいため、ダイ温度が上昇します。INTV<sub>CC</sub>には、STATUSおよびFLTオープンドレイン出力ピンに抵抗プルアップを提供するなどの目的で、最大1mAの負荷をかけることができます。

信頼性の高い動作を確保するには、1mAを超える電流で INTV<sub>CC</sub> LDOに負荷をかけないでください。

#### ソフトスタート

LT8698Sは内部ソフトスタート機能を内蔵しています。出力電圧が上昇するには1.1msかかります。ソフトスタート機能の目的は、起動中に出力コンデンサを充電するときのレギュレータへの突入電流を制限することです。V<sub>IN</sub>の低電圧ロックアウト、INTV<sub>CC</sub>の低電圧および過電圧ロックアウト、EN/UVのロー状態、サーマル・シャットダウン、出力電流制限のラッチオフが発生するか、スイッチャをオフにしてSEL1~3ピンでステートを選択すると、ソフトスタート・ランプはリセットされます。

#### FLTピン

LT8689Sの出力電圧がレギュレーション点の±7%の範囲内 (つまり、USB5Vピンの電圧が4.64V~5.34V (標準)の範囲内)にある場合、出力電圧は障害状態ではないとみなされ、オープンドレインの FLT ピンは高インピーダンスになり、通常は外付け抵抗によってハイになります。電圧がこの範囲を外れた場合、内部のプルダウン・デバイスにより、FLTピンはローになります。グリッチの発生を防ぐため、上側と下側の閾値の両方に3%のヒステリシスが含まれています。また、出力は4.2msの間デバウンスされます。

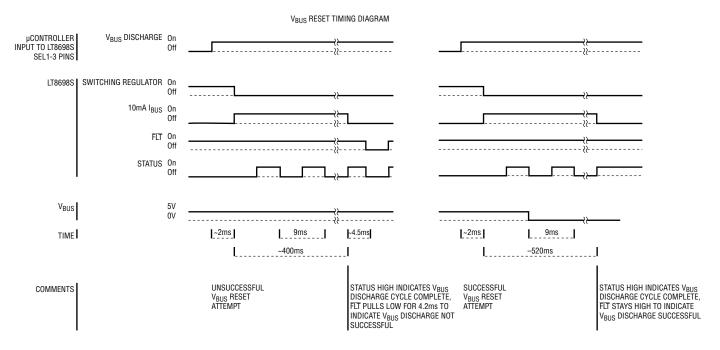

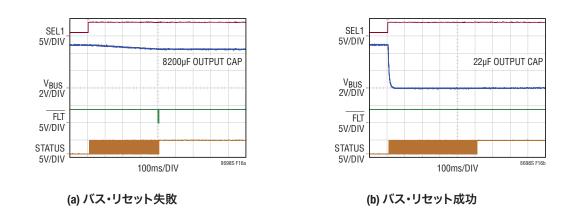

FLTピンは、いくつかの障害状態(V<sub>IN</sub>の低電圧ロックアウト、INTV<sub>CC</sub>の低電圧および過電圧ロックアウト、EN/UVのロー状態、およびサーマル・シャットダウン)の間も自動的にローになります。また、ステート・マシンのバス・リセット・シーケンスの終わりにV<sub>BUS</sub>が0.5Vより高い電圧に保たれている場合、FLTピンは4.2msの間ローになります。

#### 同期

パルス・スキップ・モードの動作を選択するには、SYNC/MODEピンを0.3Vより低い電圧に接続します。強制連続モード(FCM)を選択するには、SYNC/MODEピンをフロート状態にします。FCMとスペクトラム拡散変調(SSM)の組み合わせを選択するには、SYNC/MODEピンを3.7Vより高い電圧に接続します(SYNC/MODEはINTV<sub>CC</sub>に接続できます)。LT8698Sの発振器を外部周波数に同期させるには、デューティ・サイクルが20%~80%の方形波をSYNC/MODEピンに接続します。方形波の振幅には、0.4Vより低い谷と1.5Vより高い山が必要です。外部クロックと同期する場合、LT8698Sは強制連続モードを使用します。

LT8698Sは300kHz~3MHzの範囲にわたって同期することができます。 $R_T$ 抵抗は、LT8698Sのスイッチング周波数を最

低同期入力以下に設定するように選択します。例えば、同期信号が500kHz以上になる場合は、スイッチング周波数が公称500kHzになるように $R_T$ を選択します。

同期信号にスペクトラム拡散を組み込むと、EMIが減少する ことがあります。

#### 強制連続モード

強制連続モード(FCM)を作動させるには、SYNC/MODEピンをフロート状態にするか、1.1Vより高いDC電圧をSYNC/MODEピンに印加するか、外部クロックをSYNC/MODEピンに入力します。

強制連続モードの間、不連続モードの動作はディスエーブルされ、インダクタ電流を負の方向に流すことができるため、レギュレータは負の出力電流が2.3Aになるまで設定周波数でスイッチングできます。このモードには、負荷の全範囲にわたって設定スイッチング周波数を維持できる利点があるため、スイッチの高調波とEMIが安定して予測可能になります。また、このデバイスは出力から電流をシンクできるため、ケーブル電圧降下補償の使用時に負荷解放の過渡応答が改善されます。強制連続モードの欠点は、パルス・スキップ・モードの動作と比較して軽負荷時の効率が低くなることです。

強制連続モードを選択した場合、LT8698Sが最大スイッチング周波数を維持できなくなる動作条件がいくつかあります。例えば、非常に低い入力電圧で発生するドロップアウト状態では、強制連続モードはディスエーブルになります。ドロップアウト状態で動作する場合、LT8698Sは時間をスキップしてスイッチング周波数を低減し、レギュレーション性能を向上させます。

#### スペクトラム拡散変調

スペクトラム拡散変調(SSM)を作動させるには、3.7Vより高いDC電圧をSYNCピンに印加します。そのためには、SYNC/MODEピンをINTV<sub>CC</sub>ピンに接続します。スペクトラム拡散変調は、RTで設定された値と、その値より約20%高い値との間でスイッチング周波数を変調することにより、EMI放射を低減します。例えば、LT8698Sを2MHzに設定してスペクトラム拡散変調機能を有効にした場合、スイッチング周波数は2MHz~2.4MHzの範囲で変化します。

#### 出力短絡保護と逆入力保護

LT8698Sは、出力短絡状態に対する耐性を備えています。出力がグラウンドに短絡した状態で動作しているときは、下側スイッチの電流がモニタされ、インダクタ電流が安全なレベルを超えた場合はインダクタ電流が安全なレベルに減少する時点まで上側スイッチのスイッチングを遅らせます。

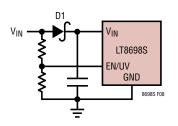

自動車のバッテリなど、出力が高電圧に短絡した状態で動作している場合、システムを流れる電流は、LT8698Sの入力電源の $V_{IN}$ の状態に依存します。イグニッション・スイッチがオフの場合など、 $V_{IN}$ が遮断されている場合、LT8698Sには、EN/UVがハイの場合は出力から約2.5mAの静止電流が流れ、EN/UVがローの場合は電流は流れません。 $V_{IN}$ が接地されるか、逆向きに接続された場合、内部上側パワーFETのボディ・ダイオードは、電流が出力(SW)から入力( $V_{IN}$ )へ制御されずに流れることを許可します。このため、LT8698Sに損傷を与える可能性があります。制御されない逆電流の発生を防ぐ方法については、図8を参照してください。

図8. 逆入力電圧保護

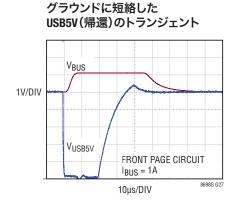

#### 出力ケーブル障害

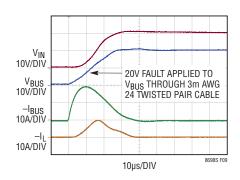

LT8698S は、 $V_{BUS}$ 出力上のGNDまたは最大20Vまでのケーブル障害に耐えられます。この出力がハイに保たれる場合、上記の逆向き入力保護回路により、SWから $V_{IN}$ への大きすぎる電流が上側スイッチのボディ・ダイオードに流れるのを防ぐ必要があります。 $20V \circ V_{BUS}$  は障害状態であり、LT8698S によって電力供給される USB ソケットに接続されたポータブル・デバイスを損傷する可能性があります。LT8698S はこの状態に耐えられますが、ポータブル・デバイスの損傷を防ぐことはできません。

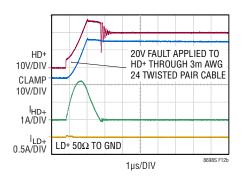

20V への高速ステップを伴う出力ケーブル障害は、ケーブルのインダクタンスとスイッチング・レギュレータのインダクタに蓄積されるエネルギーが原因で、 $V_{IN}$ に最大40Vのリンギングを引き起こすことがあります。 $V_{IN}$ の絶対最大定格42Vはこのリンギングに耐えますが、20Vを超えるケーブル障害は、

誘導性リンギングによって $V_{IN}$ の絶対最大仕様に違反し、ICに損傷を与える可能性があります。 $V_{BUS}$ の出力ピンOUT/ ISP、BUS/ISN、および USB5V の絶対最大定格は42V であるにもかかわらず、このような $V_{IN}$ の損傷が発生することがあります。20Vの高速出力を活線挿入した場合の応答を図9に示します。

図9. V<sub>BUS</sub>上の20V障害

#### 選択ピンSEL1、SEL2、SEL3

選択ピンSEL1~3は、USBホスト・マイクロコントローラとのインターフェースを目的とするトライステート入力ピンです。これらのピンは、USBデータラインD<sup>+</sup>およびD<sup>-</sup>に接続されるLT8698SのHD<sup>+</sup>およびHD<sup>-</sup>ピンの動作ステートを選択します。ステートを動的に変更したくない場合は、選択ピンを個別にローまたはハイに接続するか、オープンのままにして、単一のLT8698Sステートを選択できます。選択ピンは、USB On-The-Go (OTG) 機能用のスイッチング・レギュレータをディスエーブルにして、USB V<sub>BUS</sub>レールの9mAアクティブ放電を開始することもできます。

各選択ピンにはINTV<sub>CC</sub>とGNDの間に接続される抵抗分 圧器があり、ピンをフロート状態のままにした場合はそのピンを1Vにバイアスします。0.48Vより低い電圧に接続すると、入力ローになります。1.51Vより高い電圧またはINTV<sub>CC</sub>に接続すると、入力ハイになります。1µA未満のもれ電流でフロート状態にすると、高インピーダンスのトライステート入力になります。選択ピンの入力は、ピンの入力ステートを内部ステート・マシンに渡す前に1.5msの間デバウンスされます。

STATUS出力ピンの機能は、SEL1~3ピンで選択したステートによって決まります。FLTピンの機能も、SEL1~3ピンで選択したステートによって決まります。V<sub>BUS</sub>が電力供給されていない状態で選択ステート5、11、14、および20によってバス・リセット機能にアクセスした場合、通常のFLTピンの機能に加えて、V<sub>BUS</sub>が高すぎることからFLTをローにすることができます。

SEL1~3ピンのステートと選択されるLT8698Sのステートの対応表については、表6を参照してください。

#### データライン・スイッチ

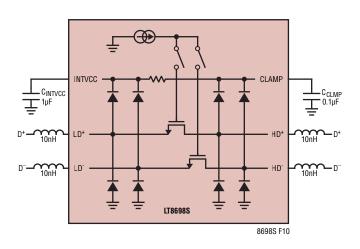

LT8698Sは、High Speed USB 2.0準拠のアナログ・スイッチを2個内蔵しています。これらのスイッチは、USBソケットとホスト・マイクロコントローラ間のUSB D<sup>+</sup>およびD<sup>-</sup>データラインに対して直列に配置されます。データライン・スイッチは、LT8698SのHD<sup>+</sup>ピンとLD<sup>+</sup>ピンを接続し、HD<sup>-</sup>ピンとLD<sup>-</sup>ピンを接続します。データライン上に最大20Vの障害またはESDストライクが発生すると、これらのスイッチは遮断されてホストを保護します。これらのスイッチは、各種のチャージャ・エミュレーション・プロファイルのうち1つに多重化する場合など、SEL1~3ピン入力によって遮断するように命令された場合にも遮断されます。

USB 2.0仕様は、D+およびD-データラインについて、 480Mb/sの高速通信に対応するPCBパターン内での特性 インピーダンスの維持とデータラインの終端を要求していま す。具体的には、D<sup>+</sup>およびD<sup>-</sup>データラインのPCBグラウンド に対するシングルエンド・インピーダンスは45Ωで、D+とD-間の差動インピーダンスは90Ωです。LT8698Sのデータラ イン・スイッチとパッケージには3Ωの標準直列抵抗があり、 高周波数では各データラインとグラウンドの間に約6pFの 並列容量が生じます。45Ωの終端抵抗と比較して、スイッチ のR<sub>DS(ON)</sub>からの実際の抵抗は3Ωと十分に小さいため、ア イ・ダイアグラム上の信号の完全性の問題は発生しません。 データライン・スイッチによって発生する6pFの容量性の不 連続からデータライン上の信号反射を除去するには、HD+、 HD<sup>-</sup>、LD<sup>-</sup>、およびLD<sup>-</sup>と各ピンに対応するデータラインの PCBパターンの間に、4個の小さいインダクタを追加します。 これらのインダクタは、LT8698Sのできるだけ近くに配置して ください。良好なインピーダンス整合を得るには、各データ ラインの合計直列インダクタンスを約20nHにする必要があ ります。したがって、各データライン・ピンHD<sup>+</sup>、HD<sup>-</sup>、LD<sup>+</sup>、 およびLD<sup>-</sup>に10nHを推奨します。HD<sup>+</sup>およびHD<sup>-</sup>ピンへの IEC61000-4-2 ESDストライクに対する堅牢性を確保するに は、最小10nHのインダクタをHD<sup>+</sup>、HD<sup>-</sup>、LD<sup>+</sup>、およびLD<sup>-</sup> に対して直列に接続する必要があります。

High Speed USB 2.0 信号の完全性を更に確実にするため、データラインの帯域幅は製造時に全数検査されています。

## 表6. 選択ピンの対応表

| SELE | CT PIN I | NPUT | CELECT          |                                                                     |                        |                                                              |                                                |                                                       |

|------|----------|------|-----------------|---------------------------------------------------------------------|------------------------|--------------------------------------------------------------|------------------------------------------------|-------------------------------------------------------|

| SEL1 | SEL2     | SEL3 | SELECT<br>STATE | STATE NAME                                                          | V <sub>BUS</sub> STATE | HD+ STATE                                                    | HD <sup>-</sup> STATE                          | STATUS FUNCTION                                       |

| LOW  | LOW      | LOW  | 0               | USB CDP 1                                                           | 5V                     | CDP Sequence,<br>Short to LD <sup>+</sup>                    | CDP Sequence,<br>Short to LD <sup>-</sup>      | Indicates CDP State                                   |

| TRI  | LOW      | LOW  | 1               | USB CDP 2                                                           | 5V                     | CDP Sequence with 20k to GND, Then Short to LD <sup>+</sup>  | CDP Sequence with 20k to GND, Then Short to LD | Indicates CDP State                                   |

| HIGH | LOW      | LOW  | 2               | USB CDP 3                                                           | 5V                     | Short to LD <sup>+</sup>                                     | Short to LD                                    | Indicates Successful CDP<br>Negotiation               |

| LOW  | TRI      | LOW  | 3               | USB SDP 1                                                           | 0V                     | Short to LD+, 20k to GND                                     | Short to LD <sup>-</sup> , 20k to GND          | Indicates V <sub>BUS</sub> Voltage                    |

| TRI  | TRI      | LOW  | 4               | USB SDP 2                                                           | 5V                     | Short to LD <sup>+</sup> , 20k to GND                        | Short to LD <sup>-</sup> , 20k to GND          | Indicates I <sub>BUS</sub> Current                    |

| HIGH | TRI      | LOW  | 5               | USB SDP 3                                                           | Discharge              | Short to LD <sup>+</sup> , 20k to GND                        | Short to LD <sup>-</sup> , 20k to GND          | Indicates V <sub>BUS</sub> Discharge<br>State         |

| LOW  | HIGH     | LOW  | 6               | Null                                                                | 5V                     | Open                                                         | Open                                           | Oscillates                                            |

| TRI  | HIGH     | LOW  | 7               | Null                                                                | 5V                     | Open                                                         | Open                                           | Oscillates                                            |

| HIGH | HIGH     | LOW  | 8               | Null                                                                | 5V                     | Open                                                         | Open                                           | Oscillates                                            |

| LOW  | LOW      | TRI  | 9               | V <sub>BUS</sub> Off with Data Pass<br>Through                      | 0V                     | Short to LD <sup>+</sup>                                     | Short to LD <sup>-</sup>                       | Indicates V <sub>BUS</sub> Voltage                    |

| TRI  | LOW      | TRI  | 10              | V <sub>BUS</sub> On with Data Pass<br>Through                       | 5V                     | Short to LD <sup>+</sup>                                     | Short to LD                                    | Indicates I <sub>BUS</sub> Current                    |

| HIGH | LOW      | TRI  | 11              | V <sub>BUS</sub> Off and Discharged<br>with Data Pass Through       | Discharge              | Short to LD <sup>+</sup>                                     | Short to LD                                    | Indicates V <sub>BUS</sub> Discharge<br>State         |

| LOW  | TRI      | TRI  | 12              | V <sub>BUS</sub> Off                                                | 0V                     | Open                                                         | Open                                           | Indicates V <sub>BUS</sub> Voltage                    |

| TRI  | TRI      | TRI  | 13              | V <sub>BUS</sub> On without Data<br>Pass Through                    | 5V                     | Open                                                         | Open                                           | Reset State, STATUS Pin<br>Indicates I <sub>BUS</sub> |

| HIGH | TRI      | TRI  | 14              | V <sub>BUS</sub> Off and Discharged<br>without Data Pass<br>Through | Discharge              | Open                                                         | Open                                           | Indicates V <sub>BUS</sub> Discharge<br>State         |

| LOW  | HIGH     | TRI  | 15              | Null                                                                | 5V                     | Open                                                         | Open                                           | Oscillates                                            |

| TRI  | HIGH     | TRI  | 16              | Null                                                                | 5V                     | Open                                                         | Open                                           | Oscillates                                            |

| HIGH | HIGH     | TRI  | 17              | Null                                                                | 5V                     | Open                                                         | Open                                           | Oscillates                                            |

| LOW  | LOW      | HIGH | 18              | USB SDP 4                                                           | 0V                     | 20k to GND                                                   | 20k to GND                                     | Indicates V <sub>BUS</sub> Voltage                    |