### 正誤表

この製品のデータシートに間違いがありましたので、お詫びして訂正いたします。 この正誤表は、2020年9月23日現在、アナログ・デバイセズ株式会社で確認した誤りを 記したものです。

なお、英語のデータシート改版時に、これらの誤りが訂正される場合があります。

正誤表作成年月日: 2020 年 9 月 23 日

製品名: ADM2461E/ADM2463E

対象となるデータシートのリビジョン(Rev): Rev.0

訂正箇所:

ページ 6

表 4 の認定規格中、UL1577 の記述が、"UL 1577 Component Recognition Protection" となっていますが、" UL 1577 Component Recognition Program"の誤りです。

アナログ・デバイセズ株式会社

社/〒105-6891 東京都港区海岸 1-16-1

ニューピア竹芝サウスタワービル 10F 電話 03 (5402) 8200

大 阪営業所/〒532-0003 大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 10F

電話 06 (6350) 6868

名古屋営業所/〒451-6038 愛知県名古屋市西区牛島 6-1 名古屋ルーセントタワー 40F 電話 052 (569) 6300

# ±15kV の IEC ESD 規格に準拠した 500kbps、5.7kV rms の 信号絶縁型 RS-485 トランシーバー

### データシート

### **ADM2461E/ADM2463E**

#### 特長

5.7kV rms の信号絶縁型 RS-485/RS-422 トランシーバー 低放射エミッション、2 層 PCB で EN55032 クラス B に 余裕を持って適合

ケーブル反転スマート機能

レシーバーのフェイルセーフをすべて維持しながら A、B、Y、Zバス・ピンの逆ケーブル接続を修正

RS-485 A、B、Y、Zバス・ピンの ESD 保護

IEC61000-4-2 接触放電: ≥±12kV IEC61000-4-2 気中放電: ≥±15kV

500kbps の低速データ・レートによる EMI 制御

柔軟性のある電源入力

ー次側電源 V<sub>DD1</sub>: 1.7V ~ 5.5V 絶縁側電源 V<sub>DD2</sub>: 3.0V ~ 5.5V 5V の V<sub>DD2</sub>で Profibus<sup>®</sup>準拠

広い動作温度範囲: -40°C~+125°C 高いコモンモード過渡耐圧: 250kV/µs 超

入力の短絡、オープン・サーキット、フローティングに対する レシーバーのフェイルセーフ機能

192 個のバス・ノードをサポート

(72kΩのレシーバー入力インピーダンス)

ホット・スワップをフル・サポート

(グリッチ・フリーのパワーアップおよびパワーダウン)

安全性と規制に対する認定(申請中)

CSA Component Acceptance Notice 5A、DIN V VDE V 0884-11、UL 1577、CQC11-471543-2012、IEC 61010-1

標準ピンアウトで 8.0mm を上回る沿面距離および クリアランスを確保した、16 ピン、ワイド・ボディの SOIC\_W パッケージ

### アプリケーション

暖房、換気、空調(HVAC)ネットワーク 工業用フィールド・バス ビルディング・オートメーション ユーティリティ・ネットワーク

#### 概要

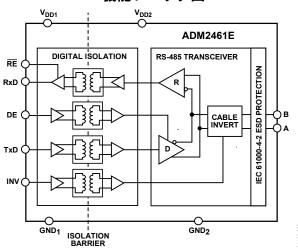

ADM2461E/ADM2463E は 500kbps、5.7kV rms の信号絶縁型 RS-485 トランシーバーで、2 層プリント回路基板 (PCB) で EN55032 クラス B 規格の放射テストに余裕を持って合格しています。ADM2461E/ADM2463E の絶縁バリアは、ノイズやシステム・レベルの EMC 事象に対し強い耐性があります。RS-485 のA、B、Y、Z ピンは、IEC61000-4-2 規格の $\pm$ 12kV 以上の接触放電および $\pm$ 15kV 以上の気中放電の静電放電 (ESD) 事象に対し保護されています。また、ケーブル反転ピンが備わっており、レシーバーのフェイルセーフ性能をすべて維持しながら、A、B、Y、Z バス・ピンの逆ケーブル接続を手早く修正できます。

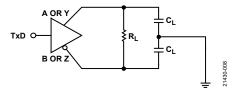

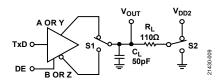

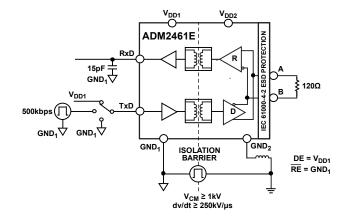

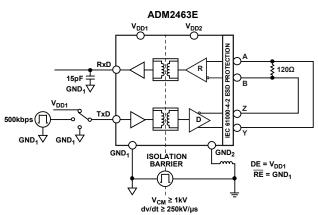

### 機能ブロック図

図 1. ADM2461E の機能ブロック図

図 2. ADM2463E の機能ブロック図

これらのデバイスは、長いケーブル長にわたって低速度用に最適化されており、最大データ・レートは 500kbps です。差動出力電圧が高いため、 $V_{DD2}$ 電源に 5V を供給した場合、Profibus ノードに最適です。一次側電源  $V_{DD1}$  および絶縁側電源  $V_{DD2}$  は、どちらも広い電圧範囲( $V_{DD1}$  は  $1.7V\sim5.5V$ 、 $V_{DD2}$  は  $3V\sim5.5V$ )に対応します。半二重および全二重デバイス・オプションが、業界標準の 16 ピン、ワイド・ボディの標準  $SOIC_{L}W$  パッケージで提供されており、8.0mm を上回る沿面距離およびクリアランスが確保されています。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって 生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示 的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有 者の財産です。※日本語版資料はREVISION が古い場合があります。最新の内容については、英語版をご参照ください。

©2020 Analog Devices, Inc. All rights reserved.

Rev. 0

本 社/〒105-6891

東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 10F 電話 03 (5402) 8200

大 阪営業所/〒532-0003

大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 10F 電話 06 (6350) 6868

名古屋営業所/〒451-6038

愛知県名古屋市西区牛島町 6-1 名古屋ルーセントタワー 38F 電話 052 (569) 6300

# データシート

## ADM2461E/ADM2463E

# 目次

| 特長                                         |

|--------------------------------------------|

| アプリケーション                                   |

| 機能ブロック図                                    |

| 概要                                         |

| 改訂履歴                                       |

| 仕様                                         |

| タイミング仕様                                    |

| パッケージ特性                                    |

| 適用規格                                       |

| 絶縁および安全性関連の仕様                              |

| DIN V VDE 0884-11 (VDE 0884-11) 絶縁特性 (申請中) |

| 絶対最大定格                                     |

| 熱抵抗                                        |

| 静電放電 (ESD) 定格                              |

|                                            |

| ESD に関する注意                                 |

| ピン配置およびピン機能の説明                             |

| 代表的な性能特性1                                  |

| テスト回路とスイッチング特性1:                           |

| <b> 即</b> 作             | 16  |

|-------------------------|-----|

| 堅牢な低消費電力デジタル・アイソレータ     | 16  |

| 高いドライバ差動出力電圧            | 16  |

| IEC61000-4-2 ESD 保護     | 16  |

| 真理値表                    | 17  |

| レシーバーのフェイルセーフ           | 17  |

| ドライバおよびレシーバーのケーブル反転     | 18  |

| ホット・スワップ入力              | 18  |

| バス上で 192 台のトランシーバー      | 18  |

| ドライバ出力保護                | 18  |

| アプリケーション情報              | 19  |

| PCB レイアウトおよび電磁場干渉 (EMI) | 19  |

| 最大データ・レートと周囲温度の関係       | 19  |

| 絶縁型 Profibus ソリューション    | 19  |

| EMC、EFT、サージ保護           | 19  |

| 絶縁寿命                    | 19  |

| 外形寸法                    | 21  |

| ナーガー・ガノド                | 2.1 |

### 改訂履歴

6/2020—Revision 0: Initial Version

### 仕様

すべての電圧値はそれぞれのグラウンドを基準とし、 $1.7V \le V_{DDI} \le 5.5V$ 、 $3.0V \le V_{DD2} \le 5.5V$ 、 $T_A = T_{MIN}$ (-40°C)  $\sim T_{MAX}$ (+125°C)。特に指定のない限り、すべての最小および最大仕様値は推奨動作範囲全体に適用されます。特に指定のない限り、すべての代表的な仕様は、 $T_A = 25$ °C、 $V_{DDI} = V_{DD2} = 3.3V$  での値です。

表 1.

| パラメータ                                                     | 記号                     | Min                  | Тур   | Max                  | 単位 | テスト条件/コメント                                                                                      |

|-----------------------------------------------------------|------------------------|----------------------|-------|----------------------|----|-------------------------------------------------------------------------------------------------|

| PRIMARY SIDE SUPPLY CURRENT                               | $I_{DD1(Q)}$           |                      | 0.6   | 1                    | mA | DE = 0V                                                                                         |

|                                                           | $I_{DD1}$              |                      | 2     | 8                    | mA | $DE = V_{DD1}$                                                                                  |

| ISOLATED SIDE SUPPLY CURRENT                              | I <sub>DD2 (Q)</sub>   |                      | 5     | 8                    | mA | $V_{DD2} \le 3.6 V$ , DE = 0V                                                                   |

|                                                           |                        |                      | 5     | 8                    | mA | $V_{DD2} \ge 4.5 V$ , DE = 0V                                                                   |

|                                                           | $I_{\mathrm{DD2}}$     |                      | 6     | 9                    | mA | $V_{DD2} \le 3.6 V_{\odot} DE = V_{DD1}$                                                        |

|                                                           |                        |                      | 6     | 9                    | mA | $V_{DD2} \ge 4.5 V_{\odot} DE = V_{DD1}$                                                        |

| ISOLATED SIDE DYNAMIC SUPPLY<br>CURRENT                   | $I_{DD2(DYN)}$         |                      | 58    | 78                   | mA | V <sub>DD2</sub> ≤ 3.6V、負荷抵抗(R <sub>L</sub> ) = 54Ω、DE =<br>V <sub>DD1</sub> 、データ・レート = 500kbps |

|                                                           |                        |                      | 100   | 145                  | mA | $V_{DD2} \ge 4.5 V$ 、 $R_L = 54 \Omega$ , $DE = V_{DD1}$ 、データ・レート = 500kbps                     |

| DRIVER DIFFERENTIAL OUTPUTS                               |                        |                      |       |                      |    |                                                                                                 |

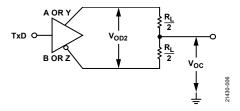

| Differential Output Voltage, Loaded                       | $ V_{\mathrm{OD2}} $   | 2.0                  | 2.5   | $V_{DD2} \\$         | V  | V <sub>DD2</sub> ≥3.0V、R <sub>L</sub> =100Ω、図31を参照                                              |

|                                                           |                        | 1.5                  | 2.1   | $V_{DD2} \\$         | V  | V <sub>DD2</sub> ≥3.0V、R <sub>L</sub> =54Ω、図31を参照                                               |

|                                                           |                        | 2.1                  | 3.3   | $V_{DD2}$            | V  | V <sub>DD2</sub> ≥4.5V、R <sub>L</sub> =54Ω、図31を参照                                               |

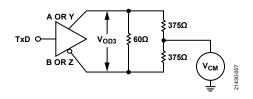

| Over Common-Mode Range                                    | $ V_{\text{OD3}} $     | 1.5                  | 2.1   | $V_{DD2}$            | V  | V <sub>DD2</sub> ≥3.0V、-7V≤コモンモード電圧 (V <sub>CM</sub> )<br>≤+12V、図 32 を参照                        |

|                                                           |                        | 2.1                  | 3.3   | $V_{DD2} \\$         | V  | V <sub>DD2</sub> ≥ 4.5V、-7V ≤ V <sub>CM</sub> ≤ +12V、図 32 を参照                                   |

| $\Delta  V_{\text{OD2}} $ for Complementary Output States | $\Delta  V_{\rm OD2} $ |                      |       | 0.2                  | V  | R <sub>L</sub> = 54Ω または 100Ω、図 31 を参照                                                          |

| Common-Mode Output Voltage                                | $V_{OC}$               |                      | 1.5   | 3.0                  | V  | $R_L = 54\Omega$ または $100\Omega$ 、図 $31$ を参照                                                    |

| $\Delta  V_{OC} $ for Complementary Output States         | $\Delta  V_{\rm OC} $  |                      |       | 0.2                  | V  | $R_L = 54\Omega$ または $100\Omega$ 、図 $31$ を参照                                                    |

| Short-Circuit Output Current                              | $I_{OS}$               | -250                 |       | +250                 | mA | -7V < 出力電圧 (V <sub>OUT</sub> ) <+12V                                                            |

| Output Leakage Current (Y, Z) <sup>1</sup>                | $I_{O}$                |                      | 1     | 50                   | μΑ | $DE = \overline{RE} = 0V$ 、 $V_{DD2} = 0V$ または 5.5V、入力電<br>圧 $(V_{IN}) = 12V$                   |

|                                                           |                        | -50                  | +10   |                      | μΑ | $DE = \overline{RE} = 0V$ 、 $V_{DD2} = 0V$ または 5.5V、 $V_{IN} = -7V$                             |

| Pin Capacitance (A, B, Y, Z)                              | $C_{IN}$               |                      | 28    |                      | pF | $V_{IN} = 0.4\sin(10 \pi t \times 10^6)$                                                        |

| RECEIVER DIFFERENTIAL INPUTS                              |                        |                      |       |                      |    |                                                                                                 |

| Differential Input Threshold Voltage,<br>Noninverted      | $V_{TH}$               | -200                 | -125  | -30                  | mV | $-7V < V_{CM} < +12V$ , INV $\pm \hbar t$ INVR = 0V                                             |

| Differential Input Threshold Voltage,<br>Inverted         |                        | 30                   | 125   | 200                  | mV | $-7V < V_{CM} < +12V$ , INV $\sharp \mathcal{L}$ INVR = $V_{DD1}$                               |

| Input Voltage Hysteresis                                  | $V_{HYS}$              |                      | 25    |                      | mV | $-7V < V_{CM} < +12V$                                                                           |

| Input Current (A, B)                                      | $I_{I}$                |                      |       | 167                  | μΑ | $DE = 0V$ 、 $V_{DD2} = 0V$ または 5.5V、 $V_{IN} = 12V$                                             |

|                                                           |                        | -133                 |       |                      | μΑ | $DE = 0V$ 、 $V_{DD2} = 0V$ または 5.5V、 $V_{IN} = -7V$                                             |

| Pin Capacitance (A, B)                                    | $C_{IN}$               |                      | 4     |                      | pF | $V_{IN} = 0.4\sin(10 \pi t \times 10^6)$                                                        |

| DIGITAL LOGIC INPUTS                                      |                        |                      |       |                      |    |                                                                                                 |

| Input Low Voltage                                         | $V_{IL}$               |                      |       | $0.3 \times V_{DD1}$ | V  | DE, RE, TxD, INV, INVR                                                                          |

| Input High Voltage                                        | $V_{IH}$               | $0.7 \times V_{DD1}$ |       |                      | V  | DE, $\overline{RE}$ , TxD, INV, INVR                                                            |

| Input Current                                             | $I_{\rm I}$            | -2                   | +0.01 | +2                   | μΑ | DE、 $\overline{RE}$ 、 $TxD$ 、 $V_{IN} = 0V$ または $V_{DD1}$                                       |

|                                                           |                        | -2                   | +10   | +30                  | μΑ | INV、INVR、 $V_{IN} = 0V$ または $V_{DD1}$                                                           |

| RxD DIGITAL OUTPUT                                        |                        |                      |       |                      |    |                                                                                                 |

| Output Voltage Low                                        | $V_{OL}$               |                      |       | 0.4                  | V  | V <sub>DDI</sub> = 3.6V、出力電流(I <sub>OUT</sub> ) = 2.0mA、差動<br>入力電圧(V <sub>ID</sub> ) ≤ −0.2V    |

|                                                           |                        |                      |       | 0.4                  | V  | $V_{DD1} = 2.7V$ , $I_{OUT} = 1.0 \text{mA}$ , $V_{ID} \le -0.2 \text{V}$                       |

|                                                           |                        |                      |       | 0.2                  | V  | $V_{DD1} = 1.95 V$ , $I_{OUT} = 500 \mu A$ , $V_{ID} \le -0.2 V$                                |

Rev. 0 - 3/21 -

### データシート

### ADM2461E/ADM2463E

| パラメータ                                                 | 記号        | Min           | Тур   | Max | 単位    | テスト条件/コメント                                                                   |

|-------------------------------------------------------|-----------|---------------|-------|-----|-------|------------------------------------------------------------------------------|

| Output Voltage High                                   | $V_{OH}$  | 2.4           |       |     | V     | $V_{DD1} = 3.0 V$ , $I_{OUT} = -2.0 \text{mA}$ , $V_{ID} \ge -0.03 V$        |

|                                                       |           | 2.0           |       |     | V     | $V_{DD1} = 2.3 V, I_{OUT} = -1.0 \text{mA}, V_{ID} \ge -0.03 V$              |

|                                                       |           | $V_{DD1}-0.2$ |       |     | V     | $V_{DD1} = 1.7V, I_{OUT} = -500 \mu A, V \ge -0.03V$                         |

| Short-Circuit Current                                 |           |               |       | 100 | mA    | $V_{OUT} = GND_1 \pm \hbar t V_{DD1}, \overline{RE} = 0V$                    |

| Three-State Output Leakage Current                    | $I_{OZR}$ | -1            | +0.01 | +1  | μΑ    | $\overline{RE} = V_{DDI}$ 、 $RxD = 0V$ または $V_{DDI}$                         |

| COMMON-MODE TRANSIENT<br>IMMUNITY (CMTI) <sup>2</sup> |           | 250           |       |     | kV/μs | $V_{CM} \ge \pm 1 k V$ 、トランジェントの大きさは、 $V_{CM}$ の 20%~80%で測定、図 37 および図 38 を参照 |

$<sup>^1</sup>$  ADM2463E のみ。

### タイミング仕様

特に指定がない限り、 $V_{DD1}=1.7V\sim5.5V$ 、 $V_{DD2}=3.0V\sim5.5V$ 、 $T_A=T_{MIN}$ (-40°C)  $\sim T_{MAX}$ (+125°C)。特に指定のない限り、すべての代表的な仕様は、 $T_A=25$ °C、 $V_{DD1}=V_{DD2}=3.3V$  での値です。

#### 表 2.

| パラメータ                             | 記号                                       | Min | Тур  | Max  | 単位   | テスト条件/コメント                                                   |

|-----------------------------------|------------------------------------------|-----|------|------|------|--------------------------------------------------------------|

| DRIVER                            |                                          |     |      |      |      |                                                              |

| Maximum Data Rate                 |                                          | 500 |      |      | kbps |                                                              |

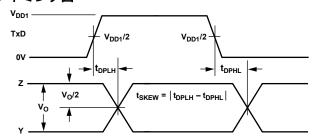

| Propagation Delay                 | $t_{DPLH}, t_{DPHL}$                     |     | 230  | 400  | ns   | R <sub>L</sub> = 54Ω、C <sub>L</sub> = 100pF、図 33 および図 3 を参照。 |

| Output Skew                       | $t_{SKEW}$                               |     | 3    | 100  | ns   | R <sub>L</sub> = 54Ω、C <sub>L</sub> = 100pF、図 33 および図 3 を参照。 |

| Rise Time and Fall Time           | $t_{DR},t_{DF}$                          | 200 | 400  | 800  | ns   | R <sub>L</sub> = 54Ω、C <sub>L</sub> = 100pF、図 33 および図 3 を参照。 |

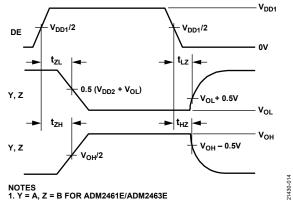

| Enable Time                       | $t_{ZL}, t_{ZH}$                         |     | 150  | 1000 | ns   | R <sub>L</sub> =110Ω、C <sub>L</sub> =50pF、図34および図5を参照。       |

| Disable Time                      | $t_{LZ},t_{HZ}$                          |     | 1700 | 2200 | ns   | R <sub>L</sub> =110Ω、C <sub>L</sub> =50pF、図 34 および図 5 を参照。   |

| RECEIVER                          |                                          |     |      |      |      |                                                              |

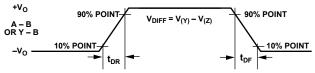

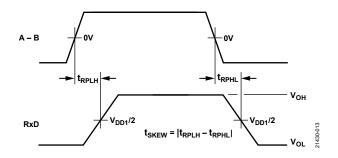

| Propagation Delay                 | $t_{RPLH}, t_{RPHL}$                     |     | 30   | 200  | ns   | C <sub>L</sub> = 15pF、図 35 と図 4 を参照。                         |

| Output Skew                       | $t_{SKEW}$                               |     | 2.5  | 50   | ns   | C <sub>L</sub> = 15pF、図 35 と図 4 を参照。                         |

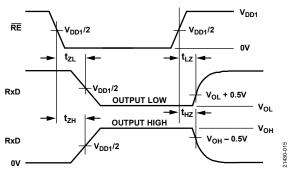

| Enable Time                       | $t_{ZL}, t_{ZH}$                         |     | 3    | 50   | ns   | R <sub>L</sub> = 1kΩ、C <sub>L</sub> = 15pF、図 36 および図 6 を参照。  |

| Disable Time                      | $t_{LZ},t_{HZ}$                          |     | 8    | 50   | ns   | R <sub>L</sub> = 1kΩ、C <sub>L</sub> = 15pF、図 36 および図 6 を参照。  |

| RECEIVER CABLE INVERT (INVR, INV) |                                          |     |      |      |      |                                                              |

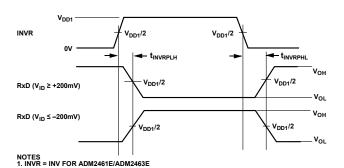

| Propagation Delay                 | $t_{\text{INVRPHL}}, t_{\text{INVRPLH}}$ |     | 20   | 40   | ns   | $V_{ID} \ge -200$ mV または $V_{ID} \le +200$ mV、図 7 を参照。       |

| DRIVER CABLE INVERT (INV)         |                                          |     |      |      |      |                                                              |

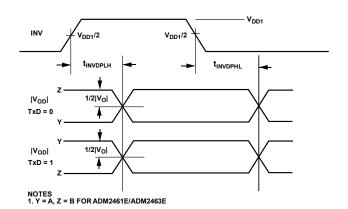

| Propagation Delay                 | $t_{\text{INVDPHL}}, t_{\text{INVDPLH}}$ |     | 230  | 400  | ns   | TxD=0VまたはTxD=V <sub>DD1</sub> 、図8を参照。                        |

Rev. 0 - 4/21 -

$<sup>^2</sup>$  CMTI は、仕様に準拠した動作を維持しながら持続できる、最大コモンモード電圧スルー・レートです。 $V_{CM}$ は、ロジックとバス側の間のコモンモード電位差です。トランジェントの大きさは、コモンモードがスルーされる範囲です。コモンモード電圧スルー・レートは、立上がりと立下がりのコモンモード電圧エッジに適用されます。

### タイミング図

NOTES 1. Y = A, Z = B FOR ADM2461E/ADM2463E

図 3. ドライバ伝搬遅延、立上がりおよび立下がりのタイミング

図 4. レシーバー伝搬遅延

図 5. ドライバ・イネーブル/ディスエーブルのタイミング

図 6. レシーバー・イネーブル/ディスエーブルのタイミング

図 7. レシーバー・ケーブル反転のタイミング仕様測定

図 8. ドライバ・ケーブル反転のタイミング仕様測定

Rev. 0 – 5/21 –

### パッケージ特性

#### 表 3.

| Parameter                                  | Symbol           | Min | Тур       | Max | Unit | Test Conditions/Comments |

|--------------------------------------------|------------------|-----|-----------|-----|------|--------------------------|

| Resistance (Input to Output) <sup>1</sup>  | R <sub>I-O</sub> |     | $10^{13}$ |     | Ω    |                          |

| Capacitance (Input to Output) <sup>1</sup> | $C_{\text{I-O}}$ |     | 2.2       |     | pF   | Test frequency = 1 MHz   |

| Input Capacitance <sup>2</sup>             | $C_{I}$          |     | 3.0       |     | pF   |                          |

<sup>「</sup>このデバイスは 2 端子デバイスとみなされます。テスト中のデバイスを 2 端子デバイスに設定するには、ピン 1~ピン 8 およびピン 9~ピン 16 を短絡します。

### 適用規格

詳細については www.analog.com/jp/icouplersafety を参照してください。

#### 表 4. ADM2461E/ADM2463E の認定

| UL(申請中)                                                                      | CSA (申請中)                                                                       | VDE (申請中)                                | CQC (申請中)                     |

|------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------|-------------------------------|

| Recognized Under UL 1577<br>Component Recognition<br>Protection <sup>1</sup> | CSA Component Acceptance Notice 5A による認定                                        | DIN V VDE 0884-11 による認証予定 <sup>2</sup>   | CQC11-471543-2012 によ<br>る認証   |

| Single Protection, 5700 V rms                                                | CSA 60950-1-07+A1+A2 および IEC 60950-<br>1、second edition、+A1+A2                  | 基本絶縁                                     | GB4943.1-2011                 |

|                                                                              | 800V rms(1131V peak)の基本絶縁                                                       | 動作電圧(V <sub>IOWM</sub> ) = 875V rms      | 800V rms(1131V peak)の<br>基本絶縁 |

|                                                                              | 400V rms(565V peak)の強化絶縁                                                        | 繰返し最大電圧(V <sub>IORM</sub> ) = 1237V peak | 400V rms(565V peak)の<br>強化絶縁  |

|                                                                              | CSA 62368-1-14、EN 62368-<br>1:2014/A11:2017、IEC 62368-1: 2014<br>second edition | サージ絶縁電圧(V <sub>IOSM</sub> ) = 10kV peak  |                               |

|                                                                              | 800V rms(1131V peak)の基本絶縁                                                       | 最大許容過電圧(V <sub>IOTM</sub> ) = 8000V peak |                               |

|                                                                              | 400V rms(565V peak)の強化絶縁                                                        | 強化絶縁                                     |                               |

|                                                                              | IEC 60601-1 Edition 3.1:                                                        | $V_{IOWM} = 750V \text{ rms}$            |                               |

|                                                                              | 1 患者保護手段(1MOPP)、400V rms<br>(565V peak)                                         | $V_{IORM} = 1060 \text{ V peak}$         |                               |

|                                                                              | 2MOPP、250V rms(353V peak)                                                       | $V_{IOSM} = 6.25 \text{ kV peak}$        |                               |

|                                                                              | 1MOPPまたは2MOPP、400V rms(565V peak)                                               | $V_{IOTM} = 8000 \text{ V peak}$         |                               |

|                                                                              | CSA 61010-1-12 および IEC 61010-1 third edition                                    |                                          |                               |

|                                                                              | 商用電源 300V rms、二次回路 800V rms<br>(1131V peak)の基本絶縁                                |                                          |                               |

|                                                                              | 商用電源 300V rms、二次回路 400V rms<br>(565V peak)の強化絶縁                                 |                                          |                               |

| ファイル (申請中)                                                                   | ファイル (申請中)                                                                      | ファイル (申請中)                               | ファイル (申請中)                    |

<sup>1</sup>UL 1577 に従い、それぞれの ADM2461E/ADM2463E には 6840V rms 以上の絶縁テスト電圧を 1 秒間加える耐電圧テストを実施しています。

<sup>2</sup>DIN V VDE 0884-11 に従い、それぞれの ADM2461E/ADM2463E には 2320V peak 以上の絶縁テスト電圧を 1 秒間加える耐電圧テストを実施しています(部分放電検出限界 = 5pC)。

### 絶縁および安全性関連の仕様

表 5. 安全に関係する重要な寸法と材料特性

| パラメータ                                                                          | 記号      | 値    | 単位     | テスト条件/コメント                          |

|--------------------------------------------------------------------------------|---------|------|--------|-------------------------------------|

| Rated Dielectric Insulation Voltage                                            |         | 5700 | V rms  | 1分間隔                                |

| Minimum External Air Gap (Clearance)                                           | L(I01)  | 8.3  | mm     | 入力端子から出力端子までを測定、空気中の最短距離            |

| Minimum External Tracking (Creepage)                                           | L(I02)  | 8.3  | mm     | 入力端子から出力端子までを測定、ボディに沿った最短距<br>離     |

| Minimum Clearance in the Plane of the Printed Circuit<br>Board (PCB Clearance) | L (PCB) | 8.1  | mm     | PCB 実装面の空中で、入力端子と出力端子の間の直線距離<br>を測定 |

| Minimum Internal Gap (Internal Clearance)                                      |         | 43   | μm min | 絶縁体を介した絶縁距離                         |

| Tracking Resistance (Comparative Tracking Index)                               | CTI     | >600 | V      | DIN IEC 112/VDE 0303 Part 1         |

| Material Group                                                                 |         | I    |        | 材料グループ (DIN VDE 0110: 1989-01、表 1)  |

Rev. 0 - 6/21 -

$<sup>^{2}</sup>$  入力容量は任意の入力データ・ピンとグラウンドの間の値です。

### DIN V VDE 0884-11 (VDE 0884-11) 絶縁特性 (申請中)

ADM2461E/ADM2463E は、安全限界データ範囲内の強化絶縁にのみ適しています。安全性データの維持は、保護回路によって確保する必要があります。

表 6.

| 説明                                                                   | テスト条件/コメント                                                                               | 記号                | 特性        | 単位     |

|----------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------|-----------|--------|

| CLASSIFICATIONS                                                      |                                                                                          |                   |           |        |

| Installation Classification per DIN VDE 0110 for Rated Mains Voltage |                                                                                          |                   |           |        |

| ≤600 V rms                                                           | 強化絶縁                                                                                     |                   | I to IV   |        |

| ≤750 V rms                                                           | 強化絶縁                                                                                     |                   | I to III  |        |

| ≤875 V rms                                                           | 基本絶縁                                                                                     |                   | I to IV   |        |

| Climatic Classification                                              |                                                                                          |                   | 40/125/21 |        |

| Pollution Degree                                                     | DIN VDE 0110、表 1 を参照                                                                     |                   | 2         |        |

| VOLTAGE                                                              |                                                                                          |                   |           |        |

| Maximum Working Insulation Voltage                                   | 基本絶縁                                                                                     | $V_{IOWM}$        | 875       | V rms  |

|                                                                      | 強化絶縁                                                                                     |                   | 750       | V rms  |

| Maximum Repetitive Peak Insulation Voltage                           | 基本絶縁                                                                                     | $V_{IORM}$        | 1237      | V peak |

|                                                                      | 強化絶縁                                                                                     |                   | 1060      | V peak |

| Maximum DC Working Insulation Voltage                                | 基本絶縁                                                                                     | V <sub>IOWM</sub> | 1237      | V dc   |

|                                                                      | 強化絶縁                                                                                     | (DC)              | 1060      | V dc   |

| Input to Output Test Voltage                                         |                                                                                          | $V_{PR}$          |           |        |

| Method b1                                                            | V <sub>IORM</sub> × 1.875 = V <sub>PR</sub> 、100%出荷テスト済み、t <sub>m</sub> = 1 秒、部分放電 < 5pC |                   | 2320      | V peak |

| Method a                                                             |                                                                                          |                   |           |        |

| After Environmental Tests, Subgroup 1                                | $V_{IORM} \times 1.5 = V_{pd}(m)$ 、 $t_{ini} = 60$ 秒、 $t_m = 10$ 秒、部分放電 $<$ 5pC          |                   | 1856      | V peak |

| After Input and/or Safety Test,<br>Subgroup 2/Subgroup 3             | $V_{IORM} \times 1.2 = V_{pd}(m)$ 、 $t_{ini} = 60$ 秒、 $t_m = 10$ 秒、部分放電 $< 5pC$          |                   | 1485      | V peak |

| Highest Allowable Overvoltage                                        | トランジェント過電圧、t <sub>TR</sub> = 10 秒                                                        | $V_{IOTM}$        | 8000      | V peak |

| Surge Isolation Voltage, Basic                                       | ピーク電圧 (V <sub>PEAK</sub> ) = 10kV、1.2μs の立上がり<br>時間、50μs の 50%立下がり時間                     | $V_{IOSM}$        | 10,000    | V peak |

| Surge Isolation Voltage, Reinforced                                  | V <sub>PEAK</sub> = 10kV、1.2μs の立上がり時間、50μs の<br>50%立下がり時間                               | $V_{\text{IOSM}}$ | 6250      | V peak |

| SAFETY-LIMITING VALUES                                               | 故障発生時に許容される最大値                                                                           |                   |           |        |

| Case Temperature                                                     |                                                                                          | Ts                | 150       | °C     |

| Total Power Dissipation at 25°C                                      |                                                                                          | $P_{S}$           | 1.95      | W      |

| Insulation Resistance at T <sub>S</sub>                              | $V_{IO} = 500V$                                                                          | $R_{S}$           | >109      | Ω      |

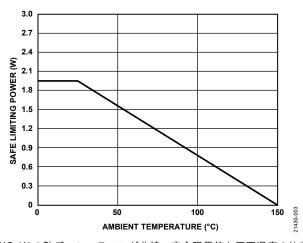

図 9. 16 ピンの標準ワイド・ボディ SOIC\_W の熱ディレーティング曲線、安全限界値と周囲温度の依存関係(DIN V VDE V 0884-10 に適合)

Rev. 0 - 7/21 -

### 絶対最大定格

特に指定のない限り、 $T_A = 25$ °C。すべての電圧は、それぞれのグラウンドを基準とします。

#### 表 7.

| Parameter                                             | Rating                                      |

|-------------------------------------------------------|---------------------------------------------|

| V <sub>DD1</sub> to GND <sub>1</sub>                  | -0.5 V to +7 V                              |

| $V_{DD2}$ to $GND_2$                                  | −0.5 V to +7 V                              |

| Digital Input Voltage (DE, RE, TxD, INV,              | $-0.3 \text{ V to V}_{DD1} + 0.3 \text{ V}$ |

| and INVR)                                             |                                             |

| Digital Output Voltage (RxD)                          | $-0.3 \text{ V to V}_{DD1} + 0.3 \text{ V}$ |

| Driver Output/Receiver Input Voltage (A, B, Y, and Z) | -9 V to +14 V                               |

| Operating Temperature Range                           | −40°C to +125°C                             |

| Storage Temperature Range                             | −55°C to +150°C                             |

| Lead Temperature                                      |                                             |

| Soldering (10 sec)                                    | 260°C                                       |

| Vapor Phase (60 sec)                                  | 215°C                                       |

| Infrared (15 sec)                                     | 220°C                                       |

上記の絶対最大定格を超えるストレスを加えると、デバイスに 恒久的な損傷を与えることがあります。この規定はストレス定 格のみを指定するものであり、この仕様の動作のセクションに 記載する規定値以上でのデバイス動作を定めたものではありま せん。デバイスを長時間にわたり絶対最大定格状態に置くと、 デバイスの信頼性に影響を与えることがあります。

### 熱抵抗

熱性能は、PCBの設計と動作環境に直接関連します。PCBの熱設計には、細心の注意を払う必要があります。

$\theta_{JA}$ は、1立方フィートの密封容器内で測定された、自然対流下におけるジャンクションと周囲温度の間の熱抵抗です。

表 8. 熱抵抗

| Package Type       | $\theta_{JA}$ | Unit |

|--------------------|---------------|------|

| RW-16 <sup>1</sup> | 63.9          | °C/W |

<sup>&</sup>lt;sup>1</sup>熱抵抗のシミュレーション値は、バイアスのない JEDEC 2S2P サーマル・テスト・ボードに基づいています。JEDEC JESD-51 を参照してください。

### 静電放電(ESD)定格

次のESD情報は、ESDに敏感なデバイスをESD保護領域内においてのみ取り扱う場合のものです。

ANSI/ESDA/JEDEC JS-001 準拠の人体モデル (HBM)。

国際電気標準会議(IEC)電磁両立性:Part 4-2(IEC)(IEC 61000-4-2 準拠)。

#### ADM2461E/ADM2463E の ESD 定格

表 9. ADM2461E/ADM2463E、16 ピン SOIC\_W

| ESD Model | Withstand Threshold (V)                          | Class                |

|-----------|--------------------------------------------------|----------------------|

| HBM       | ±4000                                            | 3A                   |

| CDM       | ±1250                                            | C5                   |

| IEC1      | ≥±12,000 (contact discharge) to GND <sub>2</sub> | Level 4              |

|           | ≥±15,000 (air discharge) to GND <sub>2</sub>     | Level 4              |

|           | ≥±8,000 (contact/air discharge) to GND₁          | Level 4 <sup>2</sup> |

¹ピンA、ピンB、ピンY、ピンZのみ。

### ESDに関する注意

ESD(静電放電)の影響を受けやすいデバイスです。 電荷を帯びたデバイスや回路ボードは、検知されない

まま放電することがあります。本製品は当社独自の特許技術であるESD保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

### 表 10. 最大連続動作電圧 1,2

| パラメータ                 | 最大値         | 単位     | 参照標準                                  |  |

|-----------------------|-------------|--------|---------------------------------------|--|

| AC Voltage (Bipolar)  |             |        |                                       |  |

| Basic Insulation      | 1237 V peak |        | 最低 50 年の寿命                            |  |

| Reinforced Insulation | 1060        | V peak | 最低 50 年の寿命                            |  |

| AC Voltage (Unipolar) |             |        |                                       |  |

| Basic Insulation      | 2474        | V peak | 最低 50 年の寿命                            |  |

| Reinforced Insulation | 1355        | V peak | 寿命は IEC60664-1 のパッケージ沿面距離により<br>制限される |  |

| DC Voltage            |             |        |                                       |  |

| Basic Insulation      | 1237        | V dc   | 最低 50 年の寿命                            |  |

| Reinforced Insulation | 830         | V dc   | 寿命は IEC60664-1 のパッケージ沿面距離により<br>制限される |  |

<sup>1</sup>最大連続動作電圧は、絶縁バリアの両端にかかる連続電圧の大きさを指します。詳細については、絶縁寿命のセクションを参照してください。

Rev. 0 - 8/21 -

<sup>2</sup>絶縁バリア両端間のクリアランスによって制限。

<sup>&</sup>lt;sup>2</sup>値は、材料グループI、汚染度IIに適用されます。

### ピン配置およびピン機能の説明

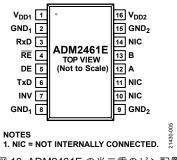

図 10. ADM2461E の半二重のピン配置

表 11. ADM2461E のピン機能の説明

| ピン番号       | 記号        | 説明                                                                                                                                                                                                                                                |

|------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | $V_{DD1}$ | 1.7V~5.5V のフレキシブルな一次側電源。ピン 1 とピン 2 の間に $0.1\mu$ F のデカップリング・コンデンサを接続し、この 2 つの電源をデカップリングします。 $10\mu$ F のデカップリング・コンデンサをピン 1 とピン 2 の間に追加接続すると、ノイズの多い環境でのノイズ耐性を向上できます。                                                                                 |

| 2, 8       | $GND_1$   | グラウンド1、ロジック側。                                                                                                                                                                                                                                     |

| 3          | RxD       | レシーバー出力データ。INV ピンがロジック・ローの場合、この出力は、 $A-B \ge -30 mV$ の場合にハイになり、 $A-B \le -200 mV$ の場合にローになります。INV ピンがロジック・ハイの場合、この出力は、 $A-B \le 30 mV$ の場合にハイになり、 $A-B \ge 200 mV$ の場合にローになります。 $\overline{RE}$ ピンがハイにドライブされると、レシーバーはディスエーブルされ、この出力はトライステートとなります。 |

| 4          | RE        | レシーバー・イネーブル入力。このピンはアクティブ・ロー入力です。この入力をローにドライブするとレシーバーはイネーブルとなります。この入力をハイにドライブするとレシーバーはディスエーブルとなります。                                                                                                                                                |

| 5          | DE        | ドライバ出力イネーブル。このピンがハイ・レベルの場合、ドライバの差動出力AとBが有効になります。ロー・レベルの場合は、高インピーダンス状態になります。                                                                                                                                                                       |

| 6          | TxD       | 送信データ入力。この入力には、ドライバで転送するデータが適用されます。INV ピンがロジック・ハイの場合、この入力に印加されたデータは反転されます。                                                                                                                                                                        |

| 7          | INV       | ケーブル反転入力。このピンはアクティブ・ハイ入力です。このピンをハイにドライブすると、印加された TxD 信号と A および B のレシーバー入力が反転されるため逆ケーブル接続を修正できます。このピンは高インピーダンスを介して内部でグラウンドに接続されます。ケーブル反転機能を使用しない場合は、このピンを GND <sub>1</sub> に接続してください。                                                              |

| 9, 15      | $GND_2$   | 内蔵 RS-485 トランシーバーの絶縁グラウンド 2、バス側。                                                                                                                                                                                                                  |

| 10, 11, 14 | NIC       | 内部では未接続。                                                                                                                                                                                                                                          |

| 12         | A         | ドライバ非反転出力/レシーバー非反転入力。                                                                                                                                                                                                                             |

| 13         | В         | ドライバ反転出力/レシーバー反転入力。                                                                                                                                                                                                                               |

| 16         | $V_{DD2}$ | $3.0V\sim5.5V$ の絶縁側電源。ピン $16$ とピン $15$ の間に $0.1\mu F$ のデカップリング・コンデンサを接続し、この $2$ つの電源をデカップリングします。 $10\mu F$ のデカップリング・コンデンサをピン $16$ とピン $15$ の間に追加接続すると、ノイズの多い環境でのノイズ耐性を向上できます。                                                                     |

Rev. 0 - 9/21 -

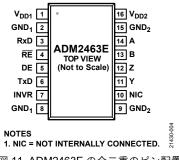

図 11. ADM2463E の全二重のピン配置

表 12. ADM2463E のピン機能の説明

| ピン番号  | 記号                 | 説明                                                                                                                                                                                                                                                                     |

|-------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | $V_{DDI}$          | 1.7V~5.5V のフレキシブルな一次側電源。ピン 1 とピン 2 の間に $0.1\mu F$ のデカップリング・コンデンサを接続し、この 2 つの電源をデカップリングします。 $10\mu F$ のデカップリング・コンデンサをピン 1 とピン 2 の間に追加接続すると、ノイズの多い環境でのノイズ耐性を向上できます。                                                                                                      |

| 2, 8  | $GND_1$            | グラウンド1、ロジック側。                                                                                                                                                                                                                                                          |

| 3     | RxD                | レシーバー出力データ。INVR ピンがロジック・ローの場合、この出力は差動レシーバー入力電圧( $A-B$ ) $\geq -30 mV$ の場合にハイになり、 $A-B \leq -200 mV$ の場合にローになります。INVR ピンがロジック・ハイの場合、この出力は、 $A-B \leq 30 mV$ の場合にハイになり、 $A-B \geq 200 mV$ の場合にローになります。 $\overline{RE}$ ピンがハイにドライブされると、レシーバーはディスエーブルされ、この出力はトライステートとなります。 |

| 4     | RE                 | レシーバー・イネーブル入力。このピンはアクティブ・ロー入力です。この入力をローにドライブするとレシーバーはイネーブルとなります。この入力をハイにドライブするとレシーバーはディスエーブルとなります。                                                                                                                                                                     |

| 5     | DE                 | ドライバ出力イネーブル。このピンがハイ・レベルの場合、ドライバの差動出力YとZが有効になります。ロー・レベルの場合は、高インピーダンス状態になります。                                                                                                                                                                                            |

| 6     | TxD                | 送信データ入力。この入力には、ドライバで転送するデータが適用されます。                                                                                                                                                                                                                                    |

| 7     | INVR               | レシーバー・ケーブル反転入力。このピンはアクティブ・ハイ入力です。このピンをハイにドライブすると、A および B のレシーバー入力が反転されるため逆ケーブル接続を修正できます。このピンは高インピーダンスを介して内部でグラウンドに接続されます。ケーブル反転機能を使用しない場合は、このピンを GND <sub>1</sub> に接続してください。                                                                                           |

| 9, 15 | $GND_2$            | 内蔵 RS-485 トランシーバーの絶縁グラウンド 2、バス側。                                                                                                                                                                                                                                       |

| 10    | NIC                | 内部では未接続。                                                                                                                                                                                                                                                               |

| 11    | Y                  | ドライバ非反転出力。                                                                                                                                                                                                                                                             |

| 12    | Z                  | ドライバ反転出力。                                                                                                                                                                                                                                                              |

| 13    | В                  | レシーバー反転入力。                                                                                                                                                                                                                                                             |

| 14    | A                  | レシーバー非反転入力。                                                                                                                                                                                                                                                            |

| 16    | $V_{\mathrm{DD2}}$ | $3.0V\sim5.5V$ の絶縁側電源。ピン $16$ とピン $15$ の間に $0.1\mu F$ のデカップリング・コンデンサを接続し、この $2$ つの電源をデカップリングします。 $10\mu F$ のデカップリング・コンデンサをピン $16$ とピン $15$ の間に追加接続すると、ノイズの多い環境でのノイズ耐性を向上できます。                                                                                          |

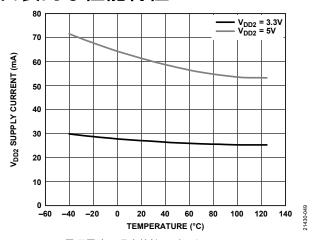

### 代表的な性能特性

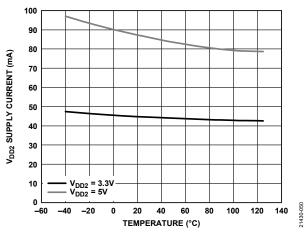

図 12. V<sub>DD2</sub> 電源電流の温度特性、データ・レート = 500kbps、 無負荷

図 13.  $V_{DD2}$ 電源電流と温度の関係、データ・レート = 500kbps、 $R_L$  =  $120\Omega$

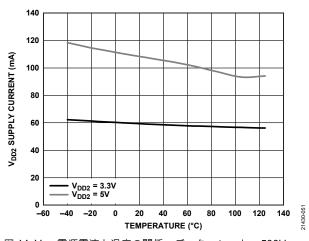

図 14.  $V_{DD2}$ 電源電流と温度の関係、データ・レート = 500kbps、 $R_L = 54\Omega$

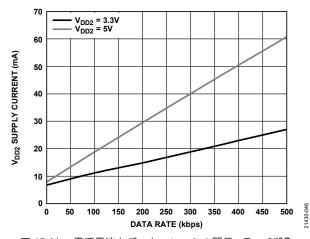

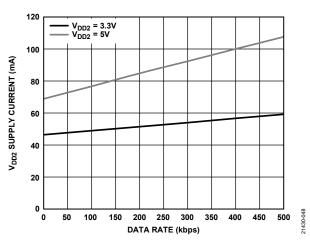

図 15.  $V_{DD2}$ 電源電流とデータ・レートの関係、 $T_A=25^{\circ}C$ 、 無負荷

図 16.  $V_{DD2}$ 電源電流とデータ・レートの関係、 $T_A=25^{\circ}C$ 、 $R_L=120\Omega$

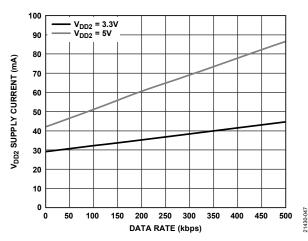

図 17.  $V_{DD2}$ 電源電流とデータ・レートの関係、 $T_A$  = 25°C、 $R_L$  = 54 $\Omega$

Rev. 0 — 11/21 —

### ADM2461E/ADM2463E

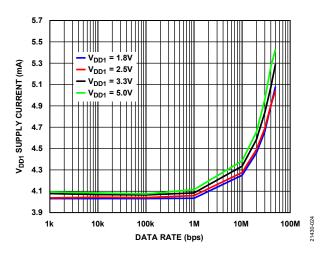

図 18. V<sub>DD1</sub> 電源電流とデータ・レートの関係

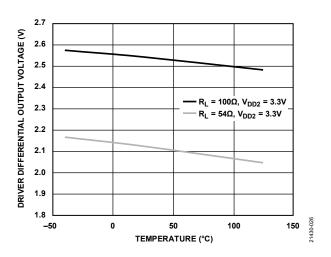

図 19. ドライバ差動出力電圧と温度の関係

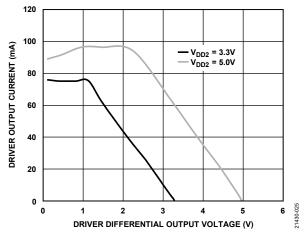

図 20. ドライバ出力電流とドライバ差動出力電圧の関係

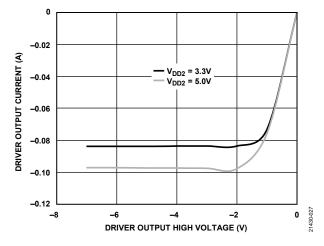

図 21. ドライバ出力電流とドライバ出力高電圧の関係

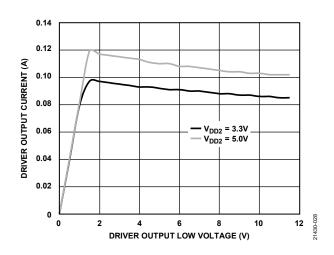

図 22. ドライバ出力電流とドライバ出力低電圧の関係

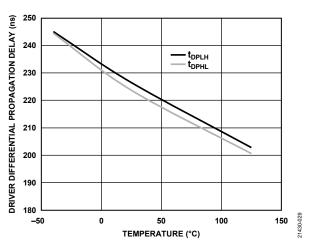

図 23. ドライバ差動伝搬遅延と温度の関係

Rev. 0 – 12/21 –

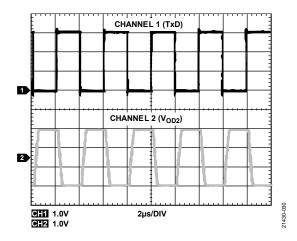

図 24. 500kbps でのドライバのスイッチング特性

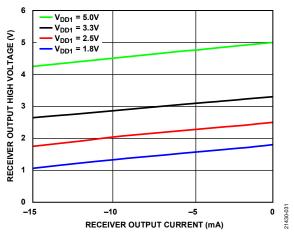

図 25. レシーバー出力高電圧とレシーバー出力電流の関係

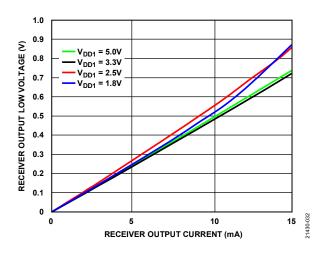

図 26. レシーバー出力低電圧とレシーバー出力電流の関係

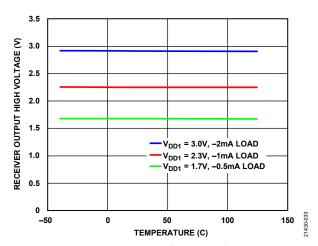

図 27. レシーバー出力高電圧と温度の関係

Rev. 0 – 13/21 –

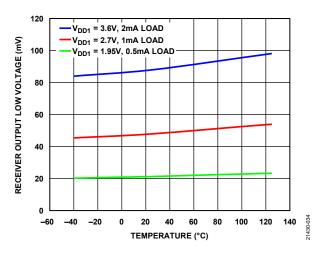

図 28. レシーバー出力低電圧と温度の関係

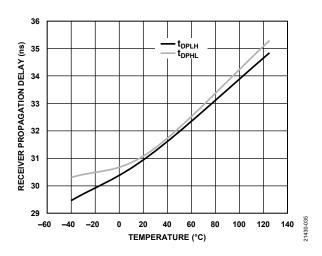

図 29. レシーバー伝搬遅延と温度の関係

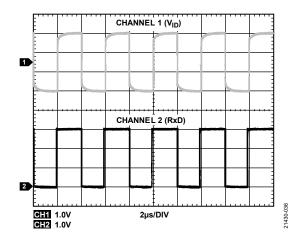

図 30. 500kbps でのレシーバーのスイッチング特性

Rev. 0 - 14/21 -

### ADM2461E/ADM2463E

### テスト回路とスイッチング特性

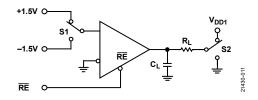

図 31. ドライバ電圧の測定、|V<sub>OD2</sub>|

図 32. コモンモード範囲でのドライバ電圧の測定、|VoD3|

図 33. ドライバの伝搬遅延測定 (タイミング図については図3を参照)

図 34. ドライバのイネーブル/ディスエーブルのタイミング測定 (タイミング図については図 5 を参照)

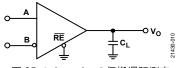

図35. レシーバーの伝搬遅延測定 (タイミング図については図4を参照)

図 36. レシーバーのイネーブル/ディスエーブルの タイミング測定 (タイミング図については図 6 を参照)

図 37. CMTI テスト回路図、半二重

図 38. CMTI テスト回路図、全二重

Rev. 0 – 15/21 –

### 動作原理

### 堅牢な低消費電力デジタル・アイソレータ

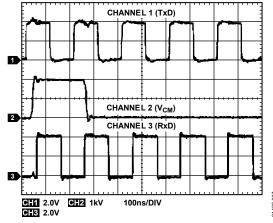

ADM2461E/ADM2463E は低消費電力のデジタル・アイソレータ・ブロックを備え、デバイスの一次側と二次側のガルバニック絶縁を提供します。共平面型トランス・コイルとオン・オフ・キーイング変調スキームを使用することで、放射エミッションを最小限に抑えながら絶縁バリアを介した高いデータ・スループットが可能です。このアーキテクチャにより、デバイスの全温度範囲と全電源電圧範囲にわたって  $250 \mathrm{kV/\mu s}$  を超えるコモンモード・トランジェントに対する耐性を備えた、堅牢なデジタル・アイソレータが実現されています。デジタル・アイソレータ回路は、入力電圧範囲が  $1.7 \mathrm{V} \sim 5.5 \mathrm{V}$  の柔軟性のある  $\mathrm{V}_{\mathrm{DDI}}$  電源を備えています。

図 39. 250kV/µs を超えるコモンモード・トランジェントの下でも 正確なスイッチング機能

### 高いドライバ差動出力電圧

ADM2461E/ADM2463E は、低インピーダンスのドライバ出力を備え差動出力電圧を増大させることができる、独自のトランスミッタ・アーキテクチャが特長です。このアーキテクチャは、伝送ラインの DC 抵抗が信号減衰の主な要因となるような長いケーブルを使用する場合に、データ・レートを落としてデバイスを動作させるときに有用です。このようなアプリケーションでは、差動電圧を増加させると長いケーブルでのデバイスの伝送距離を延ばすことができます。5Vトランシーバー( $V_{DD2}>4.5V$ )として動作する場合、ADM2461E/ADM2463E は、差動出力電圧が最低 2.1V 以上という Profibus 条件を満たすことができます。

### IEC61000-4-2 ESD 保護

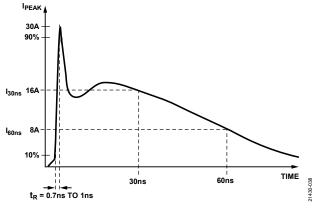

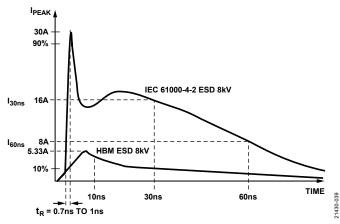

ESD とは、異なる電位を持つ物体間で静電荷が急激に移動する 現象で、近接した場合に、または電界による誘導によって発生 します。ESD が発生すると、瞬時に高電流が流れます。動作中 にシステム外部で発生する ESD 事象に対するシステムの耐性を 判断することが、IEC61000-4-2 試験の主な目的です。IEC61000-4-2 では、接触放電と気中放電の 2 つのカップリング方法を使用 した試験について説明しています。接触放電とは、放電ガンと 試験対象の装置(EUT)が直接接触することを意味します。気 中放電の試験では、放電ガンの充電された電極を EUT に向けて、 空気のギャップをまたいで円弧状に放電が発生するまで、電極 を移動します。気中放電の試験中、放電ガンは EUT とは直接接 触しません。湿度、温度、気圧、距離、EUT への接近頻度など の要因が、気中放電試験の結果や繰り返し精度に影響を与えま す。気中放電試験は、接触放電試験よりも実際の ESD 事象の発 生をより正確に再現していますが、繰り返し精度はあまり良く ありません。そのため、接触放電の方が試験方法として推奨さ れます。試験中、EUTのデータ・ポートは10回以上の正/負の 単発放電の影響を受けます。試験電圧の選択はシステム側の環 境によって決まります。図 40 に、IEC61000-4-2 の仕様に記載さ れている 8kV の接触放電の電流波形を示します。電流波形のパ ラメータには、1ns 未満の立上がり時間や約 60ns のパルス幅な どがあります。

図 40. IEC61000-4-2 ESD 波形 (8kV)

Rev. 0 – 16/21 –

図 41 では、HBM ESD 8kV の波形と IEC61000-4-2 規格の 8kV の接触放電の電流波形を比較しています。この図は、2 つの規格で仕様規定された波形の形状とピーク電流が異なることを示しています。IEC61000-4-2 の 8kV パルスの I<sub>PEAK</sub> は 30A であるのに対し、HBM ESD の I<sub>PEAK</sub> はこれの 5 分の 1 以下の 5.33A です。この他、この 2 規格の大きな違いは、初期電圧スパイクの立上がり時間です。IEC61000-4-2 の ESD 波形の立上がり時間は 1nsと、HBM ESD 波形の立上がり時間の 10ns に比べて短くなっています。IEC ESD 波形に関連付けられた電力量は、HBM ESD 波形の電力量よりも大きくなっています。HBM ESD 規格では、EUT は少なくとも 3 回にわたる正/負の放電試験が必要なのに対し、IEC ESD 規格では、少なくとも 10 回にわたる正/負の放電試験が必要です。電試験が必要です。

ADM2461E/ADM2463E は、IEC61000-4-2 規格に従い、RS-485 バス・ピン (A、B、Y、Z) と GND $_2$  ピンの間で、 $\pm$ 12kV 以上の接触 ESD 保護と $\pm$ 15kV 以上の気中 ESD 保護が定格となっています。絶縁バリアは、バス・ピンと GND $_1$  の間で $\pm$ 8kV の接触放電の保護が可能です。IEC61000-4-2 の ESD 定格に対応するこれらのデバイスは、様々なレベルの HBM ESD 保護機能を備えた他の RS-485 トランシーバーよりも、過酷な環境での動作に適しています。

図 41. IEC61000-4-2 ESD 8kV 波形と HBM ESD 8kV 波形の比較

#### 真理値表

表 14 および表 15 は、表 13 に定義した略語を使用しています。  $V_{DDI}$  は、DE ピン、TxD ピン、 $\overline{RE}$ ピン、RxD ピン、INV ピン、INVR ピンにのみ給電します。

表 13. 真理値表の略語

| Letter | Description          |

|--------|----------------------|

| Н      | High level           |

| I      | Indeterminate        |

| L      | Low level            |

| X      | Any state            |

| Z      | High impedance (off) |

表 14. 転送の真理値表

| Supply Status |           | Inputs |     |     | Outputs |        |

|---------------|-----------|--------|-----|-----|---------|--------|

| $V_{DD1}$     | $V_{DD2}$ | DE     | TxD | INV | A or Y  | B or Z |

| On            | On        | Н      | Н   | L   | Н       | L      |

| On            | On        | Н      | Н   | Н   | L       | Н      |

| On            | On        | Н      | L   | L   | L       | Н      |

| On            | On        | Н      | L   | Н   | Н       | L      |

| On            | On        | L      | X   | X   | Z       | Z      |

| Off           | On        | X      | X   | X   | Z       | Z      |

| X             | Off       | X      | X   | X   | Z       | Z      |

表 15. 受信の真理値表

|           | oply<br>itus | Inputs                   |                |    | Outputs |

|-----------|--------------|--------------------------|----------------|----|---------|

| $V_{DD1}$ | $V_{DD2}$    | A – B                    | INV or<br>INVR | RE | RxD     |

| On        | On           | ≥-0.03 V                 | L              | L  | Н       |

| On        | On           | ≤0.03 V                  | Н              | L  | Н       |

| On        | On           | ≤-0.2 V                  | L              | L  | L       |

| On        | On           | ≥0.2 V                   | Н              | L  | L       |

| On        | On           | 0.2 V < A – B < –0.03 V  | L              | L  | I       |

| On        | On           | 0.03  V < A - B < 0.2  V | Н              | L  | I       |

| On        | On           | Inputs open or shorted   | L              | L  | Н       |

| On        | X            | X                        | X              | Н  | Z       |

| On        | Off          | X                        | X              | L  | I       |

| Off       | X            | X                        | X              | X  | I       |

#### レシーバーのフェイルセーフ

ADM2461E/ADM2463E は、すべてのドライバが無効になった状 態でレシーバー入力が短絡、オープン、または終端された伝送 ラインに接続されている場合に、ロジック・ハイのレシーバー 出力を確保します。レシーバーの反転機能が無効になっている (INV または INVR = 0V) 場合にフェイルセーフのロジック・ ハイ出力を行うために、レシーバー入力閾値は-30mV~ -200mV となるよう内部で設定されています。A-B≥-30mV の 場合、RxD 出力はロジック・ハイになります。 $A - B \le -200 \text{mV}$ の場合、RxD 出力はロジック・ローになります。レシーバーの 反転機能が有効になっている (INV または INVR = VDDI) 場合に フェイルセーフ機能を保持するために、反転レシーバー入力閾 値は 30mV~200mV となるよう内部で設定されています。すべ てのトランスミッタをディスエーブルにした状態でバスが終端 処理されている場合、終端抵抗によってレシーバーの差動入力 電圧はOVになり、RxD出力は30mVの最小ノイズ・マージンで ロジック・ハイになります。この機能により、フェイルセーフ 機能を実装する場合に通常必要となる外付けバイアス部品が不 要になります。

この機能は外付けのフェイルセーフ・バイアス構成と完全互換で、フェイルセーフ機能をサポートしていない従来デバイスを使用するアプリケーションや、更なるノイズ・マージンが必要なアプリケーションで用いることができます。外付けのフェイルセーフ・バイアスについての詳細は、AN-960アプリケーション・ノート、RS-485/RS-422回路の実装ガイドを参照してください。

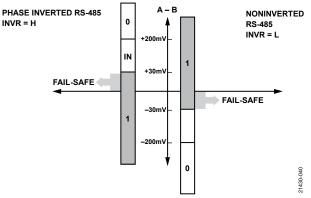

### ドライバおよびレシーバーのケーブル反転

ADM2461E/ADM2463E は、ケーブル反転機能を備えており、取り付け時の誤りを修正できます。この調整は、RS-485 トランシーバーをドライブするコントローラのソフトウェアで実行できるため、配線ミスを修正するための取り付けコストを削減できます。ADM2463E 全二重トランシーバーは、レシーバー・ケーブル反転ピン(INVR)を備えており、AピンとBピンのケーブル接続を逆にしてしまった場合にレシーバー機能を修正するために使用できます。ADM2461E 半二重トランシーバーは、1本のケーブル反転ロジック入力ピン(INV)を備えており、ドライバとレシーバーを反転することで、AピンとBピンの逆ケーブル接続を修正できます。レシーバーが反転している場合、入力が短絡またはオープン・サーキットになると、デバイスは30mVのノイズ・マージンでロジック1のレシーバー出力を維持します。図 42 に反転の場合と非反転の場合のレシーバー出力を

図 42. 非反転 RS-485 と位相反転 RS-485 の比較

### ホット・スワップ入力

回路基板が電源投入された(つまりホット)バックプレーンに挿入されると、デジタル入力に対し電源レールおよびグラウンド・レールからの寄生カップリングが発生する可能性があります。ADM2461E/ADM2463E には、電源オン時に RS-485 ドライバ出力が高インピーダンス状態を維持し、その後適切なデフォルト状態になるようにする回路が組み込まれています。例えば、 $V_{DDI}$  と  $V_{DD2}$  が同時に電源オンになり、REピンがロー、DE および TxD ピンがハイになると、A および B 出力は、A ピンの予想されるデフォルトのローにセトリングするまで、高インピーダンス状態を維持します。

### バス上で 192 台のトランシーバー

標準的な RS-485 のレシーバー入力インピーダンスは、 $12k\Omega$  (1 ユニット負荷) です。標準ドライバでは、最大 32 ユニット負荷を駆動できます。ADM2461E/ADM2463E トランシーバーは 1/6 ユニット負荷のレシーバー入力インピーダンス( $72k\Omega$  に相当)を備えているので、192 個のトランシーバーを 1 本の通信ラインに並列で接続できます。ユニット負荷の合計が 32 以下の範囲で、これらのデバイスと他の RS-485 トランシーバーを自由に組み合わせてラインに接続できます。

### ドライバ出力保護

ADM2461E/ADM2463E は、故障やバスの競合で発生する過度な出力電流と消費電力を防ぐ方法を 2 通り備えています。出力段における電流制限の保護機能を備えているので、コモンモード電圧範囲全体で短絡から即座に保護されます。更に、サーマル・シャットダウン回路は、ダイ温度が大幅に上昇した場合に、ドライバ出力を強制的に高インピーダンス状態に移行します。この回路は、ダイの温度が 150℃ に達すると、ドライバ出力をディスエーブルします。デバイスの温度が下がると、ドライバは 140℃で再度イネーブルになります。

Rev. 0 — 18/21 —

### アプリケーション情報

### PCB レイアウトおよび電磁場干渉 (EMI)

ADM2461E/ADM2463E は、低消費電力のオン・オフ・キーイング・エンコーディング・スキームを採用し、放射エミッションを最小限に抑えながら堅牢な通信を可能にしています。これらのデバイスは、標準的な 2 層 PCB で EN55032 および CISPR 32 クラス B の条件に余裕を持って適合しており、複雑で面積を縮小することに注力したレイアウト手法は不要です。

### 最大データ・レートと周囲温度の関係

大電流負荷の下では、シリコンのジャンクション温度を 150℃ 未満に保ちながら実現可能な最高周囲温度は、トランシーバー内の消費電力によって制限される場合があります。この内部消費電力は、電源電圧構成、スイッチング周波数、RS-485 バスの実効負荷、トランシーバーが送信モードにある合計時間など、アプリケーション条件に関係します。熱性能もシステムの PCB 設計や熱特性によって異なります。

$5V\pm10\%$ の  $V_{DD2}$  電源で動作する全負荷 RS-485 バス( $54\Omega$  のバス抵抗に相当)で、85% を超える高温のアプリケーションの場合、トランスミッタのデータ・レートを 300kbps に制限することを推奨します。パッケージの熱抵抗( $\theta$  JA)と  $V_{DD2}$  電源電流の代表的な性能曲線を併用することで、特定の周囲温度での最大データ・レートを計算できます。

### 絶縁型 Profibus ソリューション

ADM2461E は、絶縁型 Profibus ノードの条件を満たすトランシーバーが特長です。ADM2461E を Profibus トランシーバーとして動作させる場合、 $V_{DD2}$ 電源が 4.5V 以上となるようにしてください。ADM2461E が Profibus アプリケーションで使用できるのは、次のような特性の結果です。

- 出力ドライバは、Profibus の差動出力条件以上を出力します。トランスミッタの差動出力がいかなる場合にも 7V p-p を超えないようにするために、A および B のトランスミッタ出力に 10Ω の抵抗を直列接続してください。

- バス・ピン容量が 28pF と低容量です。

- Profibus シールド・ケーブルを使用し、GND₂ピンを基準に 最大±1kVの IEC61000-4-4 電気的高速トランジェント (EFT) に対するクラス I (データ損失なし) 耐性が実現可能です。GND₁ピンと RxD 出力ピンの間に 470pF のコンデンサを追加接続すると、最大±3kVの IEC 61000-4-4 クラス I が実現できます。

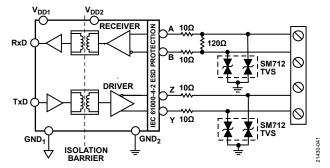

### EMC、EFT、サージ保護

IEC61000-4-5 の EFT 事象や IEC61000-4-4 のサージ事象に対する 保護レベルを上げる必要のあるアプリケーションでは、外部保護回路を追加するとデバイスの EMC 堅牢性を強化できます。推奨される EMC 保護回路については図 43 を参照してください。この回路では、一連の SM712 電圧トランジェント圧縮(TVS)と  $10\Omega$  の耐パルス抵抗を使用して、レベル 2 の IEC61000-4-5 サージ保護とレベル4を上回る IEC61000-4-2 ESD および IEC61000-4-4 EFT 保護を実現しています。表 16 と表 17 は、推奨する保護 部品とこの回路の保護レベルを示します。

図 43. ESD、EFT、サージ保護を備えた 絶縁型 RS-485 ソリューション

表 16. ESD、EFT、サージ保護ソリューション用の推奨部品

| Recommended Components            | Part Number        |

|-----------------------------------|--------------------|

| TVS                               | CDSOT23-SM712      |

| $10 \Omega$ Pulse Proof Resistors | CRCW060310R0FKEAHP |

表 17. 推奨回路を使用した場合の保護レベル

| EMC Standard                | Protection Level (kV)  |

|-----------------------------|------------------------|

| ESD—Contact (IEC 61000-4-2) | ≥±30 (exceeds Level 4) |

| ESD—Air (IEC 61000-4-2)     | ≥±30 (exceeds Level 4) |

| EFT (IEC 61000-4-4)         | ≥±4 (exceeds Level 4)  |

| Surge (IEC 61000-4-5)       | $\geq \pm 1$ (Level 2) |

| -                           | -                      |

#### 絶縁寿命

すべての絶縁構造は、十分長い時間にわたり電圧ストレスを加 えると、最終的には破壊されます。絶縁性能の低下率は、絶縁 体に加える電圧波形の特性と材料自体や材料の境界面に依存し ます。

絶縁劣化には、空気にさらされる表面に沿った破壊と絶縁疲労という注目すべき 2 つのタイプがあります。表面の破損は表面トラッキング現象で、システム・レベルの規格に定められた沿面距離条件を決定する主要な要素となります。絶縁疲労とは、チャージ・インジェクションまたは絶縁材料内部の変位電流により、長時間にわたり絶縁の劣化が生じる現象です。

Rev. 0 – 19/21 –

#### 表面トラッキング

表面トラッキングは電気安全規格に規定されており、動作電圧、環境条件、絶縁材料の特性に基づいて最小沿面距離を定めることによって決定されます。安全性規制当局は、部品の表面絶縁について特性評価テストを行い、部品を様々な材料グループに分類しています。材料グループ等級が低いものほど表面トラッキングに対する耐性が高く、短い沿面距離で十分に長い寿命を実現できます。特定の動作電圧と材料グループに対する最小沿面距離は、各システム・レベル規格の範囲内にあります。この値は、絶縁をまたぐ合計実効値電圧、汚染度、材料グループに基づいています。ADM2461E/ADM2463E 絶縁型 RS-485 トランシーバーの材料グループおよび沿面距離の情報については、表5を参照してください。

#### 絶縁疲労

疲労による絶縁寿命は、絶縁体の厚さ、材料特性、絶縁体に加わる電圧ストレスによって決まります。アプリケーションの動作電圧での製品寿命が十分であることを確認してください。アイソレータがサポートしている耐疲労動作電圧は、耐トラッキング動作電圧と異なる場合があります。トラッキングに該当する動作電圧は、ほとんどの規格で仕様規定されています。

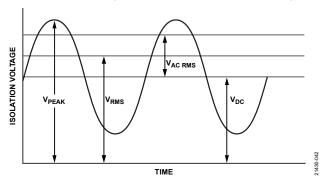

試験とモデリングにより、長期間にわたる性能低下の主な要因は、増分型の損傷を引き起こすポリイミド絶縁体内の変位電流であることが判明しています。絶縁体にかかるストレスは、DCストレスや、時間変動する電圧ストレスのAC成分など、幅広い分類が可能です。DCストレスは変位電流がないため、絶縁疲労の原因になることはほとんどありません。時間変動する電圧ストレスのAC成分が絶縁疲労を引き起こします。

通常、認定文書に記載されている定格は、60Hz のサイン波ストレスに基づいています。このストレスには、ライン電圧からの絶縁が反映されることが理由です。ただし、多くの実用的なアプリケーションでは、バリアをまたぐ60Hz の AC 電圧と DC 電圧の組み合わせが使用されます(式 1 を参照)。ストレスを受ける AC 部分のみが疲労を発生させるため、AC 実効値電圧を求めるように式を組み替えることができます(式 2 を参照)。これらの製品で使用されるポリイミド材料の絶縁疲労については、AC 実効値電圧が製品寿命を決定します。

$$V_{RMS} = \sqrt{V_{AC RMS}^2 + V_{DC}^2}$$

(1)

または

$$V_{AC\ RMS} = \sqrt{{V_{RMS}}^2 - {V_{DC}}^2} \tag{2}$$

ここで、

$V_{RMS}$ は、合計 rms 動作電圧。  $V_{AC\;RMS}$ は、動作電圧の時間と共に変化する部分。  $V_{DC}$ は、動作電圧の DC オフセット。

#### 計算とパラメータ使用の例

一般的な電力変換アプリケーションの例を以下に示します。絶縁バリアの一方に AC 実効値が 240V のライン電圧が存在し、他方に 400V dc のバス電圧が存在するとします。絶縁材料はポリイミドです。デバイスの沿面距離、クリアランス、および寿命を求める際のクリティカル電圧を決めるには、図 44、式 3、式 4 を参照してください。ここで、 $V_{PEAK}$  はピーク電圧です。

図 44. クリティカル電圧の例

この例では、式1の $V_{RMS}$ は次のように求まります。

$$V_{RMS} = \sqrt{240^2 + 400^2} = 466V \tag{3}$$

この  $V_{RMS}$  値は、システムの規格で要求される沿面距離を求める際に、材料グループおよび汚染度と組み合わせて使用する動作電圧です。

寿命が適切であるかどうかを判定するには、V<sub>AC RMS</sub>を求めます。 この例では、式2を使用して次のようにV<sub>AC RMS</sub>を計算します。

$$V_{AC\,RMS} = \sqrt{466^2 - 400^2} = 240 \text{V rms} \tag{4}$$

この場合、AC 実効値電圧は 240V rms のライン電圧です。この計算は、波形がサイン波でない場合は更に意義のあるものとなります。VACRMSの値を、予想寿命(60Hzサイン波の場合よりも短い)に対する表 10の AC 動作電圧の制限値と比較すると、50年のサービス寿命に対する制限値の範囲内に十分入っています。

DC 動作電圧の制限値は、IEC60664-1 で規定されているように、パッケージの沿面距離によって定められています。この DC 値は、特定のシステム・レベルの規格によって異なる場合があります。

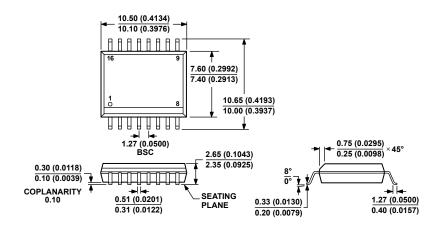

### 外形寸法

COMPLIANT TO JEDEC STANDARDS MS-013-AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

図 45. 16 ピン、標準 SOP(スモール・アウトライン・パッケージ) [SOIC\_W] ワイド・ボディ(RW-16)

寸法:mm (括弧内はインチ)

### オーダー・ガイド

| Model <sup>1</sup> | Data Rate (Mbps) | Duplex | Temperature Range | Package Description          | Package Option |

|--------------------|------------------|--------|-------------------|------------------------------|----------------|

| ADM2461EBRWZ       | 0.5              | Half   | -40°C to +125°C   | 16-Lead SOIC_W               | RW-16          |

| ADM2461EBRWZ-R7    | 0.5              | Half   | -40°C to +125°C   | 16-Lead SOIC_W               | RW-16          |

| ADM2463EBRWZ       | 0.5              | Full   | −40°C to +125°C   | 16-Lead SOIC_W               | RW-16          |

| ADM2463EBRWZ-RL7   | 0.5              | Full   | -40°C to +125°C   | 16-Lead SOIC_W               | RW-16          |

| EVAL-ADM2461EEBZ   |                  |        |                   | Half-Duplex Evaluation Board |                |

| EVAL-ADM2463EEBZ   |                  |        |                   | Full Duplex Evaluation Board |                |

<sup>&</sup>lt;sup>1</sup> Z = RoHS 準拠製品。

Rev. 0 — 21/21 —