# ゲイン範囲 30dB ステップ・サイズ 1dB の 1.0GHz DGA

データシート ADL5206

#### 特長

デジタル制御方式の VGA ゲイン範囲:2dB~32dB ゲイン・ステップ・サイズ:1dB

差動入力抵抗:100Ω差動出力抵抗:10Ω

ノイズ指数: 5.1dB (300MHz、5V 電源、最大ゲイン時)

最大ゲイン時の OIP3:

39.4dBm (300MHz、5V 電源時) 38.1dBm (700MHz、5V 電源時) ゲイン・ステップ精度: ±0.2dB

32dB 時の-3dB 帯域幅: 1.0GHz(代表値) (5V 電源時)

複数の制御インターフェース・オプション

パラレル 5 ビット制御インターフェース(ラッチ付き)

3 線式および 4 線式 SPI (高速アタック付き) ゲイン・ステップアップ/ステップダウン・

インターフェース

広い入力ダイナミック・レンジ

パワーダウン制御

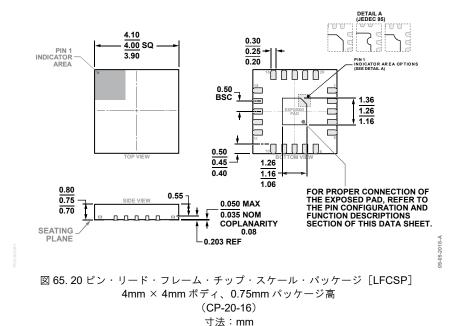

3.3V または 5V の単電源動作 静止電流: 112mA (5V 電源時) 20 ピン、4 mm × 4 mm LFCSP

#### アプリケーション

差動 ADC ドライバ 高中間周波数(IF)サンプリング・レシーバー 高出力電力の IF 増幅 DOCSIS FDx アップストリーム・アンプ 計測器

#### 概要

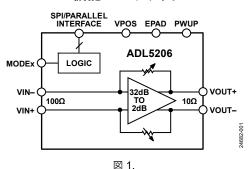

ADL5206 は、デジタル制御方式の広帯域幅、可変ゲイン・アンプ (VGA) (デジタル・ゲイン・アンプ (DGA) とも呼ばれる)で、全ゲイン範囲にわたって、高精度のゲイン制御、高出力 3 次インターセプト (OIP3) 、および低ノイズ指数を実現します。ADL5206 は、OIP3 性能が 39.4dBm (300MHz、5V 電源、最大ゲイン時)と優れているため、各種のレシーバー・アプリケーションにおけるゲイン制御デバイスに最適です。

入力ダイナミック・レンジの広いアプリケーションに対して、ADL5206 は 1dB のステップ・サイズで 2dB~32dB という広いゲイン範囲を実現します。このゲインは、パラレル・インターフェース、シリアル・ペリフェラル・インターフェース (SPI)、またはゲイン・ステップアップ/ステップダウン制御という複数のゲイン制御およびインターフェースのオプションによって調整することができます。

適切なロジック・レベルを PWUP ピンに加えることによって、ADL5206 は他と関係なくパワーアップすることができます。

#### 機能ブロック図

ADL5206 の静止電流は、5V 電源の場合に 112mA (代表値)です。ディスエーブル時に、ADL5206 はわずか 8mA しか消費しないため、入出力間で優れたアイソレーションを確保できます。このデバイスがディスエーブルされているとき、ゲインの設定値は維持されます。

ADL5206 は、アナログ・デバイセズの高速、シリコン・ゲルマニウム(SiGe)、バイポーラ相補型金属酸化膜半導体(BiCMOS)プロセスで製造されているため、優れた歪み性能と共に正確なゲイン調整能力を備えています。ADL5206 アンプは、小型、熱強化型の  $4 \text{mm} \times 4 \text{mm}$ 、20 ピン LFCSP で提供され、 $-40^{\circ}\text{C}\sim+85^{\circ}\text{C}$  の温度範囲で動作します。

このデータシートでは、CS/GS1/D3 などの多機能ピンについて、 ピン名全体を表記する場合と、ピンが持つ機能の 1 つを表記す る場合があることに注意してください。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって 生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示 的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有 者の財産です。※日本語版資料はREVISION が古い場合があります。最新の内容については、英語版をご参照ください。

©2020 Analog Devices, Inc. All rights reserved.

Rev. 0

本 社/〒105-6891

東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 10F 雷話 03 (5402) 8200

大 阪営業所/〒532-0003

大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 10F電話 06 (6350) 6868

名古屋営業所/〒451-6038

愛知県名古屋市西区牛島町 6-1 名古屋ルーセントタワー 38F 電話 052 (569) 6300

# 目次

| 特長             | 1  |

|----------------|----|

| アプリケーション       |    |

|                |    |

| 概要             |    |

| 改訂履歴           |    |

| 仕様             |    |

| <br>タイミング仕様    |    |

| <b>絶対最大定格</b>  |    |

| 熱抵抗            |    |

| 接合部と基板間の熱抵抗    |    |

| ESD に関する注意     |    |

| ピン配置およびピン機能の説明 |    |

| 代表的な性能特性       |    |

| 動作原理           | 19 |

| 基本構成             | 19 |

|------------------|----|

| 制御およびロジック回路      | 19 |

| コモンモード電圧         | 19 |

| レジスタの一覧と詳細       | 20 |

| アプリケーション情報       | 21 |

| 基本的な接続方法         | 21 |

| デジタル・インターフェースの概要 | 22 |

| <b>SPI</b> での読出し | 23 |

| ADC とのインターフェーシング | 24 |

| ノイズ指数とゲイン設定値の関係  | 24 |

| 外形寸法             | 25 |

| オーダー・ガイド         | 25 |

### 改訂履歴

9/2020—Revision 0: Initial Version

## 仕様

特に指定のない限り、 $T_A=25^{\circ}$ C、負荷インピーダンス( $Z_{LOAD}$ )=  $100\Omega$ 、最大ゲイン(ゲイン・コード=00000)、周波数= 300 MHz、および、2V p-p の差動出力。

#### 表 1.

|                                         |                                                                 |         | 3.3V 電源 | 東 <sup>1</sup> |     | 5V 電源  | 1   |        |

|-----------------------------------------|-----------------------------------------------------------------|---------|---------|----------------|-----|--------|-----|--------|

| パラメータ <sup>2</sup>                      | テスト条件/コメント                                                      | Min     | Тур     | Max            | Min | Тур    | Max | 単位     |

| DYNAMIC PERFORMANCE                     |                                                                 |         |         |                |     |        |     |        |

| −3 dB Bandwidth                         | 20dB の場合                                                        |         | 1.7     |                |     | 1.6    |     | GHz    |

|                                         | 25dB のとき                                                        |         | 1.4     |                |     | 1.3    |     | GHz    |

|                                         | 32dB のとき                                                        |         | 1.2     |                |     | 1.0    |     | GHz    |

| Slew Rate                               |                                                                 |         | 4.3     |                |     | 4.3    |     | V/ns   |

| INPUT STAGE                             | VIN+ピンおよび VIN-ピン                                                |         |         |                |     |        |     |        |

| Maximum Input Swing <sup>3</sup>        | ゲイン・コード = 11111                                                 |         | 4       |                |     | 6.2    |     | V p-p  |

| Differential Input Resistance           |                                                                 |         | 100     |                |     | 100    |     | Ω      |

| Input Common-Mode Voltage               |                                                                 |         | 1.65    |                |     | 2.5    |     | V      |

| Common-Mode Rejection Ratio (CMRR)      |                                                                 |         | 56      |                |     | 56     |     | dB     |

| GAIN                                    |                                                                 |         |         |                |     |        |     |        |

| Voltage Gain Range                      |                                                                 |         | 30      |                |     | 30     |     | dB     |

| Maximum Gain                            | ゲイン・コード=00000                                                   |         | 32      |                |     | 32     |     | dB     |

| Minimum Gain                            | ゲイン・コード = 11110~11111                                           |         | 2       |                |     | 2      |     | dB     |

| Gain Step Size                          |                                                                 |         | 1       |                |     | 1      |     | dB     |

| Gain Step Accuracy                      |                                                                 |         | ±0.2    |                |     | ±0.2   |     | dB     |

| Gain Flatness                           | 30MHz~700MHz                                                    |         | 0.2     |                |     | 0.2    |     | dB p-p |

| Gain Temperature Sensitivity            | ゲイン・コード = 00000、<br>700MHz の場合                                  | 0000, 3 |         |                |     | mdB/°C |     |        |

| Fast Attack Step Response Delay         | 入力電圧 $(V_{IN}) = 0.1V$ の場合、 $16dB$ のステップで $FA$ を $0$ から $1$ に変化 |         | 5       |                |     | 5      |     | ns     |

| COMMON-MODE INPUTS                      |                                                                 |         |         |                |     |        |     |        |

| VCM Pin Input Resistance                |                                                                 |         | 2.6     |                |     | 2.6    |     | kΩ     |

| OUTPUT STAGE                            | VOUT+ピンおよび VOUT-ピン                                              |         |         |                |     |        |     |        |

| Output Voltage Swing                    | 1dB 圧縮ポイント (P1dB) 、ゲ<br>イン・コード = 00000 の場合                      |         | 4.1     |                |     | 6.25   |     | V p-p  |

| Common-Mode Voltage Reference           | VCM ピン                                                          | 1.2     | 1.65    | 1.8            | 1.4 | 2.5    | 2.7 | V      |

| Output Common-Mode Offset               | ((VOUT+)+(VOUT -))/2 - VCM/2                                    | -10     |         | +10            | -10 |        | +10 | mV     |

| Differential Output Resistance          |                                                                 |         | 10      |                |     | 10     |     | Ω      |

| Short-Circuit Current                   |                                                                 |         | 20      |                |     | 25     |     | mA     |

| NOISE AND HARMONIC PERFORMANCE          |                                                                 |         |         |                |     |        |     |        |

| 10 MHz                                  |                                                                 |         |         |                |     |        |     |        |

| Noise Figure                            |                                                                 |         | 6.2     |                |     | 6.3    |     | dB     |

| Second Harmonic Distortion (HD2)        | $V_{OUT} = 2V p-p$                                              |         | -85     |                |     | -89.2  |     | dBc    |

| Third Harmonic Distortion (HD3)         | $V_{OUT} = 2V p-p$                                              |         | -76.5   |                |     | -85.6  |     | dBc    |

| Output Second-Order Intercept (OIP2)    | V <sub>OUT</sub> = 2V p-p コンポジット                                |         | 84.3    |                |     | 87.1   |     | dBm    |

| Third Intermodulation Distortion (IMD3) | V <sub>OUT</sub> = 2V p-p コンポジット                                |         | -78.9   |                |     | -85.8  |     | dBc    |

| Output Third-Order Intercept (OIP3)     | V <sub>OUT</sub> = 2V p-p コンポジット                                |         | 39.4    |                |     | 42.9   |     | dBm    |

Rev. 0 - 3/25 -

|                    |                                       | 3.3V 電源 | 1   | 5V 電源 <sup>1</sup> |       |       |        |  |

|--------------------|---------------------------------------|---------|-----|--------------------|-------|-------|--------|--|

| パラメータ <sup>2</sup> | テスト条件/コメント                            | Min Typ | Max | Min                | Тур   | Max   | 単位     |  |

| 100 MHz            |                                       |         |     |                    |       |       |        |  |

| Noise Figure       |                                       | 5.8     |     |                    | 5.9   |       | dB     |  |

| HD2                | $V_{OUT} = 2V p-p$                    | -75.8   |     |                    | -78.4 |       | dBc    |  |

| HD3                | $V_{OUT} = 2V p-p$                    | -72.2   |     |                    | -81   |       | dBc    |  |

| OIP2               | V <sub>OUT</sub> = 2V p-p コンポジット      | 74.7    |     |                    | 76.8  |       | dBm    |  |

| IMD3               | V <sub>OUT</sub> = 2V p-p コンポジット      | -77     |     |                    | -84.8 |       | dBc    |  |

| OIP3               | V <sub>OUT</sub> = 2V p-p コンポジット      | 38.5    |     |                    | 42.4  |       | dBm    |  |

| 300 MHz            |                                       |         |     |                    |       |       |        |  |

| Noise Figure       |                                       | 4.6     |     |                    | 5.1   |       | dB     |  |

| HD2                | $V_{OUT} = 2V p-p$                    | -67.8   |     |                    | -77.6 |       | dBc    |  |

| HD3                | $V_{OUT} = 2V p-p$                    | -56.2   |     |                    | -67.9 |       | dBc    |  |

| OIP2               | V <sub>OUT</sub> = 2V p-p コンポジット      | 70.5    |     |                    | 79.5  |       | dBm    |  |

| IMD3               | V <sub>OUT</sub> = 2V p-p コンポジット      | -75     |     |                    | -78.8 |       | dBc    |  |

| OIP3               | V <sub>OUT</sub> = 2V p-p コンポジット      | 37.5    |     |                    | 39.4  |       | dBm    |  |

| 500 MHz            | * *                                   |         |     |                    |       |       |        |  |

| Noise Figure       |                                       | 4.5     |     |                    | 5     |       | dB     |  |

| HD2                | $V_{OUT} = 2V p-p$                    | -58.7   |     |                    | -65.6 |       | dBc    |  |

| HD3                | $V_{OUT} = 2V p-p$                    | -52.6   |     |                    | -66.2 |       | dBc    |  |

| OIP2               | V <sub>OUT</sub> = 2V p-p コンポジット      | 58.3    |     |                    | 65.7  |       | dBm    |  |

| IMD3               | V <sub>OUT</sub> = 2V p-p コンポジット      | -68.3   |     |                    |       | -76.6 |        |  |

| OIP3               | V <sub>OUT</sub> = 2V p-p コンポジット      | 34      |     |                    | 38.3  |       | dBm    |  |

| OP1dB              | 1001 - FF                             | 14.3    |     |                    | 18    |       | dBm    |  |

| 700 MHz            |                                       | 1.13    |     |                    | 10    |       | uDii.  |  |

| Noise Figure       |                                       | 6.7     |     |                    | 7     |       | dB     |  |

| HD2                | $V_{OUT} = 2V p-p$                    | -62.7   |     |                    | -69   |       | dBc    |  |

| HD3                | $V_{OUT} = 2V p-p$                    | -55.4   |     |                    | -77.7 |       | dBc    |  |

| OIP2               | V <sub>OUT</sub> = 2V p-p コンポジット      | 64.2    |     |                    | 67.2  |       | dBm    |  |

| IMD3               | V <sub>OUT</sub> = 2V p-p コンポジット      | -61.2   |     |                    | -76.3 |       | dBc    |  |

| OIP3               | V <sub>OUT</sub> = 2V p-p コンポジット      | 30.6    |     |                    | 38.1  |       | dBm    |  |

| 1000 MHz           | V001 2 V P P - V N V V 1              | 20.0    |     |                    | 20.1  |       | u.Diii |  |

| Noise Figure       |                                       | 7.5     |     |                    | 7.9   |       | dB     |  |

| HD2                | $V_{OUT} = 2V p-p$                    | -60.3   |     |                    | -62.5 |       | dBc    |  |

| HD3                | $V_{OUT} = 2V p-p$                    | -49     |     |                    | -61   |       | dBc    |  |

| OIP2               | V <sub>OUT</sub> = 2V p-p コンポジット      | 61.6    |     |                    | 63.3  |       | dBm    |  |

| IMD3               | V <sub>OUT</sub> = 2V p-p コンポジット      | -56.5   |     |                    | -69.1 |       | dBc    |  |

| OIP3               | V <sub>OUT</sub> = 2V p-p コンポジット      | 28.2    |     |                    | 34.5  |       | dBm    |  |

| 1200 MHz           | VOUT 2 V p-p = V X V V Y 1            | 20.2    |     |                    | 5 1.5 |       | abii   |  |

| Noise Figure       |                                       | 6.6     |     |                    | 7     |       | dB     |  |

| HD2                | $V_{OUT} = 2V p-p$                    | -53.4   |     |                    | -57.2 |       | dBc    |  |

| HD3                | $V_{OUT} = 2V p-p$ $V_{OUT} = 2V p-p$ | -44     |     |                    | -52   |       | dBc    |  |

| OIP2               | V <sub>OUT</sub> = 2V p-p コンポジット      | 53.6    |     |                    | 57.5  |       | dBm    |  |

| IMD3               | V <sub>OUT</sub> = 2V p-p コンポジット      | -54.4   |     |                    | -66.9 |       | dBc    |  |

| OIP3               | V <sub>OUT</sub> = 2V p-p コンポジット      | 27.2    |     |                    | 33.4  |       | dBm    |  |

Rev. 0 - 4/25 -

|                                    |                                      |      | 3.3V 電源 <sup>1</sup> |      |      | 5V 電源 <sup>1</sup> |      |     |  |

|------------------------------------|--------------------------------------|------|----------------------|------|------|--------------------|------|-----|--|

| パラメータ <sup>2</sup>                 | テスト条件/コメント                           | Min  | Тур                  | Max  | Min  | Тур                | Max  | 単位  |  |

| DIGITAL INTERFACE                  |                                      |      |                      |      |      |                    |      |     |  |

| Input Voltage                      | MODE1、MODE0、PWUP、<br>LATCH、SDIO の各ピン |      |                      |      |      |                    |      |     |  |

| Logic High (V <sub>IH</sub> )      |                                      | 2    |                      | VPOS | 2    |                    | 3.3  | V   |  |

| Logic Low (V <sub>IL</sub> )       |                                      | 0    |                      | 1.0  | 0    |                    | 1.0  | V   |  |

| Input Leakage Current              | デジタル V <sub>IN</sub> = 0V~3.3V       |      | $\pm 3$              |      |      | $\pm 3$            |      | μΑ  |  |

| Output Voltage                     | SDIO ピン                              |      |                      |      |      |                    |      |     |  |

| Logic High (V <sub>OH</sub> )      | 出力ハイ電流(I <sub>OH</sub> )=-2mA        | 2.4  |                      |      | 2.4  |                    |      | 2.4 |  |

| Logic Low (V <sub>OL</sub> )       | 出力ロー電流 (I <sub>OL</sub> ) = 2mA      |      |                      | 0.5  |      |                    | 0.5  |     |  |

| POWER INTERFACE                    |                                      |      |                      |      |      |                    |      |     |  |

| Supply Voltage (V <sub>POS</sub> ) | VPOS ピン                              | 3.15 | 3.3                  | 3.45 | 4.75 | 5                  | 5.25 | V   |  |

| Quiescent Current                  |                                      |      | 87                   |      |      | 112                |      | mA  |  |

| Power-Down Current                 | PWUP ヒ°ン = □ ─                       |      | 8                    |      |      | 8                  |      | mA  |  |

$<sup>^1</sup>$ 3.3V電源は低消費電力モードで、5V電源は高性能モードです。

Rev. 0 -5/25-

<sup>&</sup>lt;sup>2</sup> 仕様表において多機能ピンが持つ機能の1つを対象にしている場合は、仕様に該当するピン名の部分だけを記載しています。多機能ピンのピン名全体につ いては、ピン配置およびピン機能の説明のセクションを参照してください。

<sup>3</sup>6.2V p-p の最大入力振幅は、ゲインを最低の 2dB に設定した場合の振幅です。同じ最大出力振幅を維持するために、ゲイン設定値を増加させた分だけ最大

入力振幅を減少させる必要があります。最大出力振幅はPldBに基づいています。

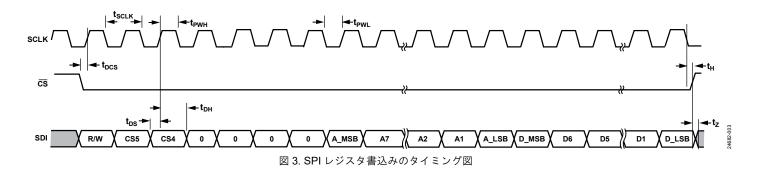

#### タイミング仕様

表 2. SPI タイミング・パラメータ

| パラメータ              | 説明                                                                 | Min | Тур | Max | 単位  |

|--------------------|--------------------------------------------------------------------|-----|-----|-----|-----|

| $f_{SCLK}$         | 最大シリアル・クロック・レート、1/t <sub>SCLK</sub> (t <sub>SCLK</sub> は SCLK の時間) |     | 25  |     | MHz |

| $t_{\mathrm{PWH}}$ | SCLK をロジック・ハイの状態に保持する最小時間                                          |     | 10  |     | ns  |

| $t_{\mathrm{PWL}}$ | SCLK をロジック・ローの状態に保持する最小時間                                          |     | 10  |     | ns  |

| $t_{DS}$           | データから SCLK の立上がりエッジまでのセットアップ時間                                     |     | 5   |     | ns  |

| $t_{\mathrm{DH}}$  | データから SCLK の立上がりエッジまでのホールド時間                                       |     | 5   |     | ns  |

| $t_{DCS}$          | ─Sの立下がりエッジから SCLK の立上がりエッジまでのセットアップ時間                              |     | 10  |     | ns  |

| $t_{\rm H}$        | CSの立上がりエッジから最後の SCLK の立下がりエッジまでのホールド時間                             |     | 10  |     | ns  |

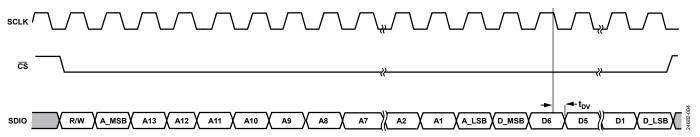

| $t_{\rm DV}$       | SCLK の立下がりエッジから出力データが読出し可能になるまでの最大時間遅延                             |     | 5   | 14  | ns  |

| $t_z$              | CSの非アクティブから SDIO バスがハイ・インピーダンスに戻るまでの最大時間遅延                         |     |     | 12  | ns  |

#### タイミング図

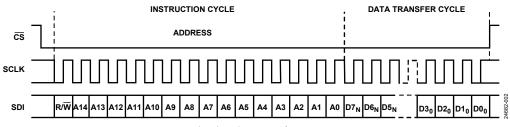

図 2. SPI レジスタのタイミング、MSB ファースト

図 4. SPI レジスタ読出しのタイミング図

Rev. 0 - 6/25 -

### 絶対最大定格

表 3.

| Parameter <sup>1</sup>                                    | Rating           |

|-----------------------------------------------------------|------------------|

| Differential Output Voltage Swing × Bandwidth             |                  |

| Product                                                   |                  |

| 5 V Supply Voltage                                        | 4 V-GHz          |

| 3.3 V Supply Voltage                                      | 3 V-GHz          |

| Supply Voltage, V <sub>POS</sub>                          | 5.4 V            |

| PWUP, D0 to D4, MODE0, MODE1, LATCH                       | -0.5 V to +3.6 V |

| Input Voltage (VIN+ and VIN-)                             | -0.5 V to +3.1 V |

| Differential Input Voltage <sup>2</sup> ((VIN+) - (VIN-)) | ±1 V             |

| Internal Power Dissipation (P <sub>DISS</sub> )           | 500 mW           |

| Temperature                                               |                  |

| Maximum Junction                                          | 135°C            |

| Operating Range                                           | −40°C to +85°C   |

| Storage Range                                             | −65°C to +150°C  |

「パラメータにおいて多機能ピンの持つ機能の1つを対象にしている場合は、仕様に該当するピン名の部分だけを記載しています。多機能ピンのピン名全体については、ピン配置およびピン機能の説明のセクションを参照してください。

<sup>2</sup> 差動入力電圧制限は、5V 電源での最大入力振幅 6.2V p-p より大幅に低い値になっています。最大入力振幅は、ゲインを最低の 2dB に設定した場合の振幅です。同じ最大出力振幅を維持するために、ゲイン設定値を増加させた分だけ最大入力振幅を減少させる必要があります。最大出力振幅は P1dB に基づいています。

上記の絶対最大定格を超えるストレスを加えると、デバイスに 恒久的な損傷を与えることがあります。この規定はストレス定 格のみを指定するものであり、この仕様の動作のセクションに 記載する規定値以上でのデバイス動作を定めたものではありま せん。デバイスを長時間にわたり絶対最大定格状態に置くと、 デバイスの信頼性に影響を与えることがあります。

#### 熱抵抗

熱性能は、プリント回路基板 (PCB) の設計と動作環境に直接 関連しています。PCB の熱設計には、細心の注意を払う必要が あります。

表 4 に、ダイと周囲間の熱抵抗( $\theta_{IA}$ )、ダイと基板間の熱抵抗 ( $\theta_{IB}$ )、およびダイとリード間の熱抵抗( $\theta_{IC}$ )を示します。

表 4. 熱抵抗

| Package Type | $\theta_{JA}$ | $\theta_{JB}$ | $\theta_{JC}$ | Unit |

|--------------|---------------|---------------|---------------|------|

| CP-20-16     | 55.42         | 16.01         | 9.08          | °C/W |

#### 接合部と基板間の熱抵抗

ダイ接合部と基板間の熱抵抗  $(\theta_{IB})$  は、ADL5206 のダイとリードとの間の熱抵抗です。表 4 に示す値は、表面実装部品の熱試験を対象とした JESD51-7 規格に記載された標準的な PCB に基づいています。PCB のサイズと複雑さ(層数)が  $\theta_{IB}$ に影響を及ぼし、層数が増加すると熱抵抗がわずかに減少する傾向にあります。

PCB の温度 (T<sub>B</sub>) が分かる場合は、ダイの温度が仕様で制限されている 135℃ を絶対に超えないようにするために、接合部と基板間の熱抵抗を使用してダイの温度 (ジャンクション温度 T<sub>J</sub> とも呼ばれる) を計算します。例えば、PCB の温度が 85℃ の場合、ダイの温度は次式で与えられます。

$T_J = T_B + (P_{DISS} \times \theta_{JB})$

ADL5206 における最も厳しい  $P_{DISS}$  は 500mW に仕様規定されています (5.0V × 110mA、表 3 を参照)。したがって、 $T_{I}$ は次式のように求められます。

$T_J = 85^{\circ}\text{C} + (0.499 \text{ W} \times 24.4^{\circ}\text{C/W}) = 97.2^{\circ}\text{C}$

#### ESD に関する注意

電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術であるESD保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

ESD(静電放電)の影響を受けやすいデバイスです。

Rev. 0 - 7/25 -

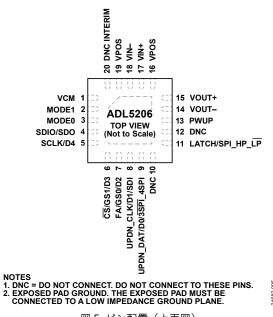

# ピン配置およびピン機能の説明

図 5. ピン配置(上面図)

表 5. ピン機能の説明

| ピン番号   | 記号                    | 説明                                                                                                                                                                                                                                                                                                                                                            |

|--------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | VCM                   | コモンモード出力。                                                                                                                                                                                                                                                                                                                                                     |

| 2      | MODE1                 | モード制御用の MSB。MODE0 ピンと MODE1 ピンの両方を使用して、高性能または低消費電力の、パラレル、SPI、またはアップ/ダウンの各インターフェース・モードを選択します。                                                                                                                                                                                                                                                                  |

| 3      | MODE0                 | モード制御用の LSB。MODE1 ピンと MODE0 ピンの両方を使用して、パラレル、SPI、または UPDN の各モード を選択します。                                                                                                                                                                                                                                                                                        |

| 4      | SDIO/SDO              | 3 線式 SPI モードの場合のシリアル・データ入出力(SDIO)。4 線式 SPI モードの場合のシリアル・データ出力<br>(SDO)。                                                                                                                                                                                                                                                                                        |

| 5      | SCLK/D4               | シリアル・クロック入力/デジタル・ビット 4。MODE0 ピンと MODE1 ピンの選択に応じて、このピンは 2 つの機能を果たします。シリアル、つまり SPI モードの場合、このピンは SCLK として機能します。パラレル・モードの場合、このピンはパラレル・ゲイン制御インターフェース内の D4 になります。                                                                                                                                                                                                   |

| 6      | CS/GS1/D3             | チップ・セレクト(アクティブ・ロー)/ゲイン・ステップ 1/デジタル・ビット 3。MODE0 ピンと MODE1 ピンの選択に応じて、このピンは 3 つの機能を果たします。シリアル、つまり SPI モードの場合、このピンは CSになります。UPDN モードの場合、このピンはゲイン・ステップ・サイズの MSB を制御する GS1 機能として有効になります。パラレル・モードの場合、このピンはパラレル・ゲイン制御インターフェース内の D3 になります。                                                                                                                             |

| 7      | FA/GS0/D2             | 高速アタック/ゲイン・ステップ 0/デジタル・ビット 2。MODE0 ピンと MODE1 ピンの選択に応じて、このピンは 3 つの機能を果たします。シリアル、つまり SPI モードの場合、このピンの FA 機能が有効になります。FA 機能を用いると、デジタル・ゲイン制御設定値以内で減衰量を大幅に増加させるための定義ができます。ユーザが定義した FA0 と FA1 (減衰量ステップ・サイズ・ビット) からなる FA SPI ワード定義に従って、FA ピンによる減衰を行うことができます。UPDN モードの場合、このピンはゲイン・ステップ・サイズの LSB を制御する GS0 機能として有効になります。パラレル・モードの場合、このピンはパラレル・ゲイン制御インターフェース内の D2 になります。 |

| 8      | UPDN_CLK/D1/SDI       | アップ/ダウン・インターフェース用のクロック・インターフェース(UPDN_CLK)。MODE0 ピンと MODE1 ピンの選択に応じて、このピンは3つの機能を果たします。アップ/ダウン・インターフェース・モードの場合、このピンは UPDN_CLK になります。パラレル・モードの場合、このピンはパラレル・ゲイン制御インターフェース内のデジタル・ビット1(D1)になります。4線式 SPIモードの場合、このピンはシリアル・データ入力(SDI)になります。                                                                                                                            |

| 9      | UPDN_DAT/D0/3SPI_4SPI | アップ/ダウン・インターフェース用のデータ・インターフェース(UPDN_DAT)。MODE0 ピンと MODE1 ピンの選択に応じて、このピンは3つの機能を果たします。アップ/ダウン・インターフェース・モードの場合、このピンは UPDN_DAT になります。パラレル・モードの場合、このピンはパラレル・ゲイン制御インターフェース内のデジタル・ビット0(D0)になります。SPIモードの場合、ロジック・ローにすると3線式SPIが選択され、ロジック・ハイにすると4線式SPIが選択されます(3SPI_4SPI)。                                                                                                |

| 10, 12 | DNC                   | 接続なし。これらのピンには接続しないでください。                                                                                                                                                                                                                                                                                                                                      |

Rev. 0 - 8/25 -

| ピン番号   | 記号              | 説明                                                                                                                                                                                                  |

|--------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11     | LATCH/SPI_HP_LP | MODE0 ピンと MODE1 ピンでパラレル・モードを選択した場合、このピンはラッチ(LATCH)になります。このピンをロジック・ローにした場合はゲインを変えることができますが、このピンをロジック・ハイにした場合はゲインを変えることができません。SPIモードの場合、ロジック・ハイにすると高性能モードが選択され、ロジック・ローにすると低消費電力モードが選択されます(SPI_HP_LP)。 |

| 13     | PWUP            | パワーアップ。PWUP は、MODE0 ピンと MODE1 ピンの選択に関係なくパワーアップ・ピンの機能を維持します。このピンをロジック・ハイにするとパワーアップし、このピンをロジック・ローにするとパワーダウンします。                                                                                       |

| 14     | VOUT-           | 負のアナログ出力。                                                                                                                                                                                           |

| 15     | VOUT+           | 正のアナログ出力。                                                                                                                                                                                           |

| 16, 19 | VPOS            | 正電源、5V。                                                                                                                                                                                             |

| 17     | VIN+            | 正のアナログ入力。                                                                                                                                                                                           |

| 18     | VIN-            | 負のアナログ入力。                                                                                                                                                                                           |

| 20     | DNC INTERIM     | 接続なし。DNC INTERIM に抵抗分圧器(5V との間に $25k\Omega$ 、およびグラウンドとの間に $50k\Omega$ )、または、プルアップ抵抗( $3.3V$ との間に $50k\Omega$ )を接続します。                                                                               |

|        | EP              | 露出パッド・グラウンド。露出パッドは、低インピーダンスのグランド・プレーンに接続する必要があります。<br>このプレーンは、表1のすべての電圧に対するグラウンド・リファレンス (0V) になります。                                                                                                 |

#### 表 6. 様々なモードに対応するピン機能の概要

| Mode             | Pin 2 | Pin 3 | Pin 4  | Pin 5  | Pin 6 | Pin 7 | Pin 8    | Pin 9    | Pin 11 | Pin 13 |

|------------------|-------|-------|--------|--------|-------|-------|----------|----------|--------|--------|

| Parallel         |       |       |        |        |       |       |          |          |        |        |

| High Performance | 0     | 0     | Unused | D4     | D3    | D2    | D1       | D0       | LATCH  | 1      |

| Low Power        | 1     | 1     | Unused | D4     | D3    | D2    | D1       | D0       | LATCH  | 1      |

| SPI, 3-Wire      |       |       |        |        |       |       |          |          |        |        |

| High Performance | 0     | 1     | SDIO   | SCLK   | CS    | FA    | Unused   | 0        | 0      | 1      |

| Low Power        | 0     | 1     | SDIO   | SCLK   | CS    | FA    | Unused   | 0        | 1      | 1      |

| SPI, 4-Wire      |       |       |        |        |       |       |          |          |        |        |

| High Performance | 0     | 1     | SDO    | SCLK   | CS    | FA    | SDI      | 1        | 0      | 1      |

| Low Power        | 0     | 1     | SDO    | SCLK   | CS    | FA    | SDI      | 1        | 1      | 1      |

| Up or Down       |       |       |        |        |       |       |          |          |        |        |

| High Performance | 1     | 0     | Unused | Unused | GS1   | GS0   | UPDN_CLK | UPDN_DAT | 0      | 1      |

| Low Power        | 1     | 0     | Unused | Unused | GS1   | GS0   | UPDN_CLK | UPDN_DAT | 1      | 1      |

Rev. 0 - 9/25 -

### 代表的な性能特性

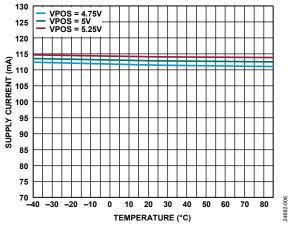

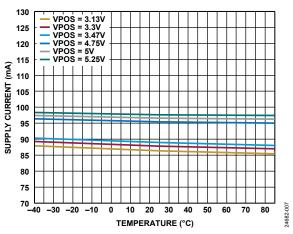

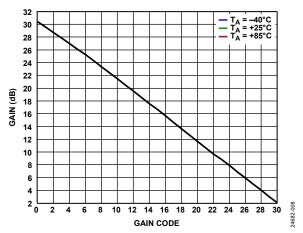

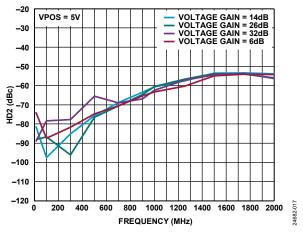

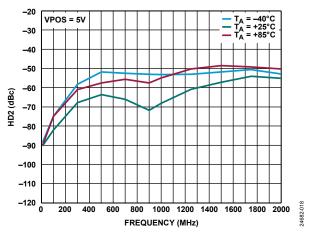

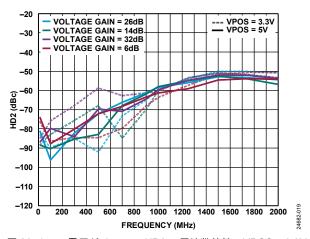

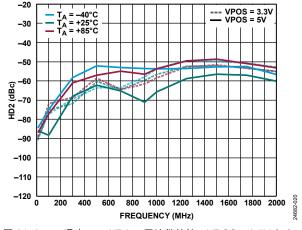

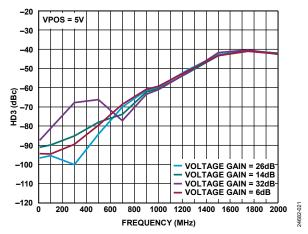

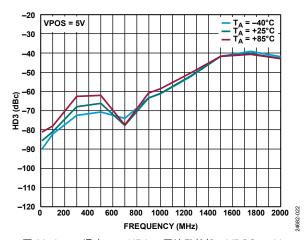

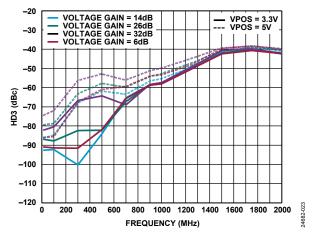

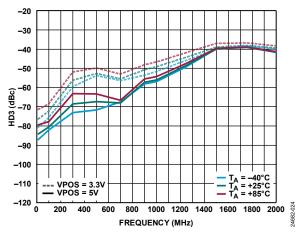

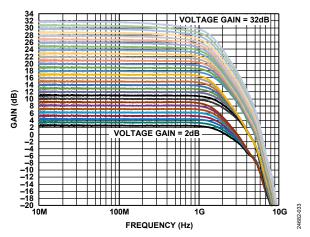

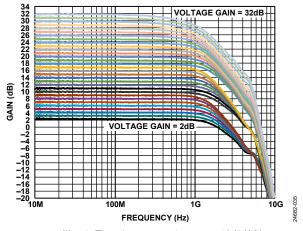

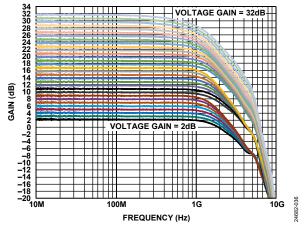

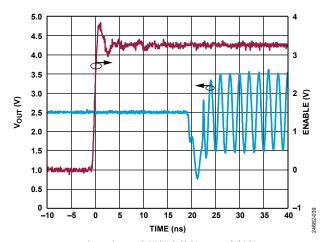

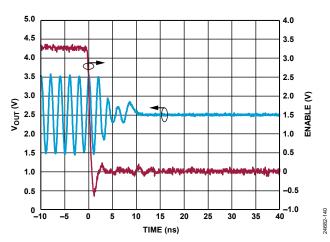

特に指定のない限り、公称  $V_{POS}=5V$ 、 $T_A=25^{\circ}C$ 、 $Z_{LOAD}=100\Omega$ 、最大ゲイン(ゲイン・コード=00000)、IMD3 と OIP3 の場合に 2V p-p のコンポジット差動出力、HD2 と HD3 の場合に 2V p-p の差動出力、VCM =  $V_{POS}/2$ 。

図 6. 電源電流の温度特性、高性能モード

図 7. 電源電流の温度特性、低消費電力モード

図 8. 様々な温度でのゲインとゲイン・コードの関係、500MHz

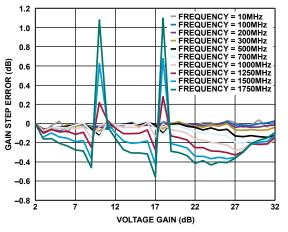

図 9. ゲイン・ステップ誤差と電圧ゲインの関係、 5V 高性能モード

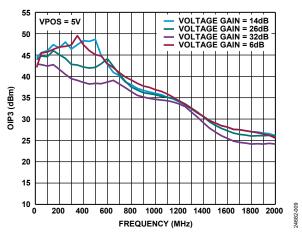

図 10.4 通りの電圧ゲインでの OIP3 の周波数特性、 VPOS = 5V、高性能モード

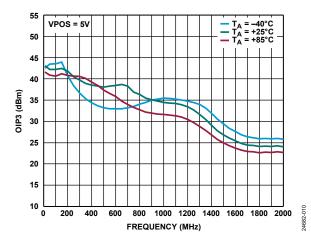

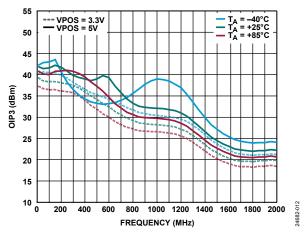

図 11.3 通りの温度での OIP3 の周波数特性、VPOS = 5V、 最大ゲイン、高性能モード

Rev. 0 – 10/25 –

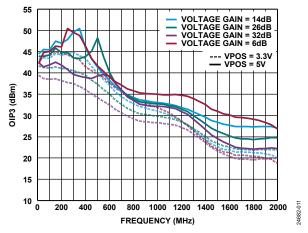

図 12.4 通りの電圧ゲインでの OIP3 の周波数特性、 VPOS = 3.3V および VPOS = 5V、低消費電力モード

図 13.3 つの温度での OIP3 の周波数特性、VPOS = 3.3V および VPOS = 5V、最大ゲイン、低消費電力モード

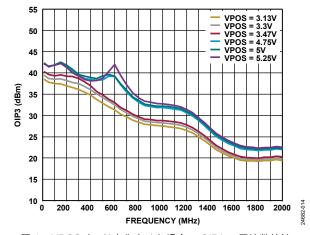

図 14. VPOS を 5%変化させた場合の OIP3 の周波数特性、 最大ゲイン、高性能モード

図 15. VPOS を 5%変化させた場合の OIP3 の周波数特性、 最大ゲイン、低消費電力モード

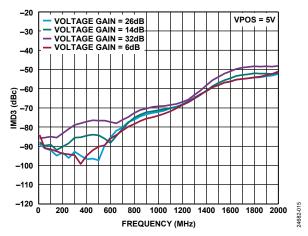

図 16.4 通りの電圧ゲインでの IMD3 の周波数特性、 VPOS = 5V、高性能モード

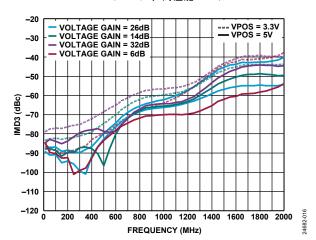

図 17. 4 つの電圧ゲインでの IMD3 の周波数特性、VPOS = 3.3V および VPOS = 5V、低消費電力モード

Rev. 0 — 11/25 —

図 18.4 つの電圧ゲインでの HD2 の周波数特性、VPOS = 5V、 高性能モード

図 19.3 つの温度での HD2 の周波数特性、VPOS = 5V、 最大ゲイン、2V p-p、高性能モード

図 20.4 つの電圧ゲインでの HD2 の周波数特性、VPOS = 3.3V および VPOS = 5V、2V p-p、低消費電力モード

図 21.3 つの温度での HD2 の周波数特性、VPOS = 3.3V および VPOS = 5V、最大ゲイン、2V p-p、低消費電力モード

図 22. 4 つの電圧ゲインでの HD3 の周波数特性、VPOS = 5V、 2V p-p、高性能モード

図 23.3 つの温度での HD3 の周波数特性、VPOS = 5V、 最大ゲイン、2V p-p、高性能モード

Rev. 0 – 12/25 –

図 24.4 つの電圧ゲインでの HD3 の周波数特性、VPOS = 3.3V および VPOS = 5V、2V p-p、低消費電力モード

図 25.3 つの温度での HD3 の周波数特性、VPOS = 3.3V および VPOS = 5V、最大ゲイン、2V p-p、低消費電力モード

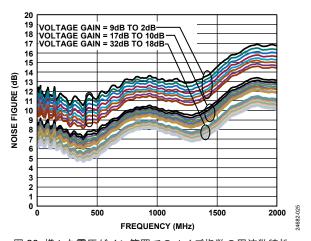

図 26. 様々な電圧ゲイン範囲でのノイズ指数の周波数特性、 5V 高性能モード

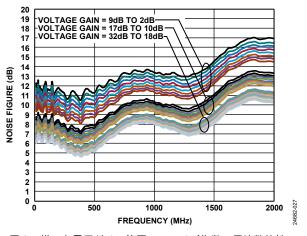

図 27. 様々な電圧ゲイン範囲でのノイズ指数の周波数特性、 5V 低消費電力モード

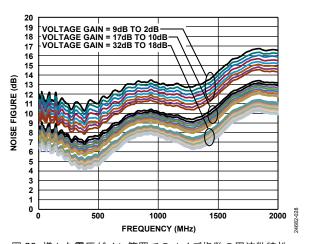

図 28. 様々な電圧ゲイン範囲でのノイズ指数の周波数特性、 3.3V 低消費電力モード

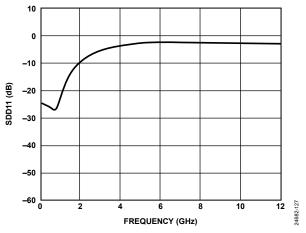

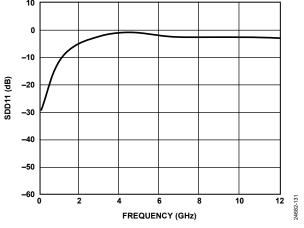

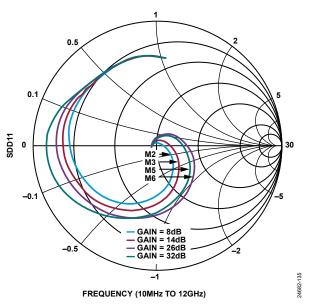

図 29. SDD11 の周波数特性、ゲイン = 2dB、5V 高性能モード

Rev. 0 – 13/25 –

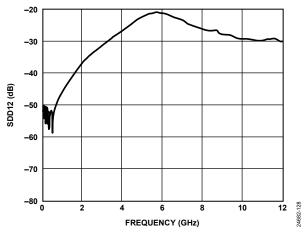

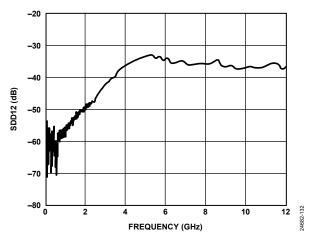

図 30. SDD12 の周波数特性、ゲイン = 2dB、5V 高性能モード

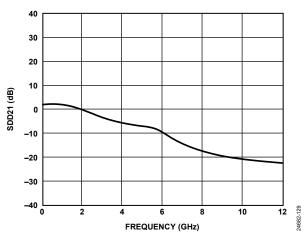

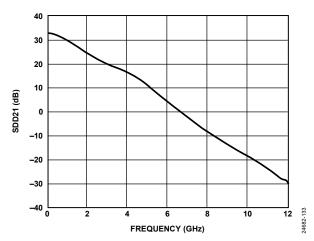

図 31. SDD21 の周波数特性、ゲイン = 2dB、5V 高性能モード

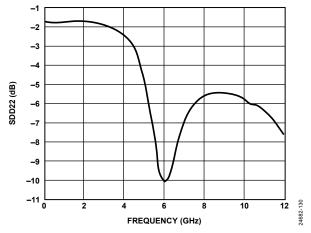

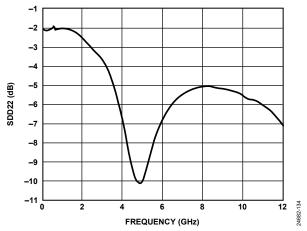

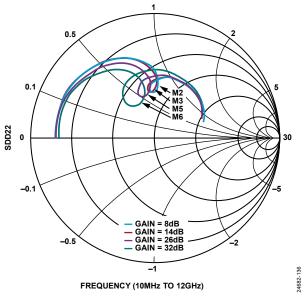

図 32. SDD22 の周波数特性、ゲイン = 2dB、5V 高性能モード

図 33. SDD11 の周波数特性、ゲイン = 32dB、5V 高性能モード

図 34. SDD12 の周波数特性、ゲイン = 32dB、5V 高性能モード

図 35. SDD21 の周波数特性、ゲイン = 32dB、5V 高性能モード

Rev. 0 – 14/25 –

図 36. SDD22 の周波数特性、ゲイン = 32dB、5V 高性能モード

図 37. 様々な電圧ゲインでのゲインの周波数特性、5V 高性能モード

図 38. 様々な電圧ゲインでのゲインの周波数特性、 5V 低消費電力モード

図 39. 様々な電圧ゲインでのゲインの周波数特性、3.3V 低消費電力モード

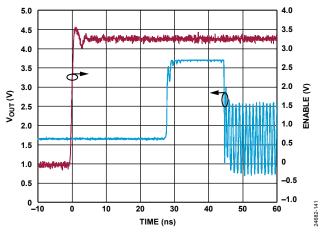

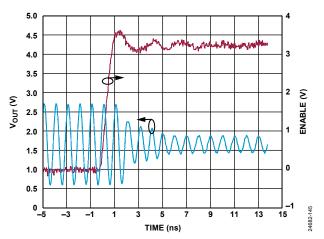

図 40. イネーブルの時間軸応答性、5V 高性能モード

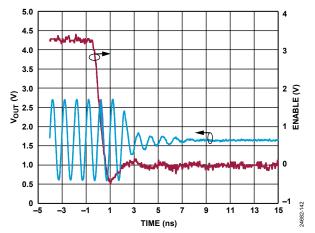

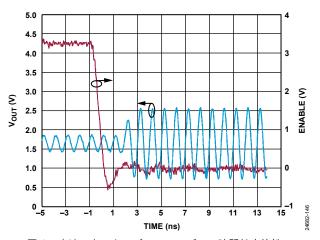

図 41. ディスエーブルの時間軸応答性、5V 高性能モード

Rev. 0 – 15/25 –

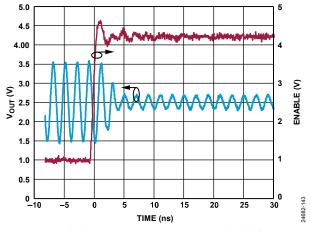

図 42. イネーブルの時間軸応答性、3.3V 低消費電力モード

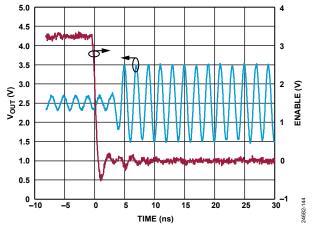

図 43. ディスエーブルの時間軸応答性、3.3V 低消費電力モード

図 44. 高速アタック・イネーブルの時間軸応答性、 5V 高性能モード

図 45. 高速アタック・ディスエーブルの時間軸応答性、 5V 高性能モード

図 46. 高速アタック・イネーブルの時間軸応答性、 3.3V 低消費電力モード

図 47. 高速アタック・ディスエーブルの時間軸応答性、 3.3V 低消費電力モード

Rev. 0 — 16/25 —

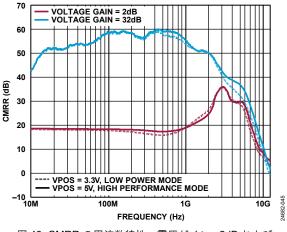

図 48. CMRR の周波数特性、電圧ゲイン= 2dB および 電圧ゲイン = 32dB、5V 高性能モードおよび 3.3V 低消費電力モード

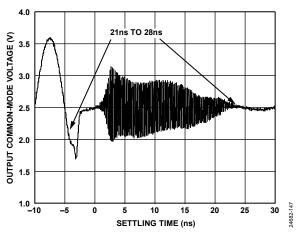

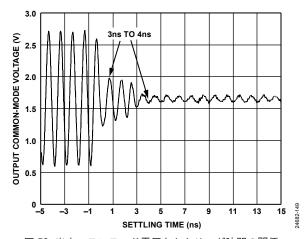

図 49. 出力コモンモード電圧とセトリング時間の関係、 5V 高性能モード、最大ゲイン遷移

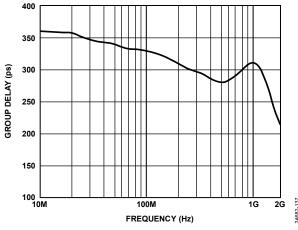

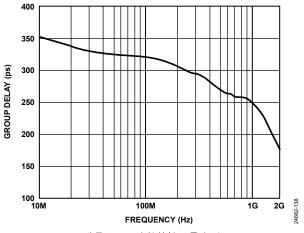

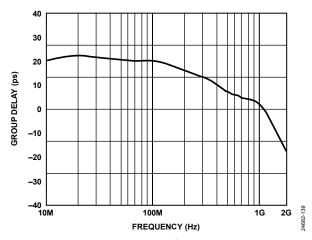

図 50. 群遅延の周波数特性、最大ゲイン、 3.3V 低消費電力モード

図 51. 群遅延の周波数特性、最大ゲイン、 5V 高性能モード

図 52. 群遅延の周波数特性、最大ゲイン、 5V 低消費電力モード

図 53. 出力コモンモード電圧とセトリング時間の関係、 3.3V 低消費電力モード、最大ゲイン遷移

Rev. 0 – 17/25 –

図 54.4 通りのゲインでの差動入力反射 (SDD11) の振幅および 位相の周波数特性

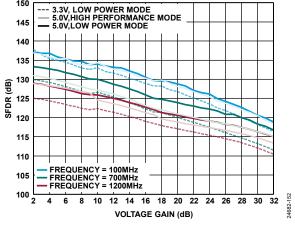

図 55. 様々な電力モードおよび様々な周波数でのスプリアスフリー・ダイナミック・レンジ (SFDR) と電圧ゲインの関係

図 56.4 通りのゲインでの差動出力反射 (SDD22) の振幅および 位相の周波数特性

Rev. 0 — 18/25 —

### 動作原理

#### 基本構成

ADL5206 は、デジタル制御方式の差動 VGA で、DGA とも呼ばれます。この DGA は、 $100\Omega$  の差動入力、デジタル制御方式のパッシブ・アッテネータ、および後段のデジタル制御方式のゲイン・アンプで構成されています。アンプの帰還内にあるデジタル制御方式の抵抗を使用するだけで、最大ゲインから最小ゲインまでの全範囲にわたってゲインを変えられるように、内蔵されたロジック回路がゲイン・コードをマッピングします。

この技術では、アンプの入力にデジタル・ステップ・アッテネータ (DSA) を必要としないため、ゲインが低下するにつれて SFDR を拡大できます。また、このトポロジでは帰還内で 30dB のゲイン全体を下げることができ、700MHz における 30dB のゲイン範囲全体にわたって、全体的なノイズ指数の劣化はわずか 7dB に留まっています。アンプの差動出力インピーダンスは  $10\Omega$ です。

#### 制御およびロジック回路

ADL5206 は、3 つの差動ゲイン制御インターフェース(シリアル制御、パラレル制御、またはアップ/ダウン制御)を搭載しており、これらのインターフェースは、MODE1 ピンと MODE0 ピンの組み合わせによって指定されます。これら各モードにおけるゲイン制御の詳細については、デジタル・インターフェースの概要のセクションを参照してください。通常、ゲイン・ステップ・サイズは 1dB です。ステップ・サイズを大きくする場合は、デジタル・インターフェースの概要のセクションに記述されているようにプログラムすることができます。アンプのゲイン範囲は、32dB の最大ゲイン(ゲイン・コード 00000)から2dB の最小ゲイン(ゲイン・コード 11110~ゲイン・コード11111)までです。

#### コモンモード電圧

ADL5206 は、入出力のカップリングに柔軟性があります。 ADL5206 は、仕様規定されている出力コモンモード電圧リファレンスの範囲内(電源電圧によって異なり、3.3V 電源で 1.2V~1.8V、5V 電源で 1.4V~2.7V)であれば、入出力で AC カップリングまたは DC カップリングが可能です。出力コモンモード電圧を外部から印加しない場合、入出力のコモンモード電圧は内部で電源電圧の 2 分の 1 に設定されます。

ADL5206の出力コモンモード電圧は、VCM ピンの電圧によって 制御されます。VCM ピンは内部で $5k\Omega$ の抵抗を介して VPOS ピンに接続され、同様に別の $5k\Omega$  の抵抗を介して露出パッドに接続されています。この結果、コモンモード出力電圧は、内部で VPOS からの電源電圧の2分の1にプリセットされます。もう1つの方法として、VCM ピンを ADC のコモンモード電圧リファレンス出力に接続すると、外付け部品なしでアンプと ADC 間のコモンモード・レベルを一致させることができます。

Rev. 0 – 19/25 –

# レジスタの一覧と詳細

#### 表 7. レジスタの一覧

| Register<br>Address | Name | Bits  | Bit 7    | Bit 6    | Bit 5    | Bit 4 | Bit 3 | Bit 2    | Bit 1 | Bit 0 | Reset | R/W |

|---------------------|------|-------|----------|----------|----------|-------|-------|----------|-------|-------|-------|-----|

| 0x0                 | CTL  | [7:0] | RESERVED | FAST_ATT | TACK_CTL |       | (     | GAIN_CTI |       |       | 0x18  | R/W |

レジスタ・アドレス:0x0、リセット:0x18、レジスタ名:CTL

#### 表 8. CTL のビットの説明

| ビット   | ビット名            | 説明              | リセット | アクセス |

|-------|-----------------|-----------------|------|------|

| 7     | RESERVED        | 予備              | 0x0  | R    |

| [6:5] | FAST_ATTACK_CTL | 高速アタック・ステップ・サイズ | 0x0  | R/W  |

| [4:0] | GAIN_CTL        | ゲイン制御           | 0x18 | R/W  |

Rev. 0 – 20/25 –

### アプリケーション情報

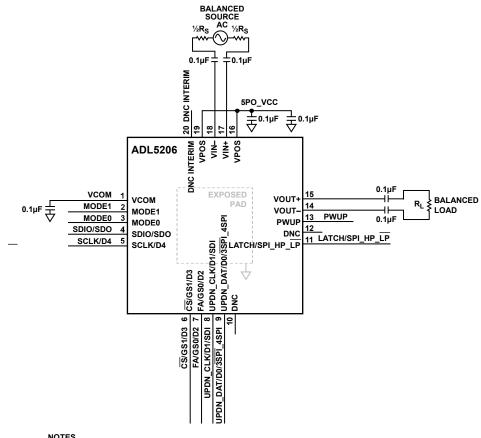

#### 基本的な接続方法

ADL5206を動作させるための基本的な接続方法を図 57 に示しま す。

3.3V または5Vの電圧をVPOSピンに加えます。このデバイスの できるだけ近くに 0.1μF の低インダクタンスの表面実装セラミ ック・コンデンサを少なくとも 1 個配置して、電源ピンをデカ ップリングします。

差動出力 (VOUT+および VOUT-) には、電源電圧の約2分の1 の DC コモンモード電圧が存在します。このため、0.1μF のコン デンサを使用して、これらの出力をデカップリングし、負荷を 平衡化します。平衡差動入力にも、出力と同じ DC コモンモー ド電圧が存在します。入力にも 0.1µF のコンデンサを使用して、 デカップリングすることに注意してください。デジタル・ピン (すなわち、モード制御ピン、SPIとパラレル・ゲイン制御に関 連するピン、パワー・モード・ピン、および PWUP ピン) は 3.3V の電圧で動作します。

ADL5206 をイネーブルするには、PWUP ピンをロジック・ハイ  $(2.0V \le PWUP \le 3.3V)$  にします。

PWUP ピンをロジック・ローにすると ADL5206 はスリープ・モ ードに設定され、消費電流は約7mAまで減少します。VCOMピ ンは出力コモンモード電圧ピンです。したがって、VCOM ピン には、ノイズをフィルタリングするための 0.1μF のコンデンサ を使用して、デカップリングする必要があります。

- 1. DNC = DO NOT CONNECT. DO NOT CONNECT TO THESE PINS.

2. EXPOSED PAD GROUND. THE EXPOSED PAD MUST BE CONNECTED TO A LOW IMPEDANCE GROUND PLANE.

図 57. 基本的な接続方法

Rev. 0 -21/25-

#### デジタル・インターフェースの概要

ADL5206 DGA には、以下のような 3 つのデジタル制御インターフェース・オプションがあります。

- パラレル制御インターフェース

- シリアル・ペリフェラル・インターフェース

- ゲイン・ステップアップ/ステップダウン・インターフェース

デジタル制御インターフェースの選択は、表 9 に示すように、2 本のデジタル・ピン(MODE1 ピンおよび MODE0 ピン)によって行うことができます。

同じ物理ピンが 3 つのインターフェースの間で共有されるため、デジタル・ピン当たり 3 つもの異なる機能を実現できます (表5を参照)。

表 9. デジタル制御インターフェース選択用の真理値表

| MODE1 | MODE0 | Interface                  |

|-------|-------|----------------------------|

| 0     | 0     | Parallel, high performance |

| 0     | 1     | Serial                     |

| 1     | 0     | Up and down                |

| 1     | 1     | Parallel, low power        |

#### パラレル・デジタル・インターフェース

パラレル・デジタル・インターフェースでは、5個のゲイン制御ビットと1本のラッチ・ピンを使用します。LATCHピンは、入力データ・ラッチをトランスペアレント(ロジック・ロー)にするか、ラッチ(ロジック・ハイ)にするかを制御します。トランスペアレント・モードの場合は、入力ゲイン制御ビットの変化に応じてゲインが変化します。ラッチ・モードの場合は、ラッチされたゲイン設定値によってゲインが確定しますが、入力ゲイン制御ビットが変化してもゲインは変化しません。

#### SPI

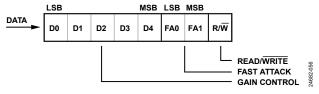

SPIでは、3線式SPIモードの場合に3本のピン (SDIO、SCLK、および CS) を使用し、4線式 SPI モードの場合に 4本のピン (SDI、SDO、SCLK、および CS) を使用します。SPI データ・レジスタは、図 58に示すように、5 つのゲイン制御ビット (D0~D4)、2 つの減衰量ステップ・サイズ・アドレス・ビット (FAO および FAI)、および、1 つの読出し/書込みビット (R/W) の合計 8 ビットで構成されています。

図 58.8 ビット構成の SPI レジスタ

SPI では、3 線式 SPI モードの場合に、SPI レジスタへの書込みと SPI レジスタからの読出し用に双方向ピン(SDIO)が使用されます。これに対して 4 線式 SPI モードの場合には、SDI がデバイスの SPI レジスタへの書込み専用に使用され、SDO がデバイスの SPI レジスタからの読出し専用に使用されます。SPI レジスタにデータを書き込むためには、 $\overline{\text{CS}}$ ピンをロジック・ローにして、8 つのクロック・パルスを加えながら、データを該当するSPI レジスタに MSB ファーストで 8 ビット分シフトします。

SPI レジスタのリード・バック動作は、SPI での読出しのセクションに記載されています。

SPI 高速アタック・モードは、FA ピンによって制御されます。 FA ピンをロジック・ハイにすると、減衰量は SPI レジスタ内の FAI ビットと FAO ビットによって選択されます。

表 10. SPI の 2 ビットを使用した減衰量ステップ・サイズの 直理値表

| FA0 | Step Size (dB)          |

|-----|-------------------------|

| 0   | 2                       |

| 1   | 4                       |

| 0   | 8                       |

| 1   | 16                      |

|     | FA0<br>0<br>1<br>0<br>1 |

#### アップ/ダウン・インターフェース

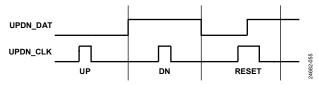

アップ/ダウン・インターフェースでは、2本のデジタル・ピンを使用してゲインを制御します。UPDN\_DAT ピンがロジック・ローのとき、UPDN\_CLK ピンのクロック・パルス(立上がりエッジおよび立下がりエッジ)によって、ゲインが増加します。UPDN\_DAT ピンがロジック・ハイのとき、UPDN\_CLK ピンのクロック・パルスによって、前記ゲインが減少します。UPDN\_CLK の立上がりエッジが UPDN\_DAT の一方の極性をラッチした後で、UPDN\_CLK の立下がりエッジが UPDN\_DAT の反対の極性をラッチしたとき、リセットが検出されます。リセットすると、最小ゲイン・コード(11110)が適用されます。

図 59. アップ/ダウン・ゲイン制御タイミング

ステップ・サイズは、GS1 ピンと GS0 ピンによって選択できます。デフォルトのステップ・サイズは 1dB です。ゲイン・コードの値は、最高と最低の間の制御範囲内で増減します。

表 11. ステップ・サイズ制御用の真理値表

| 公 11: バグググ グイバド 降消の共生 他公 |     |                |

|--------------------------|-----|----------------|

| GS1                      | GS0 | Step Size (dB) |

| 0                        | 0   | 1              |

| 0                        | 1   | 2              |

| 1                        | 0   | 4              |

| 1                        | 1   | 8              |

Rev. 0 – 22/25 –

表 12. ゲイン・コードと電圧ゲインの関係

| 5-Bit Binary Gain Code, D4 to D0 | Voltage Gain (dB) |

|----------------------------------|-------------------|

| 00000                            | 32                |

| 00001                            | 31                |

| 00010                            | 30                |

| 00011                            | 29                |

| 00100                            | 28                |

| 00101                            | 27                |

| 00110                            | 26                |

| 00111                            | 25                |

| 01000                            | 24                |

| 01001                            | 23                |

| 01010                            | 22                |

| 01011                            | 21                |

| 01100                            | 20                |

| 01101                            | 19                |

| 01110                            | 18                |

| 01111                            | 17                |

| 10000                            | 16                |

| 10001                            | 15                |

| 10010                            | 14                |

| 10011                            | 13                |

| 10100                            | 12                |

| 10101                            | 11                |

| 10110                            | 10                |

| 10111                            | 9                 |

| 11000                            | 8                 |

| 11001                            | 7                 |

| 11010                            | 6                 |

| 11011                            | 5                 |

| 11100                            | 4                 |

| 11101                            | 3                 |

| 11110                            | 2                 |

#### SPI での読出し

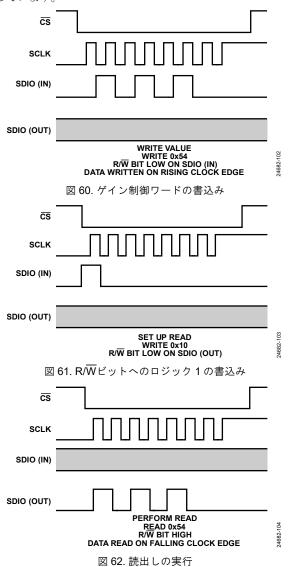

前のサイクルで  $R/\overline{W}$ ビットがハイに設定された後の読出しサイクル中 ( $\overline{CS}$ ローから $\overline{CS}$ ハイまでの間) は、シリアル・モードの場合でのみ、ADL5206 はリード・バックすることができます。 読出しサイクル中、データは SCLK の各立上がりエッジで変化するため、SCLK の立下がりエッジを使用してデータをラッチすることができます。 読出し動作を連続的に行うことはできません。 次の読出しサイクルをイネーブルするには、ロジック・ハイ (1) を  $R/\overline{W}$ ビットに書き込む必要があります。また、いったん  $R/\overline{W}$ ビットに 1 を設定すると、その書込みサイクル中、残りのビットは無視されます。

書込み後にリード・バックを行ったシーケンスの例を図 60~図 62 に示します。これらの図は、SDIO ピンの入出力機能の動作を示しています。

Rev. 0 — 23/25 —

#### ADC とのインターフェーシング

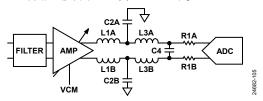

ADL5206をアンチエイリアシング・フィルタおよびADCと共に使用した、代表的なデータ・アクイジション・システムを図 63 に示します。アンプの後段にあるフィルタの主な役割は、広帯域ノイズと、アンプで発生した帯域外の高調波を減衰させることです。アクイジション帯域幅が 500MHz の場合の部品値を表13 に列挙します。このフィルタを使用しないと、帯域外のノイズと歪み成分によってナイキスト帯域内にエイリアスが発生し、S/N 比が減少します。ADL5206 アンプの前段のフィルタは、アクイジション・システムにおけるシステム阻止条件を満たすように、より詳細に設計する必要があります。

図 63. ADC インターフェース (2つのチャンネルのうちの1つを表示)

表 13. 500MHz のアクイジション・システム用の部品値

| 部品        | 値         | 説明/コメント                           |

|-----------|-----------|-----------------------------------|

| Amplifier | ½ ADL5206 | 1つのチャンネル                          |

| L1A, L1B  | 22 nH     | Q≥50(500MHz 時)                    |

| C2A, C2B  | 6.8 pF    | 最終的な値は PCB の寄生容量に依存               |

| L3A, L3B  | 22 nH     | Q≥50(500MHz 時)                    |

| C4        | 1.5 pF    | 最終的な値は PCB の寄生容量に依存               |

| R1A, R1B  | 10 Ω      | 該当せず                              |

| ADC       | ½ AD9680  | 1 つのチャンネル、入力インピー<br>ダンスを 100Ω に設定 |

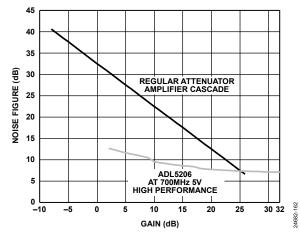

#### ノイズ指数とゲイン設定値の関係

ADL5206 のアーキテクチャによって、最大ゲイン設定値から最初の10dBのゲイン低下までは、ノイズ指数はほとんど劣化していません。最初の10dBのゲイン低下までは、ノイズ指数の増加はわずか0.5dBです。30dBのゲイン範囲全体では、ノイズ指数の変化は7dBです。

図64. ノイズ指数とゲインの関係

Rev. 0 — 24/25 —

### 外形寸法

オーダー・ガイド

| Model <sup>1</sup> | Temperature Range | Package Description                           | Package Option |

|--------------------|-------------------|-----------------------------------------------|----------------|

| ADL5206ACPZ-R7     | -40°C to +85°C    | 20-Lead Lead Frame Chip Scale Package [LFCSP] | CP-20-16       |

| ADL5206ACPZ        | −40°C to +85°C    | 20-Lead Lead Frame Chip Scale Package [LFCSP] | CP-20-16       |

| ADL5206-EVALZ      |                   | Evaluation Board                              |                |

<sup>&</sup>lt;sup>1</sup> Z = RoHS 準拠製品。

Rev. 0 — 25/25 —