# 正誤表

この製品のデータシートに間違いがありましたので、お詫びして訂正いたします。 この正誤表は、2023年6月21日現在、アナログ・デバイセズ株式会社で確認した誤りを 記したものです。

なお、英語のデータシート改版時に、これらの誤りが訂正される場合があります。

正誤表作成年月日: 2023年6月21日

製品名: ADIN2299

対象となるデータシートのリビジョン(Rev): Rev.A

訂正箇所:1ページ、左の段(特長の項)

【誤】

最短 1ms のサイクル時間・・・

【正】

最短 0.4ms (ETHERCAT) のサイクル時間・・・

社/〒105-6891 東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル

電話 03 (5402) 8200

大阪営業所/〒532-0003 大阪府大阪市淀川区宮原 3-5-36

新大阪トラストタワー 電話 06 (6350) 6868

データシート

**ADIN2299**

# 第2世代RapIDプラットフォーム(RPG2) ネットワーク・インターフェース

### 特長

- ▶ 設定化な産業用プロトコル

- ▶ PROFINET RT (クラスB)

- ▶ PROFINET IRT (クラスC) : 計画中

- ▶ DLRによるEtherNet/IP

- ▶ EtherCAT

- ▶ 全てのプロトコルが認定済み

- ▶ 設定可能なアプリケーション・プロセッサ・インターフェース

- ▶ UART : 115,200bps~1,000,000bps

- ▶ イーサネット: 10Mbpsまたは100Mbps

- ▶ SPIフォロワ:最大10MHzのクロック

- ▶ I<sup>2</sup>C、QSPI、CAN:将来的なオプション

- ▶ IEEE 802.3、10Baseまたは100Baseに準拠した産業用イーサネット・インターフェースによる半二重通信および全二重通信

- ▶ 3.3Vの単電源、840mW

- ▶ 最短1msのサイクル時間(サイクル時間は、プロトコル、リンク・タイプ、アプリケーション・データによって異なる)

- ▶ 194ボール・チップスケール・パッケージBGAのフォーム・ファクタ

- ▶ RoHS3準拠

- ▶ -40℃~+85℃の工業用温度範囲

### アプリケーション

- ▶ ファクトリ・オートメーションおよびプロセス・オートメーション

- ▶ モーション・コントロール

- ▶ ビルディング・オートメーション

- ▶ 運輸

### 概要

ADIN2299は、アプリケーション・プロセッサのために産業用プロトコルおよびネットワーク・トラフィックを管理する、事前テスト済みの全機能内蔵型ソリューションです。

モジュールには、EtherCAT、PROFINET®リアルタイム(RT)およびアイソクロナス・リアルタイム(IRT)、EtherNet/IPネットワークを利用するために必要な機能が、通信コントローラ、プロトコル・スタック、フラッシュ・メモリ、RAM、フォロワ・コントローラ、物理層(PHY)などを含め、全て搭載されています。アプリケーション・プロセッサは、ユニバーサル非同期レシーバー・トランスミッタ(UART)、シリアル・ペリフェラル・インターフェース(SPI)、あるいはイーサネット・インターフェースを介して接続されます。

ソフトウェア層では、アプリケーション・プロセッサは統合インターフェースに接続しているため、アプリケーション・プロセッサのソフトウェアを変更することなく、サポートされている産業用プロトコルを使用できます。ADIN2299プラットフォームは、サポートされている産業用イーサネット・ネットワークのいずれにおいてもフィールド・デバイスが動作できることが認定されています。

### 製品のハイライト

- 1. マルチプロトコル対応

- 2. 組み込みアプリケーションに適した小型形状

- 3. 低消費電力および低遅延

- 4. PROFINET Netload Class 3合格を確実にする堅牢なネットワーク・ポリシング

<u>データシート</u> **目次**

# **ADIN2299**

| 特長          | 1 |

|-------------|---|

| アプリケーション    | 1 |

| 概要          | 1 |

| 製品のハイライト    | 1 |

| 機能ブロック図     | 3 |

| 仕様          | 4 |

| 電気的特性       | 4 |

| プロトコル固有の特性  | 4 |

| タイミング特性     | 5 |

| 絶対最大定格      | 8 |

| 静電放電(ESD)定格 | 8 |

| ECDに関する注音   | Q |

| ピン配置とピン機能の説明                | 9  |

|-----------------------------|----|

| 動作原理                        | 13 |

| 産業用イーサネット接続                 | 14 |

| アプリケーション・プロセッサ・インターフェース     | 14 |

| 産業用イーサネットのMOD LEDおよびNET LED | 18 |

| プログラミング                     | 18 |

| アプリケーション回路サポート回路            | 18 |

| リフロー・プロファイル                 | 19 |

| 代表的なアプリケーション回路              | 20 |

| 外形寸法                        | 21 |

| オーダー・ガイド                    | 21 |

| 新年中央 16                     | 21 |

### 改訂履歴

9/2022—Rev. 0 to Rev. A

| Changes to Figure 6 and Table 9 | 9  |

|---------------------------------|----|

| Changes to Ordering Guide       | 21 |

4/2022-Revision 0: Initial Version

analog.com.jp

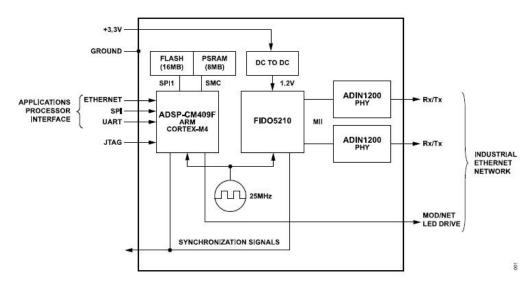

# 機能ブロック図

図 1.

analog.com.jp Rev. A | 3 / 21

### 仕様

特に指定のない限り、電源電圧( $V_{DD}$ ) = 3.3V ± 5%、GND = 0V、全ての仕様は $T_A$  = -40 $^{\circ}$ C  $\sim$ +85 $^{\circ}$ C での値。

### 電気的特性

表 1.

| パラメータ                                                                                  | 最小値 | 代表值 | 最大値 | 単位 | テスト条件/コメント                                                              |

|----------------------------------------------------------------------------------------|-----|-----|-----|----|-------------------------------------------------------------------------|

| POWER CONSUMPTION                                                                      |     |     |     |    |                                                                         |

| Supply Current 100Base-TX, Static                                                      |     | 172 |     | mA | T <sub>A</sub> =25℃、アイドル状態                                              |

| Power 100Base-TX, Static                                                               |     | 568 |     | mW | T <sub>A</sub> = 25℃、アイドル状態、発光ダイオード(LED)の<br>シンク電流およびソース電流は含まず          |

| Supply Current 100Base-TX, Full Activity <sup>1</sup>                                  |     | 225 |     | mA | $T_A = 25$ <sup>°</sup> C、 $100$ %データ・スループット、フル・アクティブ                   |

| Power 100Base-TX, Full Activity <sup>1</sup>                                           |     | 743 |     | mW | T <sub>A</sub> =25℃、100%データ・スループット、フル・アクティブ、LEDのシンク電流およびソース電流は含まず       |

| DIGITAL INPUTS AND OUTPUTS                                                             |     |     |     |    |                                                                         |

| 3.3 V Low Voltage Complementary Metal<br>Oxide Semiconductor (LVCMOS)<br>Input Voltage |     |     |     |    |                                                                         |

| $Low(V_{IL})$                                                                          |     |     | 0.8 | V  |                                                                         |

| High (V <sub>IH</sub> )                                                                | 2.0 |     |     | V  |                                                                         |

| Output Voltage                                                                         |     |     |     |    |                                                                         |

| Low (V <sub>OL</sub> )                                                                 |     |     | 0.4 | V  | 出力ロー電流( $I_{OL}$ ) = $2mA$ (最小値)                                        |

| $High(V_{OH})$                                                                         | 2.4 |     |     | V  | 出力ハイ電流 (I <sub>OH</sub> ) = 2mA (最小値)                                   |

| LED OUTPUTS                                                                            |     |     |     |    |                                                                         |

| Output Drive Current                                                                   | 4   |     |     | mA | シンク電流、MOD_LED1、MOD_LED2、NET_LED1、<br>NET_LED2に適用されます                    |

|                                                                                        | 8   |     |     | mA | シンク電流、PI_ACTIVITY、P2_ACTIVITY、<br>PI_LINK_STATUS、P2_LINK_STATUS、に適用されます |

<sup>1</sup> 設計および特性評価により裏付けられています。

### プロトコル固有の特性

### 表 2.

| パラメータ                                     | 最小値 | 代表值 | 最大値  | 単位    | テスト条件/コメント                                                                |

|-------------------------------------------|-----|-----|------|-------|---------------------------------------------------------------------------|

| BRIDGE DELAY                              |     |     |      |       | スイッチおよびPHYの遅延を含む。シミュレーションによる結果。                                           |

| EtherCAT <sup>1</sup>                     |     | 1   |      | μs    |                                                                           |

| EtherNet/IP                               |     | 3   |      | μs    |                                                                           |

| PROFINET RT                               |     | 2   |      | μs    |                                                                           |

| ETHERCAT                                  |     |     |      |       |                                                                           |

| Cyclic Input and Output Data <sup>2</sup> |     |     | 1440 | Bytes | 最大1440バイトをサポート可能です。                                                       |

| Cycle Time                                |     | 0.4 |      | ms    | このテストでは8バイトの出力データと6バイトの入力データを使用しました。イーサネット・アプリケーション・プロセッサ・インターフェース。       |

| ETHERNET/IP                               |     |     |      |       |                                                                           |

| Cyclic Input and Output Data <sup>2</sup> |     |     | 504  | Bytes | 接続を複数にすることで、巡回入出力データは最大1440バイトまで増やせます。                                    |

| Packet Interval                           | 2   |     |      | ms    |                                                                           |

| Beacon Interval                           | 0.2 |     | 1000 | ms    |                                                                           |

| Cycle Time                                |     | 1   |      | ms    | このテストでは64バイトの巡回出力データと64バイトの巡回入力データを使用しました。イーサネット・アプリケーション・プロセッサ・インターフェース。 |

analog.com.jp Rev. A | 4 / 21

### 仕様

表 2.

| パラメータ                                     | 最小値 | 代表値 | 最大値  | 単位    | テスト条件/コメント               |

|-------------------------------------------|-----|-----|------|-------|--------------------------|

| PROFINET RT                               |     |     |      |       |                          |

| Cyclic Input and Output Data <sup>2</sup> |     |     | 1440 | Bytes |                          |

| Cycle Time                                |     | 1   |      | ms    | 8バイトの巡回入出力データ。イーサネット・アプリ |

|                                           |     |     |      |       | ケーション・プロセッサ・インターフェース。    |

- 1 設計および特性評価により裏付けられています。

- 2 サイクル時間はプロトコル、リンク・タイプ、アプリケーション・データによって異なります。

### タイミング特性

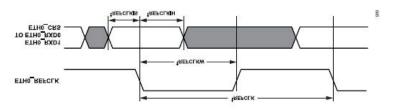

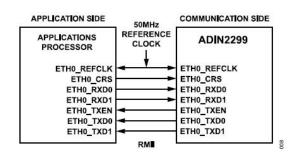

### 10Mbpsおよび100MbpsイーサネットMACインターフェースのタイミング

表3~表5および図2~図4で、イーサネットMACアプリケーション・プロセッサ、インターフェース・コントローラ、タイミング仕様について説明します。外部で生成されるイーサネットMACクロックはfreeclkextで、内部システム・クロックはfreeclkextである点に注意してください。外部で生成されるイーサネットMACクロックのタイミングと内部システム・クロック・タイミングを計算するには、次の式を用います。

$t_{REFCLKEXT} = 1/f_{REFCLKEXT}$

$t_{SYSCLK} = 1/f_{SYSCLK}$

表 3. 10Mbpsおよび100MbpsのイーサネットMAC RMII(Reduced Media Independent Interface)の受信信号タイミング

| Parameter             | Description                                                          | Min                         | Max                         | Unit |

|-----------------------|----------------------------------------------------------------------|-----------------------------|-----------------------------|------|

| $f_{REFCLKEXT}$       | ETH0_REFCLK Frequency                                                |                             | 50                          | MHz  |

| $t_{REFCLK}$          | ETH0_REFCLK Period <sup>1</sup>                                      | t <sub>REFCLKEXT</sub> - 1% |                             | ns   |

| $t_{REFCLKW}$         | ETH0_REFCLK Width <sup>1</sup>                                       | $t_{REFCLKEXT} \times 35\%$ | $t_{REFCLKEXT} \times 65\%$ | ns   |

| t <sub>REFCLKIS</sub> | Receive Input Valid to RMII ETH0_REFCLK Rising Edge (Data In Setup)  | 4                           |                             | ns   |

| t <sub>REFCLKIH</sub> | RMII ETH0_REFCLK Rising Edge to Receive Input Invalid (Data In Hold) | 2.0                         |                             | ns   |

1 この仕様は、デューティ・サイクルの変化またはジッタによる許容可能な最小瞬時幅または期間を示します。

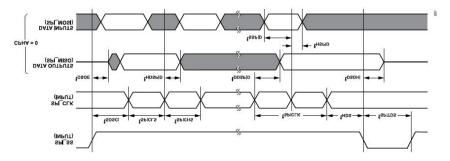

図 2. RMIIの受信タイミング

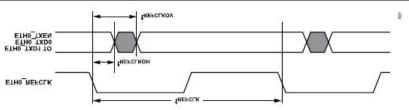

表 4. 10Mbpsおよび100MbpsイーサネットMAC RMIIの送信信号タイミング

| Parameter             | Description                                                            | Min | Max | Unit |

|-----------------------|------------------------------------------------------------------------|-----|-----|------|

| t <sub>REFCLKOV</sub> | RMII ETH0_REFCLK Rising Edge to Transmit Output Valid (Data Out Valid) |     | 14  | ns   |

| $t_{REFCLKOH}$        | RMII ETH0_REFCLK Rising Edge to Transmit Output Valid (Data Out Hold)  | 2   |     | ns   |

図 3. RMIIの送信タイミング

analog.com.jp Rev. A | 5 / 21

### 仕様

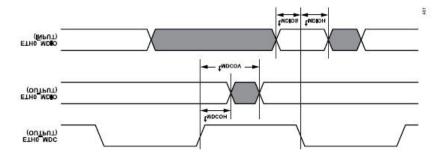

表 5. 10Mbpsおよび100MbpsイーサネットMAC管理インターフェースのタイミング

| Parameter      | Description                                              | Min                     | Max              | Unit |

|----------------|----------------------------------------------------------|-------------------------|------------------|------|

| $f_{SYSCLK}$   | Internal System Clock                                    |                         | 100              | MHz  |

| $t_{ m MDIOS}$ | ETH0_MDIO Input Valid to ETH0_MDC Rising Edge (Setup)    | 14                      |                  | ns   |

| $t_{ m MDIOH}$ | ETH0_MDC Rising Edge to ETH0_MDIO Input Invalid (Hold)   | 0                       |                  | ns   |

| $t_{MDCOV}$    | ETH0_MDC Falling Edge to ETH0_MDIO Output Valid          |                         | $t_{SYSCLK} + 5$ |      |

| $t_{MDCOH}$    | ETH0_MDC Falling Edge to ETH0_MDIO Output Invalid (Hold) | t <sub>SYSCLK</sub> - 5 |                  | ns   |

図 4. イーサネット10Mbpsおよび100Mbps MAC管理インターフェースのタイミング

analog.com.jp Rev. A | 6 / 21

### 仕様

### SPIフォロワ・インターフェースのタイミング

表6と図5に、SPIポート・フォロワのタイミング仕様を示します。SPIフォロワ・モードでは、SPIクロックが外部から供給(fspicLkext)される点に注意してください。外部SPIクロックのタイミングを計算するには、次の式を用います。

$t_{SPICLKEXT} = 1/f_{SPICLKEXT}$

表 6. SPIポート・フォロワのタイミング

| Parameter           | Description                                          | Min                        | Max                     | Unit |

|---------------------|------------------------------------------------------|----------------------------|-------------------------|------|

| $f_{SPICLKEXT}$     | SPI0_CLK Frequency                                   |                            | 10                      | MHz  |

| $t_{SPICHS}$        | SPI0_CLK High Period                                 | $0.5 \times t_{SPICLKEX}$  | <sub>T</sub> - 1        | ns   |

| t <sub>SPICLS</sub> | SPI0_CLK Low Period                                  | $0.5 \times t_{SPICLKEX}$  | <sub>T</sub> - 1        | ns   |

| t <sub>SPICLK</sub> | SPI0_CLK Period                                      | t <sub>SPICLKEXT</sub> - 1 |                         | ns   |

| $t_{HDS}$           | Last SPI0_CLK Edge to SPI0_SEL3_SS Not Asserted      | 5                          | 5                       |      |

| t <sub>SPITDS</sub> | Sequential Transfer Delay                            | t <sub>SPICLK</sub> - 1    | t <sub>SPICLK</sub> - 1 |      |

| t <sub>SDSCI</sub>  | SPI0_SEL3_SS Assertion to First SPI_CLK Edge         | 10.5                       | 10.5                    |      |

| $t_{SSPID}$         | Data Input Valid to SPI0_CLK Edge (Data Input Setup) | 2                          | 2                       |      |

| $t_{HSPID}$         | SPI0_CLK Sampling Edge to Data Input Invalid         | 1.6                        | 1.6                     |      |

| $t_{DSOE}$          | SPIO_SEL3_SS Assertion to Data Out Active            | 0                          | 14                      | ns   |

| t <sub>DSDHI</sub>  | SPI0_SEL3_SS Deassertion to Data High Impedance      | 0                          | 12.5                    | ns   |

| $t_{DDSPID}$        | SPI0_CLK Edge to Data Out Valid (Data Out Delay)     |                            | 14                      | ns   |

| $t_{HDSPID}$        | SPI0_CLK Edge to Data Out Invalid (Data Out Hold)    | 0                          |                         | ns   |

図 5. SPIフォロワのタイミング

analog.com.jp Rev. A | 7 / 21

# 絶対最大定格

特に指定のない限り、 $T_A = 25$ °C。

#### 表 7.

| Parameter                         | Rating                              |

|-----------------------------------|-------------------------------------|

| VDD to GND                        | -0.3 V to +3.6 V                    |

| Power Dissipation                 | 840 mW                              |

| Temperature                       |                                     |

| T <sub>A</sub> Range, Industrial  | −40°C to +85°C                      |

| Storage Range                     | -65°C to +150°C                     |

| Junction (T <sub>J</sub> Maximum) | 125℃                                |

| Lead, Soldering                   | JEDEC industry-standard, J- STD-020 |

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。これはストレス定格のみを規定するものであり、本仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。長時間にわたり最大動作条件を超えて動作させると、デバイスの信頼性に影響を与えることがあります。

### 静電放電(ESD)定格

以下のESD情報は、ESDに敏感なデバイスを取り扱うために示したものですが、対象はESD保護区域内だけに限られます。

ANSI/ESDA/JEDEC JS-001準拠の人体モデル (HBM)。

ANSI/ESDA/JEDEC JS-002準拠の電界誘起帯電デバイス・モデル (FICDM)。

#### ADIN2299のESD定格

表 8. ADIN2299、194ボールCSP\_BGA

| ESD Model | Withstand Threshold (V) | Class |

|-----------|-------------------------|-------|

| НВМ       | 2500                    | 2     |

| FICDM     | 2000                    | C3    |

### ESDに関する注意

#### ESD(静電放電)の影響を受けやすいデバイスです。

電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術であるESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

analog.com.jp Rev. A | 8 / 21

# ピン配置とピン機能の説明

|      |                 |                          |                           |                 |       |     |             |              | TOP VIEW<br>Not to Scal |     |     |     |     |                |                |                 |                  |

|------|-----------------|--------------------------|---------------------------|-----------------|-------|-----|-------------|--------------|-------------------------|-----|-----|-----|-----|----------------|----------------|-----------------|------------------|

|      | A               | В                        | С                         | D               | E     | F   | G           | н            | J                       | к   | L   | м   | N   | Р              | R              | т               | U                |

|      |                 | GPIO_<br>8               | GPIO_                     | STATUS_<br>LED1 | LT2   | LT0 | GND         | V_3V3<br>_JN | V_3V3<br>_IN            | GND | DNC | NC  | GND | SYS_<br>BMODE0 | SYS_<br>BMODE1 | NC              |                  |

| 1000 | GND             | NC                       | GPIO_<br>7                | STATUS_<br>LED2 | SDONE | LT1 | GND         | V_3V3<br>_IN | V_3V3<br>_IN            | GND | NC  | NC  | GND | SYS_<br>HWRST  | SYS_<br>RESOUT | GND             | P2_<br>TD_P      |

|      | NC              | WP                       | NC                        | GND             | NC    | NC  | GND         | GND          | GND                     | GND | GND | GND | GND | NC             | REM_<br>RESET  | GND             | P2_<br>TD_N      |

|      | NC              | NC                       | NC                        | GND             |       |     |             |              |                         |     |     |     |     | GND            | GND            | GND             | P2_<br>RD_P      |

|      | GND             | GND                      | RREQ                      |                 | a :   |     |             |              |                         |     |     |     |     |                | NC             | GND             | P2_<br>RD_N      |

|      | JTG_<br>TRST    | JTG_<br>TDI              | INT_IN                    |                 |       |     |             |              |                         |     |     |     |     |                | NC             | P2_<br>ACTIVITY | P2_LINI<br>STATU |

|      | JTG_<br>TMS     | JTG_<br>TDO              | JTG_<br>TCK               |                 |       |     | GND         | GND          | GND                     | GND | GND |     |     | 3              | GND            | TIMER0          | TIMER            |

| 1000 | DNC             | SPIO_<br>SEL3_SS         | GND                       |                 |       |     | GND         | GND          | GND                     | GND | GND |     |     |                | GND            | T MER1          | TIMER            |

|      | SPIO_<br>CLK    | SPIO_<br>MISO/<br>SPI_DO | SPIO_<br>MOSI/<br>SPIO_D1 |                 |       |     | GND         | GND          | GND                     | GND | GND |     |     | 9              | NC             | GND             | NC               |

| C.A  | AN1_TX          | CAN1_<br>RX              | GND                       |                 |       |     | GND         | GND          | GND                     | GND | GND |     |     |                | GND            | SYNC2           | TIMER            |

| U.   | ARTO_<br>K/BUSY | UARTO_<br>RX             | GND                       |                 |       |     | GND         | GND          | GND                     | GND | GND |     |     |                | GND            | TIMER5          | SYNC             |

|      | TXD0            | ETH0_<br>TXD1            | ETHO_<br>MDC              |                 |       |     |             |              |                         |     |     |     |     |                | NC             | P1_<br>ACTIVITY | P1_LIN           |

|      | ETHO_<br>EFCLK  | ETHO_<br>TXEN            | ETHO_<br>MDIO             | GND             |       |     |             |              |                         |     |     |     |     |                | NC             | GND             | P1_TD            |

|      | ETHO_<br>RXD0   | ETH0_<br>RXD1            | ETHO_<br>CRS              | GND             | GND   |     | 3           |              |                         |     |     |     |     | GND            | GND            | GND             | P1_TD_           |

| N    | GND             | GND                      | GND                       | GND             | GND   | SCL | SDA         | NC           | NC                      | NC  | NC  | NC  | NC  | GND            | NET_<br>LED2   | GND             | P1_RD            |

|      | NC              | 33.                      | NC                        | GND             | NC    | NC  | SP10_<br>D3 | GND          | TMO_<br>TMR2            | GND | DNC | DNC | DNC | GND            | NET_<br>LED1   | GND             | P1_RD            |

|      |                 | NC                       | NC                        | GND             | NC    | GND | SP10_<br>D2 | GND          | TMO_<br>TMR1            | GND | DNC | DNC | DNC | GND            | MOD_<br>LED1   | MOD_<br>LED2    |                  |

V\_3V3\_IN GND I/O

NC = NO CONNECT.

図 6. ボール配置

#### 表 9. ボール機能の説明

| ボール番号                               | <br>記号 |                | 説明                                      |

|-------------------------------------|--------|----------------|-----------------------------------------|

|                                     |        | İ              | i e e e e e e e e e e e e e e e e e e e |

| A2, A14, A15, B1, B14, B16, C1,     | NC     | Not applicable | 接続なし。                                   |

| C2, C14, C15, E1, E2, E15, F2,      |        |                |                                         |

| F15, H3, J3, K3, L3, L16, M3,       |        |                |                                         |

| M16, M17, N3, P15, R5, R6, R9,      |        |                |                                         |

| R12, R13, T17, U9                   |        |                |                                         |

| A3, A13, A16, B3, B13, C3, C7,      | GND    | Not applicable | グラウンド。                                  |

| C8, C10, D1, D2, D3, D4, D5,        |        |                |                                         |

| D14, D15, E3, E4, F1, G7, G8,       |        |                |                                         |

| G9, G10, G11, G15, G16, G17,        |        |                |                                         |

| H1, H2, H7, H8, H9, H10, H11,       |        |                |                                         |

| H15, J7, J8, J9, J10, J11, J15, K1, |        |                |                                         |

| K2, K7, K8, K9, K10, K11, K15,      |        |                |                                         |

| K16, K17, L7, L8, L9, L10, L11,     |        |                |                                         |

| L15, M15, N15, N16, N17, P1,        |        |                |                                         |

| P2, P3, P4, P14, R4, R7, R8, R10,   |        |                |                                         |

| R11, R14, T2, T3, T4, T5, T9,       |        |                |                                         |

| T13, T14, T15, T16                  |        |                |                                         |

Rev. A | 9 / 21 analog.com.jp

# ピン配置およびピン機能の説明

表 9. ボール機能の説明

| ボール番号 | 記号                 | 方向               | 説明                                                                                                                         |

|-------|--------------------|------------------|----------------------------------------------------------------------------------------------------------------------------|

| A4    | ETH0_RXD0          | Input            | イーサネットMAC 0 (EMAC0) の受信データ0。受信データ・バス。                                                                                      |

| A5    | ETH0_REFCLK        | Input            | EMACOのリファレンス・クロック。外部から供給されるイーサネット・<br>クロック。                                                                                |

| A6    | ETH0_TXD0          | Output           | EMACOの送信データ0。送信データ・バス。                                                                                                     |

| A7    | UART0_TX/BUSY      | Output           | UARTをアプリケーション・プロセッサ・インターフェースに選択した場合のUART0送信出力(UART0_TX)。                                                                   |

|       |                    |                  | SPIを選択時のビジー信号 (BUSY) 。この信号は、通信側がビジーであることをアプリケーション側に示します。BUSYピンには $3k\Omega$ のプルダウン抵抗を接続します。                                |

| A8    | CAN1_TX            | Output           | このボールはフロート状態のままにできます。将来のCANアプリケーション・プロセッサ・インターフェース送信 (CAN1_TX) のオプションに備えて予約されています。                                         |

| A9    | SPI0_CLK           | Input            | SPIOクロック入力                                                                                                                 |

| A10   | DNC                | Not applicable   | 何も接続しないでください。DNCピンは内部で接続されており、フローティング状態のままにする必要があります。                                                                      |

| A11   | JTG_TMS            | Input            | JTAGモードの選択。JTAGテスト・アクセス・ポート・モードの選択。                                                                                        |

| A12   | JTG_TRST           | Input            | JTAGリセット。JTAGテスト・アクセス・ポートのリセット。                                                                                            |

| B4    | ETH0_RXD1          | Input            | EMAC0 の受信データ1。受信データ・バス。                                                                                                    |

| B5    | ETH0_TXEN          | Output           | EMACOの送信イネーブル。このボールがアサートされた場合、送信データが有効であることを示します。                                                                          |

| B6    | ETH0_TXD1          | Output           | EMACOの送信データ1。送信データ・バス。                                                                                                     |

| B7    | UART0_RX           | Input            | UARTOの受信。受信入力。                                                                                                             |

| В8    | CANI_RX            | Input            | このボールはフロート状態のままにできます。将来のCANアプリケーション・プロセッサ・インターフェース受信(CAN1_RX)のオプションに備えて予約されています。                                           |

| В9    | SPI0_MISO/SPI_D0   | Input and output | SPIOリーダ入力、フォロワ出力 (SPIO_MISO)。QSPI™が選択されている場合、このボールにはQSPIのデータ0ラインとなるSPIO_DO機能があります。                                         |

| B10   | SPI0_SEL3_SS       | Input            | SPIOフォロワ選択入力。                                                                                                              |

| B11   | JTG_TDO            | Output           | JTAGシリアル・データ出力。JTAGテスト・アクセス・ポートのデータ出力。                                                                                     |

| B12   | JTG_TDI            | Input            | JTAGシリアル・データ入力。JTAGテスト・アクセス・ポートのデータ入力。                                                                                     |

| B15   | $\overline{ m WP}$ | Input            | 書込み保護 $SPI$ フラッシュ。 $\overline{WP}$ ボールはモジュール内部でハイにプルアップされます。このピンはフロート状態のままにすることを推奨します。                                     |

| B17   | GPIO_8             | Output           | 汎用入出力8。 $GPIO_8$ ボールには $10k\Omega$ のプルアップ抵抗を接続します。                                                                         |

| C4    | ETH0_CRS           | Input            | EMACOキャリア検出。1つおきのクロック・サイクルでマルチプレクスされます。<br>キャリア検出 (CRS) : 送信媒体または受信媒体がアイドル状態でない場合にPHYによってアサートされます。どちらもアイドル状態になるとデアサートされます。 |

|       |                    |                  | 受信分周器 (RXDV):受信データ・ライン1のデータ (RXD0) が有効な<br>場合にPHYによってアサートされます。                                                             |

| C5    | ETH0_MDIO          | Input and output | EMAC0管理チャンネル・シリアル・データ。PHY制御用の双方向データ・バスです。                                                                                  |

| C6    | ETH0_MDC           | Output           | EMAC0管理チャンネル・クロック。PHYのMDC入力をクロックします。                                                                                       |

| C9    | SPI0_MOSI/SPI0_D1  | Input and output | SPIOリーダ出力、フォロワ入力 (SPIO_MOSI)。 QSPIが選択されている場合、このボールにはQSPIのデータ1ラインとなるSPIO_D1機能があります。                                         |

| C11   | JTG_TCK            | Input            | JTAGクロック。JTAGテスト・アクセス・ポートのクロック。                                                                                            |

| C12   | ĪNI_IN             | Input            | アプリケーション・プロセッサへの割込み入力。 $\overline{INI\_IN}$ ボールには4.7k $\Omega$ のプルアップ抵抗を接続します。                                             |

| C13   | RREQ               | Output           | アプリケーション・プロセッサへの割込み出力。信号がハイになり、メッセージの読出し準備ができていることをアプリケーション側に伝えます。 RREQボールには $3k\Omega$ のプルダウン抵抗を接続します。                    |

| C16   | GPIO_7             | Output           | 汎用入出力7。                                                                                                                    |

analog.com.jp Rev. A | 10 / 21

# ピン配置およびピン機能の説明

表 9. ボール機能の説明

| ボール番号                       | 記号          | 方向               | 説明                                                                                          |

|-----------------------------|-------------|------------------|---------------------------------------------------------------------------------------------|

| C17                         | GPIO_6      | Input and output | 汎用入出力6。                                                                                     |

| D16                         | STATUS_LED2 | Input and output | STATUS_LED2ボールがローになると、オプションのSTATUS信号用2色 LEDの赤色LEDがアクティブになります。                               |

| D17                         | STATUS_LED1 | Output           | STATUS_LED1ボールがローになると、オプションのSTATUS信号用2色 LEDの緑色LEDがアクティブになります。                               |

| E16                         | SDONE       | Output           | 通信のスタート・アップが完了。SDONEボールには $4.7k\Omega$ のプルダウン抵抗を接続します。                                      |

| E17                         | LT2         | Input and output | アプリケーション・プロセッサ・インターフェースの選択:リンク・タイプ2 (表11参照)。                                                |

| F3                          | SCL         | Input and output | I <sup>2</sup> Cシリアル・クロック。リーダ時はクロック出力、フォロワ時はクロック入力。I <sup>2</sup> Cバス規格に対応。外付けプルアップ抵抗が必要です。 |

| F16                         | LT1         | Input and output | アプリケーション・プロセッサ・インターフェースの選択:リンク・タイプ1 (表11参照)。                                                |

| F17                         | LT0         | Input and output | アプリケーション・プロセッサ・インターフェースの選択:リンク・タイプ0 (表11参照)。                                                |

| G1                          | SPI0_D2     | Input and output | QSPIが選択されている場合、このボールにはQSPIのデータ2ラインとなる<br>SPIO_D2機能があります。                                    |

| G2                          | SPI0_D3     | Input and output | QSPIが選択されている場合、このボールにはQSPIのデータ3ラインとなる<br>SPIO_D3機能があります。                                    |

| G3                          | SDA         | Input and output | I <sup>2</sup> Cシリアル・データ。データを受信または送信。I2Cバス規格に対応。外付けプルアップ抵抗が必要です。                            |

| H16, H17, J16, J17          | V_3V3_IN    | Not applicable   | 3.3V電源。                                                                                     |

| J1                          | TMO_TMR1    | Input and output | 汎用タイマーの入出力汎用タイマーの入出力                                                                        |

| J2                          | TMO_TMR2    | Input and output | 汎用タイマーの入出力汎用タイマーの入出力                                                                        |

| L1, L2, L17, M1, M2, N1, N2 | DNC         | Not applicable   | 何も接続しないでください。このボールは内部で接続されており、フロー<br>ティング状態のままにする必要があります。                                   |

| P16                         | SYS_HWRST   | Input            | プロセッサ・ハードウェア・リセット制御。アサートされるとデバイスを<br>リセットします。このボールには10kΩのプルアップ抵抗を接続します。                     |

| P17                         | SYS_BMODE0  | Input            | ブート・モード制御0。SYS_BMODE0ボールはモジュール内でハイにプル<br>アップされています。                                         |

| R1                          | MOD_LED1    | Output           | MOD_LED1ボールがローになると、2色LED1の緑色LEDがアクティブになります。                                                 |

| R2                          | NET_LED1    | Output           | NET_LED1ボールがローになると、2色LED2の緑色LEDがアクティブになります。                                                 |

| R3                          | NET_LED2    | Output           | NET_LED2ボールがローになると、2色LED2の赤色LEDがアクティブになります。                                                 |

| R15                         | REM_RESET   | Output           | モジュールのfido5200からのリセット出力。                                                                    |

| R16                         | SYS_RESOUT  | Output           | プロセッサ・リセット出力デバイスがリセット状態であることを示します。このボールには $1k\Omega$ のプルダウン抵抗を接続します。                        |

| R17                         | SYS_BMODE1  | Input            | ブート・モード制御1。SYS_BMODE1ボールはモジュール内でローにプル<br>ダウンされています。                                         |

| T1                          | MOD_LED2    | Output           | MOD_LED2ボールがローになると、2色LED1の赤色LEDがアクティブになります。                                                 |

| T6                          | P1_ACTIVITY | Output           | ポート1のアクティビティLED出力ドライバ。                                                                      |

| T7                          | TIMER5      | Output           | 内部高精度タイマー5同期出力。                                                                             |

| Т8                          | SYNC2       | Output           | REMスイッチ同期信号。この信号をアプリケーション・プロセッサに接続すると、アイソクロナス制御アプリケーションで使用できます。                             |

| T10                         | TIMER1      | Input and output | 内部高精度タイマー1同期信号。                                                                             |

| T11                         | TIMER0      | Input and output | 内部高精度タイマー0同期信号。                                                                             |

| T12                         | P2_ACTIVITY | Input and output | ポート2のアクティビティLED出力ドライバ。                                                                      |

| U2                          | P1_RD_N     | Input and output | ポート1の物理的な受信または送信信号(負差動)                                                                     |

| U3                          | P1_RD_P     | Input and output | ポート1の物理的な受信または送信信号 (正差動)                                                                    |

analog.com.jp Rev. A | 11 / 21

# ピン配置およびピン機能の説明

### 表 9. ボール機能の説明

| ボール番号 | 記号             | 方向               | 説明                                 |

|-------|----------------|------------------|------------------------------------|

| U4    | P1_TD_N        | Input and output | ポート2の物理的な送信または受信信号(負差動)            |

| U5    | P1_TD_P        | Input and output | ポート2の物理的な送信または受信信号(正差動)            |

| U6    | P1_LINK_STATUS | Input            | PHYからポート1へのリンク・ステータス。              |

| U7    | SYNC1 Output   |                  | REMスイッチ同期信号。この信号をアプリケーション・プロセッサに接続 |

|       |                |                  | すると、アイソクロナス制御アプリケーションで使用できます。      |

| U8    | TIMER6         | Output           | 内部高精度タイマー6同期出力。                    |

| U10   | TIMER3         | Input and output | 内部高精度タイマー3同期信号。                    |

| U11   | TIMER2         | Input and output | 内部高精度タイマー2同期信号。                    |

| U12   | P2_LINK_STATUS | Input and output | PHYからポート2へのリンク・ステータス。              |

| U13   | P2_RD_N        | Input and output | ポート2の物理的な受信または送信信号(負差動)            |

| U14   | P2_RD_P        | Input and output | ポート2の物理的な受信または送信信号(正差動)            |

| U15   | P2_TD_N        | Input and output | ポート2の物理的な送信または受信信号(負差動)            |

| U16   | P2_TD_P        | Input and output | ポート2の物理的な送信または受信信号 (正差動)           |

analog.com.jp Rev. A | 12 / 21

## 動作原理

ADIN2299の主な使用例は、主流となっている産業用プロトコルにサポートされた堅牢でデターミニスティックなイーサネット機能を必要とするフィールド・デバイスに対し、マルチプロトコルの産業用イーサネット接続を可能にすることです。

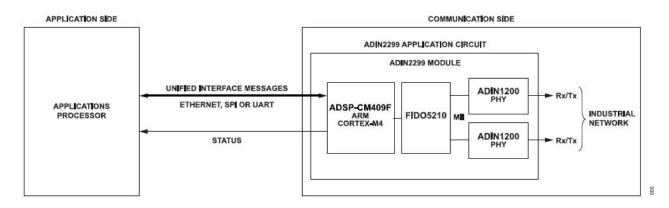

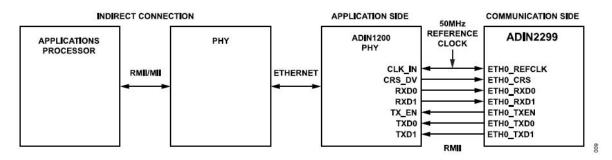

図7にADIN2299のシステム・ブロック図を示します。モジュール内にあるADSP-CM409Fが通信コントローラで、アプリケーション側にあるのがアプリケーション・プロセッサです。アプリケーション・プロセッサは、統合インターフェースの共通言語を介してADIN2299モジュールの通信コントローラと通信を行います。ADIN2299モジュールのアプリケーション・プロセッサのインターフェス・タイミングについては、タイミング特性のセクションに詳しく記載されています。

統合インターフェースについては、Unified Interface Control Document User Guideに詳しい説明があります。

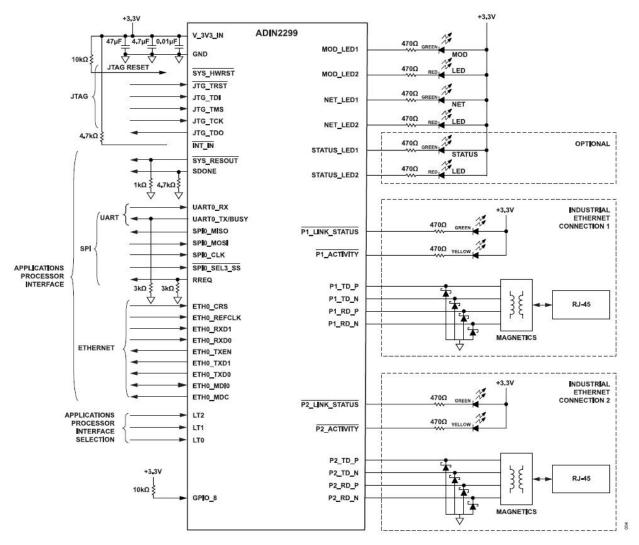

図16の代表的なアプリケーション回路に示すように、ADIN2299 モジュールには以下の接続を行う必要があります。

- ▶ ADIN2299モジュール用の3.3V電源およびグラウンド。

- ▶ 産業用イーサネット接続: PHY出力から産業用ネットワーク へのマグネティクスおよびRJ-45接続。

- ▶ アプリケーション・プロセッサ・インターフェース: SPI、 UART、またはイーサネットを利用。

- ▶ 産業用イーサネットLED (モジュール (MOD) およびネット ワーク (NET))。

図 7. システム・ブロック図

analog.com.jp Rev. A | 13 / 21

### 動作原理

### 産業用イーサネット接続

図16に示すADIN2299アプリケーション回路の各イーサネット・ポートには、リンク・ステータスとアクティビティを示すLEDと共に、マグネティクスおよびコネクタが備わっています。

ADIN2299モジュールには、産業用イーサネット・ネットワークに接続するために2つのPHYがあります。

ADIN2299からユーザ・ボード上のJ-45およびイーサネット・コネクタへの接続については表10を参照してください。また、これらは図16にも図示されています。

表 10. RJ-45およびイーサネット・コネクタへのADIN2299 の接続

| Ball No.         Mnemonic           U2         P1_RD_N           U3         P1_RD_P           U4         P1_TD_N |  |

|------------------------------------------------------------------------------------------------------------------|--|

| U3 P1_RD_P                                                                                                       |  |

|                                                                                                                  |  |

| U4 P1_TD_N                                                                                                       |  |

|                                                                                                                  |  |

| U5 P1_TD_P                                                                                                       |  |

| U13 P2_RD_N                                                                                                      |  |

| U14 P2_RD_P                                                                                                      |  |

| U15 P2_TD_N                                                                                                      |  |

| U16 P2_TD_P                                                                                                      |  |

### アプリケーション・プロセッサ・インターフェース

アプリケーション・プロセッサ・インターフェースは、表11に示すように、LTO~LT2のボールを介して選択できます。ボード設定ファイルで通信インターフェースを選択している場合は、LT2、LT1、LT0はグラウンドに接続したままにしてください。リンク設定ファイルを使用してピン配置をオーバーライドするオプションも利用できます。リンク設定ファイルの詳細については、RPG2 Hardware Design Integration Guideを参照してください。

アプリケーション・プロセッサとADIN2299のADSP-CM409Fとのインターフェース方法に関する通信プロトコルとその詳細については、RPG2 Unified Interface User Guideを参照してください。

表 11. 統合インターフェースのリンク・タイプの選択

|     |     |     | · · · · · · · · · · · · · · · · · · · |

|-----|-----|-----|---------------------------------------|

| LT2 | LT1 | LT0 | Unified Interface Link Type           |

| 0   | 0   | 0   | Ethernet                              |

| 0   | 0   | 1   | Reserved                              |

| 0   | 1   | 0   | SPI                                   |

| 0   | 1   | 1   | Reserved                              |

| 1   | 0   | 0   | UART0                                 |

| 1   | 0   | 1   | Reserved                              |

| 1   | 1   | 0   | Reserved                              |

| 1   | 1   | 1   | Reserved                              |

|     |     |     |                                       |

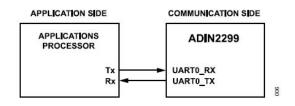

# UARTアプリケーション・プロセッサ・インターフェース

UARTインターフェースを選択した場合、表12に示すボールを使用して図8に示すように、アプリケーション・プロセッサのインターフェースをADIN2299モジュールに接続します。UARTは、8個のデータ・ビット、1個のスタート・ビット、1個のストップ・ビットを用いパリティ・ビットは用いずに、115,200bps~

1,000,000 bpsで構成されています。

図 8. UARTアプリケーション・プロセッサ

表 12. UARTアプリケーション・プロセッサ・インターフェース用ボール

| Mnemonic | Direction | Description           |

|----------|-----------|-----------------------|

| UART0_TX | Output    | UART0 transmit output |

| UART0_RX | Input     | UART0 receive input   |

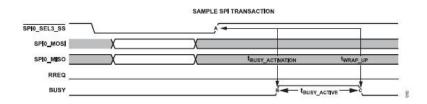

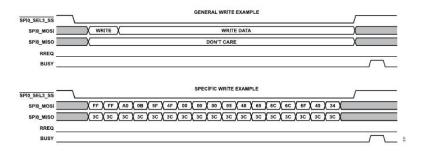

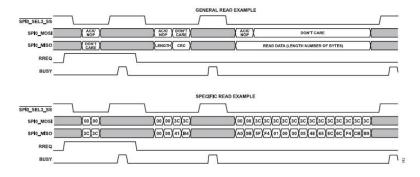

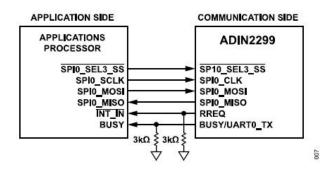

### SPIアプリケーション・プロセッサ・インターフェース

SPIを選択した場合、表14に示すボールを使用して図12に示すように、アプリケーション・プロセッサのインターフェースをADIN2299モジュールに接続します。SPIフォロワの接続は最大10MHzのクロック・レートに対応し、クロック位相ビット(CPHA)=0でデータ取得がリーディング・エッジに、クロック極性ビット(CPOL)=0でリーディング・クロック・エッジが立上がりに設定されます。このタイミングについては、SPIフォロワ・インターフェースのタイミングのセクションで説明しています。統合インターフェースのプロトコルについては、Unified Interface Control Document User Guideに詳しい説明があります。

SPIを使用する場合、BUSY信号とRREQ信号に関して以下の事項を理解しておくことが重要です。

- ▶ BUSY信号では以下の事項があてはまります。

- ▶ BUSYの立下がりエッジは、トランザクション処理が終了 し、SPIフォロワに次のトランザクションに対する準備が できていることを示します。

- ▶ マルチトランザクション読出し動作のシーケンスの詳細を 図11に示します。

- ▶ BUSYは、SPIトランザクションが発生する頻度を設定する ためにのみ用いられます。それ以外の目的でBUSYが立ち 上がることも立ち下がることもありません。

- ▶ SPIトランザクション後はBUSYは常に非アクティブになります。BUSYがハイになり、そのままハイを維持するような状況はありません。

- ▶ BUSYがハイのときにSPIトランザクションが開始される と、その動作は不定となります。

- ▶ 背景にあるハードウェアおよびソフトウェアの制約や考慮 事項により、BUSYには何らかのジッタが生じることが予 想されます。

- SPIO\_SEL3\_SSが非アクティブ状態(ハイ)になった後 1.14μs以上経過してから、BUSYがアクティブ状態(ハイ)になります。BUSYは3.3μs以上アクティブ状態(ハイ)を保ちます。

analog.com.jp Rev. A | 14 / 21

# 動作原理

- ▶ RREQ信号では以下の事項があてはまります。

- ▶ この信号の立上がりエッジでは、データが読出し可能になる前にSPIリーダが短いSPIトランザクションを用いて読出し要求をアクノレッジする必要があります。読出し要求がアクノレッジされると、SPIフォロワはRREQを発してデータが読出し可能となっていることを通知します。

- ▶ 一般的な推奨事項は、SPIリーダがRREQ信号の立上がりエッジで割込みを行うよう設定することです。ただし、割込みを用いることが不可能あるいは望ましくない場合は、RREOをポーリングすることもできます。

- ▶ RREQは読出し動作にのみ関係します。RREQはいかなる 形式の書込み動作にも関係しません。RREQは、書込み動 作中を含む任意のタイミングでアクティブ (ハイ) になる ことができます。

SPIトランザクション例については図9を参照してください。

ビジー信号の場合、これらの信号のタイミングに関して予想できる値がいくつかあります (表13参照)。

表13に示すデータは経験的に収集されたものですが、アプリケーション・プロセッサ・コードや環境など、その他の要因がこれらの数値に影響する可能性があります。

実際のデータを使用した書込みトランザクションの例を図10に、 読出しトランザクションの例を図11に示します。トランザクショ ンは、UI\_EchoReqメッセージとUI\_EchoResメッセージを伴う NI\_Discoverメッセージで、このメッセージはDeveloper PortalのNI-Example-Appワークスペースにあるni-api-srvのコードに詳細が示 されています。

図 9. トランザクション例

表 13. SPIタイミング条件

| Parameter                                          | Minimum (μs) | Maximum (μs) |

|----------------------------------------------------|--------------|--------------|

| BUSY Activation Time, t <sub>BUSY_ACTIVATION</sub> | 1.14         | 27.04        |

| BUSY Active Time, t <sub>BUSY_ACTIVE</sub>         | 3.34         | 33.04        |

| Wrap-Up Time, t <sub>WRAP_UP</sub>                 | 4.48         | 36.16        |

図 10. SPI書込みの一般例および具体例

図 11. SPI読出しの一般例および具体例

analog.com.jp Rev. A | 15 / 21

### 動作原理

SPIにはエラー回復メカニズムもあります。SPIリーダがSPIリンクに問題が生じていることを検知した場合、リンクを一掃してロー・レベルSPI通信をリセットすることができます。これは0バイトまたは1バイトの長さのSPIトランザクションを発行して開始されます。長さが1のトランザクションが発行された場合、MOSIに置かれるバイトの値はSPIフォロワからは無視されます。同様にMISOの値も無視される場合があります。リンクの一掃が2つの読出し動作または書込み動作の間で開始された場合は、特別なことは生じません。読出し動作時に開始された場合は、次のアクションが生じます。

RREQがハイで、かつ、読出し要求アクノレッジ・トランザクションが送信されない場合は、以下が生じます。

- ▶ RREQがローになります。

- ▶ この時点でリンクの一掃が行われると読出し動作が終了し、 SPIリーダはデータ・ステータス・ヘッダーまたはメッセー ジ・データを読み出そうとすることが禁じられます。

- SPIフォロワが送信のために準備していたデータ・ステータス・ヘッダーおよびメッセージ・データは、破棄されます。

- ▶ SPIフォロワは一掃されたメッセージの送信を試行しません。

- ▶ SPIトランザクションはこの時点から通常に動作できます。

RREQがハイで、かつ、読出し要求アクノレッジ・トランザクションが送信された場合は、以下が生じます。

- ▶ RREQがローになります。

- ▶ この時点でリンクの一掃が行われると読出し動作が終了し、 SPIリーダはデータ・ステータス・ヘッダーまたはメッセー ジ・データを読み出そうとすることが禁じられます。

- ▶ SPIフォロワが送信のために準備していたデータ・ステータス・ヘッダーおよびメッセージ・データは、破棄されます。

- ▶ SPIフォロワは一掃されたメッセージの送信を試行しません。

- ▶ SPIトランザクションはこの時点から通常に動作できます。

RREQがアクティブ状態でない場合は、以下が生じます。

- ▶ SPIフォロワが送信のために準備していたデータ・ステータ ス・ヘッダーおよびメッセージ・データは、破棄されます。

- ▶ SPIフォロワは一掃されたメッセージの送信を試行しません。

- ▶ SPIトランザクションはこの時点から通常に動作できます。

図 12. SPIアプリケーション・プロセッサ・インターフェース

表 14. SPIアプリケーション・プロセッサ・インターフェース・ボール

| Mnemonic     | Direction | Description                                                                                     |

|--------------|-----------|-------------------------------------------------------------------------------------------------|

| SPI0_SEL3_SS | Input     | SPI0 Follower Select Input.                                                                     |

| SPI0_CLK     | Input     | SPI0 Clock Input.                                                                               |

| SPI0_MOSI    | Input     | SPI0 Leader Out, Follower In.                                                                   |

| SPI0_MISO    | Output    | SPI0 Leader In, Follower Out.                                                                   |

| RREQ         | Output    | RREQ is a signal that notifies the application side that a message is ready to be read.         |

| BUSY         | Output    | Busy Signal. This signal indicates to the application side that the communication side is busy. |

# イーサネット・アプリケーション・プロセッサ・インターフェースの選択

図13に、RMIIを通じたイーサネット・アプリケーション・プロセッサ・インターフェースの直接接続を示します。

図 13. RMIIを通じた直接接続

図14に、イーサネット・アプリケーション・プロセッサ・インターフェースの間接接続を示します。

analog.com.jp Rev. A | 16 / 21

# 動作原理

図 14. 間接接続

表 15. イーサネット・アプリケーション・インターフェースの信号

| Mnemonic          | Direction        | Description                                                                                                     |

|-------------------|------------------|-----------------------------------------------------------------------------------------------------------------|

| ETH0_REFCLK Input |                  | EMAC0 Reference Clock. Externally supplied Ethernet clock.                                                      |

| ETH0_CRS Input    |                  | EMAC0 Carrier Sense. Multiplexed on alternate clock cycles.                                                     |

|                   | Input            | CRS: asserted by the PHY when either the transmit or receive medium is not idle. Deasserted when both are idle. |

|                   | Input            | RXDV: asserted by the PHY when the data on RXD0 is valid.                                                       |

| ETH0_RXD0         | Input            | EMAC0 Receive Data 0. Receive data bus.                                                                         |

| ETH0_RXD1         | Input            | EMAC0 Receive Data 1. Receive data bus.                                                                         |

| ETH0_TXEN         | Input and output | EMAC0 Transmit Enable. When asserted, ETH0_TXEN indicates that the data on TXD0 is valid.                       |

| ETH0_TXD0         | Output           | EMAC0 Transmit Data 0. Transmit data bus.                                                                       |

| ETH0_TXD1         | Output           | EMAC0 Transmit Data 1. Transmit data bus.                                                                       |

analog.com.jp Rev. A | 17 / 21

## 動作原理

### 産業用イーサネットのMOD LEDおよびNET LED

LEDの動作は各プロトコルによって規定されています。表16においてLED1とLED2で表されるMOD LEDとNET LEDの機能は、選択した産業用イーサネット・プロトコルによって異なります。この機能については、RPG2 Hardware Design Integration Guideに説明があります。

### プログラミング

モジュールは、以下の方法によって安全に更新することができます。

▶ RPG2 Web Server User Guideで説明されているWebサーバー・ インターフェースを介した産業用イーサネット・ポート。 ▶ RPG2 Programming Guideに詳細が説明されているJTAG接続。

モジュールを購入する代わりにADIN2299の回路図がリファレンス設計としてカスタマ・ボードに直接実装されている場合、プログラミングの唯一のオプションは、Seggerツール・チェーンを用いたJTAG接続を介することです。なお、シリアル・ワイヤ・デバッグ接続はサポートされていない点に注意してください。詳細については、RPG2 Programming Guideを参照してください。

### アプリケーション回路サポート回路

図16に示すADIN2299アプリケーション回路に必要な外付け部品を、表16に示します。

表 16. 外付け部品

|                                              |             | Recon          | nmended Component                     |                                                                                                                                                                                                                                           |

|----------------------------------------------|-------------|----------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Component                                    | Value       | Manufacturer   | Manufacturer Part Number <sup>1</sup> | Notes/Comments                                                                                                                                                                                                                            |

| Capacitors                                   |             |                |                                       |                                                                                                                                                                                                                                           |

| Decoupling for 3.3 V                         | 47 μF       | User specified | User specified                        | It is recommended to decouple each voltage rail with 47                                                                                                                                                                                   |

|                                              | 0.1 μF      | User specified | User specified                        | $\mu F$ , 0.1 $\mu F$ , and 4.7 $\mu F$ capacitors. These are at a 20%                                                                                                                                                                    |

|                                              | 4.7 μF      | User specified | User specified                        | tolerance.                                                                                                                                                                                                                                |

| LEDs                                         |             |                |                                       |                                                                                                                                                                                                                                           |

| LED1 and LED2                                |             | Kingbright     | KPBA-3010ESGC                         | Dual color, green and red.                                                                                                                                                                                                                |

| Transient Voltage<br>Suppressor (TVS) Diodes |             | Littelfuse     | SP0504SHTG                            | Each device incorporates multiple 5.5 V clamping, 8.5 V reverse standoff diodes to provide electrostatic discharge (ESD) protection. One TVS device is required per Ethernet port, and two are required per ADIN2299 application circuit. |

| Resistors                                    |             |                |                                       |                                                                                                                                                                                                                                           |

|                                              | $470\Omega$ |                |                                       | LED current limit.                                                                                                                                                                                                                        |

| Other Components                             |             |                |                                       |                                                                                                                                                                                                                                           |

| Ferrite Bead                                 |             | Murata         | BLM15EG121SN1D                        | 1.5 A, 120 Ω at 100 MHz.                                                                                                                                                                                                                  |

| MagJack                                      |             | Wurth          | 7499010121A                           | RJ-45 connector with integrated magnetics and LEDs.                                                                                                                                                                                       |

| Reset Supervisor                             |             | Analog Devices | AMD708SARZ                            | 2.9 V power monitoring reset supervisor chip.                                                                                                                                                                                             |

<sup>1</sup> 推奨部品または同等の部品を使用してください。

analog.com.jp Rev. A | 18 / 21

# 動作原理

### リフロー・プロファイル

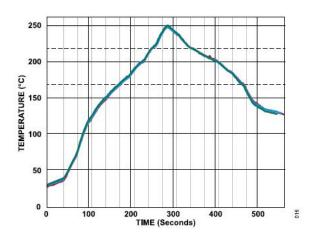

ADIN2299モジュールをPCBにハンダ付けする場合、モジュールが適切にPCBにハンダ付けされるよう、リフロー温度プロファイルに関して従うべき指定があります(図15および表17を参照)。

図 15. 高ピーク・リフロー温度プロファイル(SMTプロセス)

表 17. 高ピーク・リフロー温度プロファイル仕様

| Item                                                                                  | Temperature Change           | Profile Data(seconds) |

|---------------------------------------------------------------------------------------|------------------------------|-----------------------|

| Ramp Rate (°C/sec)                                                                    | 30℃ to approximately 150℃    | 0.86                  |

| Soak Time (sec) at 170 $^{\circ}\mathrm{C}$ to Approximately 220 $^{\circ}\mathrm{C}$ | 70°C to approximately 100°C  | 77.07                 |

| Dwell Time (sec) at More Than 220°C                                                   | 60°C to approximately 90°C   | 84.82                 |

| Peak Temperature (°C)                                                                 | 245°C to approximately 255°C | 247.69                |

| Cooling Rate (°C/sec)                                                                 | Peak to approximately 150℃   | 0.50                  |

analog.com.jp Rev. A | 19 / 21

# 代表的なアプリケーション回路

図 16.

analog.com.jp Rev. A | 20 / 21

# 外形寸法

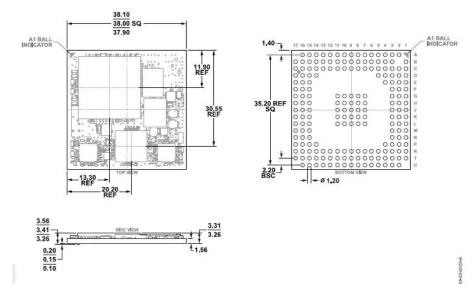

図 17. 194ボール・チップ・スケール・パッケージ・ボール・グリッド・アレイ[CSP\_BGA] (BC-194-1) 寸法:mm

更新: 2022年9月7日

### オーダー・ガイド

| Model <sup>1</sup> | Temperature Range | Package Description                     | Package Option |

|--------------------|-------------------|-----------------------------------------|----------------|

| ADIN2299BBCZ       | 0°C to +85°C      | 194-Ball CSP-BGA (38mm x 38mm x 3.41mm) | BC-194-1       |

<sup>1</sup> Z=RoHS準拠製品。

### 評価用ボード

| Model <sup>1</sup> | Package Description              |

|--------------------|----------------------------------|

| RPG2-ENZ           | Evaluation Board for EtherNet/IP |

| EV-RPG2-ECZ        | Evaluation Board for EtherCAT    |

| EV-RPG2-PNZ        | Evaluation Board for PROFINET    |

1 Z = RoHS準拠製品。

©2023 Analog Devices, Inc. All rights reserved.

本 社/〒105-6891 東京都港区海岸1-16-1 ニューピア竹芝サウスタワービル 10F

電話03(5402)8200

大阪営業所 / 〒532-0003 大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 10F 電話06 (6350) 6868