# VCO 内蔵マイクロ波広帯域シンセサイザ

#### 特長

▶ 出力周波数範囲:800MHz~12.8GHz

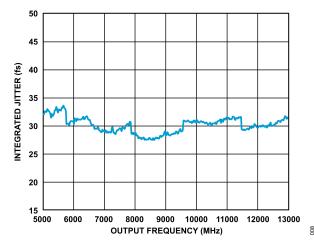

▶ ジッタ:30fs<sub>RMS</sub>未満(f<sub>OUT</sub> = 9.001GHz、

f<sub>REF</sub> = f<sub>PFD</sub> = 250MHz、フラクショナル・モードの場合)

▶ 広帯域位相ノイズ・フロア: -160dBc/Hz(12.8GHz)

▶ PLL 仕様

▶ 正規化帯域内位相ノイズ・フロア

▶ -239dBc/Hz : インテジャー・モード、 -237dBc/Hz : フラクショナル・モード

▶ 正規化 1/f 位相ノイズ・フロア

▶ -287dBc/Hz : 1Hz に正規化

▶ -147dBc/Hz: 1GHzに正規化(10kHz)

▶ 位相検出器の周波数:625MHz(インテジャー・モード)

▶ 25 ビット固定、49 ビット結合フラクショナル・モジュラス

▶ リファレンス入力周波数:4GHz

▶ PFD スプリアス: -95dBc (代表値)

▶ リファレンス出力間遅延仕様

▶ 温度係数: 0.06 ps/°C

▶ 調整ステップ・サイズ: <1ps

▶ マルチチップ出力位相アライメント

▶ SYNC ピンまたは EZSync 方式による

▶ 3.3V および 5V の電源

▶ ADIsimPLL™ループ・フィルタ設計ツールに対応

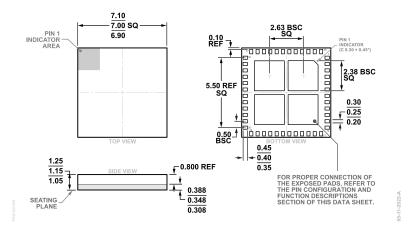

▶ 48 ピン、7mm × 7mm LGA パッケージを採用

▶ 動作ジャンクション温度範囲: -40°C~+125°C

#### アプリケーション

- ▶ ワイヤレス・インフラストラクチャ(MC-GSM、5G)

- ▶ 試験および計測

- ▶ 航空宇宙/防衛

## 概要

ADF4368 は、VCO を内蔵した高性能、超低ジッタ、インテジャーN およびフラクショナル N のフェーズ・ロック・ループ (PLL) で、周波数変換アプリケーションに最適です。

この高性能 PLL は、-239 dBc/Hz の性能指数、正規化された -287 dBc/Hz の極めて低い 1/f ノイズ、および高い PFD 周波数を 持ち、極めて小さいインバンド・ノイズと統合ジッタを実現できます。ADF4368 は、内蔵ダブラなしで800MHz~12.8GHzの範囲の任意の周波数を生成できるため、低調波フィルタが不要となります。 $\Sigma$ - $\Delta$  変調器は、ヘルツ単位の周波数分解能を可能にする 25 ビットの固定モジュラスの他、17 ビットの可変モジュラスを備えているため、より分解能が高く柔軟な周波数プランニングを実現します。12.8 GHz で9 dBm の電力をシングルエンド構成で出力でき、また、16 段階の電力調整機能を備えていることから、様々なアプリケーションで極めて高い利便性を発揮します。

フェーズド・アレイ・レーダーや Massive MIMO システムなどの多重周波数変換アプリケーションでは、SYNC 入力またはEZSync™を使用して、複数の ADF4368 からの出力を揃えることができます。EZSync 方式は、SYNC 信号をすべてのデバイスに正確に分配することが困難な場合に使用されます。確定的遅延や遅延調整機能が必要なアプリケーションに対し、リファレンスと出力の間の遅延を 1ps 未満の分解能で設定できます。このリファレンス出力間遅延は、複数のデバイスや温度変化に対して確保されるため、予測可能かつ高精度なマルチチップ・アライメントが可能です。

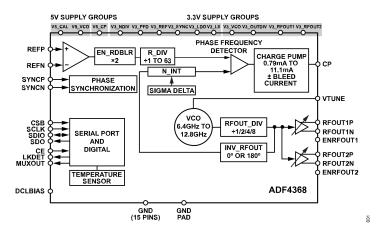

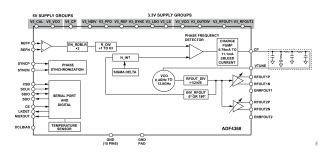

ADF4368 のブロック図は単純で、簡素化されたシリアル・ペリフェラル・インターフェース(SPI)レジスタ・マップ、外部SYNC 入力、そしてインテジャー・モードとフラクショナル・モードの両方において繰返し可能なマルチチップ位相アライメントなどの特長を備えていることから、開発時間を短縮できます。

# 機能ブロック図

図 1. ADF4368 のブロック図

Rev. 0 ※こちらのデータシートには正誤表が付属しています。当該資料の最終ページ以降をご参照ください。

**DOCUMENT FEEDBACK**

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の 特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するもの でもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有者の財産です。 ※日本搭版資料は REVISION が古い場合があります。最新の内容については、英語版を一発の大きい。

# 目次

| 特長                    | 1    |

|-----------------------|------|

| アプリケーション              |      |

| 概要                    | 1    |

| 機能ブロック図               | 1    |

| 仕様                    | 3    |

| シリアル・インターフェースのタイミング特性 | 7    |

| タイミング図                | 7    |

| 絶対最大定格                | 8    |

| トランジスタ数               | 8    |

| 熱抵抗                   | 8    |

| 静電放電(ESD)定格           | 8    |

| ESD に関する注意            | 8    |

| ピン配置およびピン機能の説明        | 9    |

| 代表的な性能特性              | . 11 |

| 動作原理                  | . 16 |

| はじめに             | 16 |

|------------------|----|

| 出力周波数            | 16 |

| 回路の説明            | 16 |

| アプリケーション情報       | 22 |

| ループ・フィルタの設計      | 22 |

| リファレンス源に関する考慮事項  | 22 |

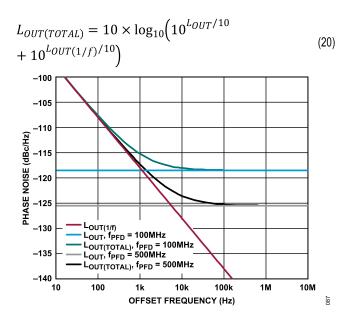

| 出力の位相ノイズ特性       | 23 |

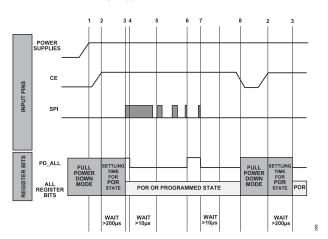

| パワーアップと初期化のシーケンス | 23 |

| 電源およびバイパス        | 26 |

| レジスタ・マップ         | 27 |

| レジスタの詳細          | 30 |

| 外形寸法             | 54 |

| オーダー・ガイド         | 54 |

| <b>証価田ボード</b>    | 54 |

# 改訂履歴

3/2023—Revision 0: Initial Version

# 仕様

特に指定のない限り、 $V_{3.3V\_1} = V_{3.3V\_2} = 3.15V \sim 3.45V$ 、 $V_{V5\_VCO} = V_{V5\_CP} = V_{V5\_CAL} = 4.75V \sim 5.25V$ 、すべての電圧は GND 基準、 $T_A = -40^{\circ}C \sim 105^{\circ}C_o$

表 1. 電気仕様

| Parameter                                      | Symbol            | Min              | Тур          | Max              | Unit      | Test Conditions/Comments                                                                    |

|------------------------------------------------|-------------------|------------------|--------------|------------------|-----------|---------------------------------------------------------------------------------------------|

| REFERENCE INPUTS (REFP, REFN)                  |                   |                  |              |                  |           |                                                                                             |

| Input Frequency                                | f <sub>REF</sub>  | 10               |              | 4000             | MHz       |                                                                                             |

| Input Signal Level                             | $V_{REF}$         | 0.5              |              | 2.6              | V p-p     | Differential                                                                                |

| Min Input Slew Rate                            |                   |                  | 100          |                  | V/µs      |                                                                                             |

| Input Duty Cycle                               |                   |                  | 50           |                  | %         |                                                                                             |

| Self-Bias Voltage                              |                   |                  | 1.85         |                  | V         |                                                                                             |

| Input Resistance                               |                   |                  | 3            |                  | kΩ        | Differential                                                                                |

| Input Capacitance                              |                   |                  | 1            |                  | pF        | Differential                                                                                |

| Input Current                                  |                   |                  | 2            |                  | μA        |                                                                                             |

| REFERENCE PEAK DETECTOR                        |                   |                  |              |                  |           |                                                                                             |

| Input Frequency                                |                   | 10               |              | 4000             | MHz       |                                                                                             |

| Minimum Input Signal Detected (REF_OK = 1)     |                   |                  | 200          |                  | $mV_{pp}$ | f <sub>REF</sub> = 100 MHz, single-ended sine wave                                          |

| Maximum Input Signal Not Detected (REF_OK = 0) |                   |                  | 160          |                  | $mV_{pp}$ | f <sub>REF</sub> = 100 MHz, single-ended sine wave                                          |

| SYNC INPUTS (SYNCP, SYNCN)                     |                   |                  |              |                  |           |                                                                                             |

| Input Signal Level                             | V <sub>REF</sub>  | 0.41             |              | 2.6 <sup>1</sup> | V p-p     | LVDS mode, differential                                                                     |

|                                                | $V_{REF}$         | 0.5 <sup>1</sup> |              | 2.6 <sup>1</sup> | V p-p     | CML mode, differential                                                                      |

| Self-Bias Voltage                              |                   |                  | 1.3          |                  | V         | LVDS mode                                                                                   |

| Č                                              |                   |                  | 1.85         |                  | V         | CML mode                                                                                    |

| Input Resistance                               |                   |                  | 3            |                  | kΩ        | Differential                                                                                |

| Input Capacitance                              |                   |                  | 1            |                  | pF        | Differential                                                                                |

| Input Current                                  |                   |                  | 3            |                  | μA        |                                                                                             |

| REFERENCE DIVIDER (R)                          |                   |                  |              |                  |           |                                                                                             |

| R                                              |                   | 1                |              | 63               |           | All integers included                                                                       |

| REFERENCE DOUBLER                              |                   |                  |              |                  |           |                                                                                             |

| Input Frequency                                | f <sub>RDBL</sub> | 10               |              | 250              | MHz       | EN_RDBLR = 1                                                                                |

| PHASE/FREQUENCY DETECTOR (PFD)                 |                   |                  |              |                  |           |                                                                                             |

| Input Frequency                                | f <sub>PFD</sub>  |                  |              |                  |           |                                                                                             |

|                                                |                   | 3 <sup>1</sup>   |              | 625              | MHz       | Integer mode                                                                                |

|                                                |                   | 31               |              | 250              | MHz       | Fractional mode sync or non-sync applications                                               |

|                                                |                   | 31               |              | 250 <sup>1</sup> | MHz       | Fractional mode phase resync applications when f <sub>OUT</sub> ≥ 3 GHz                     |

|                                                |                   | 75 <sup>1</sup>  |              | 250 <sup>1</sup> | MHz       | Fractional mode phase resync applications when f <sub>OUT</sub> < 3 GHz                     |

| CHARGE PUMP (CP)                               |                   |                  |              |                  |           |                                                                                             |

| Output Current Range                           | I <sub>CP</sub>   |                  | 0.79 to 11.1 |                  | mA        | Set by CP_I                                                                                 |

| Output Current Source/Sink Accuracy            |                   |                  | ±2           |                  | %         | All setting, = $V_{CP} = V_{V5\_CP}/2$                                                      |

| Output Current Source/Sink Matching            |                   |                  | ±2           |                  | %         | All setting, V <sub>CP</sub> = V <sub>V5_CP</sub> /2                                        |

| Output Current vs. Output Volt Sensitivity     |                   |                  | 0.2          |                  | %V/V      | $1.4 \text{ V} < \text{V}_{\text{V5}\_\text{CP}} < \text{V}_{\text{CP-5V}} - 1.6 \text{ V}$ |

| Output Current vs. Temperature                 |                   |                  | 400          |                  | ppm/C     | $V_{CP} = V_{V5\_CP} / 2$                                                                   |

| Output High-Z Leakage Current                  |                   |                  | -0.01        |                  | μA        | Minimum $I_{CP}$ , 1.4 V < $V_{V5\_CP}$ < $V_{CP-5V}$ – 1.6 V                               |

| Output High-Z Leakage Current                  |                   |                  | -0.3         |                  | μA        | Maximum $I_{CP}$ , 1.4 V < $V_{V5\_CP}$ < $V_{CP-5V}$ – 1.6 \                               |

| VCO                                            |                   |                  |              |                  |           |                                                                                             |

| Frequency Range                                | f <sub>VCO</sub>  | 6.4              |              | 12.8             | GHz       |                                                                                             |

| Tuning Sensitivity <sup>2, 3</sup>             | K <sub>VCO</sub>  |                  | 0.75 to 1.25 |                  | %Hz/V     |                                                                                             |

analog.com.jp Rev. 0 | 3 of 54

# 仕様

表 1. 電気仕様(続き)

| Parameter                                      | Symbol                                 | Min                     | Тур                                      | Max  | Unit     | Test Conditions/Comments                                                                                                                       |

|------------------------------------------------|----------------------------------------|-------------------------|------------------------------------------|------|----------|------------------------------------------------------------------------------------------------------------------------------------------------|

| DIV_RCLK VCO Calibration Frequency             | f <sub>DIV_RCLK</sub>                  |                         |                                          | 125  | MHz      | Must set DCLK_MODE = 1, when f <sub>DIV_RCLK</sub> > 80 MHz                                                                                    |

| FEEDBACK (N) AND OUTPUT DIVIDER (O)            |                                        |                         |                                          |      |          |                                                                                                                                                |

| N                                              |                                        | 4                       |                                          | 4095 |          | Integer mode                                                                                                                                   |

|                                                |                                        | 19                      |                                          | 4095 |          | Fractional mode                                                                                                                                |

| 0                                              |                                        | 1                       |                                          | 8    |          | 1, 2, 4, 8                                                                                                                                     |

| RF OUTPUTS (RFOUT1P/N, RFOUT2P/N)              |                                        |                         |                                          |      |          | Differential termination = $100 \Omega$ for all RF output specifications, unless noted                                                         |

| Output Frequency                               | f <sub>OUT</sub>                       | 0.8                     |                                          | 12.8 | GHz      |                                                                                                                                                |

| Output Single-Ended Power                      | V <sub>OD</sub>                        |                         | 9                                        |      | dBm      | CLK1_OPWR = CLK2_OPWR = 15, f <sub>OUT</sub> = 4<br>GHz to 12.8 GHz                                                                            |

|                                                |                                        |                         | 5.5                                      |      | dBm      | CLK1_OPWR = CLK2_OPWR = 10, f <sub>OUT</sub> = 4<br>GHz to 12.8 GHz                                                                            |

|                                                |                                        |                         | 1.5                                      |      | dBm      | CLK1_OPWR = CLK2_OPWR = 5, f <sub>OUT</sub> = 4<br>GHz to 12.8 GHz                                                                             |

|                                                |                                        |                         | -2                                       |      | dBm      | CLK1_OPWR = CLK2_OPWR = 0, f <sub>OUT</sub> = 4<br>GHz to 12.8 GHz                                                                             |

| Output Resistance                              |                                        |                         | 100                                      |      | Ω        | Differential                                                                                                                                   |

| Output Common Mode                             |                                        |                         | V <sub>3.3V_2</sub> –<br>V <sub>OD</sub> |      | V        | No pull-up inductor                                                                                                                            |

|                                                |                                        |                         | $V_{3.3V_2}$                             |      | V        | With pull-up inductor                                                                                                                          |

| Output Rise Time                               | t <sub>R</sub>                         |                         | 18                                       |      | ps       | 20%-80%, CLK1_OPWR = CLK2_OPWR = 10,                                                                                                           |

| Output Fall Time                               | t <sub>F</sub>                         |                         | 18                                       |      | ps       | 80%-20%, CLK1_OPWR = CLK2_OPWR = 10,                                                                                                           |

| Output Duty Cycle                              |                                        |                         | 50                                       |      | %        |                                                                                                                                                |

| Skew, RFOUT1 to RFOUT2                         |                                        |                         | 3 ± 1                                    |      | ps       | One ADF4368 device                                                                                                                             |

|                                                |                                        |                         | 3 ± 1                                    |      | ps       | Across multiple ADF4368 devices, T <sub>J</sub> within 10°C, same R_DIV, CLKOUT_DIV, EN_RDBLR used                                             |

| REFERENCE INPUT TO OUTPUT DELAY                |                                        |                         |                                          |      |          | Device setup for all delay specifications,<br>unless noted, measure rising reference edge<br>at REFP input to rising edge at RFOUT1P<br>output |

| Propagation Delay                              | t <sub>PD</sub>                        |                         | 190                                      |      | ps       | REF_SEL = 0, R = 1, doubler = disabled                                                                                                         |

| Propagation Delay Temperature Coefficient      | t <sub>PD</sub>                        |                         | 0.06                                     |      | ps/°C    | REF SEL = 0                                                                                                                                    |

| LOGIC INPUTS (CSB, SCLK, SDIO, ENCLK1, ENCLK2) |                                        |                         |                                          |      |          |                                                                                                                                                |

| Input High Voltage                             | V <sub>INH</sub>                       | 1.2                     |                                          |      | V        |                                                                                                                                                |

| Input Low Voltage                              | V <sub>INL</sub>                       |                         |                                          | 0.6  | V        |                                                                                                                                                |

| Input Current (High, Low)                      | I <sub>IH</sub> /I <sub>IL</sub>       |                         |                                          | ±1   | μA       |                                                                                                                                                |

| Input Capacitance                              | C <sub>IN</sub>                        |                         | 2                                        |      | pF       |                                                                                                                                                |

| LOGIC INPUT (CE)                               |                                        |                         |                                          |      | <u> </u> |                                                                                                                                                |

| Input High Voltage                             | V <sub>INH-3V</sub>                    | 1.8                     |                                          |      | V        |                                                                                                                                                |

| Input Low Voltage                              | V <sub>INL-3V</sub>                    |                         |                                          | 8.0  | V        |                                                                                                                                                |

| Input Current (High, Low)                      | I <sub>IH-3V</sub> /I <sub>IL-3V</sub> |                         |                                          | ±1   | μA       |                                                                                                                                                |

| Input Capacitance                              | C <sub>IN-3V</sub>                     |                         | 1                                        |      | pF       |                                                                                                                                                |

| LOGIC OUTPUTS (SDIO, SDO, LKDET, MUXOUT)       | 111.04                                 |                         |                                          |      | '        |                                                                                                                                                |

| Output High Voltage                            | V <sub>OH</sub>                        | 1.5                     | 1.8                                      |      | V        | $I_{OH}$ = 500 $\mu$ A, 1.8 V output selected (default setting)                                                                                |

| Output High Voltage                            | V <sub>OH-3V</sub>                     | V <sub>3.3V</sub> - 0.4 |                                          |      |          | I <sub>OH</sub> = 500 μA, 3.3 V output selected, set by voltage on V_LDO pin                                                                   |

analog.com.jp Rev. 0 | 4 of 54

# 仕様

表 1. 電気仕様(続き)

| Parameter                          | Symbol                           | Min  | Тур | Max  | Unit | Test Conditions/Comments                                                                                                                      |

|------------------------------------|----------------------------------|------|-----|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Output Low Voltage                 | V <sub>OL</sub>                  |      |     | 0.4  | V    | I <sub>OL</sub> = 500 μA                                                                                                                      |

| SDO High-Z Leakage                 | I <sub>ZH</sub> /I <sub>ZL</sub> |      |     | ±1   | μA   |                                                                                                                                               |

| POWER SUPPLIES                     |                                  |      |     |      |      | Device setup is default configuration for all supply current specifications, unless noted                                                     |

| V5_VCO Supply Range                | V <sub>V5_VCO</sub>              | 4.75 | 5   | 5.25 | V    |                                                                                                                                               |

| V5_CAL Supply Range                | V <sub>V5 CAL</sub>              | 4.75 | 5   | 5.25 | V    |                                                                                                                                               |

| V5_CP Supply Range                 | V <sub>V5_CP</sub>               | 4.75 | 5   | 5.25 | V    |                                                                                                                                               |

| V <sub>3.3V_1</sub> Supply Range   | V <sub>3.3V_1</sub>              | 3.15 | 3.3 | 3.45 | V    | Group 1: V3_LS, V3_LDO, V3_REF, V3_PFD, V3_NDIV, V3_SYNC                                                                                      |

| V <sub>3.3V_2</sub> Supply Range   | V <sub>3.3V_2</sub>              | 3.15 | 3.3 | 3.45 | V    | Group 2: V3_RFOUT1, V3_RFOUT2, V3_VCO, V3_CLKDIV                                                                                              |

| V5_VCO Supply Current              | I <sub>V5_VCO</sub>              |      | 98  |      | mA   | f <sub>OUT</sub> = 12.8 GHz                                                                                                                   |

|                                    |                                  |      | 173 | 220  | mA   | f <sub>OUT</sub> = 6.4 GHz                                                                                                                    |

| V5_CAL Supply Current              | I <sub>V5_CAL</sub>              |      | 50  |      | μA   |                                                                                                                                               |

|                                    | _                                |      | 8   |      | mA   | During VCO calibration                                                                                                                        |

| V5_CP Supply Current               | I <sub>V5_CP</sub>               |      | 58  | 67   | mA   | I <sub>CP</sub> = 11.1 mA, CP_I = 15                                                                                                          |

|                                    |                                  |      | 41  |      | mA   | $I_{CP} = 0.79 \text{ mA}, CP_I = 0$                                                                                                          |

|                                    |                                  |      | 3.2 |      | mA   | Additional current when EN_BLEED = 1, BLEED_I = 8191                                                                                          |

| V <sub>3.3V_1</sub> Supply Current | I <sub>3.3V_1</sub>              |      | 185 | 210  | mA   | f <sub>REF</sub> = 122.88 MHz, f <sub>PFD</sub> = 245.76 MHz,<br>fractional mode, CP_I = 15, PD_SYNC = 1<br>(sync disabled)                   |

|                                    |                                  |      | 4   |      | mA   | Additional current when PD_LD = 0                                                                                                             |

|                                    |                                  |      | 4   |      | mA   | Additional current when PD_RDET = 1                                                                                                           |

| V3_SYNC Supply Current             | I <sub>V3_SYNC</sub>             |      | 15  |      | mA   | PD_SYNC = 0 (synchronization is enabled)                                                                                                      |

| V3_RFOUTx Supply Current           | I <sub>V3_RFOUT</sub>            |      | 35  |      | mA   | CLKx_OPWR = 0                                                                                                                                 |

|                                    | .V3_KF001                        |      | 47  |      | mA   | CLKx_OPWR = 4                                                                                                                                 |

|                                    |                                  |      | 65  |      | mA   | CLKx_OPWR = 8                                                                                                                                 |

|                                    |                                  |      | 90  |      | mA   | CLKx_OPWR = 12                                                                                                                                |

|                                    |                                  |      | 105 |      | mA   | CLKx OPWR = 15                                                                                                                                |

| V3_OUTDIV Supply Current           | I <sub>V3_OUTDIV</sub>           |      | 108 |      | mA   | CLKOUT DIV = 0 (divide by 1)                                                                                                                  |

| 70_00.2.1 очерну очилош            | .03_001010                       |      | 132 |      | mA   | CLKOUT_DIV = 3 (divide by 8)                                                                                                                  |

| V <sub>3.3V_2</sub> Supply Current | I <sub>3.3V_2</sub>              |      | 149 |      | mA   | ENRFOUT1 = low, CLK2_OPWR = 0<br>(minimum power), CLKOUT_DIV = 0, f <sub>OUT</sub> = 9.6 GHz                                                  |

|                                    |                                  |      | 218 |      | mA   | ENRFOUT1 = low, CLK2_OPWR = 15<br>(maximum power), CLKOUT_DIV = 0, f <sub>OUT</sub> = 9.6 GHz                                                 |

|                                    |                                  |      | 172 |      | mA   | ENRFOUT1 = low, CLK2_OPWR = 0<br>(minimum power), CLKOUT_DIV = 1, f <sub>OUT</sub> = 5.6 GHz                                                  |

|                                    |                                  |      | 241 |      | mA   | ENRFOUT1 = low, CLK2_OPWR = 15<br>(maximum power), CLKOUT_DIV = 1, f <sub>OUT</sub> = 5.6 GHz                                                 |

| Typical Power Dissipation          | P <sub>DIS</sub>                 |      | 2.3 |      | W    | ENRFOUT1 = low, CLK2_OPWR = 15<br>(maximum power), CLKOUT_DIV = 0, f <sub>OUT</sub><br>= 9.6 GHz, SYNC block powered down,<br>fractional mode |

|                                    |                                  |      | 2.1 |      | W    | ENRFOUT1 = low, CLK2_OPWR = 15<br>(maximum power), CLKOUT_DIV = 1, f <sub>OUT</sub>                                                           |

analog.com.jp Rev. 0 | 5 of 54

# 仕様

表 1. 電気仕様(続き)

| Parameter                                         | Symbol                  | Min | Тур  | Max  | Unit              | Test Conditions/Comments                                                     |

|---------------------------------------------------|-------------------------|-----|------|------|-------------------|------------------------------------------------------------------------------|

|                                                   |                         |     |      |      |                   | = 5.6 GHz, SYNC block powered down, fractional mode                          |

| Typical Power Down Current, 3.3 V                 |                         |     | 11   | 15   | mA                | PD_ALL = 1, I <sub>3.3V_1</sub> + I <sub>3.3V_2</sub>                        |

| Typical Power Down Current, 5 V Supplies          |                         |     | 350  | 750  | μA                | PD_ALL = 1, I <sub>V5 VCO</sub> + I <sub>V5 CAL</sub> + I <sub>V5 CP</sub>   |

| Typical Disable Current, 3.3 V Supplies           |                         |     | 100  | 1500 | μA                | CE = low, $I_{3.3V_{-1}} + I_{3.3V_{-2}}$                                    |

| Typical Disable Current, 5 V Supplies             |                         |     | 350  | 750  | μA                | CE = low, I <sub>V5_VCO</sub> + I <sub>V5_CAL</sub> + I <sub>V5_CP</sub>     |

| RF OUTPUT NOISE CHARACTERISTICS                   |                         |     |      |      |                   |                                                                              |

| 12.8 GHz Output Frequency                         |                         |     |      |      |                   | f <sub>REF</sub> = f <sub>PFD</sub> = 250 MHz, fractional mode, CP_I<br>= 15 |

| Phase Noise Floor                                 |                         |     | -160 |      | dBc/Hz            |                                                                              |

| RMS Jitter, 100 Hz to 100 MHz Integration         |                         |     | 32   |      | fs <sub>RMS</sub> |                                                                              |

| 9.001 GHz Output Frequency                        |                         |     |      |      |                   | f <sub>REF</sub> = f <sub>PFD</sub> = 250 MHz, fractional mode, CP_I<br>= 15 |

| Phase Noise Floor                                 |                         |     | -160 |      | dBc/Hz            |                                                                              |

| RMS Jitter, 100 Hz to 100 MHz Integration         |                         |     | 29   |      | fs <sub>RMS</sub> |                                                                              |

| 7.6 GHz Output Frequency                          |                         |     |      |      |                   | f <sub>REF</sub> = f <sub>PFD</sub> = 250 MHz, fractional mode, CP_I<br>= 15 |

| Phase Noise Floor                                 |                         |     | -160 |      | dBc/Hz            |                                                                              |

| RMS Jitter, 100 Hz to 100 MHz Integration         |                         |     | 31   |      | fs <sub>RMS</sub> |                                                                              |

| 6.4 GHz Output Frequency                          |                         |     |      |      |                   | f <sub>REF</sub> = f <sub>PFD</sub> = 250 MHz, fractional mode, CP_I<br>= 15 |

| Phase Noise Floor                                 |                         |     | -161 |      | dBc/Hz            |                                                                              |

| RMS Jitter, 100 Hz to 100 MHz Integration         |                         |     | 30   |      | fs <sub>RMS</sub> |                                                                              |

| 5.025 GHz Output Frequency                        |                         |     |      |      |                   | f <sub>REF</sub> = f <sub>PFD</sub> = 250 MHz, fractional mode, CP_I<br>= 15 |

| Phase Noise Floor                                 |                         |     | -163 |      | dBc/Hz            |                                                                              |

| RMS Jitter, 100 Hz to 100 MHz Integration         |                         |     | 33   |      | fs <sub>RMS</sub> |                                                                              |

| Normalized In-Band Phase Noise Floor <sup>4</sup> |                         |     |      |      |                   |                                                                              |

| L <sub>NORM-INT</sub>                             |                         |     | -239 |      | dBc/Hz            |                                                                              |

| L <sub>NORM-FRC</sub>                             |                         |     | -237 |      | dBc/Hz            |                                                                              |

| Normalized 1/f Phase Noise Floor <sup>4, 5</sup>  |                         |     |      |      |                   |                                                                              |

| $L_{1/f}^5$                                       |                         |     | -287 |      | dBc/Hz            | Normalized to 1 Hz                                                           |

| L <sub>1/f_1G_10k</sub> <sup>5</sup>              |                         |     | -147 |      | dBc/Hz            | Normalized to 1 GHz at 10 kHz offset                                         |

| Integer Boundary Spurs (Filtered)                 | IBS                     |     | -95  |      | dBc               | Spur is out of the loop bandwidth                                            |

| Integer Boundary Spurs (Unfiltered)               | IBS                     |     | -60  |      | dBc               | Measured at 5 kHz offset from integer channel                                |

| PFD Spur                                          |                         |     | -95  |      | dBc               |                                                                              |

| TEMPERATURE SENSOR (ADC)                          |                         |     |      |      |                   |                                                                              |

| ADC Clock Frequency                               | f <sub>ADC_CLK</sub>    |     |      | 400  | kHz               | ADC clock divider output                                                     |

| ADC Clock Divider Frequency                       | f <sub>ADC_CLKDIV</sub> |     |      | 125  | MHz               | ADC clock divider input                                                      |

| Resolution                                        |                         |     |      | 8    | Bits              |                                                                              |

Rev. 0 | 6 of 54 analog.com.jp

<sup>&</sup>lt;sup>1</sup> 設計および特性評価に基づきます。 <sup>2</sup> 電源再投入後またはソフトウェア・パワーオン・リセット後にキャリブレーションを行ったデバイスに対し 1.60V  $\leq$  V<sub>VTUNE</sub>  $\leq$  2.85V の範囲で有効です。

<sup>3</sup>特性評価に基づきます。

<sup>&</sup>lt;sup>4</sup> これらの数値は ADIsimPLL でモデル化したものです。

$<sup>^5</sup>$  積分範囲は  $1kHz\sim f_{OUT}$ です。

# 仕様

# シリアル・インターフェースのタイミング特性

特に指定のない限り、 $V_{3.3V\_1} = V_{3.3V\_2} = 3.15V \sim 3.45V$ 、 $V_{V5\_VCO} = V_{V5\_CP} = V_{V5\_CAL} = 4.75V \sim 5.25V$ 、すべての電圧は GND 基準、 $T_A = -40^{\circ}C \sim +105^{\circ}C_{\circ}$

表 2. シリアル・インターフェースのタイミング特性

| Parameter                                | Symbol                   | Min | Тур | Max | Unit | Test Conditions/Comments             |

|------------------------------------------|--------------------------|-----|-----|-----|------|--------------------------------------|

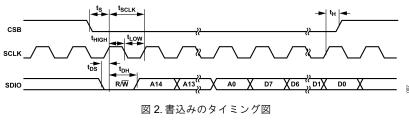

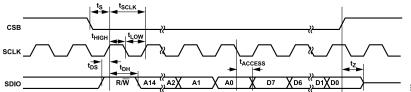

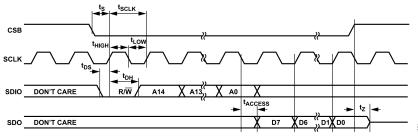

| SERIAL INTERFACE (CSB, SCLK, SDIO, SDO)  |                          |     |     |     |      | See Figure 2, Figure 3, and Figure 4 |

| SCLK Frequency                           | f <sub>SCLK</sub>        |     |     | 65  | MHz  |                                      |

| SCLK Pulse Width High                    | t <sub>HIGH</sub>        | 7.6 |     |     | ns   |                                      |

| SCLK Pulse Width Low                     | t <sub>LOW</sub>         | 7.6 |     |     | ns   |                                      |

| SDIO Setup Time                          | t <sub>DS</sub>          | 3   |     |     | ns   |                                      |

| SDIO Hold Time                           | t <sub>DH</sub>          | 3   |     |     | ns   |                                      |

| SCLK Fall Edge to SDIO Valid Prop Delay  | t <sub>ACCESS</sub> SDIO | 7.6 |     |     | ns   |                                      |

| SCLK Fall Edge to SDO Valid Prop Delay   | t <sub>ACCESS</sub> SDO  | 7.6 |     |     | ns   |                                      |

| CSB Rising Edge to SDIO High-Z           | t <sub>Z</sub> -         | 7.6 |     |     | ns   |                                      |

| CSB Falling Edge to SCLK Rise Setup Time | t <sub>S</sub>           | 3   |     |     | ns   |                                      |

| SCLK Rising Edge to CSB Rise Hold Time   | t <sub>H</sub>           | 3   |     |     | ns   |                                      |

# タイミング図

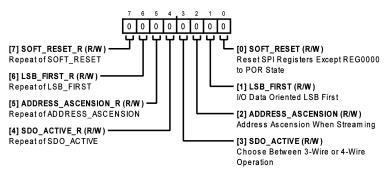

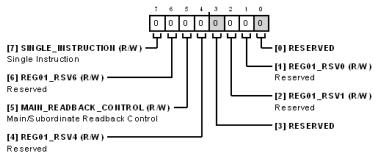

図 3.3 線式読出しのタイミング図 (SDO\_ACTIVE = 0)

図 4.4 線式読出しのタイミング図(SDO\_ACTIVE = 1)

analog.com.jp Rev. 0 | 7 of 54

# 絶対最大定格

特に指定のない限り、TA=25℃。

#### 表 3. 絶対最大定格

| Parameter                                                           | Rating                                                                            |

|---------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| V <sub>3.3V_1</sub> (V3_LS, V3_LDO, V3_REF, V3_PFD, V3_NDIV) to GND | -0.3 V to +3.6 V                                                                  |

| $V_{3.3V\_2}$ (V3_VCO, V3_OUTDIV, V3_RFOUT1, V3_FOUT2) to GND       | -0.3 V to +3.6 V                                                                  |

| V <sub>5V</sub> (V5_CAL, V5_VCO, V5_CP) to GND                      | -0.3 V to +5.5 V                                                                  |

| Voltage on CP Pin                                                   | -0.3 V to V5_CP + 0.3 V                                                           |

| Digital Outputs (MUXOUT, LKDET, SDO, SDIO)                          | 5 mA                                                                              |

| RFOUT1P, RFOUT1N, RFOUT2P, RFOUT2N                                  | Maximum (GND - 0.3 V, V <sub>3.3V_2</sub> - 1.2 V) to V <sub>3.3V_2</sub> + 0.3 V |

| REFP, REFN                                                          | -0.65 V to V <sub>3.3V 1</sub> + 0.65 V                                           |

| Voltage on all Other Pins                                           | $-0.3 \text{ V to V}_{3.3 \text{V}} + 0.3 \text{ V}$                              |

| REFP to REFN and SYNCP to SYNCN                                     | ±1.35 V                                                                           |

| Temperature                                                         |                                                                                   |

| Operating Junction Range <sup>1</sup>                               | -40°C to +125°C                                                                   |

| Storage Range                                                       | -65°C to +125°C                                                                   |

| Maximum Junction                                                    | 125°C                                                                             |

| Reflow Soldering                                                    |                                                                                   |

| Peak Temperature                                                    | 260°C                                                                             |

| Time at Peak Temperature                                            | 30 sec                                                                            |

<sup>「</sup>デバイスは、動作ジャンクション温度範囲全域にわたり、仕様規定された性能限界を確実に満たします。

上記の絶対最大定格を超えるストレスを加えると、デバイスに 恒久的な損傷を与えることがあります。この規定はストレス定 格のみを指定するものであり、この仕様の動作のセクションに 記載する規定値以上でのデバイス動作を定めたものではありま せん。デバイスを長時間にわたり絶対最大定格状態に置くと、 デバイスの信頼性に影響を与えることがあります。

#### トランジスタ数

ADF4368のトランジスタ数は199076 (CMOS) および3366 (バイポーラ)です。

# 熱抵抗

熱性能は、プリント回路基板 (PCB) の設計と動作環境に直接 関連しています。PCB の熱設計には、細心の注意を払う必要が あります。

$\theta_{JA}$  は、1 立方フィートの密閉容器内で測定された、自然対流下での周囲とジャンクションの間の熱抵抗です。 $\theta_{JC}$  は、ジャンクションとケースの間の熱抵抗です。

表 4. 熱抵抗

| Package Type          | θ <sub>JA</sub> | θ <sub>JC-TOP</sub> | θ <sub>JC</sub> .<br>BOTTOM | $\theta_{JB}$ | $\Psi_{ m JT}$ | $\Psi_{JB}$ | Unit |

|-----------------------|-----------------|---------------------|-----------------------------|---------------|----------------|-------------|------|

| CC-48-13 <sup>1</sup> | 22.38           | 16.86               | 5.1                         | 8.33          | 1.35           | 7.89        | °C/W |

<sup>「</sup>テスト条件1:熱抵抗のシミュレーション値は、熱抵抗パッドをグランド・プレーンにハンダ付けした4層PCBを使用して測定しています。

## 静電放電(ESD)定格

以下の ESD 情報は、ESD に敏感なデバイスを取り扱うために示したものですが、対象は ESD 保護区域内だけに限られます。

ANSI/ESDA/JEDDEC JS-001 準拠の人体モデル (HBM)。

ANSI/ESDA/JEDEC JS-002 準拠の帯電デバイス・モデル (CDM)。

#### ADF4368 の ESD 定格

表 5. ADF4368 の ESD 定格

| ESD Model | Withstand Threshold (V) | Class |

|-----------|-------------------------|-------|

| HBM       | 4000                    | 3A    |

| CDM       | 1000                    | C3    |

# ESD に関する注意

ESD(静電放電)の影響を受けやすいデバイスです。

電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術であるESD保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

analog.com.jp Rev. 0 | 8 of 54

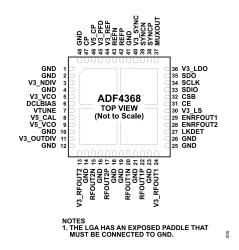

# ピン配置およびピン機能の説明

図 5. ピン配置

表6 ピン機能の説明

| 表 6. ピン機能                                                        | 記号                  | 説明                                                                                                                                                                              |

|------------------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| д ;                                                              |                     |                                                                                                                                                                                 |

| 1, 2, 4, 10, 12,<br>14, 16, 18, 19,<br>21, 23, 25, 26,<br>41, 48 | GND                 | 負側電源 (グラウンド) 。これらのピンは、グラウンド・パッドに直接接続する必要があります。                                                                                                                                  |

| 3                                                                | V3_NDIV             | PLL 帰還分周器回路用の 3.15V~3.45V 正側電源ピン。このピンは 3.3V 電源グループ 1 内の他のピンに短絡します。                                                                                                              |

| 5                                                                | V3_VCO              | VCO 回路の 3.3V 部分用の 3.15V~3.45V 正側電源ピン。このピンは 3.3V 電源グループ 2 内の他のピンに短絡します。                                                                                                          |

| 6                                                                | DCLBIAS             | このピンには接続しないでください。                                                                                                                                                               |

| 7                                                                | VTUNE               | VCO チューニング入力。通常、この周波数制御ピンは外部ループ・フィルタに接続します。                                                                                                                                     |

| 8                                                                | V5_CAL              | VCO キャリブレーション回路用の 4.75V~5.25V 正側電源ピン。このピンは、V5_VCO 電源プレーンに短絡できます。                                                                                                                |

| 9                                                                | V5_VCO              |                                                                                                                                                                                 |

| 11                                                               | V3_OUTDIV           | 出力分周器回路用の 3.15V~3.45V 正側電源ピン。このピンは 3.3V 電源グループ 2 内の他のピンに短絡します。                                                                                                                  |

| 13                                                               | V3_RFOUT2           | RF 出力 2 バッファ回路用の 3.15V~3.45V 正側電源ピン。このピンは 3.3V 電源グループ 2 内の他のピンに短絡します。                                                                                                           |

| 15, 17                                                           | RFOUT2N,<br>RFOUT2P | RF 出力 2 信号。VCO 出力分周器はバッファされ、これらのピンに差動で印加されます。出力には、1 つの側あたり $50\Omega$ (代表値) の出力抵抗( $100\Omega$ の差動インピーダンス)があります。伝送線の他端は通常、出力間に $100\Omega$ を接続して終端されます。出力振幅はシリアル・ポートを介して設定可能です。 |

| 20, 22                                                           | RFOUT1N,<br>RFOUT1P | RF 出力 1 信号。VCO 出力分周器はバッファされ、これらのピンに差動で印加されます。出力には、1 つの側あたり $50\Omega$ (代表値) の出力抵抗( $100\Omega$ の差動インピーダンス)があります。伝送線の他端は通常、出力間に $100\Omega$ を接続して終端されます。出力振幅はシリアル・ポートを介して設定可能です。 |

| 24                                                               | V3_RFOUT1           | RF 出力 1 バッファ回路用の 3.15V~3.45V 正側電源ピン。このピンは 3.3V 電源グループ 2 内の他のピンに短絡します。                                                                                                           |

| 27                                                               | LKDET               | PLL ロック検出。この出力は、PLL のロック状態を表します。LKDET がロジック・ハイの場合、PLL はロックされています。                                                                                                               |

| 28                                                               | ENRFOUT2            | RF 出力 2 バッファのイネーブル。3.3V の CMOS 入力です。ENRFOUT2 がハイ・レベルの場合、RFOUT2P と RFOUT2N の出力バッファはアクティブになります。ENRFOUT2 がロー・レベルの場合、RFOUT2P と RFOUT2N はパワーダウンします。                                  |

| 29                                                               | ENRFOUT1            | RF 出力 1 バッファのイネーブル。3.3V の CMOS 入力です。ENRFOUT1 がハイ・レベルの場合、RFOUT1P と RFOUT1N の出力バッファはアクティブになります。ENRFOUT2 がロー・レベルの場合、RFOUT1P と RFOUT1N はパワーダウンします。                                  |

| 30                                                               | V3_LS               | 内部レベル・シフト回路用の 3.15V~3.45V 正側電源ピン。このピンは 3.3V 電源グループ 1 内の他のピンに短絡します。                                                                                                              |

| 31                                                               | CE                  | チップイネーブル。1.8Vの CMOS レベルには対応していません。この CMOS 入力はハイに駆動されるとデバイスをイネーブルします。ロジック・ローになるとデバイスをディスエーブルし、デバイスは完全なパワーダウン状態になるためレジスタがリセットされます。対照的に、PD_ALL ビットはデバイスをパワーダウンしますが、レジスタはリセットしません。  |

| 32                                                               | CSB                 | シリアル・ポート・チップ・セレクト。1.8V および 3.3V に対応する CMOS 入力です。この CMOS 入力は、ローに駆動されるとシリアル・ポート通信のバーストを開始し、再度ハイに駆動されるとバーストを終了します。                                                                 |

| 33                                                               | SDIO                | シリアル・データ入出力。1.8V および3.3V に設定可能な CMOS 入出力。入力に設定された場合、シリアル・ポートはデータにこの CMOS 入力を使用します。3 線式リードバック・モード(デフォルト・モード)の場合、このピンは読出し通信 バーストの間にシリアル・ポートからデータを出力します。                           |

analog.com.jp Rev. 0 | 9 of 54

# ピン配置およびピン機能の説明

# 表 6. ピン機能の説明(続き)

| ピン番号        | 記号              | 説明                                                                                                                                                                                                                                                          |

|-------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 34          | SCLK            | シリアル・ポート・クロック。1.8V および 3.3V に対応。この CMOS 入力は、立上がりエッジでシリアル・ポート入力データをクロック同期します。                                                                                                                                                                                |

| 35          | SDO             | オプションのシリアル・データ出力。1.8V および 3.3V に設定可能な CMOS 出力。3 線式モード(デフォルト・モード)の場合、このスリーステート CMOS ピンは高インピーダンス状態を維持します。4 線式リードバック・モードの場合、このピンは読出し通信バーストの間にシリアル・ポートからデータを出力します。CSB がデアサートされると、SDO は高インピーダンスに戻ります。オプションで、200kΩ より高い値の抵抗を接続して、出力がフロート状態にならないようにできます。           |

| 36          | V3_LDO          | 内部 LDO 回路用の 3.15V~3.45V 正側電源ピン。このピンは 3.3V 電源グループ 1 内の他のピンに短絡します。                                                                                                                                                                                            |

| 37          | MUXOUT          | 内部デバイス・マルチプレクサ出力。この出力ピンは、複数の内部ノードに接続して、工場出荷テストやデバッグのために<br>使用できます。                                                                                                                                                                                          |

| 38, 39      | SYNCP,<br>SYNCN | 同期入力信号。どちらの RF 出力信号もこのピンの入力信号に同期できます。複数のチップを位相同期するために使用されます。この差動入力は、高コモンモード入力信号と低コモンモード入力信号のどちらも受容します(SPI のビット設定による)。                                                                                                                                       |

| 40          | V3_SYNC         | 同期回路用の 3.15V~3.45V 正側電源。このピンは 3.3V 電源グループ 1 内の他のピンに短絡します。                                                                                                                                                                                                   |

| 42, 43      | REFP, REFN      | リファレンス入力信号。この差動入力は、遅延一致アンプ(DMA)でバッファされ、出力伝搬遅延に対する制御されたリファレンスを提供します(デフォルト・モード、REF_SEL = 0)。低スルー・レートのリファレンス入力信号の場合は、代わりにシリアル・ポートを介してロー・ノイズ・アンプ(LNA)を選択できます(REF_SEL = 1)。リファレンス入力は自己バイアスされており、1µF のコンデンサで AC カップリングする必要があります。リファレンス入力は、差動入力またはシングルエンド入力を受容します。 |

| 44          | V3_REF          | PLL リファレンス回路用の 3.15V~3.45V 正側電源ピン。このピンは 3.3V 電源グループ 1 内の他のピンに短絡します。                                                                                                                                                                                         |

| 45          | V3_PFD          | PFD 回路用の 3.15V~3.45V 正側電源ピン。このピンは 3.3V 電源グループ 1 内の他のピンに短絡します。                                                                                                                                                                                               |

| 46          | V5_CP           | チャージ・ポンプ回路用の 4.75V~5.25V 正側電源ピン。このピンは V5_VCO 電源プレーンから絶縁してください。                                                                                                                                                                                              |

| 47          | СР              | チャージ・ポンプ出力。通常、この双方向電流出力は外部ループ・フィルタに接続します。                                                                                                                                                                                                                   |

| Exposed Pad | EP              | 露出パッド。LGAには露出パドルがあり、これを GND(負側電源)に接続する必要があります。露出パッドが PCB ランドに直接ハンダ付けする必要があります。PCB ランド・パターンには、グラウンド・インダクタンスと熱抵抗の両方を低く抑えるために、グランド・プレーンへの複数のサーマル・ビアを設ける必要があります。                                                                                                |

analog.com.jp Rev. 0 | 10 of 54

# 代表的な性能特性

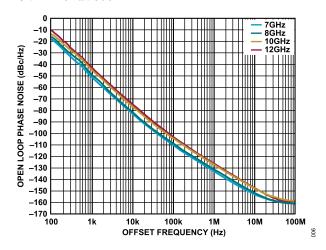

図 6. 異なる周波数でのオープン・ループ VCO の位相ノイズと オフセット周波数の関係

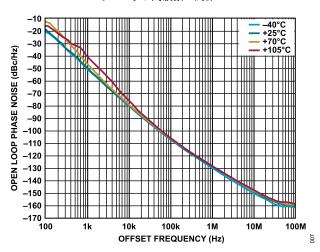

図 7. 12GHz における異なる温度でのオープン・ループ VCO の 位相ノイズとオフセット周波数の関係

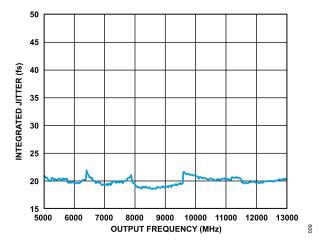

図 8. フラクショナル・モードでの 1kHz~100MHz の積分ジッタ  $(f_{PFD}$  = 250MHz)

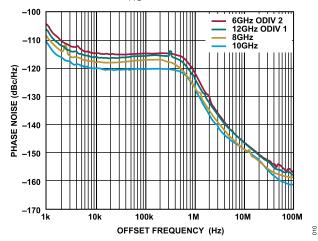

図 10. 異なる周波数でのクローズ・ループの位相ノイズ

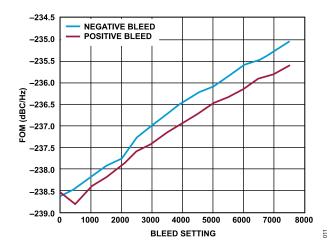

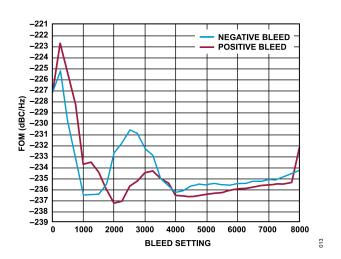

図 11. L<sub>NORM-INT</sub> とブリード設定値の関係

analog.com.jp Rev. 0 | 11 of 54

# 代表的な性能特性

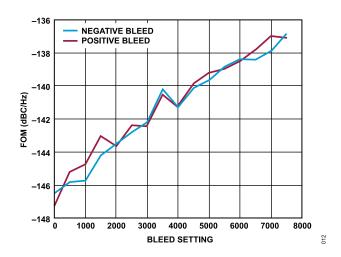

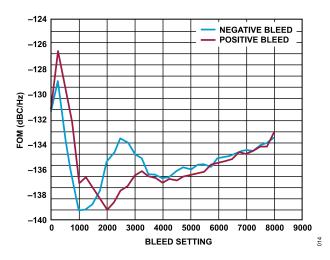

図 12. L<sub>1/f</sub> とブリード設定値の関係

図 13. L<sub>NORM-FRC</sub>(f<sub>REF</sub> = 500MHz、f<sub>PFD</sub> = 250MHz、RF<sub>Out</sub> = 12,001MHz)とブリード設定値の関係

図 14. L<sub>NORM-FRC</sub> とブリード設定値の関係

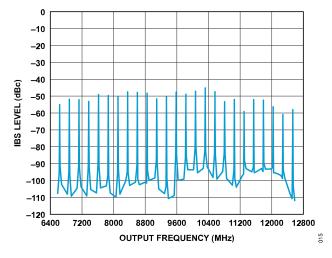

図 15. オフセットが 5kHz、50kHz、200kHz、300kHz、400kHz、960kHz、10MHz で測定した最も厳しい場合の IBS(f<sub>PFD</sub> = 245.76MHz)

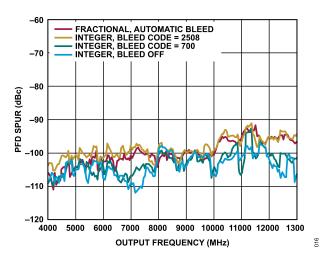

図 16. PFD のスプリアスと出力周波数

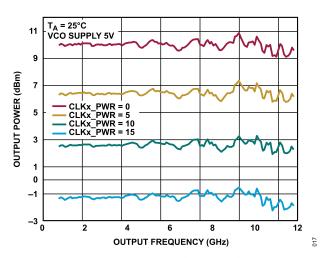

図 17. 異なる出力電力設定でのディエンベディングした シングルエンド出力電力

analog.com.jp Rev. 0 | 12 of 54

# 代表的な性能特性

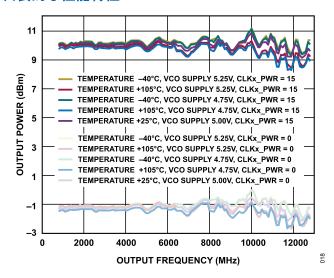

図 18. 異なる温度および電源でのディエンベディングしたシングルエンド出力電力と出力周波数の関係

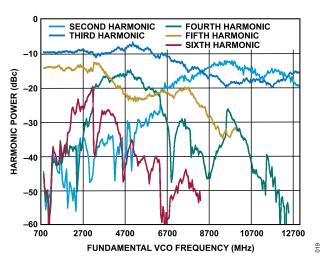

図 19. 高調波出力と VCO 周波数の関係

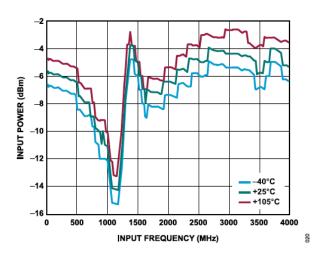

図 20. DMA バッファに対する REF\_OK = 1 とした場合の 最小入力信号

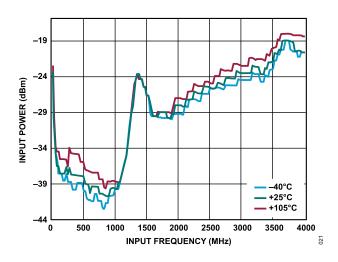

図 21. LNA のリファレンス入力感度と温度の関係

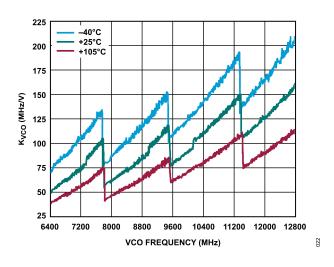

図 22. 異なる温度での K<sub>VCO</sub> と VCO 周波数の関係

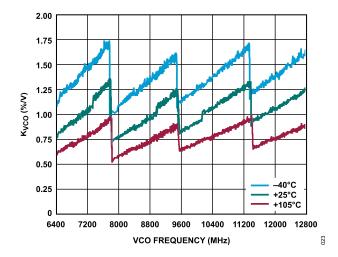

図 23. 異なる温度での K<sub>VCO</sub> のパーセント感度と VCO 周波数の関係

analog.com.jp Rev. 0 | 13 of 54

# 代表的な性能特性

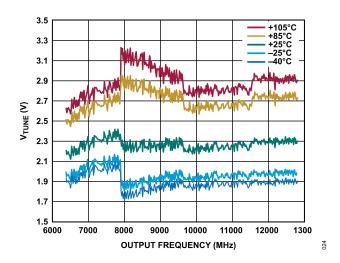

図 24. デバイスをロックした場合の V<sub>TUNE</sub> と出力周波数の関係 (25°C)

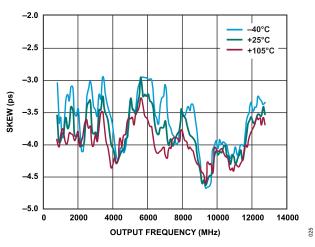

図 25. 出力間のスキュー

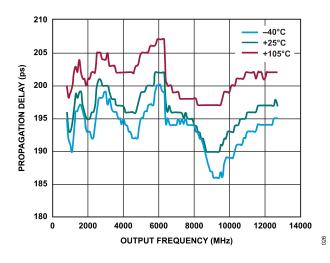

図 26. 伝搬遅延

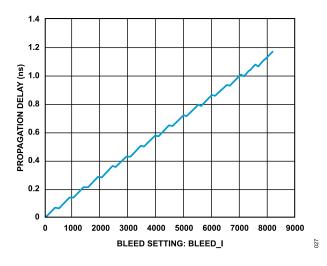

図 27. 伝搬遅延とブリード設定値の関係

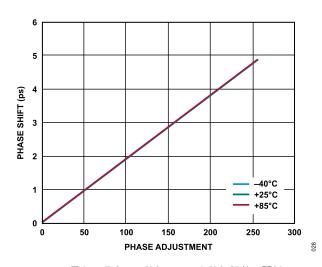

図 28. 異なる温度での位相シフトと位相調整の関係 (RF<sub>Out</sub> = 12,775MHz)

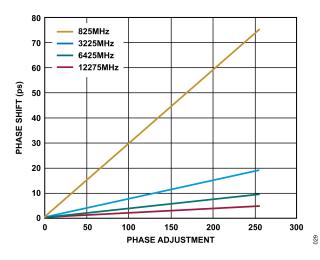

図 29. 異なる周波数での位相シフトと位相調整の関係

analog.com.jp Rev. 0 | 14 of 54

# 代表的な性能特性

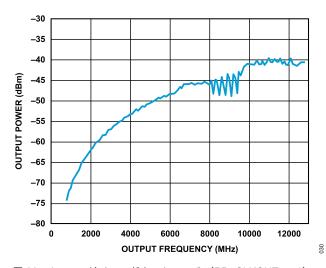

図 30. バッファがパワーダウンしている(PD\_CLKOUTx = 1) 場合の出力電力

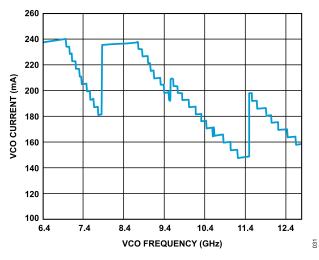

図 31. VCO 電流と VCO 周波数の関係

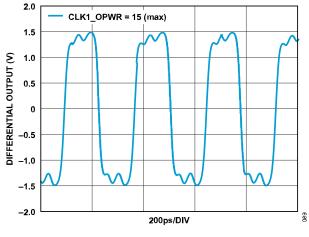

図 32. 差動出力(3GHz)

#### 動作原理

#### はじめに

PLL は、概念的には周波数逓倍器とみなせる、複合的な帰還システムです。このシステムは、REFP および REFN での周波数入力を逓倍し、高くなった周波数を RFOUT1P、RFOUT2P、RFOUT1N、RFOUT2N に出力します。PFD、チャージ・ポンプ、出力分周器、帰還分周器、VCO、外部ループ・フィルタが帰還ループを形成し、出力周波数を正確に制御します(図 33 参照)。周波数の分解能を設定するには、リファレンス分周器、またはリファレンス・ダブラを使用します。

図 33. PLL ループの回路図

# 出力周波数

ループがロックされている場合、VCO の出力に現れる fvco (Hz) は、リファレンス周波数( $f_{REF}$ )および次式で与えられる O、R、N の各値によって決まります。

$$f_{VCO} = f_{REF} \times \frac{D \times N \times O}{R} \tag{1}$$

ここでNは、

$$N = N_{INT} + \frac{FRAC 1WORD + \frac{FRAC 2WORD}{MOD 1WORD}}{MOD 1WORD}$$

(2)

出力される PFD 周波数 (fpfD) は、

$$f_{PFD} = \frac{f_{REF} \times D}{R} \tag{3}$$

fvcoは次式のように表すこともできます。

$$f_{VCO} = f_{PFD} \times N \times O \tag{4}$$

出力分周器の出力に現れる出力周波数  $f_{RFOUT}$  は、次式のようになります。

$$f_{RFOUT} = \frac{f_{VCO}}{O} \tag{5}$$

#### 回路の説明

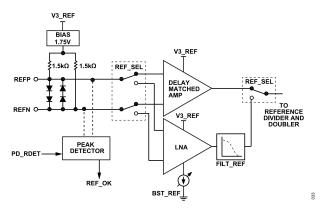

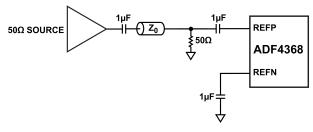

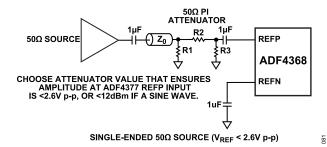

# リファレンス入力バッファ

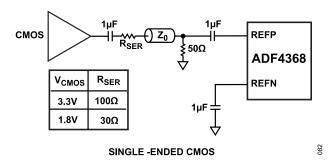

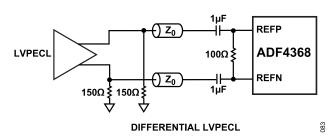

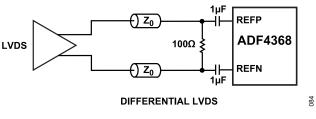

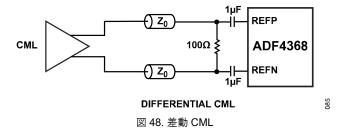

PLLのリファレンス周波数は REFP ピンと REFN ピンに差動で印加されます。これらの高インピーダンス入力は自己バイアスされており、 $1\mu$ F のコンデンサで AC カップリングする必要があります(簡略化した回路図については図 34 を参照)。あるいは、これらの入力をシングルエンドとして使用することもできます。そのためには、REFP にリファレンス周波数を印加し、REFN は $1\mu$ F のコンデンサで GND にバイパスします。

図 34. リファレンス入力段

REFP 入力と REFN 入力には高品質の信号を印加する必要があります。これらの入力が PLL 全体に周波数リファレンスを提供しているためです。デバイスの帯域内位相ノイズ性能を実現するには、スルー・レートが 1000V/μs 以上の連続波信号または方形波を印加してください。リファレンス入力信号の条件やインターフェース方法に関する詳細については、アプリケーション情報のセクションを参照してください。

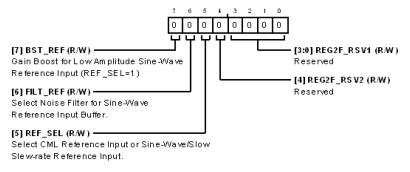

REF\_SEL ビットを 0 に設定すると、DMA バッファが選択されます。DMA は、方形波や高周波数で大振幅のサイン波などの、高スルー・レート信号に対し最適化されています。DMA では、リファレンス入力からクロック出力への伝搬遅延が制御されるため、広い温度範囲にわたり時間ゼロのマルチチップ・クロック・アライメントが容易に可能です。

REF\_SELビットを1に設定すると、LNAが選択されます。LNAは、低周波数または小振幅のサイン波などの、低スルー・レート信号に対し最適化されています。

帯域内ノイズ性能と伝搬遅延を最適なものにするために、 REF\_SEL ビットは適切に設定する必要があります。推奨する設 定については、表7を参照してください。

表 7. REF SEL の設定

| REF_SEL | Sine Wave Slew Rate (V/µs) | Square Wave    | Optimized t <sub>PD</sub> |

|---------|----------------------------|----------------|---------------------------|

| 0       | ≥1000                      | Preferred      | Yes                       |

| 1       | <1000                      | Not applicable | Not applicable            |

サイン波のスルー・レートを計算するには、次式を用います。

$$Slew Rate = 2 \times \pi \times f \times V \tag{6}$$

ここで、

f=サイン波の周波数

$V = サイン波の振幅 (V_{PK})$

FILT\_REF ビットは、リファレンス入力の LNA のローパス・フィルタを制御するビットで、リファレンスの広帯域ノイズを制限するために  $f_{REF}$  に基づいてサイン波信号用に設定する必要があります。この FILT\_REF ビットは、正規化された帯域内位相ノイズ・フロア LNORM を実現するよう適切に設定する必要があります。推奨する設定については、表 8 を参照してください。方形波を入力する場合は、FILT\_REF を 0 に設定します。

analog.com.jp Rev. 0 | 16 of 54

#### 動作原理

表 8. FILT REFの設定

| FILT_REF | Sine Wave f <sub>REF</sub> | Square Wave f <sub>REF</sub> |

|----------|----------------------------|------------------------------|

| 0        | ≥ 20 MHz                   | All f <sub>REF</sub>         |

| 1        | < 20 MHz                   | Not applicable               |

LNA のリファレンス入力バッファが飽和しないよう、BST\_REF ビットは入力信号レベルに基づいて設定する必要があります。BST\_REF の設定は、入力がサイン波か方形波かによらず同じです。推奨する設定については表 9 を参照してください。また、設定例についてはアプリケーション情報のセクションを参照してください。

表 9. BST REF の設定

| BST_REF | Sine Wave f <sub>REF</sub> |

|---------|----------------------------|

| 0       | ≥ 1.6 V <sub>PP</sub>      |

| 1       | < 1.6 V <sub>PP</sub>      |

# リファレンス・ピーク検出器

REFP 入力と REFN 入力にはリファレンス入力ピーク検出回路があり、リファレンス信号の存在を検出し REF\_OK ステータス・フラグを発します。これは、シリアル・ポート・レジスタ REG0058 を通じて読み出せます。検出閾値付近で REF\_OK が不安定になるのを防ぐため、回路にはヒステリシスが設けられています。

このピーク検出器は RMS 検出器に類似したものです。そのため、サイン波入力と方形波入力の検出閾値は 4/π だけ異なっています。 REF OK の検出値については表 10 を参照してください。

表 10. REF\_OK のステータス出力と REF 入力の関係

| REF_OK | F_OK Sine Wave f <sub>REF</sub> Square Wave f |                        |

|--------|-----------------------------------------------|------------------------|

| 1      | ≥ 200 mV <sub>PP</sub>                        | ≥ 155 mV <sub>PP</sub> |

| 0      | < 180 mV <sub>PP</sub>                        | < 140 mV <sub>PP</sub> |

#### リファレンス分周器(R)とダブラ(D)

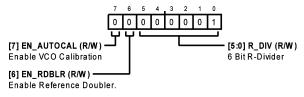

EN\_RDBLR ビットが 1 に設定されている場合、周波数通倍器によって周波数が 2 倍にされてリファレンス分周器に送られます。リファレンス・ダブラと直列に 6 ビット分周器 R\_DIV が接続されており、これを用いて周波数を減少して PFD に送ります。リファレンスの分周比 R は  $1\sim63$  の任意の整数値に設定できます。分周比 R を直接設定するには、REG0020 の R\_DIV ビットを用います。R、D と  $f_{REF}$ 、 $f_{PFD}$ 、 $f_{VCO}$ 、 $f_{OUT}$  の各周波数との関係については、出力周波数のセクションを参照してください。

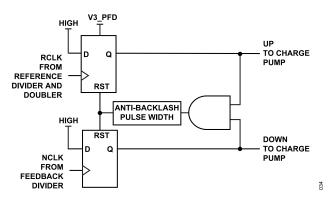

#### 位相/周波数検出器(PFD)

位相/周波数検出器(PFD)は、チャージ・ポンプと共に、リファレンス分周器またはリファレンス・ダブラの出力と帰還分周器の出力の位相差に比例した、ソース電流パルスおよびシンク電流パルスを生成します。この動作により、ループを位相ロックするのに必要な帰還が生成され、位相を PFD の入力と揃えることができます。PFD の簡略化した回路図を図 35 に示します。

図 35. PFD の簡略化した回路図

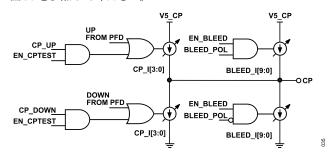

## チャージ・ポンプ

チャージ・ポンプは、PFD によって制御され、シンク(ダウン)電流パルスまたはソース(アップ)電流パルスを CP ピンに発生させます。 CP ピンは適切なループ・フィルタに接続する必要があります。 チャージ・ポンプの簡略化した回路図については  $2 \times 36$  を参照してください。

図 36. チャージ・ポンプの簡略化した回路図

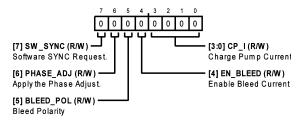

出力電流の大きさ(I<sub>CP</sub>)は、REG001F の CP\_I ビットを用いて 0.79mA~11.1mA の範囲で設定できます。I<sub>CP</sub> を大きくすると、ループ・フィルタ部品が低インピーダンスであることから、帯域内ノイズが低下します。また I<sub>CP</sub>を小さくすると、スプリアス性能が改善します。特定の値に設定するには表 11 を参照してください。また、ループ・フィルタの設計に関する詳細については、アプリケーション情報のセクションを参照してください。

表 11. CP の設定

| CP_I | I <sub>CP</sub> |

|------|-----------------|

| 0    | 0.79 mA         |

| 1    | 0.99 mA         |

| 2    | 1.19 mA         |

| 3    | 1.38 mA         |

| 4    | 1.59 mA         |

| 5    | 1.98 mA         |

| 6    | 2.39 mA         |

| 7    | 2.79 mA         |

| 8    | 3.18 mA         |

| 9    | 3.97 mA         |

| 10   | 4.77 mA         |

| 11   | 5.57 mA         |

| 12   | 6.33 mA         |

analog.com.jp Rev. 0 | 17 of 54

#### 動作原理

表 11. CP の設定(続き)

| CP_I | I <sub>CP</sub> |  |

|------|-----------------|--|

| 13   | 7.91 mA         |  |

| 14   | 9.51 mA         |  |

| 15   | 11.1 mA         |  |

# チャージ・ポンプの機能

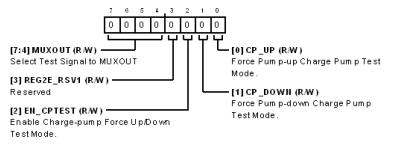

EN\_CPTEST ビットが 1 に設定されている場合、CP ピンで一定の $I_{CP}$ ソース電流やシンク電流となるよう、それぞれ $CP\_UP$ ビットと  $CP\_DOWN$  ビットを設定できます。ループをロックできるようにするには、EN\_CPTEST または  $CP\_UP$  および  $CP\_DOWN$  を 0 に設定する必要があります。これらのビットは一般に、プロジェクトのハードウェアおよびソフトウェアの開発フェーズ時に PLL 関連の問題をデバッグするための補助として使用されます。通常動作では EN\_CPTEST、 $CP\_UP$ 、 $CP\_DOWN$  は 0 に設定します。

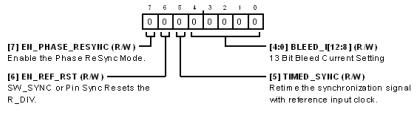

## チャージ・ポンプ・ブリード電流の最適化

ブリード電流( $I_{BLEED}$ )と呼ばれる設定可能な小さなチャージ・ポンプ電流を用いることで、位相ノイズやフラクショナル・モードでのフラクショナル・スプリアル信号を最適化できます。ブリード電流をイネーブルするには、 $EN_BLEED$  ビットを 1 に設定します。 $BLEED_POL$  ビットが 1 に設定されている場合、一定のわずかなソース電流が CP ピンに印加されます。CP ピンに印加されます。CP ピンに印加されます。

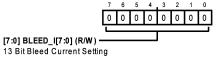

13 ビットのブリード電流設定は、粗設定用の4 ビット MSB と精細設定用の9 ビット LSB で構成されます。粗設定は  $180\mu A$  きざみ、精細設定は 490nA きざみです。

フラクショナル・モード用に最適化されたブリード電流値は、チャージ・ポンプ電流( $I_{CP}$ )、 $f_{PFD}$ 、ブリード遅延( $t_{BLEED}$ )に基づいて計算されます。推奨する  $t_{BLEED}$  と  $BLEED_POL$  を表 12 および表 13 に示します。

表 12. f<sub>PFD</sub> ≥ 120MHz の場合の t<sub>BLEED</sub> と BLEED\_POL

| Output Frequency                                  | t <sub>BLEED</sub> | BLEED_POL |

|---------------------------------------------------|--------------------|-----------|

| f <sub>RFOUT</sub> ≥ 4.2 GHz                      | 390 ps             | 0         |

| $3.0 \text{ GHz} \le f_{RFOUT} < 4.2 \text{ GHz}$ | 900 ps             | 0         |

| $1.8 \text{ GHz} \le f_{RFOUT} < 3.0 \text{ GHz}$ | 1200 ps            | 0         |

| f <sub>RFOUT</sub> < 1.8 GHz                      | 1400 ps            | 0         |

ブリード電流と BLEED I ビットは、以下の式で計算できます。

$$I_{BLEED} = T_{BLEED} \times f_{PFD} \times I_{CP} \tag{7}$$

$$CoarseBleed = INT \left(\frac{I_{BLEED}}{180\mu}\right) \tag{8}$$

FineBleed = Round

$$\left(512 \times \frac{I_{BLEED} - 180\mu \times CoarseBleed}{250\mu}\right)$$

(9)

$$BLEED_I = 512 \times CoarseBleed + FineBleed$$

(10)

表 13. f<sub>PFD</sub> < 120MHz の場合の t<sub>BLEED</sub> と BLEED POL

|                                                   | N                  | ≥ 35          | ١                  | N < 35        |

|---------------------------------------------------|--------------------|---------------|--------------------|---------------|

| RF Frequency                                      | t <sub>BLEED</sub> | BLEED_<br>POL | t <sub>BLEED</sub> | BLEED_<br>POL |

| f <sub>RFOUT</sub> ≥ 4.2 GHz                      | 390 ps             | 0             | 390 ps             | 0             |

| $3.0 \text{ GHz} \le f_{RFOUT} < 4.2 \text{ GHz}$ | 1200 ps            | 1             | 900 ps             | 0             |

| 1.8 GHz ≤ f <sub>RFOUT</sub> < 3.0<br>GHz         | 1200 ps            | 0             | 1200 ps            | 1             |

| 1.2 GHz ≤ f <sub>RFOUT</sub> < 1.8<br>GHz         | 1400 ps            | 0             | 1400 ps            | 1             |

| f <sub>RFOUT</sub> < 1.2 GHz                      | 1400 ps            | 0             | 2000 ps            | 1             |

ブリード電流によって、REFP 入力ピンおよび REFN 入力ピンから RFOUTxP 出力ピンおよび RFOUTxN 出力ピンまでの伝搬遅延の変化も生じます。インテジャー・モードでは、ブリード電流を使用して、どちらの方向の出力もシフトできます。BLEED\_POL = 0 の場合、REFP 入力ピンおよび REFN 入力ピンから RFOUTxP 出力ピンおよび RFOUTxN 出力ピンまでの伝搬遅延は増加します。

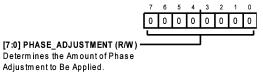

フラクショナル・モードでは、最高性能が得られるようブリード電流を設定した後、出力はREG0024のPHASE\_ADJUSTMENTビットを用いてシフトできます。これらのビットはシグマ・デルタ・モジュレータ(SDM)で効果的に用いられます。位相を調整しても位相ノイズが悪化することはありません。

#### ロック検出器

ロック検出器は、PFD からの内部信号を用いて RCLK と NCLK 間の位相の一致を測定します。この検出器は、REG002D の EN\_LOL ビットと EN\_LDWIN ビットの両方を 1 に設定することでイネーブルされ、その出力は LKDET ピンおよび REG0058 の LOCKED ビットで読み出せます。ロック検出器の出力は、REG002E の MUXOUT ビットを設定して MUXOUT ピンで読み出すこともできます。

PFD の位相差は、ロック検出器出力が PLL がロックされたことを示すまでに、設定された PFD サイクル数に対する位相差ロック・ウィンドウ時間 (t<sub>LDWIN</sub>) より小さくなっていなければなりません。ユーザは、動作モード、fpFD、fkFOUT に応じて、LDWIN\_PW ビットの有効ロック条件に対する t<sub>LDWIN</sub> を設定します。推奨する LDWIN PW ビットの設定を表 14 に示します。

表 14. LDWIN\_PW の設定

| LDWIN_PW | Configuration                                               |

|----------|-------------------------------------------------------------|

| 0        | Integer PLL, t <sub>BLEED</sub> ≤ 85 ps                     |

| 1        | Integer PLL, 85 ps > t <sub>BLEED</sub> < 250 ps            |

| 10       | Fractional PLL, f <sub>PFD</sub> > 200 MHz and RF > 6.4 GHz |

| 11       | Fractional PLL, f <sub>PFD</sub> > 200 MHz and RF > 5 GHz   |

| 100      | Fractional PLL, f <sub>PFD</sub> < 200 MHz                  |

| 101      | Fractional PLL, f <sub>PFD</sub> < 100 MHz                  |

| 110      | Fractional PLL, f <sub>PFD</sub> < 50 MHz                   |

| 111      | Fractional PLL, f <sub>PFD</sub> < 40 MHz                   |

analog.com.jp Rev. 0 | 18 of 54

#### 動作原理

設計者がロック検出の精度を重視するか速度を重視するかで、必要な PFD サイクル数は変わります。式 11 に示すように、必要な PFD サイクル数の初期推定値として、5 個のループ・フィルタ時定数を用いることができます。必要な PFD サイクル数は、レジスタの詳細のセクションで示す式のように、REG002C のLD\_COUNT ビットで設定されます。ユーザは、実際の PFD サイクルが必要とする PFD サイクルより大きくなるよう LD\_COUNT を設定します。詳細については図 37 および表 16 を参照してください。

Desired PFD Cycles =

$$\frac{5}{2 \times \pi \times LPBW}$$

(11)

ここで、LPBW はループ・フィルタの帯域幅です。

表 15. LD COUNT の設定

| LD_COUNT | Actual PFD Cycles |

|----------|-------------------|

| 0        | 27                |

| 1        | 35                |

| 2        | 51                |

| 3        | 67                |

| 4        | 99                |

| 5        | 131               |

| 6        | 195               |

| 7        | 259               |

| 8        | 387               |

| 9        | 515               |

| 10       | 771               |

| 11       | 1027              |

| 12       | 1539              |

| 13       | 2051              |

| 14       | 3075              |

| 15       | 4099              |

| 16       | 6147              |

| 17       | 8195              |

| 18       | 12291             |

| 19       | 16387             |

| 20       | 24579             |

| 21       | 32771             |

| 22       | 49155             |

| 23       | 65539             |

| 24       | 98307             |

| 25       | 131075            |

| 26       | 196611            |

| 27       | 262147            |

| 28       | 393219            |

| 29       | 524291            |

| 30       | 786435            |

| 31       | 1048579           |

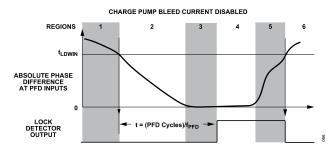

図 37. ロック検出器のタイミング (ブリード電流をディスエーブル)

表 16. ロック検出器のタイミング(ブリード電流をディスエー ブル)

| Region | Absolute Phase Difference at PFD | Lock Detector State             |

|--------|----------------------------------|---------------------------------|

| 1      | > t <sub>LDWIN</sub>             | Low                             |

| 2      | < t <sub>LDWIN</sub>             | Low, counts PFD cycles          |

| 3      | ~0                               |                                 |

| 4      | ~0                               | High, > desired PFD cycle count |

| 5      | < t <sub>LDWIN</sub>             | High                            |

| 6      | > t <sub>LDWIN</sub>             | Low (immediately)               |

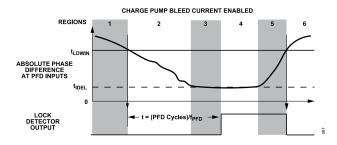

チャージ・ポンプのブリード電流がイネーブルされている場合、PFD 入力に位相オフセットが加わります。この位相オフセット(tidel) は、ブリード電流の量に比例します。図 37 および図 38 の領域 3 と領域 4 は、それぞれチャージ・ポンプ・ブリード電流がディスエーブルの場合とイネーブルの場合に PLL がセトリングする PFD 位相差に焦点を合わせたものです。

図 38. ロック検出器のタイミング(ブリード電流をイネーブル)

#### **VCO**

VCO コアは 4 個の独立した VCO で構成され、各 VCO では 256 の帯域が重なり合っているため、デバイスは高い VCO 感度  $(K_V)$  を必要とせずに広い周波数範囲に対応できます。出力周波数は出力分周器を用いることで更に拡張できます。

analog.com.jp Rev. 0 | 19 of 54

#### 動作原理

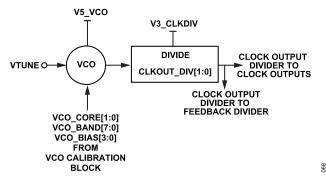

図 39. VCO およびクロック出力分周器

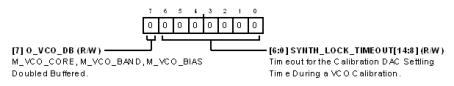

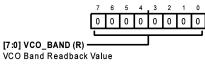

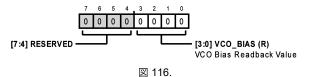

VCO\_CORE、VCO\_BAND、VCO\_BIAS の各設定値に対する適切なレジスタ値は、VCO のキャリブレーションを行うことで定まります。VCO のキャリブレーションを特定のデバイスと周波数に対して実行した後、VCO\_CORE、VCO\_BAND、VCO\_BIAS の各値を記録できます。これらの記録値は、同じデバイスと周波数を用いる場合、その後のパワーアップ時には手動でプログラムできます。そのため、VCO のキャリブレーション時間を節約できます。

# VCO のキャリブレーション

特定の VCO 周波数に対し適切な VCO コア、帯域、バイアス設定値を選択するには、VCO のキャリブレーションが必要です。この手順は、デバイスがパワーアップされており、必要なリファレンス周波数が REFP ピンと REFN ピンに入力され、その他すべてのレジスタが正しく設定されていることを前提としています。この手順を図 40 と図 41 に視覚的に示します。

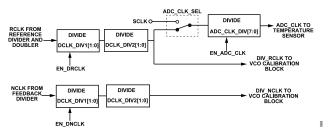

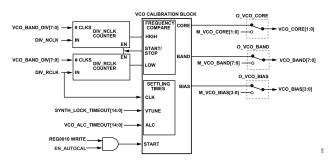

図 40. VCO キャリブレーション分周器

図 41. VCO キャリブレーション・ブロック

次の手順に示すように、VCO キャリブレーションを実行するには、いくつかのレジスタの設定を行います。

1. DCLK\_DIV1 および DCLK\_MODE を表 17 に示す値に設定します。後の使用のため、for RCLKを記録しておきます。

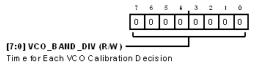

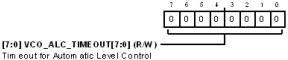

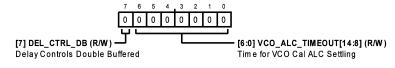

2. SYNTH\_LOCK\_TIMEOUT ビット・フィールド [14:0]、 VCO\_ALC\_TIMEOUT ビット・フィールド [14:0]、 VCO\_BAND\_DIV ビットの最小値を計算し設定します。これらのパラメータの最小値を選択する場合、VCO の代表的な自動キャリブレーション時間は  $3ms\sim 9ms$  です。値を大きくすると VCO キャリブレーション時間は長くなります。

SYNTH\_LOCK\_TIMEOUT

$$\geq$$

Ceiling (200 $\mu$ s  $\times f_{DIV\ RCLK}$ ) (12)

$$VCO\_ALC\_TIMEOUT \ge Ceiling$$

$$(50\mu s \times f_{DIV\ RCLK})$$

(13)

$$VCO\_BAND\_DIV \ge Ceiling$$

$$\left(\frac{15\mu s \times f_{DIV\_RCLK}}{16 \times 2^{DCLK\_MODE}}\right)$$

(14)

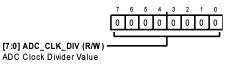

3. 必要な ADC クロック周波数が 400kHz 未満となるように ADC CLK DIV ビットを 設定し てくだ さい。

$$\frac{ADC\_CLK\_DIV > Ceiling}{\left(\frac{\frac{f_{DIV\_RCLK}}{400kHz} - 2}{4}\right)}$$

(15)

- 4. REG0010 を最後にプログラミングして N\_INT、CLKOUT\_DIV、R\_DIV、EN\_RDBLR の各ビットを設定します。REG0010に何らかの書込みを行うと VCO の自動キャリブレーションが開始されます。

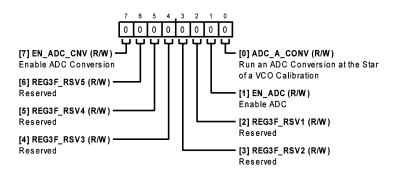

- 5. ADC\_BUSY ビットおよび FSM\_BUSY ビットをモニタします。 ADC\_BUSY がハイからローに遷移し、次いで FSM\_BUSY が ハイからローに遷移すると、キャリブレーションは終了しま す。

- 6. VCO のキャリブレーションが終了したら、 $EN_DRCLK = EN_DNCLK = EN_ADC_CLK = 0$  に設定してキャリブレーション・クロックをディスエーブルし、不要なスプリアス成分を制限します。

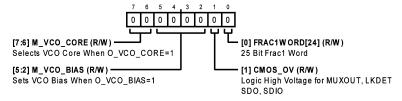

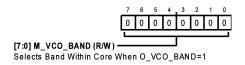

- 7. このステップはオプションです。VCO\_CORE ビット、VCO\_BAND ビット、VCO\_BIAS ビットをリードバックし記録します。これらの値を使用すると、所定のデバイスと周波数に対しキャリブレーションをバイパスし、M\_VCO\_CORE ビット、M\_VCO\_BAND ビット、M\_VCO\_BIAS ビットを手動で設定できます。

表 17. DCLK DIV1 および DCLK MODE のセットアップ

| f <sub>PFD</sub> (MHz) | DCLK_DIV1 | DCLK_MODE | f <sub>DIV_RCLK</sub> (MHz) |

|------------------------|-----------|-----------|-----------------------------|

| ≤160                   | 0         | 1         | f <sub>PFD</sub> /2         |

| >160 and ≤320          | 1         | 1         | f <sub>PFD</sub> /4         |

| >320                   | 2         | 1         | f <sub>PFD</sub> /8         |

#### クロック出力分周器

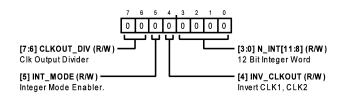

2 ビット分周器 CLKOUT\_DIV を用いると、出力バッファおよび 帰還分周器に出力される周波数を低減できます。分周比Oは1、 2、4、または 8 に設定可能です。分周比 O を直接設定するには、 REG0011 の CLKOUT\_DIV ビットを用います。CLKOUT\_DIV は PLL ループ内に置かれています。そのため、CLKOUT\_DIV に何 らかの変更を加えると、わずかなループ時定数の間、PLL の ロックが失われます。

analog.com.jp Rev. 0 | 20 of 54

#### 動作原理

## 出力反転(INV\_CLKOUT)

出力反転 (INV\_CLKOUT) を用いると、出力信号を 180° シフトできます。INV\_CLKOUT は PLL ループ内に置かれています。INV\_CLKOUT に何らかの変更を加えると、わずかなループ時定数の間、PLL のロックが失われます。出力の位相を直接設定するには、レジスタ REG0011 の INV\_CLKOUT ビットを用います。

#### 帰還分周器(N)

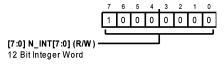

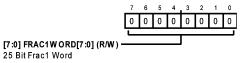

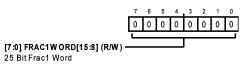

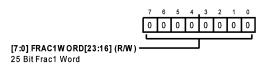

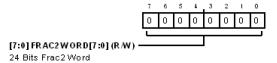

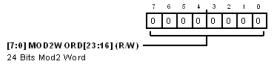

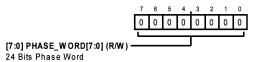

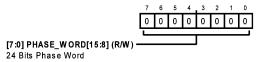

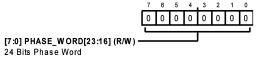

帰還分周器により PLL 帰還パスの分周比を設定できます。分周 比を定めるには、N INTビット・フィールド[11:0] (REG0011お よび REG0010)、FRAC1WORD ビット・フィールド[24:0] (REG0015, REG0014, REG0013, REG0012), FRAC2WORD ビット・フィールド[23:0] (REG0019、REG0018、REG0017)、 MOD2WORD ビット・フィールド[23:0] (REG001C、REG001B、 REG001A)の値を用います。この分周器はこれらの値に加え、 固定モジュラス MOD1WORD (2<sup>25</sup>) で構成されています。24 ビットの変数 MOD2WORD および 25 ビットの固定値 MOD1WORD が、49 ビットに結合されたフラクショナル・モ ジュラスを形成します。N INT ビット・フィールド[11:0]、 FRAC1WORD ビット・フィールド[24:0]、MOD1WORD、 FRAC2WORD ビット・フィールド[23:0]、MOD2WORD ビッ ト・フィールド[23:0]、CLKOUT\_DIV ビットや R、D、および fref、fpfD、fvco、fout の各周波数の関係については、出力周波数 のセクションを参照してください。

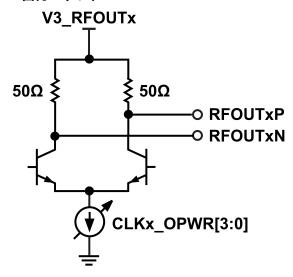

#### RF 出力パッファ

図 42. RF 出力バッファの簡略化したブロック図

図 42 の低ノイズ差動出力バッファは、差動電圧を出力します。 出力の振幅レベルおよびコモンモード電圧は、CLK1\_OPWR ビットと CLK2\_OPWR ビットで設定可能です。各出力は AC カップリングまたは DC カップリングでき、 $100\Omega$  の差動イン ピーダンスで終端されます。シングルエンド出力が必要な場合 は、それぞれの出力側を  $50\Omega$  で個別に AC カップリングまたは DC カップリングする必要があります。

4 つの CLKx\_OPWR 設定値のうちの最低値を用いる場合は、プルアップ・インダクタを外付けする必要はありません。出力電力をこれより高くするには外部インダクタが必要です。3.4nHの0302 パッケージまたはこれより小型のインダクタを推奨します。評価用ボードの回路図の詳細については、EVAL-ADF4368 ユーザ・ガイドを参照してください。

analog.com.jp Rev. 0 | 21 of 54

# アプリケーション情報

# ループ・フィルタの設計

安定なループ・フィルタを設計するためには、ADF4368 のループ・フィルタ部品を選択する際に注意が必要です。ループ・フィルタの設計とシミュレーションには ADIsimPLL<sup>TM</sup> をダウンロードしてインストールすることを推奨します。ADIsimPLL<sup>TM</sup> には、初めて使うユーザのためにチュートリアルが含まれており、また、より複雑なトピックに対してのヘルプ・マニュアルも備わっています。 www.analog.com には、いくつかのADIsimPLL トレーニング・ビデオも用意されています。ループ・フィルタの設計とシミュレーションを終了した後は、ADF4368 評価用ハードウェアを用いて新しいループ・フィルタを検証することを推奨します。

ループ・フィルタ設計の完全なチュートリアルは、このデータシートの範囲を超えています。しかし、いくつかのベスト・プラクティスを以下に列挙します。ADIsimPLL はこれらのパラメータの定義とシミュレーションの助けとなるものです。これらの項目を大幅に変更するには、新たなループ・フィルタの設計が必要です。

安定なループ・フィルタは次の条件を満たす必要があります。

- ▶ ループ・フィルタの位相マージン>45°

- ▶ ループ・フィルタの帯域幅 < f<sub>PFD</sub> ÷ 10

必要なループ・フィルタの帯域幅は、ADF4368 の次の主要な性能パラメータによって決まります。

- ▶ I<sub>CP</sub>

- ▶ K<sub>VCO</sub>

- ▶ PFD 周波数

- ▶ リファレンス入力の位相ノイズ(リファレンスの位相ノイズのセクションを参照)

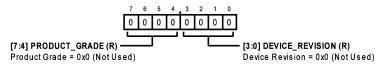

- ▶ ジッタの最小化またはセトリング・タイムの最小化のトレードオフ(それぞれ、出力の位相ノイズ特性のセクションおよび式12を参照)