# 18 ビット、2 MSPS/1 MSPS/ 500 kSPS、高精度疑似差動 SAR ADC

## -タシート

# AD4002/AD4006/AD4010

特長

スループット: 2 MSPS/1 MSPS/500 kSPS のオプション

INL: ±3.2 LSB(最大值)

18 ビットのノー・ミス・コードを確保

低消費電力: 10 kSPS で 70 µW、2 MSPS で 14 mW(合計) 2 MSPS で 9.75 mW、1 MSPS で 4.9 mW、500 kSPS で 2.5 mW (VDD のみ)

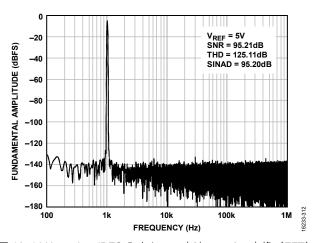

S/N 比: 1 kHz で 95 dB (代表値)

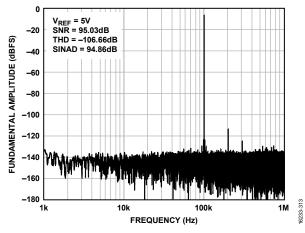

V<sub>REF</sub> = 5 V、100 kHz で 95 dB(代表値)

THD: 1 kHz で -125 dB (代表値)

V<sub>REF</sub> = 5 V、100 kHz で -108 dB (代表値)

使いやすい機能でシステムの消費電力と複雑さを低減

入力過電圧クランプ回路

非直線性入力チャージ・キックバックを低減

高インピーダンス・モード

長いアクイジション・フェーズ

入力スパン圧縮

高速変換で低 SPI クロック・レートを実現

SPI プログラマブル・モード、読出し/書込み機能、ステータ ス・ワード

疑似差動 (シングル・エンド) アナログ入力範囲:

$0 V \sim V_{REF} (V_{REF} tall 2.4 V \sim 5.1 V)$

1.71 V ~ 5.5 V のロジック・インターフェースで 1.8 V の単電源 動作

SAR アーキテクチャ: 遅延/パイプライン遅延なし、最初の変換 が有効

最初の変換の精度

確認動作: -40 °C ~ +125 °C

シリアル・インターフェース: SPI/QSPI/MICROWIRE/DSP 互換 複数の ADC をデイジーチェーン接続可能、ビジー・インジケー

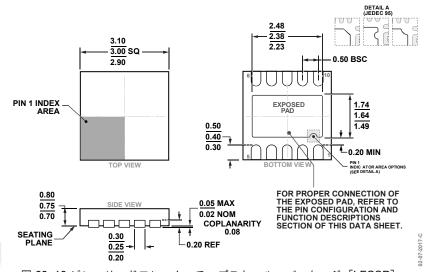

10 ピン・パッケージ: 3 mm × 3 mm の LFCSP、3 mm × 4.90 mm の MSOP

アプリケーション

ATE(自動試験装置)

マシン・オートメーション

医療機器

パッテリ駆動装置

高精度のデータ・アクイジション・システム

#### 概要

AD4002/AD4006/AD4010 は低ノイズ、低消費電力の高速 18 ビット 高精度逐次比較レジスタ (SAR) A/D コンバータ (ADC) です。 AD4002、AD4006、AD4010 のスループットは、それぞれ 2 MSPS、 1 MSPS、500 kSPS です。これらの製品には、シグナル・チェーン の消費電力を減らし、シグナル・チェーンの複雑性を軽減し、高 いチャンネル密度を実現できる、使いやすい機能が組み込まれて います。高インピーダンス・モードと長いアクイジション・フェー ズを組み合わせることで、専用の高出力、高速 ADC ドライバが不 要になり、低消費電力、高精度アンプの範囲を広げ、最適な性能を 実現しながら、これらの ADC を直接駆動できます。入力スパンの 圧縮機能を備えているので、負電源なしで ADC ドライバ・アンプ と ADC を共通の電源レールで動作させながら、ADC コードの全 範囲に対応できます。シリアル周辺機器インターフェース(SPI) のクロック・レートには、デジタル入出力の消費電力量を減らし、 プロセッサの選択肢を広げ、デジタル絶縁間でデータを送信する タスクを簡略化することが要求されます。

AD4002/AD4006/AD4010 は 1.8 V の電源で動作し、接地センス (IN-) を 基準にして $0V \sim V_{REF}$ の範囲にあるアナログ入力(IN+)をサンプ リングします。ここで、 $V_{REF}$  は  $2.4\,V\sim5.1\,V$  の範囲にあります。 SCK レートが最小の 75 MHz の場合、AD4002 は 2 MSPS 時に 14 mW しか消費せず、AD4006は1 MSPS 時に7 mW、AD4010は500 kSPS 時に3.5 mW しか消費しません。AD4002/AD4006/AD4010は、いず れも1kHzの入力周波数  $(f_{IN})$  に対して最大  $\pm 3.2$  LSB の積分非直 線性誤差(INL)、および 95 dB の S/N 比で 18 ビットのノー・ミ ス・コードを実現します。リファレンス電圧は外部から供給され、 電源電圧とは独立して設定できます。

SPI 互換の多機能シリアル・インターフェースには、7種類のモー ドがあります。このモードには、SDI入力を使用して1つの3線 式バスで複数の ADC をデイジーチェーン接続する機能も含まれ ます。オプションでビジー・インジケータも用意しています。 AD4002/AD4006/AD4010 は、独立した VIO 電源を使用すること で、1.8 V、2.5 V、3 V、5 V のロジックに対応します。

AD4002/AD4006には10ピンMSOPおよび10ピンのLFCSPを用意し ています。AD4010には10-ピンのLFCSPがあり、-40°C~+125°Cの 範囲で仕様規定されています。このデバイスは、18ビット、2MSPS のAD4003 とピン互換性があります(表 8 を参照)。

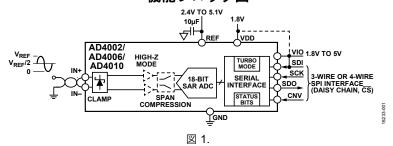

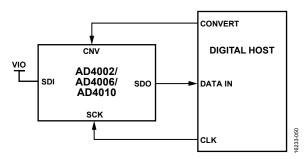

#### 機能ブロック図

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって 生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示 的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有者 の財産です。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

©2018 Analog Devices, Inc. All rights reserved.

Rev. 0

社/〒105-6891

東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 電話 03(5402)8200

大阪営業所/〒532-0003

大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 電話 06 (6350) 6868

# データシート

# AD4002/AD4006/AD4010

# 目次

| アナログ入力                              | 19 |

|-------------------------------------|----|

| ドライバ・アンプの選択                         | 20 |

| ドライブ補助機能                            | 21 |

| 電圧リファレンス入力                          | 23 |

| 電源                                  | 23 |

| デジタル・インターフェース                       | 24 |

| レジスタ読出し/書込み機能                       | 24 |

| ステータス・ワード                           | 27 |

| CS モード、3 線式ターボ・モード                  | 28 |

| CS モード、3 線式、ビジー・インジケータなし            | 29 |

| CS モード、3 線式、ビジー・インジケータあり            | 30 |

| CS モード、4 線式ターボ・モード                  | 31 |

| <del>CS</del> モード、4 線式、ビジー・インジケータなし | 32 |

| CS モード、4 線式、ビジー・インジケータあり            | 33 |

| デイジーチェーン・モード                        | 34 |

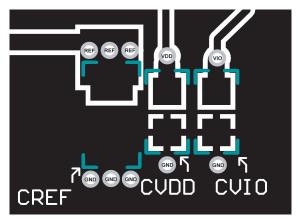

| レイアウトのガイドライン                        | 35 |

| AD4002/AD4006/AD4010 の性能の評価         | 35 |

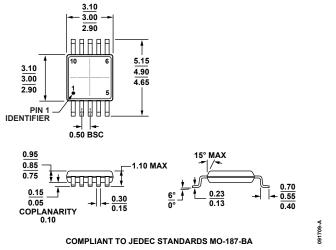

| 外形寸法                                | 36 |

| ナーダー・ガイド                            | 26 |

## 改訂履歴

1/2018-Revision 0: Initial Version

# 仕様

特に指定のない限り、VDD=1.71 V  $\sim$  1.89 V、VIO=1.71 V  $\sim$  5.5 V、V<sub>REF</sub>=5 V、すべての仕様で  $T_{MIN}$   $\sim$   $T_{MAX}$ 、高インピーダンス・モードは無効、スパン圧縮は無効、ターボ・モードは有効、サンプリング周波数は AD4002 で( $f_S$ )= 2 MSPS、AD4006 で  $f_S$ = 1 MSPS、AD4010 で  $f_S$ = 500 kSPS。

表 1.

| Parameter                                                          | Test Conditions/Comments                                   | Min                  | Тур       | Max                         | Unit   |

|--------------------------------------------------------------------|------------------------------------------------------------|----------------------|-----------|-----------------------------|--------|

| RESOLUTION                                                         |                                                            | 18                   |           |                             | Bits   |

| ANALOG INPUT                                                       |                                                            |                      |           |                             |        |

| Voltage Range                                                      | $IN+ Voltage (V_{IN+}) - IN- Voltage (V_{IN-})$            | 0                    |           | $V_{REF}$                   | V      |

| Operating Input Voltage                                            | V <sub>IN+</sub> to GND                                    | -0.1                 |           | $V_{REF} + 0.1$             | V      |

|                                                                    | V <sub>IN-</sub> to GND                                    | -0.1                 |           | +0.1                        | V      |

|                                                                    | Span compression enabled                                   | $0.1 \times V_{REF}$ |           | $0.9 \times V_{\text{REF}}$ | V      |

| Analog Input Current                                               | Acquisition phase, $T_A = 25^{\circ}C$                     |                      | 0.3       |                             | nA     |

|                                                                    | High-Z mode enabled, converting dc input at 2 MSPS         |                      | 1         |                             | μΑ     |

| THROUGHPUT                                                         |                                                            |                      |           |                             |        |

| Complete Cycle                                                     |                                                            |                      |           |                             |        |

| AD4002                                                             |                                                            | 500                  |           |                             | ns     |

| AD4006                                                             |                                                            | 1000                 |           |                             | ns     |

| AD4010                                                             |                                                            | 2000                 |           |                             | ns     |

| Conversion Time                                                    |                                                            | 270                  | 290       | 320                         | ns     |

| Acquisition Phase <sup>1</sup>                                     |                                                            |                      |           |                             |        |

| AD4002                                                             |                                                            | 290                  |           |                             | ns     |

| AD4006                                                             |                                                            | 790                  |           |                             | ns     |

| AD4010                                                             |                                                            | 1790                 |           |                             | ns     |

| Throughput Rate <sup>2</sup>                                       |                                                            |                      |           |                             |        |

| AD4002                                                             |                                                            | 0                    |           | 2                           | MSPS   |

| AD4006                                                             |                                                            | 0                    |           | 1                           | MSPS   |

| AD4010                                                             |                                                            | 0                    |           | 500                         | kSPS   |

| Transient Response <sup>3</sup>                                    |                                                            |                      | 290       |                             | ns     |

| DC ACCURACY                                                        |                                                            |                      |           |                             |        |

| No Missing Codes                                                   |                                                            | 18                   |           |                             | Bits   |

| Integral Nonlinearity Error (INL)                                  |                                                            | -3.2                 | $\pm 0.8$ | +3.2                        | LSB    |

|                                                                    |                                                            | -12.2                | ±3.1      | +12.2                       | ppm    |

| Differential Nonlinearity Error (DNL)                              |                                                            | -0.8                 | $\pm 0.5$ | +0.8                        | LSB    |

| Transition Noise                                                   |                                                            |                      | 1.6       |                             | LSB    |

| Zero Error                                                         |                                                            | -18                  |           | +18                         | LSB    |

| Zero Error Drift <sup>4</sup>                                      |                                                            | -2.2                 |           | +2.2                        | ppm/°C |

| Gain Error                                                         |                                                            | -45                  | ±10       | +45                         | LSB    |

| Gain Error Drift <sup>4</sup>                                      |                                                            | -2.6                 |           | +2.6                        | ppm/°C |

| Power Supply Sensitivity                                           | $VDD = 1.8 \text{ V} \pm 5\%$                              |                      | 2         |                             | LSB    |

| 1/f Noise <sup>5</sup>                                             | Bandwidth = 0.1 Hz to 10 Hz                                |                      | 6         |                             | μV p-p |

| AC ACCURACY                                                        |                                                            | 1                    |           |                             |        |

| Dynamic Range                                                      |                                                            |                      | 95.3      |                             | dB     |

| Total RMS Noise                                                    |                                                            | 1                    | 30.4      |                             | μV rms |

| $f_{IN} = 1 \text{ kHz}, -0.5 \text{ dBFS}, V_{REF} = 5 \text{ V}$ |                                                            | 1                    |           |                             |        |

| Signal-to-Noise Ratio (SNR)                                        |                                                            | 92.5                 | 95        |                             | dB     |

| Spurious-Free Dynamic Range (SFDR)                                 |                                                            | 1                    | 122       |                             | dB     |

| Total Harmonic Distortion (THD)                                    |                                                            | 1                    | -125      |                             | dB     |

| Signal-to-Noise-and-Distortion Ratio (SINAD)                       |                                                            | 92                   | 95        |                             | dB     |

| Oversampled Dynamic Range                                          | Oversampling ratio (OSR) = 256,<br>$V_{REF} = 5 \text{ V}$ |                      | 119       |                             | dB     |

# データシート

# AD4002/AD4006/AD4010

| Parameter                                                                        | Test Conditions/Comments  | Min                         | Тур            | Max               | Unit   |

|----------------------------------------------------------------------------------|---------------------------|-----------------------------|----------------|-------------------|--------|

| $f_{IN} = 1 \text{ kHz}, -0.5 \text{ dBFS}, V_{REF} = 2.5 \text{ V}$             |                           |                             |                |                   |        |

| SNR                                                                              |                           | 87                          | 89             |                   | dB     |

| SFDR                                                                             |                           |                             | 122            |                   | dB     |

| THD                                                                              |                           |                             | -123.5         |                   | dB     |

| SINAD                                                                            |                           | 87                          | 89             |                   | dB     |

| $f_{IN} = 100 \text{ kHz}, -0.5 \text{ dBFS}, V_{REF} = 5 \text{ V}$             |                           |                             |                |                   |        |

| SNR                                                                              |                           |                             | 95             |                   | dB     |

| THD                                                                              |                           |                             | -108           |                   | dB     |

| SINAD                                                                            |                           |                             | 94.8           |                   | dB     |

| $f_{IN} = 400 \text{ kHz}, -0.5 \text{ dBFS}, V_{REF} = 5 \text{ V}$             |                           |                             |                |                   |        |

| SNR                                                                              |                           |                             | 94             |                   | dB     |

| THD                                                                              |                           |                             | -92            |                   | dB     |

| SINAD                                                                            |                           |                             | 90             |                   | dB     |

| -3 dB Input Bandwidth                                                            |                           |                             | 10             |                   | MHz    |

| Aperture Delay                                                                   |                           |                             | 1              |                   | ns     |

| Aperture Jitter                                                                  |                           |                             | 1              |                   | ps rms |

| REFERENCE                                                                        |                           |                             |                |                   |        |

| Voltage Range, V <sub>REF</sub>                                                  |                           | 2.4                         |                | 5.1               | V      |

| Current                                                                          | $V_{REF} = 5 V$           |                             |                |                   |        |

| AD4002                                                                           | 2 MSPS                    |                             | 0.75           |                   | mA     |

| AD4006                                                                           | 1 MSPS                    |                             | 0.375          |                   | mA     |

| AD4010                                                                           | 500 kSPS                  |                             | 0.19           |                   | mA     |

| INPUT OVERVOLTAGE CLAMP                                                          |                           |                             |                |                   |        |

| IN+/IN- Current, I <sub>IN+</sub> /I <sub>IN-</sub>                              | $V_{REF} = 5 V$           |                             |                | 50                | mA     |

|                                                                                  | $V_{REF} = 2.5 \text{ V}$ |                             |                | 50                | mA     |

| V <sub>IN+</sub> /V <sub>IN-</sub> at Maximum I <sub>IN+</sub> /I <sub>IN-</sub> | $V_{REF} = 5 V$           |                             | 5.4            |                   | V      |

|                                                                                  | $V_{REF} = 2.5 \text{ V}$ |                             | 3.1            |                   | V      |

| V <sub>IN+</sub> /V <sub>IN-</sub> Clamp On/Off Threshold                        | $V_{REF} = 5 V$           | 5.25                        | 5.4            |                   | V      |

| -                                                                                | $V_{REF} = 2.5 \text{ V}$ | 2.68                        | 2.8            |                   | V      |

| Deactivation Time                                                                |                           |                             | 360            |                   | ns     |

| REF Current at Maximum I <sub>IN+</sub>                                          | $V_{IN+} > V_{REF}$       |                             | 100            |                   | μА     |

| DIGITAL INPUTS                                                                   |                           |                             |                |                   |        |

| Logic Levels                                                                     |                           |                             |                |                   |        |

| Input Low Voltage, V <sub>IL</sub>                                               | VIO > 2.7 V               | -0.3                        |                | +0.3 × VIO        | V      |

| -                                                                                | VIO ≤ 2.7 V               | -0.3                        |                | $+0.2 \times VIO$ | V      |

| Input High Voltage, V <sub>IH</sub>                                              | VIO > 2.7 V               | 0.7 × VIO                   |                | VIO + 0.3         | V      |

|                                                                                  | VIO ≤ 2.7 V               | $0.8 \times VIO$            |                | VIO + 0.3         | V      |

| Input Low Current, I <sub>IL</sub>                                               |                           | -1                          |                | +1                | μΑ     |

| Input High Current, I <sub>IH</sub>                                              |                           | -1                          |                | +1                | μA     |

| Input Pin Capacitance                                                            |                           |                             | 6              |                   | pF     |

| DIGITAL OUTPUTS                                                                  |                           |                             |                |                   | 1      |

| Data Format                                                                      |                           | Serial                      | 18 bits, strai | ght binary        |        |

| Pipeline Delay                                                                   |                           |                             | rsion results  |                   |        |

| r                                                                                |                           | immediately after completed |                | completed         |        |

|                                                                                  |                           |                             | conversio      |                   |        |

| Output Low Voltage, Vol                                                          | $I_{SINK} = 500 \mu A$    |                             |                | 0.4               | V      |

| Output High Voltage, V <sub>OH</sub>                                             | $I_{SOURCE} = -500 \mu A$ | VIO - 0.3                   |                |                   | V      |

Rev. 0 - 4/37 -

# データシート

# AD4002/AD4006/AD4010

| Parameter             | Test Conditions/Comments                                          | Min  | Тур  | Max  | Unit      |

|-----------------------|-------------------------------------------------------------------|------|------|------|-----------|

| POWER SUPPLIES        |                                                                   |      |      |      |           |

| VDD                   |                                                                   | 1.71 | 1.8  | 1.89 | V         |

| VIO                   |                                                                   | 1.71 |      | 5.5  | V         |

| Standby Current       | VDD and VIO = 1.8 V, $T_A = 25$ °C                                |      | 1.6  |      | μΑ        |

| Power Dissipation     | $VDD = 1.8 \text{ V}, VIO = 1.8 \text{ V}, V_{REF} = 5 \text{ V}$ |      |      |      |           |

|                       | 10 kSPS, high-Z mode disabled                                     |      | 70   |      | $\mu W$   |

|                       | 500 kSPS, high-Z mode disabled                                    |      | 3.5  | 4.4  | mW        |

|                       | 1 MSPS, high-Z mode disabled                                      |      | 7    | 8.4  | mW        |

|                       | 2 MSPS, high-Z mode disabled                                      |      | 14   | 16.5 | mW        |

|                       | 500 kSPS, high-Z mode enabled                                     |      | 3.8  | 5.4  | mW        |

|                       | 1 MSPS, high-Z mode enabled                                       |      | 7.6  | 10.8 | mW        |

|                       | 2 MSPS, high-Z mode enabled                                       |      | 15.2 | 21.5 | mW        |

| VDD Only              | 500 kSPS, high-Z mode disabled                                    |      | 2.5  |      | mW        |

|                       | 1 MSPS, high-Z mode disabled                                      |      | 4.9  |      | mW        |

|                       | 2 MSPS, high-Z mode disabled                                      |      | 9.75 |      | mW        |

| REF Only              | 500 kSPS, high-Z mode disabled                                    |      | 0.95 |      | mW        |

|                       | 1 MSPS, high-Z mode disabled                                      |      | 1.9  |      | mW        |

|                       | 2 MSPS, high-Z mode disabled                                      |      | 3.65 |      | mW        |

| VIO Only              | 500 kSPS, high-Z mode disabled                                    |      | 0.1  |      | mW        |

|                       | 1 MSPS, high-Z mode disabled                                      |      | 0.2  |      | mW        |

|                       | 2 MSPS, high-Z mode disabled                                      |      | 0.6  |      | mW        |

| Energy per Conversion |                                                                   |      | 7    |      | nJ/sample |

| TEMPERATURE RANGE     |                                                                   |      |      |      |           |

| Specified Performance | $T_{MIN}$ to $T_{MAX}$                                            | -40  |      | +125 | °C        |

$<sup>^1</sup>$  アクイジション・フェーズとは、入力サンプリング・コンデンサが新しい入力の取得に使用できる時間です。ここで、AD4002 では 2 MSPS、AD4006 では 1 MSPS、

AD4010 では 500 kSPS のスループット・レートで動作する ADC を使用します。  $^2$  ターボ・モードを有効にして、最小 SCK レートである 75 MHz を使用した場合のみ、2 MSPS のスループット・レートが実現します。 さまざまな動作モー ドで可能な最大スループットについては、表4を参照してください。

$<sup>^3</sup>$  過渡応答は、 $\pm 2$  LSB の精度でフルスケール入力ステップを達成するのに必要な時間です。マルチプレクス・アプリケーションにおける ADC 入力設定につ いては、図39を参照してください。

$<sup>^4</sup>$ 最小値と最大値は特性評価によって確保されていますが、出荷テストの対象外です。

<sup>&</sup>lt;sup>5</sup>図23の1/fノイズ・プロットを参照してください。

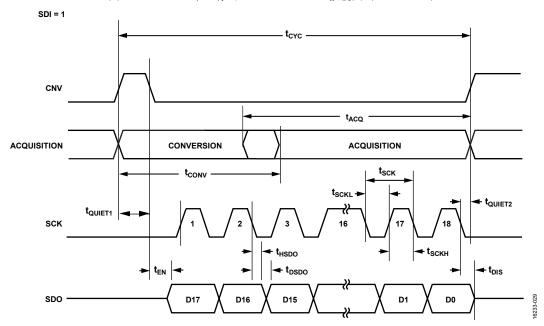

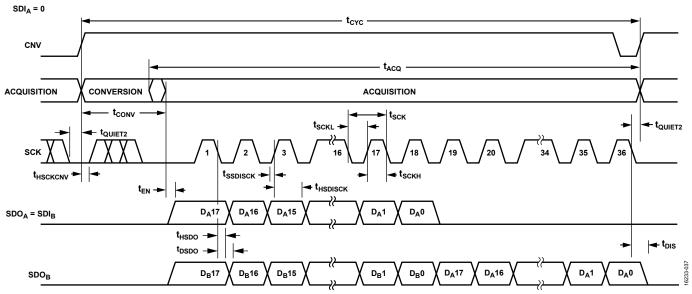

#### タイミング仕様

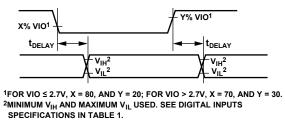

特に指定のない限り、VDD=1.71 V  $\sim$  1.89 V、VIO=1.71 V  $\sim$  5.5 V、V<sub>REF</sub>=5 V、すべての仕様で  $T_{MIN}$   $\sim$   $T_{MAX}$ 、高インピーダンス・モードは無効、スパン圧縮は無効、ターボ・モードは有効、AD4002 では  $f_S$  = 2 MSPS、AD4006 では  $f_S$  = 1 MSPS、AD4010 では  $f_S$  = 500 kSPS。タイミング電圧レベルについては、図 2 を参照してください。

表 2. デジタル・インターフェースのタイミング

| Parameter                                                                  | Symbol               | Min  | Тур | Max  | Unit |

|----------------------------------------------------------------------------|----------------------|------|-----|------|------|

| CONVERSION TIME—CNV RISING EDGE TO DATA AVAILABLE                          | t <sub>CONV</sub>    | 270  | 290 | 320  | ns   |

| ACQUISITION PHASE <sup>1</sup>                                             | $t_{ACQ}$            |      |     |      |      |

| AD4002                                                                     |                      | 290  |     |      | ns   |

| AD4006                                                                     |                      | 790  |     |      | ns   |

| AD4010                                                                     |                      | 1790 |     |      | ns   |

| TIME BETWEEN CONVERSIONS                                                   | $t_{CYC}$            |      |     |      |      |

| AD4002                                                                     |                      | 500  |     |      | ns   |

| AD4006                                                                     |                      | 1000 |     |      | ns   |

| AD4010                                                                     |                      | 2000 |     |      | ns   |

| CNV PULSE WIDTH $(\overline{CS} \text{ MODE})^2$                           | $t_{CNVH}$           | 10   |     |      | ns   |

| SCK PERIOD $(\overline{CS} \text{ MODE})^3$                                | $t_{SCK}$            |      |     |      |      |

| VIO > 2.7 V                                                                |                      | 9.8  |     |      | ns   |

| VIO > 1.7 V                                                                |                      | 12.3 |     |      | ns   |

| SCK PERIOD (DAISY-CHAIN MODE) <sup>4</sup>                                 | $t_{SCK}$            |      |     |      |      |

| VIO > 2.7 V                                                                |                      | 20   |     |      | ns   |

| VIO > 1.7 V                                                                |                      | 25   |     |      | ns   |

| SCK LOW TIME                                                               | $t_{SCKL}$           | 3    |     |      | ns   |

| SCK HIGH TIME                                                              | t <sub>SCKH</sub>    | 3    |     |      | ns   |

| SCK FALLING EDGE TO DATA REMAINS VALID DELAY                               | $t_{ m HSDO}$        | 1.5  |     |      | ns   |

| SCK FALLING EDGE TO DATA VALID DELAY                                       | $t_{ m DSDO}$        |      |     |      |      |

| VIO > 2.7 V                                                                |                      |      |     | 7.5  | ns   |

| VIO > 1.7 V                                                                |                      |      |     | 10.5 | ns   |

| CNV OR SDI LOW TO SDO D17 MOST SIGNIFICANT BIT (MSB) VALID DELAY (CS MODE) | $t_{\rm EN}$         |      |     |      |      |

| VIO > 2.7 V                                                                |                      |      |     | 10   | ns   |

| VIO > 1.7 V                                                                |                      |      |     | 13   | ns   |

| CNV RISING EDGE TO FIRST SCK RISING EDGE DELAY                             | t <sub>QUIET1</sub>  | 190  |     |      | ns   |

| LAST SCK FALLING EDGE TO CNV RISING EDGE DELAY <sup>5</sup>                | t <sub>QUIET2</sub>  | 60   |     |      | ns   |

| CNV OR SDI HIGH OR LAST SCK FALLING EDGE TO SDO HIGH IMPEDANCE (CS MODE)   | $t_{ m DIS}$         |      |     | 20   | ns   |

| SDI VALID SETUP TIME FROM CNV RISING EDGE                                  | t <sub>SSDICNV</sub> | 2    |     |      | ns   |

| SDI VALID HOLD TIME FROM CNV RISING EDGE (CS MODE)                         | t <sub>HSDICNV</sub> | 2    |     |      | ns   |

| SCK VALID HOLD TIME FROM CNV RISING EDGE (DAISY-CHAIN MODE)                | t <sub>HSCKCNV</sub> | 12   |     |      | ns   |

| SDI VALID SETUP TIME FROM SCK RISING EDGE (DAISY-CHAIN MODE)               | t <sub>SSDISCK</sub> | 2    |     |      | ns   |

| SDI VALID HOLD TIME FROM SCK RISING EDGE (DAISY-CHAIN MODE)                | t <sub>HSDISCK</sub> | 2    |     |      | ns   |

<sup>&</sup>lt;sup>1</sup> アクイジション・フェーズとは、入力サンプリング・コンデンサが新しい入力の取得に使用できる時間です。ここで、AD4002 では 2 MSPS、AD4006 では 1 MSPS、AD4010 では 500 kSPS のスループット・レートで動作する ADC を使用します。

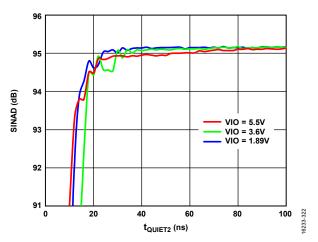

<sup>&</sup>lt;sup>5</sup> SINAD と t<sub>QUIET2</sub> の関係については、図 22 を参照してください。

図 2. タイミングの電圧レベル

<sup>&</sup>lt;sup>2</sup>ターボ・モードでは、t<sub>CNVH</sub> と最小 t<sub>QUIETI</sub> が一致する必要があります。

$<sup>^3</sup>$ ターボ・モードを有効にして、最小 SCK レートである 75 MHz を使用した場合のみ、2 MSPS のスループット・レートが実現します。 さまざまな動作モードで可能な最大スループットについては、表 4 を参照してください。

$<sup>^4</sup>$  SCK では、50% のデューティ・サイクルを想定しています。

表 3. レジスタ読出し/書込みのタイミング

| Parameter                                      | Symbol              | Min  | Тур | Max  | Unit |

|------------------------------------------------|---------------------|------|-----|------|------|

| READ/WRITE OPERATION                           |                     |      |     |      |      |

| CNV Pulse Width <sup>1</sup>                   | $t_{ m CNVH}$       | 10   |     |      | ns   |

| SCK Period                                     | $t_{ m SCK}$        |      |     |      |      |

| VIO > 2.7 V                                    |                     | 9.8  |     |      | ns   |

| VIO > 1.7 V                                    |                     | 12.3 |     |      | ns   |

| SCK Low Time                                   | $t_{ m SCKL}$       | 3    |     |      | ns   |

| SCK High Time                                  | $t_{SCKH}$          | 3    |     |      | ns   |

| READ OPERATION                                 |                     |      |     |      |      |

| CNV Low to SDO D17 MSB Valid Delay             | $t_{ m EN}$         |      |     |      |      |

| VIO > 2.7 V                                    |                     |      |     | 10   | ns   |

| VIO > 1.7 V                                    |                     |      |     | 13   | ns   |

| SCK Falling Edge to Data Remains Valid         | $t_{ m HSDO}$       | 1.5  |     |      | ns   |

| SCK Falling Edge to Data Valid Delay           | $t_{ m DSDO}$       |      |     |      |      |

| VIO > 2.7 V                                    |                     |      |     | 7.5  | ns   |

| VIO > 1.7 V                                    |                     |      |     | 10.5 | ns   |

| CNV Rising Edge to SDO High Impedance          | $t_{ m DIS}$        |      |     | 20   | ns   |

| WRITE OPERATION                                |                     |      |     |      |      |

| SDI Valid Setup Time from SCK Rising Edge      | $t_{ m SSDISCK}$    | 2    |     |      | ns   |

| SDI Valid Hold Time from SCK Rising Edge       | $t_{	ext{HSDISCK}}$ | 2    |     |      | ns   |

| CNV Rising Edge to SCK Edge Hold Time          | $t_{HCNVSCK}$       | 0    |     |      | ns   |

| CNV Falling Edge to SCK Active Edge Setup Time | $t_{SCNVSCK}$       | 6    |     |      | ns   |

$<sup>^1</sup>$ ターボ・モードでは、 $t_{CNVH}$  と最小  $t_{QUIETI}$  が一致する必要があります。

## 表 4. 各動作モードで可能なスループット

| Parameter                                        | Test Conditions/Comments                                   | Min | Тур | Max  | Unit |

|--------------------------------------------------|------------------------------------------------------------|-----|-----|------|------|

| THROUGHPUT, CS MODE                              |                                                            |     |     |      |      |

| 3-Wire and 4-Wire Turbo Mode                     | $f_{SCK} = 100 \text{ MHz}, \text{ VIO} \ge 2.7 \text{ V}$ |     |     | 2    | MSPS |

|                                                  | $f_{SCK} = 80 \text{ MHz}, VIO < 2.7 \text{ V}$            |     |     | 2    | MSPS |

| 3-Wire and 4-Wire Turbo Mode and Six Status Bits | $f_{SCK} = 100 \text{ MHz}, \text{ VIO} \ge 2.7 \text{ V}$ |     |     | 2    | MSPS |

|                                                  | $f_{SCK} = 80 \text{ MHz}, VIO < 2.7 \text{ V}$            |     |     | 1.78 | MSPS |

| 3-Wire and 4-Wire Mode                           | $f_{SCK} = 100 \text{ MHz}, \text{ VIO} \ge 2.7 \text{ V}$ |     |     | 1.75 | MSPS |

|                                                  | $f_{SCK} = 80 \text{ MHz}, VIO < 2.7 \text{ V}$            |     |     | 1.62 | MSPS |

| 3-Wire and 4-Wire Mode and Six Status Bits       | $f_{SCK} = 100 \text{ MHz}, \text{ VIO} \ge 2.7 \text{ V}$ |     |     | 1.59 | MSPS |

|                                                  | $f_{SCK} = 80 \text{ MHz}, VIO < 2.7 \text{ V}$            |     |     | 1.44 | MSPS |

## 絶対最大定格

入力過電圧クランプで過電圧状態を無期限に保つことはできません。

#### 表 5.

| 衣 3.                                  |                                             |

|---------------------------------------|---------------------------------------------|

| Parameter                             | Rating                                      |

| Analog Inputs                         |                                             |

| IN+, IN- to GND <sup>1</sup>          | $-0.3 \text{ V to V}_{REF} + 0.4 \text{ V}$ |

|                                       | or $\pm 130 \text{ mA}^2$                   |

| Supply Voltage                        |                                             |

| REF, VIO to GND                       | -0.3 V to +6.0 V                            |

| VDD to GND                            | -0.3 V to +2.1 V                            |

| VDD to VIO                            | -6 V to +2.4 V                              |

| Digital Inputs to GND                 | -0.3  V to VIO + 0.3  V                     |

| Digital Outputs to GND                | -0.3  V to VIO + 0.3  V                     |

| Storage Temperature Range             | −65°C to +150°C                             |

| Junction Temperature                  | 150°C                                       |

| Lead Temperature Soldering            | 260°C reflow as per                         |

|                                       | JEDEC J-STD-020                             |

| Electrostatic Discharge (ESD) Ratings |                                             |

| Human Body Model                      | 4 kV                                        |

| Machine Model                         | 200 V                                       |

| Field Induced Charged Device Model    | 1.25 kV                                     |

<sup>&</sup>lt;sup>1</sup> IN+および IN- の説明については、アナログ入力 セクションを参照してください。

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間にわたり絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

## 熱抵抗

熱性能は、プリント回路基板 (PCB) の設計と動作環境に直接関連しています。PCB の熱設計には、細心の注意を払う必要があります。

表 6. 熱抵抗

| Package Type <sup>1</sup> | $\theta_{JA}^2$ | θ <sub>JC</sub> <sup>3</sup> | Unit |

|---------------------------|-----------------|------------------------------|------|

| RM-10                     | 147             | 38                           | °C/W |

| CP-10-9                   | 114             | 33                           | °C/W |

<sup>「</sup>テスト条件 1: 熱抵抗のシミュレーション値は、2S2P JEDEC PCB の使用によって決定します。オーダー・ガイドを参照してください。

### ESD に関する注意

ESD (静電放電)の影響を受けやすいデバイスです。 電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

Rev. 0 - 8/37 -

$<sup>^2</sup>$  電流の条件は、 $10 \, \mathrm{ms}$  間隔でテストされています。

$<sup>^2\</sup>theta_{\rm JA}$ は、1立方フィートの密封容器内で測定された、自然対流下におけるジャンクションと周囲温度の間の熱抵抗です。

$<sup>^{3}</sup>$   $\theta_{JC}$  は、ジャンクションとケースの間の熱抵抗です。

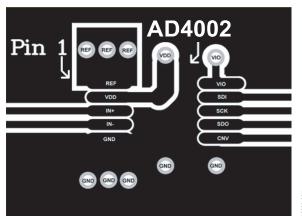

# ピン配置およびピン機能の説明

REF 1 AD4002/ D 10 VIO AD4006/ D 9 SDI IN+ 3 AD4010 B 8 SCK TOP VIEW (Not to Scale) C 6 CNV

NOTES

1. CONNECT THE EXPOSED PAD TO GND.

THIS CONNECTION IS NOT REQUIRED TO

MEET THE SPECIFIED PERFORMANCE.

図 4. 10 ピン LFCSP のピン配置

図 3.10 ピン MSOP のピン配置

表 7. ピン機能の説明

| ピン番号             | 記号   | タイプ 1 | 説明                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | REF  | AI    | リファレンス入力電圧。 $V_{REF}$ 範囲は $2.4V\sim5.1V$ です。このピンは GND ピンと呼ばれ、 $10\mu F$ の $X7R$ セラミック・コンデンサで GND ピンの近くにデカップリングする必要があります。                                                                                                                                                                                                                                                                                     |

| 2                | VDD  | P     | $\pm 1.8$ V 電源。 VDD の範囲は $1.71$ V $\sim 1.89$ V です。 $0.1$ $\mu$ F のセラミック・コンデンサを使用して、VDD を GND にバイパスします。                                                                                                                                                                                                                                                                                                      |

| 3                | IN+  | AI    | アナログ入力。このピンは、アナログ・グラウンド検出ピン(IN-)を基準にします。デバイスは、CNV の立上がりエッジで IN+ と IN- の間の電圧差をサンプリングします。(IN+) – (IN-) の動作入力範囲は $0$ $V$ $\sim$ $V_{REF}$ .                                                                                                                                                                                                                                                                     |

| 4                | IN-  | AI    | アナログ入力のグラウンド・センス。このピンはアナログ・グラウンド・プレーンまたはリモート・センス・グラウンドに接続します。                                                                                                                                                                                                                                                                                                                                                |

| 5                | GND  | P     | 電源グラウンド                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6                | CNV  | DI    | 入力変換。この入力には、複数の機能があります。立上がりエッジでは、変換を開始して、デバイスのインターフェース・モードをデイジーチェーン・モードまたは $\overline{CS}$ モードから選択します。 $\overline{CS}$ モードでは、 $\overline{CS}$ モードでは、 $\overline{CS}$ モードでは、 $\overline{CS}$ モードでは、 $\overline{CS}$ モードでは、 $\overline{CS}$ モードでは、 $\overline{CS}$ ボークの場合に $\overline{SDO}$ ピンがイネーブルになります。デイジーチェーン・モードでは、 $\overline{CS}$ ボークの 読出しが実行されます。                                                     |

| 7                | SDO  | DO    | シリアル・データ出力変換結果はこのピンに出力されます。SCK に同期されます。                                                                                                                                                                                                                                                                                                                                                                      |

| 8                | SCK  | DI    | シリアル・データ・クロック入力デバイスを選択すると、変換結果はこのクロックによってシフト出力されます。                                                                                                                                                                                                                                                                                                                                                          |

| 9                | SDI  | DI    | シリアル・データ入力。この入力には、複数の機能があります。ADC のインターフェース・モードを次のように選択します。                                                                                                                                                                                                                                                                                                                                                   |

|                  |      |       | CNV 立上がりエッジの発生時に SDI がローの場合、デイジーチェーン・モードが選択されます。このモードでは、SDI がデータ入力として使用され、 $2$ つ以上の ADC の変換結果が $1$ 本の SDO ラインでデイジーチェーン接続されます。SDI のデジタル・データ・レベルは、 $18$ SCK サイクルの遅延で SDO に出力されます。CNV 立上がりエッジの発生時に SDI がハイの場合、 $\overline{CS}$ モードが選択されます。このモードでは、SDI または CNV がローの場合に、シリアル出力信号を有効にできます。SDI または CNV がローの場合、変換が完了すると、ビジー・インジケータ機能が有効になります。CNV がローの場合は、SCK の立上がりエッジの発生時に、SDIで $18$ ビット・ワードをクロック入力してデバイスをプログラムできます。 |

| 10               | VIO  | P     | 入出力インターフェースのデジタル電源。通常、このピンはホスト・インターフェースと同じ電源 $(1.8 \text{ V}, 2.5 \text{ V}, 3 \text{ V}, または 5 \text{ V}) 0.1 \muF のセラミック・コンデンサで VIO を GND へバイパスします。$                                                                                                                                                                                                                                                       |

| N/A <sup>2</sup> | EPAD | P     | 露出パッド(LFCSPのみ)。露出パッドはGNDに接続します。この接続がなくても、仕様規定されている性能を満たすことができます。                                                                                                                                                                                                                                                                                                                                             |

¹AIはアナログ入力、Pは電源、DIはデジタル入力、DOはデジタル出力です。

<sup>&</sup>lt;sup>2</sup>N/A は該当なしを意味します。

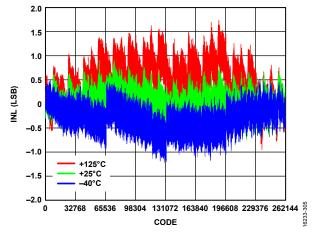

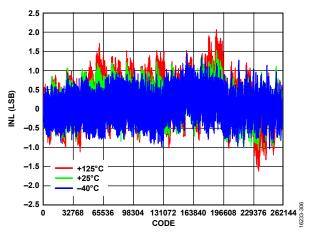

## 代表的な性能特性

特に注記のない限り、VDD=1.8 V、VIO=3.3 V、 $V_{REF}$ =5 V、 $T_A$ =25 °C、高インピーダンス・モードは無効、スパン圧縮は無効、ターボ・モードは有効、AD4002 では  $f_S$ =2 MSPS、AD4006 では  $f_S$ =1 MSPS、AD4010 では  $f_S$ =500 kSPS。

図 5. 多様な温度での INL とコードの関係、V<sub>REF</sub> = 5 V

図 6. 多様な温度での INL とコードの関係、V<sub>REF</sub> = 2.5 V

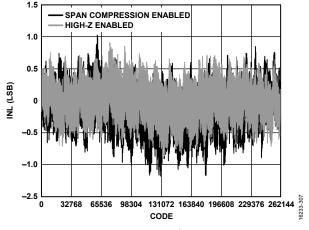

図 7. INL とコードの関係、高インピーダンス・ モードとスパン圧縮モードを有効、V<sub>REF</sub> = 5 V

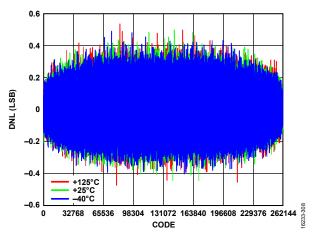

図 8. 多様な温度での DNL とコードの関係、V<sub>REF</sub> = 5 V

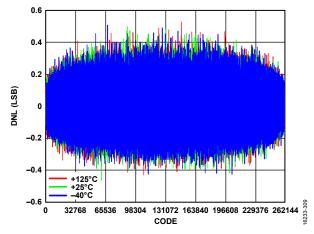

図 9. 多様な温度での DNL とコードの関係、V<sub>REF</sub> = 2.5 V

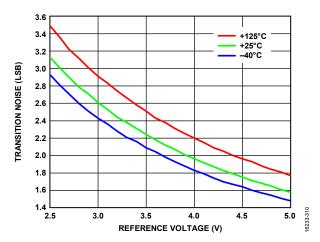

図 10. 多様な温度での遷移ノイズとリファレンス電圧の関係

Rev. 0 — 10/37 —

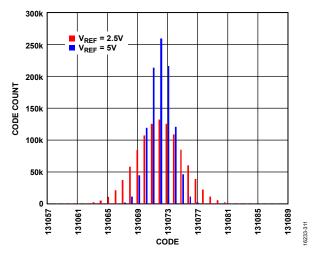

図 11. コード中央での DC 入力のヒストグラム、  $V_{REF}$  = 2.5 V および  $V_{REF}$  = 5 V

図 12.1 kHz、  $\theta$ .5 dBFS 入力トーン高速フーリエ変換(FFT)、 広視野、 $V_{REF}$  = 5 V

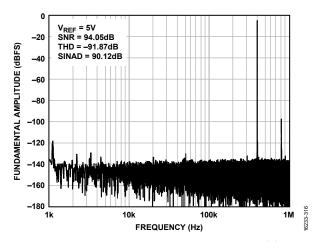

図 13. 100 kHz、 θ.5 dBFS 入力トーン FFT、広視野

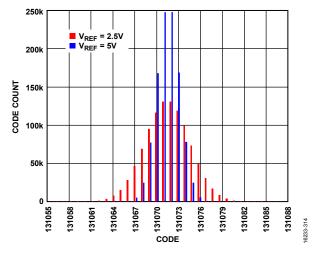

図 14. コード遷移での DC 入力のヒストグラム、  $V_{REF}$  = 2.5 V および  $V_{REF}$  = 5 V

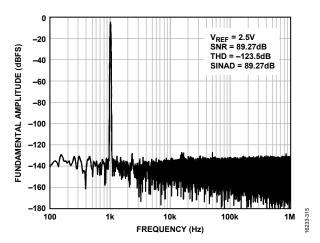

図 15.1 kHz、 θ.5 dBFS 入力トーン FFT、広視野、V<sub>REF</sub> = 2.5 V

図 16.400 kHz、  $\theta$ .5 dBFS 入力トーン FFT、広視野

Rev. 0 — 11/37 —

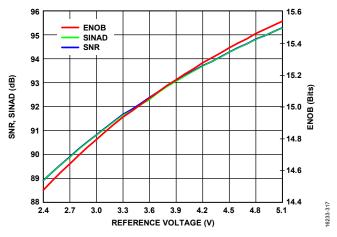

図 17. SNR、SINAD、有効ビット数(ENOB)とリファレンス 電圧の関係、f<sub>IN</sub> = 1 kHz

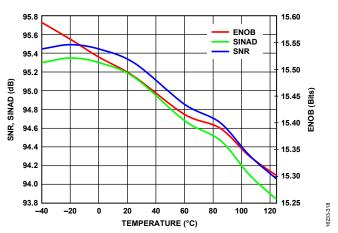

図 18. SNR、SINAD、ENOB と温度の関係、f<sub>IN</sub> = 1 kHz

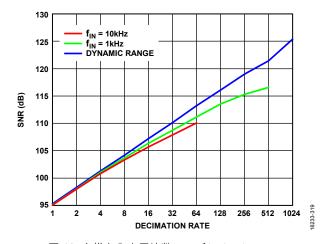

図 19. 多様な入力周波数でのデシメーション・ レシオと SNR の関係、2 MSPS

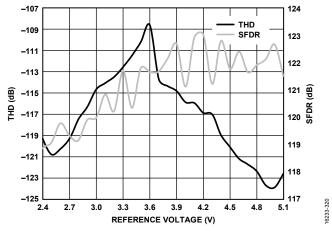

図 20. THD、SFDR とリファレンス電圧の関係、 $f_{IN}$  = 1 kHz

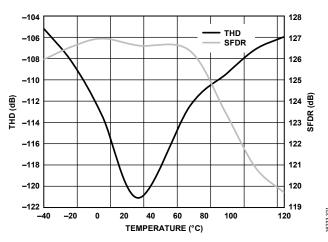

図 21. THD、SFDR と温度の関係、f<sub>IN</sub> = 1 kHz

図 22. SINAD と t<sub>QUIET2</sub> の関係

Rev. 0 — 12/37 —

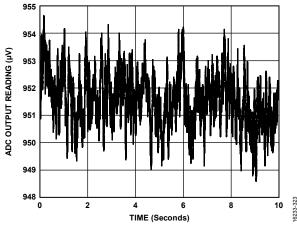

図 23. 0.1 Hz ~ 10 Hz 帯域幅の 1/f ノイズ、50 kSPS、 1 回の読出しで 2500 個のサンプルを平均化

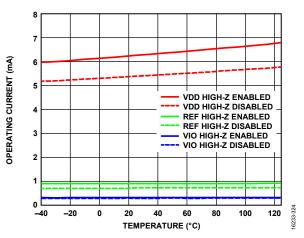

図 24. 動作電流と温度の関係、AD4002、2 MSPS

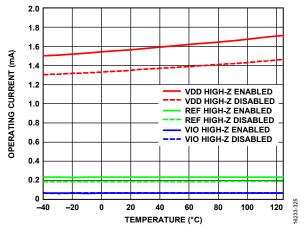

図 25. 動作電流と温度の関係、AD4010、500 kSPS

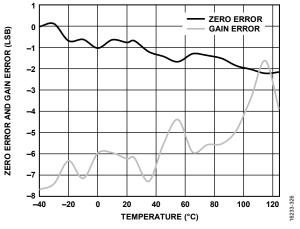

図 26. ゼロ誤差、ゲイン誤差と温度の関係

図 27. 動作電流と温度の関係、AD4006、1 MSPS

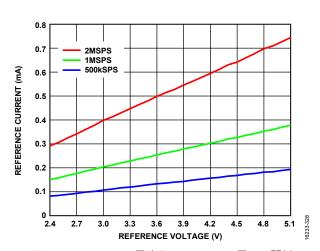

図 28. リファレンス電流とリファレンス電圧の関係

Rev. 0 — 13/37 —

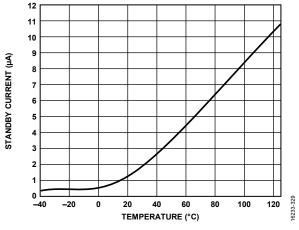

図 29. スタンバイ電流と温度の関係

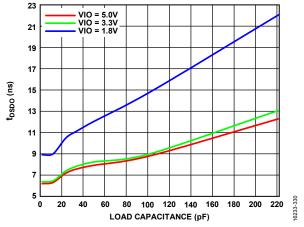

図 30. t<sub>DSDO</sub> と負荷容量の関係

Rev. 0 - 14/37 -

## 用語の定義

#### 積分非直線性誤差 (INL)

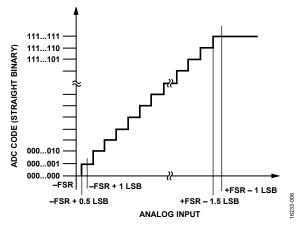

INLは、負のフルスケールと正のフルスケールを結ぶ直線と個々のコードとの偏差です。最初のコード遷移より ½LSB だけ手前の点を負のフルスケールとして使います。正のフルスケールは、最後のコード遷移を 1½LSB 上回ったレベルとして定義されます。偏差は各コードの中央から真の直線までの距離として測定されます(図 32 を参照)。

#### 微分非直線性誤差(DNL)

理想的な ADC では、コード遷移は 1 LSB だけ離れた位置で発生します。DNLとは、この理想値からの最大偏差のことです。ノー・ミス・コードの分解能で仕様規定されます。

#### ゼロ誤差

ゼロ誤差は、最初のコード遷移で発生する理想的な電圧 (アナログ・グラウンドより 1/2 LSB 高い) とコードを生成する実際の電圧の間の差です。

#### ゲイン誤差

最初の遷移( $100\cdots00$  から  $100\cdots01$ )は負の公称フルスケールより 1 LSB 上のレベル( $\pm 5$  V の範囲で -4.999981 V)で発生します。最後の遷移( $011\cdots10$  から  $011\cdots11$ )は、公称フルスケールより 1 LSB 低いアナログ電圧( $\pm 5$  V の範囲では +4.999943 V)で発生します。実際のゲインにおける最初の遷移と最後の遷移間の変化量および理想的なゲインにおける最初の遷移と最後の遷移間の変化量は一致しません。この変化量の相違がゲイン誤差になります。

## スプリアスフリー・ダイナミック・レンジ(SFDR)

SFDR は、入力信号の二乗平均平方根 (rms) 振幅とピーク・スプリアス信号間の差で、単位はデシベル (dB) です。

## 有効ビット数 (ENOB)

ENOBは、サイン波入力による分解能の測定値です。次のように SINAD を使用して計算します。

$ENOB = (SINAD_{dB} - 1.76) /6.02$

ENOB の単位はビットです。

#### 全高調波歪み (THD)

THD は、フルスケール入力信号の rms 値に対する最初の 5 次高調波成分の rms 総和の比率で、単位はデシベルです。

#### ダイナミック・レンジ

ダイナミック・レンジは、測定した合計 rms ノイズに対するフルスケールの rms 値の比率です。ダイナミック・レンジの単位はデシベルです。すべてのノイズ・ソースと DNL アーティファクトが含まれるように、-60 dBFS の信号で測定されます。

#### S/N比(SNR)

S/N 比 は、ナイキスト周波数を下回るすべてのスペクトル成分(高調波成分と直流成分を除く)の rms 総和に対する実際の入力信号の rms 値の比です。 S/N 比 の単位はデシベルです。

#### 信号/ノイズ + 歪み (SINAD)

SINAD は、ナイキスト周波数を下回るすべてのスペクトル成分の rms 総和(高調波成分は含むが、直流成分と入力信号は除く)に対する実際の入力信号の rms 値の比です。 SINAD の単位はデシベルです。

#### アパーチャ遅延

アパーチャ遅延は、アクイジション性能の測定値です。CNV 入力の立上がりエッジと入力信号が変換のために保持される間の時間です。

#### 過渡応答

過渡応答は、±0.5 LSB の精度でフルスケール入力ステップを達成するのに必要な時間です。

#### 電源電圧変動除去比 (PSRR)

PSRR は、周波数 f での ADC VDD 電源に加えられた  $200\,\mathrm{mV}$  p-p サイン波の電力に対する周波数 f での ADC 出力電力の比です。

PSRR (dB) = 10 log ( $P_{VDD\_IN}/P_{ADC\_OUT}$ )

ここで、

$P_{VDD\_IN}$ は、周波数 f での VDD ピンの電力。 $P_{ADC\_OUT}$ は、周波数 f での ADC の出力電力。

## 動作原理

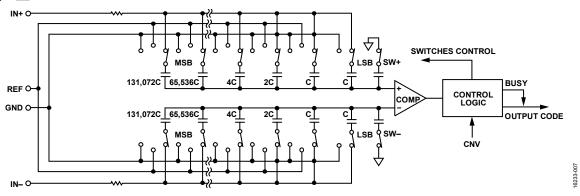

図 31. ADC の簡略化した回路図

### 回路説明

AD4002/AD4006/AD4010 は、SAR アーキテクチャに基づいた、 高速、低消費電力、単電源、高精度の 18 ビット疑似差動 ADC です。

AD4002 は 1 秒あたり 2,000,000 サンプルを変換でき (2 MSPS)、AD4006 は 1 秒あたり 1,000,000 サンプルを変換でき (1 MSPS)、AD4010 は 1 秒あたり 500,000 サンプルを変換できます (500 kSPS)。変換を実行していない場合、AD4002/AD4006/AD4010 は電源をオフにするので、消費電力はスループットに比例します。例えば、10 kSPS で動作させる場合、通常の消費電力は、バッテリ駆動アプリケーションに最適な 70  $\mu$ W になります。また、AD4002/AD4006/AD4010 では、長期間にわたるパワーダウン後の最初の変換でも有効な結果が得られるため、ADC が継続的に変換を行う必要のないアプリケーションでは、さらに消費電力を低減することができます。

AD4002/AD4006/AD4010 は、オンチップ・トラック&ホールド機能を備えています。また、パイプライン遅延などの遅延がないので、マルチプレクス・アプリケーションに最適です。

AD4002/AD4006/AD4010 では、利便性の高い多数の独自機能を 実装することで、システムの消費電力とフットプリントを低減し ています。

AD4002/AD4006/AD4010 には、アナログ入力の過電圧による損傷からデバイスを保護する内部電圧クランプが備わっています。

アナログ入力には、代表的なスイッチド・キャパシタ SAR 入力に見られる、非直線性チャージ・キックバックを減らす回路を実装しています。このキックバックの削減と長いアクイジション・フェーズを組み合わせると、駆動アンプでのセトリング条件が緩和されます。この組み合わせにより、帯域幅が狭く、消費電力が小さいアンプをドライバとして使用できます。さらに、入力 RC フィルタの大きな抵抗値とそれに対応する小さなコンデンサを利用できるという利点もあります。この結果、アンプの RC 負荷が小さくなり、安定性と消費電力が向上します。

レジスタ・ビットをプログラミングすることで、SPIインターフェース経由で高インピーダンス・モードを有効にできます(表 14 を参照)。高インピーダンス・モードを有効にすると、ADC入力の充電電流と信号周波数が低くなり、最大100kHzの広い周波数での歪みが改善されます。100kHzを超える周波数とマルチプレクスでは、高インピーダンス・モードを無効にしてください。

単電源アプリケーションでは、スパン圧縮機能により、駆動アンプが ADC の全範囲にアクセスするため、ヘッドルームとフットルームが余分に形成されます。

AD4002/AD4006/AD4010 の高速変換とターボ・モードにより、それぞれの最大スループット・レートで動作する場合でも、低いクロック・レートで変換をリードバックできます。AD4002 の場合、2 MSPS のフルスループット・レートは、ターボ・モードでのみ実現できます。

AD4002/AD4006/AD4010 は、 $1.8\,V\sim 5\,V$ のデジタル・ロジック・ファミリーのすべての製品に接続できます。  $10\,$ ピン MSOP またはスペースの節約と柔軟な設定が可能な小型  $10\,$ ピン LFCSP を用意しています。

AD4002/AD4006/AD4010 は、表 8 にある 14/16/18/20 ビットの高 精度 SAR ADC とのピン互換を実現するピンです。

表 8. MSOP、LFCSP 14/16/18/20 ビットの高精度 SAR ADC

|                 |                       |                       | 400 kSPS to           |                       |

|-----------------|-----------------------|-----------------------|-----------------------|-----------------------|

| Bits            | 100 kSPS              | 250 kSPS              | 500 kSPS              | ≥1000 kSPS            |

| $20^{1}$        |                       |                       |                       | $AD4020^{2}$          |

| 18 <sup>1</sup> | AD7989-1 <sup>2</sup> | AD7691 <sup>2</sup>   | $AD4011^{2}$ ,        | $AD4003^{2}$ ,        |

|                 |                       |                       | $AD7690^{2}$ ,        | $AD4007^{2}$ ,        |

|                 |                       |                       | AD7989-5 <sup>2</sup> | $AD7982^2$ ,          |

|                 |                       |                       |                       | AD7984 <sup>2</sup>   |

| $18^{3}$        |                       |                       | $AD4010^{2}$          | $AD4002^{2}$ ,        |

|                 |                       |                       |                       | AD4006 <sup>2</sup>   |

| 16 <sup>1</sup> | AD7684                | AD7687 <sup>2</sup>   | $AD7688^{2}$ ,        | AD4001 <sup>2</sup> , |

|                 |                       |                       | $AD7693^{2}$ ,        | $AD4005^{2}$ ,        |

|                 |                       |                       | AD7916 <sup>2</sup>   | AD7915 <sup>2</sup>   |

| $16^{3}$        | AD7680,               | AD7685 <sup>2</sup> , | $AD7686^{2}$ ,        | $AD4000^{2}$ ,        |

|                 | AD7683,               | AD7694                | $AD7988-5^2$ ,        | $AD4004^{2}$ ,        |

|                 | AD7988-1 <sup>2</sup> |                       | $AD4008^{2}$          | $AD7980^{2}$ ,        |

|                 |                       |                       |                       | AD7983 <sup>2</sup>   |

| 14 <sup>3</sup> | AD7940                | AD7942 <sup>2</sup>   | AD7946 <sup>2</sup>   | Not applicable        |

<sup>&</sup>lt;sup>l</sup> 真の差動。

Rev. 0 — 16/37 —

<sup>2</sup>ピン互換。

<sup>3</sup> 疑似差動。

### コンバータの動作

AD4002/AD4006/AD4010 は、電荷再配分式サンプリング D/A コンバータ(DAC)を使用した SAR ベースの ADC です。図 31 に、ADC の簡略化した回路図を示します。容量性 DAC は、18 個のバイナリ重み付けコンデンサからなる 2 つの同一なアレイで構成されており、これらのアレイは 2 つのコンパレータ入力に接続されます。

アクイジション・フェーズ中、コンパレータの入力に接続されたアレイの端子は、SW+スイッチとSW-スイッチを経由してGNDに接続されます。独立したスイッチを使用して、各コンデンサの他の端子をアナログ入力に接続します。コンデンサのアレイをサンプリング・コンデンサとして使用して、IN+入力とIN-入力のアナログ信号を取得できます。

アクイジション・フェーズが完了し、CNV 入力がハイになると、変換フェーズが開始されます。変換フェーズが開始すると、SW+と SW-が最初にオープンになります。次に、2つのコンデンサ・アレイが入力から切断され、GND 入力に接続されます。アクイジション・フェーズの最後に収集される IN+と IN-の間の差動電圧がコンパレータの入力に印加され、コンパレータが不均衡状態になります。GND と  $V_{REF}$ の間にあるコンデンサ・アレイの各要素を切り替えることで、コンパレータの入力値はバイナリ重み付けされた電圧ステップ( $V_{REF}/2$ 、 $V_{REF}/4$ 、…、 $V_{REF}/262,144$ )によって変化します。コントロール・ロジックはこれらのスイッチを切り替え、MSB からコンパレータを均衡状態に戻します。この

プロセスの完了後、コントロール・ロジックは ADC 出力コード とビジー信号インジケータを生成します。

AD4002/AD4006/AD4010 には変換クロックが内蔵されているので、変換プロセスでシリアル・クロック SCK は必要ありません。

#### 伝達関数

図 32 と表 9 に、AD4002/AD4006/AD4010 の理想的な伝達特性を示します。

図 32. ADC の理想的な伝達関数 (FSR はフルスケール範囲)

表 9. 出力コードと入力電圧の理論値

| Description      | Analog Input, V <sub>REF</sub> = 5 V | V <sub>REF</sub> = 5 V with Span Compression Enabled (V) | Digital Output Code (Hex) |

|------------------|--------------------------------------|----------------------------------------------------------|---------------------------|

| FSR – 1 LSB      | 4.999981 V                           | 4.499985                                                 | 0x3FFFF <sup>1</sup>      |

| Midscale + 1 LSB | 2.500019 V                           | 2.500015                                                 | 0x20001                   |

| Midscale         | 2.5 V                                | 2.5                                                      | 0x20000                   |

| Midscale - 1 LSB | 2.499981 V                           | 2.499985                                                 | 0x1FFFF                   |

| -FSR + 1 LSB     | 19.07 μV                             | 0.50001526                                               | 0x00001                   |

| -FSR             | 0 V                                  | 0.5                                                      | $0x00000^2$               |

<sup>&</sup>lt;sup>1</sup> この出力コードはオーバーレンジ・アナログ入力のコードです(スパン圧縮が無効の場合は、 $V_{REF}$  を  $V_{IN+}$  -  $V_{IN-}$  だけ上回り、スパン圧縮が有効の場合は、0.9 ×  $V_{REF}$  だけ上回る)。

$<sup>^2</sup>$ この出力コードはアンダーレンジ・アナログ入力のコードです(スパン圧縮が無効の場合は、VREF を  $V_{\rm IN+}$  -  $V_{\rm IN-}$  だけ下回り、スパン圧縮が有効の場合は、0.1 ×  $V_{\rm REF}$  だけ下回る)。

# アプリケーション情報

## 代表的なアプリケーション図

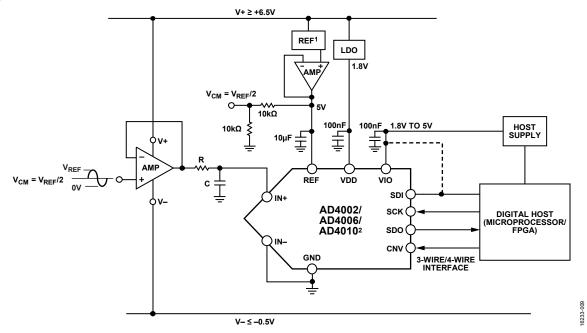

図33 に、複数の電源を使用できる場合のAD4002/AD4006/AD4010 の推奨接続図の例を示します。この構成を使用すると、最大信号範囲を実現するアンプ電力を選択できるので、最高の性能を達成できます。

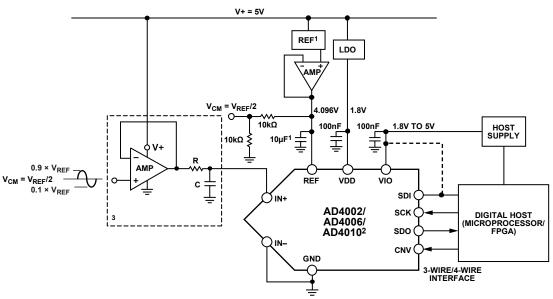

図34に、単電源システムを使用する場合に推奨される接続図を示します。このセットアップは、システムで使用できるレールの数が限られ、消費電力が非常に重要になる場合のみ選択します。

図 33. 複数の電源を使用する場合の代表的なアプリケーション図

<sup>1</sup>SEE THE VOLTAGE REFERENCE INPUT SECTION FOR REFERENCE SELECTION. C<sub>REF</sub> IS USUALLY A 10µF CERAMIC CAPACITOR (X7R).

<sup>2</sup>SPAN COMPRESSION MODE ENABLED.

<sup>3</sup>SEE TABLE 10 FOR RC FILTER AND AMPLIFIER SELECTION.

図 34. 単電源を使用する場合の代表的なアプリケーション図

010

Rev. 0

#### アナログ入力

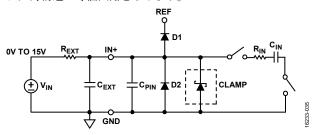

図 35 に、AD4002/AD4006/AD4010 の過電圧クランプを含むアナログ入力構造の等価回路を示します。

図 35. アナログ入力の等価回路

#### 入力過電圧クランプ回路

ほとんどの ADC アナログ入力 IN+ と IN- には、ESD 保護ダイオードの他に、過電圧保護回路はありません。過電圧が発生すると、アナログ入力ピン(IN+または IN-)と REF 順方向バイアスの間に接続された ESD 保護ダイオードによって、入力ピンが REF に短絡されるので、リファレンスの過電圧やデバイスの損傷が発生する可能性があります。 AD4002/AD4006/AD4010 は、内部過電圧クランプ回路と大きな外部抵抗( $R_{\rm EXT}$  = 200  $\Omega$ )を備えているので、外部保護ダイオードが不要になり、ADC 入力を DC 過電圧から保護します。

アンプ・レールが  $V_{REF}$  よりも大きく、グラウンドよりも小さいアプリケーションでは、出力がデバイスの入力電圧を超える場合があります。この場合、AD4002/AD4006/AD4010 の内部電圧クランプ回路は、入力電圧を安全な動作範囲にクランプし、リファレンスの外乱を防ぐことで、入力ピンの電圧が  $V_{REF}$  + 0.4 V を超えないようにしてデバイスの損傷を防ぎます。この機能は複数のADC でリファレンスを共有するシステムで特に重要です。

アナログ入力がリファレンス電圧を 0.4 V 超えると、内部クランプ回路がオンになり、電流がクランプからグラウンドに流れるので、入力の上昇によるデバイスの損傷を防止できます。クランプは D1 の前でオンになり(図 35 を参照)、最大 50 mA の電流をシンクできます。

クランプがアクティブな場合、リードバックできるレジスタで OV クランプ・フラグ・ビットが設定されます(表 14 を参照)。これは読出しでクリアする必要のあるスティッキー・ビットです。過電圧クランプ・フラグを使用すれば、ステータス・ビットでもクランプのステータスを確認できます(表 15 を参照)。クラン

プ回路は、オフの状態では静的電力を消費しません。クランプで 過電圧状態を無期限に保つことはできません。

通常、ADC 入力には外部 RC フィルタが適用され、入力信号の帯域が制限されます。過電圧時に、超過電圧は  $R_{\rm EXT}$  で降下し、 $R_{\rm EXT}$  は保護回路の一部になります。 $R_{\rm EXT}$  値は 15 V の保護のために  $200~\Omega\sim20~k\Omega$  の間で変化します。クランプを正常に動作させるため、 $C_{\rm EXT}$  値を 100~pF まで下げることができます。入力過電圧クランプの仕様については、表1 を参照してください。

アナログ入力構造により、IN+とIN-の間の真の差動信号のサンプリングが可能になります。これらの差動入力を使用すると、両方の入力に共通する信号が除去されます。IN-を使用してリモート信号グラウンドを検出することで、センサーとローカルADCグラウンド間のグラウンド電位差は除去されます。

#### スイッチド・キャパシタ入力

アクイジション・フェーズ中、アナログ入力のインピーダンス (IN+または IN-) は、 $R_{\rm IN}$  と  $C_{\rm IN}$  の直列接続によって形成されるネットワークおよびコンデンサ  $C_{\rm PIN}$  の並列組み合わせとしてモデリングできます。 $C_{\rm PIN}$  の大部分はピン容量です。通常、 $R_{\rm IN}$  は 400  $\Omega$  で、直列抵抗とスイッチのオン抵抗で構成される集中定数コンポーネントです。通常、 $C_{\rm IN}$  は 40 pF で、ADC のサンプリング・コンデンサです。

スイッチがオープンになる変換フェーズ中、入力インピーダンスは  $C_{PIN}$  に制限されます。 $R_{IN}$  と  $C_{IN}$  は、不要なエイリアシング効果を削減してノイズを抑える単極のローパス・フィルタを生成します。

#### RC フィルタ値

RC フィルタの値(図 33 と 図 34 の R と C で表される)と駆動アンプは、フル・スループットで入力信号の帯域幅によって選択できます。入力信号の帯域幅を狭くすると、RC カットオフを減らすことができ、コンバータに混入するノイズを低減できます。さまざまなスループットで最適な性能を発揮するには、推奨される RC 値(200  $\Omega$ 、180 pF)と ADA4807-1 を使用します。

表 10 に示す RC 値を選択してドライブに関する要件を緩和し、ADC 入力保護を向上できます。大きな R 値( $200\Omega$ )と小さな C 値を組み合わせると、駆動するアンプの動的負荷が減少します。 C の値を小さくすると、アンプの安定性/位相マージンに関する 懸念事項が減ります。R の値を大きくすると、アンプの出力が ADC の入力範囲を超えた場合に ADC 入力に流れ込む電流が制限されます。

表 10. さまざまな入力帯域幅に対する RC フィルタとアンプの選択

| 20 101 C 01 C 01 01 173 113 70 III 7 3 | , , , , , , , , , , , , , , , , , , , , |                             |                             |

|----------------------------------------|-----------------------------------------|-----------------------------|-----------------------------|

| Input Signal Bandwidth (kHz)           | R (Ω)                                   | C (pF)                      | Recommended Amplifier       |

| <10                                    | See the High-Z Mode section             | See the High-Z Mode section | See the High-Z Mode section |

| <200                                   | 200                                     | 180                         | ADA4807-1                   |

| >200                                   | 200                                     | 120                         | ADA4897-1                   |

| Multiplexed                            | 200                                     | 120                         | ADA4897-1                   |

## ドライバ・アンプの選択

AD4002/AD4006/AD4010 は簡単に駆動できますが、ドライバ・アンプは次の条件を満たす必要があります。

• AD4002/AD4006/AD4010 の S/N 比と遷移ノイズ性能を維持するには、ドライバ・アンプによって生成されるノイズを低く抑える必要があります。ドライバから発生するノイズは、アナログ入力回路の  $R_{\rm IN}$  と  $C_{\rm IN}$  で構成される単極ローパス・フィルタ、または外付けフィルタ(使用した場合)によって除去されます。 AD4002/AD4006/AD4010 のノイズは30.4  $\mu$ V rms(代表値)であるため、アンプに起因する S/N 比の性能低下は、次式で与えられます。

$$SNR_{LOSS} = 20 \log \left( \frac{(30.4 \,\mu\text{V})}{\sqrt{(30.4 \,\mu\text{V})^2 + \frac{\pi}{2} f_{-3 \,dB} (Ne_N)^2}} \right)$$

ここで、

$f_{-3dB}$  は AD4002/AD4006/AD4010(10 MHz)の入力帯域幅 (MHz)、または入力フィルタのカットオフ周波数(使用する場合)。

Nはアンプのノイズ・ゲイン(例えば、バッファ構成では 1)。  $e_N$ は、オペ・アンプの等価入力ノイズ電圧  $(nV/\sqrt{Hz})$ 。

- ACアプリケーションの場合、ドライバはAD4002/AD4006/ AD4010 に見合う THD 性能を発揮する必要があります。

- マルチチャンネルのマルチプレクス・アプリケーションでは、コンデンサ・アレイへのフルスケール・ステップに対して18 ビット・レベル(0.000384%、3.84 ppm)でドライバ・アンプとAD4002/AD4006/AD4010のアナログ入力回路をセトリングする必要があります。

一般に、アンプのデータシートでは、0.1%~0.01%で設定が仕様規定されます。18 ビット・レベルでは、このセトリング時間が大幅に異なる場合があるので、ドライバの選択前に検証する必要があります。

#### 高周波の入力信号

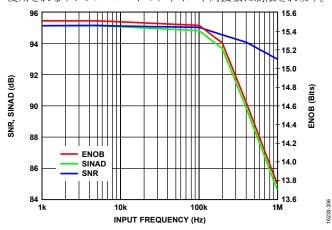

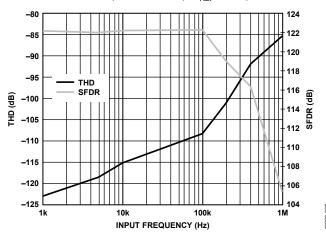

5 V のリファレンス電圧を使用し、広い入力周波数範囲にわたる AD4002/AD4006/AD4010 の AC 性能を図 36 および 図 37 に示します。従来の SAR ADC とは異なり、AD4002/AD4006/AD4010 の AC 性能はわずかに低下しますが、ナイキスト周波数までの入力周波数に対して優れた AC 性能が維持されます。入力周波数は、使用されるサンプル・レートのナイキスト周波数に制限されます。

図 36. /N 比、SINAD、有効ビット数と入力周波数の関係、 VDD = 1.8 V、VIO = 3.3 V、V<sub>REF</sub> = 5 V、25 ° C

図 37. THD、SFDR と入力周波数の関係、VDD = 1.8 V、 VIO = 3.3 V、V<sub>REF</sub> = 5 V、25 ° C

Rev. 0

#### マルチプレクス・アプリケーション

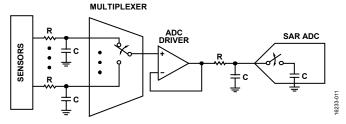

AD4002/AD4006/AD4010 は、ノイズ、電力、スループットの点で優れた性能が必要になるマルチプレクス・アプリケーションの複雑さを軽減し、コストを削減します。図 38 に、マルチプレクサ、ADC ドライバ、高精度 SAR ADC を含むマルチプレクス・データ・アクイジション・システムの簡略ブロック図を示します。

図 38. AD4002/AD4006/AD4010 を使用したマルチプレクス・ データ・アクイジション・シグナル・チェーン

通常、マルチプレクサ・チャンネルを切り替えると、ADC 入力で大きな電圧ステップが発生します。正確な変換結果を得られるようにするには、ADC が (CNVの立上がりエッジで)入力をサンプリングする前に、このステップに十分なセトリング時間を割り当てる必要があります。システムのセトリング時間は、駆動回路(マルチプレクサと ADC ドライバ)、RC フィルタ値、マルチプレクサのチャンネル切り替え時間によって異なります。変換結果の破損を防ぐ一方で最大限のセトリング時間を確保するには、変換開始から toueri が経過した直後にマルチプレクサ・チャンネルを切り替える必要があります。

アナログ入力が変換開始の禁止時間(t<sub>QUIETI</sub>)中にマルチプレクスされると、実行中の変換が破損する可能性があります。変換の破損を避けるため、t<sub>QUIETI</sub>時間中にマルチプレクサ・チャンネルを切り替えないでください。

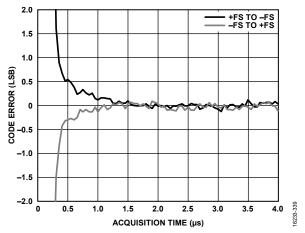

図39に、正と負のフルスケール入力間での切替え時の変換誤差とセトリング時間を示します(表9で説明)。変換誤差とは、正または負のフルスケールの入力に対するコード出力の予想値と実際の値の間の偏差です。

図 39. 変換誤差とセトリング時間の関係、 フルスケール入力ステップ VDD = 1.8 V、VIO = 3.3 V、 $V_{REF}$  = 5 V、 $T_A$  = 25 °C

#### ドライブ補助機能

#### 入力スパン圧縮

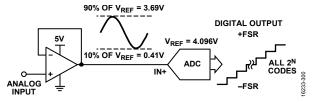

単電源アプリケーションでは、ADC の全範囲を使用することが望ましいですが、アンプにはヘッドルームとフットルームの条件があり、レール to レールの入出力アンプでも、問題が発生する可能性があります。AD4002/AD4006/AD4010 は、スパン圧縮機能を備えています。これにより、範囲の上下から入力範囲を10%削減することで、アンプが使用できるヘッドルームとフットルームを増やしながら、すべてのADCコードに引き続きアクセスできます(図40を参照)。スパン圧縮を有効にすると、削減された入力範囲でS/N比は約1.9 dB(20×log(8/10))減少します。デフォルトでは、スパン圧縮は無効になっていますが、関連するレジスタ・ビットに書出しを実行することで有効になります(デジタル・インターフェースセクションを参照)。

図 40. スパン圧縮

#### 高インピーダンス・モード

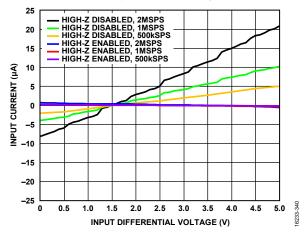

AD4002/AD4006/AD4010 には、高インピーダンス・モードが組み込まれています。これにより、アクイジションの開始時にコンデンサの DAC が入力に切り替わるとき、非直線性のチャージ・キックバックが削減されます。図 41 に、高インピーダンス・モードを有効にした場合と無効にした場合の AD4002/AD4006/AD4010の入力電流を示します。入力電流が低く、高インピーダンス・モードが無効な場合でも、市販されている従来型の SAR ADC よりも簡単に ADC を駆動できます。さらに、高インピーダンス・モードを有効にすると、入力電流はマイクロアンペア未満まで減少します。高インピーダンス・モードはデフォルトで無効ですが、レジスタに書出しを実行することで有効になります(表 14 セクション)。100 kHz を超える周波数やマルチプレクスでは、高インピーダンス・モードを無効にしてください。

図 41. 入力電流と入力差動電圧の関係、VDD = 1.8 V、 VIO = 3.3 V、V<sub>REF</sub> = 5 V、T<sub>A</sub> = 25 °C

精度と分解能の高い SAR ADC の最適なデータシート性能を実現するアプリケーションを設計するには、専用の高出力、高速アンプを使用して従来型のスイッチド・キャパシタ SAR ADC 入力を駆動する必要があります。通常、正確なデータ・アクイジション・シグナル・チェーンの設計中、この課題に直面します。低速(<10 kHz)または DC タイプの信号では入力電流が低くなり、最大 100 kHz までの周波数範囲では歪み(THD)性能が改善することが、高インピーダンス・モードの利点です。高インピーダンス・モードを使用すると、低い RC フィルタ・カットオフで低電力、低帯域幅、高精度のアンプを選択できるので、専用の高速 ADC ドライバが不要になります。この結果、高精度、低帯域幅アプリケーションのシステム消費電力、サイズ、コストを節約できます。高インピーダンス・モードでは、スイッチド・キャパシタ SAR ADC入力のセトリング条件ではなく、対象となる信号帯域幅に応じて、ADC の前段にあるアンプと RC フィルタを選択できます。

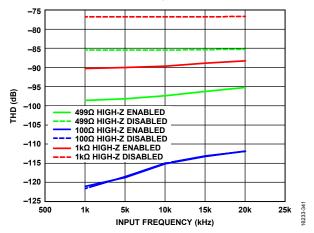

さらに、AD4002/AD4006/AD4010では、従来型の SAR よりも高いソース・インピーダンスで駆動できます。つまり、RC フィルタなしの抵抗は、以前の SAR 設計よりも値が 10 倍高くなります。ここで、高インピーダンス・モードを有効にすると、さらに大きなインピーダンスに耐えることができます。図 42 に、高インピーダンス・モードが有効/無効な場合、さまざまなソース・インピーダンスでの THD 性能を示します。

図 42. 各ソース・インピーダンスの THD と入力周波数の関係、 VDD = 1.8 V、VIO = 3.3 V、V<sub>REF</sub> = 5 V、T<sub>A</sub> = 25 °C

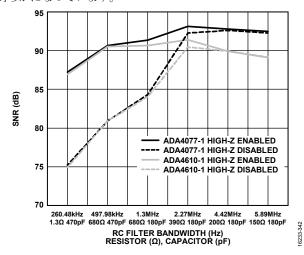

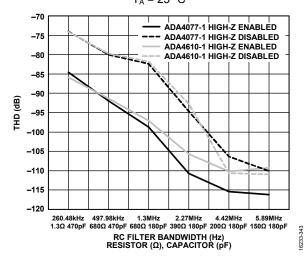

図 43 および図 44 に、ADA4077-1 (アンプ当たりの電源電流  $(I_{SY})$  = 400  $\mu$ A)、ADA4610-1  $(I_{SY}=1.50~\text{mA})$  高精度アンプを使用して、フル・スループット(2 MSPS)で AD4002 を駆動するときにさまざまな RC フィルタ値に対して高インピーダンス・モードが有効の場合と無効の場合の AD4002/AD4006/AD4010 の S/N 比と THD 性能を示します。2.27 MHz RC 帯域幅で高インピーダンスを有効にすると、これらのアンプは93.2 dB と 90.7 dB (代表値)の S/N 比、および -1111~dB と -105~dB (代表値)の THD をそれぞれ実現できます。高インピーダンス・モードを有効にすると、Rの値が大きい場合でも、THD が約 10~dB 向上します。RC フィルタ・カットオフが非常に低い場合でも、S/N 比は 88~dB 付近の値に維持されます。

高インピーダンス・モードを有効にすると、ADC は約2 mW/MSPS の余分な電力を消費しますが、この消費量は ADA4807-1 などの専用のADC ドライバを使用する場合よりも大幅に低くなります。フロント・エンドはシステムの種類に関係なく、シグナル・チェーン全体のAC/DC 性能を制限します。図43 および図44 に記載された高精度アンプのデータシートによると、特定の入力周波数でノイズと歪みの性能がS/N比とTHDの仕様に影響を与えることが明らかになっています。

図 43. 各種の高精度 ADC ドライバの S/N 比 と RC フィルタ帯域幅の関係、 $f_{IN}$  = 1 kHz(ターボ・モードをオン、高インピーダンスを有効/無効)、VDD = 1.8 V、VIO = 3.3 V、 $V_{REF}$  = 5 V、 $T_A$  = 25 °C

図 44. 各種の高精度 ADC ドライバの THD と RC フィルタ帯域幅の関係、 $f_{IN}$  = 1 kHz(ターボ・モードをオン、高インピーダンスを有効/無効)、VDD = 1.8 V、VIO = 3.3 V、 $V_{REF}$  = 5 V、 $T_A$  = 25 °C

Rev. 0 — 22/37 —

#### 長いアクイジション・フェーズ

AD4002/AD4006/AD4010 の変換時間は 290 ns と非常に短いため、アクイジション・フェーズが長くなります。アクイジションは、AD4002/AD4006/AD4010 の主な機能によってさらに延長されます。通常、ADC は変換の終わる 100 ns 前にアクイジション・フェーズに戻ります。この機能により、ADC が新しい入力電圧を取得する時間が長くなります。アクイジション・フェーズが長くなると、駆動アンプのセトリング条件が緩和されるので、消費電力/帯域幅の小さいアンプを選択できます。アクイジション・フェーズが長くなると、RC フィルタ(図 33 および 図 34 の R と Cで表される)のカットオフが低くなります。つまり、ノイズの大きなアンプも許容されます。RC フィルタで大きな R 値とそれに対応する小さな C 値を使用できると、歪みの性能に大きな影響を与えずに、アンプの安定性に関する懸念事項を減らすことができます。R の値が大きくなると、アンプの動的消費電力も減ります。

RC フィルタの設定と適切なアンプの選択の詳細については、表 10 を参照してください。

#### 電圧リファレンス入力

リファレンス入力の性能を最適に発揮するには、10 μF (X7R、0805 サイズ)のセラミック・チップ・コンデンサが適しています。

高性能と低ドリフトを実現するには、ADR4550 などのリファレンスを使用します。ADR3450 などの低消費電力リファレンスを使用できますが、ノイズ性能がわずかに低下します。リファレンスと ADC リファレンス入力の間に ADA4807-1 などのリファレンス・バッファを配置することが推奨されます。リファレンス・バッファの安定性を維持し、このセクションで説明した ADC の最低条件を満たすようコンデンサの最適サイズを考慮することが重要です( $10\,\mu F$  のセラミック・チップ・コンデンサ、 $C_{REF}$ )。

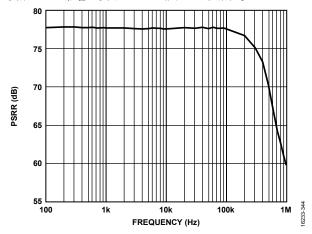

#### 電源

AD4002/AD4006/AD4010 は、コア電源(VDD)とデジタル入出カインターフェース電源 (VIO) の 2 つの電源ピンを使用します。 VIO では、 $1.8\,V\sim5.5\,V$  のあらゆるロジックと直接インターフェースを形成できます。 $1.8\,V$  動作では、システムのロジック・レベルに応じて VIO と VDD を接続することで、電源の数を削減できます。 VDD ピンと VIO ピンに電力を供給するには、ADP7118 の低ノイズ、CMOS、低ドロップアウト(LDO)リニア電圧レギュレータが推奨されます。AD4002/AD4006/AD4010 は、VIO と VDD間の電源シーケンスに依存しません。さらに、AD4002/AD4006/AD4010 は、広い周波数範囲にわたって、電源の変動による影響を受けません(図 45 を参照)。

図 45. PSRR の周波数特性、VDD = 1.8 V、VIO = 3.3 V、 V<sub>REF</sub> = 5 V、T<sub>A</sub> = 25 ° C

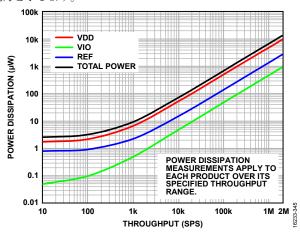

AD4002/AD4006/AD4010 は各変換フェーズの終わりに自動的にパワーダウンします。このため、消費電力はサンプリング・レートに比例します。この機能により、低サンプリング・レートのアプリケーション(秒あたり数サンプルのものを含む)や、バッテリ駆動のアプリケーションに最適なデバイスとなっています。図 46 に、AD4002/AD4006/AD4010 の合計消費電力と各レールの消費電力を示します。

図 46. 消費電力とスループットの関係、VDD = 1.8 V、 VIO = 1.8 V、V<sub>REF</sub> = 5 V、T<sub>A</sub> = 25 °C

## デジタル・インターフェース

AD4002/AD4006/AD4010 は、ピン数が少ないにも関わらず、シリアル・インターフェース・モードで柔軟に対応できます。また、AD4002/AD4006/AD4010 は、設定レジスタへの 16 ビット SPI の書込みでもプログラムできます。

でS モードにおいて、AD4002/AD4006/AD4010 は SPI、QSPI™、MICROWIRE®、デジタル・ホスト、デジタル・シグナル・プロセッサ (DSP) と互換性があります。このモードでは、AD4002/AD4006/AD4010 は3線式または4線式のインターフェースを使用できます。CNV、SCK、SDOの信号を使用する3線式インターフェースは、最小限の配線で機能するので、絶縁アプリケーションなどに便利です。SDI、CNV、SCK、SDOの信号を使用する4線式インターフェースでは、リードバック・タイミングに依存せずにCNVで変換を開始できます(SDI)。このインターフェースは、低ジッタ・サンプリングまたは同時サンプリング・アプリケーションで便利です。

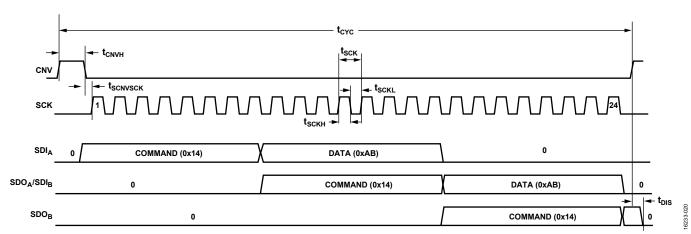

AD4002/AD4006/AD4010 は、シフト・レジスタと同様に、SDI 入力を使用して 1 つのデータ・ラインで複数の ADC をカスケード接続するためのデイジーチェーン機能を備えています。

デバイスの動作モードは、CNV の立上がりエッジが発生したときの CNV レベルによって決定されます。SDI がハイの場合は $\overline{CS}$  モードが選択され、SDI がローの場合はデイジーチェーン・モードが選択されます。SDI と CNV が同時に接続される場合の SDI ホールド時間には、デイジーチェーン・モードが常に選択されます。

AD4002/AD4006/AD4010 を 3 線式または 4 線式のモードで使用する場合、データ・ビットの前にスタート・ビットを強制的に挿入するオプションがあります。このスタート・ビットをビジー信号インジケータとして使用すれば、デジタル・ホストに割り込み、データ読出しをトリガすることができます。ビジー・インジケータとして使用しない場合、リードバック前に最大変換時間をタイムアウトさせる必要があります。

CS モードでは、CNV または SDI がローの場合に ADC 変換が終了すると、ビジー・インジケータ機能が有効になります。

表 11 に示すように、電源投入時の SDO の状態は、CNV および SDI の状態によって、ローまたは高インピーダンスのいずれかになります。

表 11. 電源投入時の SDO の状態

| CNV | SDI | SDO    |

|-----|-----|--------|

| 0   | 0   | Low    |

| 0   | 1   | Low    |

| 1   | 0   | Low    |

| 1   | 1   | High-Z |

AD4002/AD4006/AD4010 は、3 線式モードまたは4 線式モードの両方でターボ・モード機能を備えています。ターボ・モードは、設定レジスタへの書出しによって有効になります。このモードは、ビジー・インジケータ機能を置き換えます。ターボ・モードを使用すると、SPI クロック・レートが遅くなるので、インターフェースがシンプルになります。AD4002 の最大スループットである 2 MSPS は、ターボ・モードを有効にして、75 MHz の最小 SCK レートを使用した場合のみ実現します。

新たな変換が開始される前に変換結果がクロック出力されるように、SCK レートを十分に速くする必要があります。アプリケーションで必要な最低 SCK レートは、サンプル期間(tcvc)、読出しの必要があるビット数(データとオプションのステータス・ビットを含む)、使用するデジタル・インターフェース・モードに基づいて求めることができます。各デジタル・インターフェース・モードのタイミング図と説明については、動作セクションのデジタル・モードで指定します(CS モード、3線式ターボ・モードセクションからデイジーチェーン・モードセクションを参照)。

設定レジスタでステータス・ビットが有効な場合、変換データの 最後でステータス・ビットをクロック出力できます。表 15 に示 すように、合計 6 つのステータス・ビットがあります。

AD4002/AD4006/AD4010 は、目的の設定レジスタへの 16 ビット SPI の書込みによって設定されます。16 ビット・ワードは、CNV がローの間に SDI ラインから書き込めます。16 ビット・ワードは、8 ビットのヘッダーと 8 ビットのレジスタ・データで構成されます。絶縁システムでは、ADuM141D が推奨されます。これにより、AD4002 をフル・スループットの 2 MSPS で動作させるために必要な 75 MHz SCK をサポートできます。

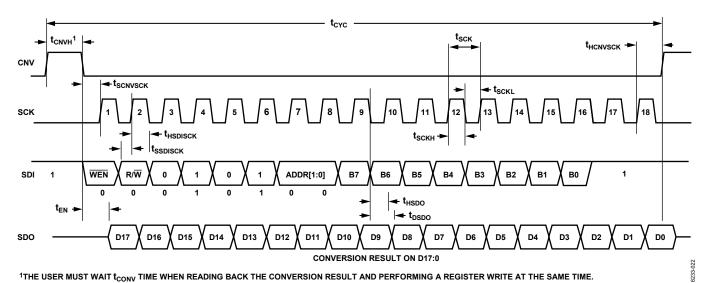

#### レジスタ読出し/書込み機能

AD4002/AD4006/AD4010 レジスタ・ビットはプログラマブルで、デフォルトのステータスは表 12 のようになります。 レジスタ・マップを表 14 に示します。過電圧クランプ・フラグ  $(\overline{OV})$  は、読出し専用のスティッキー・ビットで、過電圧状態が解消された後でレジスタの読出しが実行された場合のみクリアされます。過電圧状態の場合、このフラグは 0 になります。

表 12. レジスタ・ビット

| Register Bits               | Default Status                         |  |  |

|-----------------------------|----------------------------------------|--|--|

| Overvoltage (OV) Clamp Flag | 1 bit, 1 = inactive (default)          |  |  |

| Span Compression            | 1 bit, 0 = disabled (default)          |  |  |

| High-Z Mode                 | 1 bit, $0 = \text{disabled (default)}$ |  |  |

| Turbo Mode                  | 1 bit, $0 = \text{disabled (default)}$ |  |  |

| Enable Six Status Bits      | 1 bit, $0 = \text{disabled (default)}$ |  |  |

レジスタ・マップへのアクセスを開始するには、SPI インターフェース・ブロックの8 ビット・コマンド・レジスタへの書込みを実行する必要があります。AD4002/AD4006/AD4010 は、最初の 0 がクロック入力されるまですべての1を無視します。コマンド・レジスタにロードされる値は常に0で、これに7つのコマンド・ビットが続きます。このコマンドによって、動作が書込みか読出しかどうか決定されます。AD4002/AD4006/AD4010 のコマンド・レジスタは、表13 のようになります。

表 13. コマンド・レジスタ

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| WEN   | R/W   | 0     | 1     | 0     | 1     | 0     | 0     |

レジスタの読出し/書込みはすべて、CNV がローの間に発生します。SDIのデータは、SCK の立上がりエッジでクロック入力されます。SDOのデータは SCK の立下がりエッジでクロック出力されます。デイジーチェーン・モードが有効でない場合、データ転送の最後に、CNVの立上がりエッジで SDO は高インピーダンス状態になります。デイジーチェーン・モードが有効な場合、CNV の立上がりエッジで SDO はローになります。デイジーチェーン・モードでは、レジスタの読出しを実行できません。

レジスタの読出しには、SCK、CNV、SDIの3つの信号ラインが必要です。レジスタへの書込み中にSDOの現在の変換結果の読出しを実行するには、変換を完了した後にCNVピンをローにする必要があります。そうしないと、間違った変換結果がSDOに出力される可能性があります。ただし、レジスタの書込みはCNVピンの状態に関係なく発生します。

16 ビット変換データの読出しは 16 ビット SPI フレームに制限される可能性があるので、各設定レジスタの LSB は予約済みになります。SDI フレームの最終ビットでの SDI の状態は、CNV の立上がりで持続する場合があります。インターフェース・モードの一部は、CNV の立上がり発生時の SDI の状態によって設定されるので、このシナリオでは、最終的な SDI の状態を設定する必要があります。

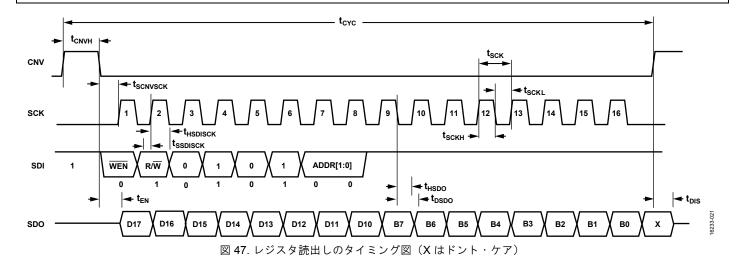

図  $47 \sim 図 49$  のタイミング図に、レジスタの読出し、書出し、デイジーチェーン・モードで AD4002/AD4006/AD4010 を構成する場合にデータの読出し/書出しを実行する方法を示します。

表 14. レジスタ・マップ

| ADDR[1:0] | Bit 7    | Bit 6    | Bit 5    | Bit 4       | Bit 3       | Bit 2       | Bit 1 | Bit 0                       | Reset |

|-----------|----------|----------|----------|-------------|-------------|-------------|-------|-----------------------------|-------|

| 0x0       | Reserved | Reserved | Reserved | Enable six  | Span        | High-Z mode | Turbo | Overvoltage (OV) clamp      | 0xE1  |

|           |          |          |          | status bits | compression |             | mode  | flag (read only sticky bit) |       |

図 48. レジスタ書込みのタイミング図

図 49. レジスタ書込みのタイミング図、デイジーチェーン・モード

Rev. 0

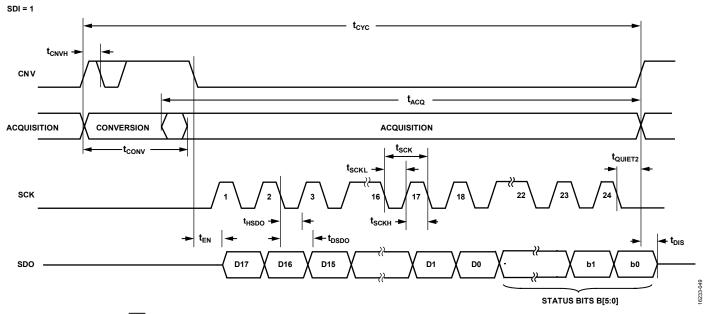

#### ステータス・ワード

変換結果の最後に6ビットのステータス・ワードを追加できます。これらのビットのデフォルト状態は、表 15で示されます。レジスタ設定でステータス・ビットを有効にする必要があります。過電圧クランプ・フラグ  $(\overline{OV})$  が 0 の場合、過電圧状態が発生しています。過電圧クランプ・フラグのステータス・ビットは、変換ごとに更新されます。

SDO ラインは、6番目のステータス・ビットがクロック出力された後に高インピーダンスになります(デイジーチェーン・モードを除く)。次の変換を開始するため、すべてのステータスをクロック出力する必要はありません。 $\overline{\text{CS}}$  モード、ビジー・インジケータなしの3線式シリアル・インターフェース(ステータス・ビットを含む)のタイミング図を図50に示します。

表 15. ステータス・ビット (デフォルト条件)

| Bit 5                       | Bit 4            | Bit 3       | Bit 2      | Bit 1    | Bit 0    |

|-----------------------------|------------------|-------------|------------|----------|----------|

| Overvoltage (OV) clamp flag | Span compression | High-Z mode | Turbo mode | Reserved | Reserved |

図 50.  $\overline{\text{CS}}$  モード、ビジー・インジケータなしの 3 線式シリアル・インターフェースのタイミング図、ステータス・ビットを含む(SDI ハイ)

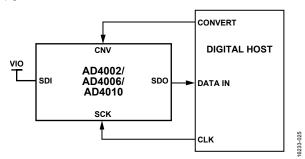

## CS モード、3 線式ターボ・モード

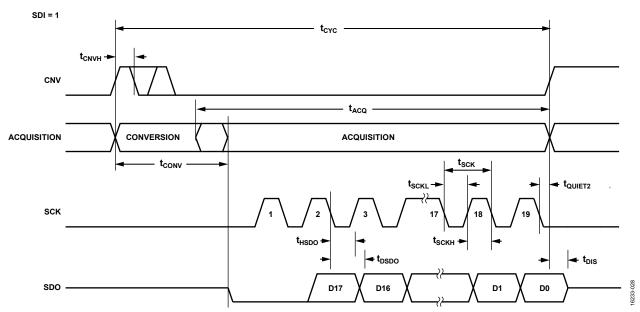

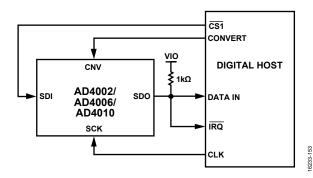

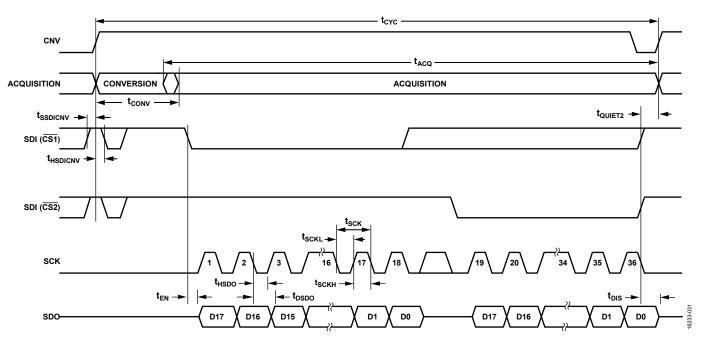

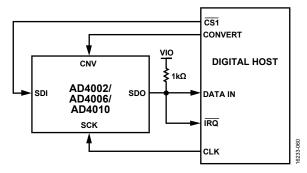

通常、このモードは、1 台の AD4002/AD4006/AD4010 デバイスを SPI 互換デジタル・ホストに接続する場合に使用されます。前回 の変換結果をクロック出力する ADC 変換プロセスの最後に時間 が追加されるので、SCK レートが遅くなります。AD4002 では、ターボ・モードを有効にして、75 MHz の最小 SCK レートを使用 した場合のみ、2 MSPS のスループット・レートを実現できます。 また、ターボ・モードを有効にすると、AD4006 では 25 MHz の最小 SCK レートで 1 MSPS を達成でき、AD4010 では 11 MHz の最小 SCK レートで 500 kSPS の最大スループット・レートを達成 できます。接続図を 図 51 に示します。対応するタイミング図は 図 52 に示します。

ターボ・モードのビット1をプログラムすることで、ビジー・インジケータ付きの3線式モードがターボ・モードに変わります(表14を参照)。

SDI が強制的にハイになると、CNV の立上がりエッジで変換が開始されます。前回の変換データは、CNV の立上がりエッジ後の読出しで使用できます。CNV がハイになった後、CNV がローになる前に、前回の変換結果をクロック出力するには、tquieti 時間だけ待機する必要があります。また、CNV がハイの場合、SCKの最後の立下がりエッジの後、tquieti 時間だけ待機する必要があります。

変換が完了すると、AD4002/AD4006/AD4010 はアクイジション・フェーズに移行し、パワーダウンします。CNV がローになると、MSB が SDO に出力されます。残りのデータ・ビットは、後続のSCK の立下がりエッジで記録されます。両方の SCK エッジでデータは有効です。立上がりエッジでデータをキャプチャできますが、SCK の立下がりエッジを使用するデジタル・ホストでは、ホールド時間を許容できれば読出しレートが速くなります。18 番目の SCK の立下がりエッジの発生後または CNV がハイになった後(どちらか先に発生した方)、SDO は高インピーダンス状態に戻ります。

図 51.  $\overline{\text{CS}}$  モード、3 線式ターボ・モードの接続図(SDI はハイ)

図 52. CS モード、3 線式ターボ・モードのシリアル・インターフェースのタイミング図(SDI はハイ)

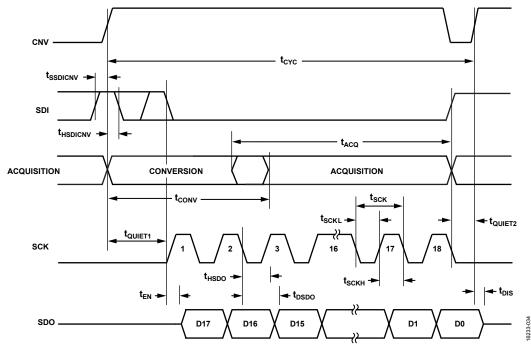

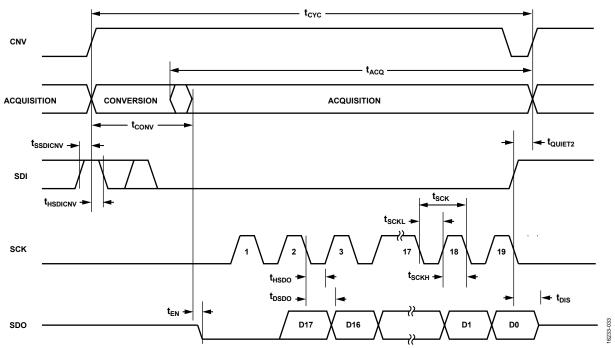

#### CS モード、3 線式、ビジー・インジケータなし

通常、このモードは、1台の AD4002/AD4006/AD4010 デバイスを SPI 互換デジタル・ホストに接続する場合に使用されます。

接続図を 図 53 に示します。対応するタイミング図は 図 54 に示します。

SDIを VIO に接続すると、CNV の立上がりエッジで変換が開始され、CS モードが選択され、SDO が強制的に高インピーダンスに移行します。変換を開始すると、CNV の状態に関係なく、変換が完了するまで続行されます。この機能は、CNV をローにして、アナログ・マルチプレクサなどの SPI デバイスを選択する場合に便利です。ただし、ビジー信号インジケータの生成を防ぐため、最小変換時間が経過する前に CNV をハイに戻し、最大変換時間にわたりハイに保つ必要があります。

変換が完了すると、AD4002/AD4006/AD4010 はアクイジション・フェーズに移行し、パワーダウンします。CNV がローになると、MSB が SDO に出力されます。残りのデータ・ビットは、後続のSCK の立下がりエッジで記録されます。両方の SCK エッジでデータは有効です。立上がりエッジでデータをキャプチャできますが、SCK の立下がりエッジを使用するデジタル・ホストでは、ホールド時間を許容できれば読出しレートが速くなります。18 番目の SCK の立下がりエッジの発生後または CNV がハイになった後(どちらか先に発生した方)、SDO は高インピーダンス状態に戻ります。

変換中に SCK のデジタル動作が発生しないようにします。

図 53. CS モード、3 線式 (ビジー・インジケータなし) の接続図 (SDI はハイ)

図 54.  $\overline{\text{CS}}$  モード、3 線式シリアル・インターフェース(ビジー・インジケータなし)のタイミング図(SDI ハイ)

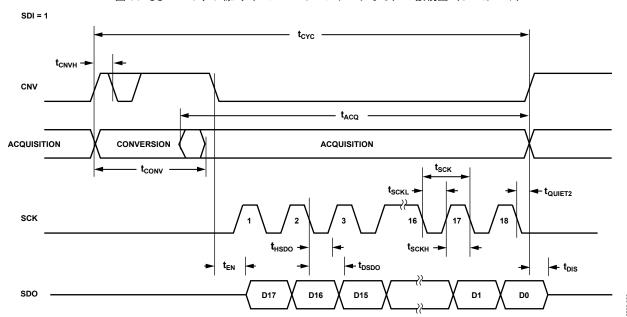

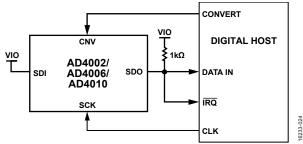

#### CS モード、3 線式、ビジー・インジケータあり

通常、このモードは、割込み入力を備えた SPI 互換のデジタル・ホストに 1 台の AD4002/AD4006/ AD4010 デバイスを接続する場合に使用されます  $(\overline{IRQ})$ 。

接続図を 図 55 に示します。対応するタイミング図は 図 56 に示します。

SDI を VIO に接続すると、CNV の立上がりエッジで変換が開始され、 $\overline{CS}$  モードが選択され、SDO が強制的に高インピーダンスに移行します。SDO は CNV の状態に関係なく、変換が完了するまで高インピーダンス状態に保たれます。最小変換時間が経過する前に、CNV でアナログ・マルチプレクサなどの SPI デバイスを選択できます。ただし、ビジー信号インジケータが確実に生成されるように、最小変換時間が経過する前に CNV をローに戻し、最大変換時間にわたりローに保つ必要があります。

変換が完了すると、SDO は高インピーダンスから低インピーダンスになります。SDO ラインの  $1\,\mathrm{k}\Omega$  のプルアップ抵抗とこの遷移を組み合わせて、割込み信号として使用すれば、デジタル・ホスト

によって制御されるデータ読出しを開始できます。その後、AD4002/AD4006/AD4010 はアクイジション・フェーズに移行し、パワーダウンします。後続の SCK の立下がりエッジで、データ・ビットが MSB ファーストでクロック出力されます。両方の SCK エッジでデータは有効です。立上がりエッジでデータをキャプチャできますが、SCK の立下がりエッジを使用するデジタル・ホストでは、ホールド時間を許容できれば読出しレートが速くなります。オプションの 19番目の SCK の立下がりエッジ発生後またはSDI がハイになった後(どちらか先に発生した方)、SDO は高インピーダンスに戻ります。

複数の AD4002/AD4006/AD4010 デバイスを同時に選択すると、SDO 出力ピンは、損傷や誘導ラッチアップなしでこの競合を処理します。ただし、余分な消費電力を制限するために、この競合は可能な限り短くすることが推奨されます。

変換中に SCK のデジタル動作が発生しないようにします。

図 55.  $\overline{CS}$  モード、3 線式 (ビジー・インジケータあり) の接続図 (SDI はハイ)

図 56. CS モード、3 線式シリアル・インターフェース(ビジー・インジケータあり)のタイミング図(SDI はハイ)

## <del>CS</del> モード、4 線式ターボ・モード

通常、このモードは、1台の AD4002/AD4006/AD4010 デバイスを SPI 互換デジタル・ホストに接続する場合に使用されます。前回 の変換結果をクロック出力する ADC 変換プロセスの最後に追加 の時間が消費されるので、SCK レートが遅くなります。AD4002 では、ターボ・モードを有効にして、75 MHz の最小 SCK レートを使用した場合のみ、2 MSPS のスループット・レートを実現できます。また、ターボ・モードを有効にすると、AD4006 では 25 MHz の最小 SCK レートで 1 MSPS を達成でき、AD4010 では 11 MHz の最小 SCK レートで 500 kSPS の最大スループット・レートを達成できます。

接続図を 図 57 に示します。対応するタイミング図は 図 58 に示します。

ターボ・モードのビット1をプログラムすることで、ビジー・インジケータ付きの 4 線式モードがターボ・モードに変わります(表14を参照)。

SDI がハイの場合、CNV の立上がりエッジで変換が開始されます。前回の変換データは、CNV の立上がりエッジ後の読出しで使用できます。CNV がハイになった後、SDI がローになる前に、前回の変換結果をクロック出力するため、tquieti 時間だけ待機する必要があります。また、CNV がハイの場合、SCK の最後の立下がりエッジの後、tquieti 時間だけ待機する必要があります。

変換が完了すると、AD4002/AD4006/AD4010 はアクイジション・フェーズに移行し、パワーダウンします。SDI 入力をローにすると、ADC 結果の読出しを実行できます。その結果、MSB が SDO に出力されます。残りのデータ・ビットは、後続の SCK の立下がりエッジで記録されます。両方の SCK エッジでデータは有効です。立上がりエッジでデータをキャプチャできますが、SCK の立下がりエッジを使用するデジタル・ホストでは、ホールド時間を許容できれば読出しレートが速くなります。18番目の SCK の立下がりエッジの発生後または SDI がハイになった後(どちらか最初に発生した方)、SDO は高インピーダンスに戻ります。

図 57. CS モード、4 線式ターボ・モードの接続図

図 58. CS モード、4 線式ターボ・モードのタイミング図

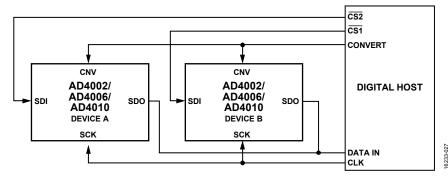

## CS モード、4 線式、ビジー・インジケータなし

通常、このモードは、複数の AD4002/AD4006/AD4010 デバイスを SPI 互換のデジタル・ホストに接続する場合に使用されます。

2 台の AD4002/AD4006/AD4010 デバイスを使用する接続図の例を 図 59 に示します。対応するタイミング図は 図 60 に示します。

SDI がハイの場合、CNV の立上がりエッジで変換が開始され、CS モードが選択され、SDO が強制的に高インピーダンスに移行します。このモードでは、変換フェーズと後続のデータ・リードバックの間、CNV をハイに保つ必要があります。SDI と CNV がローの場合、SDO はローになります。最小変換時間の前に、SDI でアナログ・マルチプレクサなどの SPI デバイスを選択できます。ただし、ビジー信号インジケータの生成を防ぐため、最小変換時

間が経過する前に SDI をハイに戻し、最大変換時間にわたりハイに保つ必要があります。

変換が完了すると、AD4002/AD4006/AD4010 はアクイジション・フェーズに移行し、パワーダウンします。SDI 入力をローにすると、ADC 結果の読出しを実行できます。その後、MSB が SDO に出力されます。残りのデータ・ビットは、後続の SCK の立下がりエッジで記録されます。両方の SCK エッジでデータは有効です。立上がりエッジでデータをキャプチャできますが、SCK の立下がりエッジを使用するデジタル・ホストでは、ホールド時間を許容できれば読出しレートが速くなります。18番目の SCK の立下がりエッジの発生後または CNV がハイになった後(どちらか最初に発生した方)、SDO は高インピーダンスに戻り、別のAD4002/AD4006/AD4010 の読出しを実行できます。

図 59. CS モード、4 線式 (ビジー・インジケータなし) の接続図

図  $60.\overline{\text{CS}}$  モード、4 線式シリアル・インターフェース(ビジー・インジケータなし)のタイミング図

## CS モード、4 線式、ビジー・インジケータあり

通常、このモードは、割込み入力( $\overline{IRQ}$ )を使用して SPI 互換の デジタル・ホストに 1 台の AD4002/AD4006/AD4010 デバイスを 接続し、データの読出しに使用される信号に関係なく、CNV を 維持してアナログ入力をサンプリングする場合に使用されます。この独立性は、CNV で低ジッタが必要なアプリケーションで特に重要になります。

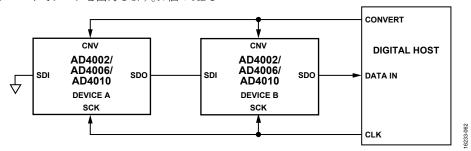

接続図を 図 61 に示します。対応するタイミング図は 図 62 に示します。