#

### DAC制御ブースト/インバータ LCDバイアス電源、内部スイッチ付

概要

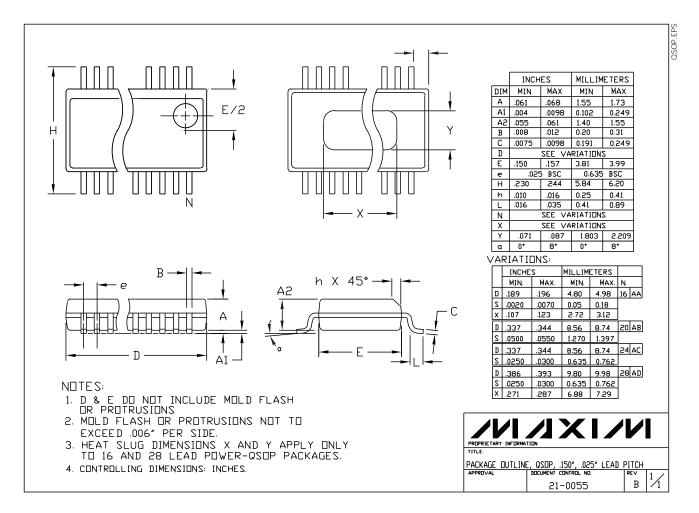

MAX686は、正入力電圧を+27.5V又は-27.5Vまでの 負LCDバイアス電圧に変換するDAC制御ブースト/イン バータICです。このデバイスは内部NチャネルMOSFET スイッチ、プログラマブル電流制限及び出力電圧の ディジタル調整用6ビットDACを包含し、小型16ピン QSOPパッケージ(8ピンSOPパッケージと同サイズ)で 提供されています。

MAX686は広範囲の負荷で高い効率を提供するために、 電流制限パルス周波数変調(PFM)制御を使用していま す。スイッチング周波数は高くなっているため(300kHz まで)、小型の外部コンポーネントも利用できます。

ディスプレイロジック電圧を排除すると、LCDON出力 によってLCDバイアス電圧が自動的にディセーブルさ れ、ディスプレイが保護されるようになっています。 MAX686のIC用入力電圧範囲は+2.7V~+5.5V、イン ダクタ用の入力電圧範囲は+0.8V~+27.5Vです。自己 消費電流は65µA(typ)、シャットダウン電流は1.5µAと なっています。

MAX686は省スペース、消費電力の低減及びバッテリ 寿命の延長を目的として高集積化されているため、 バッテリ駆動の携帯機器用に最適です。MAX629は MAX686と同じ機能を提供しますが、DACは組み込ま れていません。これらのデバイスには、設計を容易に するための評価キットも用意されています。

#### アプリケーション

正又は負LCDバイアス

パーソナルディジタルアシスタント

ノートブックコンピュータ

ポータブルデータ収集ターミナル

パームトップコンピュータ

バラクタチューニングダイオードバイアス

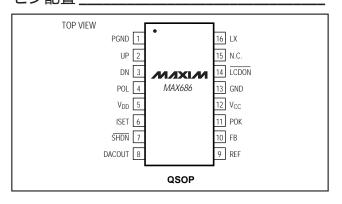

#### ピン配置

特長

◆ 内部500mA、28V Nチャネルスイッチ (外部FET不要)

◆ 出力電圧: +27.5V~-27.5Vの範囲で調整可能

◆ 6ビットDAC制御出力電圧

◆ 効率: 最高90%

◆ パッケージ:小型16ピンQSOPパッケージ (8ピンSOPと同サイズ)

◆ パワーOKインジケータ

◆ 自己消費電流:65µA

◆ シャットダウン電流: 1.5µA

◆ スイッチング周波数:最高300kHz

#### 型番

| PART      | TEMP. RANGE    | PIN-PACKAGE |

|-----------|----------------|-------------|

| MAX686C/D | 0°C to +70°C   | Dice*       |

| MAX686EEE | -40°C to +85°C | 16 QSOP     |

<sup>\*</sup>Dice are specified at  $T_A = +25$ °C, DC parameters only.

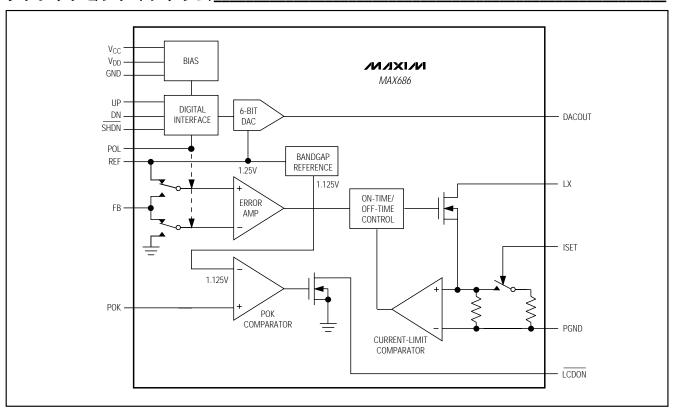

ファンクションダイアグラムは、データシートの最後に記載 されています。

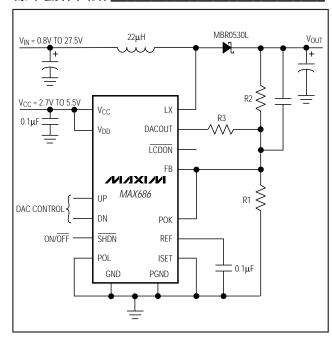

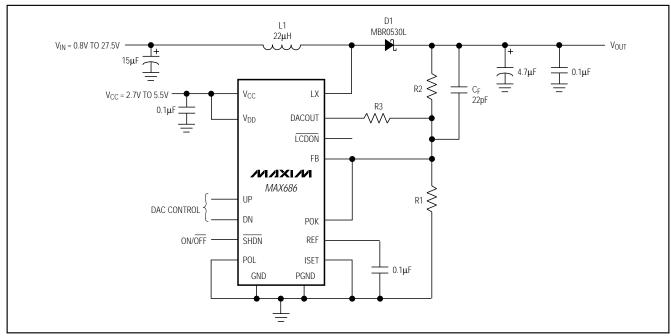

#### 標準動作回路

#### **ABSOLUTE MAXIMUM RATINGS**

| Voltage                                 |                      |

|-----------------------------------------|----------------------|

| V <sub>CC</sub> , ISET, POK, POL, SHDN, |                      |

| UP, DN, V <sub>DD</sub> to GND          | 0.3V to +6V          |

| FB, REF, DACOUT to GND                  | 0.3V to (Vcc + 0.3V) |

| PGND to GND                             | 0.3V to +0.3V        |

| LX, LCDON to GND                        | 0.3V to +30V         |

| Current                                 |                      |

| LX (sinking)                            | 600mA                |

| LCDON (sinking)                         |                      |

| Continuous Power Dissipation ( $T_A = +70$ °C) |                |

|------------------------------------------------|----------------|

| QSOP (derate 8.30mW/°C above +70°C)            | 667mW          |

| Operating Temperature Ranges                   |                |

| MAX686C/D                                      | 0°C to +70°C   |

| MAX686EEE                                      | 40°C to +85°C  |

| Storage Temperature Range                      | 65°C to +160°C |

| Lead Temperature (soldering, 10sec)            | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = V_{DD} = V_{IN} = +5V, C_{REF} = 0.1\mu F, T_A = 0^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                          | SYMBOL                            | CONDITIONS                                                                                   | MIN  | TYP  | MAX  | UNITS |

|----------------------------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------|------|------|------|-------|

| Supply Voltage (Note 1)                            | V <sub>CC</sub> , V <sub>DD</sub> |                                                                                              | 2.7  |      | 5.5  | V     |

| Input Voltage                                      | VIN                               | Voltage applied to L1                                                                        | 0.8  |      | Vout | V     |

| Supply Current                                     | ICC + IDD                         | POL = GND, V <sub>FB</sub> = 1.3V, IDACOUT = 0mA                                             |      | 65   | 125  | μΑ    |

| Shutdown Current                                   | ISHDN                             | SHDN = GND                                                                                   |      | 1.3  | 4    | μΑ    |

| V <sub>CC</sub> Undervoltage Lockout               | VLOCK                             | Rising or falling                                                                            | 2.10 | 2.5  | 2.65 | V     |

| V <sub>CC</sub> Undervoltage Lockout<br>Hysteresis |                                   |                                                                                              |      | 100  |      | mV    |

| V <sub>CC</sub> DAC Reset Threshold                | VRESET                            |                                                                                              | 0.5  | 1.5  | 2.1  | V     |

| Line Regulation                                    |                                   | Boost configuration, $V_{OUT} = 27.5V$ , $I_{LOAD} = 5mA$ , $V_{CC} = V_{DD} = 2.7V$ to 5.5V |      | 0.1  |      | %/V   |

| Load Regulation                                    |                                   | Boost configuration, V <sub>OUT</sub> = 27.5V,<br>I <sub>LOAD</sub> = 0mA to 5mA             |      | 0.01 |      | %/mA  |

| LX                                                 | •                                 |                                                                                              |      |      |      |       |

| LX Voltage Range                                   | VLX                               |                                                                                              |      |      | 28   | V     |

| LX Switch Current Limit                            | I <sub>LX</sub>                   | ISET = V <sub>CC</sub>                                                                       | 0.42 | 0.50 | 0.58 | A     |

| EX SWITCH CUITERIT LITTIL                          |                                   | ISET = GND                                                                                   | 0.21 | 0.25 | 0.29 |       |

| LX On-Resistance                                   | R <sub>L</sub> X                  | $V_{CC} = V_{DD} = 5V$ , $I_{LX} = 100$ mA                                                   |      | 0.6  | 1.2  | Ω     |

| LA OII-RESISIANCE                                  |                                   | $V_{CC} = V_{DD} = 3.3V$ , $I_{LX} = 100mA$                                                  |      | 0.8  | 1.6  |       |

| LX Leakage Current                                 | ILXLEAK                           | $V_{LX} = 28V$                                                                               |      |      | 1.5  | μΑ    |

| Maximum LX On-Time                                 | ton                               |                                                                                              | 8    | 10   | 12   | μs    |

| Minimum I X Off-Time                               | Off Time o                        | POL = GND, V <sub>FB</sub> > 1.2V                                                            | 0.8  | 1    | 1.2  | 116   |

|                                                    |                                   | POL = V <sub>CC</sub> , V <sub>FB</sub> < 0.15V                                              | 2.8  | 3.5  | 4.2  |       |

| IVIII III LA OII-TIITIE                            | tOFF                              | POL = GND, V <sub>FB</sub> < 0.8V                                                            | 4    | 5    | 6    | μs    |

|                                                    |                                   | POL = V <sub>CC</sub> , V <sub>FB</sub> > 0.4V                                               | 4    | 5    | 6    |       |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = V_{DD} = V_{IN} = +5V, C_{REF} = 0.1 \mu F, T_A = 0 ^{\circ}C$  to  $+85 ^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25 ^{\circ}C$ .)

| PARAMETER                     | SYMBOL            | CONDITIONS                                                | MIN                      | TYP              | MAX                      | UNITS |

|-------------------------------|-------------------|-----------------------------------------------------------|--------------------------|------------------|--------------------------|-------|

| REFERENCE AND FB INPUT        | J.                |                                                           |                          |                  |                          |       |

| REF Output Voltage            | V <sub>REF</sub>  | $V_{CC} = V_{DD} = 2.7V$ to 5.5V, no load                 | 1.225                    | 1.250            | 1.275                    | V     |

| DEE Land Danielakan           |                   | I <sub>REF</sub> = 0μA to 25μA, C <sub>REF</sub> = 0.1μF  |                          | 1                | 10                       | \/    |

| REF Load Regulation           |                   | I <sub>REF</sub> = 0μA to 50μA, C <sub>REF</sub> = 0.47μF |                          | 1.5              |                          | mV    |

| FB Set Point                  | \/                | POL = GND                                                 | 1.225                    | 1.250            | 1.275                    | V     |

| FB Set Foldt                  | V <sub>FB</sub>   | POL = V <sub>CC</sub>                                     | -15                      | 0                | 15                       | mV    |

| FB Input Bias Current         | IFB               |                                                           |                          |                  | ±50                      | nA    |

| POWER OK COMPARATOR, LC       | DON OUTPU         | T                                                         | '                        |                  |                          |       |

| POK Threshold                 | Vpok              | V <sub>POK</sub> rising                                   | 1.100                    | 1.125            | 1.150                    | V     |

| POK Input Current             | IPOK              |                                                           |                          |                  | ±50                      | nA    |

| POK Hysteresis                |                   |                                                           |                          | 12               |                          | mV    |

| LCDON Sink Current            | ICDON             | $V_{\overline{LCDON}} = 0.4V, V_{POK} = 1.25V$            | 2                        | 6                |                          | mA    |

| LCDON Leakage Current         |                   | V <del>LCDON</del> = 28V, V <sub>POK</sub> = GND          |                          | 0.02             | 1                        | μΑ    |

| DAC OUTPUT (Notes 2, 3)       |                   |                                                           |                          |                  |                          |       |

| Full-Scale Output Voltage     | V <sub>FS</sub>   | -50μA < I <sub>DACOUT</sub> < 0μA                         | V <sub>REF</sub> - 0.015 | V <sub>REF</sub> | V <sub>REF</sub> + 0.015 | V     |

| Zero-Scale Output Voltage     | Vzs               | 0μA < IDACOUT < 20μA                                      | 0                        |                  | 15                       | mV    |

| Resolution                    |                   |                                                           | 6                        |                  |                          | bits  |

| Mid-Scale Accuracy            | MSA               | Mid-scale = V <sub>REF</sub> x 32/63                      | -2                       |                  | 2                        | %     |

| Differential Nonlinearity     | DNL               | Guaranteed monotonic                                      | -1                       |                  | 1                        | LSB   |

| Output Resistance in Shutdown | RDACOUT           |                                                           |                          | 1.5              |                          | kΩ    |

| LOGIC INPUTS: POL, ISET, UP,  | DN, SHDN          |                                                           |                          |                  |                          |       |

| Input Low Level               | V <sub>IL</sub>   | $2.7V < V_{CC} = V_{DD} < 5.5V$                           |                          |                  | 0.7                      | V     |

| Input High Level              | VIH               | $2.7V < V_{CC} = V_{DD} < 5.5V$                           | 2.4                      |                  |                          | V     |

| Input Bias Current            | I <sub>BIAS</sub> |                                                           |                          |                  | ±1                       | μΑ    |

| Pulse Width High              | tpwH              | UP, DN, T <sub>A</sub> = +25°C                            | 1                        |                  |                          | μs    |

| Pulse Width Low               | tpwL              | UP, DN, T <sub>A</sub> = +25°C                            | 1                        |                  |                          | μs    |

| Pulse Separation              | tpws              | UP, DN, T <sub>A</sub> = +25°C                            | 1                        |                  |                          | μs    |

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = V_{DD} = V_{IN} = +5V, C_{REF} = 0.1 \mu F, T_A = -40 ^{\circ} C$  to  $+85 ^{\circ} C$ , unless otherwise noted.) (Note 4)

| PARAMETER                            | SYMBOL            | CONDITIONS                                              | MIN                     | TYP | MAX                     | UNITS |  |

|--------------------------------------|-------------------|---------------------------------------------------------|-------------------------|-----|-------------------------|-------|--|

| Supply Voltage (Note 1)              | VCC, VDD          |                                                         | 2.7                     |     | 5.5                     | V     |  |

| Input Voltage                        | VIN               | Voltage applied to L1                                   | 0.8                     |     | Vout                    | V     |  |

| Supply Current                       | ICC + IDD         | POL = GND, VFB = 1.3V, I <sub>DACOUT</sub> = 0mA        |                         |     | 125                     | μΑ    |  |

| Shutdown Current                     | ISHDN             | SHDN = GND                                              |                         |     | 4                       | μΑ    |  |

| V <sub>CC</sub> Undervoltage Lockout | VLOCK             | Rising or falling                                       | 2.10                    |     | 2.65                    | V     |  |

| LX                                   |                   |                                                         |                         |     |                         |       |  |

| LX Voltage Range                     | V <sub>L</sub> X  |                                                         |                         |     | 28                      | V     |  |

| LX Switch Current Limit              | Live              | ISET = Vcc                                              | 0.4                     |     | 0.6                     | Α     |  |

| LX SWITCH CUITER LITTE               | I <sub>L</sub> X  | ISET = GND                                              | 0.2                     |     | 0.3                     | А     |  |

| LX On-Resistance                     | RLX               | $V_{CC} = V_{DD} = 5V$ , $I_{LX} = 100$ mA              |                         |     | 1.2                     | Ω     |  |

| _A On-Resistance                     | KLX               | $V_{CC} = V_{DD} = 3.3V$ , $I_{LX} = 100mA$             |                         |     | 1.6                     |       |  |

| LX Leakage Current                   | ILXLEAK           | V <sub>L</sub> X = 28V                                  |                         |     | 1.5                     | μΑ    |  |

| Maximum LX On-Time                   | ton               |                                                         | 7.5                     |     | 12.5                    | μs    |  |

|                                      |                   | POL = GND, V <sub>FB</sub> > 1.2V                       | 0.7                     |     | 1.3                     |       |  |

| Minimum LX Off-Time                  | toff              | POL = VCC, VFB < 0.15V                                  | 2.8                     |     | 4.2                     | μs    |  |

| MINIMUM LA ON-TIME                   | IOFF              | POL = GND, V <sub>FB</sub> < 0.8V                       | 3.8                     |     | 6.2                     |       |  |

|                                      |                   | POL = V <sub>CC</sub> , V <sub>FB</sub> > 0.4V          | 3.8                     |     | 6.2                     |       |  |

| REFERENCE AND FB INPUT               |                   |                                                         |                         |     |                         |       |  |

| REF Output Voltage                   | VREF              | VCC = VDD = 2.7V to 5.5V, no load                       | 1.22                    |     | 1.28                    | V     |  |

| REF Load Regulation                  |                   | $I_{REF} = 0\mu A$ to 25 $\mu A$ , $C_{REF} = 0.1\mu F$ |                         |     | 10                      | mV    |  |

| FB Set Point                         | VFB               | POL = GND                                               | 1.22                    |     | 1.28                    | V     |  |

| I D Set I OIIIt                      | VFB VFB           | POL = VCC                                               | -15                     |     | 15                      | mV    |  |

| FB Input Bias Current                | IFB               |                                                         |                         |     | ±50                     | nA    |  |

| POWER OK COMPARATOR, I               | CDON OUTPU        | Т                                                       |                         |     |                         |       |  |

| POK Threshold                        | V <sub>POK</sub>  | V <sub>POK</sub> rising                                 | 1.05                    |     | 1.20                    | V     |  |

| POK Input Current                    | IPOK              |                                                         |                         |     | ±50                     | nA    |  |

| LCDON Sink Current                   | ILCDON            | $V_{\overline{LCDON}} = 0.4V$ , $V_{POK} = 1.25V$       | 2                       |     |                         | mA    |  |

| DAC OUTPUT (Notes 2, 3)              |                   |                                                         |                         |     |                         |       |  |

| Full-Scale Output Voltage            | VFS               | -50μA < IDACOUT < 0μA                                   | V <sub>REF</sub> - 0.02 |     | V <sub>REF</sub> + 0.02 | V     |  |

| Zero-Scale Output Voltage            | Vzs               | 0μA < I <sub>DACOUT</sub> < 20μA                        | 0                       |     | 15                      | mV    |  |

| Resolution                           |                   |                                                         | 6                       |     |                         | Bits  |  |

| Mid-Scale Accuracy                   | MSA               | Mid-scale = V <sub>REF</sub> x 32/63                    | -3                      |     | 3                       | %     |  |

| OGIC INPUTS: POL, ISET, U            | P, DN, SHDN       | •                                                       | •                       |     |                         |       |  |

| Input Low Level                      | VIL               | $2.7V < V_{CC} = V_{DD} < 5.5V$                         |                         |     | 0.7                     | V     |  |

| Input High Level                     | VIH               | $2.7V < V_{CC} = V_{DD} < 5.5V$                         | 2.4                     |     |                         | V     |  |

| Input Bias Current                   | I <sub>BIAS</sub> |                                                         |                         |     | ±1                      | μΑ    |  |

Note 1: The MAX686 requires a supply voltage at V<sub>CC</sub> = V<sub>DD</sub> between +2.7V and +5.5V; however, the voltage that supplies the inductor can vary from +0.8V to +27.5V, depending on circuit operating conditions.

**Note 2:** The DAC output is set to its midpoint value at power-on.

Note 3: The DAC setting is guaranteed to remain valid as long as V<sub>CC</sub> is greater than the V<sub>CC</sub> DAC Reset Threshold.

**Note 4:** Specifications to -40°C are guaranteed by design, not production tested.

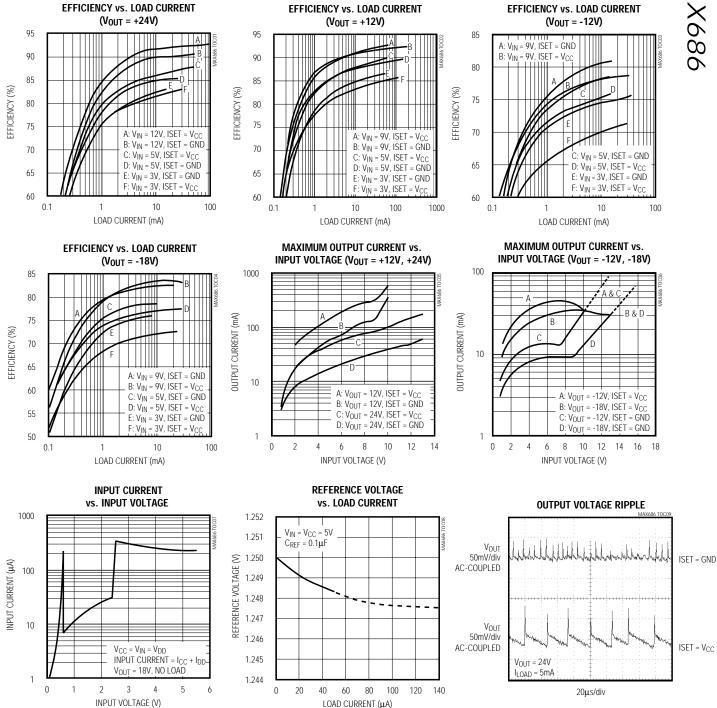

#### 標準動作特性

(Circuits of Figures 1 and 2, V<sub>CC</sub> = V<sub>DD</sub> = V<sub>IN</sub> = +5V, L1 = 22µH, SHDN = V<sub>CC</sub>, C<sub>REF</sub> = 0.1µF, T<sub>A</sub> = +25°C, unless otherwise noted.)

標準動作特性(続き)\_\_

(Circuits of Figures 1 and 2,  $V_{CC} = V_{DD} = V_{IN} = +5V$ ,  $L1 = 22\mu H$ ,  $\overline{SHDN} = V_{CC}$ ,  $C_{REF} = 0.1\mu F$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

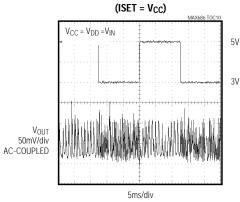

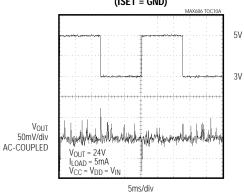

### LINE-TRANSIENT RESPONSE

#### LINE-TRANSIENT RESPONSE (ISET = GND)

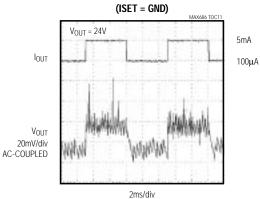

### LOAD-TRANSIENT RESPONSE

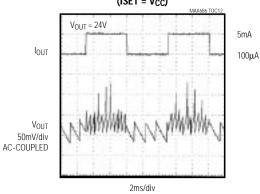

#### LOAD-TRANSIENT RESPONSE (ISET = V<sub>CC</sub>)

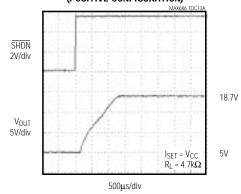

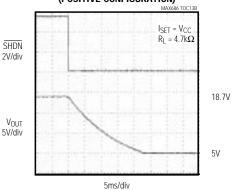

### POWER-UP RESPONSE (POSITIVE CONFIGURATION)

### POWER-DOWN RESPONSE (POSITIVE CONFIGURATION)

### 標準動作特性(続き)\_

(Circuits of Figures 1 and 2,  $V_{CC} = V_{DD} = V_{IN} = +5V$ ,  $L1 = 22\mu H$ ,  $\overline{SHDN} = V_{CC}$ ,  $C_{REF} = 0.1\mu F$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

20ms/div

### 端子説明

| 端子 | 名称              | 機能                                                                                                                                    |

|----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 1  | PGND            | パワーグランド。GNDに接続してください。                                                                                                                 |

| 2  | UP              | インクリメント出力電圧入力。¦V <sub>OUT</sub> ¦が増加するように、各立上りエッジでDACをステップアップします。                                                                     |

| 3  | DN              | デクリメント出力電圧入力。¦V <sub>OUT</sub> ¦が減少するように、各立上りエッジでDACをステップダウンします。                                                                      |

| 4  | POL             | 極性入力。正又は負の出力電圧をレギュレーションできるように、FBの極性及びスレッショルドを変化します。又、コードが増加すると常に出力電圧が増加するように、DAC出力の極性も変化します。正の出力電圧の場合はPOL = V <sub>C</sub> に設定してください。 |

| 5  | V <sub>DD</sub> | 内部MOSFET用のゲート駆動電源。 $V_{\mathbb{C}}$ に接続してください。                                                                                        |

| 6  | ISET            | LX電流リミットの設定。内部スイッチのピーク電流リミットを設定します。 $500$ mA電流リミットの場合は $V_{CC}$ に、 $250$ mA電流リミットの場合はGNDに接続してください。                                    |

| 7  | SHDN            | シャットダウン入力。 $\overline{\text{SHDN}}$ がロジックローになると、 $\text{MAX}686$ はシャットダウンモードになります。通常動作時は $\text{V}_{\mathbb{C}}$ に接続してください。           |

| 8  | DACOUT          | DAC出力電圧                                                                                                                               |

| 9  | REF             | リファレンス出力。0.1μFセラミックコンデンサでGNDにバイパスしてください。                                                                                              |

| 10 | FB              | フィードバック入力。MAX686の出力電圧を設定するには、外部分圧器に接続してください。詳細については、「DACを使用した場合の出力電圧の設定」の項を参照してください。                                                  |

| 11 | POK             | パワーOKセンス入力/パワーOKコンパレータ入力。 1.125 $V$ 以上の電圧をPOKに供給すると、 $\overline{LCDON}$ がローに設定されます。 $V_{IN}$ 又は $V_{OUT}$ の監視用抵抗分圧器に接続してください。         |

| 12 | Vcc             | IC電源入力                                                                                                                                |

| 13 | GND             | グランド                                                                                                                                  |

| 14 | <u>ICDON</u>    | パワーOKコンパレータオープンドレイン出力。LCDの電源をオン/オフするには、外部スイッチに接続してください。詳細については、「POK及びLCDONによるLCDの制御」の項を参照してください。                                      |

| 15 | N.C.            | 無接続。内部接続されていません。                                                                                                                      |

| 16 | LX              | 内部28V、500mA Nチャネルスイッチのドレイン                                                                                                            |

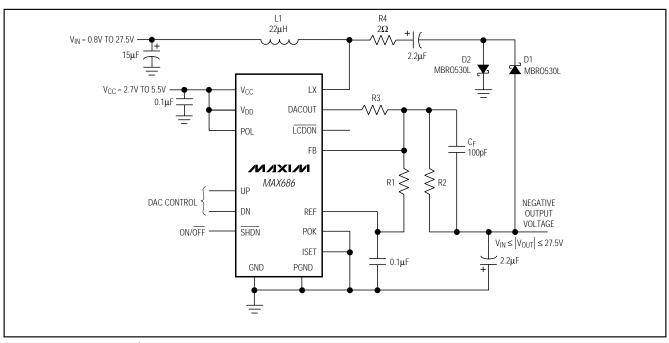

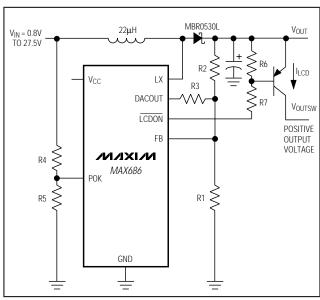

図1. ブーストコンバータ:正の出力電圧

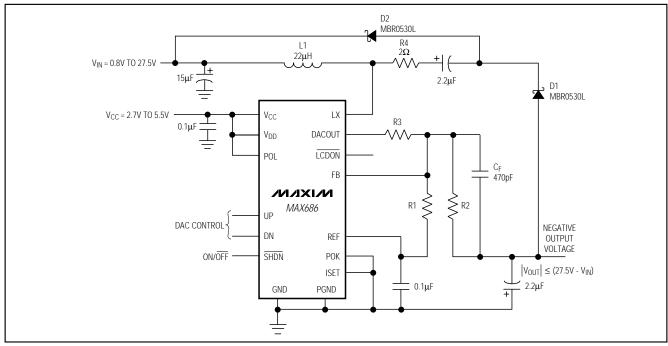

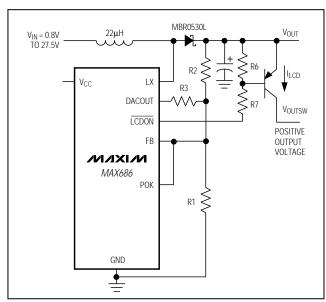

図2. 負出力電圧のアプリケーション回路

図3. 負出力電圧の別のアプリケーション回路

#### 詳細

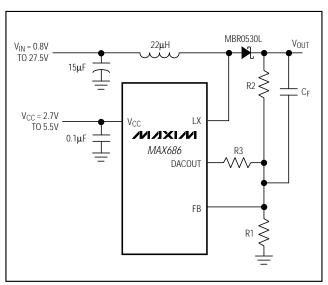

MAX686は、+0.8V~+27.5Vのバッテリ電圧をより高い正又は負の電圧に変換するための内部NチャネルMOSFETスイッチを備えたステップアップコンバータです。図1は正の出力電圧を発生するように構成したMAX686、図2はダイオードとコンデンサを1つで追加して、負の出力電圧を発生するように構成したMAX686を示しています。又、図3に負の出力電圧を開発する別の方法を示します。出力電圧は、外部の抵抗分圧ネットワークで設定します。出力電圧の調整には、内部のディジタルアナログコンバータ(DAC)を使用します。MAX686の電流制限パルス周波数変調(PFM)制御には、プログラマブル電流制限を適用しており、広い範囲の負荷に対して高い効率を提供できます。

#### ブースト制御法(POL = GND)

MAX686のスイッチングは、ピーク電流制限及び1組のワンショットを組み合せて制御しています。オンサイクルでは、内部スイッチが閉じ、 $10\mu$ s固定の最大オンタイムが(低入力電圧で)経過するか、又はスイッチピーク電流リミットに達するまで、インダクタを流れる電流がランプアップします。このピーク電流リミットは、 $500mA(ISET=V_{CC})$ 又は250mA(ISET=GND)のどちらにでも設定できます(「ピークインダクタ電流リミットの設定」の項参照)。

オンサイクルが終わるとスイッチがオフになり、ダイオードを介しインダクタによって出力コンデンサが充電されます。最小オフタイムの経過後、出力がレギュレーション範囲外の場合は、次のオンサイクルが開始されます。最小オフタイムが経過した時に出力がレギュレーション範囲内になった場合は、出力がレギュレーション範囲外になるまでオフサイクルが延長され、レギュレーション範囲外になった時点でオンサイクルが開始されます。

MAX686は、 $FB(V_{FB})$ の電圧を1.25Vに安定化します。出力がレギュレーション以下の時( $V_{FB}$ が1V以下で、スイッチ電流リミットを越えた時)は、MAX686が初期パワーアップモードで動作し、ソフトスタートを実行するために最小オフタイムが5 $\mu$ sまで増加します。負荷に依存するスイッチング周波数、入力電圧及び出力電圧は、300kHzまで対応できます。

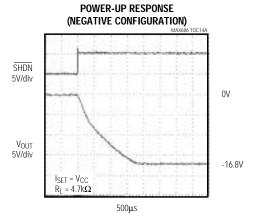

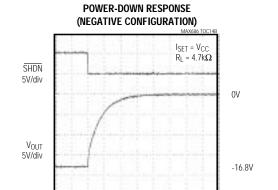

#### 反転制御法(POL = V<sub>CC</sub>)

反転動作時は、MAX686がFBの電圧( $V_{FB}$ )を0Vに安定化し、誤差アンプの極性が反転します。負出力電圧では、最小オフタイムが3.5 $\mu$ sに変化します。出力がレギュレーション以下の時( $V_{FB}$ が0.25V以上で、スイッチ電流リミットを越えた時)は、初期パワーアップが想定され、ソフトスタートを実行するために最小オフタイムが5 $\mu$ sまで増加します。

パワーOKコンパレータ

POKはパワーOKコンパレータの入力です。このコンパレータは、内部NチャネルMOSFETを駆動します。MOSFETのオープンドレイン出力 $\overline{\text{LCDON}}$ は、1つの外部PNPトランジスタ又はPチャネルMOSFETを駆動することができますが、正の $\overline{\text{VOUT}}$ をLCDに切り替えることになります(図6及び図7参照)。POKの電圧が1.125Vを超えると(パワーOK)、 $\overline{\text{LCDON}}$ がローになり、外部PNPトランジスタがオンになります。POKの電圧が1.125V以下に下がると(パワーノットOK)、外部PNPトランジスタがオフになり、LCDディスプレイへの電源が切れます。この特長により、LCDディスプレイを不正レベルの電圧から保護します。シャットダウン又は低電圧ロックアウト時は、 $\overline{\text{LCDON}}$ がハイインピーダンスになります。

#### シャットダウンモード

SHDNがローの時は、MAX686がシャットダウンモードになり、制御回路、POKコンパレータ、DAC出力バッファ、リファレンス及び内部バイアス回路がオフになります。DAC設定は、VCCがDACリセットスレッショルド以上である限り保存されます。この時の消費電流は1.5μAに低下します。SHDNはロジックレベル入力です。通常動作時はVCCに接続してください。

シャットダウンモードにおける出力電圧は、出力電圧の極性によって異なります。正の出力電圧構成(図1)では、ダイオード(D1)及びインダクタ(L1)を介して直接入力に接続されます。デバイスがシャットダウンモードになると、1つのダイオードに対する出力電圧降下が入力電圧以下に下がり、出力に接続されている負荷には電流が流れ続けることもあります。負の出力電圧構成(図2及び図3)では、入力と出力の間にDC経路がなく、シャットダウンモードにおいては出力がGNDに降下します。

#### 内部DAC

MAX686は出力電圧をディジタル制御するための内部6ビットカウンタ及びDACが備わっています(「DACを使用した場合の出力電圧の設定」の項参照)。UP及びDN入力ピンがDACを直接制御する内部アップ/ダウンカウンタを駆動します。ブースト構成においてVOUTを増加するには、立上りエッジをUPに供給します。これによってDAC出力電圧が1ステップだけ低下し、その分だけVOUTが増加します。逆に、VOUTを低下させるには、立上りエッジをDNに供給します。この場合DAC出力電圧が1ステップだけ増加し、その分だけVOUTが低下します。負の出力では、出力電圧の絶対値の制御方向を一定に保つために、UPとDNの制御方向が反転します。パワーアップ時には、DACコードが内部的に中間スケールになります。DACの内部カウンタは、一旦フルスケール又はゼロに達するとロールオーバーしません。従って、

この状態で立上りエッジが発生しても無視されるため、 予期しない低電圧や過電圧を防止できます。

#### 内部リファレンス

MAX626の1.25V内部リファレンスは、温度範囲で 2%の精度になっています。 $50 \mu A$ までの電流を供給で きるようになっているため、少なくとも $0.1 \mu F$ のコンデンサでバイパスしてください。「バイパスコンデンサ」の項を参照してください。

設計手順 \_\_\_\_\_\_

#### DACを使用した場合の出力電圧の設定

アプリケーションでは出力電圧が正又は負にかかわらず、MAX686の出力電圧は図1、図2及び図3に示す3つの外部抵抗(R1、R2、R3)を使用して設定してください。FBの最大入力バイアス電流は50nAになるため、大きな抵抗をフィードバックループに使用しても、精度にはそれ程影響がありません。R1には10k~220kの範囲のものを選択し、R2とR3には、次の項で示す計算式で適切な値を決定してください。

#### 最小正出力電圧の設定

最小出力電圧は、 $V_{OUT}$ からFBの抵抗分圧器(R1 ~ R2、図1)で設定します。出力電圧は、 $V_{DACOUT}$ =  $V_{FB}$  = 1.25Vの時に最小になります。従って、R3 は最小出力電圧には関係ありません。R1 の値としては、分圧器の電流が約  $10\,\mu$ A になるように、120k を選択します。R2の値は次式で求めます。

$R2 = R1 \times (V_{OUT(MIN)} - V_{FB}) / V_{FB}$

例えば、 $V_{OUT(MIN)} = 12.5V$ とすると、R2の値は次のようになります。

$R2 = 120k\Omega \times (12.5 - 1.25) / (1.25) = 1.08M\Omega$

R1及びR2は、寄生容量が最小になるように、FBの近くに配置してください。

#### 最大正出力電圧の設定

DACは、 $0V \sim 1.25V$ の範囲を64ステップで調整でき、1LSB = 1.25V/63 = 19.8mVです。R3には、DACOUTで $V_{OLIT}$ を調整できるような値を選択します(図1)。

$V_{OUT(MAX)} = 25V$ 、 $V_{OUT(MIN)} = 12.5V$ の場合は、R3の値が次のようになります。

R3 = R2 x (V<sub>FB</sub>) / (V<sub>OUT</sub>(MAX) - V<sub>OUT</sub>(MIN)) =  $1.08M\Omega$  x (1.25) / (25 - 12.5) =  $108k\Omega$

DAC出力(V<sub>DACOUT</sub>)の関数としてのV<sub>OUT</sub>は、一般に次の通りです。

Vout = Vout(MIN) + (VFB - VDACOUT) x R2 / R3

パワーアップ時は、 $V_{DACOUT}$ = 0.635VでDACが中間スケールにリセットされます。

従って、パワーアップ後の出力電圧は次のようになります。

VOUT(MID) = VOUT(MIN) + (1.25 - 0.635) xR2 / R3 = 18.65V

尚、正の出力電圧では、V<sub>OUT</sub>が増加するとV<sub>DACOUT</sub>が低下することに注意してください。この場合、V<sub>OUT(MAX)</sub>はV<sub>DACOUT</sub>= 0Vに対応し、V<sub>OUT(MIN)</sub>はV<sub>DACOUT</sub>= 1.25Vに対応します。

#### 最小負出力電圧の設定

負出力電圧では、FBのスレッショルド電圧( $V_{FB}$ )が 0Vで、R1がFBとREFの間になります(図2及び図3)。この場合も同様に、分圧器の電流が約  $10\,\mu A$  になるように、120k をR1の値として選択します。R2の値は、次式で求めます。

例えば、 $V_{OUT(MIN)}$ = -12.5Vとすると、R2の値は次のようになります。

$R2 = 120k\Omega \times |(-12.5) / (1.25)| = 1.2M\Omega$

#### 最大負出力電圧の設定

$V_{OUT(MAX)} = -25V$ 、 $V_{OUT(MIN)} = -12.5V$ とすると、R3及び $V_{OUT(MID)}$ の値は次のようになります。

R3 = R2 x (VFB - VDACOUT(MAX)) / (VOUT(MAX) - VOUT(MIN))

=  $1.2M\Omega \times (0 - 1.25) / (-25 - -12.5) = 120k\Omega$

#### 負出力電圧では次のようになります。

Vout = Vout(MIN) + (VFB - VDACOUT) x R2 / R3.

パワーアップ時は、V<sub>DACOUT</sub>= 0.635VでDACが中間スケールにリセットされます。従って、リセット後の出力電圧は次のようになります

$$V_{OUT(MID)} = -12.5 + (0 - 0.635) \times (1.2M) / (120k) = -18.85V$$

尚、負の出力電圧では、 $V_{DACOUT}$ が増加すると $!V_{OUT}$ も増加することに注意してください。この場合、 $!V_{OUT(MAX)}$ !は  $V_{DACOUT}=1.25$ Vに対応し、 $!V_{OUT(MIN)}$ !は $V_{DACOUT}=0$ Vに対応します。

#### DACを使用しない場合の出力電圧の設定

MAX686はDACを使用しなくても出力電圧を制御できます。この場合、出力電圧は正、負に関係なく、図1、図2及び図3に示すように2つの外部抵抗(R1及びR2)だけを使用して設定してください。FBには最大50nAの入力バイアス電流が流れるため、フィードバックループに大きな抵抗を使用しても、精度に大きな影響が現れることはありません。R1には10k ~ 220k の範囲内のものを選択し、R2の値は次の項で示す式で求めます。

#### 正出力電圧の設定

ここでは、POLをGNDに接続し、R3を省略した図1の回路を使用します。POLをGNDに接続すると、FBのスレッショルド電圧がV<sub>REF</sub>に設定されます。R1の値は10k ~220k の範囲内で選択し、R2の値は次式で求めます。

$R2 = R1 \times (V_{OUT} / V_{REF} - 1)$

ここで、V<sub>RFF</sub>= 1.25Vです。

#### 負出力電圧の設定

負出力電圧の場合は、POLを $V_{CC}$ に接続し、R3を省略した図2及び図3のように、R1とR2を構成します。POLを $V_{CC}$ に接続すると、FBのスレッショルド電圧が負出力電圧用のGNDに設定されます。R1の値は10k~220kの範囲内で選択し、R2の値は次式で求めます。

R2 = R1 x |Vout|/ VREF

ここで、V<sub>REF</sub>= 1.25Vです。

図2と図3は、それぞれMAX686で負電圧を発生するための方法例を示したものです。図3では、D2を入力電源  $(V_{IN})$ に接続しています。この構成は出力リップル性能に優れていますが、 $!V_{OUT}!$ を-27.5 $V_{IN}$ 以下に制限することが必要です。アプリケーションにより大きな負電圧が必要な場合は、D2をGNDに接続した図2の構成を使用してください。この構成では、許容最大出力電圧が-27.5 $V_{IN}$ になりますが、 $!V_{OUT}!$ は $V_{IN}$ 以上であることが必要です。

#### ピークインダクタ電流リミットの設定

電流リミットを外部で選択すると、MAX686の出力性能 をより正確に制御できます。電流リミットが高い程 1サイクルでインダクタに貯蔵されるエネルギーの量も 多くなり、出力電流能力も高くなります。より大きな 出力電流を必要とするアプリケーションでは、ISETを Vccに接続し、500mAの電流リミットを選択してくだ さい。負荷に要する出力電流が低い場合は、250mAの 電流リミットを選択します。この場合インダクタが 小さくなるため、ボード面積とコストが節約できるだけ でなく、1サイクル当たりの転送エネルギーも小さくな るため、与えられたコンデンサに対する出力リップル も低減できます。電流リミットを250mAに設定するに は、ISETをGNDに接続します。ISETをV<sub>CC</sub>に接続する と、電流リミットが500mAに設定されます。それぞれ のISET電流設定における効率及び負荷電流グラフにつ いては、「標準動作特性」を参照してください。

#### インダクタの選択

MAX686はスイッチング周波数が高くなっているため、小さなインダクタを使用できます。殆どのアプリケーションでは、図1、図2及び図3に示す22μHインダクタが勧められますが、10μH~47μHの範囲内のものも使用できます。インダクタには、フェライトコア又はその相当品を使用してください。スイッチング周波数が高い場合には、鉄粉コアは勧められません。インダクタの増分飽和定格は、選択した電流リミット以上であることが必要です。最高の効率を得るには、DC抵抗の低いインダクタ(200m 以下)を使用してください。表1のインダクタメーカを参照してください。

図4. 順方向フィードコンデンサ

#### 表1. 部品メーカ

| 1X 1. IDUIL 7. 73                   |                |                |  |  |  |  |  |

|-------------------------------------|----------------|----------------|--|--|--|--|--|

| SUPPLIER                            | PHONE          | FAX            |  |  |  |  |  |

| CAPACITORS                          |                |                |  |  |  |  |  |

| AVX: TPS series                     | (803) 946-0690 | (803) 626-3123 |  |  |  |  |  |

| Matsuo: 267 series                  | (714) 969-2491 | (714) 960-6492 |  |  |  |  |  |

| Sprague 595D series                 | (603) 224-1961 | (603) 224-1430 |  |  |  |  |  |

| DIODES                              |                |                |  |  |  |  |  |

| Motorola: MBR0530L                  | (602) 303-5454 | (602) 994-6430 |  |  |  |  |  |

| Nihon; EC11 FS1 series              | (805) 867-2555 | (805) 867-2698 |  |  |  |  |  |

| INDUCTORS                           |                |                |  |  |  |  |  |

| Coilcraft: DO1608 and DT1608 series | (847) 639-6400 | (847) 639-1469 |  |  |  |  |  |

| Murata-Erie: LQH4 series            | (814) 237-1431 | (814) 238-0490 |  |  |  |  |  |

| Sumida: CD43, CD54, and CD74 series | (847) 956-0666 | (847) 956-0702 |  |  |  |  |  |

| TDK: NLC565050 series               | (847) 390-4373 | (847) 390-4428 |  |  |  |  |  |

#### ダイオードの選択

MAX686はスイッチング周波数が高いため、高速整流器が必要です。この場合1N5818やMBR0530Lなどのショットキダイオードが勧められます。但し、ダイオードのピーク電流定格は、ISETで設定したピーク電流以上であり、ブレークダウン電圧は出力電圧以上であることが必要です。最も好ましいのは、順方向電圧の低いショットキダイオードですが、超高速シリコン整流器でも構いません。表1のショットキダイオードのメーカを参照してください。

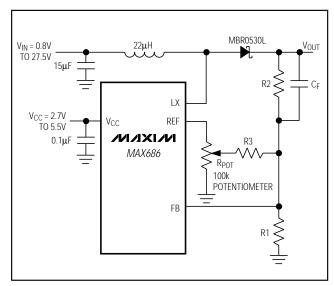

図5. 出力電圧の調整にポテンショメータを使用

#### コンデンサの選択

#### 出力フィルタコンデンサ

出力フィルタコンデンサの選択で最も重要な基準は、等価直列抵抗(ESR)の低さです。出力電圧に発生する高周波数リップルの影響は、ピークインダクタ電流と出力フィルタコンデンサのESRとの積によって決まります。「ピークインダクタ電流リミットの設定」の項でも述べたように、この条件は電流リミットを正しく選択することによってバランスを取ることができます。表1の低ESRコンデンサのメーカを参照してください。

#### バイパスコンデンサ

MAX686アプリケーションの多くは、出力電流が比較的小さくなっていますが、入力電源は、ISET電流リミットと等しい電流トランジェントに電流を提供できなければなりません。入力バイパスコンデンサは、電圧ソースからのピーク電流を低下し、MAX686のスイッチング動作によるノイズを低減します。入力 $(V_{IN})$ に必要なコンデンサのサイズは、入力ソースインピーダンスによって決まります。出力フィルタコンデンサと同様に最も重要になるのは、低ESRです。殆どのアプリケーションでは、15 $\mu$ Fの低ESRコンデンサで十分です。軽負荷アプリケーションでは、より小さなバイパスージンサでも問題ありません。ICは、できるだけ $V_{CC}$ とン及びGNDピンの近くに0.1 $\mu$ Fセラミックコンデンサを接続し、バイパスしてください。

REF電流が $25\,\mu$ Aまでの場合は、REFからGNDを $0.1\,\mu$ F セラミックコンデンサでバイパスしてください。REF では、 $50\,\mu$ Aまでの電流を外部負荷に供給できます。  $25\,\mu$ A  $I_{REF}$   $50\,\mu$ Aの場合は、 $0.47\,\mu$ FコンデンサでREFをバイパスしてください。

図6. 入力電圧の監視にPOKを使用

#### 順方向フィードコンデンサ

フィードバックループを補償し、安定性を保証するために、順方向フィードコンデンサ $(C_F)$ をR2と並列に接続してください(図4)。殆どのアプリケーションでは、コンデンサ値として100pFを使用してください。この場合、安定性を保証できる最低のコンデンサ値を選択してください。コンデンサ値が大きいと、ラインレギュレーションが劣化します。

#### アプリケーション情報

出力電圧の調整にポテンショメータを使用する場合 出力はDACの代わりにポテンショメータを使用しても 調整できます(図5)。この場合、RPOT= 100k のもの を選択し、REFとGND間に接続します。R3は、 DACOUTではなくポテンショメータのワイパに接続しま す。設計式はDACで出力電圧を調整する場合と同じです。

#### POK及びLCDONを使用したLCDの制御

POKの電圧が1.125V(typ)以上になると、オープンドレイン $\overline{\text{LCDON}}$ 出力がローに引き下げられます。外部PNPトランジスタでMAX686の正出力をオンに設定するための制御では、 $\overline{\text{LCDON}}$ で27.5Vまでに対応できます(図6及び図7)。PFETも使用できますが、この場合は抵抗分圧器も使用し、PFETが $V_{GS}$ 定格を越えないようにすることが必要です。この機能の便利なアプリケーションとしては、次の3つがあります。

● シャットダウン時に正のブースト出力を 0Vにする オフスイッチドライバ。POKはSHDNに接続します。

図7. 出力電圧の監視にPOKを使用

このスイッチを使用しない場合は、シャットダウン時に1つのダイオードに対する正出力の降下が入力電圧(V<sub>IN</sub>)以下になります。負出力では、シャットダウン時の電圧が0Vに降下するため、LCDONは必要ありません。

- 正出力に対する入力センスカットオフ。POKは、入力 電圧を検出するために分圧器に接続します。出力 スイッチがオンになるのは、入力が設定したレベル に達した時のみです(図6)。

- 正出力に対する出力センスカットオフ。POKは、出力 電圧を検出するためにフィードバック分圧器に接続 します。出力スイッチがオンになるのは、出力が設定 電圧の90%に達した時のみです(図7)。

正出力電圧を検出する場合は、出力電圧を監視するためにPOKを直接FBに接続します(図7)。POKスレッショルドは、FBの設定電圧の90%です。従って、出力電圧が設定値から10%低下すると、POK回路によって外部PNPトランジスタがオフに設定され、負荷の接続が切断されます。

入力電圧の検出では、VINからPOKの抵抗分圧器(図6のR4からR5)が、 $V_{POK} > 1.125$ Vでローに引き下がるオープンドレイン出力LCDONを制御します。R5には100k を選択してください。例えば、最小バッテリ電圧が5.3Vとすると、R4の値は次のようになります。

R4 = R5 x [(

$$V_{IN} / V_{POK}$$

) - 1]

= 100k x [(5.3 / 1.125) -1] = 371k $\Omega$

LCDONは、通常低コストのPNPトランジスタ (2N2907又はその相当品等)を駆動し、正のVOUTを

図8. 一般の電源電圧ソースを使用

LCDに切り替えます。PNPには、必要な負荷電流で $V_{CESAT}$ が低くなるものを選択してください。R7はPNPのベース電流を制限し、R6はLCDONがハイになった時オフになります。R6とR7には同じ値のものを使用できます。この場合、R7は最小ベース電流がコレクタ電流の1/50以上あるものを選択してください。例えば、 $V_{OUT(MIN)}$ = 12.5 $V_{CLCD}$ = 10mAとすると、R7は次のようになります。

$R7 \le 50 \text{ x } (12.5 - 0.7) / 10\text{mA} = 59\text{k}\Omega$

尚、LCD電圧V<sub>OUTSW</sub>は、レギュレーション後の出力電圧からPNPスイッチの降下(300mV typ)を差し引いた値になることに注意してください。

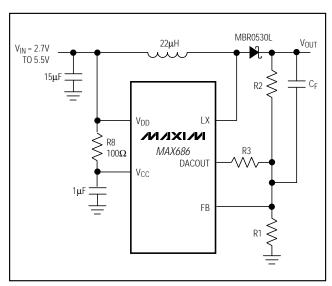

#### VINとVCCとの接続

+5.5Vの $V_{CC}$ 最大リミットさえ厳守すれば、MAX686 ( $V_{CC}$ 、 $V_{DD}$ )及びインダクタ( $V_{IN}$ )には同一のソースを使用できます。安定性を保証するには、図8に示すように、 $V_{IN}$ 及び $V_{DD}$ をソースに直接接続し、 $V_{CC}$ は100

抵抗(R8)を介してソースに接続した上で、 $V_{CC}$ は1 $\mu$ F セラミックコンデンサでバイパスします。この場合、消費電流が非常に少ないため、R8の電圧降下は小さく、性能に影響することはありません。RCはインダクタと内部電源スイッチによるスイッチングノイズから $V_{CC}$ を保護します。

多くの場合、MAX686とインダクタには同一のソースを使用しますが、バッテリ駆動アプリケーションでは、MAX686  $IC(V_{CC}, V_{DD})$ には安定化した電源を使用し、インダクタ $(V_{IN})$ にはバッテリから直接電源を供給するのが適切です。この場合、MAX686  $OV_{CC}$  は+2.7 $V_{CC}$  +5.5 $V_{CC}$ を必要としますが、インダクタは0.8 $V_{CC}$  でも問題ないため、バッテリ寿命の延長につながります。

#### レイアウト上の留意点

高い電流レベル及び高速のスイッチング波形はノイズを発生するため、正しいPCボードのレイアウトが重要になります。初期のプロトタイプでは、MAX686評価キット又はこれに該当するPCボード設計を利用することをお勧めします。スイッチングレギュレータを試作する時は、ブレッドボードやプロトボードは使用しないでください。

グランドノイズを最小にし、レギュレーションを向上させるには、GNDピン、入力バイパスコンデンサのグランドリード及び出力フィルタコンデンサのグランドリードを1点(星型構成)に接続します。又、フィードバック回路、グランド回路及びLXを優先し、浮遊容量、トレース抵抗及び放射ノイズを低減するには、リードの長さを最小にします。R1とR2は、できるだけフィードバックピンの近くに配置してください。又、バイパスコンデンサはできるだけピンの近くに配置してください。正しいボードレイアウトの例については、MAX686評価キットのデータシートをご覧ください。

### ファンクションダイアグラム\_

チップ情報

TRANSISTOR COUNT: 1325

SUBSTRATE CONNECTED TO GND