#### 概要

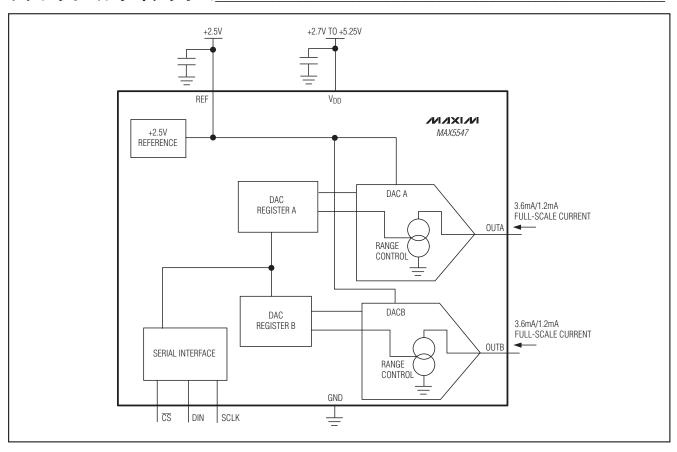

デュアル、10ビット、デュアルレンジ、ディジタル-アナログコンバータ(DAC)のMAX5547は最大3.6mA の電流をシンクし、レーザドライバ制御アプリケー ションに最適です。これより大きい電流(7.2mA max) をシンクするには、MAX5547の出力を並列接続します。 MAX5547は+2.7V~+5.25Vの単一電源で動作し、 消費電流は1mA (typ)です(内部リファレンス)。

MAX5547は高精度4ppm/℃の+2.5V内部リファレンス、 または+2.45V~+2.55Vの範囲の外部リファレンスで 動作します。最大フルスケール電流シンクレンジは、DAC ごとに3.6mAまたは1.2mAにソフトウェアでプログラム 可能です。デバイスは、10MHz SPI™対応シリアル インタフェースを通じて設定されます。

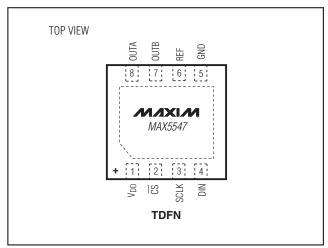

MAX5547は、3mm x 3mm x 0.8mmの8ピンTDFN パッケージで提供され、-40℃~+85℃の拡張温度範囲 での動作が保証されています。

### アプリケーション

レーザドライバ制御

ピンダイオードバイアス電流

変調電流

平均電力

消光比

#### 特長

- ♦ デュアル電流シンクDAC

- ◆ 分解能:10ビット

- ◆ ソフトウェアで選択可能な2つのフルスケール 電流レンジ: 3.6mAまたは1.2mA

- ◆ 並列接続可能な出力で7.2mA (max)まで可能

- ◆ +2.5Vの内部リファレンスはわずか4ppm/℃の ドリフト

- ◆ +2.7V~+5.25Vの単一電源動作

- ♦ INL: ±1 LSB

- ◆ DNL: ±0.75 LSB(単調性保証)

- ◆ +0.8Vの低出力に対応

- ♦ 3mm x 3mm x 0.8mmの超小型8ピンTDFN パッケージ

### 型番

| PART        | TEMP<br>RANGE  | PIN-PACKAGE | TOP MARK |  |

|-------------|----------------|-------------|----------|--|

| MAX5547ETA+ | -40°C to +85°C | 8 TDFN-EP*  | APF      |  |

\*EP = エクスポーズドパッド

+は鉛(Pb)フリー/RoHS準拠パッケージを表します。

ピン配置はデータシートの最後に記載されています。

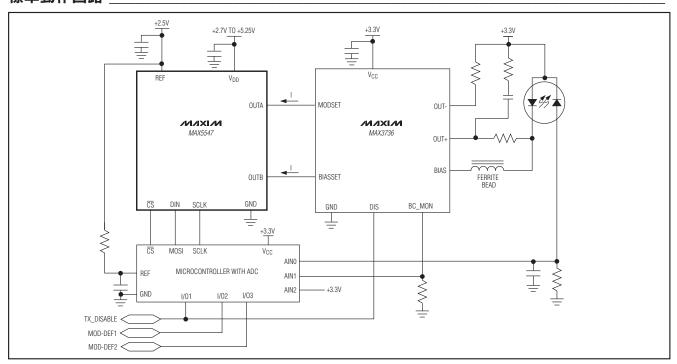

#### 標準動作回路

SPIはMotorola, Inc.の商標です。

MIXIM

\_ Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to GND0.3V to +6V OUTA, OUTB, REF to GND0.3V to (V <sub>DD</sub> + 0.3V) SCLK, DIN, CS to GND0.3V to +6V | Operating Temperature Range40°C to +85°C Junction Temperature+150°C Storage Temperature Range65°C to +150°C |

|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )                                                                    | Lead Temperature (soldering, 10s)+300°C                                                                     |

| 8-Pin TDFN (derate 18.2mW/°C above +70°C)1454.5mW                                                                        |                                                                                                             |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = +2.7 V \text{ to } +5.25 V, V_{GND} = 0 V, \text{ external reference} = +2.5 V, \text{ output voltage} = +2.0 V, T_{A} = -40 ^{\circ} C \text{ to } +85 ^{\circ} C.$  Typical values are at  $V_{DD} = +3.0 V, \text{ and } T_{A} = +25 ^{\circ} C.)$  (Note 1)

| PARAMETER                                  | SYMBOL           | COND                                | MIN                        | TYP  | MAX  | UNITS |        |  |

|--------------------------------------------|------------------|-------------------------------------|----------------------------|------|------|-------|--------|--|

| STATIC PERFORMANCE—ANAI                    | LOG SECTIO       | N                                   |                            |      |      |       | •      |  |

| Resolution                                 |                  |                                     |                            | 10   |      |       | Bits   |  |

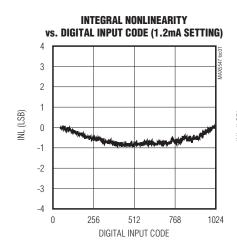

| Integral Nonlinearity (Note 2)             | INL              | $I_{OUT} = 1.2mA$                   |                            |      | ±1   | ±6    | LSB    |  |

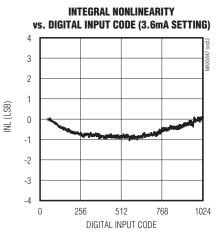

| integral Northineanty (Note 2)             | IINL             | I <sub>OUT</sub> _ = 3.6mA          |                            |      | ±1   | ±6    | LOD    |  |

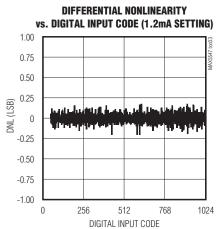

| Differential Nonlinearity                  | DNL              | Guaranteed monotoni                 |                            |      |      | ±0.75 | LSB    |  |

| Offset Error                               | OE               | Code = 030h, $T_A = +2$             | 25°C                       |      |      | ±9    | LSB    |  |

| Offset Temperature Coefficent              |                  | (Note 3)                            |                            |      | 0.05 | 0.15  | LSB/°C |  |

| Gain Error                                 | GE               | Measured from code                  | I <sub>OUT</sub> _ = 1.2mA |      | ±0.1 | ±3    | %      |  |

| daiii Eiroi                                |                  | 030h to 3FFh                        | $I_{OUT} = 3.6 \text{mA}$  |      | ±0.1 | ±5.5  | /6     |  |

| Gain Temperature Coefficient               |                  | I <sub>OUT</sub> _ = 1.2mA          |                            |      | 15   |       | ppm/°C |  |

| dan remperature docinicient                |                  | I <sub>OUT</sub> _ = 3.6mA          |                            |      | 25   |       | ррии о |  |

| Line Regulation                            |                  | $V_{DD} = +2.7V \text{ to } +5.25$  |                            |      | 8.0  | LSB/V |        |  |

| Output Crosstalk                           |                  | OUTA = midscale, OU<br>030h to 3FFh |                            | 54   |      | dB    |        |  |

| REFERENCE                                  |                  | •                                   |                            |      |      |       |        |  |

| Internal-Reference Voltage                 | V <sub>REF</sub> | T <sub>A</sub> = +25°C              |                            | 2.48 | 2.5  | 2.52  | V      |  |

| Internal-Reference Temperature Coefficient |                  | (Note 4)                            |                            |      | 4    | 30    | ppm/°C |  |

| Internal-Reference Load<br>Regulation      |                  | 0μA < I <sub>REF</sub> < +300μA     |                            |      | 1    | 3.5   | Ω      |  |

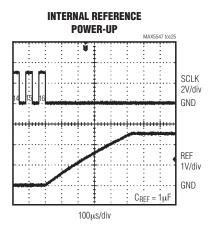

| Internal-Reference Power-Up<br>Time        |                  | $C_{REF} = 1\mu F$ , to 0.05%       |                            |      | 0.55 |       | ms     |  |

| Internal-Reference Sink Current            |                  |                                     |                            |      |      | 50    | μΑ     |  |

| Internal-Reference Source<br>Current       |                  |                                     |                            |      |      | 300   | μΑ     |  |

| REF Capacitive Load                        |                  | (Note 4)                            |                            | 0.1  |      | 10.0  | μF     |  |

| Reference Line Regulation                  |                  | $V_{DD} = +2.7V \text{ to } +5.25$  | ïV                         |      | 25   |       | μV/V   |  |

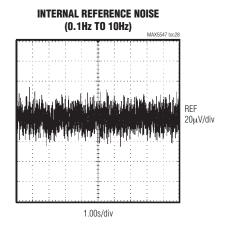

| Internal Defenses Nation                   |                  | f = 0.1Hz to 10Hz                   |                            |      | 10   |       |        |  |

| Internal-Reference Noise                   |                  | f = 10Hz to 10kHz                   |                            | İ    | 27   |       | μVRMS  |  |

| External-Reference Range                   | V <sub>REF</sub> |                                     |                            | 2.45 |      | 2.55  | V      |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +2.7V \text{ to } +5.25V, V_{GND} = 0V, \text{ external reference} = +2.5V, \text{ output voltage} = +2.0V, T_{A} = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}.$  Typical values are at  $V_{DD} = +3.0V, \text{ and } T_{A} = +25^{\circ}\text{C}.$ ) (Note 1)

| PARAMETER                                  | SYMBOL           | CONDIT                                                                                    | IONS                       | MIN                      | TYP                       | MAX   | UNITS              |

|--------------------------------------------|------------------|-------------------------------------------------------------------------------------------|----------------------------|--------------------------|---------------------------|-------|--------------------|

| External-Reference Input Impedance         |                  |                                                                                           |                            |                          | 90                        |       | kΩ                 |

| DAC OUTPUTS                                | •                |                                                                                           |                            |                          |                           |       | •                  |

|                                            |                  | 1.2mA low-current range                                                                   | Code = 030h<br>Code = 3FFh | 1170                     | 50<br>1200                | 1230  |                    |

| Output Current (Note 5)                    | IOUT_            | 3.6mA high-current range                                                                  | Code = 030h<br>Code = 3FFh | 3400                     | 150<br>3600               | 3800  | μA                 |

| LSB Size                                   |                  | 1.2mA full-scale current 3.6mA full-scale current                                         |                            |                          | 1.17<br>3.52              |       | μΑ                 |

| Current-Source Compliance<br>Voltage Range |                  | IOUT_ = full-scale (Note                                                                  | 6)                         | 0.8                      |                           |       | V                  |

| Output Impedance at Full-Scale Current     |                  | I <sub>OUT</sub> = 1.2mA, V <sub>OUT</sub> = I <sub>OUT</sub> = 3.6mA, V <sub>OUT</sub> = |                            |                          | 600<br>180                |       | kΩ                 |

| DYNAMIC PERFORMANCE                        |                  |                                                                                           |                            |                          |                           |       |                    |

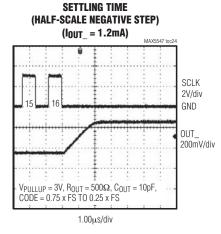

| Settling Time                              | ts               | To 1% (Note 7)                                                                            |                            |                          | 10                        |       | μs                 |

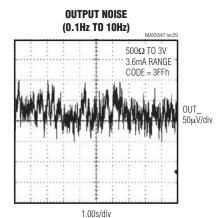

| Output Noise                               | Inuo             | f = 0.1Hz to 10Hz                                                                         |                            |                          | 0.05                      |       | LSB <sub>RMS</sub> |

| Output Noise                               | IRMS             | f = 10Hz to 10kHz                                                                         |                            |                          | 0.35                      |       | LODRING            |

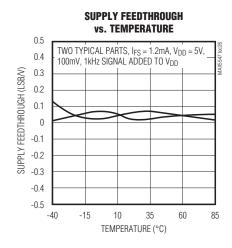

| Supply Feedthrough                         |                  | 100mV, 1kHz signal add                                                                    |                            | 0.85                     |                           | LSB/V |                    |

| Digital Feedthrough                        |                  | $R_{LOAD} = 500\Omega$ , $C_{LOAD}$ :                                                     |                            |                          | 2                         |       | pA•s               |

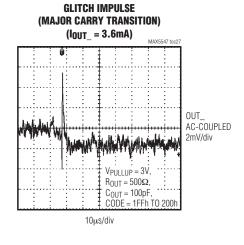

| Digital-to-Analog Glitch Impulse           |                  | $R_{LOAD} = 500\Omega$ , $C_{LOAD}$ :                                                     | = 100pF                    |                          | 16                        |       | pA•s               |

| DAC-to-DAC Full-Scale Current Matching     |                  |                                                                                           |                            |                          | 2                         |       | %                  |

| POWER SUPPLIES                             |                  |                                                                                           |                            |                          |                           |       |                    |

| Supply Voltage                             | $V_{DD}$         |                                                                                           |                            | +2.70                    |                           | +5.25 | V                  |

| Supply Current                             | IDD              | $V_{DD} = +5.25V$ , no load,                                                              | Internal reference mode    |                          | 1.1                       | 2     | - mA               |

|                                            | .00              | SCLK not switching                                                                        | External reference mode    |                          | 0.75                      | 1.5   |                    |

| LOGIC AND CONTROL INPUTS                   | 1                | 1                                                                                         |                            |                          |                           |       |                    |

| Input High Voltage                         | VIH              | (Note 8)                                                                                  |                            | 0.7 x<br>V <sub>DD</sub> |                           |       | V                  |

| Input Low Voltage                          | VIL              | (Note 8)                                                                                  |                            |                          |                           | 0.8   | V                  |

| Input Hysteresis                           | V <sub>HYS</sub> |                                                                                           |                            |                          | 0.05 x<br>V <sub>DD</sub> |       | V                  |

| Input Capacitance                          | CIN              |                                                                                           |                            |                          | 10                        |       | рF                 |

| Input Leakage Current                      | I <sub>IN</sub>  |                                                                                           |                            |                          |                           | ±1    | μΑ                 |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +2.7V \text{ to } +5.25V, V_{GND} = 0V, \text{ external reference} = +2.5V, \text{ output voltage} = +2.0V, T_{A} = -40^{\circ}\text{C}$  to +85°C. Typical values are at  $V_{DD} = +3.0V, \text{ and } T_{A} = +25^{\circ}\text{C}.)$  (Note 1)

| PARAMETER                       | SYMBOL                                    | CONDITIONS | MIN | TYP | MAX | UNITS |  |  |  |  |

|---------------------------------|-------------------------------------------|------------|-----|-----|-----|-------|--|--|--|--|

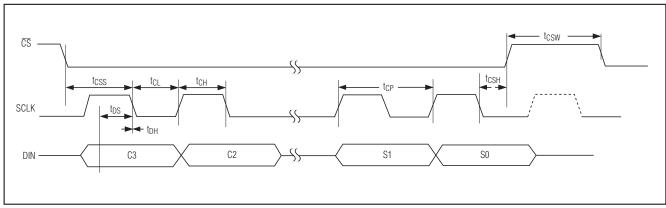

| SPI TIMING CHARACTERISTICS      | SPI TIMING CHARACTERISTICS (see Figure 1) |            |     |     |     |       |  |  |  |  |

| SCLK Clock Period               | tcp                                       |            | 100 |     |     | ns    |  |  |  |  |

| SCLK Pulse-Width High           | tch                                       |            | 40  |     |     | ns    |  |  |  |  |

| SCLK Pulse-Width Low            | tCL                                       |            | 40  |     |     | ns    |  |  |  |  |

| CS Fall to SCLK Fall Setup Time | tcss                                      |            | 25  |     |     | ns    |  |  |  |  |

| SCLK Fall to CS Rise Hold Time  | tcsh                                      |            | 50  |     |     | ns    |  |  |  |  |

| DIN to SCLK Fall Setup Time     | tDS                                       |            | 40  |     |     | ns    |  |  |  |  |

| DIN to SCLK Fall Hold Time      | t <sub>DH</sub>                           |            | 0   | •   |     | ns    |  |  |  |  |

| CS Pulse-Width High             | tcsw                                      |            | 100 |     |     | ns    |  |  |  |  |

- Note 1: Devices are 100% production tested at T<sub>A</sub> = +25°C. Limits over temperature are guaranteed by design.

- Note 2: INL linearity is from code 48 to code 1023.

- Note 3: Specification based on characterization data. Not production tested.

- Note 4: Guaranteed by design. Not production tested.

- Note 5: The DACs continue to operate at currents lower than 50μA on the 1.2mA range and 150μA on the 3.6mA range. However, performance is not guaranteed at these low currents. A code of all zeros has a nominal output current of 0μA.

- Note 6: Compliance voltage range is defined as the range where the output current is -2 LSB of its value at V<sub>OUT</sub> = +1V.

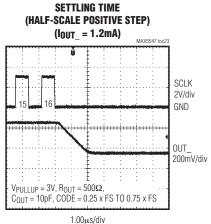

- **Note 7:** Settling time is measured from 0.25 x full scale to 0.75 x full scale.

- **Note 8:** The device draws higher supply current when the digital inputs are driven with voltages between (V<sub>DD</sub> 0.5V) and (V<sub>GND</sub> + 0.5V). See Supply Current vs. Digital Input Voltage in the *Typical Operating Characteristics*.

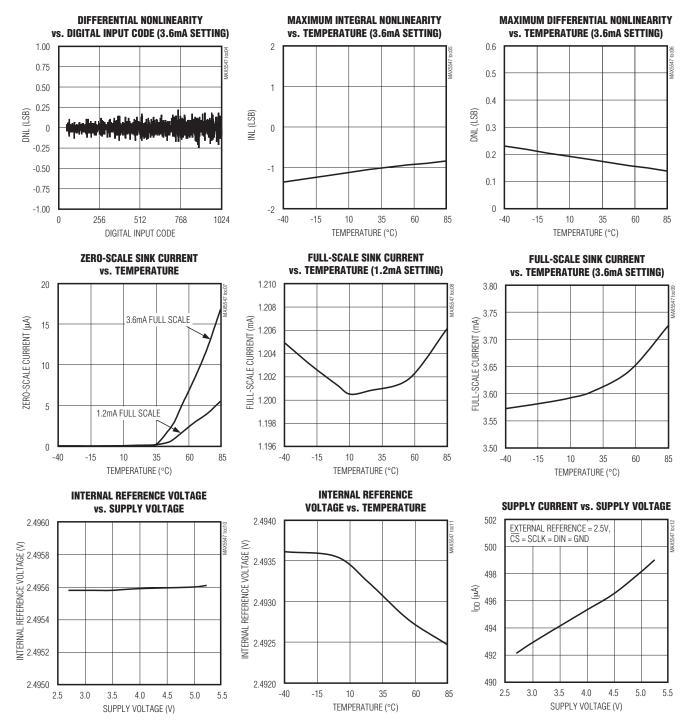

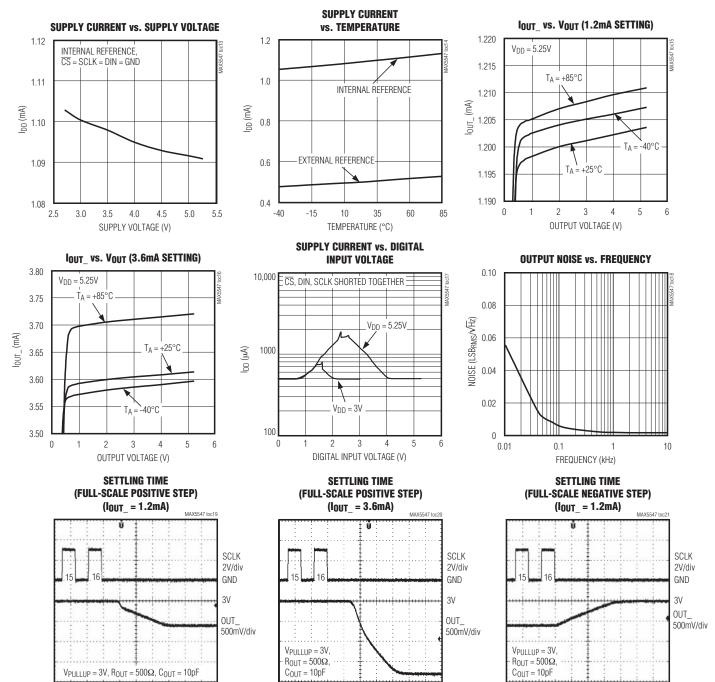

### 標準動作特性

(VDD = +3.0V, VGND = 0V, external reference = +2.5V, TA = +25°C, unless otherwise noted.)

### 標準動作特性(続き)

(VDD = +3.0V, VGND = 0V, external reference = +2.5V, TA = +25°C, unless otherwise noted.)

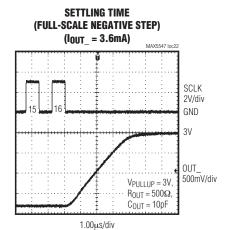

## 標準動作特性(続き)

(VDD = +3.0V, VGND = 0V, external reference = +2.5V, TA = +25°C, unless otherwise noted.)

1.00µs/div

1.00µs/div

1.00µs/div

### 標準動作特性(続き)

(VDD = +3.0V, VGND = 0V, external reference = +2.5V, TA = +25°C, unless otherwise noted.)

#### 端子説明

| 端子 | 名称              | 機能                                                                                                                                                           |

|----|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | V <sub>DD</sub> | 電源電圧。 $V_{DD}$ を $+2.7V\sim+5.25V$ に設定してください。デバイスにできる限り近接させて $0.1\mu$ Fコンデンサで $V_{DD}$ をGNDにバイパスしてください。                                                      |

| 2  | CS              | アクティブロー、ディジタルチップ選択入力。シリアルインタフェースをイネーブルするには、CSをローに設定してください。                                                                                                   |

| 3  | SCLK            | シリアルクロック入力。                                                                                                                                                  |

| 4  | DIN             | シリアルデータ入力。DINは、SCLKの立下りエッジでシリアルインタフェースにクロックインされます。                                                                                                           |

| 5  | GND             | グランド                                                                                                                                                         |

| 6  | REF             | 外部リファレンス入力/内部リファレンス出力。内部リファレンスモードに設定する場合は、REFは+2.5V出力です。外部リファレンスモードに設定する場合は、+2.45V~+2.55Vの電圧を印加してください(表1参照)。デバイスにできる限り近接させて1µFセラミックコンデンサをREFとGNDの間に接続してください。 |

| 7  | OUTB            | DAC B電流出力。OUTBは最大3.6mAをシンクします。                                                                                                                               |

| 8  | OUTA            | DAC A電流出力。OUTAは最大3.6mAをシンクします。                                                                                                                               |

|    | EP              | エクスポーズドパッド。GNDに接続してください。グランド接続部として使用しないでください。                                                                                                                |

#### 詳細

MAX5547は10ビット、デュアルレンジ、電流シンク DACであり、最高10MHzのシリアルデータクロックレートで動作します。ダブルバッファDAC入力は、16ビット入力レジスタおよび2つの10ビットDACレジスタ、後続の電流ステアリングアレイから構成されます(「ファンクションダイアグラム」を参照)。MAX5547は、DACごとに1.2mAまたは3.6mAのフルスケール出力電流をシンクします。各DACのフルスケール電流を個別に設定することができます。

MAX5547は $+2.7V\sim+5.25V$ の単一電源で動作し、 消費電流は1mA (typ)です。MAX5547は+2.5Vの内部 リファレンス、または $+2.45V\sim+2.55V$ の範囲の外部 リファレンスで動作します。

MAX5547は、MAX3736などの電流制御入力付きのレーザダイオードドライバ用のディジタル/アナログインタフェースとして最適です(「標準動作回路」を参照)。MAX5547のDAC出力によってMAX3736のMODSETおよびBIASSET電流制御入力の電流レベルを設定してください。MAX3736のMODSETおよびBIASSETラインによって、レーザドライバの任意の変調電流とバイアス電流が設定されます。

#### リファレンスアーキテクチャおよび動作

MAX5547は+2.5Vの内部リファレンスで動作するか、または+2.45V~+2.55Vの外部リファレンス電圧源を受け付けます。内部リファレンスは最大50μAをシンクし、最大300μAをソースすることができます。REFは、外部リファレンスモードで低インピーダンスのリファレンス供給源の入力として機能します。内部および外部リファ

レンスの両モードにおいて、デバイスにできる限り近接 させて $0.1\mu F\sim 10\mu F$ の範囲のセラミックコンデンサを 使って、REFをGNDにバイパスしてください。

起動時に電源が初めて印加されると、MAX5547は、デフォルトで外部リファレンスモードと1.2mAのフルスケール電流レンジモードに設定されます。ソフトウェアコマンドを使って、内部リファレンスモードと3.6mAのフルスケール電流レンジモードを選択してください(表1参照)。

#### DACデータ

MAX5547の内部レジスタによって、DACフルスケール 出力電流( $I_{FS}$ )を1.2mAまたは3.6mAに設定します(表1を参照)。10ビットDACデータは、1 LSB =  $I_{FS}$ /1023で ストレートバイナリとしてデコードされ、表2に示すよう に対応する電流に変換されます。

#### シリアルインタフェース

MAX5547は、3線式、10MHz SPI対応シリアルインタフェースを通じて動作します。 $\overline{\text{CS}}$ 、SCLK、およびDINはシリアルインタフェースのタイミングおよびデータを制御します。通常はマイクロコントローラ( $\mu$ C)であるSPIバスマスタがシリアルクロック信号を生成するように、マスタモードで動作させてください。10MHz以下のSCLK周波数を選択し、 $\mu$ Cの制御レジスタのクロック極性(CPOL)と位相(CPHA)を相反する値に設定してください。MAX5547は、SCLKについてハイまたはローのアイドル状態で動作します。このため、CPOL=0およびCPHA=1、またはCPOL=1およびCPHA=0に設定してください。

図1. SPIシリアルインタフェースのタイミング図

SCLKの立下りエッジでDINへの入力データのクロックによる入力を開始するには、CSをローに設定してください(図1参照)。シフトレジスタとのシリアル通信は、DINからロードされた16ビットコマンドワードで構成されます。先頭の4ビットの制御ビット(C3~C0)は、目的とするレジスタを決定します(表1参照)。その次の10ビットのデータビットは電流シンクレベルを設定します。D9はMSBで、D0はLSBです。正常に動作させるには、ビットS1およびS0をゼロに設定してください。データは、16回目のSCLKの立下りエッジで該当するDACレジスタにラッチされます。16ビットが書き込まれた後に、CSをハイにしてください。16ビットワード全体の期間についてCSをローに維持してください。

DACレジスタAおよびBを個別に設定するか、または両レジスタを同時に設定するには、コマンドワードを書き込んでください。また、コマンドワードは、DACが内部リファレンスを使用するか、または外部リファレンスを使用するかも設定します。

MAX5547は電源投入時、DACレジスタAおよびBがコード000hの $I_{FS} = 1.2$ mAに設定された外部リファレンスモードになります。

### アプリケーション情報

#### 電源シーケンス

REF、OUTA、およびOUTBに印加される電圧は常に $V_{DD}$  を超えないようにしてください。適切な電源シーケンスが不可能な場合は、絶対最大定格に適合させるために、外付けショットキダイオードをREF/OUTA/OUTBと  $V_{DD}$ の間に接続してください。

#### 電源バイパスおよびグランド管理

GNDのディジタルまたはAC過渡信号は、アナログ出力にノイズを生成します。GNDをできる限り良質なグランドプレーンにリターンさせてください。極めてノイズが多い環境の場合は、 $0.1\mu F$ のコンデンサをデバイスにできる限り近接させて、 $10\mu F$ および $0.1\mu F$ の並列コンデンサで、REFおよび $V_{DD}$ をGNDにバイパスしてください。綿密なPCBのグランドレイアウトによって、DAC出力とディジタル入力間のクロストークが最低限に抑制されます。

## 表1. コマンドワード概要

| C  | ONTR | OL BI | TS | MSB |    |             | DATA BITS LSB |       |             | REGISTER FUNCTION |    |    |                                                              |    |                                                                                                                        |                                                                                                           |                                                              |

|----|------|-------|----|-----|----|-------------|---------------|-------|-------------|-------------------|----|----|--------------------------------------------------------------|----|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| C3 | C2   | C1    | C0 | D9  | D8 | D7          | D6            | D5    | D4          | D3                | D2 | D1 | D0                                                           | S1 | S0                                                                                                                     |                                                                                                           |                                                              |

| 0  | 0    | 0     | 0  | X   | X  | X           | X             | X     | X           | X                 | X  | X  | X                                                            | 0  | 0                                                                                                                      | External reference mode (default state). Connect an external voltage source at REF from +2.45V to +2.55V. |                                                              |

| 1  | 0    | 0     | 0  | Х   | Χ  | Χ           | X             | Χ     | Х           | X                 | Χ  | Χ  | Х                                                            | 0  | 0                                                                                                                      | Internal reference mode. Internal reference is +2.5V.                                                     |                                                              |

| 0  | 0    | 1     | 0  |     |    |             |               | 10-bi | t data      |                   |    |    |                                                              | 0  | 0                                                                                                                      | Load DAC register A and set IouTA full-scale range to 1.2mA.                                              |                                                              |

| 0  | 0    | 1     | 1  |     |    | -           |               |       | 10-bit data |                   | 0  | 0  | Load DAC register A and set IOUTA full-scale range to 3.6mA. |    |                                                                                                                        |                                                                                                           |                                                              |

| 0  | 1    | 0     | 0  |     |    | 10-         |               |       | 10-bit data |                   | 0  | 0  | Load DAC register B and set IOUTB full-scale range to 1.2mA. |    |                                                                                                                        |                                                                                                           |                                                              |

| 0  | 1    | 0     | 1  |     |    | 10-bit data |               | 10-b  |             | t data            |    |    |                                                              |    | 0                                                                                                                      | 0                                                                                                         | Load DAC register B and set IOUTB full-scale range to 3.6mA. |

| 0  | 1    | 1     | 0  |     |    | 10-b        |               |       | 10-bit data |                   |    |    | 0                                                            | 0  | Load DAC registers A and B and set I <sub>OUTA</sub> and I <sub>OUTB</sub> full-scale ranges to 1.2mA (default state). |                                                                                                           |                                                              |

| 0  | 1    | 1     | 1  |     |    |             |               | 10-bi | t data      |                   |    |    |                                                              | 0  | 0                                                                                                                      | Load DAC registers A and B and set IOUTA and IOUTB ranges to 3.6mA.                                       |                                                              |

X = 任意。未使用コードは予備。

## 表2. 理想的なDAC出力コード表

| BINARY DAC CODE | lout_                                 |

|-----------------|---------------------------------------|

| 11 1111 1111    | 1023 × <sup>I<sub>FS</sub></sup> 1023 |

| 10 0000 0000    | 512 × <sup>I</sup> FS 1023            |

| 00 0000 0001    | <u> FS</u><br>  1023                  |

| 00 0000 0000    | 0                                     |

## ピン配置

### ファンクションダイアグラム

## チップ情報

PROCESS: BiCMOS

## パッケージ

最新のパッケージ図面情報およびランドパターンは、japan.maximic.com/packagesを参照してください。なお、パッケージコードに含まれる「+」、「#」、または「-」はRoHS対応状況を表したものでしかありません。パッケージ図面はパッケージそのものに関するものでRoHS対応状況とは関係がなく、図面によってパッケージコードが異なることがある点を注意してください。

| パッケージタイプ  | パッケージコード | ドキュメントNo.      |

|-----------|----------|----------------|

| 8 TDFN-EP | T833+2   | <u>21-0137</u> |

NIXIN

#### 改訂履用

| 版数 | 改訂日  | 説明                                                                                | 改訂ページ |

|----|------|-----------------------------------------------------------------------------------|-------|

| 2  | 7/09 | 「Electrical Characteristics (電気的特性)」の表を更新。「型番」に鉛フリーの注意書きを追加。「OUT」およびリニアリティの情報を更新。 | 1–5   |

# マキシム・ジャパン株式会社

〒169-0051東京都新宿区西早稲田3-30-16(ホリゾン1ビル) TEL. (03)3232-6141 FAX. (03)3232-6149

Maximは完全にMaxim製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。Maximは随時予告なく回路及び仕様を変更する権利を留保します。

12 \_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600