### 概要

高精度、低ノイズ、低ドリフトデュアルオペアンプのMAX44267 は、出力がゼロを通過することが可能な真のゼロ出力を提供し、ADCのダイナミックレンジを最大化して分解能を高めます。さらに、入力コモンモード範囲は+13.5Vから-12Vまで広がっています。MAX44267は、外付けコンデンサとの組合せで負の電圧レールを生成するチャージポンプ回路を内蔵しています。これによって、このアンプは+4.5V~+15Vの単一電源で動作可能ですが、通常の±4.5V~±15Vのデュアルレールアンプと同等の効率を備えています。このアーキテクチャは負の電源レールが不要なため、システムのコストとサイズが削減されます。

MAX44267は、5MHzの利得帯域幅積でユニティーゲイン 安定です。このデバイスは、50 $\mu$ V (max)の低オフセット電圧、0.4 $\mu$ V/ $\mathbb C$  (max)のドリフト、および200nV<sub>P-P</sub> (0.1Hz~10Hz)のノイズを特長とします。低オフセット/低ノイズ仕様と広い入力コモンモード範囲によって、このデバイスはセンサートランスミッタおよびインタフェースに最適です。外付けチャージポンプコンデンサを変更することによって、チャージポンプのノイズを最小限に抑えることができます。

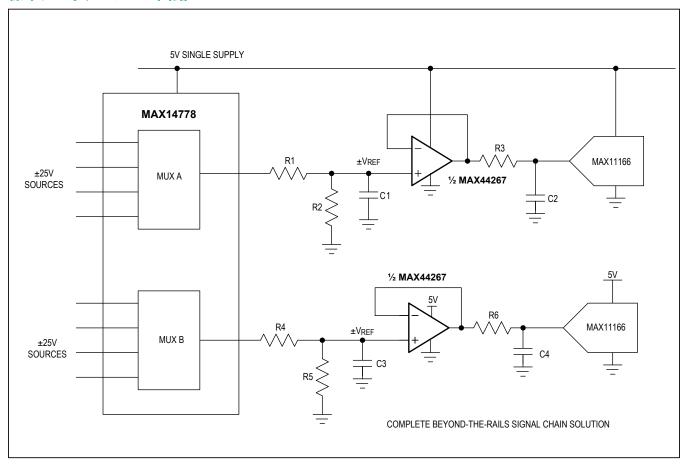

MAX44267は、アンプ、マルチプレクサ、およびADCを含むシグナルチェーンICファミリの一製品です。これらのICによって、マルチプレクサ、アンプ、およびADCへの負の電源が不要になり、スペースとコストが節約されます。詳細については、フルデータシートの「標準アプリケーション回路」および表1を参照してください。

MAX44267は14ピンTSSOPパッケージで提供され、-40℃~+125℃の温度範囲での動作が保証されています。

型番はデータシートの最後に記載されています。

#### 主な特長

- +15V単一電源で±10V以上の真のバイポーラ出力が可能なため負電源のスペースとコストが不要

- 単一電源で真のゼロ出力が可能

- 全温度で高精度検出

- 低入力Vos: 50µV (max)

- 低オフセットドリフト: 0.4µV/℃ (max)

- 広いADCダイナミックレンジを提供する低入力ノイズ: 9nV√Hz (1kHz時)

- 広い入力周波数範囲を提供する利得帯域幅積:5MHz

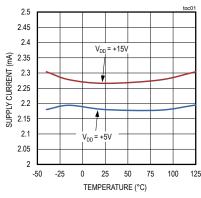

- 低消費電力と低発熱動作を可能にする低自己消費電流: 2.4mA (max)

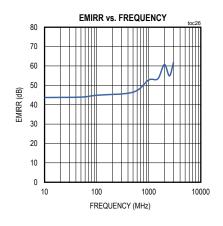

- 内蔵EMIフィルタによってモーターやその他の 高周波数ノイズ発生源に対する感度を低減

- 外付けチャージポンプコンデンサを使用する14ピンTSSOP パッケージによってノイズの最適化を実現

## アプリケーション

- PLCアナログI/Oモジュール

- センサインタフェース

- 圧力センサー

- ブリッジセンサー

- アナログレベルシフト/調整

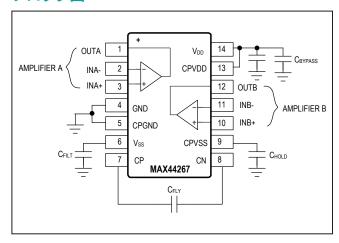

#### ブロック図

## **Absolute Maximum Ratings**

| V <sub>DD</sub> to GND                             | 0.3V to +16.5V           |

|----------------------------------------------------|--------------------------|

| CPVDD to GND                                       | 0.3V to +16.5V           |

| CP, CN, CPVSS, V <sub>SS</sub> Input Current       | ±20mA                    |

| Common-Mode Input Voltage (-V <sub>DD</sub> - 0.3V | ') to $(+V_{DD} + 0.3V)$ |

| Differential Input Current                         | ±20mA                    |

| Differential Input Voltage (Note 1)                | ±1V                      |

| OUTA, OUTB to GND (-V <sub>DD</sub> - 0.3V         | ') to $(+V_{DD} + 0.3V)$ |

| Short-Circuit Duration, OUTA, OUTB to either       | r Supply Rail 1s         |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |           |

|-------------------------------------------------------|-----------|

| 14-Pin TSSOP (derate 10mW/°C above +70°C)             | 796.8mW   |

| Operating Temperature Range40°C                       | to +125°C |

| Junction Temperature                                  | +150°C    |

| Storage Temperature Range65°C                         | to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C    |

| Soldering Temperature (reflow)                        | +260°C    |

|                                                       |           |

Note 1: The amplifier inputs are connected by internal back-to-back clamp diodes. In order to minimize noise in the input stage, current-limiting resistors are not used. If differential input voltages exceeding ±1V are applied, limit input current to ±20mA.

## **Package Thermal Characteristics (Note 2)**

**TSSOP**

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) .....100.4°C/W

Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )......30°C/W

Note 2: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/jp/thermal-tutorial.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect

### **Electrical Characteristics**

$(V_{DD} = V_{CPVDD} = 15V, V_{GND} = 0V, V_{CM} = GND, R_L = 5k\Omega$  to GND,  $C_{FLY} = 0.022\mu F, C_{HOLD} = 0.1\mu F, C_{FILT} = 0.1\mu F, T_A = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 3)

| PARAMETER                                          | SYMBOL            | CONI                                                       | DITIONS                         | MIN   | TYP   | MAX   | UNITS |

|----------------------------------------------------|-------------------|------------------------------------------------------------|---------------------------------|-------|-------|-------|-------|

| DC SPECIFICATIONS                                  |                   |                                                            |                                 |       |       |       |       |

| Power-Supply Voltage Input Range                   | V <sub>DD</sub>   | Guaranteed by PSR                                          | R                               | 4.5   |       | 15.5  | V     |

| Charge-Pump Supply Voltage Input<br>Range (Note 4) | CPV <sub>DD</sub> |                                                            |                                 | 4.5   |       | 15.5  | V     |

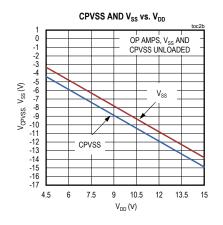

| Charge-Pump Negative Supply                        | CDV               | V <sub>DD</sub> = 15V, R <sub>L</sub> = ∞                  |                                 |       | -14.8 |       | V     |

| Output                                             | CPV <sub>SS</sub> | V <sub>DD</sub> = 5V, R <sub>L</sub> = ∞                   |                                 |       | -4.8  |       | V     |

| Ellered News time Organic Order t                  | \/                | $V_{DD}$ = 15V, $R_L$ = 5k $\Omega$                        |                                 |       | -13   |       | V     |

| Filtered Negative Supply Output                    | $V_{SS}$          | $V_{DD} = 5V$ , $R_L = 5k\Omega$                           |                                 |       | -3.6  |       | V     |

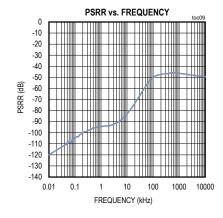

|                                                    | PSRR              |                                                            | T <sub>A</sub> = +25°C          | 117   | 137   |       | dB    |

| Power-Supply Rejection Ratio                       |                   | +4.5V ≤ V <sub>DD</sub> ≤<br>+15.5V                        | -40°C ≤ T <sub>A</sub> ≤ +125°C | 112   |       |       |       |

| T-1-1-0 :                                          | I <sub>DD</sub>   | R <sub>L</sub> = ∞                                         | T <sub>A</sub> = +25°C          |       | 2.4   | 3.6   | mA    |

| Total Quiescent Current                            |                   |                                                            | -40°C ≤ T <sub>A</sub> ≤ +125°C |       |       | 4.0   |       |

| Innut Common Mada Dance                            | V <sub>CM</sub>   | Guaranteed by CMRR test                                    | V <sub>DD</sub> = 15V           | -12.0 |       | +13.5 | V     |

| Input Common-Mode Range                            |                   |                                                            | V <sub>DD</sub> = 5V            | -2.0  |       | +3.5  |       |

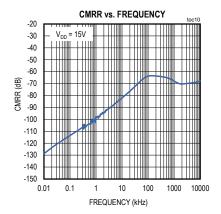

|                                                    | CMRR              | V <sub>DD</sub> = 15V,<br>V <sub>CM</sub> = -12V to +13.5V | T <sub>A</sub> = +25°C          | 138   | 150   |       | 40    |

| Common-Mode Rejection Ratio                        |                   |                                                            | -40°C ≤ T <sub>A</sub> ≤ +125°C | 122   |       |       | dB    |

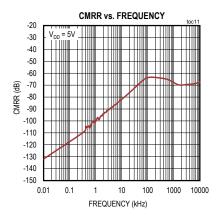

|                                                    |                   | V <sub>DD</sub> = 5V,                                      | T <sub>A</sub> = +25°C          | 125   | 140   |       | ٩D    |

|                                                    |                   | $V_{CM} = -2V \text{ to } +3.5V$                           | -40°C ≤ T <sub>A</sub> ≤ +125°C | 118   |       |       | dB    |

# 出力範囲±10V

## **Electrical Characteristics (continued)**

$(V_{DD} = V_{CPVDD} = 15V, V_{GND} = 0V, V_{CM} = GND, R_L = 5k\Omega \text{ to GND, } C_{FLY} = 0.022\mu\text{F, } C_{HOLD} = 0.1\mu\text{F, } C_{FILT} = 0.1\mu\text{F, } T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C, unless otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}\text{C.}$ ) (Note 3)

| PARAMETER                              | SYMBOL                                                           | CONI                                             | DITIONS                                 | MIN       | TYP   | MAX | UNITS              |

|----------------------------------------|------------------------------------------------------------------|--------------------------------------------------|-----------------------------------------|-----------|-------|-----|--------------------|

| La 1 Off 1 Valla                       | .,,                                                              | $T_A = +25^{\circ}C$<br>-40°C \le T_A \le +125°C |                                         |           | 4     | 45  | /                  |

| Input Offset Voltage                   | Vos                                                              |                                                  |                                         |           |       | 50  | μV                 |

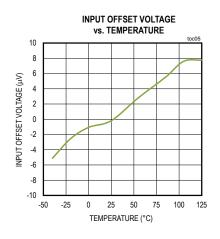

| Input Offset Voltage Drift (Note 5)    | TCV <sub>OS</sub>                                                | -40°C ≤ T <sub>A</sub> ≤ +125°C                  | ;                                       |           | 0.1   | 0.4 | μV/°C              |

| In and Bing Comment                    | IB                                                               | T <sub>A</sub> = +25°C                           |                                         |           | 0.5   | 1.5 | ^                  |

| Input Bias Current                     |                                                                  | -40°C ≤ T <sub>A</sub> ≤ +125°C                  | -40°C ≤ T <sub>A</sub> ≤ +125°C         |           |       | 2.5 | nA                 |

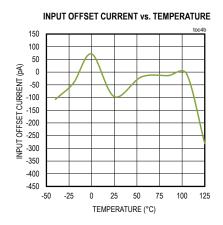

| Innut Officet Current                  |                                                                  | T <sub>A</sub> = +25°C                           |                                         |           | 0.3   | 1.0 | 4                  |

| Input Offset Current                   | los                                                              | -40°C ≤ T <sub>A</sub> ≤ +125°C                  | ;                                       |           |       | 2.0 | nA                 |

|                                        |                                                                  | V <sub>DD</sub> = 15V,                           | T <sub>A</sub> = +25°C                  | 136       | 145   |     |                    |

| Onen Leen Cain                         | _                                                                | -11V ≤ V <sub>OUT</sub> ≤ +13.5V                 | -40°C ≤ T <sub>A</sub> ≤ +125°C         | 129       |       |     | 40                 |

| Open-Loop Gain                         | A <sub>VOL</sub>                                                 | V <sub>DD</sub> = 5V,                            | T <sub>A</sub> = +25°C                  | 130       | 140   |     | dB                 |

|                                        |                                                                  | $-1.3V \le V_{OUT} \le +3.5V$                    | -40°C ≤ T <sub>A</sub> ≤ +125°C         | 121       |       |     |                    |

| Input Resistance                       | R <sub>IN</sub>                                                  |                                                  |                                         |           | 50    |     | ΜΩ                 |

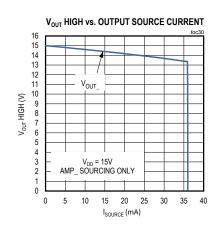

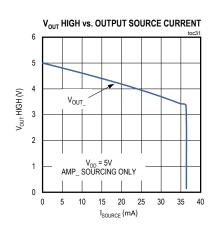

| Maximum Output Current                 | lout                                                             | Sinking                                          |                                         |           | 17    |     | m ^                |

| Maximum Output Current                 |                                                                  | Sourcing                                         |                                         |           | 36    |     | mA                 |

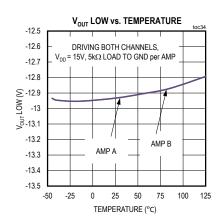

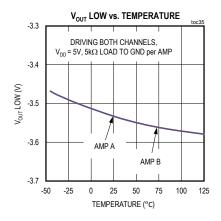

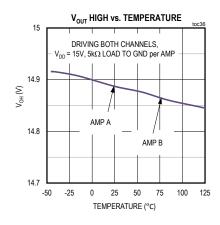

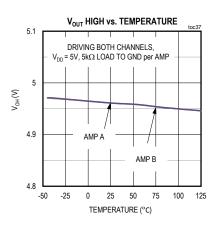

| Output Voltage Swing High              | V                                                                | $V_{DD} = 15V, R_{L} = 5k\Omega$                 | Ω, both channels driven                 | 13.8 14.8 |       | - v |                    |

| (V <sub>OUT</sub> to GND)              |                                                                  | $V_{DD}$ = 5V, $R_L$ = 5kΩ, both channels driven |                                         | 3.8       | 4.9   |     |                    |

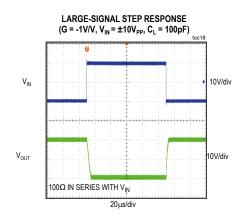

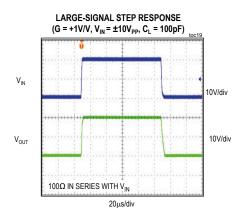

| \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |                                                                  | $V_{DD} = 15V, R_L = 5k\Omega$                   | Ω, both channels driven                 | -11.3     | -12.7 |     | V                  |

| (V <sub>OUT</sub> to GND)              | $V_{OL}$ $V_{DD} = 5V$ , $R_L = 5k\Omega$ , both channels driven |                                                  | -1.5                                    | -3.5      |       | V   |                    |

| AC SPECIFICATIONS                      |                                                                  |                                                  |                                         |           |       |     |                    |

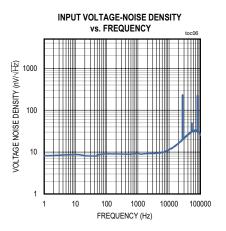

| Input Voltage-Noise Density            | e <sub>N</sub>                                                   | f = 1kHz                                         |                                         |           | 9     |     | nV/√ <del>Hz</del> |

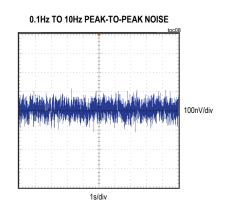

| Input Voltage Noise                    |                                                                  | 0.1Hz < f < 10Hz                                 |                                         |           | 200   |     | nV <sub>P-P</sub>  |

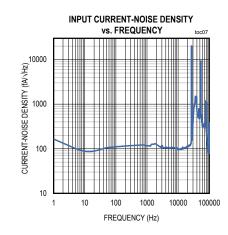

| Input Current-Noise Density            | i <sub>N</sub>                                                   | f = 1kHz                                         |                                         |           | 200   |     | fA/√Hz             |

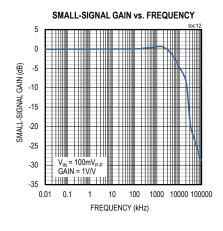

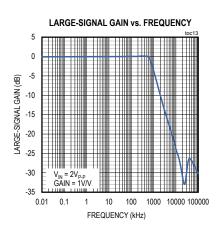

| Gain-Bandwidth Product                 | GBW                                                              |                                                  |                                         |           | 5     |     | MHz                |

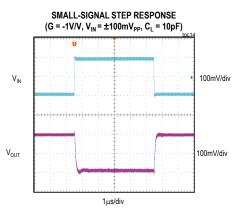

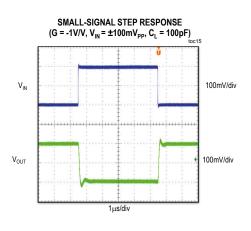

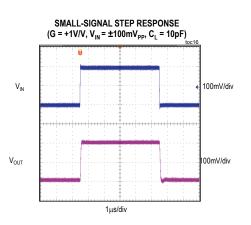

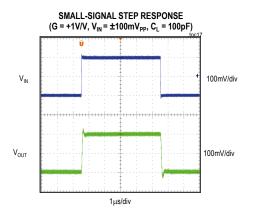

| Slew Rate                              | SR                                                               |                                                  |                                         |           | 3     |     | V/µs               |

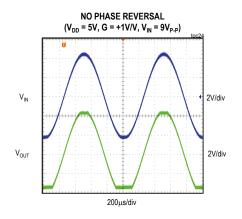

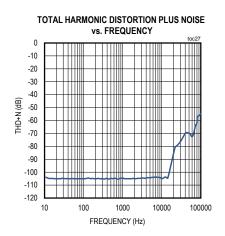

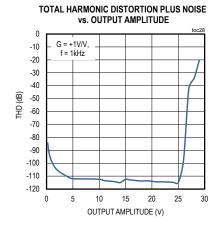

| Total Harmonic Distortion              | THD                                                              | f = 1kHz, V <sub>OUT</sub> = 2V                  | <sub>P-P</sub> , A <sub>V</sub> = +1V/V |           | -100  |     | dB                 |

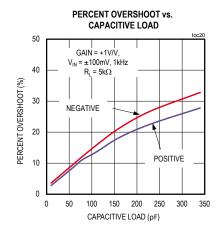

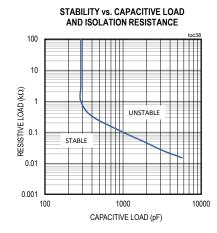

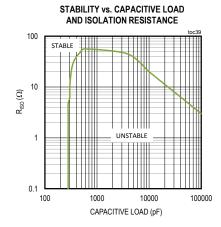

| Capacitive Loading                     | CL                                                               | No sustained oscillat                            | tion, $A_V = +1V/V$                     |           | 300   |     | pF                 |

| Charge-Pump Frequency                  | fosc                                                             |                                                  |                                         |           | 500   |     | kHz                |

| Charge-Pump Feedthrough                |                                                                  |                                                  |                                         |           | 2     |     | mV                 |

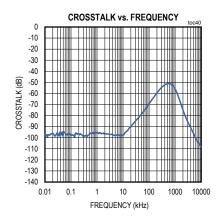

| Crosstalk                              | X <sub>talk</sub>                                                | f = 1kHz                                         |                                         |           | -100  |     | dB                 |

| Settling Time                          | t <sub>S</sub>                                                   |                                                  |                                         |           | 1     |     | μs                 |

Note 3: All devices are 100% production tested at  $T_A = +25$ °C. Temperature limits are guaranteed by design.

Note 4: CPVDD voltage must be equal to V<sub>DD</sub> voltage. Connect CPVDD to V<sub>DD</sub>.

Note 5: Parameter is guaranteed by design.

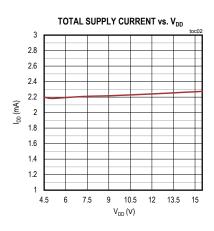

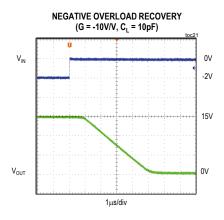

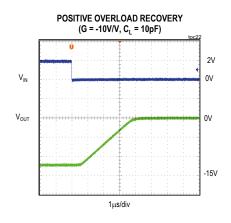

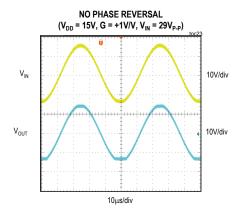

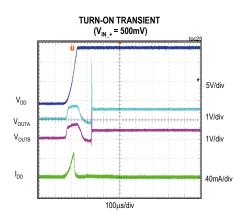

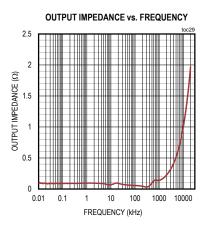

## 標準動作特性

$(V_{DD} = V_{CPVDD} = 15V, V_{GND} = V_{CPGND} = 0V, V_{CM} = 0V, C_{FLY} = 0.022 \mu F, C_{HOLD} = 0.1 \mu F, C_{FILT} = 0.1 \mu F, R_L = 5 k\Omega \text{ and } C_L = 10 pF \text{ to GND}, T_A = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.})$

## TOTAL SUPPLY CURRENT vs. TEMPERATURE

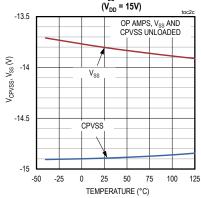

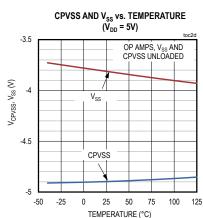

#### CPVSS AND V<sub>SS</sub> vs. TEMPERATURE (V<sub>SS</sub> = 15V)

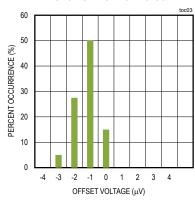

#### INPUT OFFSET VOLTAGE HISTOGRAM

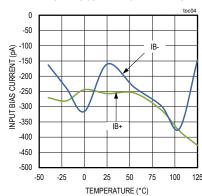

#### INPUT BIAS CURRENT vs. TEMPERATURE

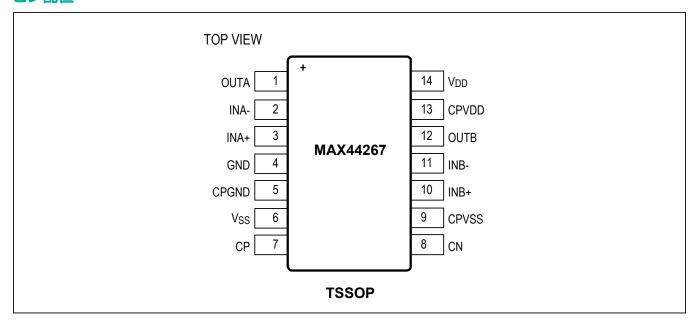

## ピン配置

## 端子説明

| 端子 | 名称              | 機能                                                                                                                                    |

|----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 1  | OUTA            | チャネルAの出力                                                                                                                              |

| 2  | INA-            | チャネルAの負の入力                                                                                                                            |

| 3  | INA+            | チャネルAの正の入力                                                                                                                            |

| 4  | GND             | グランド。GNDを安定したグランドプレーンに接続してください。                                                                                                       |

| 5  | CPGND           | チャージポンプのグランド。CPGNDをGNDに接続してください。                                                                                                      |

| 6  | V <sub>SS</sub> | フィルタ内蔵の負の電源出力。低ESRのコンデンサ( $C_{FILT}=1\mu F$ )で、 $V_{SS}$ をGNDに接続してください。                                                               |

| 7  | СР              | チャージポンプの正のコンデンサ接続。 $CN$ のみへのコンデンサ接続。いかなる電圧も $CP$ または $CN$ に接続しないでください。 $CP$ と $CN$ 間に低 $ESR$ のコンデンサ( $C_{FLY}=0.022\mu F$ )を接続してください。 |

| 8  | CN              | チャージポンプの負のコンデンサ接続。 $CP$ のみへのコンデンサ接続。いかなる電圧も $CN$ または $CP$ に接続しないでください。 $CP$ と $CN$ 間に低 $ESR$ のコンデンサ( $C_{FLY}=0.022\mu F$ )を接続してください。 |

| 9  | CPVSS           | チャージポンプの負の電源出力。0.1μFのコンデンサでCPVSSをCPGNDに接続してください。                                                                                      |

| 10 | INB+            | チャネルBの正の入力                                                                                                                            |

| 11 | INB-            | チャネルBの負の入力                                                                                                                            |

| 12 | OUTB            | チャネルBの出力                                                                                                                              |

| 13 | CPVDD           | チャージポンプの電源電圧入力。 $CPVDD$ を $V_{DD}$ に接続してください。 $0.1\mu F$ のコンデンサで $CPVDD$ を $GND$ に接続してください。                                           |

| 14 | V <sub>DD</sub> | デバイスの電源電圧入力。0.1μFのコンデンサでV <sub>DD</sub> をGNDに接続してください。                                                                                |

### 詳細

MAX44267は、50µV以下の最大入力基準オフセットと 低1/fノイズを提供する高精度アンプです。これらの特性は、 独自のオートゼロ技法とチョッパ安定化技法の組合せを使 用することによって実現されます。このオートゼロとチョッ ピングの組合せによって、これらのアンプはゼロドリフト アンプのすべての利点を提供しつつ、低ノイズを確保し、 チョッパスパイクを最小限に抑え、広い帯域幅を提供する ことが保証されます。

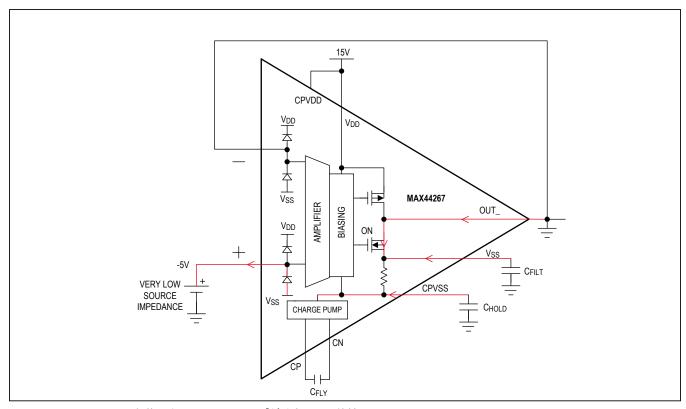

#### 共通の内蔵チャージポンプ

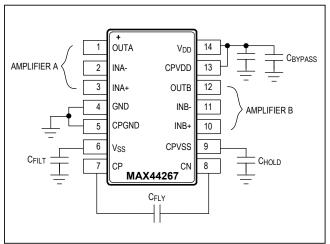

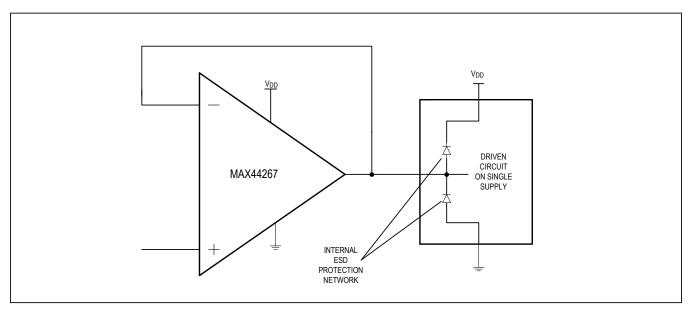

MAX44267の内蔵チャージポンプは、両方のアンプに共 通の負の電圧レール(VSS)を生成します(外付けコンデンサ の接続については、図1を参照してください)。このデバイ スの総自己消費電流は、4mA (max)です(両方のオペアン プとチャージポンプの動作を含む)。

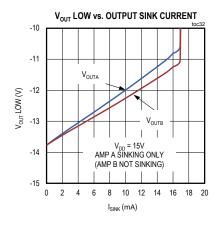

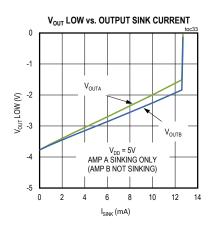

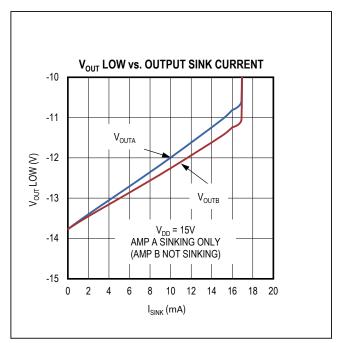

VSS発生器はMAX44267の負の電源として機能し、限ら れたシンク電流能力を備えています。その能力を超えて負 荷をかけようとすると、負の電源電圧が低下し、電流シン

図1. 外付けコンデンサの接続

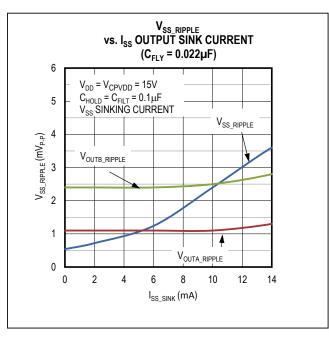

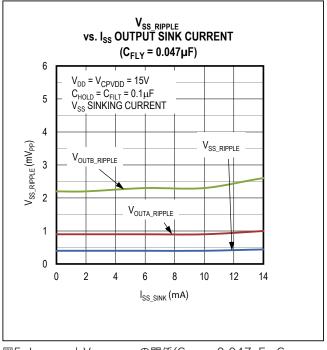

ク時の駆動能力に影響します。チャネル当り17mA (typ) を超えたシンクは、負方向の振幅の減少とリップルの増大 につながり、両方の出力に影響を与えて、両方のアンプの 出力精度と性能が低下します。

出力Vss負電源は、両方のアンプチャネルに共通です。 1つのチャネルの出力に推奨値を超える負荷をかけると、 上記のように第2のアンプチャネルに影響します。両方の チャネルの総負荷を17mA以下に維持する必要があります。 1つのチャネルの負荷が非常に小さい場合、たとえば 100µAのみをシンクしているときは、もう一方のチャネルは 16.9mAをシンク可能です。図2に示すように、+15Vの VDDを使用する場合、VSS出力は無負荷時で約-13.6V (typ) になります。アンプAのシンクによってVSSレールが上昇し、 それがVOUTBに反映されます。

図2. VOUT LOWと出力シンク電流の関係

#### ESD回路

基板上の他のすべての回路は負の最大端がOVでも、 MAX44267の出力振幅はOVを大幅に下回る可能性があ ります。最近のほぼすべてのICは電源レールへのダイオー ドクランプ回路で入力を保護しているため、駆動されるIC がMAX44267の出力をクランプしていることが明らかに なる可能性があります(図3)。

Maxim Integratedでは、ADC、マルチプレクサ、および電 流検出アンプなど、電源レールを超えた(Beyond the Rails) 駆動が可能な入力を備えた多数の製品を提供しています。 MAX44267の出力が他のICのESD回路によってクランプ されないように他の回路を設計してください。この問題に 対する一般的な解決策として、MAX44267による増幅 または調整とともに、出力をレベルシフトする方法があり ます。MAX44267アンプの周囲のどのデバイスも絶対最 大定格を超えないように注意してください。

#### コンデンサの選択

MAX44267は、VSS負電源レールを生成するために3つ の外付けコンデンサ(CFLY、CHOLD、およびCFILT)を必要 とします。チャージポンプの出力抵抗は、CFLY、CHOLD、 およびCFILTのESRの関数です。最小の出力抵抗を維持す るために、低ESRのコンデンサを使用してください。

#### フライングコンデンサ(CFLY)

フライングコンデンサの値を大きくすると、出力抵抗が減少 します。0.047µF以上では、内部スイッチの抵抗とコン デンサのESRが出力抵抗の大半を占めるため、CFIYの容 量の増大による影響は非常にわずかとなります。

### 出力コンデンサ(CHOLD)

出力コンデンサの値を大きくすると、出力リップル電圧が 低減します。出力コンデンサのESRを小さくすると、出力 抵抗とリップルの両方が低減します。出力リップルの増大 を許容することができる場合は、軽負荷時により小さい

図3. 別の回路のESD回路によってMAX44267の出力がクランプされる可能性

容量値を使用することができます。下記のグラフを参照し て、特定のシンク電流値に対するピーク間リップルを概算 してください。

### CPVSSのバイパスコンデンサ

入力電源(CPVSS)をグランドに接続して、そのACインピー ダンスおよびチャージポンプのスイッチングノイズの影響 を低減してください。できる限りICに近い位置で、CPVSS とCPGND間に0.1µF (min)の低ESRコンデンサを接続し てください。

#### ノイズ抑制

すべてのアクティブデバイスに固有の低周波数ノイズは、 周波数に反比例します。酸化物およびPN接合によって捕 捉/解放される酸化物シリコン界面の電荷は、より多くの 場合に低周波数で発生します。MAX44267は内部で1/f ノイズを除去するため、DCまたは低周波数、高精度アプ リケーションに最適です。1/fノイズは低速で変化するオフ セット電圧の形で現れ、チョッピング技法の使用によって 除去されます。

電磁干渉(EMI)ノイズはより高い周波数で発生し、電気機 器の誤動作や性能低下を引き起こします。ICは、無線周波 数干渉による出力への影響を防ぐための入力EMIフィルタ を備えています。受動デバイスで構成されたEMIフィルタは、 より高い周波数に対して大幅に高いインピーダンスを示し ます。

図4. IOUTSINKとVSS RIPPLEの関係(CFLY = 0.022µF、CHOLD =  $C_{FILT} = 0.1 \mu F$

図5. IOUTSINKとVSS RIPPLEの関係(CFLY = 0.047µF、CHOLD =  $C_{FILT} = 0.1 \mu F$

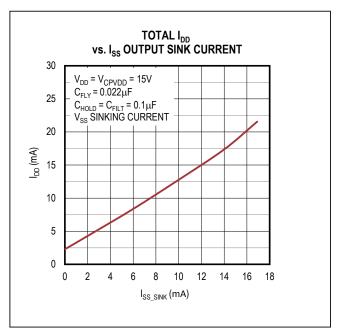

図6. 総消費電流とISINKの関係

#### 真のゼロ出力アーキテクチャ

MAX44267は、大部分のオペアンプと比べて独自性があります。MAX44267は、両方のアンプに共通の負電圧レール(V<sub>SS</sub>)を生成するチャージポンプを内蔵しています。これによって、単一の正電源のみによる給電で、アンプの入力および出力範囲が0Vを大幅に下回ることが可能です。V<sub>SS</sub>出力は、両方のアンプおよびその出力負荷電流に給電します。V<sub>SS</sub>を外部回路の給電に使用することができますが、追加の負荷電流はチャージポンプにとって追加の負荷となります。この内部で生成される負電源によって、想定外の経路に(特に最近のほぼすべてのICが備えている静電気放電保護回路を介して)電流が流れる可能性があります(図7)。

#### ほぼゼロのソースインピーダンス

負の電圧発生器は、有限の電流シンク能力を備えています( $C_{FLY} = 0.022 \mu F$ 、 $C_{HOLD} = C_{FILT} = 0.1 \mu F$ の場合、約15mA (typ))。1つまたは両方のアンプの組合せの出力シンク電流によってデバイスに過負荷がかかった場合、

安定化が失われ、負方向の出力振幅が制限されます。 さらに、安定化が失われた状態で、入力が強制的に負レー ルに向かって駆動されると、MAX44267はラッチアップ 状態になります。このラッチアップは非破壊的で、障害状態が除去されるとデバイスは回復します。

MAX44267は、各出力チャネルに対して $5k\Omega$ の負荷で仕様が規定されています。この場合、最大出力負荷電流はジェネレータの過負荷を大幅に下回るため、デバイスはラッチアップしません。さらに高い負荷を駆動することは可能ですが、総出力シンク電流(両方のチャネルの組合せ)が15mAのピークを超えないようにしてください(詳細については、「標準動作特性」の「 $V_{OUT}$  LOW vs. Output Sink Current ( $V_{OUT}$  LOWと出力シンク電流の関係)」のグラフを参照)。出力の限界に近づく可能性のある負荷を駆動する場合は、入力をハイインピーダンスソースとするか、または保護用の $5k\Omega$ 直列抵抗を追加することが推奨されます。

図7. MAX44267への過負荷によってラッチアップが発生する可能性

## アプリケーション情報

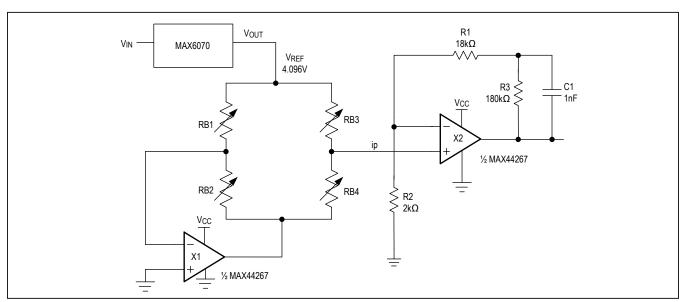

#### 計測アンプを使用しないブリッジ測定構成

MAX44267は低入力オフセット電圧と低ノイズを特長とす るため、バイアス調整される歪みゲージに最適です(図8)。 歪みゲージブリッジは基準ソースによるバイアスが最も一 般的で、その場合ブリッジからの出力は基準電圧の約半 分になります。グランド付近にバイアスする場合、負の電 源が利用可能である必要があります。そのため、ブリッジ を基準電圧の2倍でバイアスし、中央をOVにします(アン プX1のオフセット電圧内)。ブリッジにかかる電圧を2倍 にすると感度が2倍になりますが、もちろん、流れる電流 も2倍になるという欠点があります。

この場合ブリッジの中央は強制的にOVになるため、歪み が加えられていない場合、ノード[ip]も0Vになり、ブリッ ジのゼロ歪みの較正範囲内になります。ゼロバイアスポイン トを制御した後、アプリケーションはデュアルMAX44267 内の第2のアンプを使用して、コモンモード誤差による出 力の飽和という通常のリスクなしに、非常に大きい、ダイ レクト結合された利得を得ることができます。

図に示したフルブリッジは、通常はフルスケールがバイア ス電圧の約0.1%の差動出力を生成します。バイアス電圧 を2倍にすると、感度が2倍になり、高利得アンプのコモン モード誤差も除去されます。歪みの増大とともにRB3と RB2の抵抗値が減少し、RB1とRB4の抵抗値が増大する ように設定されている場合、出力でのフルスケール出力は +819.2mVになります。 コンデンサC1のサイズの選択に よって、不要な帯域幅とそれに伴うノイズを排除すること ができます。ブリッジが各レッグに10kΩの抵抗値を使用 している場合、ノイズは約24nV√Hzになり、それが信号と

ともに100倍に増幅されて2.4µVになります。帯域幅を 100Hzまでに維持した場合、これはわずか24µVRMSまた は約300µV<sub>P-P</sub>であり、SN比は68dBになります。もちろん、 適切な長さの時間にわたって読み値を平均することによっ てこれを改善することが可能で、通常は60Hz (50Hz)の サイクルの整数倍にすることで分解能の向上と60Hzの電 源系に対する感度の低下の両方が提供されます。

#### レイアウトのガイドライン

MAX44267は超低オフセット電圧およびノイズを特長と するため、ゼーベック効果による誤差が大きくなります。 そのため、最高の性能を実現するには、以下のレイアウト のガイドラインに従ってください。

2つの異なる金属の接合部での温度勾配を避けてください。 PCBで異なる金属が使用される最も一般的な場所は、 はんだと部品のリード間およびはんだと基板トレース間 です。異なる金属は局所的な熱電対を作ります。基板全体 の温度にばらつきがあると、はんだ接合部でのゼーベック 効果によって追加のオフセットが発生します。ゼーベック 効果を最小限に抑えるため、可能な場合はアンプを基板 上の潜在的熱源から遠ざけて配置してください。抵抗は両 端が等しく加熱されるように向きを決めてください。熱電 気接合部の種類と数が常に同じになるように入力信号経路 を整合させるのは良い手法です。たとえば、ダミーの $0\Omega$ 抵抗を使用して、信号経路の実際の抵抗による熱電気発 生源を相殺する向きに配置することを検討してください。 PCB全体にグランドプレーンを充填することが推奨され ます。グランドプレーンは熱の均一な分散を確保し、ゼー ベック効果によってオフセット電圧が劣化する可能性を 低減します。

図8. 計測アンプを使用しないブリッジ測定構成

# 標準アプリケーション回路

## 表1. 標準動作回路の選択ガイド

| PART NO. | FUNCTION            | VOLTAGE SUPPLY RANGE (V) | INPUT VOLTAGE RANGE (V) |

|----------|---------------------|--------------------------|-------------------------|

| MAX44267 | Precision amplifier | +4.5 to +15.5            | -12.0 to +13.5          |

| MAX14778 | 4:1 mux             | +3 to +5.5               | ±25                     |

| MAX14762 | 2-channel switch    | +3 to +5.5               | ±25                     |

| MAX11167 | 16-bit ADC          | +5                       | ±5                      |

## 型番

| PART         | TEMP RANGE       | PIN-PACKAGE |  |

|--------------|------------------|-------------|--|

| MAX44267AUD+ | -40°C to + 125°C | 14 TSSOP    |  |

<sup>+</sup>は鉛(Pb)フリー/RoHS準拠パッケージを表します。

# チップ情報

PROCESS: BiCMOS

## パッケージ

最新のパッケージ図面情報およびランドパターン(フットプリント)は www.maximintegrated.com/jp/packagingを参照してください。 なお、 パッケージコードに含まれる[+]、[#]、または[-]はRoHS対応状 況を表したものでしかありません。パッケージ図面はパッケージ そのものに関するものでRoHS対応状況とは関係がなく、図面によって パッケージコードが異なることがある点を注意してください。

| パッケージ<br>タイプ | パッケージ<br>コード | 外形図No.         | ランド<br>パターンNo. |

|--------------|--------------|----------------|----------------|

| 14 TSSOP     | U14+1        | <u>21-0066</u> | <u>90-0113</u> |

### 改訂履歴

| 版数 | 改訂日   | 説明      | 改訂ページ |

|----|-------|---------|-------|

| 0  | 11/14 | 初版      | _     |

| 1  | 2/15  | 「概要」を更新 | 1     |

マキシム・ジャパン株式会社 〒141-0032 東京都品川区大崎1-6-4 大崎ニューシティ 4号館 20F TEL: 03-6893-6600

Maxim Integratedは完全にMaxim Integrated製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。Maxim Integratedは随時予告なく回路及び仕様を変更する権利を留保します。「Electrical Characteristics (電気的特性)」の表に示すパラメータ値(min、maxの各制限値)は、このデータシートの他の場所で引用している値より優先されます。