## 概要

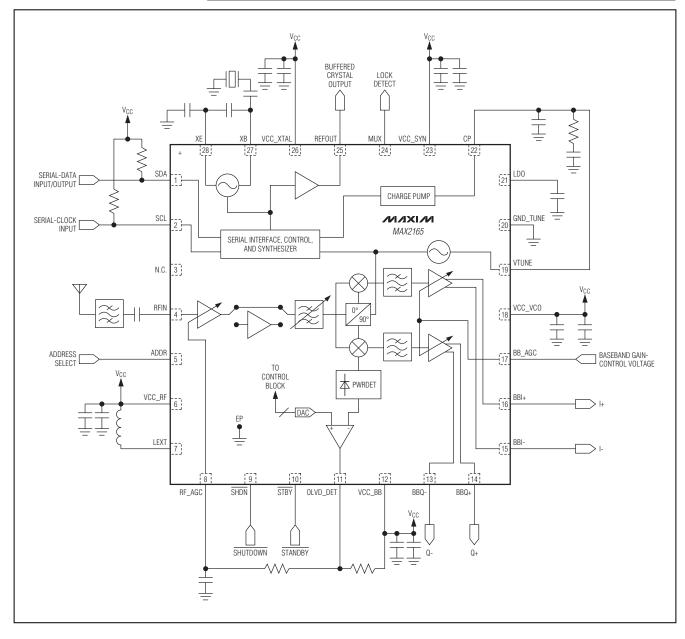

ダイレクトコンバージョンチューナIC MAX2165は、 携帯型のディジタルビデオ放送(DVB-H)アプリケー ション用に設計されています。このチューナは470MHz~ 780MHzの入力周波数範囲に対応し、I/Qベースバンド インタフェースを備えています。

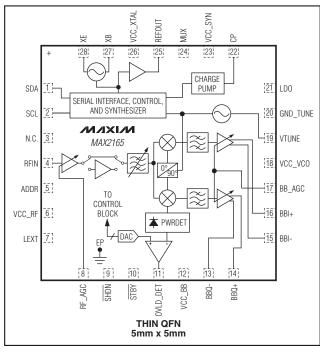

MAX2165のダイレクトコンバージョンアーキテクチャ は、IF-SAWフィルタが不要であり、部品コストを削減 することができます。このデバイスの設計には、可変 利得の低ノイズアンプ(LNA)、ノッチフィルタ、RF トラッキングフィルタ、直交ミキサ、電力検出器、 プログラマブルなベースバンドローパスチャネル選択 フィルタ、ベースバンド可変利得アンプ(VGA)、DC オフセット補正回路、および完全なフラクショナルN 周波数シンセサイザが内蔵されています。このデバイス は2線式I<sup>2</sup>C対応シリアルインタフェースを通してプロ グラムすることができます。

MAX2165は、調節可能なノッチフィルタを内蔵して います。このフィルタは、大きなセルラ信号が存在する 条件下での動作に対応するため、830MHz~950MHz の周波数範囲の干渉信号を除去するよう設計されてい ます。プログラマブルなベースバンドチャネル選択フィ ルタによって、7MHzおよび8MHz各チャネルでの動作 が可能です。ディジタルDCオフセット補正回路は、 立上り時間遅延を最小化することによって時分割動作 をサポートします。フラクショナルNシンセサイザが VCOのロック時間を短縮し、隣接位相ノイズが最小化 されるため、多くの計算量を必要とする位相ノイズ低減 アルゴリズムが不要となります。

MAX2165は、エクスポーズドパッドを備えた5mm x 5mm x 0.8mmの小型28ピンTQFNパッケージで提供 されます。このデバイスは、-40℃~+85℃の拡張温度 範囲での動作が保証されています。

## アプリケーション \_\_\_

DVB-Hハンドヘルドレシーバ

DVB-Tポータブルデバイス

DMB-T/Hポータブルデバイス

ISDB-Tレシーバ(13セグメント)

## 特長

- ◆ 単一電源電圧:+2.85V、消費電流:93mA (typ)

- ◆ 平均消費電力:21mW (tvp) (8%デューティサイクル時)

- ◆ ダイレクトコンバージョンアーキテクチャの採用で IF-SAWフィルタが不要

- ◆ セルラ妨害信号存在下での動作を可能にする RF調節可能ノッチフィルタ内蔵

- ◆ DCオフセット補正回路内蔵

- ♦ 最大-7dBmのセルラ妨害信号存在下での動作を 可能にするRFノッチフィルタ内蔵

- ◆ 拡張UHFバンド動作

- ♦ 5mm x 5mm x 0.8mmの28ピンTOFNパッケージ

### 型番

| PART        | TEMP RANGE     | PIN-PACKAGE |  |  |

|-------------|----------------|-------------|--|--|

| MAX2165ETI+ | -40°C to +85°C | 28 TQFN-EP* |  |  |

+は鉛(Pb)フリー/RoHS準拠パッケージを表します。

\*EP = エクスポーズドパッド

## ピン配置/ファンクションダイアグラム

## **ABSOLUTE MAXIMUM RATINGS**

| All V <sub>CC</sub> Pins to GND    | 0.3V to +3.6V                    | Operating Temperature Range       |

|------------------------------------|----------------------------------|-----------------------------------|

| GND_TUNE to GND                    | 0.3V to +0.3V                    | Junction Temperature              |

| All Other Pins to GND              | 0.3V to (V <sub>CC</sub> + 0.3V) | Storage Temperature Range         |

| BBI_, BBQ_ Short Circuit to Ground | DurationIndefinite               | Lead Temperature (soldering, 10s) |

| Maximum RF Input Power             | +13dBm                           | , , ,                             |

| Continuous Power Dissipation (TA = | +70°C)                           |                                   |

| 28-Pin Thin QFN (derate 34.5mW/    | °C above +70°C)2758mW            |                                   |

.....-40°C to +85°C .....+150°C .....-65°C to +150°C .....+300°C

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**CAUTION!** ESD SENSITIVE DEVICE

#### DC ELECTRICAL CHARACTERISTICS

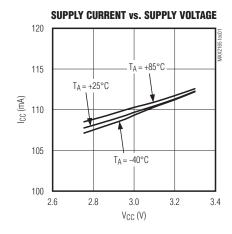

(MAX2165 EV kit, V<sub>CC</sub> = +2.75V to +3.3V, V<sub>RF</sub> A<sub>GC</sub> = V<sub>BB</sub> A<sub>GC</sub> = 2.3V (maximum gain), no RF input signals at RFIN, default register settings, TA = -40°C to +85°C, unless otherwise noted. Typical values are at V<sub>CC</sub> = +2.85V, TA = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                               | CONDITIONS                                            | MIN                      | TYP                        | MAX                       | UNITS  |

|-----------------------------------------|-------------------------------------------------------|--------------------------|----------------------------|---------------------------|--------|

| SUPPLY VOLTAGE AND CURF                 | RENT                                                  |                          |                            |                           |        |

| Supply Voltage                          |                                                       | 2.75                     |                            | 3.30                      | V      |

| Supply Current                          | LNASW = 1 (RF LNA on)                                 |                          | 109                        | 134                       | mA     |

| варрту Сапепі                           | LNASW = 0 (RF LNA off)                                |                          | 93                         | 116                       | ] IIIA |

| Shutdown Current                        |                                                       |                          |                            | 20                        | μΑ     |

| Gain-Control Voltage                    | Required to obtain full range of RF and baseband gain | 0.4                      |                            | 2.3                       | V      |

| RF_AGC and BB_AGC Input<br>Bias Current | V <sub>AGC</sub> at +0.4V and +2.3V                   | -50                      |                            | +50                       | μA     |

| SERIAL INTERFACE                        |                                                       | •                        |                            |                           |        |

| Input Logic-Level Low                   |                                                       |                          |                            | 0.3 x<br>V <sub>C</sub> C | V      |

| Input Logic-Level High                  |                                                       | 0.7 x<br>V <sub>CC</sub> |                            |                           | V      |

| Input Hysteresis                        |                                                       |                          | 0.05 x<br>V <sub>C</sub> C |                           | V      |

| SDA, SCL Input Current                  |                                                       | -10                      |                            | +10                       | μΑ     |

| Output Logic-Level Low                  | I <sub>SINK</sub> = 0.3mA                             |                          |                            | 0.4                       | V      |

| Output Logic-Level High                 | ISOURCE = 0.3mA                                       | V <sub>CC</sub> - 0.4    |                            |                           | V      |

## **AC ELECTRICAL CHARACTERISTICS**

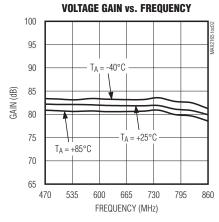

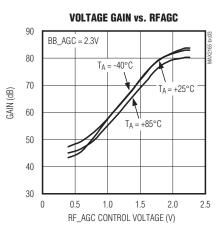

(MAX2165 EV kit, V<sub>CC</sub> = +2.75V to +3.3V, V<sub>RF AGC</sub> = V<sub>BB AGC</sub> = 2.3V (maximum gain), V<sub>OUT</sub> = 1V<sub>P-P</sub>, 75Ω system impedance, registers set according to the specified default register conditions, TA = -40°C to +85°C, unless otherwise noted. Typical values are at VCC = +2.85V, TA = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                          | CONDITIONS                                                                   | MIN | TYP | MAX | UNITS |  |  |

|----------------------------------------------------|------------------------------------------------------------------------------|-----|-----|-----|-------|--|--|

| OVERALL PERFORMANCE (RF INPUT TO BASEBAND OUTPUTS) |                                                                              |     |     |     |       |  |  |

| Operating Frequency Range                          | Meets specified performance                                                  | 470 |     | 783 | MHz   |  |  |

|                                                    | Operates with derated performance (Note 2)                                   | 470 |     | 832 | IVIHZ |  |  |

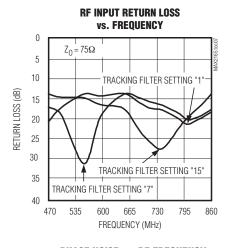

| Input Return Loss                                  | $50\Omega$ system, worst case across band, any gain-control setting (Note 3) | 7   |     |     | dB    |  |  |

## **AC ELECTRICAL CHARACTERISTICS (continued)**

(MAX2165 EV kit,  $V_{CC}$  = +2.75V to +3.3V,  $V_{RF\_AGC}$  =  $V_{BB\_AGC}$  = 2.3V (maximum gain),  $V_{OUT}$  = 1V<sub>P-P</sub>, 75 $\Omega$  system impedance, registers set according to the specified default register conditions,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{CC}$  = +2.85V,  $T_A$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                               | CONI                                                  | DITIONS                                   | MIN    | TYP                 | MAX  | UNITS            |  |  |

|-----------------------------------------|-------------------------------------------------------|-------------------------------------------|--------|---------------------|------|------------------|--|--|

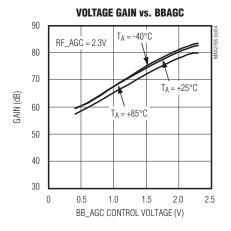

|                                         |                                                       | Maximum gain                              | 74     | 82                  |      |                  |  |  |

| Voltage Gain                            | $Z_{SOURCE} = 75\Omega, Z_{LOAD} > 1k\Omega$          | Minimum gain on (LNASW = 1)               |        | 23                  | 29   | dB               |  |  |

| RF Gain-Control Range                   | $0.4V \le V_{RF\_AGC} \le 2.3V$                       |                                           | 29     | 34                  |      | dB               |  |  |

| Baseband Gain-Control Range             | 0.4V ≤ V <sub>BB_AGC</sub> ≤ 2.3V                     |                                           | 21     | 25                  |      | dB               |  |  |

| LNA Gain Step                           | Gain change caused by sw 1) and off (LNASW = 0)       | itching RF LNA on (LNASW =                | 13.5   | 17                  |      | dB               |  |  |

| LNA Gain Step Phase Change              | Phase change caused by st<br>= 1) and off (LNASW = 0) | witching RF LNA on (LNASW                 |        | 10                  |      | degrees          |  |  |

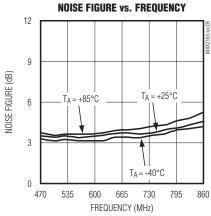

| Noise Figure (Note 3)                   | At 470MHz                                             |                                           |        | 3.8                 | 6.5  | dB               |  |  |

| Noise Figure (Note 3)                   | At 783MHz                                             |                                           |        | 4.0                 | 6.5  | uБ               |  |  |

| Input IP2 (Note 4)                      | Maximum gain                                          |                                           | 0      | 9                   |      | dBm              |  |  |

| input ii 2 (Note 4)                     | 23dB gain reduction                                   |                                           |        | 26                  |      | иып              |  |  |

| Input IP3 (Note 5)                      | Maximum gain                                          |                                           | -20 -4 |                     |      | dBm              |  |  |

| input ir 3 (Note 3)                     | 23dB gain reduction                                   |                                           | 17     |                     | aBm  |                  |  |  |

| In-Band Input P <sub>1dB</sub>          | Maximum gain (Note 6)                                 | -22                                       |        |                     | dBm  |                  |  |  |

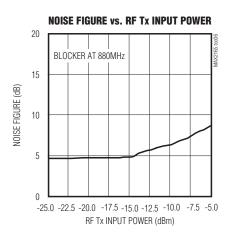

| Cellular Blocker Desensitization        | Cellular Tx blocker gain con                          | npression                                 |        | 1.2                 | 3    | dB               |  |  |

| (Note 7)                                | Cellular Tx blocker noise fig                         | ure rise                                  |        | 3                   |      | ив               |  |  |

| In-Band IM3                             | Two tones (782.8MHz and 7 baseband filter, 780MHz LC  | 782.3MHz) within passband of of prequency |        | -55                 | -40  | dBc              |  |  |

|                                         | 170MHz to 960MHz RF inpu                              | it frequency                              |        | < -60               |      | -ID -            |  |  |

| RF Beats Converted to Output            | 960MHz to 1400MHz RF inp                              | out frequency                             |        | < -60               |      | dBc              |  |  |

| RF Isolation                            | DC to 50MHz, RF input to b desired channel            | aseband outputs relative to               |        | -60                 |      | dBc              |  |  |

| I/Q Output Swing                        | $Z_{LOAD} = 10k\Omega II 10pF$                        |                                           |        | 0.5                 | 1    | V <sub>P-P</sub> |  |  |

| I/Q DC Voltage                          | I+, I-, Q+, Q- outputs to gro                         | und                                       |        | V <sub>CC</sub> / 2 |      | V                |  |  |

| 1/0.0                                   | Phase error                                           |                                           |        |                     | 2    | degrees          |  |  |

| I/Q Quadrature Accuracy                 | Amplitude error                                       |                                           | -1.5   |                     | +1.5 | dB               |  |  |

|                                         | 50MHz to 470MHz                                       |                                           |        | -38                 | -33  |                  |  |  |

| Spurious Emissions at RF Input (Note 3) | 470MHz to 878MHz                                      |                                           | -52    | -35                 | dBmV |                  |  |  |

|                                         | 878MHz to 1732MHz                                     |                                           |        | -49                 | -35  | 35               |  |  |

|                                         | Spur at four times Rx freque fSPUR = 1896MHz          | ency, tested at f <sub>LO</sub> = 474MHz, |        | -58                 | -51  | dBm              |  |  |

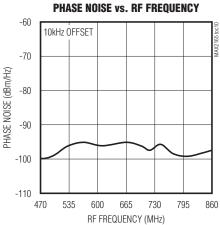

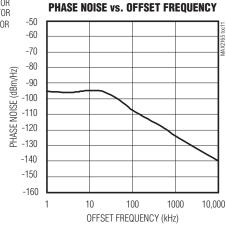

|                                         | 1kHz offset to 10kHz (Note 3                          | 3)                                        | -86    | -96                 |      |                  |  |  |

| Closed-Loop Phase Noise                 | 1MHz offset (Note 3)                                  |                                           | -108   | -126                |      | dBc/Hz           |  |  |

|                                         | > 10MHz offset                                        | -14                                       |        | -140                |      | 1                |  |  |

## **AC ELECTRICAL CHARACTERISTICS (continued)**

(MAX2165 EV kit,  $V_{CC}$  = +2.75V to +3.3V,  $V_{RF\_AGC}$  =  $V_{BB\_AGC}$  = 2.3V (maximum gain),  $V_{OUT}$  = 1V<sub>P-P</sub>, 75 $\Omega$  system impedance, registers set according to the specified default register conditions,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{CC}$  = +2.85V,  $T_A$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                | CONDITIONS                                                                                 | MIN | TYP         | MAX | UNITS             |  |

|------------------------------------------|--------------------------------------------------------------------------------------------|-----|-------------|-----|-------------------|--|

| Power-Up Time                            | Shutdown to full operation, VCO settled to the Rx frequency, DC offset calibrated (Note 8) |     | < 1         | 20  | ms                |  |

| BASEBAND FILTERS                         |                                                                                            |     |             |     |                   |  |

|                                          | Lower corner (Note 9)                                                                      |     | 0 or<br>200 |     | Hz                |  |

| Passband Cutoff Attenuation              | Upper corner at 3.85MHz (UHF mode), T <sub>A</sub> = +25°C                                 |     | 0.9         | 5   |                   |  |

|                                          | Upper corner at 3.35MHz (VHF mode), T <sub>A</sub> = +25°C                                 |     | 2.7         | 5   | dB                |  |

| Amplitude Ripple                         | T <sub>A</sub> = +25°C                                                                     |     | 0.5         | 1.5 | dB <sub>P-P</sub> |  |

| Group Delay Ripple                       |                                                                                            |     | 150         |     | µsp-p             |  |

| Group Delay Matching                     |                                                                                            |     | 5           |     | ns                |  |

|                                          | 4.75MHz (VHF mode) (Note 11)                                                               | 23  |             |     |                   |  |

| Rejection Ratio (Note 10)                | 5.25MHz (UHF mode) (Note 11)                                                               | 23  |             |     |                   |  |

|                                          | 14.5MHz (VHF and UHF mode) (Note 12)                                                       | 59  | 75          |     | dB                |  |

|                                          | > 16.2MHz                                                                                  |     | 84          |     | 1                 |  |

| FRACTIONAL SYNTHESIZER                   |                                                                                            |     |             |     | •                 |  |

| RF N-Divider Ratio                       |                                                                                            | 7   |             | 251 |                   |  |

| RF R-Divider Ratio                       |                                                                                            | 1   |             | 2   |                   |  |

| Fractional Ratio                         | Length of fractional accumulator (Note 13)                                                 |     | 20          |     | bits              |  |

| Integer Spurs                            | Worst-case spur inside baseband filter bandwidth                                           |     | -60         |     | dBc               |  |

| Settling Time                            | 35MHz step, settled to within 100Hz frequency error/20° phase error                        |     | 200         |     | μs                |  |

|                                          | ICP = 0                                                                                    |     | 0.6         |     |                   |  |

| Charge-Pump Current                      | ICP = 1                                                                                    |     | 1.2         |     | - mA              |  |

| Charge-Pump Leakage                      |                                                                                            | -10 |             | +10 | μΑ                |  |

| REFERENCE OSCILLATOR                     |                                                                                            |     |             |     |                   |  |

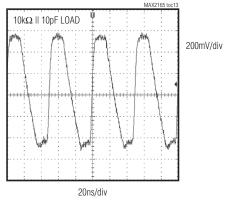

| Reference Frequency                      |                                                                                            | 4   |             | 26  | MHz               |  |

| Reference Buffer Output Voltage<br>Swing | 10kΩ II 10pF load                                                                          | 0.5 | 1           |     | V <sub>P-P</sub>  |  |

| Input Impedance                          | When used as a passive input for an external reference oscillator                          |     | 12          |     | kΩ                |  |

| Input Voltage                            | When used as a passive input for an external reference oscillator                          | 100 |             | 600 | mV <sub>RMS</sub> |  |

| OVERLOAD DETECTOR                        |                                                                                            |     |             |     |                   |  |

| Attack-Point Accuracy                    |                                                                                            |     | ±2.5        |     | dB                |  |

| Attack-Point Increment                   | 3-bit DAC, change per LSB step                                                             |     | 2.5         |     | dB                |  |

|                                          | Detector on                                                                                | 0.1 |             |     | mA                |  |

| Detector Output Sink                     | Detector off                                                                               |     |             | 5   | μΑ                |  |

| L                                        | L                                                                                          |     |             |     | <u> </u>          |  |

## **AC ELECTRICAL CHARACTERISTICS (continued)**

(MAX2165 EV kit,  $V_{CC}$  = +2.75V to +3.3V,  $V_{RF\_AGC}$  =  $V_{BB\_AGC}$  = 2.3V (maximum gain),  $V_{OUT}$  = 1V<sub>P-P</sub>, 75 $\Omega$  system impedance, registers set according to the specified default register conditions,  $T_{A}$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{CC}$  = +2.85V,  $T_{A}$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER               | CONDITIONS                    | MIN | TYP | MAX | UNITS |

|-------------------------|-------------------------------|-----|-----|-----|-------|

| Detector Gain           |                               |     | 150 |     | V/V   |

| Detector Response Time  |                               |     | 5   |     | μs    |

| 2-WIRE SERIAL INTERFACE |                               |     |     |     |       |

| Clock Rate              | I2C fast mode, slave category |     |     | 400 | kHz   |

- Note 1: Min and max limits are guaranteed by test at T<sub>A</sub> = +25°C and are guaranteed by design and characterization at T<sub>A</sub> = -40°C and +85°C. The default register settings are not production tested. Load registers no sooner than 100μs after power-up.

- Note 2: Notch filter must be disabled by programming the TF\_NTCH[3:0] bits to 1111 to enable operation up to 832MHz. Under extreme conditions, the part can experience up to 3dB degradation in sensitivity and intermodulation distortion.

- Note 3: Guaranteed by design and characterization over the specified operating conditions. Not production tested.

- **Note 4:** UHF tones resulting in f<sub>1</sub> f<sub>2</sub> beat frequency within the baseband output. Two tones at 350MHz and 1133MHz with IM2 measured at 783MHz.

- Note 5: Two tones converted to 5.25MHz and 10.75MHz, IM3 measured at 250kHz.

- Note 6: A desired signal at PDESIRED = -78dBm is injected and downconverted to 3.75MHz. A blocker tone is injected at 10MHz higher in frequency. Specified level is blocker power at which desired output signal compresses by 1dB. T<sub>A</sub> = +25°C.

- **Note 7:** A single blocker at -7dBm with a bandwidth of less than 4MHz is injected at 880MHz with the receiver tuned to 783MHz and set to maximum gain.

- Note 8: VCO locked to within 100Hz of the Rx frequency. Wake-up initiated by toggling the SHDN pin from low to high and connecting the STBY pin to ground.

- **Note 9:** Applies to continuous DC correction operation (DVB-T mode). In DVB-H mode, optional correction hold feature allows quasi-DC-coupling.

- Note 10: Depends on 7MHz/8MHz bandwidth mode.

- **Note 11:** Equivalent to video carrier in upper adjacent channel.  $T_A = +25$ °C.

- **Note 12:** Equivalent to f<sub>NYQUIST</sub> 3.8MHz for 18.3MHz sampling rate baseband DAC.

- Note 13: Total frequency resolution is f<sub>REF</sub>/220, or approximately 20Hz with a 20MHz reference frequency.

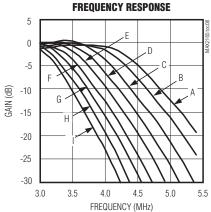

#### 標準動作特性

(MAX2165 EV kit,  $V_{CC}$  = +2.85V, default register settings,  $V_{RF\_AGC}$  =  $V_{BB\_AGC}$  = 2.3V,  $V_{IOUT}$  =  $V_{QOUT}$  = 500m $V_{P-P}$ ,  $T_A$  = +25°C, unless otherwise noted.)

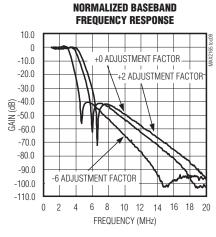

## 標準動作特性(続き)

(MAX2165 EV kit,  $V_{CC}$  = +2.85V, default register settings,  $V_{RF\_AGC}$  =  $V_{BB\_AGC}$  = 2.3V,  $V_{IOUT}$  =  $V_{QOUT}$  = 500m $V_{P-P}$ ,  $T_A$  = +25°C, unless otherwise noted.)

**NORMALIZED BASEBAND**

## 標準動作特性(続き)

(MAX2165 EV kit,  $V_{CC}$  = +2.85V, default register settings,  $V_{RF\_AGC}$  =  $V_{BB\_AGC}$  = 2.3V,  $V_{IOUT}$  =  $V_{QOUT}$  = 500mV<sub>P-P</sub>,  $T_{A}$  = +25°C, unless otherwise noted.)

# POWER-DETECTOR OUTPUT VOLTAGE vs. RF INPUT POWER

#### REFERENCE BUFFER OUTPUT SIGNAL

## 端子説明

| 端子 | 名称       | 機能                                                                                                         |

|----|----------|------------------------------------------------------------------------------------------------------------|

| 1  | SDA      | シリアルデータ入出力。プルアップ抵抗でV <sub>CC</sub> に接続する必要があります。                                                           |

| 2  | SCL      | シリアルクロック入力。プルアップ抵抗でVccに接続する必要があります。                                                                        |

| 3  | N.C.     | 接続なし。この端子はグランドに接続してください。                                                                                   |

| 4  | RFIN     | RF入力。内部で75Ωに整合されています。DCブロッキングコンデンサが必要です。                                                                   |

| 5  | ADDR     | アドレス選択入力。I <sup>2</sup> Cのスレーブアドレスを選択します。表20をご覧ください。                                                       |

| 6  | VCC_RF   | RF電源入力。低ノイズの電源に接続してください。できる限り端子の近くに配置した2200pFと 100nFのコンデンサで、PCBのグランドプレーンにバイパスしてください。                       |

| 7  | LEXT     | 外付けインダクタ接続点。39nHのインダクタでV <sub>CC</sub> に接続してください。                                                          |

| 8  | RF_AGC   | RF利得制御電圧入力。0.4V~2.3Vの電圧を受け付け、2.3VのときRF利得が最大になります。<br>この端子は、OVLD_DET出力で制御することもできます。「標準アプリケーション回路」をご覧ください。   |

| 9  | SHDN     | シャットダウン入力。すべての内部回路をディセーブルして、デバイスを低電力のシャットダウンモードに<br>するには、この端子をローに駆動してください。通常動作させる場合は、この端子をハイに駆動してください。     |

| 10 | STBY     | スタンバイ入力。チップの起動シーケンスを制御します。この端子の動作の詳細については、<br>「起動シーケンス」の項をご覧ください。                                          |

| 11 | OVLD_DET | 過負荷検出出力。この出力は、内蔵の電力検出器の出力電圧と、プログラマブルな内部リファレンス電圧の間の誤差信号を出力します。この出力をRF_AGC入力に接続して、閉ループのRF自動利得制御を実行することも可能です。 |

| 12 | VCC_BB   | ベースバンド電源入力。低ノイズ電源に接続してください。できる限り端子の近くに配置した<br>1000pFと100nFのコンデンサで、PCBのグランドプレーンにバイパスしてください。                 |

| 13 | BBQ-     | 反転直交ベースバンド出力                                                                                               |

## 端子説明(続き)

| 端子 | 名称       | 機能                                                                                                                                               |

|----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 14 | BBQ+     | 非反転直交ベースバンド出力                                                                                                                                    |

| 15 | BBI-     | 反転同相ベースバンド出力                                                                                                                                     |

| 16 | BBI+     | 非反転同相ベースバンド出力                                                                                                                                    |

| 17 | BB_AGC   | ベースバンド利得制御電圧入力。0.4V~2.3Vの電圧を受け付け、2.3Vのときベースバンド利得が<br>最大になります。                                                                                    |

| 18 | VCC_VCO  | VCO電源入力。低ノイズの電源電圧に接続してください。できる限り端子の近くに配置した1000pFと100nFのコンデンサで、PCBのグランドプレーンにバイパスしてください。                                                           |

| 19 | VTUNE    | VCO同調電圧入力。PLLループフィルタの出力に接続してください。                                                                                                                |

| 20 | GND_TUNE | VCO同調電圧グランド。PCBのグランドプレーンに接続してください。                                                                                                               |

| 21 | LDO      | VCOリニアレギュレータノイズバイパス。できる限り端子の近くに配置した470nFのコンデンサで、<br>PCBのグランドプレーンにバイパスしてください。                                                                     |

| 22 | СР       | チャージポンプ出力。PLLループフィルタの入力に接続してください。                                                                                                                |

| 23 | VCC_SYN  | シンセサイザ電源入力。低ノイズの電源電圧に接続してください。できる限り端子の近くに配置した 1000pFと100nFのコンデンサで、PCBのグランドプレーンにバイパスしてください。                                                       |

| 24 | MUX      | 多重化出力ライン。各種のテスト機能の出力であり、PLLロック検出インジケータとして使用することもできます。詳細については表9をご覧ください。PLLロック検出器として使用する場合、ロジックのハイはPLLがロックされていないことを示し、ロジックのローはPLLがロックされていることを示します。 |

| 25 | REFOUT   | リファレンスバッファ出力。デモジュレータ用のクロックリファレンスとして使用可能なバッファ付き水晶発振器信号を供給します。DCブロッキングコンデンサが必要です。                                                                  |

| 26 | VCC_XTAL | 水晶発振器電源入力。低ノイズの電源電圧に接続してください。できる限り端子の近くに配置した<br>1000pFと100nFのコンデンサで、PCBのグランドプレーンにバイパスしてください。                                                     |

| 27 | ХВ       | リファレンス入力。負荷整合コンデンサを通して並列共振モードの水晶に接続するか、またはリファレンス発振器に接続してください。                                                                                    |

| 28 | XE       | リファレンス発振器フィードバック入力。チップ上のリファレンス発振器を使用する場合、容量性フィード<br>バック回路網に接続してください。外部リファレンスを使用する場合は、未接続のままにしてください。                                              |

| EP | EP       | エクスポーズドパッド。インピーダンスを最小にするために、ボードのグランドプレーンに均一に<br>はんだ付けしてください。                                                                                     |

## 詳細

#### レジスタの説明

MAX2165は、15個のプログラマブルなレジスタと、3個の読取り専用レジスタを内蔵しています。レジスタの構成については、表1をご覧ください。表1のレジスタ構成には、すべてのレジスタについて各ビットの名称およびビットの用途に関する情報が示してあります。各ビットの名称の下にUと標記されている場合、特定のアプリケーションの要件に合わせてそのビットの値をユーザが定義することを示します。0または1と標記され

ている場合、正しく動作させるためにはそのビットを定義通り0または1の値に設定する必要があることを示します。これらのビットに他の値をプログラムした場合の動作はテストも保証もされておらず、ファクトリ/ベンチ評価の場合にのみ使用してください。一般的なアプリケーションの場合は、常に動作が定義されている状態にプログラムしてください。

各レジスタの詳しい説明は、表2~19をご覧ください。 すべてのレジスタは起動から100µs後に書き込む必要 があり、起動後100µs以内に書き込んではいけません。

## 表1. レジスタ構成\*

| DE010755                   | DE010755 | REGISTER S | SETTINGS | MSB           |               |               |               |              |              |              | LSB          |

|----------------------------|----------|------------|----------|---------------|---------------|---------------|---------------|--------------|--------------|--------------|--------------|

| REGISTER<br>NAME           | REGISTER | OPERATION  | DEFAULT  |               |               |               | DAT           | A BYTE       |              |              |              |

| NAME                       | ADDRESS  | DEFINED    | (POR)    | D7            | D6            | D5            | D4            | D3           | D2           | D1           | D0           |

| N-Divider Integer          | 0x00     | _          | H17      | N7<br>U       | N6<br>U       | N5<br>U       | N4<br>U       | N3<br>U      | N2<br>U      | N1<br>U      | N0<br>U      |

| N-Divider Frac2            | 0x01     | _          | H18      | X<br>0        | X<br>0        | X<br>0        | FRAC<br>U     | F19<br>U     | F18<br>U     | F17<br>U     | F16<br>U     |

| N-Divider Frac1            | 0x02     | _          | H00      | F15<br>U      | F14<br>U      | F13<br>U      | F12<br>U      | F11<br>U     | F10<br>U     | F9<br>U      | F8<br>U      |

| N-Divider Frac0            | 0x03     | _          | H00      | F7<br>U       | F6<br>U       | F5<br>U       | F4<br>U       | F3<br>U      | F2<br>U      | F1<br>U      | F0<br>U      |

| Tracking Filter            | 0x04     | _          | H72      | TF_NTCH3<br>U | TF_NTCH2<br>U | TF_NTCH1<br>U | TF_NTCH0<br>U | TF_BAL3<br>U | TF_BAL2<br>U | TF_BAL1<br>U | TF_BAL0<br>U |

| LNA                        | 0x05     | _          | H01      | X<br>0        | X<br>0        | X<br>0        | X<br>0        | X<br>0       | X<br>0       | X<br>0       | LNASW<br>U   |

| PLL<br>Configuration       | 0x06     | _          | H0A      | RDIV<br>U     | ICP<br>U      | CPS<br>U      | ADLY0<br>U    | ADLY0<br>U   | LFDIV2<br>U  | LFDIV1<br>U  | LFDIV0<br>U  |

| Test                       | 0x07     | _          | H08      | CP_TST2<br>0  | CP_TST1<br>0  | CP_TST0<br>0  | X<br>0        | X<br>1       | LD_MUX2<br>U | LD_MUX1<br>U | LD_MUX0<br>U |

| Shutdown                   | 0x08     | _          | H00      | X<br>0        | SHDN_REF<br>U | X<br>O        | SHDN_SYN<br>U | SHDN_RF<br>U | SHDN_BB<br>U | SHDN_PD<br>U | SHDN_BG<br>U |

| VCO Control                | 0x09     | _          | H50      | VCO1<br>U     | VCO0<br>U     | BS2<br>U      | BS1<br>U      | BS0<br>U     | VAS<br>1     | ADL<br>0     | ADE<br>0     |

| Baseband<br>Control        | 0x0A     | _          | HF3      | BB_BW3<br>U   | BB_BW2<br>U   | BB_BW1<br>U   | BB_BW0<br>U   | BB_BIA0<br>0 | PD_TH2<br>U  | PD_TH1<br>U  | PD_TH0<br>U  |

| DC Offset Control          | 0x0B     | H79        | H71      | X<br>0        | DC_DAC8       | DC_MO1<br>1   | DC_MO0<br>1   | DC_SP1<br>1  | DC_SP0<br>0  | DC_TH1<br>0  | DC_TH0<br>0  |

| DC Offset DAC              | 0x0C     | H00        | H00      | DC_DAC7<br>0  | DC_DAC6<br>0  | DC_DAC5<br>0  | DC_DAC4<br>0  | DC_DAC3<br>0 | DC_DAC2<br>0 | DC_DAC1<br>0 | DC_DAC0<br>0 |

| ROM Table<br>Address       | 0x0D     | _          | H00      | X<br>0        | FUSE_TH<br>0  | X<br>0        | WR<br>0       | TFA3<br>U    | TFA2<br>U    | TFA1<br>U    | TFA0<br>U    |

| Reserved                   | 0x0E     | H00        | H00      | X<br>0        | X<br>0        | X<br>0        | X<br>0        | X<br>0       | X<br>0       | X<br>0       | X<br>0       |

| ROM Table Data<br>Readback | 0x10     | N/A        | N/A      | TRF7          | TRF6          | TRF5          | TRF4          | TRF3         | TRF2         | TRF1         | TRF0         |

| Chip Status<br>Readback    | 0x11     | N/A        | N/A      | POR           | VASA          | VASE          | LD            | DC_LO        | DC_HI        | Х            | PD_OVLD      |

| Autotuner<br>Readback      | 0x12     | N/A        | N/A      | VCO1          | VCO0          | BS2           | BS1           | BS0          | ADC2         | ADC1         | ADC0         |

<sup>\*</sup>推奨される設定の詳細については、「レジスタの説明」の項をご覧ください。

## 表2. N分周器整数部レジスタ(アドレス: 0x00)

| BIT NAME | BIT NAME  BIT LOCATION (0 = LSB)  FUNCTION |                                                                                            |

|----------|--------------------------------------------|--------------------------------------------------------------------------------------------|

| N[7:0]   | 7–0                                        | Programs the integer value of the PLL N-divider ratio. Default integer divide value is 23. |

NIXIN

## 表3. N分周器Frac2レジスタ\* (アドレス: 0x01)

| BIT NAME | BIT LOCATION<br>(0 = LSB) | FUNCTION                                                                    |

|----------|---------------------------|-----------------------------------------------------------------------------|

| Х        | 7, 6, 5                   | Reserved. Set to 000 for normal operation.                                  |

| FRAC     | 4                         | PLL mode select:  1 = Fractional mode selected.  0 = Integer mode selected. |

| F[19:16] | 3–0                       | Sets the 4 most significant bits of the fractional PLL divider ratio.       |

<sup>\*</sup>分数の分周比をプログラムする場合は、分周比を更新する前に3個すべての分数分周器レジスタの書込みを行う必要があります。

## 表4. N分周器Frac1レジスタ\* (アドレス: 0x02)

| BIT NAME | BIT LOCATION<br>(0 = LSB) | FUNCTION                                                    |

|----------|---------------------------|-------------------------------------------------------------|

| F[15:8]  | 7–0                       | Sets bits 15 through 8 of the fractional PLL divider ratio. |

<sup>\*</sup>分数の分周比をプログラムする場合は、分周比を更新する前に3個すべての分数分周器レジスタの書込みを行う必要があります。

## 表5. N分周器Frac0レジスタ\*(アドレス:0x03)

| BIT NAME | BIT LOCATION<br>(0 = LSB) | FUNCTION                                                               |

|----------|---------------------------|------------------------------------------------------------------------|

| F[7:0]   | 7–0                       | Sets the 8 least significant bits of the fractional PLL divider ratio. |

<sup>\*</sup>分数の分周比をプログラムする場合は、分周比を更新する前に3個すべての分数分周器レジスタの書込みを行う必要があります。

## 表6. トラッキングフィルタレジスタ(アドレス: 0x04)

| BIT NAME     | BIT LOCATION<br>(0 = LSB) | FUNCTION                                                                                                                                                                                                      |

|--------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TF_NTCH[3:0] | 7–4                       | Programs the notch frequency of the internal tracking filter. Optimal values for notch frequencies of 783MHz and 725MHz can be read from the ROM table entries. See the <i>Reading the ROM Table</i> section. |

| TF_BAL[3:0]  | 3–0                       | Programs the tracking filter balun. Optimum values over frequency can be interpolated from the ROM table entries. See the <i>Reading the ROM Table</i> section.                                               |

## 表7. LNAレジスタ(アドレス: 0x05)

| BIT NAME | BIT LOCATION<br>(0 = LSB) | FUNCTION                                               |

|----------|---------------------------|--------------------------------------------------------|

| X        | 7–1                       | Reserved. Set to all zeros for normal operation.       |

| LNASW    | 0                         | LNA enable:  1 = LNA is enabled.  0 = LNA is disabled. |

## 表8. PLLコンフィギュレーションレジスタ(アドレス: 0x06)

| BIT NAME    | BIT LOCATION<br>(0 = LSB) | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDIV        | 7                         | Selects the PLL reference divider:  1 = Divide reference by 2.  0 = Divide reference by 1.                                                                                                                                                                                                                                                                                                                                                                                                     |

| ICP         | 6                         | Selects the charge-pump current:<br>1 = 1.2mA<br>0 = 0.6mA                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CPS         | 5                         | Selects how the charge-pump current is programmed:  1 = Charge-pump current is automatically programmed to the optimal setting by the VCO autotuner.  0 = Charge-pump current is set manually by programming the ICP bit.                                                                                                                                                                                                                                                                      |

| ADLY[1:0]   | 4, 3                      | Sets the VCO autoselect wait time: $00 = ~200\mu s$ $01 = ~400\mu s$ $10 = ~800\mu s$ $11 = ~1600\mu s$                                                                                                                                                                                                                                                                                                                                                                                        |

| LF_DIV[2:0] | 2, 1, 0                   | Sets the prescaler for internal low-frequency clocks; program these bits so the crystal frequency divided by the prescaler value is equal to 2MHz:  000 = Divide by 8 (for 16MHz crystals).  001 = Divide by 9 (for 18MHz crystals).  010 = Divide by 10 (for 20MHz crystals).  011 = Divide by 11 (for 22MHz crystals).  100 = Divide by 12 (for 24MHz crystals).  101 = Divide by 13 (for 26MHz crystals).  110 = Divide by 14 (for 28MHz crystals).  111 = Divide by 2 (for 4MHz crystals). |

## 表9. テストレジスタ(アドレス: 0x07)

| BIT NAME    | BIT LOCATION<br>(0 = LSB) | FUNCTION                                                                                                                                                                                                                                 |

|-------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CP_TST[2:0] | 7, 6, 5                   | Charge-pump test modes:  000 = Normal operation.  100 = Force charge pump into low-impedance state.  101 = Force charge-pump source current.  110 = Force charge-pump sink current.  111 = Force charge pump into high-impedance state.  |

| Х           | 4, 3                      | Reserved. Set to 01 for normal operation.                                                                                                                                                                                                |

| LD_MUX[2:0] | 2, 1, 0                   | Selects which signal is output to the MUX pin:  000 = PLL lock indicator (normal operation).  001 = N-divider output (after divide by 2).  010 = R-divider output (after divide by 2).  011 = Factory use only.  1XX = Factory use only. |

## 表10. シャットダウンレジスタ(アドレス: 0x08)

| BIT NAME | BIT LOCATION<br>(0 = LSB) | FUNCTION                                                                                                                                                                                                                                                                                                                                                                   |

|----------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Х        | 7                         | Reserved. Set to 0 for normal operation.                                                                                                                                                                                                                                                                                                                                   |

| SHDN_REF | 6                         | Crystal-oscillator buffer shutdown control:  1 = Buffered crystal-oscillator output is disabled.  0 = Buffered crystal-oscillator output is enabled.  Note: The crystal oscillator is activated by either the SHDN_SYN bit or the SHDN_REF bit. If either bit is 0, the crystal oscillator is enabled. If both are 1, the crystal oscillator is disabled.                  |

| X        | 5                         | Reserved. Set to 0 for normal operation.                                                                                                                                                                                                                                                                                                                                   |

| SHDN_SYN | 4                         | PLL shutdown control:  1 = PLL is disabled.  0 = PLL is enabled.  Note: The crystal oscillator is activated by either the SHDN_SYN bit or the SHDN_REF bit. If either bit is 0, the crystal oscillator is enabled. If both are 1, the crystal oscillator is disabled.                                                                                                      |

| SHDN_RF  | 3                         | RF front-end shutdown control:  1 = RF circuits are disabled.  0 = RF circuits are enabled.                                                                                                                                                                                                                                                                                |

| SHDN_BB  | 2                         | Mixer, baseband filters, and baseband variable-gain amplifiers (VGA) shutdown control:  1 = Mixer, baseband filters, and baseband VGA are disabled.  0 = Mixer, baseband filters, and baseband VGA are enabled.                                                                                                                                                            |

| SHDN_PD  | 1                         | Baseband power-detector shutdown control:  1 = Baseband power detector is disabled.  0 = Baseband power detector is enabled.                                                                                                                                                                                                                                               |

| SHDN_BG  | 0                         | Main bias shutdown control:  1 = Main bias circuits are disabled.  0 = Main bias circuits are enabled.  Note: The main bias circuits can and will be shut down once all other blocks are shut down (all bits in the Shutdown register are set to 1, and the VCO[1:0] bits in the VCO Control register and the DC_MO[1:0] in the DC Offset Control register are set to 00). |

## 表11. VCO制御レジスタ(アドレス: 0x09)

| BIT NAME | BIT LOCATION<br>(0 = LSB) | FUNCTION                                                                                                                                                                                                                                                                                                                                                 |

|----------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCO[1:0] | 7, 6                      | Controls which VCO is activated when using manual VCO programming mode:  00 = VCO disabled.  01 = Select VCO 0 (lowest frequency VCO).  10 = Select VCO 1.  11 = Select VCO 2 (highest frequency VCO).                                                                                                                                                   |

| SB[2:0]  | 5, 4, 3                   | Selects which VCO sub-band is activated when using manual VCO programming mode:  000 = Select sub-band 0 (lowest frequency sub-band).  001 = Select sub-band 1.  010 = Select sub-band 2.  011 = Select sub-band 3.  100 = Select sub-band 4.  101 = Select sub-band 5.  110 = Select sub-band 6.  111 = Select sub-band 7 (highest frequency sub-band). |

| VAS      | 2                         | Enables or disables the VCO autotuner function:  1 = VCO and VCO sub-band are programmed automatically by the autotuner.  0 = VCO and VCO sub-band selection is controlled manually by programming the VCO[1:0] and SB[2:0] bits.                                                                                                                        |

| ADL      | 1                         | Enables or disables the VCO tuning voltage ADC latch when the VCO autotuner is disabled (VAS = 0):  1 = Latches the ADC output.  0 = Disables the ADC latch.                                                                                                                                                                                             |

| ADE      | 0                         | Enables or disables the VCO tuning voltage ADC read when the VCO autotuner is disabled (VAS = 0):  1 = Enables ADC read.  0 = Disables ADC read.                                                                                                                                                                                                         |

# 表12. ベースバンド制御レジスタ(アドレス: 0x0A)

| BIT NAME   | BIT LOCATION<br>(0 = LSB) | FUNCTION                                                                                                                                                                                             |

|------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BB_BW[3:0] | 7–4                       | Programs the bandwidth of the baseband filter. Optimum values for 6MHz to 8MHz wide channels can be calculated after reading a ROM table entry. See the <i>Reading the ROM Table</i> section.        |

| BB_BIA     | 3                         | Baseband filter bias current control:  1 = High-bias current.  0 = Low-bias current.                                                                                                                 |

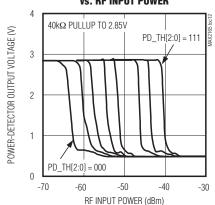

| PD_TH[2:0] | 2, 1, 0                   | Programs the power-detector attack point for closed-loop RF gain control; see the Typical Operating Characteristics for power-detector behavior:  000 = Most aggressive RF gain reduction.  001  110 |

## 表13. DCオフセット制御レジスタ(アドレス: 0x0B)

| BIT NAME   | BIT LOCATION<br>(0 = LSB) | FUNCTION                                                                                                                                                                                                                                                                                                                   |

|------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Х          | 7                         | Reserved. Set to 0 for normal operation.                                                                                                                                                                                                                                                                                   |

| DC_DAC8    | 6                         | Most significant bit of the DC offset correction DAC.                                                                                                                                                                                                                                                                      |

| DC_MO[1:0] | 5, 4                      | Controls the DC offset correction mode of operation:  00 = Offset correction disabled.  01, 10 = I/Q channel DC correction DACs are programmed direct from the DC_DAC[8:0] bits for manual offset correction.  11 = Normal operation.                                                                                      |

| DC_SP[1:0] | 3, 2                      | Controls the DC offset correction speed (highpass corner frequency):  00 = Offset correction off, hold DAC values.  01 = Select correction speed 1 (slowest correction speed, ~20Hz highpass corner).  10 = Select correction speed 2.  11 = Select correction speed 3 (fastest correction speed, ~500Hz highpass corner). |

| DC_TH[1:0] | 1, 0                      | Control the DC offset correction accuracy thresholds:  00 = Not recommended.  01 = Keep typical DC offset to within ±100mV.  10 = Keep typical DC offset to within ±200mV.  11 = Keep typical DC offset to within ±400mV.                                                                                                  |

## 表14. DCオフセットDACレジスタ(アドレス: 0x0C)

| BIT NAME    | BIT LOCATION<br>(0 = LSB) | FUNCTION                                                                                                                             |

|-------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| DC_DAC[7:0] | /-()                      | Programs the I/Q DC offset DAC for manual DC offset correction. Note the MSB, DC_DAC8, is located in the DC Offset Control register. |

## 表15. ROMテーブルアドレスレジスタ(アドレス: 0x0D)

| BIT NAME | BIT LOCATION<br>(0 = LSB) | FUNCTION                                                                                                                                                                                                                                                                                              |

|----------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X        | 7–4                       | Reserved. Set to 0000 for normal operation.                                                                                                                                                                                                                                                           |

| TFA[3:0] | 3–0                       | Programs which ROM table address that data is to be read from (see Table 21):  0001 = Tracking filter notch coefficients for 783MHz and 725MHz.  0010 = Balun coefficients for 470MHz and 780MHz.  0011 = Baseband filter bandwidth settings for 7MHz and 8MHz channels.  All other codes = Reserved. |

## 表16. 予約済みレジスタ(アドレス: 0x0E)

| BIT NAME | BIT LOCATION<br>(0 = LSB) | FUNCTION                                    |

|----------|---------------------------|---------------------------------------------|

| X        | 7–0                       | Reserved. Set to 0x00 for normal operation. |

MIXIM

## 表17. ROMテーブルデータ読取りレジスタ(アドレス: 0x10)

| BIT NAME | BIT LOCATION<br>(0 = LSB) | FUNCTION                                                                                                                                                              |

|----------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TFR[7:0] | 7–0                       | ROM table data read register. Data from the register at the address programmed into the TFA[3:0] bits are written to this register for reading by the host processor. |

## 表18. チップステータス読取りレジスタ(アドレス: 0x11)

| BIT NAME | BIT LOCATION<br>(0 = LSB) | FUNCTION                                                                                                                                                                                                            |

|----------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POR      | 7                         | Power-on-reset indicator:  1 = Power has been reset since last read.  0 = Power has not been reset since last read.                                                                                                 |

| VASA*    | 6                         | Indicates whether VCO autotuner selection was successful:  1 = Indicates successful automatic VCO selection.  0 = Indicates the autoselect function is disabled or automatic VCO selection was unsuccessful.        |

| VASE*    | 5                         | Status indicator for the VCO autotuner function:  1 = Indicates the automatic VCO selection process is active.  0 = Indicates the automatic VCO selection process is inactive.                                      |

| LD       | 4                         | PLL lock detect: 1 = PLL is locked. 0 = PLL is unlocked.                                                                                                                                                            |

| DC_LO*   | 3                         | Indicates DC offset correction accuracy:  1 = DC offset correction detected negative signal excursions in either the I or Q channel.  0 = No signal excursions detected.                                            |

| DC_HI*   | 2                         | Indicates DC offset correction accuracy:  1 = DC offset correction detected positive signal excursions in either the I or Q channel.  0 = No signal excursions detected.                                            |

| Х        | 1                         | Reserved.                                                                                                                                                                                                           |

| PD_OVLD  | 0                         | Indicates whether the signal level is above or below the programmed attack-point threshold:  1 = Signal is above the programmed attack-point threshold.  0 = Signal is below the programmed attack-point threshold. |

<sup>\*</sup>これらのビットの機能についてはプロダクションテストも保証もされていません。

## 表19. オートチューナ読取りレジスタ(アドレス: 0x12)

| BIT NAME  | BIT LOCATION<br>(0 = LSB) | FUNCTION                                                        |

|-----------|---------------------------|-----------------------------------------------------------------|

| VCO[1:0]* | 7, 6                      | Indicates which VCO was selected by the VCO autotuner.          |

| BS[2:0]*  | 5, 4, 3                   | Indicates which VCO sub-band was selected by the VCO autotuner. |

| ADC[2:0]* | 2, 1, 0                   | Provides a 3-bit digital reading of the VCO tuning voltage.     |

<sup>\*</sup>これらのビットの機能についてはプロダクションテストも保証もされていません。

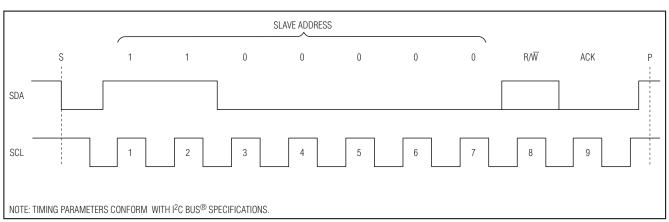

## 2線式シリアルインタフェース

MAX2165は、シリアルデータライン(SDA)とシリアルクロックライン(SCL)で構成される、2線式の $I^2$ C対応シリアルインタフェースを使用しています。SDAとSCLによって、MAX2165とマスタの間で最高400kHzのクロック周波数での双方向通信が実現されます。マスタがバス上でのデータ転送を開始する側であり、SCL信号を生成してデータ転送を許可します。MAX2165はマスタとの間でデータの送受信を行うスレーブデバイスとして動作します。バスを正常に動作させるためには、SDAとSCLを外付けのプルアップ抵抗( $1k\Omega$ 以上)でハイにプルアップする必要があります。

各SCLクロックサイクルの間に1ビットが転送されます。MAX2165との間で1バイトの転送を行うためには、最低9クロックサイクルが必要です(8ビットおよびACK/NACK)。SDA上のデータは、SCLのクロックパルスがハイの期間にわたって安定状態を保つ必要があります。SCLがハイで安定しているときにSDAが変化すると、制御信号と見なされます(「STARTおよびSTOP条件」の項参照)。バスがビジーでないときは、SDAとSCLの両方ともハイのままになります。

#### STARTおよびSTOP条件

マスタはSTART条件(S)、すなわちSCLがハイの間にSDAをハイからローに遷移させることで転送を開始します。マスタはSTOP条件(P)、すなわちSCLがハイの間にSDAをローからハイに遷移させることで転送を終了します。

表20. プログラマブルなデバイスアドレス

|      | <u></u>      |               |

|------|--------------|---------------|

| ADDR | READ ADDRESS | WRITE ADDRESS |

| 1    | 0xC3         | 0xC2          |

| 0    | 0xC1         | 0xC0          |

I<sup>2</sup>C busはPhilips Corp.の登録商標です。

## アクノリッジおよび非アクノリッジ条件

データ転送はアクノリッジビット(ACK)または非アクノリッジビット(NACK)で区切られます。マスタとMAX2165 (スレーブ)の両方がアクノリッジビットを生成します。アクノリッジビットを生成するには、アクノリッジ関連のクロックパルス(9番目のパルス)の立上りエッジより前に受信側デバイスがSDAをローに強制して、そのクロックパルスがハイの間SDAをローに維持する必要があります。

非アクノリッジ条件を生成するには、アクノリッジ関連のクロックパルスの立上りエッジより前にSDAがハイになるのを受信側が容認して、そのクロックパルスがハイの間SDAをハイに保持する必要があります。アクノリッジビットを監視することによって、データ転送の失敗を検出することができます。データ転送の失敗は、受信側デバイスがビジーであるか、またはシステム障害の発生によって起こります。データ転送に失敗した場合、バスマスタが後で通信を再試行する必要があります。

#### スレーブアドレス

MAX2165は7ビットのスレーブアドレスを持っており、通信を開始するためにはSTART条件に続けてそれをMAX2165に送信する必要があります。スレーブアドレスは、選択可能な2個のアドレスが用意されており、ADDR端子でどちらかにプログラムすることができます(表20)。7ビットのアドレスに続く8番目のビット(R/W)で、読取りまたは書込みのどちらの操作が行われるかが決まります。

MAX2165は、START条件に続く自分のスレーブアドレスを常に待っています。MAX2165が自分のスレーブアドレスを認識すると、1クロックの期間SDAラインをローに強制することによってアクノリッジを行い、R/Wビットに応じて、データの受信または送信の準備が整ったことを示します(図1)。

#### 書込みサイクル

書込みコマンドでアクセスされた場合、MAX2165はマスタが単一のレジスタまたは複数の連続したレジスタに書込みを行うことを許可します。

図1. MAX2165スレーブアドレスバイト

| START | WRITE DEVICE<br>ADDRESS | R/W | ACK | WRITE REGISTER<br>ADDRESS | ACK | WRITE DATA TO<br>REGISTER 0x00 | ACK | WRITE DATA TO<br>REGISTER 0x01 | ACK | WRITE DATA TO<br>REGISTER 0x02 | ACK | STOP |

|-------|-------------------------|-----|-----|---------------------------|-----|--------------------------------|-----|--------------------------------|-----|--------------------------------|-----|------|

| Omail | 110000[ADDR]            | 0   |     | 0x00                      |     | 0x0E                           |     | 0xD8                           |     | 0xE1                           |     | 0101 |

図2. レジスタ0~2にそれぞれ0x0E、0xDS、および0xE1を書き込む例

| START | WRITE DEVICE<br>ADDRESS | R/W | ACK | WRITE 1st REGISTER<br>ADDRESS | ACK | START   | WRITE DEVICE<br>ADDRESS | R/W | ACK | WRITE DATA<br>REG 0 | ACK | WRITE DATA<br>REG 1 | NACK | STOP |

|-------|-------------------------|-----|-----|-------------------------------|-----|---------|-------------------------|-----|-----|---------------------|-----|---------------------|------|------|

|       | 110000[ADDR]            | 0   |     | 00000000                      |     | 0171111 | 110000[ADDR]            | 1   |     | D7-D0               |     | D7-D0               |      | 0101 |

図3. レジスタ0~2からデータを読み取る例

書込みサイクルは、バスマスタがSTART条件を発行し、 それに続けて7個のスレーブアドレスビットと1個の書込み ビット(R/W = 0)を送信することによって開始されます。 スレーブアドレスバイトを正常に受信すると、MAX2165 はACKを発行します。次にバスマスタは、書込みを行う 最初のレジスタのアドレスをスレーブに送信する必要が あります(レジスタアドレスについては表1をご覧くだ さい)。スレーブがそのアドレスに対してアクノリッジを 行った場合、マスタは指定したアドレスのレジスタに1 バイトを書き込むことができます。データの書込みは 最上位ビットから始まり、SCLKの立上りエッジごとに 送り込まれます。データがレジスタに正常に書き込ま れた場合、MAX2165は再びACKを発行します。マスタ は連続した内蔵レジスタに対してデータの書込みを続け ることができ、MAX2165は転送が成功するごとにアク ノリッジを行うか、またはSTOP条件を発行して送信を終 了させることができます。書込みサイクルは、マスタ がSTOP条件を発行するまで終了しません。

図2は、レジスタ0~2にそれぞれ0x0E、0xD8、および0xE1を書き込む例を示しています。

#### 読取りサイクル

MAX2165のレジスタはすべてマスタによる読取りが可能であり、レジスタの内の3個は読取り専用です。

読取りサイクルは、バスマスタがSTART条件を発行し、 それに続けて7個のスレーブアドレスビットと1個の書 込みビット $(R/\overline{W} = 0)$ を送信することによって開始され ます。スレーブアドレスバイトの受信に成功すると、 MAX2165はACKを発行します。次にバスマスタは、 読取りを行う最初のレジスタのアドレスを送信します。 するとMAX2165は再びACKを発行します。次に、マスタ はSTART条件を発行し、それに続けて7個のスレーブ アドレスビットと1個の読取りビット $(R/\overline{W} = 1)$ を送信 する必要があります。MAX2165が自分のアドレスの 認識に成功した場合はACKを発行して、最上位ビット (MSB)から順に、指定されたレジスタアドレスから データの送信を開始します。データはSCLKの立上り エッジでMAX2165から送り出されます。SCLKの9個目 の立上りエッジで、マスタはACKを発行して後続の レジスタの読取りを続けるか、またはNACKに続けて STOP条件を発行することによって送信を終了させることができます。読取りサイクルは、マスタがSTOP条件を発行するまで終了しません。図3に、レジスタ0および1の読取りを行う例を示します。

## アプリケーション情報

## RF入力

RF入力は内部で整合されており、 $50\Omega$ または $75\Omega$ のシステムに対して全動作帯域にわたる良好な反射減衰量を提供します。DCブロッキングコンデンサが必要です。

### RFおよびベースバンド利得制御

MAX2165はRFとベースバンド用に個別の利得制御入力を備えており、それらを使用して幅広い入力ダイナミックレンジにわたって最高のSNRを実現することができます。ベースバンド利得制御は、BB\_AGC端子を通して行います。この端子は、一般的にはベースバンドプロセッサによって制御され、0.4V~2.3Vの電圧を受け付けることができ、2.3Vのときベースバンド利得が最大になります。

RF利得制御は、RF\_AGC端子を通して行います。この端子も0.4V~2.3Vの制御電圧を受け付け、2.3VのときRF利得が最大になります。ローパスフィルタを通してOVLD\_DET端子をRF\_AGC端子に接続することによって、閉ループ自動RF利得制御を実現することが可能です。「IF電力検出器」の項をご覧ください。

RF信号経路には低ノイズアンプ(LNA)が実装されており、信号経路への組込み/切離しが可能になっています。LNAレジスタ(表7)のLNASWビットに1をプログラムすると、LNAがイネーブルされます。LNAをイネーブルすると、電流が約17mA、利得が16dB増大して、受信信号の位相変化は10°未満です。

#### IF電力検出器

MAX2165のベースバンド電力検出器は、目的のチャネルから約2チャネル分に含まれる受信入力信号の加重合計を、プログラマブルなスレッショルドと比較します。このスレッショルドは、ベースバンド制御レジスタのPD\_TH[2:0] ビットで他の値にプログラムすることが可能です。

RF利得制御ループを閉じるため、電力検出器の $300\mu$ A制御電流シンク(OVLD\_DET端子)を $40k\Omega$ のプルアップ抵抗で $V_{CC}$ に接続してください。その結果の電圧は、RCローパスを通してRF AGC入力に供給されます。

### VCOオートチューナ

MAX2165は3個のVCOを内蔵しており、各VCOに8個のVCOサブバンドが含まれています。必要な局部発振器周波数に対する適切なVCOおよびVCOサブバンドの選択は、VCO制御レジスタ(表11)のVCO[1:0]およびSB[2:0]ビットのプログラミングによって、手動で行うことができます。

あるいは、VCOおよびVCOサブバンドを自律的に選択するようにMAX2165を設定することも可能です。VCOの自動選択は、VCO制御レジスタ(表11)のVASビットを設定することによってイネーブルになります。オートチューナは、N分周器の分数部がプログラムされた時点で適切なVCOの選択を開始します。したがって、LO周波数を変更するときは、すべてのN分周器レジスタ(整数部および分数部)をプログラムしてオートチューナ機能を作動させる必要があります。

PLLロック検出は、MUX端子を監視するか、または チップステータス読取りレジスタ(表18)のLDビットを 読み取ることによって実現することができます。

#### チャージポンプ電流の選択

PLLチャージポンプ電流も、手動でプログラムするか、またはVCOオートチューナによって自動的に選択することが可能です。PLLコンフィギュレーションレジスタ(表8)のCPSビットに1をプログラムして自動チャージポンプ電流選択をイネーブルにするか、またはCPSに0を

プログラムして手動チャージポンプ電流選択をイネーブルにしてください。自動チャージポンプ電流選択をイネーブルにするには、オートチューナ機能をイネーブル(VAS = 1)にする必要があります。手動モードでは、チャージポンプ電流はPLLコンフィギュレーションレジスタのICPビットによってプログラムされます。

#### VCOオートチューナ遅延の選択

オートチューナの選択過程において、オートチューナでは、VCO選択の成否を判断する前に、PLLが安定化する十分な時間を見込む必要があります。このウェイト時間は、PLLコンフィギュレーションレジスタ(表8)のADLY[1:0]ビットでプログラム可能です。予想されるPLLセトリング時間よりも長くなるようにウェイト時間をプログラムしてください。

### RFノッチフィルタ

MAX2165にはRFノッチフィルタが内蔵されており、これを使用することによって830MHz~950MHzの周波数範囲から大きな干渉信号を除去して、大きな携帯電話信号の存在下で動作させる場合の性能低下を防ぐことができます。フィルタのノッチ周波数は、トラッキングフィルタレジスタ(表6)のTF\_NTCH[3:0]ビットでプログラム可能です。2種類の異なるノッチ周波数に対する最適なノッチフィルタコードが、チップ内蔵のROMテーブルに格納されています。詳細については、「ベースバンドフィルタとトラッキングフィルタ」の項をご覧ください。干渉セルラ信号が存在しない場合、または783MHz~860MHzの周波数範囲の信号を受信する場合は、TF\_NTCH[3:0]ビットに111をプログラムすることによって、指定可能な最も高い周波数にノッチを移動して、フィルタの帯域内減衰を最小化する必要があります。

表21. ROMテーブル

|                                                                                                   |         | MSB        |                                                                                                  |             |              |                                                                                                                |    |     | LSB |  |  |  |

|---------------------------------------------------------------------------------------------------|---------|------------|--------------------------------------------------------------------------------------------------|-------------|--------------|----------------------------------------------------------------------------------------------------------------|----|-----|-----|--|--|--|

| DESCRIPTION                                                                                       | ADDRESS |            |                                                                                                  |             | DATA         | A BYTE                                                                                                         |    |     |     |  |  |  |

|                                                                                                   |         | D7         | D6                                                                                               | D5          | D4           | D3                                                                                                             | D2 | D1  | D0  |  |  |  |

| Reserved                                                                                          | 0x0     | Χ          | Χ                                                                                                | Х           | X            | Х                                                                                                              | Х  | Χ   | Х   |  |  |  |

| Optimal tracking<br>filter notch settings<br>for operation<br>below 725MHz<br>and above<br>725MHz | 0x1     | Recommen   | er notch low                                                                                     | equency set | tings for Rx | TF_NTCH[3:0]  Tracking filter notch high  Recommended notch frequency settings for Rx frequencies above 725MHz |    |     |     |  |  |  |

| Optimal tracking<br>settings at<br>780MHz and<br>470MHz                                           | 0x2     |            | TF_BAL[3:0]  Optimal tracking filter settings at 780MHz  Optimal tracking filter settings at 470 |             |              |                                                                                                                |    | MHz |     |  |  |  |

| Optimal baseband filter BW for 8MHz channel                                                       | 0x3     | BB_BW[3:0] | BB_BW[3:0]<br>BMHz wide                                                                          |             |              |                                                                                                                | X  | Х   | Х   |  |  |  |

トラッキングフィルタとは異なり、様々な動作周波数に合わせてノッチフィルタの設定を補間する必要はありません。セルラ妨害信号の存在下で725MHzより低いチャネルを受信する場合は、ROMテーブルに格納されている低い方のノッチ周波数用にTF\_NTCH[3:0]ビットをプログラムしてください。セルラ妨害信号の存在下で725MHzより高いチャネルを受信する場合は、ROMテーブルに格納されている高い方のノッチ周波数用にTF\_NTCH[3:0]ビットをプログラムすることができます。

## ベースバンドフィルタとトラッキングフィルタ

MAX2165には、プログラマブルなベースバンドフィルタとトラッキングフィルタが内蔵されています。ベースバンドフィルタの帯域幅は、ベースバンド制御レジスタ(表12)のBB\_BW[3:0]ビットで制御します。トラッキングフィルタのバラン周波数は、トラッキングフィルタレジスタ(表6)のTF\_BAL[3:0]でプログラム可能です。

#### ROMテーブルの読取り

製品のバラツキに対処するため、個々のデバイスの較正が 工場で行われます。較正の過程で、2種類の異なるノッチ 周波数に対する最良のノッチフィルタの設定、470MHzと 780MHz用の最良のバラン設定、および6MHz~8MHzの 各チャネルに対する最良のベースバンドフィルタ設定が決 定されます。これらの設定は、チップに内蔵されたROM テーブルに格納されており、起動時に読み取ってマイクロ プロセッサのローカルメモリに格納する必要があります (計3バイト)。表21に、ROMテーブルの各エントリについ てアドレスとビット構成を示します。

ROMテーブルの各エントリは、2段階の手順で読み取る必要があります。最初に、読み取るビットのアドレスをROMテーブルアドレスレジスタ(表15)のTFA[3:0]ビットにプログラムする必要があります。

アドレスのプログラムが終わると、そのアドレスに格納されているデータがROMテーブルデータ読取りレジスタ(表17)のTRF[7:0]ビットに転送されます。その後、指定されたアドレスのROMデータをTRF[7:0]ビットから読み取って、マイクロプロセッサのローカルメモリに格納することができます。

#### バラン係数の補間計算

TF\_BAL[3:0]ビットを個々のチャネル周波数について再プログラムして、帯域全体の性能を最適化する必要があります。ROMテーブルに格納されている780MHzと470MHz用の値を元に、次式を使用して他の任意の周波数に対する最適な係数を補間計算することができます。

値 = BAL\_L + (BAL\_H - BAL\_L) $\times \frac{f - 470MHz}{780MHz - 470MHz}$

#### ここで

値 = 目的のチャネル周波数f用の最適な $TF_BAL[3:0]$ の設定値(10進)

BAL\_L = ROMテーブルから読み取った470MHz用の 最適なTF BAL[3:0]の設定値(10進)

BAL\_H = ROMテーブルから読み取った780MHz用の 最適なTF BAL[3:0]の設定値(10進)

f = 目的のチャネル周波数(単位:MHz)

**例**:ROMテーブルから読み取った780MHz用と470MHz 用のTF\_BAL[3:0]の値がそれぞれ14と2であり、RF周 波数620MHzでの動作用にバランをプログラムしたいと 仮定します。

先ほどの式を使用して、次のように計算を行うことができます。

620MHzでの値=2+(14-2)× 620MHz-470MHz = 7.8

四捨五入によって最も近い整数値を求めると、8になります。したがって、620MHzで動作させる場合、トラッキングフィルタレジスタのTF\_BAL[3:0]ビットには1000をプログラムする必要があります。

#### ベースバンドフィルタの設定

MAX2165のベースバンドフィルタは、約3.0MHz~4.3MHzという広い範囲にわたって3dBカットオフ周波数を自由にプログラム可能ですが、正確なカットオフ周波数は製造プロセスの変動が原因で個々のデバイスごとに異なります。ユーザが正しい設定を見つける必要がないように、カットオフ周波数3.9MHz(すなわち、8MHz幅のDVB-T/-Hチャネル)に対する最良の設定がMaximによって決定され、個々のチップのROMテーブルに格納されています。ユーザはMAX2165の起動時にROMテーブルのエントリ0x3(表21参照)からこの値を読み取って、レジスタ0xAのBB\_BW[3:0]ビット(表12参照)に書き戻す必要があります。

## 8MHz以外のRFチャネルまたはDVB-T以外の 変調タイプに対するベースバンドフィルタの設定

3.9MHz以外のカットオフ周波数が必要な場合、該当する MAX2165のレジスタに書き戻す前に、ROMテーブル から読み取った数値に表22の固定値を加算または減算 することができます。この場合も工場での較正は依然 として利用され、結果のカットオフ周波数は妥当な 正確さを維持しています。

## 表22. いろいろなカットオフ周波数用のオフセット

| DESIRED 3dB CUTOFF FREQUENCY (TYPICAL) (MHz) | OFFSET TO BE ADDED TO ROM TABLE ENTRY 0x3 BEFORE WRITING BACK INTO REGISTER 0xA |

|----------------------------------------------|---------------------------------------------------------------------------------|

| 3.10                                         | -6                                                                              |

| 3.20                                         | -5                                                                              |

| 3.30                                         | -4                                                                              |

| 3.44                                         | -3                                                                              |

| 3.56                                         | -2                                                                              |

| 3.70                                         | -1                                                                              |

| 3.90                                         | 0                                                                               |

| 4.10                                         | +1                                                                              |

| 4.23                                         | +2                                                                              |

#### DCオフセット補正

ダイレクトコンバージョンレシーバはDCオフセットの影響を受けやすく、リニアリティ性能が制限される可能性があり、ダウンストリームのデータコンバータ/デモジュレータのダイナミックレンジも狭くなります。MAX2165は高速セトリングDCオフセットキャンセル回路をチップに内蔵しており、出力信号に含まれる有害なDCオフセットを除去するための外付け部品は必要ありません。

補正のスレッショルドは、DCオフセット制御レジスタ (表13)のDC\_TH[1:0]ビットによって、4種類の異なる 値にプログラム可能です。

オフセット補正の作動時には、補正回路が、信号経路にオフセット補正速度を決定するハイパス特性を作ります。この補正速度は、DCオフセット制御レジスタのDC SP[1:0]ビットでプログラム可能です。

DVB-Hアプリケーションの場合、デバイスがシャットダウンから復帰するごとに1度DC補正を実施して、その後DC\_SP[1:0]ビットに00 (ホールド状態)をプログラムすることによってディセーブルすることが推奨されます。信号受信中はDCオフセット補正をディセーブルしておくことによって、補正回路に伴うハイパス特性によって受信信号の低周波数成分に歪みが生じるのを防ぐことができ、デモジュレータへのDC結合が可能になります。DC結合で動作させるための唯一の要件は、1度限りの除去の後は受信周波数とベースバンドフィルタの設定が一定であることです。DVB-Hの典型的な時分割動作の性質によって、こうした環境下での動作が容易になっています。

このデバイスは、SHDNおよびSTBY端子を使用することによって、起動時に自動的にDC補正を行うように設定することも可能です。詳細については、「起動シーケンス」の項をご覧ください。

## 起動シーケンスとシャットダウンモード

SHDN端子をローに駆動するとMAX2165はハードウェアシャットダウンモードに移行し、すべての内部回路がディセーブルされて電源電流が20µA未満に減少します。SHDNをローに駆動すると、シャットダウンリファレンスビット(SHDN\_REF)を除いて、内部レジスタの状態に関係なくIC全体がシャットダウンされます。デバイスがシャットダウンモードから復帰したとき、レジスタ設定は維持されています。

MAX2165は、ソフトウェアシャットダウンモードも備えています。ソフトウェアシャットダウンモードでは、シャットダウンレジスタの個々のビットをプログラムすることによって、MAX2165の各機能ブロックを停止することができます。ソフトウェアからチップ全体をシャットダウンするには、シャットダウンレジスタ(表10)をOXFFに、VCO制御レジスタ(表11)のVCO[1:0]ビットをOOに、DCオフセット制御レジスタ(表13)のDC\_MO[1:0]ビットをOOにプログラムしてください。

MAX2165は、ハードウェアシャットダウンモードからの復帰時にDCオフセットを非常に迅速に除去する起動シーケンサを備えています。起動シーケンス機能をイネーブルするには、SHDNがローからハイに遷移する間にSTBYをグランドに接続してください。

#### 起動シーケンス

SHDNがハイに遷移する間STBYをローに保つと、デバイスは2段階のプロセスで起動します。第1段階では、VCOとPLLが起動して安定化します。この第1段階における標準的な電流消費は、約20mAです。第2段階では信号経路全体が起動して、RF\_AGC電圧、BB\_AGC電圧、およびDC補正が自動的にオーバーライドされ、DCオフセット補正が0.5ms未満で実行されます。DC補正が完了すると、デバイスは元々プログラムされていた状態に復帰します。起動プロセス全体は、約2msで完了します。

20 \_\_\_\_\_\_ /VI/IXI/VI

自動DC補正のメリットは、0.5ms未満でDCオフセット を除去することが可能になる点です。これは、自動DC 補正なしの場合に補正回路の実効ハイパスコーナー周 波数で実現可能な速度よりも大幅に高速です。ハード ウェアシャットダウンから復帰する前にDC SP[1:0] ビットに00がプログラムされると、このデバイスは起動 時に1度限りのDCオフセット除去を行い、起動シー ケンスが完了した後でDC補正回路をディセーブルします。 1度限りのオフセット除去後、受信周波数、ベースバンド フィルタの設定、およびチップ温度が一定である限り、 これによってベースバンド出力とデモジュレータの間 のDC結合が可能になります。チップが受信中のときに これらのパラメータを変更すると、DCオフセットの 再較正が必要になります。しかし、DVB-Hの典型的な 時分割の性質は、DC結合での動作に関する上記の要件 を満たしています。

STBYがV<sub>CC</sub>に接続されている場合、チップは前述の起動手順に従わず、すべての回路ブロックが同時に起動します。DC\_SP[1:0]ビットに00を設定していると(すなわち、疑似DC結合)、DC較正が1度も実行されず、MAX2165は正しく機能しません。

ハードウェアシャットダウンから復帰したときにDC補 正が自動的に実行されるかどうかは、STBY端子の状態 によってのみ決定されます。

#### 水晶発振器インタフェース

MAX2165のリファレンス発振器入力は、水晶発振器として構成するか、または外部ソースによって駆動されるハイインピーダンスのリファレンス入力として使用することができます。

外部のリファレンス発振器を使用する場合、AC結合コンデンサを通して約 $1V_{P-P}$ の信号振幅でXBを駆動して、XEは未接続のままにしてください。外部リファ

レンスの位相ノイズは、1kHz~100kHzのオフセットで-140dBc/Hzを上回る必要があります。

じかに水晶に接続する場合は、必要なトポロジーを「標準 アプリケーション回路」で確認してください。

## 水晶発振器バッファ出力

バッファ付きの水晶発振器信号がREFOUT端子で供給され、デモジュレータの駆動に使用することができます。この出力にはDCブロッキングコンデンサが必要です。このバッファは、シャットダウンレジスタ(表10)のSHDN\_REFビットでイネーブルまたはディセーブルすることができます。

## レイアウトについて

このEVキットは、PCBレイアウトの指針としても役立 ちます。RF信号ラインはできる限り短くして、損失と 放射を最小限に抑えてください。すべての高周波配線 には、インピーダンスを考慮して使用してください。 適正な動作のために、エクスポーズドパッドを基板の グランドプレーンに均一に半田付けしてください。 エクスポーズドパッドの下に十分な数のビアを使用して、 熱放散を最大化してください。各RFトレース間に十分な 数のグランドビアを使用して、有害な結合を最小化し てください。ICの異なるセクション間の結合を最小化 するための理想的な電源レイアウトはスター構成で あり、大容量のデカップリングコンデンサを中央のVcc ノードに実装します。このノードからVccトレースを分岐 させ、各トレースをMAX2165の個々のVcc端子に配線 します。各Vcc端子には、該当周波数でグランドに対して 低いインピーダンスを示すバイパスコンデンサを実装 する必要があります。PCBのグランドプレーンに対 する複数の接続間でグランドビアを共有しないでくだ さい。

## 標準アプリケーション回路

# MAX2165

# シングルコンバージョンDVB-Hチューナ

## パッケージ

最新のパッケージ情報とランドパターンは、japan.maxim-ic.com/packagesをご参照ください。

| パッケージタイプ   | パッケージコード | ドキュメントNo.      |

|------------|----------|----------------|

| 28 TQFN-EP | T2855-8  | <u>21-0140</u> |

## 改訂履歷

| 版数 | 改訂日  | 説明                                                                                                                                                                    | 改訂ページ   |