### 概要

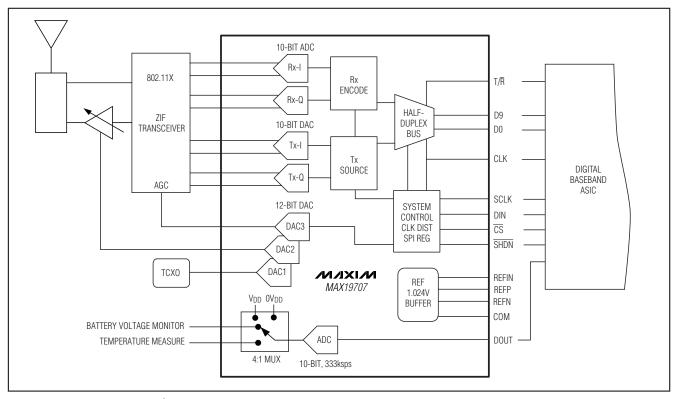

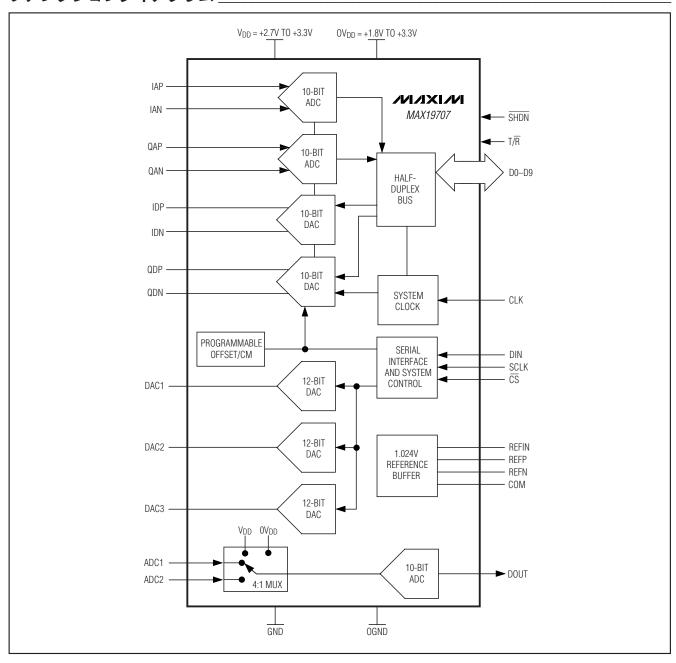

MAX19707は、消費電力重視の通信機器用に設計された 超低電力、ミックスドシグナルのアナログフロントエンド (AFE)です。この製品は超低電力で高ダイナミック性能に 最適化され、デュアル10ビットの45Msps受信(Rx) ADC、 デュアル10ビットの45Msps送信(Tx) DAC、補助RF フロントエンド制御用の3つの高速セトリング12ビット 補助DACチャネル、および10ビット、333kspsハウスキー ピング用補助ADCを内蔵しています。Tx-Rx高速モードでの 標準動作電力は、45MHzのクロック周波数で84.6mWです。

Rx ADCは、 $f_{IN} = 5.5MHz$ および $f_{CLK} = 45MHz$ において 54.2dBのSNRと71.2dBcのSFDRを備えています。アナ ログI/Q入力アンプは、完全差動化され、1.024V<sub>P-P</sub>の フルスケール信号を受け付けます。標準I/Qチャネルマッ チングは、位相が±0.03°で、利得が±0.01dBです。

Tx DACは、four = 2.2MHzおよびf<sub>CLK</sub> = 45MHzにおいて 73.2dBcのSFDRを備えています。アナログI/Qのフル スケール出力電圧は、±400mV(差動)です。Tx DACの コモンモードDCレベルは、0.71V~1.05Vに設定する ことができます。I/Qチャネルのオフセットは、無線ライン アップの側波帯/搬送波の抑圧が最適になるように設定する ことができます。標準I/Qチャネルマッチングは、利得が ±0.01dBで、位相が±0.07°です。

Rx ADCとTx DACは、単一の10ビット、パラレル、高速 ディジタルバスを共有しているため、時分割デュープレクス (TDD)アプリケーション用のハーフデュープレクス動作が 可能です。3線式シリアルインタフェースを通じて、電源 管理モード、補助DACチャネル、および補助ADCチャネル が制御されます。

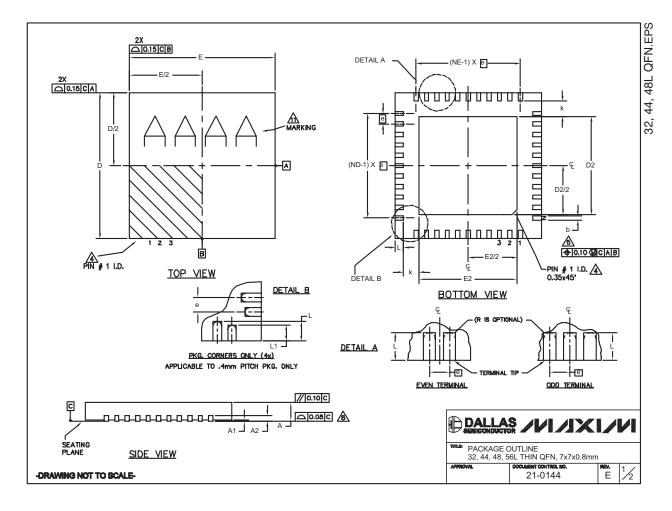

MAX19707は、+2.7V~+3.3Vのアナログ単一電源と +1.8V~+3.3VのディジタルI/O電源で動作します。 MAX19707は、拡張温度範囲(-40℃~+85℃)での動作 が保証され、48ピンTQFNパッケージで提供されます。 データシートの最後の「選択ガイド」には、このAFEファミリ の他のピンコンパチブルバージョンが記載されています。

### アプリケーション

WiMAX CPE

VoIP端末

802.11a/b/g WLAN

ポータブル通信機器

### 型番

| PART*        | PIN-PACKAGE      | PKG CODE |

|--------------|------------------|----------|

| MAX19707ETM  | 48 Thin QFN-EP** | T4877-4  |

| MAX19707ETM+ | 48 Thin QFN-EP** | T4877-4  |

\*すべてのデバイスは-40℃~+85℃の使用範囲での動作が保証 されています。

\*\*EP = Exposed paddle.

+は鉛フリーパッケージを示します。

#### 特長

- ◆ デュアル、10ビットの45Msps Rx ADC、 およびデュアル、10ビットの45Msps Tx DAC

- ◆ 超低電力 84.6mW(f<sub>CLK</sub> = 45MHz、高速モードにおいて) 77.1mW(f<sub>CLK</sub> = 45MHz、低速モードにおいて) 低電流スタンバイおよびシャットダウンモード

- ◆ プログラム可能なTx DACコモンモードDCレベルおよび I/Qオフセット調整

- ◆ 優れたダイナミック性能  $SNR = 54.2dB(f_{IN} = 5.5MHz(Rx ADC)において)$ SFDR = 73.2dBc(f<sub>OUT</sub> = 2.2MHz(Tx DAC)において)

- ◆ 3 x 12ビット、1µsの補助DAC

- ◆ 10ビット、333kspsの補助ADC、 4:1入力多重化およびデータ平均化付き

- ◆ 優れた利得/位相マッチング 位相:±0.03°、利得:±0.01dB(Rx ADC)  $(f_{IN} = 5.5MHzにおいて)$

- ◆ 多重化パラレルディジタルI/O

- ◆ シリアルインタフェース制御

- ◆ 汎用電源制御回路 シャットダウン、スタンバイ、アイドル、 Tx/Rxディセーブル

- ◆ 小型48ピンThin QFNパッケージ  $(7mm \times 7mm \times 0.8mm)$

### ピン配置

ファンクションダイアグラムと選択ガイドは、データシートの 最後に記載されています。

\_ Maxim Integrated Products 1

本データシートに記載された内容はMaxim Integrated Productsの公式な英語版データシートを翻訳したものです。翻訳により生じる相違及び 誤りについては責任を負いかねます。正確な内容の把握には英語版データシートをご参照ください。

### **ABSOLUTE MAXIMUM RATINGS**

| VDD to GND, OVDD to OGND                                                  | 0.3V to +3.6V                       | Continu  |

|---------------------------------------------------------------------------|-------------------------------------|----------|

| GND to OGND                                                               | 0.3V to +0.3V                       | 48-Pi    |

| IAP, IAN, QAP, QAN, IDP, IDN, QDP,                                        |                                     | Therma   |

| QDN, DAC1, DAC2, DAC3 to GND                                              | 0.3V to VDD                         | Operatir |

| ADC1, ADC2 to GND                                                         | 0.3V to (VDD + 0.3V)                | Junction |

| REFP, REFN, REFIN, COM to GND-0.3\                                        | √ to (V <sub>DD</sub> + 0.3V)D0–D9, | Storage  |

| DOUT, $T/\overline{R}$ , $\overline{SHDN}$ , SCLK, DIN, $\overline{CS}$ , |                                     | Lead Te  |

| CLK to OGND                                                               | 0.3V to (OVDD + 0.3V)               |          |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |                |

|-------------------------------------------------------|----------------|

| 48-Pin Thin QFN (derate 27.8mW/°C above               | +70°C)2.22W    |

| Thermal Resistance θJA                                | 36°C/W         |

| Operating Temperature Range                           | 40°C to +85°C  |

| Junction Temperature                                  | +150°C         |

| Storage Temperature Range                             | 60°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C         |

|                                                       |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(VDD = 3V, OVDD = 1.8V, internal reference (1.024V),  $C_L \approx 10$ pF on all digital outputs,  $f_{CLK} = 45$ MHz (50% duty cycle), Rx ADC input amplitude = -0.5dBFS, Tx DAC output amplitude = 0dBFS, differential Rx ADC input, differential Tx DAC output,  $C_{REFP} = C_{REFN} = C_{COM} = 0.33$ µF, unless otherwise noted.  $C_L < 5$ pF on all aux-DAC outputs. Typical values are at  $T_A = +25$ °C.) (Note 1)

| PARAMETER                      | SYMBOL          | CONDITIONS                                                                                                                                                                            | MIN | TYP  | MAX      | UNITS |

|--------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|----------|-------|

| POWER REQUIREMENTS             | •               |                                                                                                                                                                                       |     |      |          |       |

| Analog Supply Voltage          | V <sub>DD</sub> |                                                                                                                                                                                       | 2.7 | 3.0  | 3.3      | V     |

| Output Supply Voltage          | $OV_DD$         |                                                                                                                                                                                       | 1.8 |      | $V_{DD}$ | V     |

| V <sub>DD</sub> Supply Current |                 | Ext1-Tx, Ext3-Tx, and SPI2-Tx states; transmit DAC operating mode (Tx): f <sub>CLK</sub> = 45MHz, f <sub>OUT</sub> = 2.2MHz on both channels; aux-DACs ON and at midscale, aux-ADC ON |     | 16.5 |          |       |

|                                |                 | Ext2-Tx, Ext4-Tx, and SPI4-Tx states; transmit DAC operating mode (Tx): $f_{CLK} = 45MHz$ , $f_{OUT} = 2.2MHz$ on both channels; aux-DACs ON and at midscale, aux-ADC ON              |     | 29.8 | 35       |       |

|                                |                 | Ext1-Rx, Ext4-Rx, and SPI3-Rx states; receive ADC operating mode (Rx): f <sub>CLK</sub> = 45MHz, f <sub>IN</sub> = 5.5MHz on both channels; aux-DACs ON and at midscale, aux-ADC ON   |     | 28.2 | 34       | - mA  |

|                                |                 | Ext2-Rx, Ext3-Rx, and SPI1-Rx states; receive ADC operating mode (Rx): f <sub>CLK</sub> = 45MHz, f <sub>IN</sub> = 5.5MHz on both channels; aux-DACs ON and at midscale, aux-ADC ON   |     | 25.7 |          |       |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD}=3V,\,OV_{DD}=1.8V,\,$  internal reference (1.024V),  $C_L\approx 10$ pF on all digital outputs,  $f_{CLK}=45$ MHz (50% duty cycle), Rx ADC input amplitude = -0.5dBFS, Tx DAC output amplitude = 0dBFS, differential Rx ADC input, differential Tx DAC output,  $C_{REFP}=C_{REFN}=C_{COM}=0.33$ µF, unless otherwise noted.  $C_L<5$ pF on all aux-DAC outputs. Typical values are at  $T_A=+25$ °C.) (Note 1)

| PARAMETER                       | SYMBOL  | CONDITIONS                                                                                                                                                                                                   | MIN   | TYP   | MAX   | UNITS  |

|---------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|--------|

| V. Carrela Carrent              |         | Standby mode: CLK = 0 or OV <sub>DD</sub> ;<br>aux-DACs ON and at midscale,<br>aux-ADC ON                                                                                                                    |       | 3.2   | 5     | mA     |

| V <sub>DD</sub> Supply Current  |         | Idle mode: f <sub>CLK</sub> = 45MHz; aux-DACs ON and at midscale, aux-ADC ON                                                                                                                                 |       | 12.1  | 15    |        |

|                                 |         | Shutdown mode: CLK = 0 or OV <sub>DD</sub>                                                                                                                                                                   |       | 1     |       | μΑ     |

| OV <sub>DD</sub> Supply Current |         | Ext1-Rx, Ext2-Rx, Ext3-Rx, Ext4-Rx, SPI1-Rx, SPI3-Rx states; receive ADC operating mode (Rx): f <sub>CLK</sub> = 45MHz, f <sub>IN</sub> = 5.5MHz on both channels; aux-DACs ON and at midscale, aux-ADC ON   |       | 7.7   |       | mA     |

|                                 |         | Ext1-Tx, Ext2-Tx, Ext3-Tx, Ext4-Tx, SPI2-Tx, SPI4-Tx states; transmit DAC operating mode (Tx), f <sub>CLK</sub> = 45MHz, f <sub>OUT</sub> = 2.2MHz on both channels; aux-DACs ON and at midscale, aux-ADC ON |       | 485   |       | μА     |

|                                 |         | Standby mode: CLK = 0 or OV <sub>DD</sub> ; aux-DACs<br>ON and at midscale, aux-ADC ON                                                                                                                       |       | 1     |       |        |

|                                 |         | Idle mode: f <sub>CLK</sub> = 45MHz; aux-DACs ON and at midscale, aux-ADC ON                                                                                                                                 |       | 76    |       |        |

|                                 |         | Shutdown mode: CLK = 0 or OV <sub>DD</sub>                                                                                                                                                                   |       | 1     |       |        |

| Rx ADC DC ACCURACY              |         |                                                                                                                                                                                                              |       |       |       |        |

| Resolution                      | N       |                                                                                                                                                                                                              |       | 10    |       | Bits   |

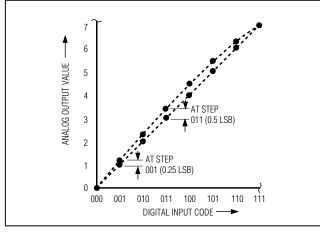

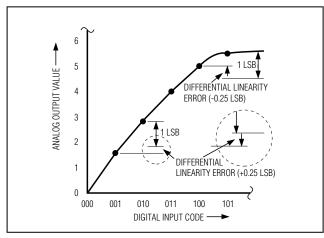

| Integral Nonlinearity           | INL     |                                                                                                                                                                                                              |       | ±1.6  |       | LSB    |

| Differential Nonlinearity       | DNL     |                                                                                                                                                                                                              |       | ±0.7  |       | LSB    |

| Offset Error                    |         | Residual DC offset error                                                                                                                                                                                     | -5    | ±0.5  | +5    | %FS    |

| Gain Error                      |         | Include reference error                                                                                                                                                                                      | -5.5  | ±1.0  | +5.5  | %FS    |

| DC Gain Matching                |         |                                                                                                                                                                                                              | -0.15 | ±0.01 | +0.15 | dB     |

| Offset Matching                 |         |                                                                                                                                                                                                              |       | ±13   |       | LSB    |

| Gain Temperature Coefficient    |         |                                                                                                                                                                                                              |       | ±30   |       | ppm/°C |

| Power-Supply Rejection          | PSRR    | Offset error (V <sub>DD</sub> ±5%)                                                                                                                                                                           |       | ±0.4  |       | LSB    |

|                                 | 1 01111 | Gain error (V <sub>DD</sub> ±5%)                                                                                                                                                                             |       | ±0.1  |       | %FS    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD}=3V,\,OV_{DD}=1.8V,\,internal\,\,reference\,\,(1.024V),\,\,C_{L}\approx10$ pF on all digital outputs,  $f_{CLK}=45$ MHz (50% duty cycle), Rx ADC input amplitude = -0.5dBFS, Tx DAC output amplitude = 0dBFS, differential Rx ADC input, differential Tx DAC output,  $C_{REFP}=C_{REFN}=C_{COM}=0.33$ µF, unless otherwise noted.  $C_{L}<5$ pF on all aux-DAC outputs. Typical values are at  $T_{A}=+25$ °C.) (Note 1)

| Rx ADC ANALOG INPUT                   |                 |                                                                                                           |      |                     |       |         |

|---------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------|------|---------------------|-------|---------|

|                                       |                 |                                                                                                           |      |                     |       | •       |

| nput Differential Range               | V <sub>ID</sub> | Differential or single-ended inputs                                                                       |      | ±0.512              |       | V       |

| nput Common-Mode Voltage<br>Range     | VcM             |                                                                                                           |      | V <sub>DD</sub> / 2 |       | V       |

| nput Impedance                        | R <sub>IN</sub> | Switched capacitor load                                                                                   |      | 120                 |       | kΩ      |

| riput impedance                       | CIN             |                                                                                                           |      | 5                   |       | рF      |

| Rx ADC CONVERSION RATE                |                 |                                                                                                           |      |                     |       |         |

| Maximum Clock Frequency               | fclk            | (Note 2)                                                                                                  |      |                     | 45    | MHz     |

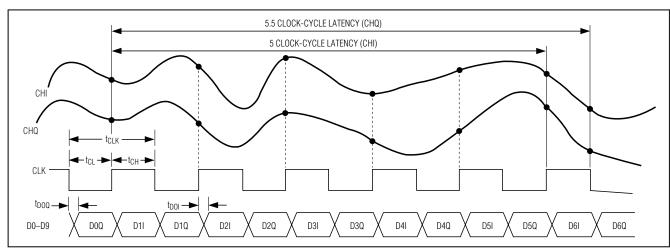

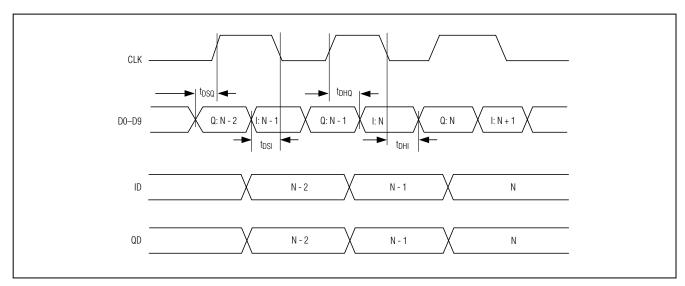

| Data Latency (Figure 3)               |                 | Channel I                                                                                                 |      | 5                   |       | Clock   |

| Data Latericy (Figure 3)              |                 | Channel Q                                                                                                 |      | 5.5                 |       | Cycles  |

| Rx ADC DYNAMIC CHARACTER              | ISTICS (Note 3  | 3)                                                                                                        |      |                     |       |         |

| Signal-to-Noise Ratio                 | SNR             | $f_{IN} = 5.5MHz$ , $f_{CLK} = 45MHz$                                                                     | 52.5 | 54.2                |       | dB      |

| orginal to recise ridite              | SIVIT           | $f_{IN} = 22MHz$ , $f_{CLK} = 45MHz$                                                                      |      | 54.1                |       | GD      |

| Signal-to-Noise Plus Distortion       | SINAD           | $f_{IN} = 5.5MHz$ , $f_{CLK} = 45MHz$                                                                     | 52.2 | 54.1                |       | dB      |

|                                       | SINAD           | $f_{IN} = 22MHz$ , $f_{CLK} = 45MHz$                                                                      |      | 54                  |       | QD.     |

| Spurious-Free Dynamic Range           | SFDR            | $f_{IN} = 5.5MHz$ , $f_{CLK} = 45MHz$                                                                     | 62.1 | 71.2                |       | dBc     |

| ppunous rice bynamic riange           | OI DIT          | $f_{IN} = 22MHz$ , $f_{CLK} = 45MHz$                                                                      |      | 70.4                |       | авс     |

| hird-Harmonic Distortion              | HD3             | $f_{IN} = 5.5MHz$ , $f_{CLK} = 45MHz$                                                                     |      | -78.1               |       | dBc     |

| Third Flatmonic Distortion            | 1100            | $f_{IN} = 22MHz$ , $f_{CLK} = 45MHz$                                                                      |      | -73.1               |       | авс     |

| ntermodulation Distortion             | IMD             | $f_1 = 1.8MHz$ , -7dBFS;<br>$f_2 = 1MHz$ , -7dBFS                                                         |      | -68.6               |       | dBc     |

| hird-Order Intermodulation Distortion | IM3             | $f_1 = 1.8MHz$ , -7dBFS;<br>$f_2 = 1MHz$ , -7dBFS                                                         |      | -79.2               |       | dBc     |

| Tatal I la responsia Diatortian       | TUD             | f <sub>IN</sub> = 5.5MHz, f <sub>CLK</sub> = 45MHz                                                        |      | -68.4               | -61.5 | ٩D      |

| otal Harmonic Distortion              | THD             | $f_{IN} = 22MHz$ , $f_{CLK} = 45MHz$                                                                      |      | -68.8               |       | dB      |

| Aperture Delay                        |                 |                                                                                                           |      | 3.5                 |       | ns      |

| Overdrive Recovery Time               |                 | 1.5x full-scale input                                                                                     |      | 2                   |       | ns      |

| Rx ADC INTERCHANNEL CHAR              | ACTERISTICS     |                                                                                                           |      |                     |       |         |

| Crosstalk Rejection                   |                 | $f_{\text{INX,Y}} = 5.5 \text{MHz}$ at -0.5dBFS, $f_{\text{INX,Y}} = 1.8 \text{MHz}$ at -0.5dBFS (Note 4) |      | -90                 | _     | dB      |

| Amplitude Matching                    |                 | f <sub>IN</sub> = 5.5MHz at -0.5dBFS (Note 5)                                                             |      | ±0.01               |       | dB      |

| Phase Matching                        |                 | f <sub>IN</sub> = 5.5MHz at -0.5dBFS (Note 5)                                                             |      | ±0.03               |       | Degrees |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD}=3V,\,OV_{DD}=1.8V,\,$  internal reference (1.024V),  $C_L\approx 10$ pF on all digital outputs,  $f_{CLK}=45$ MHz (50% duty cycle), Rx ADC input amplitude = -0.5dBFS, Tx DAC output amplitude = 0dBFS, differential Rx ADC input, differential Tx DAC output,  $C_{REFP}=C_{REFN}=C_{COM}=0.33$ µF, unless otherwise noted.  $C_L<5$ pF on all aux-DAC outputs. Typical values are at  $T_A=+25$ °C.) (Note 1)

| PARAMETER                              | SYMBOL           | CONDIT                                       | TONS                   | MIN   | TYP    | MAX   | UNITS        |  |

|----------------------------------------|------------------|----------------------------------------------|------------------------|-------|--------|-------|--------------|--|

| Tx DAC DC ACCURACY                     | 1                | •                                            |                        |       |        |       |              |  |

| Resolution                             | N                |                                              |                        |       | 10     |       | Bits         |  |

| Integral Nonlinearity                  | INL              |                                              |                        |       | ±0.3   |       | LSB          |  |

| Differential Nonlinearity              | DNL              | Guaranteed monotonic                         | (Note 6)               | -1    | ±0.2   | +1    | LSB          |  |

| Residual DC Offset                     | Vac              | T <sub>A</sub> ≥ +25°C                       |                        | -4    | ±1     | +4    | mV           |  |

| Residual DC Oliset                     | Vos              | T <sub>A</sub> < +25°C                       |                        | -4.5  | ±1     | +4.5  | IIIV         |  |

| Full-Scale Gain Error                  |                  | Include reference error                      | T <sub>A</sub> ≥ +25°C | -30   |        | +30   | mV           |  |

| Full-Scale Gaill Error                 |                  | (peak-to-peak error)                         | T <sub>A</sub> < +25°C | -40   |        | +40   | IIIV         |  |

| Tx DAC DYNAMIC PERFORMANC              | E                |                                              |                        |       |        |       |              |  |

| DAC Conversion Rate                    | fCLK             | (Note 2)                                     |                        |       |        | 45    | MHz          |  |

| In-Band Noise Density                  | N <sub>D</sub>   | fout = 2.2MHz, fclk =                        | 45MHz                  |       | -130.6 |       | dBc/Hz       |  |

| Third-Order Intermodulation Distortion | IM3              | $f_1 = 2MHz, f_2 = 2.2MHz$                   | Z                      |       | 80     |       | dBc          |  |

| Glitch Impulse                         |                  |                                              |                        |       | 10     |       | pV∙s         |  |

| Spurious-Free Dynamic Range to Nyquist | SFDR             | f <sub>CLK</sub> = 45MHz, f <sub>OUT</sub> = | 2.2MHz                 | 60    | 73.2   |       | dBc          |  |

| Total Harmonic Distortion to Nyquist   | THD              | f <sub>CLK</sub> = 45MHz, f <sub>OUT</sub> = | 2.2MHz                 |       | -71    | -59   | dB           |  |

| Signal-to-Noise Ratio to Nyquist       | SNR              | f <sub>CLK</sub> = 45MHz, f <sub>OUT</sub> = | 2.2MHz                 |       | 57.1   |       | dB           |  |

| Tx DAC INTERCHANNEL CHARA              | CTERISTICS       |                                              |                        |       |        |       |              |  |

| I-to-Q Output Isolation                |                  | foutx,y = 2MHz, foutx                        | (,γ = 2.2MHz           |       | 85     |       | dB           |  |

| Gain Mismatch Between DAC              |                  | Maranina di at DO                            | T <sub>A</sub> ≥ +25°C | -0.3  | ±0.01  | +0.3  | -ID          |  |

| Outputs                                |                  | Measured at DC                               | T <sub>A</sub> < +25°C | -0.42 |        | +0.42 | dB           |  |

| Phase Mismatch Between DAC Outputs     |                  | fout = 2.2MHz, f <sub>CLK</sub> =            | 45MHz                  |       | ±0.07  |       | Degrees      |  |

| Differential Output Impedance          |                  |                                              |                        |       | 800    |       | Ω            |  |

| Tx DAC ANALOG OUTPUT                   | •                |                                              |                        | •     |        |       |              |  |

| Full-Scale Output Voltage              | VFS              |                                              |                        |       | ±400   |       | mV           |  |

|                                        |                  | Bits CM1 = 0, CM0 = 0                        | (default)              | 1.0   | 1.05   | 1.1   |              |  |

| Output Common Made Valtage             | \/cc+            | Bits CM1 = 0, CM0 = 1                        |                        |       | 0.95   |       |              |  |

| Output Common-Mode Voltage             | V <sub>СОМ</sub> | Bits CM1 = 1, CM0 = 0                        |                        |       | 0.80   |       | <del> </del> |  |

|                                        |                  | Bits CM1 = 1, CM0 = 1                        |                        |       | 0.71   |       |              |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD}=3V, OV_{DD}=1.8V, internal reference (1.024V), C_{L}\approx 10 pF on all digital outputs, f_{CLK}=45 MHz (50% duty cycle), Rx ADC input amplitude = -0.5 dBFS, Tx DAC output amplitude = 0 dBFS, differential Rx ADC input, differential Tx DAC output, C_{REFP}=C_{REFN}=C_{COM}=0.33 \mu F, unless otherwise noted. C_{L}<5 pF on all aux-DAC outputs. Typical values are at T_A=+25 °C.) (Note 1)$

| PARAMETER                                  | SYMBOL           | CONDITIONS                                                                                | MIN  | TYP                      | MAX  | UNITS |

|--------------------------------------------|------------------|-------------------------------------------------------------------------------------------|------|--------------------------|------|-------|

| Rx ADC-Tx DAC INTERCHANNEL                 | CHARACTE         | RISTICS                                                                                   |      |                          |      |       |

| Receive Transmit Isolation                 |                  | ADC $f_{INI} = f_{INQ} = 5.5MHz$ , DAC $f_{OUTI} = f_{OUTQ} = 2.2MHz$ , $f_{CLK} = 45MHz$ |      | 85                       |      | dB    |

| AUXILIARY ADC (ADC1, ADC2)                 |                  |                                                                                           |      |                          |      |       |

| Resolution                                 | N                |                                                                                           |      | 10                       |      | Bits  |

| Full-Scale Reference                       | V <sub>REF</sub> | AD1 = 0 (default)                                                                         |      | 2.048                    |      | V     |

| Tuli deale Helerenee                       | VHEF             | AD1 = 1                                                                                   |      | $V_{DD}$                 |      | ·     |

| Analog Input Range                         |                  |                                                                                           |      | 0 to<br>V <sub>REF</sub> |      | V     |

| Analog Input Impedance                     |                  | At DC                                                                                     |      | 500                      |      | kΩ    |

| Input-Leakage Current                      |                  | Measured at unselected input from 0 to VREF                                               |      | ±0.1                     |      | μΑ    |

| Gain Error                                 | GE               | Includes reference error                                                                  | -5   |                          | +5   | %FS   |

| Zero-Code Error                            | ZE               |                                                                                           |      | 2                        |      | mV    |

| Differential Nonlinearity                  | DNL              |                                                                                           |      | ±0.53                    |      | LSB   |

| Integral Nonlinearity                      | INL              |                                                                                           |      | ±0.45                    |      | LSB   |

| Supply Current                             |                  |                                                                                           |      | 210                      |      | μΑ    |

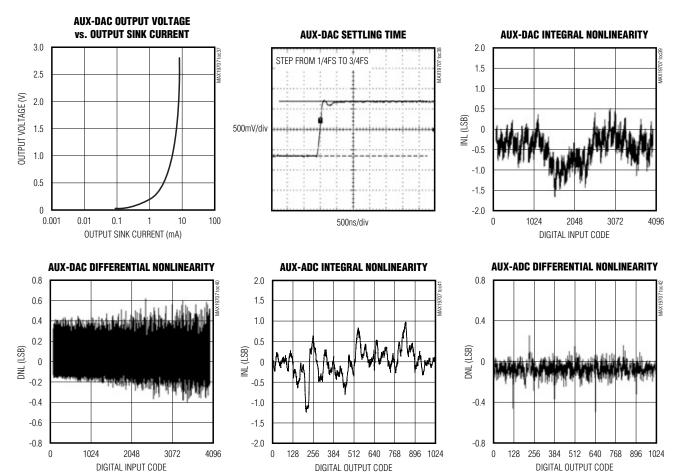

| AUXILIARY DACs (DAC1, DAC2, D              | AC3)             |                                                                                           |      |                          |      |       |

| Resolution                                 | N                | (Note 6)                                                                                  |      | 12                       |      | Bits  |

| Integral Nonlinearity                      | INL              |                                                                                           |      | ±1.25                    |      | LSB   |

| Differential Nonlinearity                  | DNL              | Guaranteed monotonic over codes 100 to 4000 (Note 6)                                      | -1.0 | ±0.65                    | +1.1 | LSB   |

| Gain Error                                 | GE               | $R_L > 200k\Omega$                                                                        |      | ±0.7                     |      | %FS   |

| Zero-Code Error                            | ZE               |                                                                                           |      | ±0.6                     |      | %FS   |

| Output-Voltage Low                         | VoL              | $R_L > 200k\Omega$                                                                        |      |                          | 0.1  | V     |

| Output-Voltage High                        | VoH              | $R_L > 200k\Omega$                                                                        | 2.56 |                          |      | V     |

| DC Output Impedance                        |                  | DC output at midscale                                                                     |      | 4                        |      | Ω     |

| Settling Time                              |                  | From 1/4 FS to 3/4 FS, within ±10 LSB                                                     |      | 1                        |      | μs    |

| Glitch Impulse                             |                  | From 0 to FS transition                                                                   |      | 24                       |      | nV∙s  |

| Rx ADC-Tx DAC TIMING CHARAC                | TERISTICS        |                                                                                           |      |                          |      |       |

| CLK Rise to Channel-I Output Data<br>Valid | tDOI             | Figure 3 (Note 6)                                                                         | 4.6  | 6.5                      | 8.5  | ns    |

| CLK Fall to Channel-Q Output<br>Data Valid | t <sub>DOQ</sub> | Figure 3 (Note 6)                                                                         | 6.8  | 8.8                      | 11.5 | ns    |

| I-DAC DATA to CLK Fall Setup<br>Time       | t <sub>DSI</sub> | Figure 5 (Note 6)                                                                         | 10   |                          |      | ns    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD}=3V,\,OV_{DD}=1.8V,\,$  internal reference (1.024V),  $C_L\approx 10$ pF on all digital outputs,  $f_{CLK}=45$ MHz (50% duty cycle), Rx ADC input amplitude = -0.5dBFS, Tx DAC output amplitude = 0dBFS, differential Rx ADC input, differential Tx DAC output,  $C_{REFP}=C_{REFN}=C_{COM}=0.33$ µF, unless otherwise noted.  $C_L<5$ pF on all aux-DAC outputs. Typical values are at  $T_A=+25$ °C.) (Note 1)

| PARAMETER                                                                | SYMBOL           | CONDITIONS                                                                                          | MIN | TYP  | MAX  | UNITS |

|--------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------|-----|------|------|-------|

| Q-DAC DATA to CLK Rise Setup<br>Time                                     | t <sub>DSQ</sub> | Figure 5 (Note 6)                                                                                   | 10  |      |      | ns    |

| CLK Fall to I-DAC Data Hold Time                                         | tDHI             | Figure 5 (Note 6)                                                                                   | 0   |      |      | ns    |

| CLK Rise to Q-DAC Data Hold Time                                         | tDHQ             | Figure 5 (Note 6)                                                                                   | 0   |      |      | ns    |

| CLK Duty Cycle                                                           |                  |                                                                                                     |     | 50   |      | %     |

| CLK Duty-Cycle Variation                                                 |                  |                                                                                                     |     | ±15  |      | %     |

| Digital Output Rise/Fall Time                                            |                  | 20% to 80%                                                                                          |     | 2.6  |      | ns    |

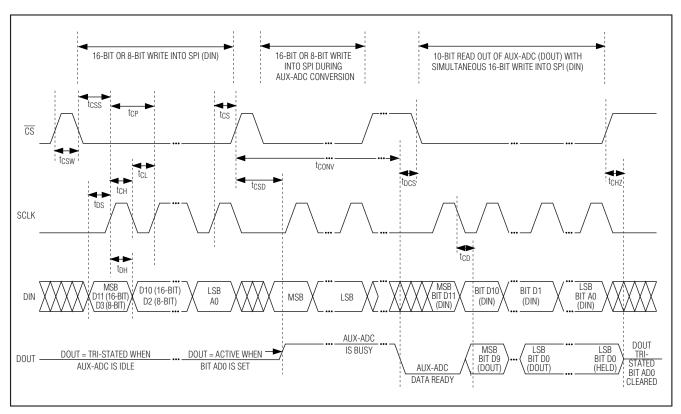

| SERIAL-INTERFACE TIMING CHA                                              | RACTERISTI       | CS (Figure 6, Note 6)                                                                               |     |      |      |       |

| Falling Edge of $\overline{\text{CS}}$ to Rising Edge of First SCLK Time | tcss             |                                                                                                     | 10  |      |      | ns    |

| DIN to SCLK Setup Time                                                   | tDS              |                                                                                                     | 10  |      |      | ns    |

| DIN to SCLK Hold Time                                                    | tDH              |                                                                                                     | 0   |      |      | ns    |

| SCLK Pulse-Width High                                                    | tсн              |                                                                                                     | 25  |      |      | ns    |

| SCLK Pulse-Width Low                                                     | t <sub>CL</sub>  |                                                                                                     | 25  |      |      | ns    |

| SCLK Period                                                              | tCP              |                                                                                                     | 50  |      |      | ns    |

| SCLK to CS Setup Time                                                    | tcs              |                                                                                                     | 10  |      |      | ns    |

| CS High Pulse Width                                                      | tcsw             |                                                                                                     | 80  |      |      | ns    |

| CS High to DOUT Active High                                              | tcsp             | Bit AD0 set                                                                                         |     | 200  |      | ns    |

| CS High to DOUT Low (Aux-ADC Conversion Time)                            | tCONV            | Bit AD0 set, no averaging (see Table 14), f <sub>CLK</sub> = 45MHz, CLK divider = 16 (see Table 15) |     | 4.27 |      | μs    |

| DOUT Low to CS Setup Time                                                | tDCS             | Bit AD0, AD10 set                                                                                   |     | 200  |      | ns    |

| SCLK Low to DOUT Data Out                                                | tcD              | Bit AD0, AD10 set                                                                                   |     |      | 14.5 | ns    |

| CS High to DOUT High Impedance                                           | tchz             | Bit AD0, AD10 set                                                                                   |     | 200  |      | ns    |

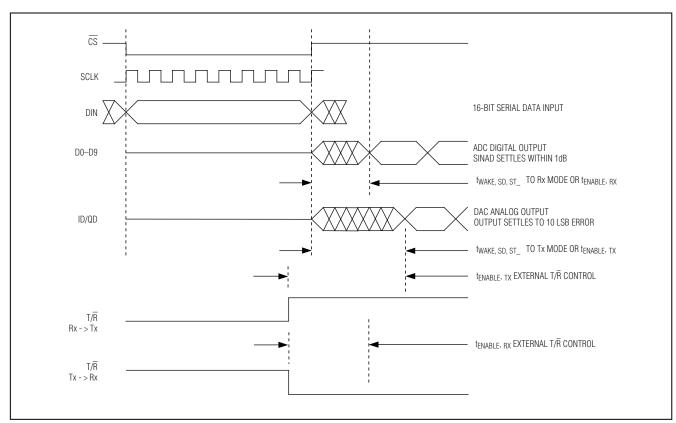

| MODE-RECOVERY TIMING CHARA                                               | ACTERISTICS      | S (Figure 7)                                                                                        |     |      |      |       |

| Object design Welse He Time                                              |                  | From shutdown to Rx mode, ADC settles to within 1dB SINAD                                           |     | 85.2 |      |       |

| Shutdown Wake-Up Time                                                    | twake,sd         | From shutdown to Tx mode, DAC settles to within 10 LSB error                                        |     | 28.2 |      | μs    |

| THE WALL TO AMERICAN                                                     |                  | From idle to Rx mode with CLK present during idle, ADC settles to within 1dB SINAD                  |     | 9.8  |      |       |

| Idle Wake-Up Time (With CLK)                                             | twake,sto        | From idle to Tx mode with CLK present during idle, DAC settles to 10 LSB error                      |     | 6.4  |      | μs    |

| Ctandby Waka Ha Time                                                     | h                | From standby to Rx mode, ADC settles to within 1dB SINAD                                            |     | 13.7 |      | 1.0   |

| Standby Wake-Up Time                                                     | twake,st1        | From standby to Tx mode, DAC settles to 10 LSB error                                                |     | 24   |      | μs    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD}=3V,\,OV_{DD}=1.8V,\,internal\,reference\,(1.024V),\,C_{L}\approx10$ pF on all digital outputs, f $_{CLK}=45$ MHz (50% duty cycle), Rx ADC input amplitude = -0.5dBFS, Tx DAC output amplitude = 0dBFS, differential Rx ADC input, differential Tx DAC output, CREFP = CREFN = CCOM = 0.33 µF, unless otherwise noted. CL < 5pF on all aux-DAC outputs. Typical values are at TA = +25°C.) (Note 1)

| PARAMETER                                                                                          | SYMBOL                              | CONDITIONS                                                                                  | MIN                           | TYP                 | MAX                           | UNITS     |

|----------------------------------------------------------------------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------|---------------------|-------------------------------|-----------|

| Enable Time from Tx to Rx, (Ext2-Tx to Ext2-Rx, Ext4-Tx to Ext4-Rx, and SPI4-Tx to SPI3-Rx States) | <sup>†</sup> ENABLE, RX             | ADC settles to within 1dB SINAD                                                             |                               | 500                 |                               | ns        |

| Enable Time from Rx to Tx, (Ext1-Rx to Ext1-Tx, Ext4-Rx to Ext4-Tx, and SPI3-Rx to SPI4-Tx States) | tENABLE, TX                         | DAC settles to within 10 LSB error                                                          |                               | 500                 |                               | ns        |

| Enable Time from Tx to Rx, (Ext1-Tx to Ext1-Rx, Ext3-Tx to Ext3-Rx, and SPI1-Tx to SPI2-Rx States) | tENABLE, RX                         | ADC settles to within 1dB SINAD                                                             |                               | 4.1                 |                               | μs        |

| Enable Time from Rx to Tx, (Ext2-Rx to Ext2-Tx, Ext3-Rx to Ext3-Tx, and SPI1-Rx to SPI2-Tx States) | tENABLE, TX                         | DAC settles to within 10 LSB error                                                          |                               | 7.0                 |                               | μs        |

| INTERNAL REFERENCE (VREFIN =                                                                       | V <sub>DD</sub> ; V <sub>REFP</sub> | , V <sub>REFN</sub> , V <sub>COM</sub> levels are generated internal                        | lly)                          |                     |                               |           |

| Positive Reference                                                                                 |                                     | VREFP - VCOM                                                                                |                               | 0.256               |                               | V         |

| Negative Reference                                                                                 |                                     | VREFN - VCOM                                                                                |                               | -0.256              |                               | V         |

| Common-Mode Output Voltage                                                                         | VCOM                                |                                                                                             | V <sub>DD</sub> / 2<br>- 0.15 | V <sub>DD</sub> / 2 | V <sub>DD</sub> / 2<br>+ 0.15 | V         |

| Maximum REFP/REFN/COM Source Current                                                               | ISOURCE                             |                                                                                             |                               | 2                   |                               | mA        |

| Maximum REFP/REFN/COM Sink Current                                                                 | ISINK                               |                                                                                             |                               | 2                   |                               | mA        |

| Differential Reference Output                                                                      | V <sub>REF</sub>                    | VREFP - VREFN                                                                               | +0.489                        | +0.512              | +0.534                        | V         |

| Differential Reference Temperature<br>Coefficient                                                  | REFTC                               |                                                                                             |                               | ±10                 |                               | ppm/°C    |

| BUFFERED EXTERNAL REFEREN                                                                          | CE (external                        | V <sub>REFIN</sub> = 1.024V applied; V <sub>REFP</sub> , V <sub>REFN</sub> , V <sub>C</sub> | OM level                      | s are gen           | erated in                     | ternally) |

| Reference Input Voltage                                                                            | VREFIN                              |                                                                                             |                               | 1.024               |                               | V         |

| Differential Reference Output                                                                      | V <sub>DIFF</sub>                   | VREFP - VREFN                                                                               |                               | 0.512               |                               | V         |

| Common-Mode Output Voltage                                                                         | V <sub>COM</sub>                    |                                                                                             |                               | V <sub>DD</sub> /2  |                               | V         |

| Maximum REFP/REFN/COM Source Current                                                               | ISOURCE                             |                                                                                             |                               | 2                   |                               | mA        |

| Maximum REFP/REFN/COM Sink Current                                                                 | ISINK                               |                                                                                             |                               | 2                   |                               | mA        |

| REFIN Input Current                                                                                |                                     |                                                                                             |                               | -0.7                |                               | μΑ        |

| REFIN Input Resistance                                                                             |                                     |                                                                                             |                               | 500                 |                               | kΩ        |

|                                                                                                    |                                     |                                                                                             |                               |                     |                               |           |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD}=3V,\,OV_{DD}=1.8V,\,$  internal reference (1.024V),  $C_L\approx 10$ pF on all digital outputs,  $f_{CLK}=45$ MHz (50% duty cycle), Rx ADC input amplitude = -0.5dBFS, Tx DAC output amplitude = 0dBFS, differential Rx ADC input, differential Tx DAC output,  $C_{REFP}=C_{REFN}=C_{COM}=0.33$ µF, unless otherwise noted.  $C_L<5$ pF on all aux-DAC outputs. Typical values are at  $T_A=+25$ °C.) (Note 1)

| PARAMETER                    | SYMBOL           | CONDITIONS                                                                                               | MIN                    | TYP I | MAX              | UNITS |

|------------------------------|------------------|----------------------------------------------------------------------------------------------------------|------------------------|-------|------------------|-------|

| DIGITAL INPUTS (CLK, SCLK, D | N, CS, D0-D9,    | T/R, SHDN)                                                                                               | •                      |       |                  |       |

| Input High Threshold         | VINH             |                                                                                                          | 0.7 x OV <sub>DE</sub> | )     |                  | V     |

| Input Low Threshold          | VINL             |                                                                                                          |                        | 0.3 x | OV <sub>DD</sub> | V     |

| Input Leakage                | DI <sub>IN</sub> | D0-D9, CLK, SCLK, DIN, $\overline{CS}$ , $\overline{T/R}$ , $\overline{SHDN}$ = OGND or OV <sub>DD</sub> | -1                     |       | +1               | μΑ    |

| Input Capacitance            | DCIN             |                                                                                                          |                        | 5     |                  | рF    |

| DIGITAL OUTPUTS (D0-D9, DOU  | T)               |                                                                                                          |                        |       |                  |       |

| Output-Voltage Low           | VoL              | ISINK = 200µA                                                                                            |                        | 0.2 x | OV <sub>DD</sub> | V     |

| Output-Voltage High          | VoH              | ISOURCE = 200µA                                                                                          | 0.8 x OV <sub>DE</sub> | )     |                  | V     |

| Tri-State Leakage Current    | ILEAK            |                                                                                                          | -1                     |       | +1               | μΑ    |

| Tri-State Output Capacitance | Cout             |                                                                                                          |                        | 5     | •                | рF    |

- Note 1: Specifications from T<sub>A</sub> = +25°C to +85°C are guaranteed by production tests. Specifications from T<sub>A</sub> = +25°C to -40°C are guaranteed by design and characterization.

- Note 2: The minimum clock frequency (f<sub>CLK</sub>) for the MAX19707 is 7.5MHz (typical). The minimum aux-ADC sample rate clock frequency (ACLK) is determined by f<sub>CLK</sub> and the chosen aux-ADC clock-divider value. The minimum aux-ADC ACLK > 7.5MHz / 128 = 58.6kHz. The aux-ADC conversion time does not include the time to clock the serial data out of the SPI™. The maximum conversion time (for no averaging, NAVG = 1) will be, t<sub>CONV</sub> (max) = (12 x 1 x 128) / 7.5MHz = 205µs.

- **Note 3:** SNR, SINAD, SFDR, HD3, and THD are based on a differential analog input voltage of -0.5dBFS referenced to the amplitude of the digital outputs. SINAD and THD are calculated using HD2 through HD6.

- **Note 4:** Crosstalk rejection is measured by applying a high-frequency test tone to one channel and a low-frequency tone to the second channel. FFTs are performed on each channel. The parameter is specified as the power ratio of the first and second channel FFT test tone.

- **Note 5:** Amplitude and phase matching is measured by applying the same signal to each channel, and comparing the two output signals using a sine-wave fit.

- Note 6: Guaranteed by design and characterization.

SPIはMotorola, Inc.の商標です。

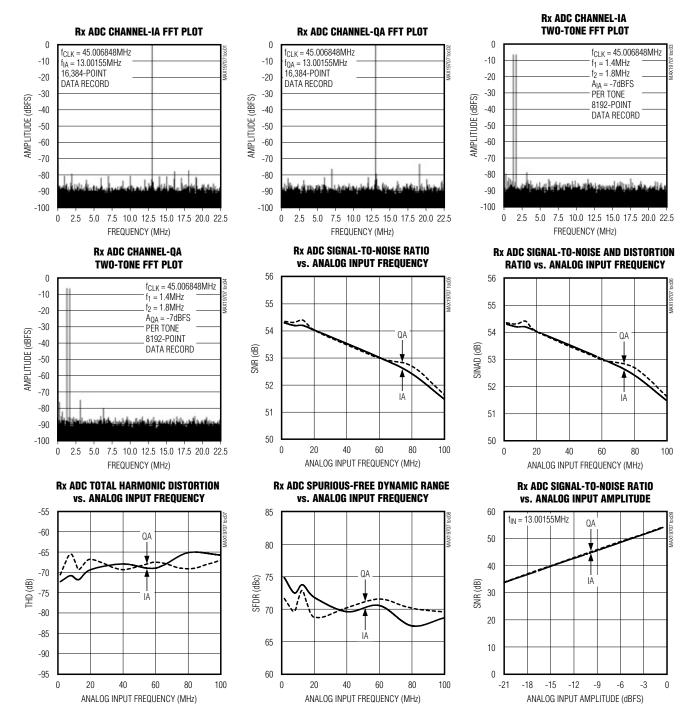

### 標準動作特性

$(V_{DD}=3V,\ OV_{DD}=1.8V,\ internal\ reference\ (1.024V),\ C_L\approx 10pF$  on all digital outputs,  $f_{CLK}=45MHz$  (50% duty cycle), Rx ADC input amplitude = -0.5dBFS, Tx DAC output amplitude = 0dBFS, differential Rx ADC input, differential Tx DAC output,  $C_{REFP}=C_{REFN}=C_{COM}=0.33\mu F,\ T_A=+25^{\circ}C,\ unless otherwise\ noted.)$

# 10ビット、45Msps、超低電力 アナログフロ<u>ントエンド</u>

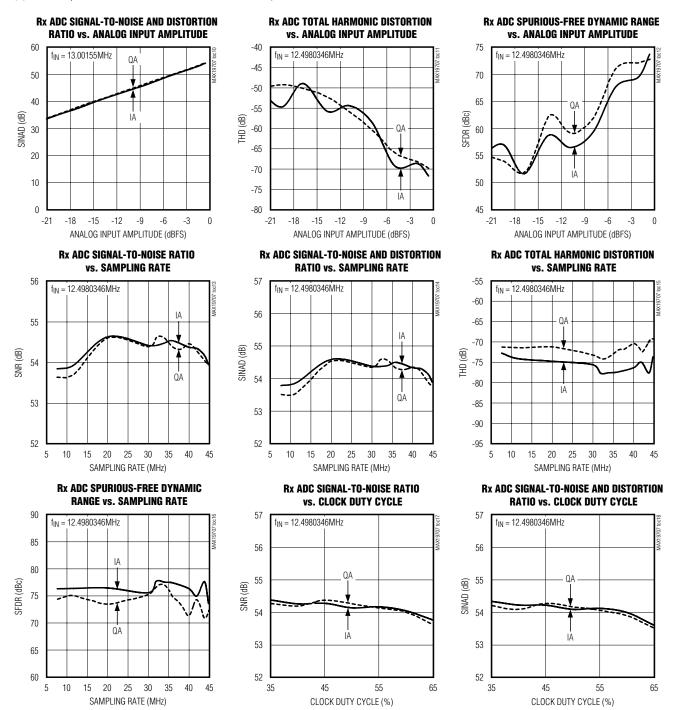

### 標準動作特性(続き)

$(V_{DD}=3V,\,OV_{DD}=1.8V,\,$  internal reference (1.024V),  $C_L\approx 10$ pF on all digital outputs,  $f_{CLK}=45$ MHz (50% duty cycle), Rx ADC input amplitude = -0.5dBFS, Tx DAC output amplitude = 0dBFS, differential Rx ADC input, differential Tx DAC output,  $C_{REFP}=C_{REFN}=C_{COM}=0.33$ µF,  $T_A=+25$ °C, unless otherwise noted.)

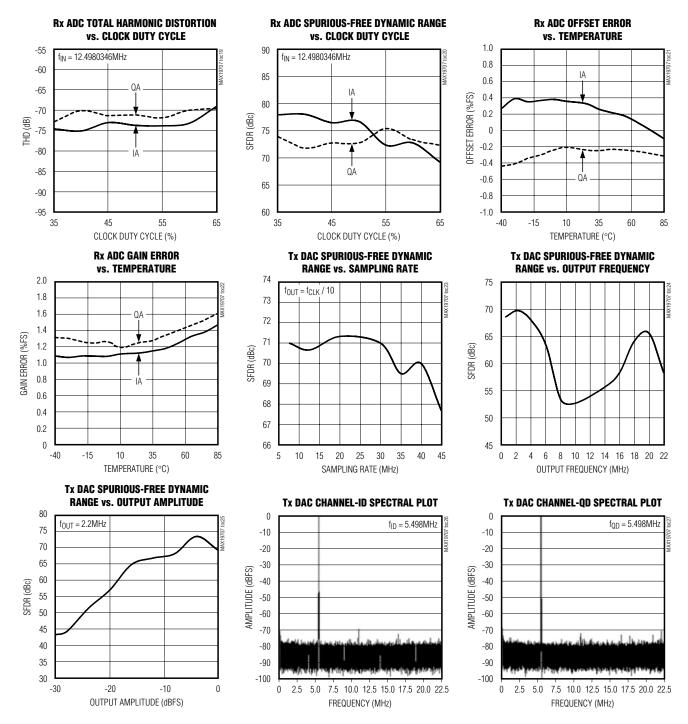

### 標準動作特性(続き)

$(V_{DD}=3V,\,OV_{DD}=1.8V,\,$  internal reference (1.024V),  $C_L\approx 10$ pF on all digital outputs,  $f_{CLK}=45$ MHz (50% duty cycle), Rx ADC input amplitude = -0.5dBFS, Tx DAC output amplitude = 0dBFS, differential Rx ADC input, differential Tx DAC output,  $C_{REFP}=C_{REFN}=C_{COM}=0.33$ µF,  $T_A=+25$ °C, unless otherwise noted.)

# 10ビット、45Msps、超低電力 アナログフロ<u>ントエンド</u>

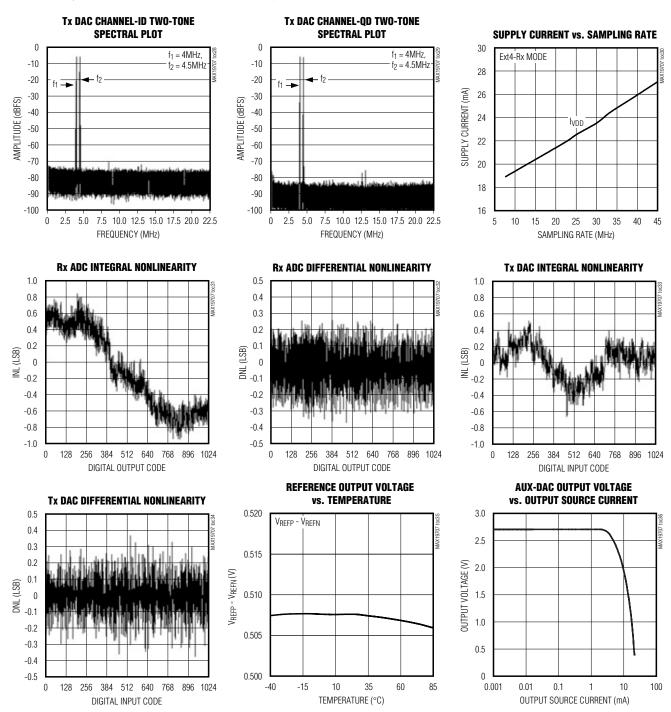

### 標準動作特性(続き)

$(V_{DD}=3V,\,OV_{DD}=1.8V,\,$  internal reference (1.024V),  $C_L\approx 10$ pF on all digital outputs,  $f_{CLK}=45$ MHz (50% duty cycle), Rx ADC input amplitude = -0.5dBFS, Tx DAC output amplitude = 0dBFS, differential Rx ADC input, differential Tx DAC output,  $C_{REFP}=C_{REFN}=C_{COM}=0.33$ µF,  $T_{A}=+25$ °C, unless otherwise noted.)

### 標準動作特性(続き)

$(V_{DD}=3V,\,OV_{DD}=1.8V,\,$  internal reference (1.024V),  $C_{L}\approx 10$ pF on all digital outputs,  $f_{CLK}=45$ MHz (50% duty cycle), Rx ADC input amplitude = -0.5dBFS, Tx DAC output amplitude = 0dBFS, differential Rx ADC input, differential Tx DAC output,  $C_{REFP}=C_{REFN}=C_{COM}=0.33$ µF,  $T_{A}=+25$ °C, unless otherwise noted.)

#### 端子説明

| 端子                          | 名称       | 機能                                                                           |

|-----------------------------|----------|------------------------------------------------------------------------------|

| 1                           | REFP     | 上側リファレンス電圧。REFPのできる限り近くで、0.33µFのコンデンサでGNDにバイパスしてください。                        |

| 2, 8, 11, 31,<br>33, 39, 43 | $V_{DD}$ | アナログ電源電圧。 $V_{DD}$ を $0.1\mu F$ のコンデンサと並列の $2.2\mu F$ のコンデンサでGNDにバイパスしてください。 |

| 3                           | IAP      | チャネルIAの正アナログ入力。シングルエンド動作の場合は、信号ソースをIAPに接続してください。                             |

| 4                           | IAN      | チャネルIAの負アナログ入力。シングルエンド動作の場合は、IANをCOMに接続してください。                               |

| 5, 7, 12, 32, 42            | GND      | アナロググランド。すべてのGNDピンをグランドプレーンに接続してください。                                        |

| 6                           | CLK      | 変換クロック入力。受信ADCと送信DACの両方に対するクロック信号。                                           |

| 9                           | QAN      | チャネルQAの負アナログ入力。シングルエンド動作の場合は、QANをCOMに接続してください。                               |

### 端子説明(続き)

| 端子           | 名称               | 機能                                                                                                         |

|--------------|------------------|------------------------------------------------------------------------------------------------------------|

| 10           | QAP              | チャネルQAの正アナログ入力。シングルエンド動作の場合は、信号ソースをQAPに接続してください。                                                           |

| 13–18, 21–24 | D0-D9            | ディジタルI/O。Rxモードにおける受信ADC用出力。Txモードにおける送信DAC用入力。D9が最上位ビット(MSB)で、D0が最下位ビット(LSB)です。                             |

| 19           | OGND             | 出力ドライバグランド。                                                                                                |

| 20           | OV <sub>DD</sub> | 出力ドライバ電源。電圧範囲は $+1.8V\sim V_{DD}$ です。 $OV_{DD}$ を $0.1\mu F$ のコンデンサと並列の $2.2\mu F$ のコンデンサでOGNDにバイパスしてください。 |

| 25           | SHDN             | アクティブローシャットダウン入力。MAX19707をシャットダウンするためには、ロジックローを印加してください。                                                   |

| 26           | DOUT             | 補助ADCディジタル出力。                                                                                              |

| 27           | T/R              | 送信または受信モード選択入力。T/Rのロジックロー入力でデバイスは受信モードに設定されます。<br>ロジックハイ入力でデバイスは送信モードに設定されます。                              |

| 28           | DIN              | 3線式シリアルインタフェースデータ入力。データはSCLKの立上りエッジでラッチされます。                                                               |

| 29           | SCLK             | 3線式シリアルインタフェースクロック入力                                                                                       |

| 30           | CS               | 3線式シリアルインタフェースチップ選択入力。ロジックローでシリアルインタフェースはイネーブルされます。                                                        |

| 34           | ADC2             | 補助ADC用アナログ入力                                                                                               |

| 35           | ADC1             | 補助ADC用アナログ入力                                                                                               |

| 36           | DAC3             | 補助DAC3用アナログ出力                                                                                              |

| 37           | DAC2             | 補助DAC2用アナログ出力                                                                                              |

| 38           | DAC1             | 補助DAC1用アナログ出力(AFC DAC、V <sub>OUT</sub> = 1.1V(電源投入時))                                                      |

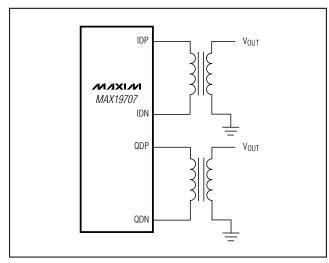

| 40, 41       | IDN, IDP         | DACチャネルID差動電圧出力                                                                                            |

| 44, 45       | QDN, QDP         | DACチャネルQD差動電圧出力                                                                                            |

| 46           | REFIN            | リファレンス入力。内部リファレンスとする場合は、V <sub>DD</sub> に接続してください。                                                         |

| 47           | COM              | コモンモード電圧I/O。COMを0.33µFのコンデンサでGNDにバイパスしてください。                                                               |

| 48           | REFN             | 負リファレンスI/O。Rx ADCの変換範囲は±(V <sub>REFP</sub> - V <sub>REFN</sub> )です。REFNを0.1μFのコンデンサでGNDにバイパスしてください。        |

| _            | EP               | エクスポーズドパッド。エクスポーズドパッドは内部でGNDに接続されています。EPをGNDプレーンに接続してください。                                                 |

#### 詳細

MAX19707は、デュアル、10ビットのRx ADCとデュアル、10ビットのTx DACを内蔵しており、45Mspsの変換レートで超低電力と高ダイナミック性能を提供します。Rx ADCアナログ入力アンプは、完全差動型で、1.024VP-Pのフルスケール信号を受け付けます。Tx DACアナログ出力は、完全差動型で、 $\pm 400$ mVのフルスケール出力、選択可能なコモンモードDCレベル、および可変I/Qオフセット調整を備えています。

MAX19707は、3つの12ビット補助DAC(aux-DAC) チャネル、および4:1の入力マルチプレクサ付き10ビット、333ksps補助ADC(aux-ADC)を内蔵しています。補助DACチャネルは、高速自動利得制御(AGC)のための1 $\mu$ sのセトリング時間、可変利得アンプ(VGA)、および自動周波数制御(AFC)レベル設定を備えています。

補助ADCは、プロセッサのオーバヘッドを低減するデータ平均化、および変換レートを設定するための選択可能なクロック分周器を備えています。

MAX19707は、動作モードと電源管理を制御するための 3線式シリアルインタフェースを内蔵しています。シリ アルインタフェースは、SPIおよびMICROWIRE™に対応 しています。MAX19707のシリアルインタフェースは、 シャットダウン、アイドル、スタンバイ、送信(Tx)、および 受信(Rx)の各モードを選択し、かつ補助DACおよび 補助ADCチャネルを制御します。

ディジタルインタフェースを単一の10ビットパラレル 多重化バスとするために、Rx ADCとTx DACに共通 ディジタルI/Oを共有させています。この10ビットディジ タルバスは、+1.8V~+3.3Vの単一電源で動作します。

MICROWIREはNational Semiconductor Corp.の商標です。

### デュアル、10ビットRx ADC

ADCには、消費電力を最小限に抑えながら高速変換が可能な7段から成る完全差動のパイプラインアーキテクチャが採用されています。入力に取り込まれたサンプルは、1/2クロックサイクルごとにパイプラインステージを順次移動します。出力ラッチによる遅延を含む全クロックサイクルの待ち時間は、チャネルIAでは5クロックサイクルで、チャネルQAでは5.5クロックサイクルです。ADCのフルスケールアナログ入力範囲は ${}^{1}$  VREFで、コモンモード入力範囲は ${}^{1}$  VDD/2  ${}^{1}$   ${}^{1}$   ${}^{2}$   ${}^{2}$   ${}^{3}$   ${}^{2}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$   ${}^{3}$

$V_{REFP}$ と $V_{REFN}$ の差です。詳しくは、「リファレンスの構成」の項をご覧ください。

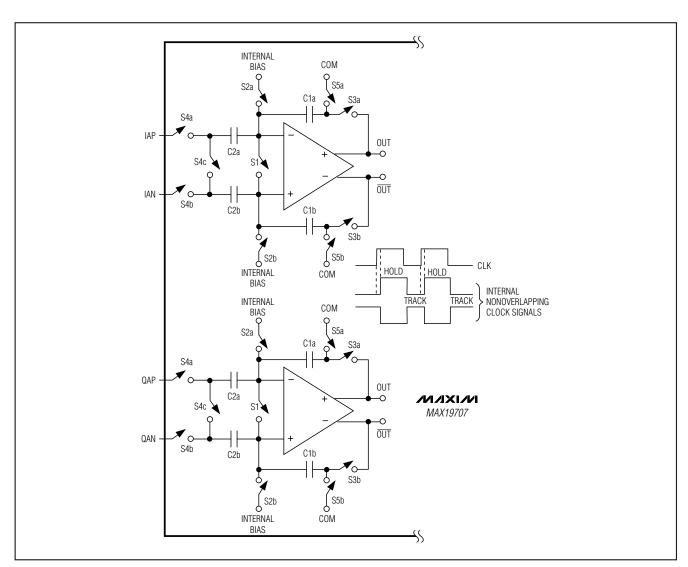

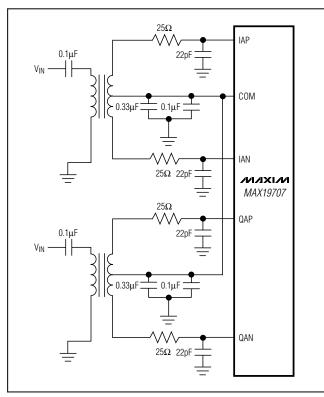

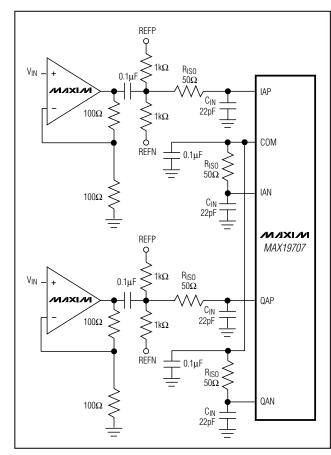

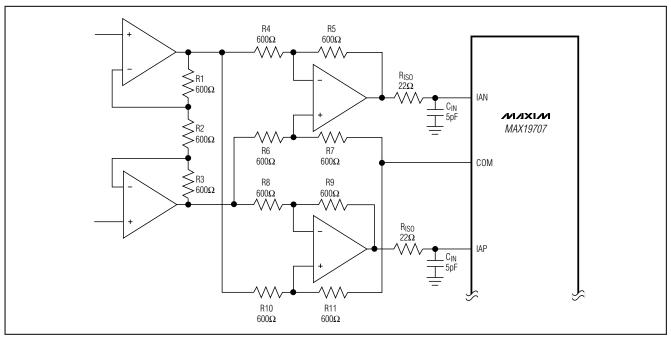

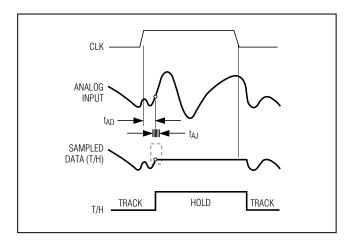

#### 入力トラック/ホールド(T/H)回路

図1は、Rx ADCの入力トラック/ホールド(T/H)回路の簡略図を示します。ADC入力(IAP)、QAP、IAN、および QAN)はいずれも、差動またはシングルエンドのいずれかで駆動することができます。IAPとIAN、およびIAPとQANのインピーダンスを整合させ、入力信号のコモンモード電圧を最適性能が得られるIAP0のIAP1のIAP2のIAP2のIAP2のIAP2のIAP2のIAP3のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP4のIAP

図1. Rx ADCの内部T/H回路

### 表1. Rx ADCの出力コードと入力電圧

| DIFFERENTIAL INPUT<br>VOLTAGE | DIFFERENTIAL INPUT (LSB)  | OFFSET BINARY (D0-D9) | OUTPUT DECIMAL CODE |

|-------------------------------|---------------------------|-----------------------|---------------------|

| V <sub>REF</sub> x 512/512    | 511 (+Full Scale - 1 LSB) | 11 1111 1111          | 1023                |

| V <sub>REF</sub> x 511/512    | 510 (+Full Scale - 2 LSB) | 11 1111 1110          | 1022                |

| V <sub>REF</sub> x 1/512      | +1                        | 10 0000 0001          | 513                 |

| V <sub>REF</sub> x 0/512      | 0 (Bipolar Zero)          | 10 0000 0000          | 512                 |

| -V <sub>REF</sub> x 1/512     | -1                        | 01 1111 1111          | 511                 |

| -V <sub>REF</sub> x 511/512   | -511 (-Full Scale +1 LSB) | 00 0000 0001          | 1                   |

| -V <sub>REF</sub> x 512/512   | -512 (-Full Scale)        | 00 0000 0000          | 0                   |

図2. Rx ADCの伝達関数

#### Rx ADCシステムのタイミング要件

図3は、クロック、アナログ入力、および得られた出力データの関係を示します。チャネルI(CHI)とチャネルQ(CHQ)は、クロック信号(CLK)の立上りエッジでサンプリングされ、得られたデータは出力D0~D9で多重化されます。CHIのデータはCLKの立上りエッジで更新され、CHQのデータはCLKの立下りエッジで更新されます。出力ラッチによる遅延を含む全クロックサイクル待ち時間は、CHIでは5クロックサイクルで、CHQでは5.5クロックサイクルです。

#### ディジタル入力/出力データ(D0~D9)

MAX19707が受信モードにあるとき、D0~D9はRx ADCのディジタルロジック出力です。このバスは、 各Tx DACディジタルロジック入力に共用され、ハーフ デュープレクスモードで動作します。MAX19707が 送信モードにあるとき、D0~D9はTx DACのディジタル ロジック入力です。ロジックレベルは、1.8V~V<sub>DD</sub>の OV<sub>DD</sub>によって設定されます。ディジタル出力コードは オフセットバイナリです(表1)。MAX19707のアナログ 部に大きなディジタル電流がフィードバックされてその ダイナミック性能が低下することのないように、ディジ タル出力DO~D9の容量性負荷をできる限り小さく (15pF以下)保ってください。ディジタル出力のバッファ によって、出力は容量性の重負荷から分離されます。 MAX19707の近くでディジタル出力と直列に100Ωの 抵抗器を接続すると、Rx ADCとTx DACの性能が改善 されます。100Ωの直列抵抗器を介してディジタル バッファを駆動するディジタル出力の例については、 MAX19707EVKITの回路図を参照してください。

シャットダウン、アイドル、およびスタンバイ状態でディジタル入力が開放されないように、DO~D9は内部でプルアップされています。DO~D9 I/Oを通して電流が流れないようにするためには、外部バスをトライステートとするかまたはOV<sub>DD</sub>にプルアップする必要があり、グランドに駆動してはなりません。

図3. Rx ADCシステムのタイミング図

### デュアル、10ビットTx DAC

デュアル、10ビットのディジタル-アナログコンバータ (Tx DAC)は、最大45MHzのクロック速度で動作します。 Tx DACの各ディジタル入力DO~D9は、単一の10ビットバス上に多重化されています。電圧リファレンスは、Tx DACのフルスケール出力電圧を決定します。リファレンス電圧の設定に関する詳細については、「リファレンスの構成」の項をご覧ください。

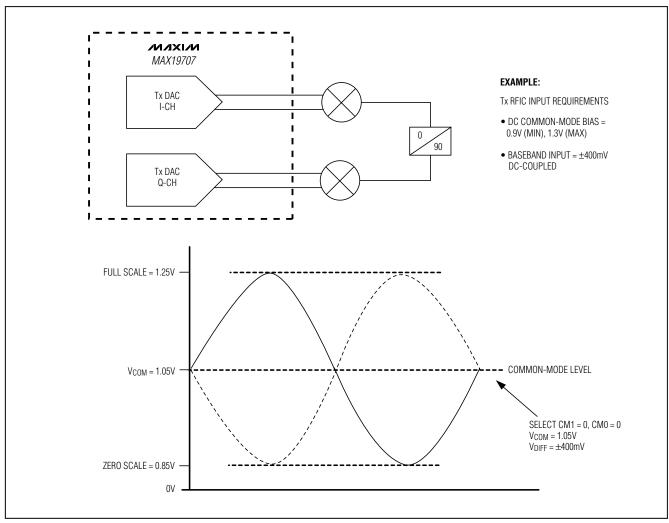

IDN、IDP、およびQDN、QDPにおける各Tx DAC出力は、 $0.7V\sim1.05V$ の可変DCコモンモードバイアスにバイアスされ、 $70k\Omega$ 以上の入力インピーダンスを有する差動入力段を駆動するように設計されています。

このため、RF直交アップコンバータとMAX19707の間のアナログインタフェースが簡素化されます。多くのRFアップコンバータは、 $0.7V\sim1.05V$ のコモンモードバイアスを必要とします。Tx DACのDCコモンモードバイアスは個別のレベル設定抵抗器とコードが生成するレベルシフトが不要となり同時に各Tx DACのフルダイナミックレンジが維持されます。Tx DACの差動アナログ出力はシングルエンドモードで使用することができません。これはコモンモードDCレベルが内部で生成されるためです。表2は、Tx DACの出力電圧と入力コードの関係を示します。表10は、DCコモンモードレベルの選択を示します。Tx DACアナログ出力レベルの説明については、図4を参照してください。

### 表2. Tx DACの出力電圧と入力コード

(Internal Reference Mode VREFDAC = 1.024V, External Reference Mode VREFDAC = VREFIN; VFS = ±400 for 800mVp-p Full Scale)

| DIFFERENTIAL OUTPUT VOLTAGE (V)                              | OFFSET BINARY (D0-D9) | INPUT DECIMAL CODE |

|--------------------------------------------------------------|-----------------------|--------------------|

| $(V_{FS})\frac{V_{REFDAC}}{1024} \times \frac{1023}{1023}$   | 11 1111 1111          | 1023               |

| $(V_{FS}) \frac{V_{REFDAC}}{1024} \times \frac{1021}{1023}$  | 11 1111 1110          | 1022               |

| $(V_{FS}) \frac{V_{REFDAC}}{1024} \times \frac{3}{1023}$     | 10 0000 0001          | 513                |

| $ (V_{FS}) \frac{V_{REFDAC}}{1024} \times \frac{1}{1023} $   | 10 0000 0000          | 512                |

| $ (V_{FS}) \frac{-V_{REFDAC}}{1024} \times \frac{1}{1023} $  | 01 1111 1111          | 511                |

| $(V_{FS}) \frac{-V_{REFDAC}}{1024} \times \frac{1021}{1023}$ | 00 0000 0001          | 1                  |

| $(V_{FS}) \frac{-V_{REFDAC}}{1024} \times \frac{1023}{1023}$ | 00 0000 0000          | 0                  |

また、Tx DACでは、各I/QチャネルのDCオフセット補正が独立に行われます。この機能はSPIインタフェースを通じて設定されます。DCオフセット補正は、Tx信号

経路において側波帯および搬送波の抑圧を最適化するために使用されます(表9参照)。

図4. IDN、IDP、またはQDN、QDP差動出力でのTx DACのコモンモードDCレベル

#### Tx DACのタイミング

図5は、クロック、入力データ、およびアナログ出力の関係を示します。Iチャネルのデータ(ID)はクロック信号の立下りエッジでラッチされ、Qチャネルのデータ(QD)はクロック信号の立上りエッジでラッチされます。I出力とQ出力は、クロック信号の次の立上りエッジで同時に更新されます。

#### 3線式シリアルインタフェースおよび動作モード

3線式シリアルインタフェースは、MAX19707の動作モードおよび3つの12ビット補助DACと10ビット補助ADCを制御します。電源投入時に、MAX19707を所望のモードで動作するように設定してください。シャットダウン、アイドル、スタンバイ、Rx、Tx、補助DACの各制御、または補助ADC変換に関してデバイスを設定するためには、3線式シリアルインタフェースを使用してください。16ビットデータレジスタによって、表3に示すようにモード制御を設定します。16ビットワードは、A3~A0の制御ビットとD11~D0のデータ

ビットで構成されます。データは、MSB(D11)を先頭としてLSB(A0)が最後にシフトインされます。表4、5、および6は、MAX19707の動作モードおよびSPIコマンドを示します。シリアルインタフェースは、すべてのモードでアクティブのままです。

#### SPIレジスタの説明

動作モードを選択するためには、レジスタの制御ビット  $A3 \sim A0$  を表3に示すように設定してください。 ENABLE-16、補助DAC1、補助DAC2、補助DAC3、IOFFSET、QOFFSET、補助ADC、ENABLE-8、および COMSELの各モードを選択するためには、 $A3 \sim A0$  ビットを変更してください。ENABLE-16はデフォルトの動作モードです。このモーでは、シャットダウン、アイドル、およびスタンバイの各状態が可能であり、また高速、低速、Rx、およびTxの各モードの切替えが可能です。表4はMAX19707の電源管理モードを示します。表5は、T/R端子で制御される外部Tx-Rxの切替えモードを示します。表6は、SPIで制御されるTx-Rxの切替えモードを示します。

図5. Tx DACシステムのタイミング図

### 表3. MAX19707のモード制御

| REGISTER  | D11                  | D10                 | D9  | D8  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  | А3 | A2 | <b>A</b> 1 | A0      |

|-----------|----------------------|---------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|------------|---------|

| NAME      | (MSB)                | 15                  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4  | 3  | 2          | 1 (LSB) |

| ENABLE-16 | E11 = 0<br>Reserved  | E10 = 0<br>Reserved | E9  | _   | _   | E6  | E5  | E4  | E3  | E2  | E1  | E0  | 0  | 0  | 0          | 0       |

| Aux-DAC1  | 1D11                 | 1D10                | 1D9 | 1D8 | 1D7 | 1D6 | 1D5 | 1D4 | 1D3 | 1D2 | 1D1 | 1D0 | 0  | 0  | 0          | 1       |

| Aux-DAC2  | 2D11                 | 2D10                | 2D9 | 2D8 | 2D7 | 2D6 | 2D5 | 2D4 | 2D3 | 2D2 | 2D1 | 2D0 | 0  | 0  | 1          | 0       |

| Aux-DAC3  | 3D11                 | 3D10                | 3D9 | 3D8 | 3D7 | 3D6 | 3D5 | 3D4 | 3D3 | 3D2 | 3D1 | 3D0 | 0  | 0  | 1          | 1       |

| IOFFSET   |                      |                     |     |     |     | _   | 105 | 104 | 103 | 102 | IO1 | IO0 | 0  | 1  | 0          | 0       |

| QOFFSET   | _                    |                     |     |     |     | _   | Q05 | Q04 | QO3 | Q02 | Q01 | QO0 | 0  | 1  | 0          | 1       |

| COMSEL    | _                    | _                   | _   | _   | _   | _   | _   | _   | _   | _   | CM1 | CM0 | 0  | 1  | 1          | 0       |

| Aux-ADC   | AD11 = 0<br>Reserved | AD10                | AD9 | AD8 | AD7 | AD6 | AD5 | AD4 | AD3 | AD2 | AD1 | AD0 | 0  | 1  | 1          | 1       |

| ENABLE-8  | _                    | _                   | _   | _   | _   | _   | _   |     | E3  | E2  | E1  | E0  | 1  | 0  | 0          | 0       |

<sup>- =</sup> 空き

### 表4. 電源管理モード

|    | ADDRESS                                             |            | 6  | DATA BITS |            |    |    |    | T/R    | MODE | FUNCTION              |                                                                           |                                                                  |         |                                                                                 |                                                                |

|----|-----------------------------------------------------|------------|----|-----------|------------|----|----|----|--------|------|-----------------------|---------------------------------------------------------------------------|------------------------------------------------------------------|---------|---------------------------------------------------------------------------------|----------------------------------------------------------------|

| А3 | A2                                                  | <b>A</b> 1 | Α0 | E9*       | <b>E</b> 3 | E2 | E1 | E0 | PIN 27 | MODE | (POWER<br>MANAGEMENT) | DESCRIPTION                                                               | COMMENT                                                          |         |                                                                                 |                                                                |

|    |                                                     |            |    |           | 1X000      |    |    |    |        | SHDN | SHUTDOWN              | Rx ADC = OFF Tx DAC = OFF Aux-DAC = OFF Aux-ADC = OFF CLK = OFF REF = OFF | Device is in complete shutdown. Overrides T/R pin.               |         |                                                                                 |                                                                |

| ,  | 0000<br>(16-Bit Mode)<br>or<br>1000<br>(8-Bit Mode) |            |    | XX001     |            |    |    |    | X      | IDLE | IDLE                  | Rx ADC = OFF Tx DAC = OFF Aux-DAC = Last State CLK = ON REF = ON          | Fast turn-on time.<br>Moderate idle power.<br>Overrides T/R pin. |         |                                                                                 |                                                                |

|    |                                                     |            |    | 1X010     |            |    |    |    | 1X010  |      |                       | X                                                                         | STBY                                                             | STANDBY | Rx ADC = OFF Tx DAC = OFF Aux-DAC = Last State Aux-ADC = OFF CLK = OFF REF = ON | Slow turn-on time.<br>Low standby power.<br>Overrides T/R pin. |

X = 任意

<sup>\*8</sup>ビットモードではビットE9がありません。

### 表5. $T/\overline{R}$ ピンを使用した外部Tx-Rx制御 $(T/\overline{R}=0=Rx$ モード、 $T/\overline{R}=1=Tx$ モード)

| A   | ADDF                  | RESS       | 3  | D          | ATA | BIT | S  | T/R     | STATE                | FUNCTION<br>Rx TO Tx-Tx TO Rx                              | DESCRIPTION                                                      | COMMENT                                                          |

|-----|-----------------------|------------|----|------------|-----|-----|----|---------|----------------------|------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------|

| А3  | <b>A2</b>             | <b>A</b> 1 | Α0 | <b>E</b> 3 | E2  | E1  | E0 | PIN 27  |                      | SWITCHING SPEED                                            |                                                                  |                                                                  |

|     |                       |            |    |            | 00  |     |    | 0       | Ext1-Rx              | FAST-SLOW                                                  | Rx Mode:<br>Rx ADC = ON<br>Tx DAC = ON<br>Rx Bus = Enable        | Moderate Power:<br>Fast Rx to Tx when T/R<br>transitions 0 to 1. |

|     |                       |            |    |            | 00  |     |    | 1       | Ext1-Tx              | FAST-SLOW                                                  | Tx Mode:<br>Rx ADC = OFF<br>Tx DAC = ON<br>Tx Bus = Enable       | Low Power:<br>Slow Tx to Rx when T/R<br>transitions 1 to 0.      |

|     |                       |            |    | 0100       |     |     |    | 0       | Ext2-Rx<br>(Default) | SLOW-FAST                                                  | Rx Mode:<br>Rx ADC = ON<br>Tx DAC = OFF<br>Rx Bus = Enable       | Low Power:<br>Slow Rx to Tx when T/R<br>transitions 0 to 1.      |

| (16 | 0000<br>(16-Bit Mode) | e)         | 1  |            |     |     |    | Ext2-Tx | SLUW-FAST            | Tx Mode:<br>Rx ADC = ON<br>Tx DAC = ON<br>Tx Bus = Enable  | Moderate Power:<br>Fast Tx to Rx when T/R<br>transitions 1 to 0. |                                                                  |

| (8  | o<br>100<br>3-Bit N   | 00         | e) |            |     |     | 0  | Ext3-Rx | SLOW-SLOW            | Rx Mode:<br>Rx ADC = ON<br>Tx DAC = OFF<br>Rx Bus = Enable | Low Power:<br>Slow Rx to Tx when T/R<br>transitions 0 to 1.      |                                                                  |

|     |                       |            |    | 0101       |     |     | 1  | Ext3-Tx | SLOW-SLOW            | Tx Mode:<br>Rx ADC = OFF<br>Tx DAC = ON<br>Tx Bus = Enable | Low Power:<br>Slow Tx to Rx when T/R<br>transitions 1 to 0.      |                                                                  |

|     |                       |            |    |            | 01  | 10  |    | 0       | Ext4-Rx              | FAST-FAST                                                  | Rx Mode:<br>Rx ADC = ON<br>Tx DAC = ON<br>Rx Bus = Enable        | Moderate Power:<br>Fast Rx to Tx when T/R<br>transitions 0 to 1. |

|     |                       |            |    | 0110       |     |     |    | 1       | Ext4-Tx              | FAOI-FAOI                                                  | Tx Mode:<br>Rx ADC = ON<br>Tx DAC = ON<br>Tx Bus = Enable        | Moderate Power:<br>Fast Tx to Rx when T/R<br>transitions 1 to 0. |

表6. SPIコマンドを使用したTx-Rx制御

|                            | ADDRESS               |            | 3    | DATA BITS  |    |    | s  | T/R     | MODE    | FUNCTION<br>(Tx-Rx SWITCHING                               | DESCRIPTION                                                | COMMENTS                                            |  |  |