#### 概要

8回路、12ビットアナログ-ディジタルコンバータ(ADC) のMAX1438Bは完全な差動信号経路を含めて、完全 差動入力、パイプライン構造およびディジタル誤差補正 を備えています。このADCは、医療用画像計測機器や ディジタル通信アプリケーションにおいて、低電力で 高ダイナミック性能となるように最適化されています。 MAX1438Bは1.8Vの単一電源で動作し、わずか913mW (チャネル当り114mW)ながら、5.3MHzの入力周波数 で69.9dB (typ)の信号対ノイズ比(SNR)を提供します。 低電力動作に加えて、MAX1438Bはアイドル期間の低 電力スタンバイモードを備えています。

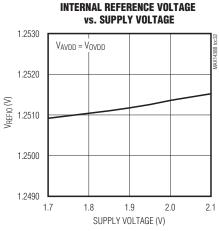

内部の1.24Vの高精度バンドギャップリファレンスが ADCのフルスケールレンジを設定します。柔軟なリファ レンス構造により、高い精度または異なった差動入力 電圧範囲を必要とするアプリケーション用に外部リファ レンスを使用することができます。リファレンス方式は 低ノイズ用に最適化されています。

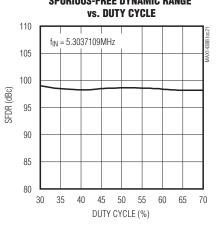

シングルエンドのクロックがデータ変換プロセスを制御 します。内部のデューティサイクルイコライザがクロック デューティサイクルの大幅な変動を補償します。内蔵の フェーズロックループ(PLL)が高速度のシリアル低電圧 差動信号(LVDS)クロックを生成します。

MAX1438Bはデータ、クロックおよびフレーム整列 信号に対して自己整列シリアルLVDS出力を提供します。 出力データは2の補数形式で表されます。

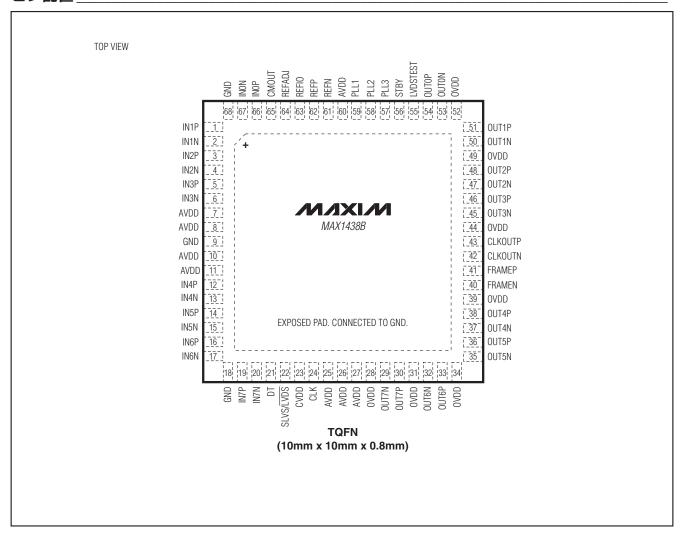

MAX1438Bの最高サンプル速度は64Mspsです。この デバイスは10mm x 10mm x 0.8mmと小型で、エクス ポーズドパッド付きの68ピンのTQFNパッケージで提供 され、工業用拡張温度範囲(-40℃~+85℃)での動作が 保証されています。

### アプリケーション

超音波および医療用画像処理 計測器

マルチチャネル通信

#### 特長

◆ 優れたダイナミック性能

SNR: 69.9dB (5.3MHzにおいて) SFDR: 94dBc (5.3MHzにおいて)

◆ 招低雷力

チャネル当り114mW (通常動作)

- ◆ シリアルLVDS出力

- ◆ 端子選択が可能なLVDS/SLVS (スケーラブル低電圧 信号)モード

- ♦ LVDS出力は最長30インチのFR4バックプレーン 接続をサポート

- ◆ ディジタル信号の完全性のためのテストモード

- ◆ 完全差動アナログ入力

- ◆ 広い差動入力電圧範囲: 1.4V<sub>P-P</sub>

- ◆ 1.24Vの高精度バンドギャップリファレンスを内蔵

- ◆ クロックデューティサイクルイコライザ

- ◆ エクスポーズドパッド付きの小型、68ピンのTOFN パッケージ

- ◆ 評価キットを提供(MAX1437BEVKITを注文して ください)

#### 型番

| PART         | TEMP RANGE     | PIN-PACKAGE     |

|--------------|----------------|-----------------|

| MAX1438BETK+ | -40°C to +85°C | 68 Thin QFN-EP* |

+は鉛(Pb)フリー/RoHS準拠パッケージを表します。 \*EP = エクスポーズドパッド

ピン配置はデータシートの最後に記載されています。

### **ABSOLUTE MAXIMUM RATINGS**

| AVDD to GND                   | 0.3V to +2.0V                      |

|-------------------------------|------------------------------------|

| CVDD to GND                   | 0.3V to +3.6V                      |

| OVDD to GND                   | 0.3V to +2.0V                      |

| IN_P, IN_N to GND             | 0.3V to (V <sub>AVDD</sub> + 0.3V) |

| CLK to GND                    | 0.3V to (V <sub>CVDD</sub> + 0.3V) |

| OUT_P, OUT_N, FRAME_,         |                                    |

| CLKOUT_ to GND                | 0.3V to (V <sub>OVDD</sub> + 0.3V) |

| DT, SLVS/LVDS, LVDSTEST, PLL_ |                                    |

| REFIO, REFADJ, CMOUT to GN    | ND0.3V to (VAVDD + 0.3V)           |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) 68-Pin Thin QFN, 10mm x 10mm x 0.8mm (derate 70mW/°C above +70°C) | 40°C to +85°C<br>+150°C<br>65°C to +150°C |

|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| Lead Temperature (soldering, 10s)                                                                                       |                                           |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{AVDD} = 1.8V, V_{OVDD} = 1.8V, V_{CVDD} = 1.8V, V_{GND} = 0V, external V_{REFIO} = 1.24V, C_{REFIO}$  to GND = 0.1 $\mu$ F || 1.0 $\mu$ F, C\_{REFP} to GND = 10 $\mu$ F, C\_{REFN} to GND = 10 $\mu$ F, f\_{CLK} = 64MHz (50% duty cycle), DT = 0, T\_A = T\_{MIN} to T\_MAX, unless otherwise noted. Typical values are at T\_A = +25°C.) (Note 1)

| PARAMETER                              | SYMBOL          | CONDITIONS                           | MIN  | TYP     | MAX  | UNITS            |

|----------------------------------------|-----------------|--------------------------------------|------|---------|------|------------------|

| DC ACCURACY (Note 2)                   | <b>.</b>        |                                      |      |         |      | 1                |

| Resolution                             | N               |                                      | 12   |         |      | Bits             |

| Integral Nonlinearity                  | INL             |                                      |      | ±0.4    | ±2.5 | LSB              |

| Differential Nonlinearity              | DNL             | No missing codes over temperature    |      | ±0.25   | ±1   | LSB              |

| Offset Error                           |                 |                                      |      |         | ±0.5 | %FS              |

| Gain Error                             |                 |                                      | -3   | ±0.5    | +2   | %FS              |

| ANALOG INPUTS (IN_P, IN_N)             |                 |                                      |      |         |      |                  |

| Input Differential Range               | V <sub>ID</sub> | Differential input                   |      | 1.4     |      | V <sub>P-P</sub> |

| Common-Mode Voltage Range              | Vcmo            |                                      |      | 0.76    |      | V                |

| Common-Mode Voltage Range<br>Tolerance |                 | (Note 3)                             |      | ±50     |      | mV               |

| Differential Input Impedance           | RIN             | Switched capacitor load              |      | 2       |      | kΩ               |

| Differential Input Capacitance         | CIN             |                                      |      | 12.5    |      | рF               |

| CONVERSION RATE                        | •               |                                      | •    |         |      | •                |

| Maximum Conversion Rate                | fSMAX           |                                      | 64   |         |      | MHz              |

| Minimum Conversion Rate                | fsmin           |                                      |      | 4.0     |      | MHz              |

| Data Latency                           |                 |                                      |      | 6.5     |      | Cycles           |

| DYNAMIC CHARACTERISTICS                | (Differential   | Inputs, 4096-Point FFT) (Note 2)     |      |         |      | -                |

| Cional ta Naisa Datia                  | SNR             | f <sub>IN</sub> = 5.3MHz at -0.5dBFS |      | 69.9    |      | dB               |

| Signal-to-Noise Ratio                  | SINK            | f <sub>IN</sub> = 20MHz at -0.5dBFS  | 67   | 69.6    |      | ab ab            |

| Cignal to Naise and Distortion         | SINAD           | f <sub>IN</sub> = 5.3MHz at -0.5dBFS |      | 69.8    |      | dB               |

| Signal-to-Noise and Distortion         | SINAD           | f <sub>IN</sub> = 20MHz at -0.5dBFS  | 67   | 67 69.6 |      | ub               |

| Effective Number of Bits               | ENOB            | f <sub>IN</sub> = 5.3MHz at -0.5dBFS |      | 11.4    |      | Bits             |

| LITECTIVE INTITIDES OF DIS             | ENOB            | f <sub>IN</sub> = 20MHz at -0.5dBFS  | 10.8 | 11.4    |      | DIIS             |

| Spurious Froe Dynamic Bases            | SFDR            | f <sub>IN</sub> = 5.3MHz at -0.5dBFS |      | 94      |      | dPc              |

| Spurious-Free Dynamic Range            | SEDK            | f <sub>IN</sub> = 20MHz at -0.5dBFS  | 79   | 93      | dBc  |                  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = 1.8V, V_{OVDD} = 1.8V, V_{CVDD} = 1.8V, V_{GND} = 0V , external \ V_{REFIO} = 1.24V, C_{REFIO} \ to \ GND = 0.1 \mu F \ II \ 1.0 \mu F, C_{REFP} \ to \ GND = 10 \mu F, f_{CLK} = 64 MHz \ (50\% \ duty \ cycle), DT = 0, T_A = T_{MIN} \ to \ T_{MAX}, unless otherwise noted. Typical values are at T_A = +25°C.) (Note 1)$

| PARAMETER                                         | SYMBOL           | CONDITIONS                                                                 | MIN                      | TYP   | MAX                        | UNITS              |

|---------------------------------------------------|------------------|----------------------------------------------------------------------------|--------------------------|-------|----------------------------|--------------------|

| Tatal Hamanaia Diatantian                         | TUD              | f <sub>IN</sub> = 5.3MHz at -0.5dBFS                                       |                          | -95   |                            | -ID -              |

| Total Harmonic Distortion                         | THD              | f <sub>IN</sub> = 20MHz at -0.5dBFS                                        |                          | -92   | -79                        | dBc                |

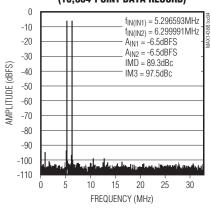

| Intermodulation Distortion                        | IMD              | f <sub>1</sub> = 5.3MHz at -6.5dBFS<br>f <sub>2</sub> = 6.3MHz at -6.5dBFS |                          | 89.3  |                            | dBc                |

| Third-Order Intermodulation                       | IM3              | $f_1 = 5.3MHz$ at -6.5dBFS<br>$f_2 = 6.3MHz$ at -6.5dBFS                   |                          | 97.5  |                            | dBc                |

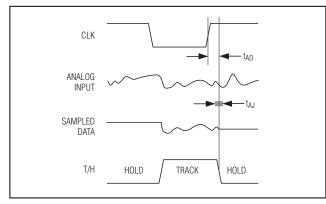

| Aperture Jitter                                   | taj              | Figure 10                                                                  |                          | < 0.4 |                            | psrms              |

| Aperture Delay                                    | t <sub>AD</sub>  | Figure 10                                                                  |                          | 1     |                            | ns                 |

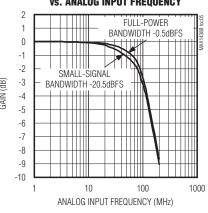

| Small-Signal Bandwidth                            | SSBW             | Input at -20dBFS                                                           |                          | 100   |                            | MHz                |

| Full-Power Bandwidth                              | LSBW             | Input at -0.5dBFS                                                          |                          | 100   |                            | MHz                |

| Output Noise                                      |                  | IN_P = IN_N                                                                |                          | 0.44  |                            | LSB <sub>RMS</sub> |

| Overrange Recovery Time                           | tor              | $R_S = 25\Omega$ , $C_S = 50pF$                                            |                          | 1     |                            | Clock<br>cycle     |

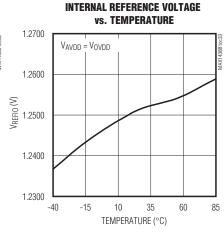

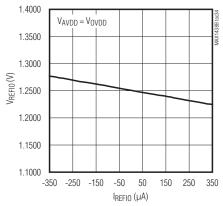

| INTERNAL REFERENCE                                |                  |                                                                            | •                        |       |                            | •                  |

| REFADJ Internal Reference-Mode<br>Enable Voltage  |                  | (Note 4)                                                                   |                          |       | 0.1                        | V                  |

| REFADJ Low-Leakage Current                        |                  |                                                                            |                          | 1.5   |                            | mA                 |

| REFIO Output Voltage                              | VREFIO           |                                                                            | 1.18                     | 1.24  | 1.30                       | V                  |

| Reference Temperature<br>Coefficient              | TCREFIO          |                                                                            |                          | 120   |                            | ppm/°C             |

| EXTERNAL REFERENCE                                | 1                |                                                                            | l                        |       |                            |                    |

| REFADJ External Reference-<br>Mode Enable Voltage |                  | (Note 4)                                                                   | V <sub>AVDD</sub> - 0.1V |       |                            | V                  |

| REFADJ High-Leakage Current                       |                  |                                                                            |                          | 200   |                            | μΑ                 |

| REFIO Input Voltage                               |                  |                                                                            |                          | 1.24  |                            | V                  |

| REFIO Input Voltage Tolerance                     |                  |                                                                            |                          | ±5    |                            | %                  |

| REFIO Input Current                               | IREFIO           |                                                                            |                          | < 1   |                            | μΑ                 |

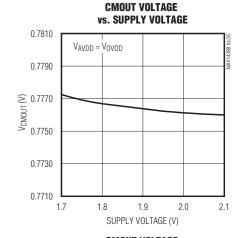

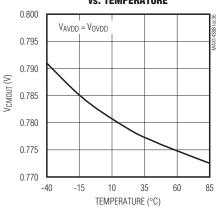

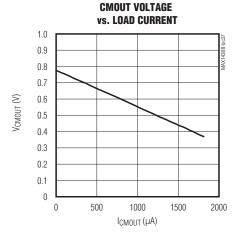

| COMMON-MODE OUTPUT (CMO                           | UT)              |                                                                            |                          |       |                            | •                  |

| CMOUT Output Voltage                              | VCMOUT           |                                                                            |                          | 0.76  |                            | V                  |

| CLOCK INPUT (CLK)                                 |                  |                                                                            |                          |       |                            |                    |

| Input High Voltage                                | VCLKH            |                                                                            | 0.8 x<br>Vavdd           |       |                            | V                  |

| Input Low Voltage                                 | VCLKL            |                                                                            |                          |       | 0.2 x<br>V <sub>AVDD</sub> | V                  |

| Clock Duty Cycle                                  |                  |                                                                            |                          | 50    |                            | %                  |

| Clock Duty-Cycle Tolerance                        |                  |                                                                            |                          | ±30   |                            | %                  |

| Input Leakage                                     | Divi             | Input at GND                                                               |                          |       | 5                          |                    |

| IIIput Leakaye                                    | DI <sub>IN</sub> | Input at V <sub>AVDD</sub>                                                 |                          |       | 80                         | μΑ                 |

| Input Capacitance                                 | DCIN             |                                                                            |                          | 5     |                            | рF                 |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = 1.8V, V_{OVDD} = 1.8V, V_{CVDD} = 1.8V, V_{GND} = 0V, external V_{REFIO} = 1.24V, C_{REFIO}$  to GND = 0.1 $\mu$ F || 1.0 $\mu$ F, C\_{REFP} to GND = 10 $\mu$ F, C\_{REFN} to GND = 10 $\mu$ F, f\_{CLK} = 64MHz (50% duty cycle), DT = 0, T\_A = T\_{MIN} to T\_MAX, unless otherwise noted. Typical values are at T\_A = +25°C.) (Note 1)

| PARAMETER                    | SYMBOL            | CONDITIONS                                                             |                          | MIN                | TYP   | MAX   | UNITS |

|------------------------------|-------------------|------------------------------------------------------------------------|--------------------------|--------------------|-------|-------|-------|

| DIGITAL INPUTS (PLL_, LVDSTE | ST, DT, SL\       | VS, STBY)                                                              |                          |                    |       |       | •     |

| Input High Threshold         | VIH               |                                                                        |                          | 0.8 x              |       |       | V     |

| Input riigh riireshold       | V III             |                                                                        |                          | V <sub>A</sub> VDD |       |       | V     |

| Input Low Threshold          | VIL               |                                                                        |                          |                    |       | 0.2 x | V     |

|                              | - 12              |                                                                        |                          |                    |       | VAVDD | -     |

| Input Leakage                | DIIN              | Input at GND                                                           |                          |                    |       | 5     | μΑ    |

|                              |                   | Input at VAVDE                                                         | )                        |                    |       | 80    | '     |

| Input Capacitance            | DCIN              |                                                                        |                          |                    | 5     |       | рF    |

| LVDS OUTPUTS (OUT_P, OUT_I   | I), SLVS/LV       | DS = 0                                                                 |                          |                    |       |       | 1     |

| Differential Output Voltage  | Vohdiff           | $R_{TERM} = 100\Omega$                                                 | 2                        | 250                |       | 450   | mV    |

| Output Common-Mode Voltage   | Vocm              | $R_{TERM} = 100\Omega$                                                 | 2                        | 1.125              |       | 1.375 | V     |

| Rise Time (20% to 80%)       | t <sub>RL</sub>   | $R_{TERM} = 100\Omega$                                                 | $P$ , $C_{LOAD} = 5pF$   |                    | 350   |       | ps    |

| Fall Time (80% to 20%)       | t <sub>FL</sub>   | $R_{TERM} = 100\Omega$                                                 | $P$ , $C_{LOAD} = 5pF$   |                    | 350   |       | ps    |

| SLVS OUTPUTS (OUT_P, OUT_N   | I, CLKOUTP        | , CLKOUTN, F                                                           | RAMEP, FRAMEN), SLVS/L\  | /DS = 1, D         | Γ = 1 |       |       |

| Differential Output Voltage  | Vohdiff           | $R_{TERM} = 100\Omega$                                                 | 2                        |                    | 205   |       | mV    |

| Output Common-Mode Voltage   | Vocm              | $R_{TERM} = 100\Omega$                                                 | 2                        |                    | 220   |       | mV    |

| Rise Time (20% to 80%)       | t <sub>RS</sub>   | $R_{TERM} = 100\Omega$                                                 | $2$ , $C_{LOAD} = 5pF$   |                    | 320   |       | ps    |

| Fall Time (80% to 20%)       | tFS               | $R_{TERM} = 100\Omega$                                                 | $P$ , $C_{LOAD} = 5pF$   |                    | 320   |       | ps    |

| STANDBY MODE (STBY)          |                   |                                                                        |                          |                    |       |       |       |

| STBY Fall to Output Enable   | tENABLE           |                                                                        |                          |                    | 200   |       | μs    |

| STBY Rise to Output Disable  | tDISABLE          |                                                                        |                          |                    | 60    |       | ns    |

| POWER REQUIREMENTS           |                   |                                                                        |                          |                    |       |       |       |

| AVDD Supply Voltage Range    | Vavdd             |                                                                        |                          | 1.7                | 1.8   | 1.9   | V     |

| OVDD Supply Voltage Range    | Vovdd             |                                                                        |                          | 1.7                | 1.8   | 1.9   | V     |

| CVDD Supply Voltage Range    | VCVDD             |                                                                        |                          | 1.7                | 1.8   | 3.5   | V     |

|                              |                   |                                                                        | STBY = 0, DT = 0         |                    | 422   | 465   |       |

| AVDD Supply Current          | I <sub>AVDD</sub> | f <sub>IN</sub> = 20MHz<br>at -0.5dBFS                                 | STBY = 0, DT = 1         |                    | 422   |       | mA    |

|                              |                   | at -0.50BF3                                                            | STBY = 1, no clock input |                    | 37    |       |       |

| OVDD Supply Current          |                   |                                                                        | STBY = 0                 |                    | 85    | 110   |       |

|                              | lovdd             | fIN = 20MHz                                                            | STBY = 0, DT = 1         |                    | 85    |       | mA    |

|                              |                   | at -0.5dBFS                                                            | STBY = 1, no clock input |                    | 16    |       | μΑ    |

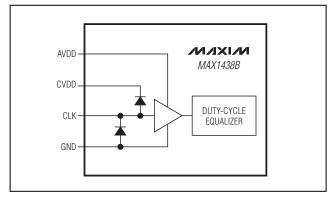

| CVDD Supply Current          | ICVDD             | CVDD is used only to bias ESD-protection diodes on CLK input, Figure 2 |                          |                    | 0     |       | mA    |

| Power Dissipation            | P <sub>DISS</sub> | f <sub>IN</sub> = 20MHz a                                              |                          |                    | 913   | 1035  | mW    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = 1.8V, V_{OVDD} = 1.8V, V_{CVDD} = 1.8V, V_{GND} = 0.4V, V_{GND} = 0.4V, V_{REFIO} = 1.24V, V_{$

| PARAMETER                      | SYMBOL          | CONDITIONS                        | MIN                    | TYP MAX                | UNITS   |

|--------------------------------|-----------------|-----------------------------------|------------------------|------------------------|---------|

| TIMING CHARACTERISTICS (Not    | e 5)            |                                   |                        |                        |         |

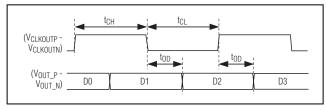

| Data Valid to CLKOUT Rise/Fall | top             | Figure 5 (Note 6)                 | (tsample/24)<br>- 0.15 | (tsample/24)<br>+ 0.15 | ns      |

| CLKOUT Output-Width High       | tcH             | Figure 5                          | tsa                    | MPLE/12                | ns      |

| CLKOUT Output-Width Low        | t <sub>CL</sub> | Figure 5                          | tsa                    | MPLE/12                | ns      |

| FRAME Rise to CLKOUT Rise      | tCF             | Figure 4 (Note 6)                 | (tsample/24)<br>- 0.15 | (tsample/24)<br>+ 0.15 | ns      |

| Sample CLK Rise to FRAME Rise  | tsF             | Figure 4 (Note 6)                 | (tsample/2)<br>+ 1.1   | (tsample/2)<br>+ 2.6   | ns      |

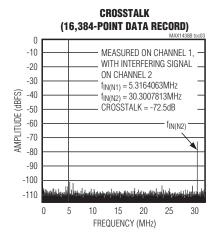

| Crosstalk                      |                 | (Note 2)                          |                        | -73                    | dB      |

| Gain Matching                  | Сдм             | f <sub>IN</sub> = 5.3MHz (Note 2) |                        | ±0.1                   | dB      |

| Phase Matching                 | СРМ             | f <sub>IN</sub> = 5.3MHz (Note 2) | =                      | ±0.25                  | Degrees |

- Note 1: Specifications at T<sub>A</sub> ≥ +25°C are guaranteed by production testing. Specifications at T<sub>A</sub> < +25°C are guaranteed by design and characterization and not subject to production testing.

- Note 2: See definition in the *Parameter Definitions* section at the end of this data sheet.

- Note 3: See the Common-Mode Output (CMOUT) section.

- **Note 4:** Connect REFADJ to GND directly to enable internal reference mode. Connect REFADJ to AVDD directly to disable the internal bandgap reference and enable external reference mode.

- Note 5: Data valid to CLKOUT rise/fall timing is measured from 50% of data output level to 50% of clock output level.

- Note 6: Guaranteed by design and characterization. Not subject to production testing.

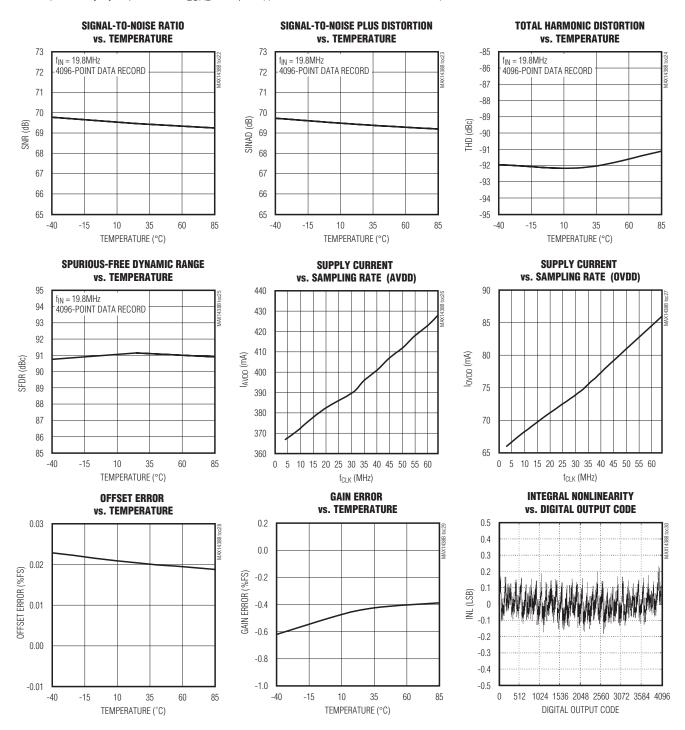

#### 標準動作特性

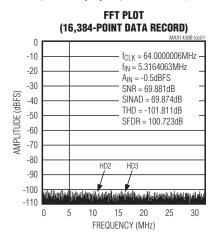

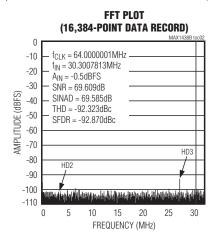

$(V_{AVDD} = 1.8V, V_{OVDD} = 1.8V, V_{CVDD} = 1.8V, V_{GND} = 0V, internal reference, differential input at -0.5dBFS, <math>f_{IN} = 5.3MHz$ ,  $f_{CLK} = 64MHz$  (50% duty cycle), DT = 0,  $C_{LOAD} = 10pF$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

### 標準動作特性(続き)

$(VAVDD = 1.8V, VOVDD = 1.8V, VCVDD = 1.8V, VGND = 0V, internal reference, differential input at -0.5dBFS, f_{IN} = 5.3MHz, f_{CLK} = 64MHz (50% duty cycle), DT = 0, C_{LOAD} = 10pF, T_A = +25°C, unless otherwise noted.)$

BANDWIDTH vs. analog input frequency

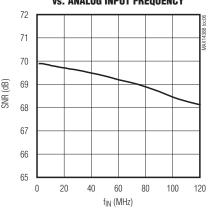

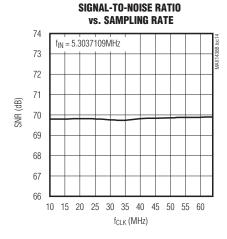

SIGNAL-TO-NOISE RATIO

vs. Analog input frequency

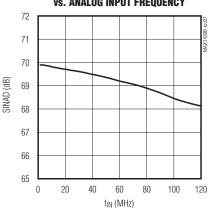

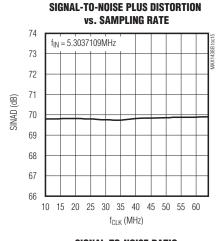

SIGNAL-TO-NOISE PLUS DISTORTION vs. ANALOG INPUT FREQUENCY

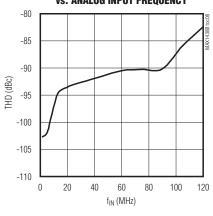

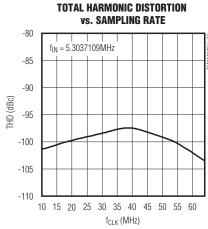

TOTAL HARMONIC DISTORTION vs. Analog input frequency

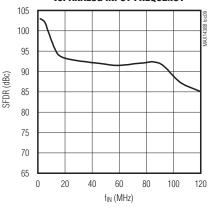

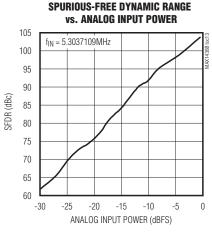

SPURIOUS-FREE DYNAMIC RANGE vs. Analog input frequency

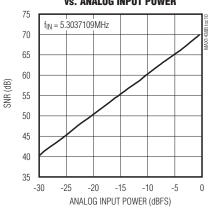

SIGNAL-TO-NOISE RATIO vs. ANALOG INPUT POWER

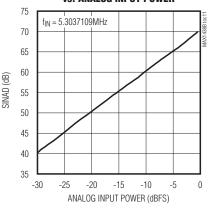

SIGNAL-TO-NOISE PLUS DISTORTION vs. Analog input power

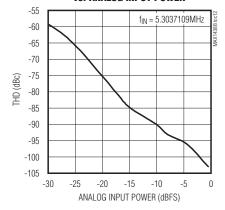

TOTAL HARMONIC DISTORTION vs. ANALOG INPUT POWER

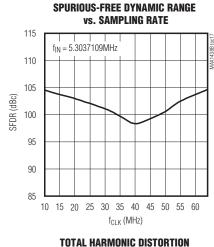

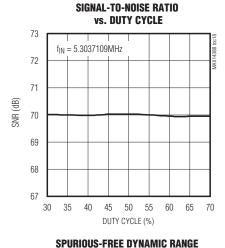

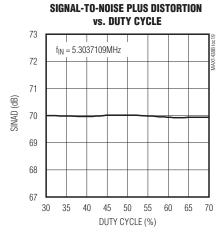

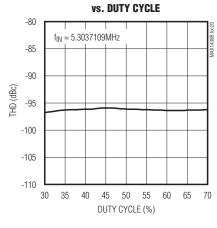

### 標準動作特性(続き)

$(V_{AVDD} = 1.8V, V_{OVDD} = 1.8V, V_{CVDD} = 1.8V, V_{GND} = 0V, internal reference, differential input at -0.5dBFS, <math>f_{IN} = 5.3MHz$ ,  $f_{CLK} = 64MHz$  (50% duty cycle), DT = 0,  $C_{I_{CDAD}} = 10pF$ ,  $T_{A} = +25^{\circ}C$ , unless otherwise noted.)

### 標準動作特性(続き)

$(VAVDD = 1.8V, VOVDD = 1.8V, VCVDD = 1.8V, VGND = 0V, internal reference, differential input at -0.5dBFS, f_{IN} = 5.3MHz, f_{CLK} = 64MHz (50% duty cycle), DT = 0, C_{LOAD} = 10pF, T_A = +25°C, unless otherwise noted.)$

### 標準動作特性(続き)

$(VAVDD = 1.8V, VOVDD = 1.8V, VCVDD = 1.8V, VGND = 0V, internal reference, differential input at -0.5dBFS, f_{IN} = 5.3MHz, f_{CLK} = 64MHz (50% duty cycle), DT = 0, C_{LOAD} = 10pF, T_A = +25^{\circ}C, unless otherwise noted.)$

INTERNAL REFERENCE VOLTAGE vs. REFERENCE LOAD CURRENT

CMOUT VOLTAGE vs. TEMPERATURE

## 端子説明 \_\_\_\_\_\_

| 端子                              | 名称        | 機能                                                                                                                                                            |

|---------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                               | IN1P      | チャネル1の正入力                                                                                                                                                     |

| 2                               | IN1N      | チャネル1の負入力                                                                                                                                                     |

| 3                               | IN2P      | チャネル2の正入力                                                                                                                                                     |

| 4                               | IN2N      | チャネル2の負入力                                                                                                                                                     |

| 5                               | IN3P      | チャネル3の正入力                                                                                                                                                     |

| 6                               | IN3N      | チャネル3の負入力                                                                                                                                                     |

| 7, 8, 10, 11,<br>25, 26, 27, 60 | AVDD      | アナログ電源入力。AVDDを1.7V~1.9Vの電源に接続します。デバイスに可能な限り近接して0.1μFのコンデンサでAVDDをGNDにバイパスしてください。最低2.2μFの大型コンデンサでAVDDの電源平面をGND平面にバイパスしてください。すべてのAVDD端子を同じ電位に接続してください。           |

| 9, 18, 68                       | GND       | グランド。すべてのGND端子を同じ電位に接続してください。                                                                                                                                 |

| 12                              | IN4P      | チャネル4の正入力                                                                                                                                                     |

| 13                              | IN4N      | チャネル4の負入力                                                                                                                                                     |

| 14                              | IN5P      | チャネル5の正入力                                                                                                                                                     |

| 15                              | IN5N      | チャネル5の負入力                                                                                                                                                     |

| 16                              | IN6P      | チャネル6の正入力                                                                                                                                                     |

| 17                              | IN6N      | チャネル6の負入力                                                                                                                                                     |

| 19                              | IN7P      | チャネル7の正入力                                                                                                                                                     |

| 20                              | IN7N      | チャネル7の負入力                                                                                                                                                     |

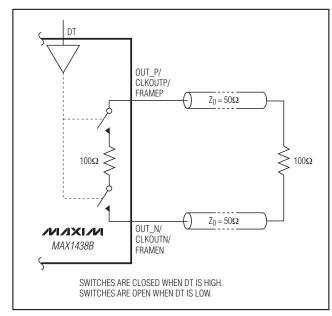

| 21                              | DT        | 2重終端選択。DTをハイに強制すると、各差動出力ペア間の内部の100Ω終端が選択されます。<br>DTをローに強制すると内部の出力終端は選択されません。                                                                                  |

| 22                              | SLVS/LVDS | 差動出力信号のフォーマット選択入力。SLVS/LVDSをハイに強制すると、SLVS出力が選択されます。SLVS/LVDSをローに強制すると、LVDS出力が選択されます。                                                                          |

| 23                              | CVDD      | クロック電源入力。CVDDを1.7V~3.5Vの電源に接続します。最低2.2μFのコンデンサと並列に0.1μFのコンデンサでCVDDをGNDにバイパスします。バイパスコンデンサは、可能な限りデバイスの近くに取り付けてください。CVDDは、CLKのESD保護ダイオードをバイアスするために使用されます(図2を参照)。 |

| 24                              | CLK       | シングルエンドのCMOSクロック入力                                                                                                                                            |

| 28, 31, 34, 39,<br>44, 49, 52   | OVDD      | 出力ドライバ用電源入力。OVDDを1.7V~1.9Vの電源に接続します。デバイスに可能な限り近接して 0.1μFのコンデンサでOVDDをGNDにバイパスしてください。最低2.2μFの大型コンデンサでOVDDのパワープレーンをGNDプレーンにバイパスしてください。すべてのOVDD端子を同じ電位に接続してください。  |

| 29                              | OUT7N     | チャネル7の負LVDS/SLVS出力                                                                                                                                            |

| 30                              | OUT7P     | チャネル7の正LVDS/SLVS出力                                                                                                                                            |

| 32                              | OUT6N     | チャネル6の負LVDS/SLVS出力                                                                                                                                            |

| 33                              | OUT6P     | チャネル6の正LVDS/SLVS出力                                                                                                                                            |

| 35                              | OUT5N     | チャネル5の負LVDS/SLVS出力                                                                                                                                            |

| 36                              | OUT5P     | チャネル5の正LVDS/SLVS出力                                                                                                                                            |

| 37                              | OUT4N     | チャネル4の負LVDS/SLVS出力                                                                                                                                            |

| 38                              | OUT4P     | チャネル4の正LVDS/SLVS出力                                                                                                                                            |

| 40                              | FRAMEN    | 負のフレーム整列LVDS/SLVS出力。差動FRAME出力の立上りエッジは出力データストリームの<br>有効なDOに整列します。                                                                                              |

| 41                              | FRAMEP    | 正のフレーム整列LVDS/SLVS出力。差動FRAME出力の立上りエッジは出力データストリームの<br>有効なDOに整列します。                                                                                              |

| 42                              | CLKOUTN   | 負のLVDS/SLVSシリアルクロック出力                                                                                                                                         |

|                                 |           |                                                                                                                                                               |

### 端子説明(続き)\_\_\_\_\_

| 端子 | 名称       | 機能                                                                                                                                                                        |

|----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 43 | CLKOUTP  | 正のLVDS/SLVSシリアルクロック出力                                                                                                                                                     |

| 45 | OUT3N    | チャネル3の負LVDS/SLVS出力                                                                                                                                                        |

| 46 | OUT3P    | チャネル3の正LVDS/SLVS出力                                                                                                                                                        |

| 47 | OUT2N    | チャネル2の負LVDS/SLVS出力                                                                                                                                                        |

| 48 | OUT2P    | チャネル2の正LVDS/SLVS出力                                                                                                                                                        |

| 50 | OUT1N    | チャネル1の負LVDS/SLVS出力                                                                                                                                                        |

| 51 | OUT1P    | チャネル1の正LVDS/SLVS出力                                                                                                                                                        |

| 53 | OUTON    | チャネル0の負LVDS/SLVS出力                                                                                                                                                        |

| 54 | OUT0P    | チャネル0の正LVDS/SLVS出力                                                                                                                                                        |

| 55 | LVDSTEST | LVDSテストパターンイネーブル。LVDSTESTをハイに強制すると、出力パターン0000 1011 1101 がイネーブルになります。アナログ変換結果と同じように、テストパターンデータはLSBを先頭に出力されます。LVDSTESTをローに強制すると通常動作になります。                                   |

| 56 | STBY     | スタンバイ入力。STBYをハイに強制するとMAX1438Bはスタンバイモードに入ります。スタンバイではリファレンス回路はアクティブのままです。STBYをローに強制すると通常動作になります。                                                                            |

| 57 | PLL3     | PLL制御入力3。詳細は表1を参照してください。                                                                                                                                                  |

| 58 | PLL2     | PLL制御入力2。詳細は表1を参照してください。                                                                                                                                                  |

| 59 | PLL1     | PLL制御入力1。詳細は表1を参照してください。                                                                                                                                                  |

| 61 | REFN     | 負のリファレンスバイパス出力。REFPとREFNの間に最低 $1\mu F$ ( $10\mu F$ 、 $typ$ )のコンデンサを接続し、REFNとGND間に最低 $1\mu F$ ( $10\mu F$ 、 $typ$ )を接続してください。各コンデンサはMAX1438Bと同じPCB面でデバイスに可能な限り近くに配置してください。 |

| 62 | REFP     | 正のリファレンスバイパス出力。REFPとREFNの間に最低 $1\mu$ F ( $10\mu$ F、 $typ$ )のコンデンサを接続し、REFNとGND間に最低 $1\mu$ F ( $10\mu$ F、 $typ$ )を接続してください。各コンデンサはMAX1438Bと同じPCB面でデバイスに可能な限り近くに配置してください。   |

| 63 | REFIO    | リファレンス入力/出力。内部のリファレンス動作(REFADJ = GND)の場合、リファレンス出力電圧は1.24Vです。外部のリファレンス動作(REFADJ = AVDD)の場合は、REFIOに安定なリファレンス電圧を印加してください。最低 $0.1\mu$ FのコンデンサでGNDにバイパスしてください。                 |

| 64 | REFADJ   | 内部/外部リファレンスモード選択およびリファレンス調整入力。内部リファレンスの場合は、REFADJをGNDに接続してください。外部リファレンスの場合は、REFADJをAVDDに接続してください。リファレンスの調整は、「内部リファレンスを使用するフルスケール範囲の調整」の項を参照してください。                        |

| 65 | CMOUT    | コモンモードのリファレンス電圧出力。CMOUTはDC結合アプリケーション用に入力コモンモード電圧を出力します。CMOUTは最低0.1µFのコンデンサでGNDにバイパスしてください。                                                                                |

| 66 | IN0P     | チャネル0の正入力                                                                                                                                                                 |

| 67 | INON     | チャネル0の負入力                                                                                                                                                                 |

| _  | EP       | エクスポーズドパッド。内部でGNDに接続されています。最高の熱性能を得るためにはEPを大きいグランド平面に接続してください。GNDに接続する必要があります。                                                                                            |

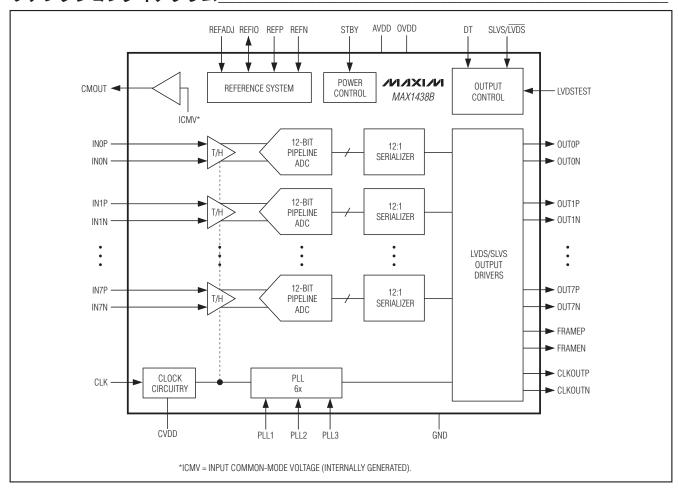

### ファンクションダイアグラム

### 詳細 \_\_\_\_\_

MAX1438BのADCは、完全な差動入力、パイプライン構造および高速信号変換用のディジタル誤差補正を備えています。ADCのパイプライン構造は、入力で捕捉したサンプルをクロックの半サイクルごとに各パイプライン段を通じて移動させます。変換されたディジタル結果はシリアル化されて、LVDS/SLVS出力ドライバを通じて送出されます。入力から出力までの総クロックサイクルの待ち時間は6.5クロックサイクルです。

MAX1438Bは、入力と出力が同期した8個の独立した 完全差動チャネルを提供します。全体のスタンバイに よって電力消費が最小になります。

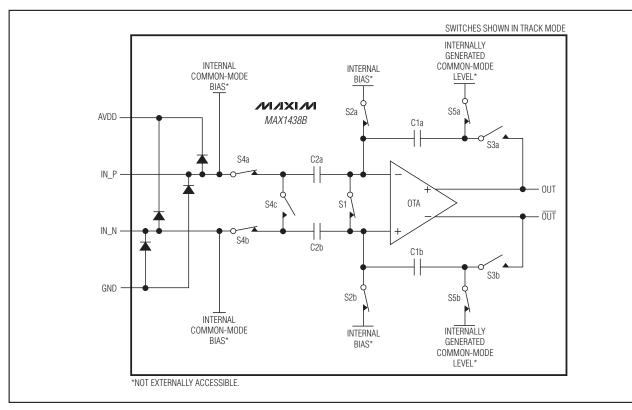

#### 入力回路

図1は入力T/H回路の簡略図を示しています。トラックモードでは、スイッチS1、S2a、S2b、S4a、S4b、S5aおよびS5bは閉じられています。完全差動回路は、入力信号をスイッチS4aとS4bを通じて2つのコンデンサ(C2aとC2b)にサンプリングします。S2aとS2bは、トランスコンダクタンスオペアンプ(OTA)のコモンモードを設定し、S1と同時に開かれて入力波形をサンプリングします。つぎに、スイッチS3aとS3bがコンデンサC1aとC1bをアンプの出力に接続してスイッチS4cが閉じられる前に、スイッチS4a、S4b、S5aおよびS5bが開かれます。生じた差動電圧はコンデンサC2aとC2bに保持されます。アンプは、コンデンサC1aとC1bを

図1. 内部入力回路

最初にC2aとC2bに保持されていた同じ電圧に充電します。その後、これらの値は最初の量子化器に入力され、高速変化している入力からパイプラインを切り離します。アナログ入力のIN\_P~IN\_Nは差動駆動されます。差動入力に対してIN\_PとIN\_Nの入力インピーダンスを最適性能になるように整合させてください。

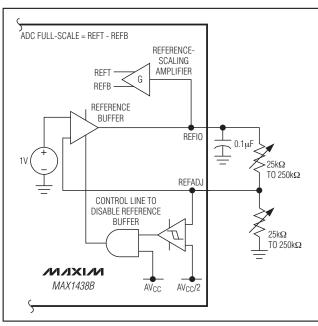

### リファレンス構成(REFIO、REFADJ、REFPおよび REFN)

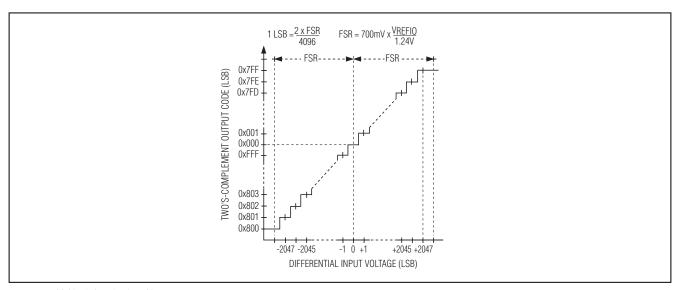

MAX1438Bは、内部の1.24Vのバンドギャップリファレンスを提供するか、または外部のリファレンス電圧で駆動することができます。フルスケールのアナログ差動入力範囲は±FSRです。FSR (フルスケール範囲)は次の式によって与えられます。

$$FSR = \frac{(0.700 \times V_{REFIO})}{1.24V}$$

ここで、 $V_{REFIO}$ はREFIOにおける電圧で、内部または外部で生成されます。 $V_{REFIO}=1.24V$ に対して、フルスケール入力範囲は $\pm 700$ mV( $1.4V_{P-P}$ )です。

#### 内部リファレンスモード

内部のバンドギャップリファレンスを直接使用するには、REFADJをGNDに接続します。内部リファレンスモードでは、内部のバンドギャップリファレンスは、120ppm/℃の温度係数を持った1.24VのV<sub>REFIO</sub>を生成します。安定性のためにREFIOとGND間に0.1µF以上のバイパスコンデンサを外付けしてください。REFIOは外部回路に対して最大200µAのソースとシンクを行い、REFIOは75mV/mAの負荷レギュレーションを備えています。MAX1438Bをスタンバイモードにすると、リファレンス回路を除いてすべての回路がオフになり、STBYのハイからローへの遷移信号でADCがスタンバイから抜け出す時に、コンバータの電源を早くオンにすることができます。MAX1438Bの内部回路は、コンバータがスタンバイモードから抜け出す時に、電源がオンになって安定するまでに200µsを要します。

利得誤差を補償するか、ADCのFSRを縮小または拡大させるためには、REFADJとGND間またはREFADJとREFIO間に外部抵抗を追加します。これにより、MAX1438Bの内部リファレンスはその公称値の最大±5%まで調整されます。「内部リファレンスを使用するフルスケール範囲の調整」の項を参照してください。

$1\mu F$ 以上 $(10\mu F, typ)$ のコンデンサをREFPおよびREFNとGNDの間に、 $1\mu F$ 以上 $(10\mu F, typ)$ のコンデンサをREFPとREFNの間に、デバイスと同じPCB面で可能な限りデバイスに近づけて接続してください。

### 外部リファレンスモード

外部リファレンスモードによってMAX1438Bのリファレンス電圧に優る制御が可能になり、複数のコンバータが共通のリファレンスを使用することができます。内部リファレンスをディセーブルするには、REFADJをAVDDに接続します。安定な $1.18V\sim1.30V$ の電源をREFIOに印加してください。REFIOをGNDに $0.1\mu$ F以上のコンデンサでバイパスしてください。REFIOの入力インピーダンスは $1M\Omega$ 以上です。

#### クロック入力(CLK)

MAX1438Bは、20%~80%という広い入力クロックデューティサイクルのCMOS対応クロック信号を受け付けます。CLKは、外部のシングルエンドクロック信号で駆動してください。図2は簡略化したクロック入力図を示しています。

MAX1438Bの指定されたSNR性能を得るためには、低ジッタのクロックが必要になります。アナログ入力のサンプリングはCLKの立上りエッジで起こるため、このエッジは可能な限り低ジッタにする必要があります。次の関係式に従って、ジッタはADCの最大SNR性能を制限します。

$$SNR = 20 \times log \left( \frac{1}{2 \times \pi \times f_{IN} \times t_{J}} \right)$$

ここで、 $f_{IN}$ はアナログ入力周波数を表し、 $t_J$ はシステムの総クロックジッタです。

#### PLL入力(PLL1、PLL2、PLL3)

MAX1438Bは、入力クロックの6倍の周波数の出力クロック信号を生成するPLLを備えています。出力クロック信号は、MAX1438Bからデータをクロック

図2. クロック入力回路

表1. PLL1、PLL2、およびPLL3の設定表

| PLL1 | PLL2 | PLL3 |      | CK RANGE<br>Hz) |

|------|------|------|------|-----------------|

|      |      |      | MIN  | MAX             |

| 0    | 0    | 0    | 45.0 | 64.0            |

| 0    | 0    | 1    | 32.5 | 45.0            |

| 0    | 1    | 0    | 22.5 | 32.5            |

| 0    | 1    | 1    | 16.3 | 22.5            |

| 1    | 0    | 0    | 11.3 | 16.3            |

| 1    | 0    | 1    | 8.1  | 11.3            |

| 1    | 1    | 0    | 5.6  | 8.1             |

| 1    | 1    | 1    | 4.0  | 5.6             |

同期出力するために使用されます(「システムタイミング要件」の項を参照)。PLL1、PLL2およびPLL3の各端子の設定は、表1に示されている入力クロック範囲に設定してください。

#### システムタイミング要件

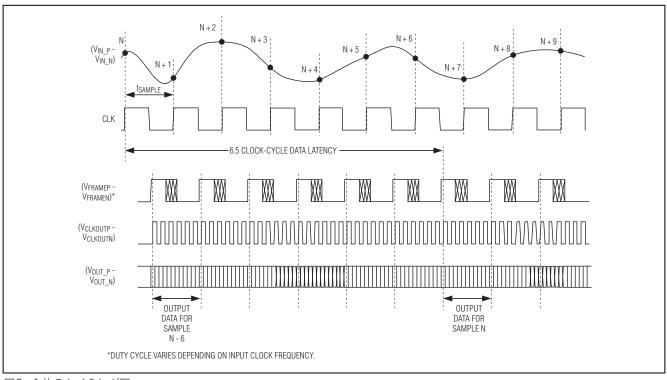

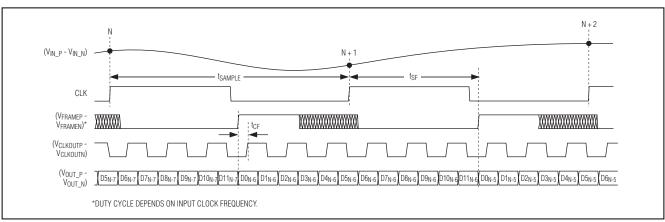

図3は、アナログ入力、入力クロック、フレーム整列出力、シリアルクロック出力、およびシリアルデータ出力の関係を示しています。差動アナログ入力(IN\_PおよびIN\_N)はCLK信号の立上りエッジでサンプリングされ、その結果のデータはディジタル出力に6.5クロックサイクル後に現れます。図4は、入力と出力間の関係の詳細な2変換タイミング図を示しています。

#### クロック出力(CLKOUTP、CLKOUTN)

MAX1438Bは、CLKOUTPとCLKOUTNからなる差動クロック出力を提供します。図4に示すように、シリアル出力データは、クロック出力の両方のエッジでMAX1438Bからクロック同期出力されます。出力クロックの周波数はCLKの周波数の6倍です。

#### フレーム整列出力(FRAMEP、FRAMEN)

MAX1438Bは、FRAMEPとFRAMENからなる差動フレーム整列信号を提供します。図4に示すように、フレーム整列信号の立上りエッジは、12ビットのシリアルデータストリームの先頭ビット(D0)に対応します。フレーム整列信号の周波数は入力クロックの周波数と同じです。

### シリアル出力データ(OUT\_P、OUT\_N)

MAX1438Bは、その変換結果をOUT\_PとOUT\_Nからなる個別の差動出力経由で提供します。変換結果は、サンプルが取り込まれてから6.5入力クロックサイクル後に有効です。図3に示すように、出力データは、出力クロックの両方のエッジでLSB (D0)を先頭にクロック同期出力されます。図5に詳細なシリアル出力タイミング図を示します。

図3. 全体のタイミング図

図4. 詳細な2変換タイミング図

図5. シリアル化された出力の詳細タイミング図

### 表2. 出力コード表(V<sub>RFFIO</sub> = 1.24V)

|                    | TWO'S-COMPLEMENT DIGITAL OUTPUT CODE  |                                                                                                 |                                                         |  |  |  |

|--------------------|---------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------|--|--|--|

| BINARY<br>D11 → D0 | HEXADECIMAL EQUIVALENT<br>OF D11 → D0 | $\begin{array}{c} \text{DECIMAL EQUIVALENT} \\ \text{OF D11} \rightarrow \text{D0} \end{array}$ | $V_{IN\_P} - V_{IN\_N}$ (mV)<br>( $V_{REFIO} = 1.24V$ ) |  |  |  |

| 0111 1111 1111     | 0x7FF                                 | +2047                                                                                           | +699.66                                                 |  |  |  |

| 0111 1111 1110     | 0x7FE                                 | +2046                                                                                           | +699.32                                                 |  |  |  |

|                    |                                       |                                                                                                 |                                                         |  |  |  |

| 0000 0000 0001     | 0x001                                 | +1                                                                                              | +0.34                                                   |  |  |  |

| 0000 0000 0000     | 0x000                                 | 0                                                                                               | 0                                                       |  |  |  |

| 1111 1111 1111     | 0xFFF                                 | -1                                                                                              | -0.34                                                   |  |  |  |

|                    |                                       |                                                                                                 |                                                         |  |  |  |

| 1000 0000 0001     | 0x801                                 | -2047                                                                                           | -699.66                                                 |  |  |  |

| 1000 0000 0000     | 0x800                                 | -2048                                                                                           | -700.00                                                 |  |  |  |

図6.2の補数形式の伝達関数

#### 出力データの伝達関数

MAX1438Bの出力データは2の補数形式です。次の式、表2および図6によって、ディジタル出力とアナログ入力の関係が定義されます。

$$V_{IN_P} - V_{IN_N} = FSR \times 2 \times \frac{CODE_{10}}{4096}$$

ここで、CODE<sub>10</sub>は、表2に示すようにディジタル出力 コードと等価な10進数です。 MAX1438Bのディジタル出力の容量性負荷は、可能な限り小さくしてください。

#### LVDSおよびSLVSの選択(SLVS/LVDS)

MAX1438Bの出力(OUT\_P、OUT\_N、CLKOUTP、CLKOUTN、FRAMEPおよびFRAMEN)をLVDSにするためにはSLVS/LVDSをローに駆動し、SLVSレベルにするためにはSLVS/LVDSをハイに駆動します。SLVSレベルにするには、DTをハイに駆動して2重終端をイネーブルします。LVDSおよびSLVSの出力電圧レベルについては「Electrical Characteristics(電気的特性)」の表を参照してください。

#### LVDSのテストパターン(LVDSTEST)

すべてのLVDSまたはSLVSの出力チャネルのテストパターンをイネーブルにするには、LVDSTESTをハイに駆動します。出力テストパターンは0000 1011 1101です。LVDSTESTをローに駆動すると通常の動作(テストパターンがディセーブル)になります。

### コモンモード出力(CMOUT)

CMOUTは、DC結合のアナログ入力用のコモンモードリファレンスを提供します。入力がDC結合される場合、MAX1438Bを駆動する回路出力のコモンモード電圧をV<sub>CMOUT</sub>の出力電圧の±50mV以内に合わせてください。駆動回路の出力コモンモード電圧はCMOUTから駆動することを推奨します。

#### 2重終端(DT)

MAX1438Bは、各差動出力ペア(OUT\_PとOUT\_N、CLKOUTPとCLKOUTN、FRAMEPとFRAMEN)間にオプションで内蔵の100 $\Omega$ の終端を提供します。ラインの端末の終端に加えて、出力に直接配置される2番目の終端は、ラインを逆行する望ましくない反射の排除に役立ちます。この機能は、長い配線パターン長(5インチ以上)またはインピーダンスが不整合の場合のアプリケーションに有用です。DTをハイに駆動すると2重終端が選択され、DTをローに駆動すると内部の終端抵抗が切り離されます(単一終端)。2重終端を選択すると、OVDDの電源電流が増加します(図7を参照)。

#### スタンバイモード

MAX1438Bは、変換が必要でないときにローパワー状態に遷移して、電力を効率的に使用するためにスタンバイモードを提供します。STBYは、すべてのチャネルおよび内部リファレンス回路のスタンバイモードを制御します。リファレンスはスタンバイモードで電源切断されません。STBYをハイに駆動するとスタンバイがイネーブルになります。スタンバイモードでは、LVDS/SLVSの全出力の出力インピーダンスは、DTがローの場合にはおよそ342 $\Omega$ になります。差動LVDS/SLVSの各出力の出力インピーダンスは、DTがハイの場合は100 $\Omega$ です。スタンバイ中の標準的な電源電流は「Electrical Characteristics」の表を参照してください。以下のリストは、スタンバイモードでのアナログ入力とディジタル出力の状態を示しています。

- IN\_PとIN\_Nの各アナログ入力は内部の入力アンプから切り離されます。

- リファレンス回路はアクティブのままです。

- OUT\_P、OUT\_N、CLKOUTP、CLKOUTN、FRAMEP およびFRAMENは、DTがローの場合には各出力ペア 間でおよそ342Ωです。DTがハイの場合は各差動出力 ペアのペア間で100Ωです。

図7. 2重終端

内部リファレンスモードで動作している場合、MAX1438B は、コンバータがスタンバイモードから抜け出すときに電源オンおよび安定化に200µsを要します。スタンバイモードから抜け出すには、STBYに印加される制御信号はハイからローに遷移しなければなりません。外部リファレンスを使用する場合、ウェイクアップ時間は外部のリファレンスドライバに依存します。

### アプリケーション情報

### 内部リファレンスを使用する フルスケール範囲の調整

MAX1438Bのフルスケール調整範囲は10% ( $\pm$ 5%)です。フルスケールの範囲を縮小するには、 $25k\Omega\sim250k\Omega$ の外付け抵抗またはポテンショメータ( $R_{ADJ}$ )をREFADJとGND間に追加してください。フルスケールの範囲を拡大するには、 $25k\Omega\sim250k\Omega$ の抵抗をREFADJとREFIO間に追加してください。図8は2つの可能な構成を示しています。

次式はR<sub>ADJ</sub>とアナログフルスケール範囲の変化との 関係を示しています。

$$FSR = 0.7V \left( 1 + \frac{1.25k\Omega}{R_{AD,I}} \right)$$

REFADJとREFIOの間に接続されたRADIの場合

$$FSR = 0.7V \left( 1 - \frac{1.25k\Omega}{R_{ADJ}} \right)$$

REFADJとGND間に接続されたRADIの場合

図8. ADCのフルスケール範囲の調整法を示す回路

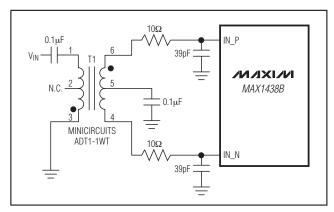

### トランス結合の使用

RFトランス(図9)は、シングルエンド入力信号源を完全な差動信号に変換する優れたソリューションを提供します。 MAX1438Bの入力コモンモード電圧は、 $f_{CLK}=64MHz$ では内部で0.76V (typ)にバイアスされています。1:1のトランスが示されていますが、駆動要件を緩和するためにステップアップトランスを選択することができます。オペアンプなどの入力ドライバからの信号振幅を小さくすると、全体的なひずみを改善することもできます。

#### グランド、バイパス、および基板レイアウト

MAX1438Bには高周波基板のレイアウト設計技術が必要です。基板レイアウトの参考用にMAX1438Bの EVキットのデータシートを参照してください。すべてのバイパスコンデンサは、可能な限りADCと同じ面でデバイスの近くに配置し、最小のインダクタンスとするために表面実装型のデバイスを使用してください。0.1 $\mu$ Fのセラミックコンデンサと並列にした0.1 $\mu$ Fのセラミックコンデンサで、AVDDをGNDにバイパスしてください。2.2 $\mu$ F以上のセラミックコンデンサと並列にした0.1 $\mu$ Fのセラミックコンデンサで、OVDDをGNDにバイパスしてください。2.2 $\mu$ F以上のセラミックコンデンサと並列にした0.1 $\mu$ Fのセラミックコンデンサと並列にした0.1 $\mu$ Fのセラミックコンデンサで、CVDDをGNDにバイパスしてください。

図9. トランス結合の入力駆動

充分に広い面積のグランドおよび電源平面の多層基板は、最高レベルの信号の整合性を実現します。MAX1438Bのグランド端子と裏面のエクスポーズドパッドは、同じグランド平面に接続してください。MAX1438Bは、低インダクタンスのグランド接続とするために裏面エクスポーズドパッドの接続が重要になります。このグランド平面はノイズの大きいディジタルシステムのグランド平面とは分離してください。

高速のディジタル信号の配線パターンは、敏感なアナログ 配線パターンから遠ざけて配線してください。すべての 信号ラインは短くして直角に曲げないでください。

差動アナログ入力回路のレイアウトは対称にして、すべての寄生要素が等しくバランスするようにしてください。対称な入力のレイアウトの例については、MAX1438BのEVキットのデータシートを参照してください。

### パラメータの定義

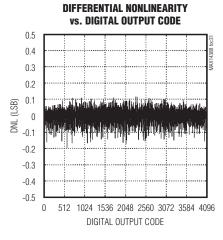

#### 積分非直線性(INL)

INLは実際の伝達関数上の値の直線からの偏差です。MAX1438Bの場合、この直線は、オフセットおよび利得誤差をゼロにした後の伝達関数の両端点を結んだ直線です。INL偏差はすべてのステップで測定され、ワーストケースの偏差は「Electrical Characteristics」の表に記載されています。

### 微分非直線性(DNL)

DNLは、1 LSBの実際のステップ幅と理想値との間の差です。1 LSB以下のDNL誤差仕様は、コード落ちがなくモノトニックな伝達関数を保証します。MAX1438Bの場合、DNL偏差はすべてのステップで測定され、ワーストケースの偏差は「Electrical Characteristics」の表に記載されています。

#### オフセット誤差

オフセット誤差は、実際の伝達関数が理想的な伝達関数と1点において、一致している程度を示す性能指数です。MAX1438Bの場合、理想的な中間スケールのディジタル出力の遷移は、アナログ入力間に-1/2 LSBが存在するときに起こります(図6)。バイポーラのオフセット誤差は、測定された中間スケール遷移点と理想的な中間スケール遷移点の間の偏差の大きさです。

#### 利得誤差

利得誤差は、実際の伝達関数の傾斜が理想的な伝達 関数の傾斜と一致している程度を示す性能指数です。 MAX1438Bの場合、利得誤差は、測定されたフル スケールとゼロスケール点の両遷移点の差から、理想的な フルスケールとゼロスケールの両遷移点の差を差し 引いた値です。

バイポーラデバイス(MAX1438B)の場合、フルスケール 遷移点は0x7FEから0x7FFで、ゼロスケール遷移点は0x800から0x801です。

#### クロストーク

クロストークは、各アナログ入力が他の入力から絶縁されている程度を示します。MAX1438Bの場合、5.3MHzで-0.5dBFSのアナログ信号が1つのチャネルに印加され、別のチャネルには30.3MHzで-0.5dBFSのアナログ信号が印加されます。5.3MHzのアナログ信号のチャネルでFFTが実行されます。このFFTから、クロストークは5.3MHzと30.3MHzの振幅の差として測定されます。

#### アパーチャ遅延

アパーチャ遅延(t<sub>AD</sub>)は、サンプリングクロックの立上り エッジと実際のサンプルが取得される時点との間と定義 される時間です。図10を参照してください。

#### アパーチャジッタ

アパーチャジッタ $(t_{AJ})$ はアパーチャ遅延のサンプル間の変動です。図10を参照してください。

#### 信号対ノイズ比(SNR)

ディジタルサンプルから完全に再生された波形に対して、理論的な最大SNRは、フルスケールアナログ入力(RMS値)のRMS量子化誤差(残留誤差)に対する比です。理想的で理論的な最小アナログ-ディジタル変換ノイズは量子化誤差のみに起因し、直接的にADCの分解能(Nビット)によってのみ生じます。

$SNR_{dB[max]} = 6.02_{dB} \times N + 1.76_{dB}$

実際には、量子化ノイズ以外に、サーマルノイズ、リファレンスノイズ、クロックジッタなどのその他のノイズ源があります。

図10. アパーチャジッタ/遅延仕様

MAX1438Bの場合、SNRはRMS信号のRMSノイズに対する比を取ることによって計算されます。RMSノイズには、基本波、最初の6つの高調波(HD2~HD7)およびDCオフセットを除いて、ナイキスト周波数までのすべてのスペクトル成分が含まれます。

### 信号対ノイズ+歪(SINAD)

SINADは、RMS信号のRMSノイズ+歪に対する比を取ることによって計算されます。RMSノイズ+歪には、基本波とDCオフセットを除くナイキスト周波数までのすべてのスペクトル成分が含まれます。

#### 有効ビット数(ENOB)

ENOBは、特定の入力周波数およびサンプリング速度でのADCのダイナミック性能を規定します。理想的なADCの誤差は量子化ノイズのみです。フルスケールの正弦波入力波形に対するENOBは次式で計算されます。

$$ENOB = \left(\frac{SINAD - 1.76}{6.02}\right)$$

#### 全高調波歪み(THD)

THDは、入力信号の最初の6個の高調波のRMS和の基本波自身に対する比です。これは次のように表されます。

THD =

$$20 \times \log \left( \frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + V_5^2 + V_6^2 + V_7^2}}{V_1} \right)$$

#### スプリアスフリーダイナミックレンジ(SFDR)

SFDRは、基本波(最大信号成分)のRMS振幅のDCオフセットを除いた2番目に大きいスプリアス成分のRMS値に対する比をデシベルで表したものです。SFDRはキャリアを基準にしたデシベル(dBc)で表されます。

#### 相互変調歪み(IMD)

IMDは、2つの入力トーン $f_1$ と $f_2$ の総合入力パワーを基準とする、ナイキスト周波数までのIM2 $\sim$ IM5の相互変調積の総合パワーです。各入力トーンのレベルは-6.5dBFSです。相互変調積は次の通りです。

- 2次相互変調積(IM2): f<sub>1</sub> + f<sub>2</sub>、f<sub>2</sub> f<sub>1</sub>

- 3次相互変調積(IM3): 2 x f<sub>1</sub> f<sub>2</sub>、2 x f<sub>2</sub> f<sub>1</sub>、2 x f<sub>1</sub> + f<sub>2</sub>、2 x f<sub>2</sub> + f<sub>1</sub>

- 4次相互変調積(IM4): 3 x f<sub>1</sub> f<sub>2</sub>、3 x f<sub>2</sub> f<sub>1</sub>、3 x f<sub>1</sub> + f<sub>2</sub>、3 x f<sub>2</sub> + f<sub>1</sub>

- 5次相互変調積(IM5): 3 x f<sub>1</sub> 2 x f<sub>2</sub>、3 x f<sub>2</sub> 2 x f<sub>1</sub>、3 x f<sub>1</sub> + 2 x f<sub>2</sub>、3 x f<sub>2</sub> + 2 x f<sub>1</sub>

#### 3次相互変調(IM3)

IM3は、2つの入力トーン $f_1$ と $f_2$ の総合入力パワーを基準とする、ナイキスト周波数までの3次相互変調積の総合パワーです。各入力トーンのレベルは-6.5dBFSです。3次相互変調積は、2 x  $f_1$  -  $f_2$ 、2 x  $f_2$  -  $f_1$ 、2 x  $f_1$  +  $f_2$ 、2 x  $f_2$  +  $f_1$ です。

#### 小信号帯域幅

信号のスルーレートがADC性能を制限しないように、-20.5dBFSの小さいアナログ入力信号がADCに印加されます。次に、ディジタル化した変換結果の大きさが-3dBだけ減衰するポイントまで入力周波数を変化させます。

#### フルパワー帯域幅

大きい-0.5dBFSのアナログ入力信号をADCに印加し、次に、ディジタル化した変換結果の大きさが-3dBだけ減衰するポイントまで入力周波数を変化させます。このポイントがフルパワーの入力帯域幅周波数として定義されます。

#### 利得マッチング

利得マッチングは、8個のすべてのADCチャネルの利得が相互に一致する程度を示す性能指数です。MAX1438Bの場合、利得マッチングは、すべてのアナログ入力チャネルに同じ5.3MHzで-0.5dBFSのアナログ信号を印加して測定されます。これらのアナログ入力は64Mspsでサンプルされ、振幅の最大偏差は利得マッチングとしてdBで「Electrical Characteristics」の表に示されています。

#### 位相マッチング

位相マッチングは、8個のすべてのADCチャネルの位相が相互に良く一致する程度を示す性能指数です。MAX1438Bの場合、位相マッチングは、同じ5.3MHzで-0.5dBFSのアナログ信号をすべてのアナログ入力チャネルに印加して測定されます。これらのアナログ入力は64Mspsでサンプルされ、位相の最大偏差は度で位相マッチングとして「Electrical Characteristics」の表に示されています。

#### ピン配置

#### パッケージ

最新のパッケージ情報とランドパターンは、japan.maxim-ic.com/packagesをご参照ください。

| パッケージタイプ   | パッケージコード | ドキュメントNo. |

|------------|----------|-----------|

| 68 TQFN-EP | T6800-4  | 21-0142   |

# マキシム・ジャパン株式会社

〒169-0051東京都新宿区西早稲田3-30-16(ホリゾン1ビル) TEL. (03)3232-6141 FAX. (03)3232-6149

マキシムは完全にマキシム製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。 マキシムは随時予告なく回路及び仕様を変更する権利を留保します。

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_\_\_\_\_