# デイジーチェーン・インターフェースを備えた 15セルのバッテリ・スタック・モニタ

## 特長

- 最大15個の直列バッテリ・セルを測定

- 最大全測定誤差:2.2mV

- スタック可能なアーキテクチャで数百セルをサポート

- isoSPI™ インターフェース内蔵

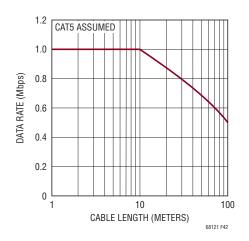

- 1Mbの絶縁型シリアル通信

- 1本のツイスト・ペア・ケーブルを使用(最大100m)

- 低いEMI感度およびEMI放射

- 双方向により破損ワイヤを保護

- 245 µs でシステム内の全てのセルを測定

- 電圧と電流の同期測定

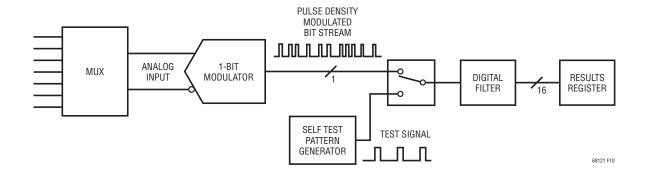

- プログラム可能な3次ノイズ・フィルタを備えた16ビット・デルタシグマ $(\Delta\Sigma)$ 型 A/D コンバータ(ADC)

- ISO 26262 準拠システム用に設計

- プログラム可能なパルス幅変調によるパッシブ・セル・ バランス調整(最大 200mA)

- 9個の汎用デジタルI/0またはアナログ入力

- 温度やその他のセンサー入力

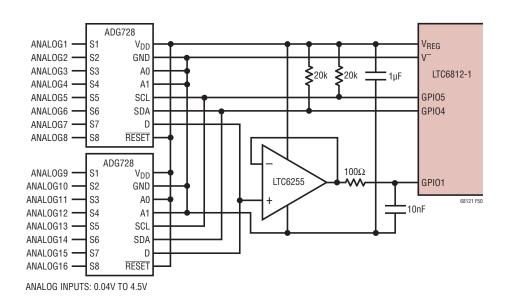

- I<sup>2</sup>CまたはSPIマスタとして設定可能

- スリープ・モード時電源電流:6uA

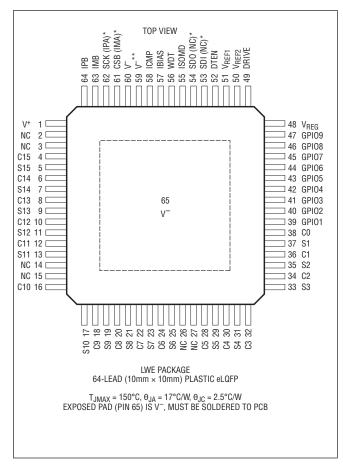

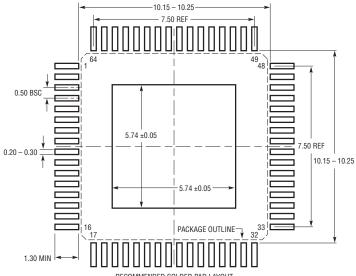

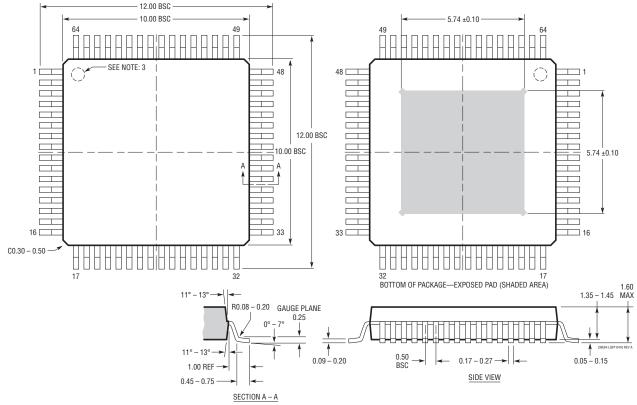

- 64ピンeLQFPパッケージ

# アプリケーション

- 電気自動車およびハイブリッド電気自動車

- バックアップ・バッテリ・システム

- グリッド蓄電システム

- 高出力携帯機器

### 概要

LTC<sup>®</sup>6812-1は、最大15個の直列接続バッテリ・セルを2.2mV未満の全測定誤差で測定するマルチセル・バッテリ・スタック・モニタです。LTC6812-1のセル測定範囲は0V~5Vなので、ほとんどのバッテリの組成に適しています。15個全てのセルを245 µs 以内に測定可能であり、低めのデータ・アクイジション・レートを選択することにより、ノイズを大幅に低減できます。

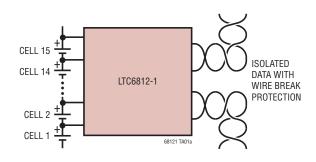

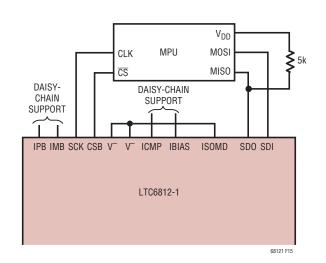

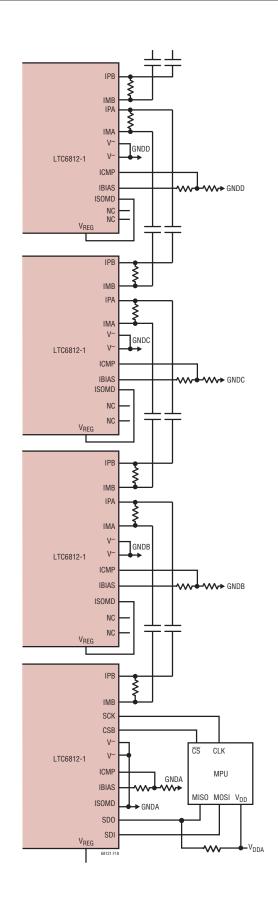

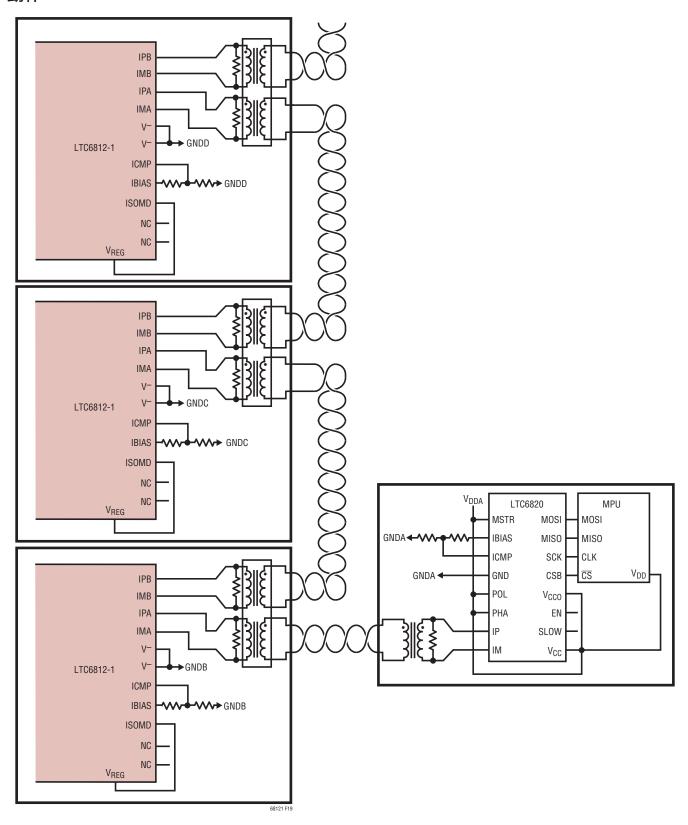

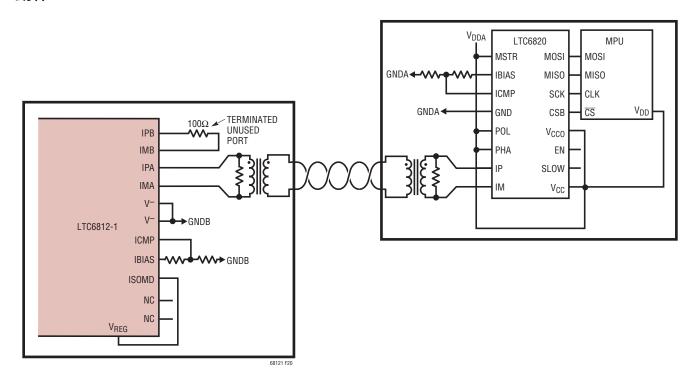

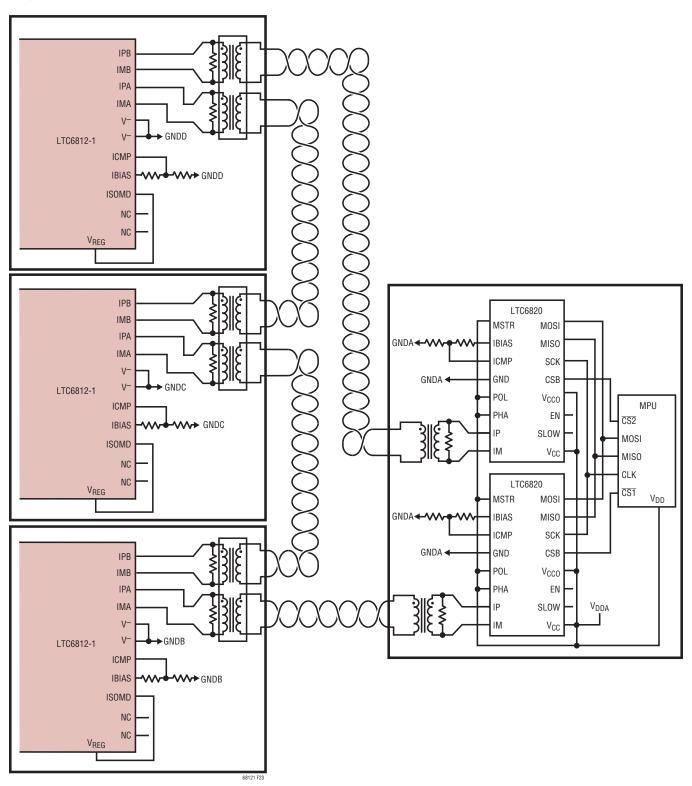

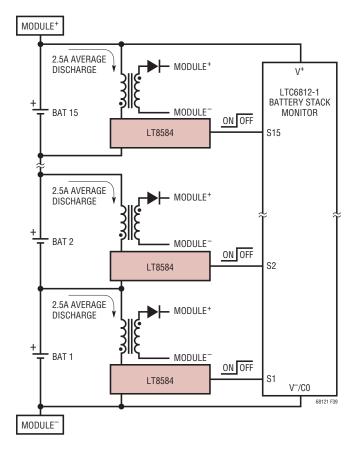

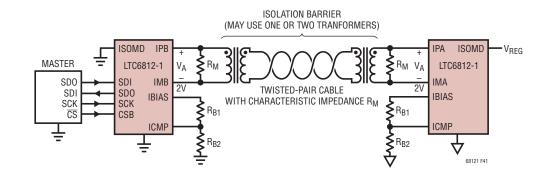

複数のLTC6812-1デバイスを直列接続できるので、長い高電圧バッテリ列のセルを同時に監視できます。各LTC6812-1は、RF耐性のある高速、長距離通信用のisoSPIインターフェースを備えています。複数のデバイスをデイジーチェーンで接続し、1つのホスト・プロセッサを全てのデバイスに接続します。このデイジーチェーンは双方向に動作するので、通信経路に障害が発生した場合でも、通信の完全性が確保されます。

LTC6812-1には、バッテリ・スタックまたは絶縁型電源から直接給電できます。LTC6812-1は、セルごとのパッシブ方式バランス調整機能を内蔵しており、PWMのデューティ・サイクルをセルごとに個別制御できます。その他の機能には、内蔵の5Vレギュレータ、9つの汎用I/Oライン、消費電流が6μAまで減少するスリープ・モードなどがあります。

全ての登録商標および商標の所有権は、それぞれの所有者に帰属します。8908779、 9182428、9270133を含む米国特許によって保護されています。

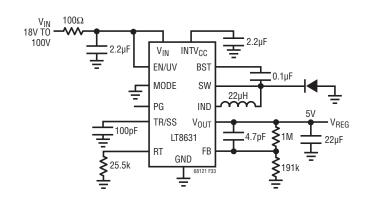

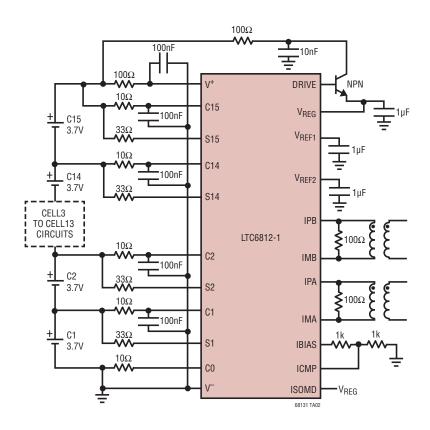

# 標準的応用例

#### 15 セルのモニタおよびバランス調整 IC

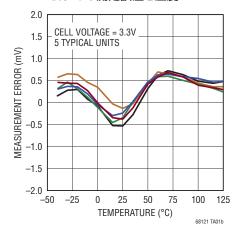

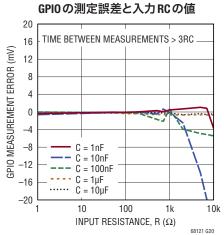

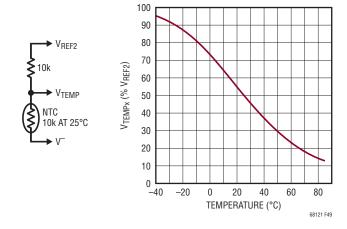

#### セル15の測定誤差と温度

Rev. 0

1

# LTC6812-1

# 目次

| 特長                     | 1     |

|------------------------|-------|

| アプリケーション               | 1     |

| 標準的応用例                 | 1     |

| 概要                     | 1     |

| 絶対最大定格                 | 3     |

| 発注情報                   | 3     |

| ピン配置                   | 3     |

| 電気的特性                  |       |

| 代表的な性能特性               | 9     |

| ピン機能                   |       |

| ブロック図                  |       |

| LTC6811-1 からの改善点       |       |

| 動作                     | 18    |

| ステート図                  | 18    |

| LTC6812-1 のコアのステートの説明  | 18    |

| isoSPIステートの説明          | 19    |

| 消費電力                   | 19    |

| ADCの動作                 | 20    |

| データ・アクイジション・システムの診断    | 25    |

| ウォッチドッグ・タイマーと放電タイマー    | 32    |

| セル・バランス調整に対応したSピンのパルス幅 | 変調.33 |

| 放電タイマー・モニタ             | 34    |

| GPIO を使用するLTC6812-1のI <sup>2</sup> C/SPIマスタ | 34 |

|---------------------------------------------|----|

| Sピンの制御設定を使用したSピンのパルス生成                      | 39 |

| \$ピンのミュート                                   | 40 |

| シリアル・インターフェースの概要                            | 40 |

| 4線式シリアル・ペリフェラル・インターフェース                     |    |

| (SPI)の物理層                                   | 40 |

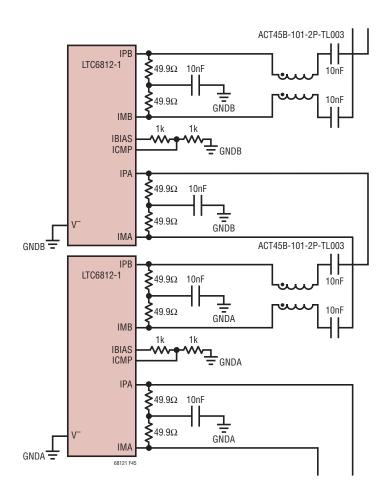

| 2線絶縁型インターフェース(isoSPI)の物理層                   | 40 |

| データ・リンク層                                    | 51 |

| ネットワーク層                                     | 51 |

| アプリケーション情報                                  | 67 |

| DC 電力の供給                                    | 67 |

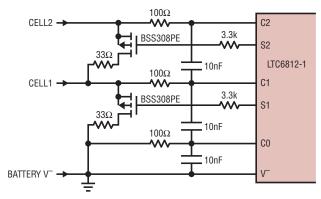

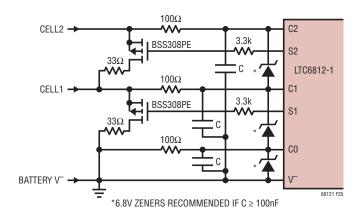

| 内部保護とフィルタリング                                | 68 |

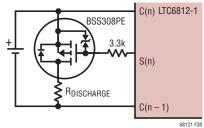

| セルのバランス調整                                   | 71 |

| セル測定時の放電制御                                  | 72 |

| デジタル通信                                      | 75 |

| 高度なアプリケーション                                 | 82 |

| 外部温度プローブの読取り                                | 84 |

| <b>パッケージ</b>                                | 85 |

| 票準的応用例                                      | 86 |

| 旧本制口                                        |    |

# 絶対最大定格

### (Note 1)

| 全電源電圧                                              |

|----------------------------------------------------|

| V <sup>+</sup> - V <sup>-</sup> 間93.75V            |

| 電源電圧(C10基準)                                        |

| V <sup>+</sup> - C10 間50V                          |

| 入力電圧(V-基準)                                         |

| C00.3V~6V                                          |

| C150.3V~(V+ + 5.5Vと93.75Vの低い方)                     |

| C(n)、S(n)0.3V~(8 • nと93.75Vの低い方)                   |

| IPA、IMA、IPB、IMB $-0.3V \sim V_{REG} + 0.3V \le 6V$ |

| DRIVE0.3V~7V                                       |

| その他全てのピン0.3V~6V                                    |

| 入力間の電圧                                             |

| C(n)-C(n-1) 間、S(n)-C(n-1) 間0.3V~8V                 |

| C13-C10 間0.3V~21V                                  |

| C8-C5 間0.3V~21V                                    |

| C3-C0 間0.3V~21V                                    |

| ピンへの流入電流/ピンからの流出電流                                 |

| V <sub>REG</sub> 、IPA、IMA、IPB、IMB、C(n)、S(n) 以外の    |

| 全てのピン10mA                                          |

| IPA、IMA、IPB、IMB30mA                                |

| 規定ジャンクション温度範囲                                      |

| LTC6812I-140°C~85°C                                |

| LTC6812H-140°C~125°C                               |

| ジャンクション温度150°C                                     |

| 保存温度範囲65°C~150°C                                   |

| デバイスのHBM(人体モデル)ESD分類レベル:1C                         |

| デバイスのCDM(デバイス帯電モデル)ESD分類レベル:C5                     |

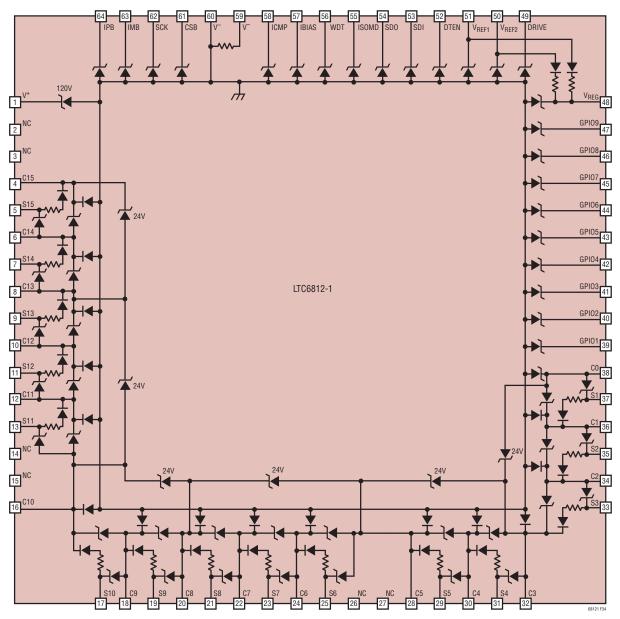

# ピン配置

- \*これらのピンの機能は、ISOMDの接続先により異なる。 ISOMDをVでに接続した場合: CSB、SCK、SDI、SDO ISOMDをV<sub>REG</sub>に接続した場合: IPA、IMA、NC、NC

- \*\*このピンはV゚に接続する必要がある。

# 発注情報

| トレイ                  | 製品マーキング*     | パッケージ                 | MSL定格 | 規定ジャンクション温度範囲  |

|----------------------|--------------|-----------------------|-------|----------------|

| LTC6812ILWE-1#3ZZPBF | LTC6812LWE-1 | 64-Lead Plastic eLQFP | 3     | -40°C to 85°C  |

| LTC6812HLWE-1#3ZZPBF | LTC6812LWE-1 | 64-Lead Plastic eLQFP | 3     | -40°C to 125°C |

更に広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。

テープ&リールの仕様。一部のパッケージは、#TRMPBF接尾部の付いた指定の販売経路を通じて500個入りのリールで供給可能です。

LTC####モデルのバージョンは、車載アプリケーションの品質と信頼性の条件に対応するため、管理された製造工程により供給されます。これらのモデルは#WTRPBF、#WPBF、または#ZZPBF 接尾部を付けて供給されており、アナログ・デバイセズのARPLに記載されています。

これらの車載モデルの仕様は商用モデルと異なる場合があるため、設計者はこのデータシートの電気的特性のセクションを慎重にレビューしてください。車載アプリケーションには、上記の車載グレード製品のみを提供しています。特定製品の発注情報とこれらのモデルに特有の車載信頼性レポートについては、弊社または弊社代理店にお問い合わせください。

●は規定の全温度範囲での規格値を意味する。それ以外は  $T_A=25^\circ C$  での値。注記がない限り、テスト条件は  $V^+=49.5V$ 、 $V_{REG}=5.0V$ 。注記がない限り、ISOMD ピンは  $V^-$ ピンに接続する。

| SYMBOL  | PARAMETER                                 | CONDITIONS                                              |   | MIN   | TYP   | MAX   | UNITS  |

|---------|-------------------------------------------|---------------------------------------------------------|---|-------|-------|-------|--------|

| ADCのDCイ | 仕様                                        |                                                         |   |       |       |       |        |

|         | Measurement Resolution                    |                                                         |   |       | 0.1   |       | mV/Bit |

|         | ADC Offset Voltage                        | (Note 2)                                                |   |       | 0.1   |       | mV     |

|         | ADC Gain Error                            | (Note 2)                                                |   |       | 0.01  |       | %      |

|         | Total Measurement Error (TME) in Normal   | C(n) to C(n-1), GPIO(n) to $V^- = 0$                    |   |       | ±0.2  |       | mV     |

|         | Mode                                      | C(n) to $C(n-1) = 2.0$                                  |   |       |       | ±1.6  | mV     |

|         |                                           | C(n) to C(n-1), GPIO(n) to $V^- = 2.0$ , LTC6812I       | • |       |       | ±1.8  | mV     |

|         |                                           | C(n) to C(n-1), GPIO(n) to $V^- = 2.0$ , LTC6812H       | • |       |       | ±2.0  | mV     |

|         |                                           | C(n) to $C(n-1) = 3.3$                                  |   |       |       | ±2.2  | mV     |

|         |                                           | C(n) to C(n-1), GPIO(n) to $V^- = 3.3$ , LTC6812I       | • |       |       | ±3.0  | mV     |

|         |                                           | C(n) to C(n-1), GPIO(n) to $V^- = 3.3$ , LTC6812H       | • |       |       | ±3.3  | mV     |

|         |                                           | C(n) to $C(n-1) = 4.2$                                  |   |       |       | ±2.8  | mV     |

|         |                                           | C(n) to C(n-1), GPIO(n) to $V^- = 4.2$ , LTC6812I       | • |       |       | ±3.8  | mV     |

|         |                                           | C(n) to C(n-1), GPIO(n) to $V^- = 4.2$ , LTC6812H       | • |       |       | ±4.2  | mV     |

|         |                                           | C(n) to C(n-1), GPIO(n) to $V^- = 5.0$                  |   |       | ±1    |       | mV     |

|         |                                           | Sum of Cells                                            | • |       | ±0.05 | ±0.35 | %      |

|         |                                           | Internal Temperature, T = Maximum Specified Temperature |   |       | ±5    |       | °C     |

|         |                                           | V <sub>REG</sub> Pin                                    | • | -1    | -0.15 | 0     | %      |

|         |                                           | V <sub>REF2</sub> Pin                                   | • | -0.05 | 0.05  | 0.20  | %      |

|         |                                           | Digital Supply Voltage, V <sub>REGD</sub>               | • | -0.5  | 0.5   | 1.5   | %      |

|         | Total Measurement Error (TME) in Filtered | C(n) to C(n-1), GPIO(n) to $V^- = 0$                    |   |       | ±0.1  |       | mV     |

|         | Mode                                      | C(n) to C(n-1) = 2.0                                    |   |       |       | ±1.6  | mV     |

|         |                                           | C(n) to C(n-1), GPIO(n) to $V^- = 2.0$ , LTC6812I       | • |       |       | ±1.8  | mV     |

|         |                                           | C(n) to C(n-1), GPIO(n) to $V^- = 2.0$ , LTC6812H       | • |       |       | ±2.0  | mV     |

|         |                                           | C(n) to $C(n-1) = 3.3$                                  |   |       |       | ±2.2  | mV     |

|         |                                           | C(n) to C(n-1), GPIO(n) to $V^- = 3.3$ , LTC6812I       | • |       |       | ±3.0  | mV     |

|         |                                           | C(n) to C(n-1), GPIO(n) to $V^- = 3.3$ , LTC6812H       | • |       |       | ±3.3  | mV     |

|         |                                           | C(n) to $C(n-1) = 4.2$                                  |   |       |       | ±2.8  | mV     |

|         |                                           | C(n) to C(n-1), GPIO(n) to $V^- = 4.2$ , LTC6812I       | • |       |       | ±3.8  | mV     |

|         |                                           | C(n) to C(n-1), GPIO(n) to $V^- = 4.2$ , LTC6812H       | • |       |       | ±4.2  | mV     |

|         |                                           | C(n) to C(n-1), GPIO(n) to $V^- = 5.0$                  |   |       | ±1    |       | mV     |

|         |                                           | Sum of Cells                                            | • |       | ±0.05 | ±0.35 | %      |

|         |                                           | Internal Temperature, T = Maximum Specified Temperature |   |       | ±5    |       | °C     |

|         |                                           | V <sub>REG</sub> Pin                                    | • | -1    | -0.15 | 0     | %      |

|         |                                           | V <sub>REF2</sub> Pin                                   | • | -0.05 | 0.05  | 0.20  | %      |

|         |                                           | Digital Supply Voltage, V <sub>REGD</sub>               | • | -0.5  | 0.8   | 1.5   | %      |

● は規定の全温度範囲での規格値を意味する。 それ以外は  $T_A=25^\circ C$  での値。注記がない限り、テスト条件は  $V^+=49.5V$ 、 $V_{REG}=5.0V$ 。注記がない限り、ISOMD ピンは  $V^-$ ピンに接続する。

| SYMBOL            | PARAMETER                                           | CONDITIONS                                       |                    |   | MIN          | TYP          | MAX          | UNITS    |

|-------------------|-----------------------------------------------------|--------------------------------------------------|--------------------|---|--------------|--------------|--------------|----------|

|                   | Total Measurement Error (TME) in                    | C(n) to C(n-1), GPIO(n) to                       | V <sup>-</sup> = 0 |   |              | ±2           |              | mV       |

|                   | Fast Mode                                           | C(n) to C(n-1), GPIO(n) to                       | V = 2.0            | • |              |              | ±4           | mV       |

|                   |                                                     | C(n) to C(n-1), GPIO(n) to                       | V = 3.3            | • |              |              | ±6           | mV       |

|                   |                                                     | C(n) to C(n-1), GPIO(n) to                       | V = 4.2            | • |              |              | ±8.3         | mV       |

|                   |                                                     | C(n) to C(n-1), GPIO(n) to $V^- = 5.0$           |                    |   | ±10          |              | mV           |          |

|                   |                                                     | Sum of Cells                                     |                    | • |              | ±0.15        | ±0.5         | %        |

|                   |                                                     | Internal Temperature, T = Temperature            | Maximum Specified  |   |              | ±5           |              | °C       |

|                   |                                                     | V <sub>REG</sub> Pin                             |                    | • | -1.5         | -0.15        | 1            | %        |

|                   |                                                     | V <sub>REF2</sub> Pin                            |                    | • | -0.18        | 0.05         | 0.32         | %        |

|                   |                                                     | Digital Supply Voltage, V <sub>R</sub>           | EGD                | • | -2.5         | -0.4         | 2            | %        |

|                   | Input Range                                         | C(n) n = 1 to 15                                 |                    | • | C(n-1)       | C(n-         | -1) + 5      | V        |

|                   |                                                     | CO                                               |                    | • | 0            |              | 1            | V        |

|                   |                                                     | GPIO(n) n = 1 to 9                               |                    | • | 0            |              | 5            | V        |

| IL                | Input Leakage Current When Inputs Are Not           | C(n) n = 0 to 15                                 |                    | • |              | 10           | ±250         | nA       |

|                   | Being Measured                                      | GPIO(n) n = 1 to 9                               |                    | • |              | 10           | ±250         | nA       |

|                   | Input Current When Inputs Are Being                 | C(n) n = 0 to 15                                 |                    |   |              | ±1           |              | μА       |

|                   | Measured (State: Core = MEASURE)                    | GPIO(n) n = 1 to 9                               |                    |   |              | ±1           |              | μА       |

|                   | Input Current During Open Wire Detection            |                                                  |                    | • | 70           | 100          | 130          | μА       |

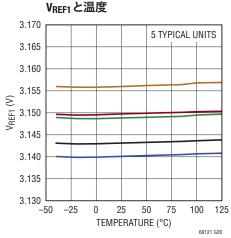

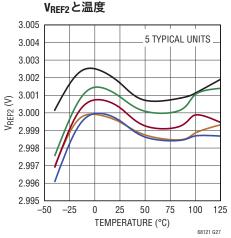

| 電圧リファ             | アレンスの仕様                                             |                                                  |                    |   |              |              |              |          |

| V <sub>REF1</sub> | 1st Reference Voltage                               | V <sub>REF1</sub> Pin, No Load                   |                    | • | 3.0          | 3.15         | 3.3          | V        |

|                   | 1st Reference Voltage TC                            | V <sub>REF1</sub> Pin, No Load                   |                    |   |              | 3            |              | ppm/°C   |

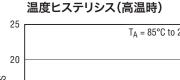

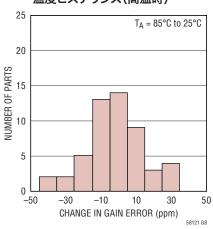

|                   | 1st Reference Voltage Thermal Hysteresis            | V <sub>REF1</sub> Pin, No Load                   |                    |   |              | 20           |              | ppm      |

|                   | 1st Reference Voltage Long Term Drift               | V <sub>REF1</sub> Pin, No Load                   |                    |   |              | 20           |              | ppm/√khr |

| V <sub>REF2</sub> | 2nd Reference Voltage                               | V <sub>REF2</sub> Pin, No Load                   |                    | • | 2.993        | 3            | 3.007        | V        |

|                   |                                                     | V <sub>REF2</sub> Pin, 5k Load to V <sup>-</sup> |                    | • | 2.992        | 3            | 3.008        | V        |

|                   | 2nd Reference Voltage TC                            | V <sub>REF2</sub> Pin, No Load                   |                    |   |              | 10           |              | ppm/°C   |

|                   | 2nd Reference Voltage Thermal Hysteresis            | V <sub>REF2</sub> Pin, No Load                   |                    |   |              | 100          |              | ppm      |

|                   | 2nd Reference Voltage Long Term Drift               | V <sub>REF2</sub> Pin, No Load                   |                    |   |              | 60           |              | ppm/√khr |

| 全般的な              | DC仕様                                                |                                                  |                    |   |              |              |              |          |

| lvp               | V <sup>+</sup> Supply Current                       | State: Core = SLEEP,                             | $V_{REG} = 0V$     |   |              | 6.1          | 11           | μА       |

|                   | (SeeFigure 1: LTC6812-1 Operation<br>State Diagram) | isoSPI = IDLE                                    | $V_{REG} = 0V$     | • |              | 6.1          | 18           | μА       |

|                   | oute Diagram,                                       |                                                  | $V_{REG} = 5V$     |   |              | 3            | 5            | μА       |

|                   |                                                     |                                                  | $V_{REG} = 5V$     | • |              | 3            | 9            | μА       |

|                   |                                                     | State: Core = STANDBY                            |                    | • | 9<br>6       | 14<br>14     | 22<br>28     | μA<br>μA |

|                   | State: Core = REFUP                                 |                                                  |                    | • | 0.4<br>0.375 | 0.55<br>0.55 | 0.8<br>0.825 | mA<br>mA |

|                   |                                                     | State: Core = MEASURE                            |                    | • | 0.65<br>0.6  | 0.95<br>0.95 | 1.35<br>1.4  | mA<br>mA |

●は規定の全温度範囲での規格値を意味する。それ以外は  $T_A=25^\circ C$  での値。注記がない限り、テスト条件は  $V^+=49.5V$ 、 $V_{REG}=5.0V$ 。注記がない限り、ISOMD ピンは  $V^-$ ピンに接続する。

| SYMB0L                   | PARAMETER                                           | CONDITIONS                         |                       |   | MIN        | TYP        | MAX        | UNITS    |

|--------------------------|-----------------------------------------------------|------------------------------------|-----------------------|---|------------|------------|------------|----------|

| I <sub>REG(CORE)</sub>   | V <sub>REG</sub> Supply Current                     | State: Core = SLEEP,               | $V_{REG} = 5V$        |   |            | 3.1        | 6          | μА       |

|                          | (SeeFigure 1: LTC6812-1 Operation State Diagram)    | isoSPI = IDLE $V_{REG} = 5V$       |                       | • |            | 3.1        | 9          | μА       |

|                          |                                                     | State: Core = STANDBY              |                       |   | 10         | 35         | 60         | μА       |

|                          |                                                     |                                    |                       | • | 6          | 35         | 65         | μΑ       |

|                          |                                                     | State: Core = REFUP                |                       | • | 0.4<br>0.3 | 0.9<br>0.9 | 1.4<br>1.5 | mA<br>mA |

|                          |                                                     | State: Core = MEASURE              |                       | + | 14         | 15         | 16         | mA       |

|                          |                                                     | otato. Ooro – MEAOONE              |                       | • | 13.5       | 15         | 16.5       | mA       |

| I <sub>REG(isoSPI)</sub> | Additional V <sub>REG</sub> Supply Current          | ISOMD = 0,                         | READY                 | • | 3.6        | 4.5        | 5.2        | mA       |

|                          | if isoSPI in READY/ACTIVE States                    | $R_{B1} + R_{B2} = 2k$             | ACTIVE                | • | 5.6        | 6.8        | 8.1        | mA       |

|                          | Note: ACTIVE State Current                          | ISOMD = 1,                         | READY                 | • | 4.0        | 5.2        | 6.5        | mA       |

|                          | Assumes $t_{CLK} = 1\mu s$ , (Note 3)               | $R_{B1} + R_{B2} = 2k$             | ACTIVE                | • | 7.0        | 8.5        | 10.5       | mA       |

|                          |                                                     | ISOMD = 0,                         | READY                 | • | 1.0        | 1.8        | 2.4        | mA       |

|                          |                                                     | $R_{B1} + R_{B2} = 20k$            | ACTIVE                | • | 1.3        | 2.3        | 3.3        | mA       |

|                          |                                                     | ISOMD = 1,                         | READY                 | • | 1.6        | 2.5        | 3.5        | mA       |

|                          |                                                     | $R_{B1} + R_{B2} = 20k$            | ACTIVE                | • | 1.8        | 3.1        | 4.8        | mA       |

|                          | V <sup>+</sup> Supply Voltage                       | TME Specifications Met             |                       | • | 16         | 50         | 75         | V        |

|                          | V <sup>+</sup> to C15 Voltage                       | TME Specifications Met             |                       | • | -0.3       |            |            | V        |

|                          | V <sup>+</sup> to C10 Voltage                       | TME Specifications Met             |                       | • |            |            | 40         | V        |

|                          | C11 Voltage                                         | TME Specifications Met             |                       | • | 2.5        |            |            | V        |

|                          | C6 Voltage                                          | TME Specifications Met             |                       | • | 1          |            |            | V        |

| V <sub>REG</sub>         | V <sub>REG</sub> Supply Voltage                     | TME Supply Rejection < 1           | mV/V                  | • | 4.5        | 5          | 5.5        | V        |

|                          | DRIVE Output Voltage                                | Sourcing 1µA                       |                       |   | 5.4        | 5.7        | 5.9        | V        |

|                          |                                                     |                                    |                       | • | 5.2        | 5.7        | 6.1        | V        |

|                          |                                                     | Sourcing 500µA                     |                       | • | 5.2        | 5.7        | 6.1        | V        |

| V <sub>REGD</sub>        | Digital Supply Voltage                              |                                    |                       | • | 2.7        | 3          | 3.6        | V        |

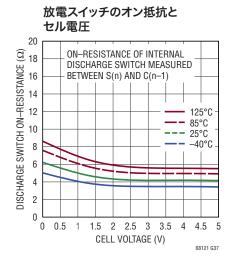

|                          | Discharge Switch ON Resistance                      | V <sub>CELL</sub> = 3.6V           |                       | • |            | 4          | 10         | Ω        |

|                          | Thermal Shutdown Temperature                        |                                    |                       |   |            | 150        |            | °C       |

| V <sub>OL(WDT)</sub>     | Watch Dog Timer Pin Low                             | WDT Pin Sinking 4mA                |                       | • |            |            | 0.4        | V        |

| V <sub>OL(GPIO)</sub>    | General Purpose I/O Pin Low                         | GPIO Pin Sinking 4mA (Us           | ed as Digital Output) | • |            |            | 0.4        | V        |

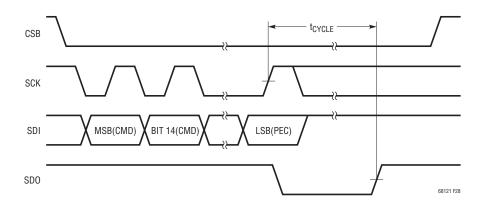

| ADC のタイ                  | /ミング仕様                                              |                                    |                       |   |            |            |            |          |

| tcycle                   | Measurement + Calibration Cycle Time                | Measure 15 Cells                   |                       | • | 1692       | 1956       | 2077       | μs       |

| (Figure 3,<br>Figure 4,  | When Starting from the REFUP State in Normal Mode   | Measure 3 Cells                    |                       | • | 352        | 407        | 432        | μs       |

| Figure 6)                |                                                     | Measure 15 Cells and 2 GPIO Inputs |                       | • | 2382       | 2753       | 2924       | μs       |

|                          | Measurement + Calibration Cycle Time                | Measure 15 Cells                   |                       | • | 145.2      | 167.8      | 178.2      | ms       |

|                          | When Starting from the REFUP State in Filtered Mode | Measure 3 Cells                    |                       | • | 29.1       | 33.6       | 35.7       | ms       |

|                          |                                                     | Measure 15 Cells and 2 G           | PIO Inputs            | • | 203.2      | 234.9      | 249.5      | ms       |

|                          | Measurement + Calibration Cycle Time                | Measure 15 Cells                   |                       | • | 811        | 937        | 996        | μs       |

|                          | When Starting from the REFUP State in Fast Mode     | Measure 3 Cells                    |                       | • | 176        | 203        | 215        | μs       |

|                          |                                                     | Measure 15 Cells and 2 G           | PIO Inputs            | • | 1149       | 1328       | 1410       | μs       |

Rev. 0

6

詳細:www.analog.com

● は規定の全温度範囲での規格値を意味する。 それ以外は  $T_A=25^\circ C$  での値。注記がない限り、テスト条件は  $V^+=49.5V$ 、 $V_{REG}=5.0V$ 。注記がない限り、ISOMD ピンは  $V^-$ ピンに接続する。

| SYMBOL                                          | PARAMETER                                                                                                                               | CONDITIONS                                                                               |   | MIN               | TYP                      | MAX        | UNITS          |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---|-------------------|--------------------------|------------|----------------|

| tskew1                                          | Skew Time.The Time Difference Between                                                                                                   | Fast Mode                                                                                | • | 168               | 194                      | 206        | μs             |

| (Figure 6)                                      | GPIO2 and Cell 1 Measurements, Command<br>= ADCVAX                                                                                      | Normal Mode                                                                              | • | 470               | 543                      | 577        | μs             |

| t <sub>SKEW2</sub>                              | Skew Time.The Time Difference Between                                                                                                   | Fast Mode                                                                                | • | 162               | 187                      | 198        | μs             |

| (Figure 3)                                      | Cell 15 and Cell 1 Measurements,<br>Command = ADCV                                                                                      | Normal Mode                                                                              | • | 464               | 536                      | 569        | μs             |

| tskew3                                          | Skew Time.The Time Difference Between                                                                                                   | Fast Mode                                                                                | • | 127               | 147                      | 156        | μs             |

| (Figure 6)                                      | Cell 15 and GPIO1 Measurements,<br>Command = ADCVAX                                                                                     | Normal Mode                                                                              | • | 354               | 409                      | 434        | μs             |

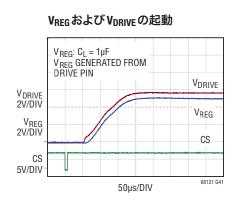

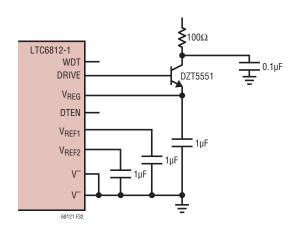

| twake                                           | Regulator Start-Up Time                                                                                                                 | V <sub>REG</sub> Generated from DRIVE Pin (Figure 32)                                    | • |                   | 200                      | 400        | μs             |

| t <sub>SLEEP</sub>                              | Watchdog or Discharge Timer                                                                                                             | DTEN Pin = 0 or DCT0[3:0] = 0000                                                         | • | 1.8               | 2                        | 2.2        | sec            |

| (Figure 26)                                     |                                                                                                                                         | DTEN Pin = 1 and DCT0[3:0] ≠ 0000                                                        |   | 0.5               |                          | 120        | min            |

| t <sub>REFUP</sub><br>(Figure 3 for<br>example) | Reference Wake-Up Time.Added to $t_{CYCLE}$ Time When Starting from the STANDBY State. $t_{REFUP} = 0$ When Starting from Other States. | t <sub>REFUP</sub> is Independent of the Number of Channels<br>Measured and the ADC Mode | • | 2.7               | 3.5                      | 4.4        | ms             |

| fs                                              | ADC Clock Frequency                                                                                                                     |                                                                                          |   |                   | 3.3                      |            | MHz            |

| SPIインター                                         | -フェースのDC仕様                                                                                                                              |                                                                                          |   |                   |                          |            |                |

| V <sub>IH(SPI)</sub>                            | SPI Pin Digital Input Voltage High                                                                                                      | Pins CSB, SCK, SDI                                                                       | • | 2.3               |                          |            | V              |

| V <sub>IL(SPI)</sub>                            | SPI Pin Digital Input Voltage Low                                                                                                       | Pins CSB, SCK, SDI                                                                       | • |                   |                          | 0.8        | V              |

| V <sub>IH(CFG)</sub>                            | Configuration Pin Digital Input Voltage High                                                                                            | Pins ISOMD, DTEN, GPI01 to GPI09, A0 to A3                                               | • | 2.7               |                          |            | V              |

| V <sub>IL(CFG)</sub>                            | Configuration Pin Digital Input Voltage Low                                                                                             | Pins ISOMD, DTEN, GPI01 to GPI09, A0 to A3                                               | • |                   |                          | 1.2        | V              |

| ILEAK(DIG)                                      | Digital Input Current                                                                                                                   | Pins CSB, SCK, SDI, ISOMD, DTEN, A0 to A3                                                | • |                   |                          | ±1         | μΑ             |

| V <sub>OL(SDO)</sub>                            | Digital Output Low                                                                                                                      | Pin SD0 Sinking 1mA                                                                      | • |                   |                          | 0.3        | V              |

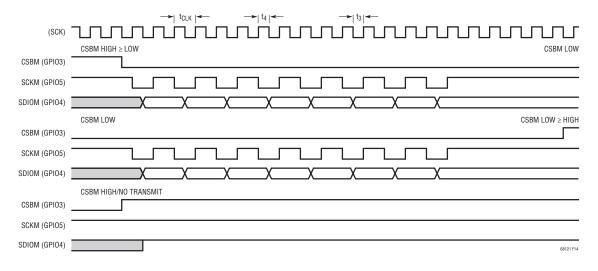

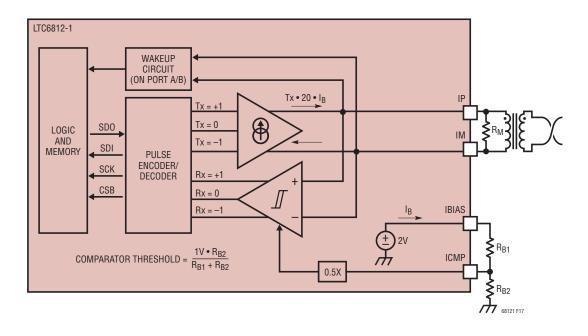

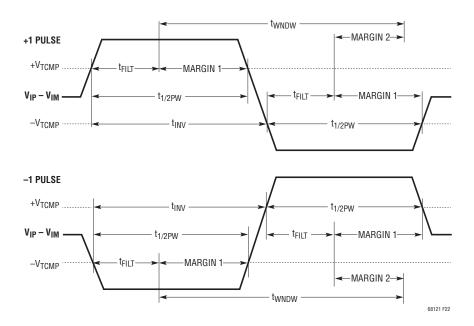

| isoSPIのDC                                       | 仕様(図17を参照)                                                                                                                              |                                                                                          |   |                   |                          |            |                |

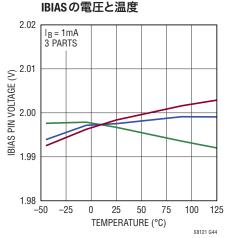

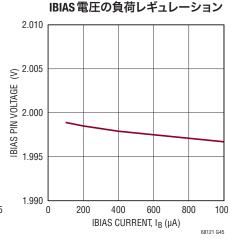

| V <sub>BIAS</sub>                               | Voltage on IBIAS Pin                                                                                                                    | READY/ACTIVE State<br>IDLE State                                                         | • | 1.9               | 2.0<br>0                 | 2.1        | V<br>V         |

| I <sub>B</sub>                                  | Isolated Interface Bias Current                                                                                                         | R <sub>BIAS</sub> = 2k to 20k                                                            | • | 0.1               |                          | 1.0        | mA             |

| A <sub>IB</sub>                                 | Isolated Interface Current Gain                                                                                                         | $V_A = \leq 1.6V \hspace{1cm} I_B = 1 mA \\ I_B = 0.1 mA$                                | • | 18<br>18          | 20<br>20                 | 22<br>24.5 | mA/mA<br>mA/mA |

| V <sub>A</sub>                                  | Transmitter Pulse Amplitude                                                                                                             | $V_A =  V_{IP} - V_{IM} $                                                                | • |                   |                          | 1.6        | V              |

| V <sub>ICMP</sub>                               | Threshold-Setting Voltage on ICMP Pin                                                                                                   | V <sub>TCMP</sub> = A <sub>TCMP</sub> • V <sub>ICMP</sub>                                | • | 0.2               |                          | 1.5        | V              |

| I <sub>LEAK(ICMP)</sub>                         | Input Leakage Current on ICMP Pin                                                                                                       | V <sub>ICMP</sub> = 0V to V <sub>REG</sub>                                               | • |                   |                          | ±1         | μА             |

| I <sub>LEAK(IP/IM)</sub>                        | Leakage Current on IP and IM Pins                                                                                                       | IDLE State, V <sub>IP</sub> or V <sub>IM</sub> , OV to V <sub>REG</sub>                  | • |                   |                          | ±1         | μА             |

| A <sub>TCMP</sub>                               | Receiver Comparator Threshold<br>Voltage Gain                                                                                           | $V_{CM} = V_{REG}/2$ to $V_{REG} - 0.2V$ , $V_{ICMP} = 0.2V$ to 1.5V                     | • | 0.4               | 0.5                      | 0.6        | V/V            |

| V <sub>CM</sub>                                 | Receiver Common Mode Bias                                                                                                               | IP/IM Not Driving                                                                        |   | (V <sub>REG</sub> | - V <sub>ICMP</sub> /3 - | 167mV)     | V              |

| R <sub>IN</sub>                                 | Receiver Input Resistance                                                                                                               | Single-Ended to IPA, IMA, IPB, IMB                                                       | • | 26                | 35                       | 45         | kΩ             |

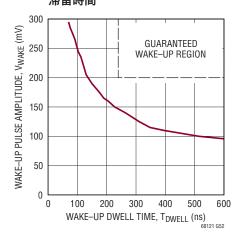

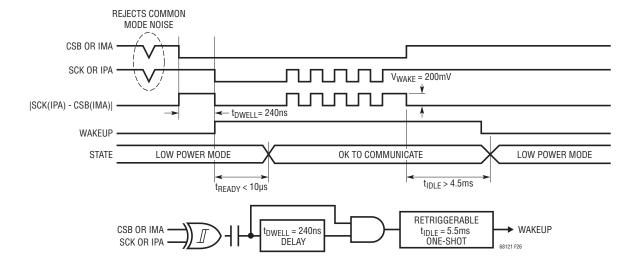

| isoSPIのアー                                       | イドル/ウェイクアップ仕様(図 26 を参照                                                                                                                  | )                                                                                        |   |                   |                          |            |                |

| V <sub>WAKE</sub>                               | Differential Wake-Up Voltage                                                                                                            | t <sub>DWELL</sub> = 240ns                                                               | • | 200               |                          |            | mV             |

| t <sub>DWELL</sub>                              | Dwell Time at V <sub>WAKE</sub> Before Wake Detection                                                                                   | V <sub>WAKE</sub> = 200mV                                                                | • | 240               |                          |            | ns             |

| t <sub>READY</sub>                              | Start-Up Time After Wake Detection                                                                                                      |                                                                                          | • |                   |                          | 10         | μs             |

| t <sub>IDLE</sub>                               | Idle Timeout Duration                                                                                                                   |                                                                                          | • | 4.3               | 5.5                      | 6.7        | ms             |

●は規定の全温度範囲での規格値を意味する。それ以外は  $T_A=25^\circ C$  での値。注記がない限り、テスト条件は  $V^+=49.5V$ 、 $V_{REG}=5.0V$ 。注記がない限り、ISOMD ピンは  $V^-$  ピンに接続する。

| SYMBOL                 | PARAMETER                              | CONDITIONS                                                      |   | MIN  | TYP | MAX  | UNITS |

|------------------------|----------------------------------------|-----------------------------------------------------------------|---|------|-----|------|-------|

| isoSPIのバ               | ルス・タイミング仕様(図22を参照)                     |                                                                 |   |      |     |      |       |

| t <sub>1/2PW(CS)</sub> | Chip-Select Half-Pulse Width           | Transmitter                                                     | • | 120  | 150 | 180  | ns    |

| t <sub>FILT(CS)</sub>  | Chip-Select Signal Filter              | Receiver                                                        | • | 70   | 90  | 110  | ns    |

| t <sub>INV(CS)</sub>   | Chip-Select Pulse Inversion Delay      | Transmitter                                                     | • | 120  | 155 | 190  | ns    |

| twndw(cs)              | Chip-Select Valid Pulse Window         | Receiver                                                        | • | 220  | 270 | 330  | ns    |

| t <sub>1/2PW(D)</sub>  | Data Half-Pulse Width                  | Transmitter                                                     | • | 40   | 50  | 60   | ns    |

| t <sub>FILT(D)</sub>   | Data Signal Filter                     | Receiver                                                        | • | 10   | 25  | 35   | ns    |

| t <sub>INV(D)</sub>    | Data Pulse Inversion Delay             | Transmitter                                                     | • | 40   | 55  | 65   | ns    |

| t <sub>WNDW(D)</sub>   | Data Valid Pulse Window                | Receiver                                                        | • | 70   | 90  | 110  | ns    |

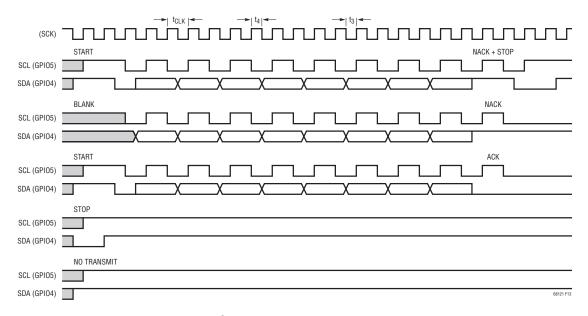

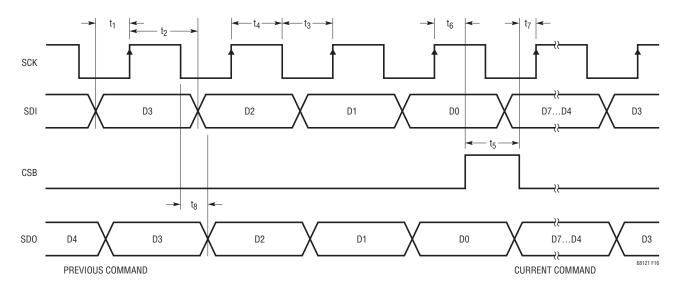

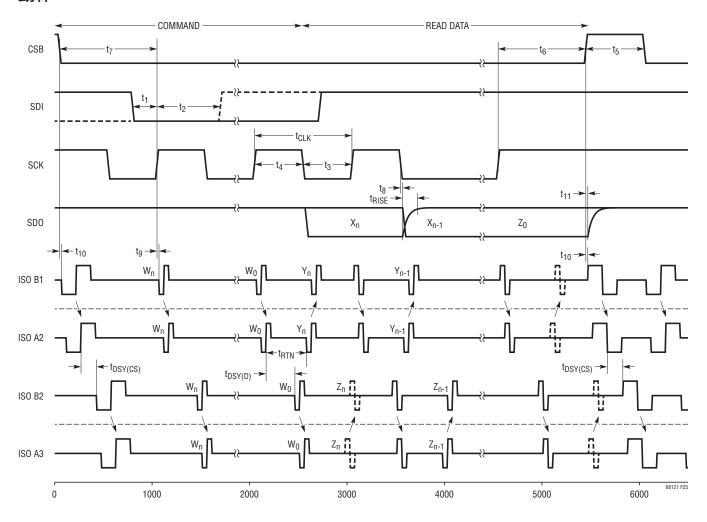

| SPIのタイ                 | ミング条件(図16および図25を参照)                    |                                                                 |   |      |     |      |       |

| t <sub>CLK</sub>       | SCK Period                             | (Note 4)                                                        | • | 1    |     |      | μs    |

| t <sub>1</sub>         | SDI Setup Time before SCK Rising Edge  |                                                                 | • | 25   |     |      | ns    |

| t <sub>2</sub>         | SDI Hold Time after SCK Rising Edge    |                                                                 | • | 25   |     |      | ns    |

| t <sub>3</sub>         | SCK Low                                | $t_{CLK} = t_3 + t_4 \ge 1 \mu s$                               | • | 200  |     |      | ns    |

| t <sub>4</sub>         | SCK High                               | $t_{CLK} = t_3 + t_4 \ge 1 \mu s$                               | • | 200  |     |      | ns    |

| t <sub>5</sub>         | CSB Rising Edge to CSB Falling Edge    |                                                                 | • | 0.65 |     |      | μs    |

| t <sub>6</sub>         | SCK Rising Edge to CSB Rising Edge     | (Note 4)                                                        | • | 0.8  |     |      | μs    |

| t <sub>7</sub>         | CSB Falling Edge to SCK Rising Edge    | (Note 4)                                                        | • | 1    |     |      | μs    |

| isoSPIのタ               | イミング仕様(図25を参照)                         |                                                                 |   |      |     |      |       |

| t <sub>8</sub>         | SCK Falling Edge to SDO Valid          | (Note 5)                                                        | • |      |     | 60   | ns    |

| t <sub>9</sub>         | SCK Rising Edge to Short ±1 Transmit   |                                                                 | • |      |     | 50   | ns    |

| t <sub>10</sub>        | CSB Transition to Long ±1 Transmit     |                                                                 | • |      |     | 60   | ns    |

| t <sub>11</sub>        | CSB Rising Edge to SDO Rising          | (Note 5)                                                        | • |      |     | 200  | ns    |

| t <sub>RTN</sub>       | Data Return Delay                      |                                                                 | • | 325  | 375 | 425  | ns    |

| t <sub>DSY(CS)</sub>   | Chip-Select Daisy-Chain Delay          |                                                                 | • |      | 120 | 180  | ns    |

| t <sub>DSY(D)</sub>    | Data Daisy-Chain Delay                 |                                                                 | • | 200  | 250 | 300  | ns    |

| t <sub>LAG</sub>       | Data Daisy-Chain Lag (vs Chip-Select)  | $= [t_{DSY(D)} + t_{1/2PW(D)}] - [t_{DSY(CS)} + t_{1/2PW(CS)}]$ | • | 0    | 35  | 70   | ns    |

| t <sub>5(GOV)</sub>    | Chip-Select High-to-Low Pulse Governor |                                                                 | • | 0.6  |     | 0.82 | μs    |

| t <sub>6(GOV)</sub>    | Data to Chip-Select Pulse Governor     |                                                                 | • | 0.8  |     | 1.05 | μs    |

| t <sub>BLOCK</sub>     | isoSPI Port Reversal Blocking Window   |                                                                 | • | 2    |     | 10   | μs    |

Note 1: 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。また、長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える恐れがある。

Note 2:ADCの仕様は、全測定誤差の仕様によって確認されている。

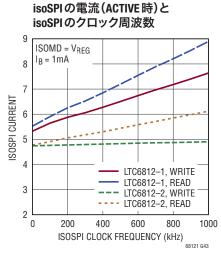

Note 3: ACTIVE ステートの電流はDCの測定値から計算される。データ1が50%、データ0が50%の連続した1MHzの通信がisoSPIポートに存在する場合、ACTIVE ステートの電流は、 $V_{REG}$ に流れ込む平均電源電流の増加分になる。クロック・レートが遅くなるほど、電源電流は減少する。詳細については、アプリケーション情報のセクションを参照。

Note 4: これらのタイミング仕様はケーブルの遅延によって異なり、各方向に50nsの遅延を許容する。50nsは10mのCAT5ケーブル(伝播速度が光速の66%)に対応する。これより長いケーブルを使用する場合は、遅延が大きくなる分、仕様を低減する必要がある。

Note 5: これらの仕様には、SDOの立上がり時間と立下がり時間は含まれない。立下がり時間 (内部ブルダウン・トランジスタのため標準で5ns) は問題ではないが、立上がりエッジの遷移時間t<sub>RISE</sub> はSDO ピンでのブルアップ抵抗と負荷容量によって異なる。SDO がMCUのセットアップ時間要件を満たすように、時定数を選択する必要がある。

Rev. 0

8

詳細:www.analog.com

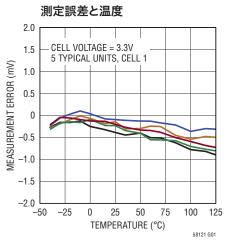

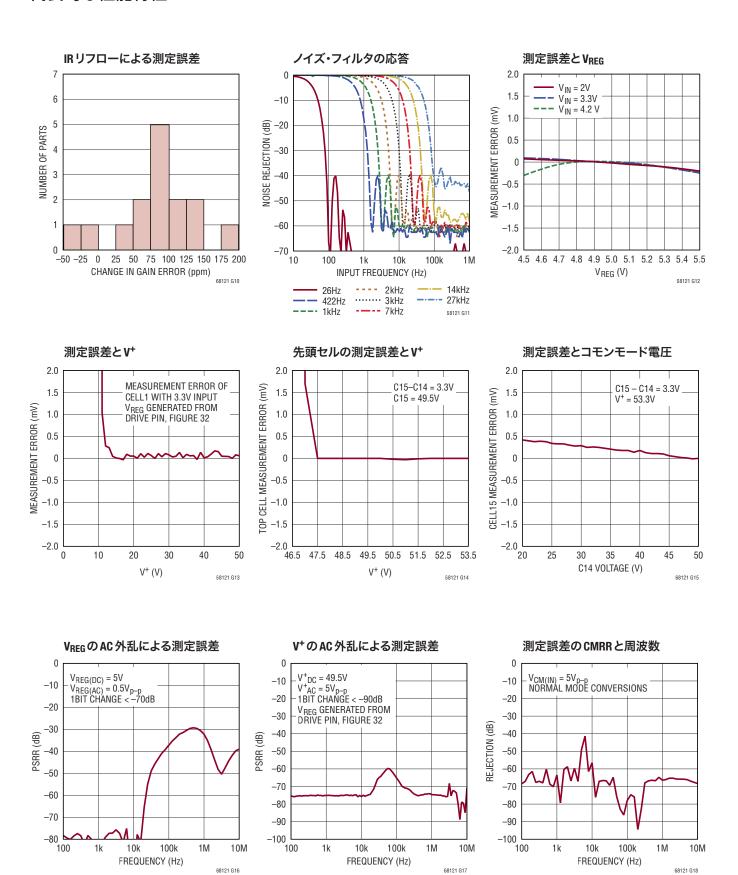

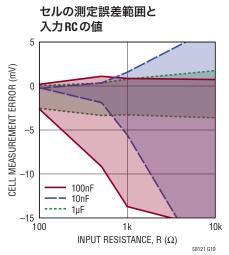

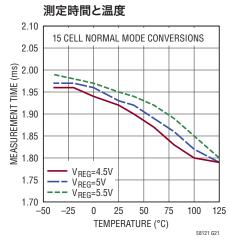

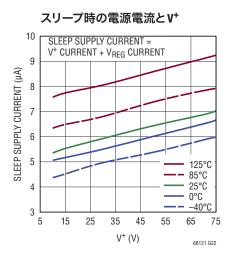

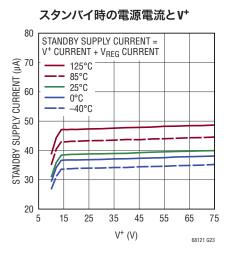

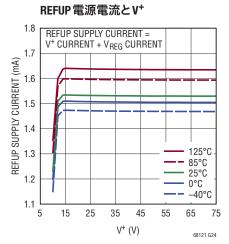

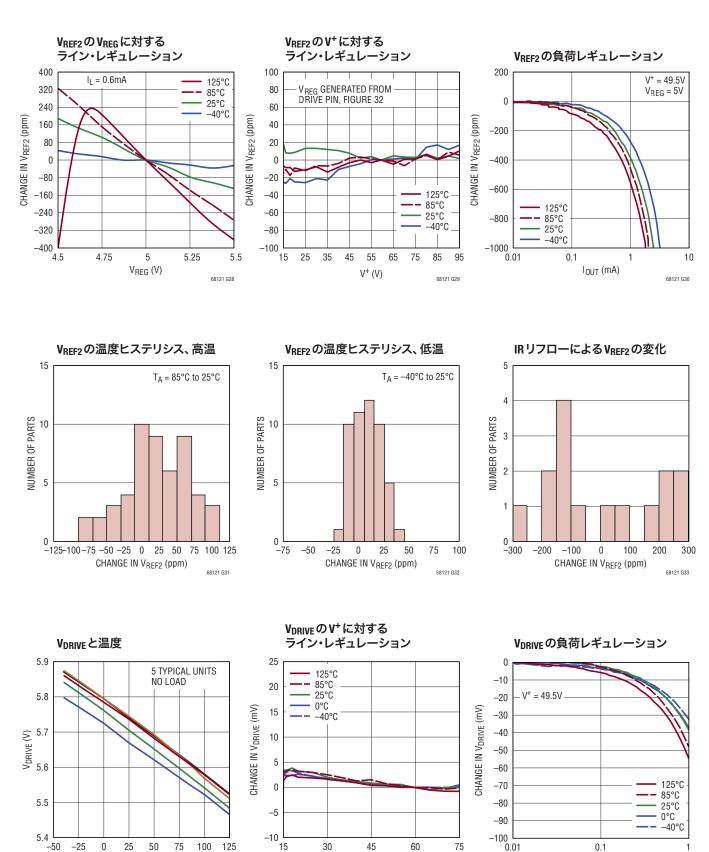

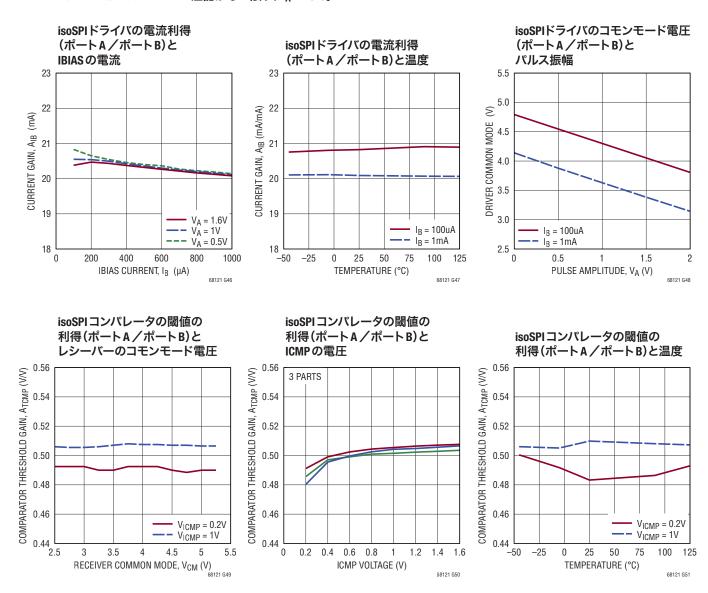

# 代表的な性能特性

注記がない限り、T<sub>A</sub> = 25°C。

68121 G02

測定誤差と入力電圧 (高速モード) 10

測定ノイズと入力電圧 (高速モード)

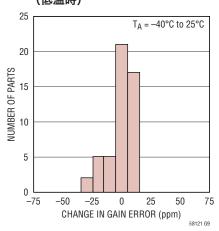

測定ゲイン誤差の

測定ゲイン誤差のヒステリシス (低温時)

Rev. 0

Rev. 0

10

Rev. 0

11

$V^{+}(V)$

68121 G35

Rev. 0

68121 G36

I<sub>OUT</sub> (mA)

12 詳細:www.analog.com

68121 G34

TEMPERATURE (°C)

VREF1 および VREF2 の起動

VREF1: CL = 1μF VREF2: CL = 1μF, RL = 5kΩ VREF1

VREF1 1V/DIV VREF2 VREF2

1V/DIV CS 5V/DIV CS 500μs/DIV 66121 640

Rev. 0

13

標準的なウェイクアップ・パルスの 振幅(ポートA/ポートB)と 滞留時間

Rev. 0

14

# ピン機能

CO~C15:セルの入力。

**S1~S15**: バランス入力/バランス出力。セルを放電するため、15個の内部 N チャンネル MOSFET が S(n) と C(n-1) の間に接続されています。

**V<sup>+</sup>:**正電源ピン。

**V**:負電源ピン。デバイスの外部で、各 V⁻ピンを互いに短絡 させる必要があります。

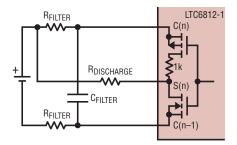

VREF2: 複数の10kサーミスタを駆動するための2番目のバッファ付きリファレンス電圧。外付けの1μFコンデンサを使用してバイパスします。

VREF1: ADCのリファレンス電圧。外付けの1μFコンデンサを使用してバイパスします。DC負荷を接続することはできません。

**GPIO[1:9]:**汎用 I/O。 デジタル入力またはデジタル出力として使用するか、 $V^-$ ~5Vの測定範囲でアナログ入力として使用できます。 GPIO[3:5]は $I^2$ CポートまたはSPIポートとして使用できます。

DTEN: 放電タイマーのイネーブル・ピン。 放電タイマーをイネーブルするには、このピンを VREG に接続します。

**DRIVE:** NPNのベースをこのピンに接続します。コレクタは $V^+$ に接続し、エミッタは $V_{REG}$ に接続します。

**VREG**:5Vレギュレータ入力。外付けの1µFコンデンサを使用してバイパスします。

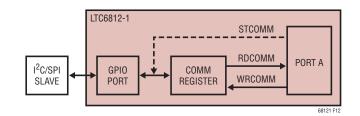

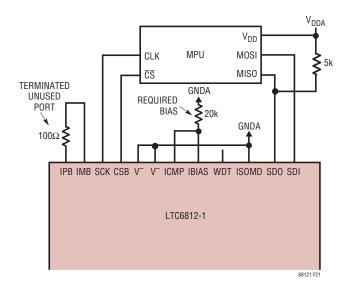

**ISOMD**:シリアル・インターフェース・モード。ISOMDを $V_{REG}$ に接続すると、LTC6812-1のピン53、54、61、および62は絶縁型の2線式インターフェース(isoSPI)モードに合わせて構成されます。ISOMDを $V^-$ に接続すると、LTC6812-1は4線SPIモードに合わせて構成されます。

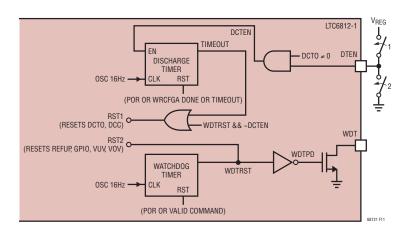

WDT:ウォッチドッグ・タイマーの出力ピン。これはオープン・ドレインNMOSのデジタル出力です。このピンは未接続のままにするか、1Mの抵抗を介してVREGに接続することができます。LTC6812-1が2秒以内に有効なコマンドを受信しない場合は、ウォッチドッグ・タイマー回路がLTC6812-1をリセットし、WDTピンが高インピーダンスになります。

#### シリアル・ポート・ピン

|                 | ISOMD = V <sub>REG</sub> | ISOMD = V |

|-----------------|--------------------------|-----------|

| ポートB            | IPB                      | IPB       |

| (ピン57、58、63、64) | IMB                      | IMB       |

|                 | ICMP                     | ICMP      |

|                 | IBIAS                    | IBIAS     |

| ポートA            | (NC)                     | SD0       |

| (ピン53、54、61、62) | (NC)                     | SDI       |

|                 | IPA                      | SCK       |

|                 | IMA                      | CSB       |

**CSB、SCK、SDI、SDO**:4線式シリアル・ペリフェラル・インターフェース(SPI)。アクティブ・ローのチップ選択(CSB)、シリアル・クロック(SCK)、およびシリアル・データ入力(SDI)はデジタル入力です。シリアル・データ出力(SDO)はオープン・ドレインNMOS出力ピンです。SDOには5kのプルアップ抵抗が必要です。

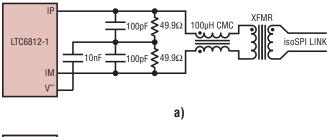

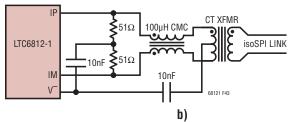

IPA、IMA: 絶縁型の2線式シリアル・インターフェース・ポートA。IPA (プラス)とIMA (マイナス)は、差動入力/出力対です。

**IPB、IMB**: 絶縁型の2線式シリアル・インターフェース・ポートB。IPB (プラス)とIMB (マイナス)は、差動入力/出力対です。

IBIAS: 絶縁型インターフェースの電流バイアス。IBIASをVに抵抗分圧器を介して接続し、インターフェースの出力電流レベルを設定します。 isoSPI インターフェースがイネーブルされている場合、IBIAS ピンの電圧は2Vです。 IPA/IMA または IPB/IMB の出力駆動電流は、IBIAS ピンから流れ出る電流  $(I_B)$ の 20 倍に設定されます。

ICMP: 絶縁型インターフェースのコンパレータ電圧閾値設定。このピンをIBIASとV<sup>-</sup>の間の抵抗分圧器に接続し、isoSPIレシーバーのコンパレータの電圧閾値を設定します。コンパレータの閾値はICMPピンの電圧の半分に設定されます。

**露出パッド:**V<sup>-</sup>。露出パッドはPCBにハンダ付けする必要があります。

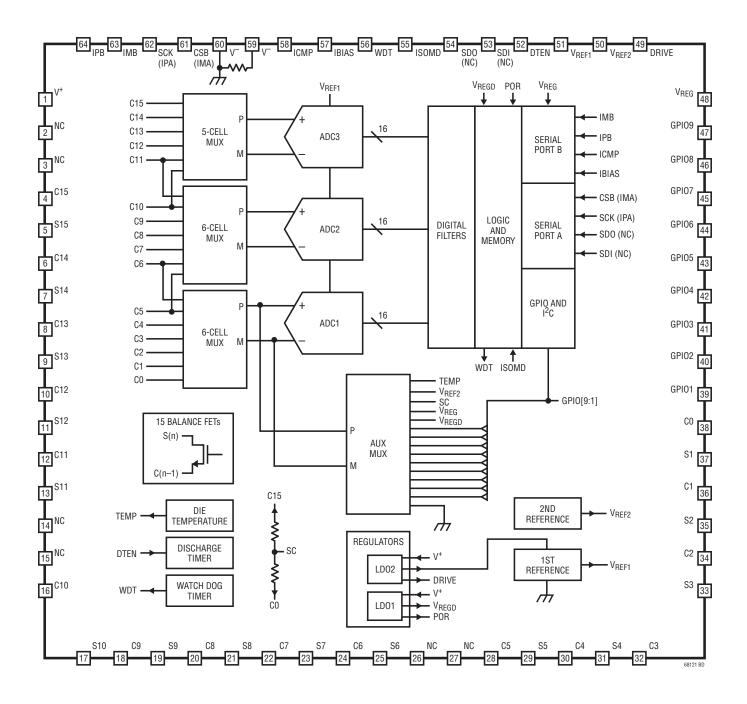

# ブロック図

# LTC6811-1からの改善点

LTC6812-1 は、LTC6811-1のデザインを発展させたものです。LTC6812-1での機能の変更点と追加点を次の表にまとめています。

| LTC6812-1 の追加機能                                                            | 利点                                                     | 関連のデータシート・セクション                                             |

|----------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------------|

| LTC6812-1 は同時に動作するADCを3つ内蔵しているのに対して、LTC6811-1では2つ                          | 各変換サイクル時に3つのセルを測定できる                                   | ADCの動作                                                      |

| 3つのADCデジタル・フィルタの他に第4のフィルタがあり、冗長性を確保するために使用される                              | 全てのデジタル・フィルタで障害が発生しないことを確認する                           | 表 10 の説明と PS[1:0] ビットについては、<br><b>デジタル冗長化機能を使用した A/D 変換</b> |

| ADOLコマンドを使用して、ADC1とADC2によりセル6を同時に測定し、ADC2とADC3によりセル11を同時に測定する              | ADC2とADC1の精度が同程度であることを確認し、またADC3とADC2の精度が同程度であることを確認する | セル電圧測定の重複(ADOLコマンド)                                         |

| 放電タイマーの動作中にモニタ機能を有効化できるセルの電圧がプログラム可能な低電圧閾値に達すると、セル・バランス調整機能を自動的に終了できる      | セル・バランス調整機能の向上                                         | 放電タイマー・モニタ                                                  |

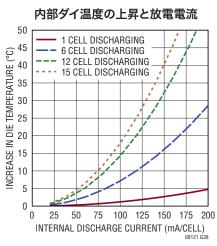

| 内部の放電MOSFETは200mAのバランス調整電流を供給できる(ダイ温度が95°Cを超えた場合は80mA)。バランス調整電流はセルの電圧とは無関係 | セル・バランス調整の高速化、特にセルの電圧 が低い場合                            | 内部 MOSFET によるセル・バランス調整                                      |

| COピンの電圧範囲をOV~1Vにすることが可能で、全測定誤差(TME)にも影響しない                                 | COをV「に直接接続する必要がない                                      | 電気的特性での入力範囲                                                 |

| MUTEコマンドとUNMUTEコマンドにより、ホストがレジスタの値を上書きせずに放電ピン(Sピン)をオン/オフすることが可能             | Sピンをオフしてからセルの測定までのタイミングの制御範囲が拡大                        | Sピンのミュート                                                    |

| 補助測定に断線診断機能を組み込む                                                           | 障害検出能力の向上                                              | 補助断線チェック(AXOWコマンド)                                          |

| GPIOピンを4つ追加して合計9ピンとなる                                                      | 測定可能な温度センサーまたはその他のセン<br>サーの数が増加                        | 補助(GPIO)測定(ADAX コマンド)および補助断線チェック(AXOW コマンド)                 |

| LTC6812-1のデイジーチェーンは双方向で動作できる(両方のポートがマスタにもスレーブにもなる)                         | 冗長な通信経路                                                | 可逆的なisoSPI                                                  |

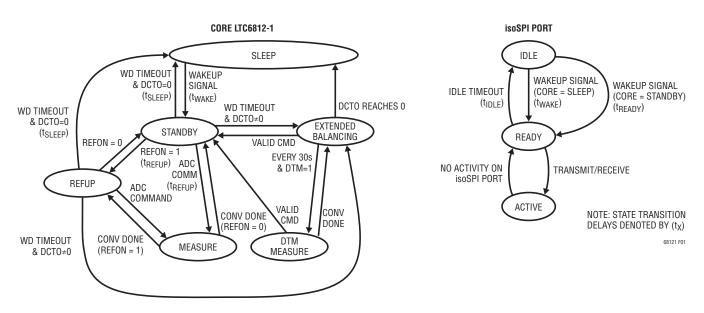

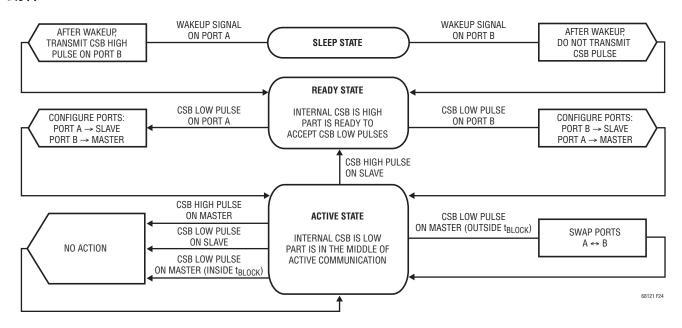

#### ステート図

LTC6812-1の動作は、コア回路とisoSPI回路の2つのセクションに分かれています。両方のセクションは、独立した一連の動作ステートと、タイムアウトによるシャットダウンを備えています。

#### LTC6812-1 のコアのステートの説明

#### SLEEP ステート

リファレンスとADCの電力が遮断されます。ウォッチドッグ・タイマー(ウォッチドッグ・タイマーと放電タイマーを参照)はタイムアウトしています。また、放電タイマーも無効化されているかタイムアウトしています。電源電流は最小レベルまで減少します。isoSPIポートは、IDLEステートになります。DRIVEピンは0Vです。

WAKEUP信号を受信すると(シリアル・インターフェースのウェイクアップを参照)、LTC6812-1はSTANDBYステートに入ります。

#### STANDBY ステート

リファレンスとADCはオフになります。ウィッチドッグ・タイマーまたは放電タイマー (あるいはその両方)は動作中です。DRIVEピンは外付けトランジスタを介して $V_{REG}$ ピンに5Vの電源を供給します(あるいは、 $V_{REG}$ ピンには外部電源から電力を供給してもかまいません)。

有効なADCコマンドを受け取るか、構成レジスタ・グループAのREFONビットが1に設定されると、デバイスはリファレンスを起動できる状態になるまでt<sub>REFUP</sub>の間停止し、その

後REFUPステートまたはMEASUREステートに移行します。 それ以外で、tsleepの間(ウォッチドッグ・タイマーと放電タイマーの両方が期限切れになるまで)有効なコマンドを受け取らなかった場合、LTC6812-1はSLEEPステートに戻ります。放電タイマーが無効化されている場合は、ウォッチドッグ・タイマーのみが関係します。

#### REFUPステート

このステートに達するには、構成レジスタ・グループAの REFONビットを1に設定する必要があります(WRCFGA コマンドを使用。表36を参照)。ADCはオフになります。 LTC6812-1がSTANDBYステートから開始するよりも早く AD変換を開始できるようにするために、リファレンスが起動 します。

有効なADCコマンドを受け取るとデバイスはMEASUREステートになり、変換を開始します。それ以外の場合、手動で (WRCFGAコマンドを使用)もしくは(ウォッチドッグ・タイマーが期限切れになったときに)自動的にREFONビットに0が設定されると、LTC6812-1はSTANDBYステートに戻ります(その後、ウォッチドッグ・タイマーと放電タイマーの両方が期限切れになると、LTC6812-1は直接SLEEPステートに移行します)。

#### MEASUREステート

このステートでは、LTC6812-1はA/D変換を実行します。リファレンスとADCの電源が投入されます。

LTC6812-1は、A/D変換が完了すると、REFONビットに応じてREFUPステートまたはSTANDBYステートのいずれかに

図1. LTC6812-1の動作ステート図

Rev. 0

18

移行します。REFONを1に設定してREFUPステートを活用することによって、追加のA/D変換をより迅速に開始できます。

注記:ADCコマンド以外のコマンドでは、コアのステートが移行しません。A/D変換または診断コマンドのみが、コアをMEASUREステートに移行します。

### isoSPIステートの説明

注記:LTC6812-1は、デイジーチェーン通信用に2つisoSPIポート(AおよびB)を備えています。

#### IDLEステート

isoSPIポートの電力が遮断されます。

isoSPIのポートAまたはポートBがWAKEUP信号を受信すると(シリアル・インターフェースのウェイクアップを参照)、isoSPIはREADYステートに移行します。コアがSTANDBYステートにある場合、この移行は素早く( $t_{READY}$ 以下で)行われます。コアがSLEEPステートにある場合、isoSPIは、WAKEUP信号を受信してから、 $t_{WAKE}$ 以内にREADYステートに移行します。

### **READY ステート**

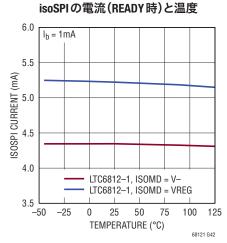

isoSPIポートは通信可能な状態にあります。このステートでのシリアル・インターフェース電流は、ISOMDピンの状態と $R_{BIAS} = R_{B1} + R_{B2}$ (IBIASピンに接続された外付け抵抗)によって決まります。

ポートAまたはポートBで動作がない(つまり、WAKEUP信号がない)時間がt<sub>IDLE</sub>より長くなると、LTC6812-1はIDLEステートに移行します。シリアル・インターフェースがデータを送信または受信すると、LTC6812-1はACTIVEステートに移行します。

#### ACTIVEステート

LTC6812-1は、一方または両方のisoSPIポートを使用してデータの送受信を行います。シリアル・インターフェースは、この状態で最も多くの電力を消費します。isoSPIパルスの密度が高くなるので、電源電流はクロック周波数の増加に伴って増加します。

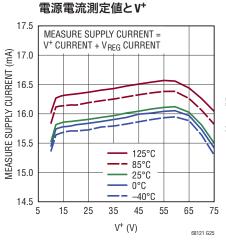

## 消費電力

LTC6812-1の電力は、次の2つのピン( $V^+$ および $V_{REG}$ )から 供給されます。 $V^+$ 入力は、先頭セルの電圧より0.3V低い電圧以上の電圧を必要とし、コア回路の高電圧素子に電力を供給します。 $V_{REG}$ 入力は5Vを必要とし、残りのコア回路とisoSPI回路に電力を供給します。 $V_{REG}$ 入力には、安定化されたDRIVE出力ピンによって駆動される外付けトランジスタを介して電力を供給できます。あるいは、 $V_{REG}$ ピンには外部電源から電力を供給してもかまいません。

消費電力は動作ステートによって異なります。各ステートでの電源ピンの電流を概算する式を表1および表2に示します。 $V^+$ ピンの電流は、コアのステートにのみ依存します。ただし、 $V_{REG}$ ピンの電流は、コアのステートと isoSPIのステートの両方に依存するため、2つの成分に分けることができます。 isoSPIインターフェースに流れる電流は、 $V_{REG}$ ピンからの電流だけです。

$I_{REG} = I_{REG(CORE)} + I_{REG(isoSPI)}$

SLEEPステートでは、外部電源から電力を供給した場合、 $V_{REG}$ ピンが約3.1 $\mu$ Aを吸い込みます。そうでない場合は、 $V^+$ ピンが必要な電流を供給します。

表1. コアの電源電流

| ステ      | ステート           |       | I <sub>REG(CORE)</sub> |

|---------|----------------|-------|------------------------|

| SLEEP   | $V_{REG} = 0V$ | 6.1µA | 0μΑ                    |

| SLEEP   | $V_{REG} = 5V$ | 3µА   | 3.1µA                  |

| STAN    | STANDBY        |       | 35μΑ                   |

| REFUP   |                | 550µA | 900μΑ                  |

| MEASURE |                | 950μΑ | 15mA                   |

表2 isoSPIの電源電流の式

| <b>久と, 1900 1 77 电心 电心 フン</b> ( |                  |                                                                                                                                                                                                                            |  |  |  |  |  |

|---------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| isoSPI<br>ステート                  | ISOMDの<br>接続     | I <sub>REG(isoSPI)</sub>                                                                                                                                                                                                   |  |  |  |  |  |

| IDLE                            | N/A              | 0mA                                                                                                                                                                                                                        |  |  |  |  |  |

| READY V <sub>REG</sub>          |                  | 2.2mA + 3 • I <sub>B</sub>                                                                                                                                                                                                 |  |  |  |  |  |

| KEADY                           | V-               | 1.5mA + 3 • I <sub>B</sub>                                                                                                                                                                                                 |  |  |  |  |  |

| ACTIVE                          | V <sub>REG</sub> | Write: $2.5\text{mA} + \left(3 + 20 \cdot \frac{100\text{ns}}{t_{\text{CLK}}}\right) \cdot I_{\text{B}}$ Read: $2.5\text{mA} + \left(3 + 20 \cdot \frac{100\text{ns} \cdot 1.5}{t_{\text{CLK}}}\right) \cdot I_{\text{B}}$ |  |  |  |  |  |

|                                 | V                | $1.8\text{mA} + \left(3 + 20 \bullet \frac{100\text{ns}}{t_{\text{CLK}}}\right) \bullet I_{\text{B}}$                                                                                                                      |  |  |  |  |  |

#### ADCの動作

LTC6812-1の内部には3つのADCがあります。これら3つのADCは、15セルを測定するときに同時に動作します。汎用入力の測定に使用されるADCは1つだけです。以下の説明では、実行される動作に応じて、ADCという用語を使用して1つまたは全部のADCを表わします。以下の説明では、例えばタイミング図で3つの回路を区別する必要があるときは、ADC1、ADC2、およびADC3と表記します。

#### ADC モード

構成レジスタ・グループAのADCOPTビット(CFGAR0[0])と変換コマンドのモード選択ビットMD[1:0]を組み合わせると、ADCの8つの動作モードが得られます。これらのモードは、異なるオーバーサンプリング率(OSR)に対応しています。これらのモードの精度とタイミングを表3にまとめています。それぞれのモードにおいて、ADCは最初に入力を測定し、次に各チャンネルのキャリブレーションを行います。モードの名前は、ADC測定の-3dB帯域幅に基づいています。

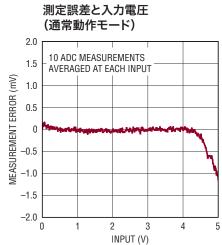

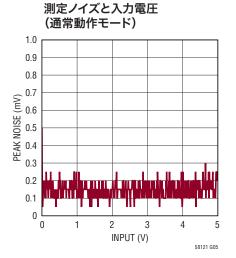

**7kHzモード(通常動作モード)**:このモードでは、ADCの分解能が高く、TME(全測定誤差)が低く抑えられています。これは、速度と精度のバランスが最適になるように組み合わされていることから、通常動作モードと見なされます。

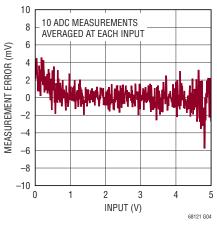

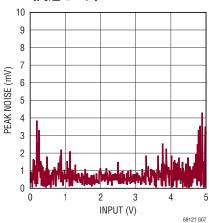

27kHzモード(高速モード):このモードでは、ADCのスループットが最大になりますが、TME (全測定誤差)はある程度増加します。そのためこのモードは、高速モードとも呼ばれます。速度の向上は、オーバーサンプリング率を小さくすることによって実現されます。その結果、ノイズと平均測定誤差が増加します。

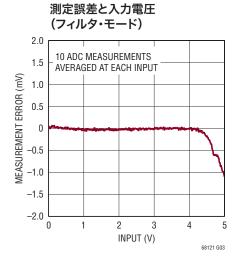

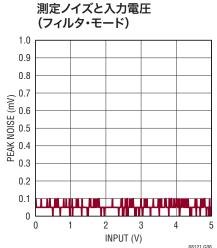

**26Hzモード(フィルタ・モード)**:このモードでは、OSRを増やすことによって、ADCのデジタル・フィルタの-3dB周波数が26Hzに減少します。このモードは、-3dB周波数が低いため、フィルタ・モードとも呼ばれます。精度は7kHzモード(通常動作モード)と同様ですが、ノイズが少なくなります。

**14kHz、3kHz、2kHz、1kHz、および422Hzモード**: 14kHz、3kHz、2kHz、1kHz、および422Hzモードは、ADCデジタル・フィルタの-3dB 周波数をそれぞれ13.5kHz、3.4kHz、1.7kHz、845Hz、および422Hzに設定する追加オプションを提供します。14kHzモードの精度は、27kHzモード(高速モード)と同様です。3kHz、2kHz、1kHz、および422Hzモードの精度は、7kHzモード(通常動作モード)と同様です。

これらのモードにおけるフィルタの帯域幅と変換時間を表3 および表5に示します。コアがSTANDBYステートにある場合、A/D変換を開始する前にリファレンスを起動するために、trefupの追加時間が必要です。構成レジスタ・グループAのREFONビットを1に設定した場合、A/D変換とA/D変換の間にリファレンスを起動したままにすることができます。したがって、遅延trefupの後、コアはREFUPステートになっています。その後のADCコマンドでは、A/D変換を開始する前にtrefupの遅延は発生しません。

表3, ADCフィルタの帯域幅と精度

| モード                     | -3dB<br>フィルタの<br>帯域幅 | -40dB<br>フィルタの<br>帯域幅 | 3.3V、<br>25°Cでの<br>TME仕様 | 3.3V、-40°C、<br>125°Cでの<br>TME 仕様 |

|-------------------------|----------------------|-----------------------|--------------------------|----------------------------------|

| 27kHz<br>(Fast Mode)    | 27kHz                | 84kHz                 | ±6mV                     | ±6mV                             |

| 14kHz                   | 13.5kHz              | 42kHz                 | ±6mV                     | ±6mV                             |

| 7kHz<br>(Normal Mode)   | 6.8kHz               | 21kHz                 | ±2.2mV                   | ±3.3mV                           |

| 3kHz                    | 3.4kHz               | 10.5kHz               | ±2.2mV                   | ±3.3mV                           |

| 2kHz                    | 1.7kHz               | 5.3kHz                | ±2.2mV                   | ±3.3mV                           |

| 1kHz                    | 845Hz                | 2.6kHz                | ±2.2mV                   | ±3.3mV                           |

| 422Hz                   | 422Hz                | 1.3kHz                | ±2.2mV                   | ±3.3mV                           |

| 26Hz<br>(Filtered Mode) | 26Hz                 | 82Hz                  | ±2.2mV                   | ±3.3mV                           |

注記:TME は全測定誤差。

#### ADCの範囲と分解能

C入力とGPIO入力の範囲および分解能は同じです。LTC6812-1内部のADCの範囲は、およそ $-0.82V\sim+5.73V$ です。負の読出し値は0Vに丸められます。データのフォーマットは16ビットの符号なし整数で、LSBは $100\mu V$ です。したがって、0x80E8(10進数で33,000)は3.3Vの測定値を示します。

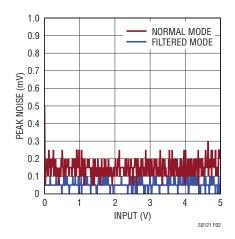

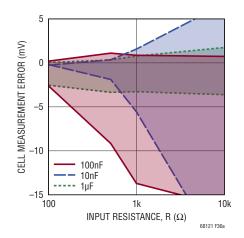

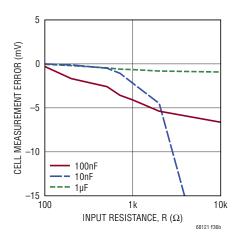

デルタシグマ型ADCでは、特に高速モードなどでオーバーサンプリング率(OSR)が低い場合に、入力電圧に応じて量子化ノイズが発生します。ADCモードの一部では、入力電圧がADC範囲の上限と下限に近づくにつれて量子化ノイズが増加します。例として、通常動作モードとフィルタ・モードでの全測定ノイズと入力電圧を図2に示します。

ADCの規定範囲は0V~5Vです。表4では、ADCの精度範囲は、0.5V~4.5Vの間で任意に定義されます。これは、低OSRモードでも量子化ノイズが比較的一定になる範囲です(図2を参照)。ADCの8つの動作モード全てについて、この範囲内の全ノイズを表4にまとめます。ノイズのない分解能も示されています。例えば、通常動作モードでのノイズのない14ビットの分解能とは、DC入力では上位14ビットにはノイズがないが、15番目と16番目の最下位ビット(LSB)にはフリッカ・ノイズがあることを意味しています。

図2. 測定ノイズと入力電圧

#### ADCの範囲と電圧リファレンスの値

標準的なADCの範囲は、電圧リファレンスを正確に2倍した値であり、ADCの測定誤差は電圧リファレンスの誤差に正比例します。LTC6812-1のADCは、標準的なものではあ

りません。 $V_{REFI}$ の絶対値は、ADCのゲイン誤差を補正するために増加または減少の調整が行われます。したがって、ADCの全測定誤差 (TME)の規格値は、 $V_{REFI}$ の規格値よりも優れています。例えば、7kHzモード(通常動作モード)で3.300Vを測定する場合、全測定誤差の25°Cでの規格値は±2.2mVですが、 $V_{REFI}$ の25°Cでの規格値は3.150V±150mVです。

## セル電圧の測定(ADCVコマンド)

ADCVコマンドは、ピンCOからC15までのバッテリ・セル入力の測定を開始します。このコマンドには、測定対象のチャンネル数とADCモードを選択するためのオプションが複数あります。ADCVコマンドのフォーマットについては、コマンドのセクションを参照してください。

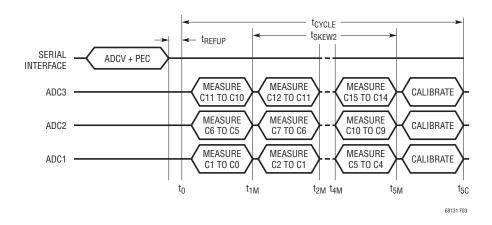

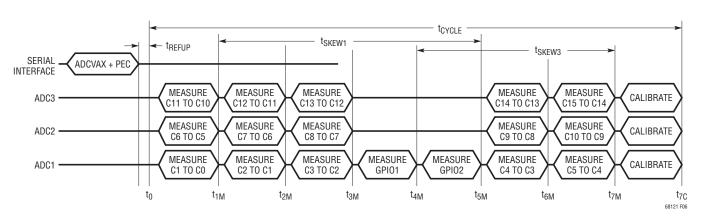

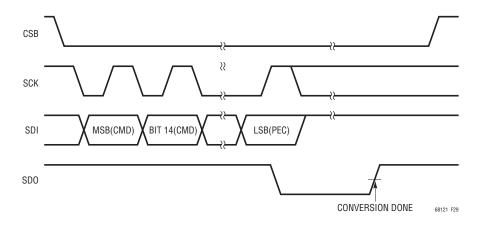

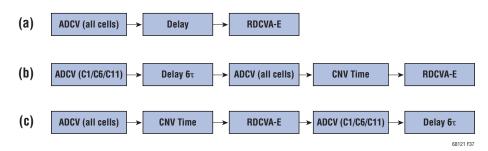

全15セルを測定するADCVコマンドのタイミングを図3に示します。全15セルを測定するADCVコマンドを受け取ると、ADC1は下部の5セルを順次測定します。ADC2は中間の5セルを測定し、ADC3は上部の5セルを測定します。セル測定が完了すると、各チャンネルは補正され、オフセット誤差が除去されます。

全15セルを測定するADCVコマンドの変換時間を表5に示します。合計変換時間は、キャリブレーション・ステップの終了を示すt<sub>5C</sub>により与えられます。

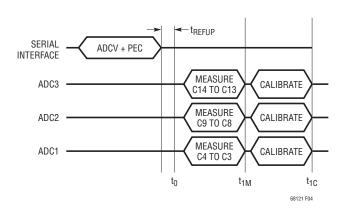

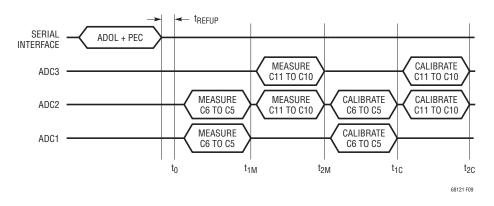

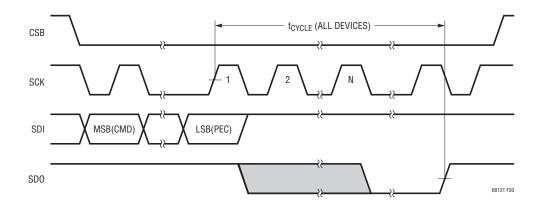

3セルだけを測定するADCVコマンドのタイミングを図4に示します。

表4. ADCの範囲と分解能

| モード             | 全範囲 <sup>1</sup> | 規定範囲     | 精度範囲 <sup>2</sup> | LSB    | フォーマット           | 最大ノイズ                   | ノイズのない<br>分解能 <sup>3</sup> |

|-----------------|------------------|----------|-------------------|--------|------------------|-------------------------|----------------------------|

| 27kHz (Fast)    |                  |          |                   |        |                  | $\pm 4 mV_{P-P}$        | 10 Bits                    |

| 14kHz           |                  |          |                   |        |                  | $\pm 1 \text{mV}_{P-P}$ | 12 Bits                    |

| 7kHz (Normal)   |                  |          |                   |        |                  | ±250 μV <sub>P-P</sub>  | 14 Bits                    |

| 3kHz            | -0.8192V to      | OV to 5V | 0.5V to 4.5V      | 100V   | Ungigned 16 Dite | ±150 μV <sub>P-P</sub>  | 14 Bits                    |

| 2kHz            | 5.7344V          | 00 10 50 | 0.57 (0 4.57      | 100 μV | Unsigned 16 Bits | ±100 μV <sub>P-P</sub>  | 15 Bits                    |

| 1kHz            |                  |          |                   |        |                  | ±100 μV <sub>P-P</sub>  | 15 Bits                    |

| 422Hz           |                  |          |                   |        |                  | ±100 μV <sub>P-P</sub>  | 15 Bits                    |

| 26Hz (Filtered) |                  |          |                   |        |                  | ±50 μV <sub>P-P</sub>   | 16 Bits                    |

<sup>1.</sup>負の読出し値はOVに丸められます。

<sup>2.</sup> 精度範囲は、ノイズが最大ノイズより小さくなる範囲です。

<sup>3.</sup>ノイズのない分解能は、精度範囲内のノイズ・レベルの測定値です。

図3.全15セルを測定するADCVコマンドのタイミング

表5. 全15セルを様々なモードで測定するADCVコマンドの変換時間と同期時間

|       |                |                 |                 | 同期時間(μs)        |                 |                 |                    |

|-------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|--------------------|

| モード   | t <sub>0</sub> | t <sub>1M</sub> | t <sub>2M</sub> | t <sub>4M</sub> | t <sub>5M</sub> | t <sub>5C</sub> | t <sub>SKEW2</sub> |

| 27kHz | 0              | 58              | 104             | 198             | 244             | 937             | 187                |

| 14kHz | 0              | 87              | 163             | 314             | 390             | 1,083           | 303                |

| 7kHz  | 0              | 145             | 279             | 547             | 681             | 1,956           | 536                |

| 3kHz  | 0              | 261             | 512             | 1,012           | 1,263           | 2,537           | 1,001              |

| 2kHz  | 0              | 494             | 977             | 1,943           | 2,426           | 3,701           | 1,932              |

| 1kHz  | 0              | 960             | 1,908           | 3,805           | 4,753           | 6,028           | 3,794              |

| 422Hz | 0              | 1,890           | 3,770           | 7,529           | 9,408           | 10,683          | 7,518              |

| 26Hz  | 0              | 29,818          | 59,624          | 119,238         | 149,044         | 167,774         | 119,227            |

図4.3セルを測定するADCVコマンドのタイミング

Rev. 0

22 詳細:www.analog.com

3セルだけを測定するADCVコマンドの変換時間を表6に示します。t<sub>IC</sub>は、このコマンドの合計変換時間を表します。

表 6.3つのセルを様々なモードで測定する ADCVコマンドの変換時間

|       | 変換時間(μs)       |                 |                 |  |  |  |  |

|-------|----------------|-----------------|-----------------|--|--|--|--|

| モード   | t <sub>0</sub> | t <sub>1M</sub> | t <sub>1C</sub> |  |  |  |  |

| 27kHz | 0              | 58              | 203             |  |  |  |  |

| 14kHz | 0              | 87              | 232             |  |  |  |  |

| 7kHz  | 0              | 145             | 407             |  |  |  |  |

| 3kHz  | 0              | 261             | 523             |  |  |  |  |

| 2kHz  | 0              | 494             | 756             |  |  |  |  |

| 1kHz  | 0              | 960             | 1,221           |  |  |  |  |

| 422Hz | 0              | 1,890           | 2,152           |  |  |  |  |

| 26Hz  | 0              | 29,818          | 33,570          |  |  |  |  |

#### 低電圧/過電圧モニタ

C入力が測定されるたびに、結果は、メモリに格納されている低電圧閾値および過電圧閾値と比較されます。セルの測定値が過電圧制限値を超えている場合は、メモリ内のビットがフラグとしてセットされます。同様に、測定結果が低電圧制限値より低い場合にもフラグがセットされます。過電圧閾値と低電圧閾値は構成レジスタ・グループAに格納されます。フラグはステータス・レジスタ・グループBと補助レジスタ・グループDに格納されます。

#### 補助(GPIO)測定(ADAXコマンド)

ADAXコマンドによってGPIO入力の測定が開始されます。このコマンドには、測定するGPIO入力(GPIO1~9)と使用するADCモードを選択するためのオプションがあります。また、ADAXコマンドは、2番目のリファレンスも測定します。ADAXコマンドには、GPIOのサブセットと2番目のリファレンスを個別に測定するためのオプションと、9つのGPIO全てと2番目のリファレンスを1つのコマンドで測定するためのオプションがあります。ADAXコマンドのフォーマットについては、コマンドのセクションを参照してください。全ての補助測定はVーピンの電圧を基準にしています。GPIOに温度センサーを接続すれば、このコマンドを使用して外部温度を読み出すことができます。これらのセンサーの電源は2番目のリファレンスから取ることができ、このリファレンスもADAXコマンドによって測定されるので、正確なレシオメトリック測定を行うことができます。

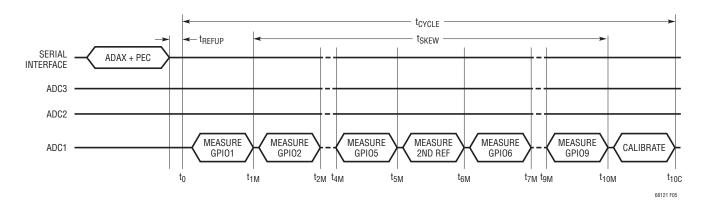

全てのGPIOと2番目のリファレンスを測定するADAXコマンドのタイミングを図5に示します。全部で10回の測定がADC1単独で実行されます。2番目のリファレンスは、GPIO5の測定後からGPIO6の測定前の間に測定されます。

全てのGPIOと2番目のリファレンスを測定するADAXコマンドの変換時間を表7に示します。 $t_{10C}$ は合計変換時間を表します。

図5.全てのGPIOと2番目のリファレンスを測定するADAXコマンドのタイミング

表7.全てのGPIOと2番目のリファレンスを様々なモードで測定するADAXコマンドの変換時間と同期時間

|       |                | 変換時間(μs)        |                 |                 |                  |                  |         |  |  |  |

|-------|----------------|-----------------|-----------------|-----------------|------------------|------------------|---------|--|--|--|

| モード   | t <sub>0</sub> | t <sub>1M</sub> | t <sub>2M</sub> | t <sub>9M</sub> | t <sub>10M</sub> | t <sub>10C</sub> | tskew   |  |  |  |

| 27kHz | 0              | 58              | 104             | 431             | 478              | 1,825            | 420     |  |  |  |

| 14kHz | 0              | 87              | 163             | 693             | 769              | 2,116            | 682     |  |  |  |

| 7kHz  | 0              | 145             | 279             | 1,217           | 1,350            | 3,862            | 1,205   |  |  |  |

| 3kHz  | 0              | 261             | 512             | 2,264           | 2,514            | 5,025            | 2,253   |  |  |  |

| 2kHz  | 0              | 494             | 977             | 4,358           | 4,841            | 7,353            | 4,347   |  |  |  |

| 1kHz  | 0              | 960             | 1,908           | 8,547           | 9,496            | 12,007           | 8,536   |  |  |  |

| 422Hz | 0              | 1,890           | 3,770           | 16,926          | 18,805           | 21,316           | 16,915  |  |  |  |

| 26Hz  | 0              | 29,818          | 59,624          | 268,271         | 298,078          | 335,498          | 268,260 |  |  |  |

# デジタル冗長化機能を備えた補助(GPIO)測定(ADAXDコマンド)

ADAXDコマンドはADAXコマンドと同様に動作しますが、デジタル冗長化機能を使用して追加の診断を実行することだけが異なります。冗長化を有効にするには、ADAXDの実行時に構成レジスタ・グループBのPS[1:0]を0または1に設定する必要があります。デジタル冗長化機能を使用したA/D変換のセクションを参照してください。

ADAXとADAXDの実行時間は同じです。

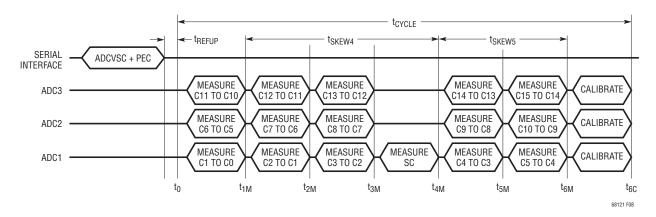

### セル電圧とGPIOの測定(ADCVAXコマンド)

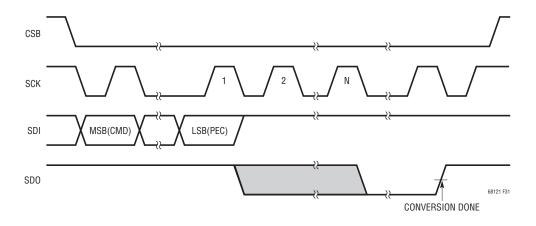

ADCVAXコマンドは、15個のセルの測定値を2つのGPIO測定値(GPIO1およびGPIO2)と組み合わせます。このコマンドを使用すると、電流センサーをGPIO1入力またはGPIO2入力に接続した場合に、バッテリ・セルの電圧測定値と電流測定値の同期が容易になります。ADCVAXコマンドのタイミングを図6に示します。ADCVAXコマンドのフォーマットについては、コマンドのセクションを参照してください。高速モードでの電流測定値と電圧測定値の同期時間(tskew1およびtskew3)は、それぞれ194μsおよび147μs以内です。

様々なモードでのADCVAXコマンドの変換時間と同期時間を表8に示します。このコマンドの合計変換時間はtrcにより与えられます。

図6. ADCVAX コマンドのタイミング

Rev. 0

**24** 詳細∶www.analog.com

表8. 様々なモードでのADCVAXコマンドの変換時間と同期時間

|       |                |                 |                 |                 | 同期時間(μs)        |                 |                 |                 |                 |         |                    |

|-------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|---------|--------------------|

| モード   | t <sub>0</sub> | t <sub>1M</sub> | t <sub>2M</sub> | t <sub>3M</sub> | t <sub>4M</sub> | t <sub>5M</sub> | t <sub>6M</sub> | t <sub>7M</sub> | t <sub>7C</sub> | tskew1  | t <sub>SKEW3</sub> |

| 27kHz | 0              | 58              | 104             | 151             | 205             | 252             | 306             | 352             | 1,328           | 194     | 147                |

| 14kHz | 0              | 87              | 163             | 238             | 321             | 397             | 480             | 556             | 1,531           | 310     | 235                |

| 7kHz  | 0              | 145             | 279             | 413             | 554             | 688             | 829             | 963             | 2,753           | 543     | 409                |

| 3kHz  | 0              | 261             | 512             | 762             | 1,020           | 1,270           | 1,527           | 1,778           | 3,568           | 1,008   | 758                |

| 2kHz  | 0              | 494             | 977             | 1,460           | 1,950           | 2,433           | 2,924           | 3,407           | 5,197           | 1,939   | 1,456              |

| 1kHz  | 0              | 960             | 1,908           | 2,857           | 3,812           | 4,761           | 5,717           | 6,665           | 8,455           | 3,801   | 2,853              |

| 422Hz | 0              | 1,890           | 3,770           | 5,649           | 7,536           | 9,415           | 11,302          | 13,181          | 14,971          | 7,525   | 5,645              |

| 26Hz  | 0              | 29,818          | 59,624          | 89,431          | 119,245         | 149,052         | 178,866         | 208,672         | 234,899         | 119,234 | 89,427             |

### データ・アクイジション・システムの診断

バッテリ・モニタリング・データ・アクイジション・システムは、マルチプレクサ、ADC、1番目のリファレンス、デジタル・フィルタ、およびメモリで構成されます。信頼性の高い性能を長期間確保するために、診断コマンドがいくつかあります。これらのコマンドを使用して、各回路が正常に動作していることを確認できます。

#### 内部デバイス・パラメータの測定(ADSTATコマンド)

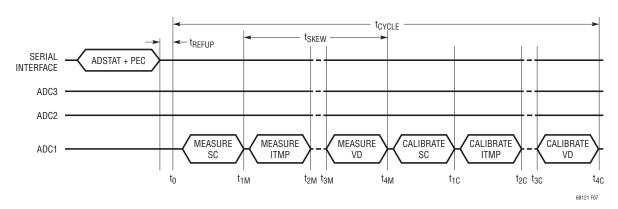

ADSTATコマンドは、以下に示す内部デバイス・パラメータ を測定する診断コマンドです。対象となるパラメータは、セ ル合計測定値(SC)、内部ダイ温度(ITMP)、アナログ電源電圧(VA)、およびデジタル電源電圧(VD)です。これらのパラメータについて、以降のセクションで説明します。前述した8つのADCモードは、全てこれらの変換で使用できます。ADSTATコマンドのフォーマットについては、コマンドのセクションを参照してください。4つの内部デバイス・パラメータ全てを測定するADSTATコマンドのタイミングを図7に示します。

4つの内部パラメータ全てを測定するADSTATコマンドの変換時間を表9に示します。 $t_{4C}$ は、ADSTATコマンドの合計変換時間を表します。

図7. SC、ITMP、VA、VDを測定する ADSTAT コマンドのタイミング

表9、SC、ITMP、VA、VDを様々なモードで測定するADSTATコマンドの変換時間と同期時間

|       |                |                 | 変換時             | 間(µs)           |                 |                 | 同期時間(μs) |

|-------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------|

| モード   | t <sub>0</sub> | t <sub>1M</sub> | t <sub>2M</sub> | t <sub>3M</sub> | t <sub>4M</sub> | t <sub>4C</sub> | tskew    |

| 27kHz | 0              | 58              | 104             | 151             | 198             | 742             | 140      |

| 14kHz | 0              | 87              | 163             | 238             | 314             | 858             | 227      |

| 7kHz  | 0              | 145             | 279             | 413             | 547             | 1,556           | 402      |

| 3kHz  | 0              | 261             | 512             | 762             | 1,012           | 2,022           | 751      |

| 2kHz  | 0              | 494             | 977             | 1,460           | 1,943           | 2,953           | 1,449    |

| 1kHz  | 0              | 960             | 1,908           | 2,857           | 3,805           | 4,814           | 2,845    |

| 422Hz | 0              | 1,890           | 3,770           | 5,649           | 7,529           | 8,538           | 5,638    |

| 26Hz  | 0              | 29,818          | 59,624          | 89,431          | 119,238         | 134,211         | 89,420   |

**セル合計測定値**: セル合計測定値は、C15とC0の間の電圧を30:1に減衰させた値です。セル合計測定値(SC)の16ビットADCの値は、ステータス・レジスタ・グループAに格納されます。C0ピンとVーピンの間に電位差があると、この差と等しい誤差がSCの値に生じます。SCの値から、全セルの電圧測定値の合計は次式により与えられます。

Sum of All Cells = SC • 30 • 100 uV

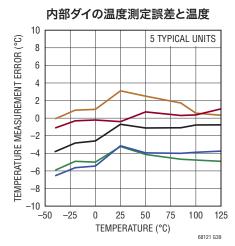

内部ダイ温度: ADSTATコマンドは、内部ダイ温度の測定にも使用できます。ダイ温度測定値(ITMP)の16ビットADCの値は、ステータス・レジスタ・グループAに格納されます。ITMPから、実際のダイ温度は次式を使用して計算されます。

Internal Die Temperature (°C) =

ITMP •

$$\left(\frac{100 \ \mu V}{7.6 mV}\right)$$

°C - 276°C

電源測定値: ADSTATコマンドは、アナログ電源 ( $V_{REG}$ )とデジタル電源 ( $V_{REGD}$ )の測定にも使用されます。アナログ電源電圧測定値 ( $V_{AD}$ )の16ビットADCの値は、ステータス・レジスタ・グループ A に格納されます。デジタル電源電圧測定値 ( $V_{AD}$ )の16ビットADCの値は、ステータス・レジスタ・グループ B に格納されます。 $V_{AD}$ と $V_{AD}$ から、各電源の測定値は次の式によって得られます。

Analog Power Supply Measurement ( $V_{REG}$ ) =  $V_A \bullet 100 \ \mu V$ Digital Power Supply Measurement ( $V_{REGD}$ ) =  $V_D \bullet 100 \ \mu V$   $V_{REG}$ の値は外付け部品によって決まります。精度を維持するため、 $V_{REG}$ は4.5 $V\sim$ 5.5Vの範囲内にします。 $V_{REGD}$ の値は内部部品によって決まります。 $V_{REGD}$ の通常の範囲は2.7 $V\sim$ 3.6Vです。

### デジタル冗長化機能を使用した内部デバイス・ パラメータの測定(ADSTATDコマンド)

ADSTATDコマンドはADSTATコマンドと同様に動作しますが、デジタル冗長化機能を使用して追加の診断を実行することだけが異なります。冗長化を有効にするには、ADSTATDの実行時に構成レジスタ・グループBのPS[1:0]を0または1に設定する必要があります。デジタル冗長化機能を使用したA/D変換のセクションを参照してください。

ADSTATとADSTATDの実行時間は同じです。

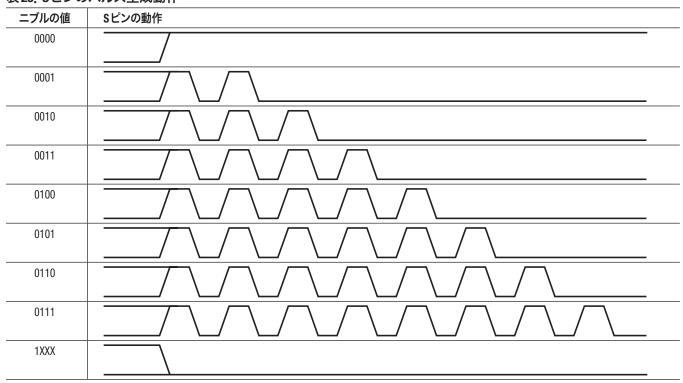

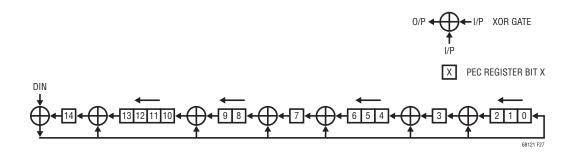

#### デジタル冗長化機能を使用したA/D変換

3つの内部ADCは、独自のデジタル積分マシンおよびデジタル微分マシンをそれぞれ搭載しています。また、LTC6812-1は、冗長化と誤り検査に使用される第4のデジタル積分マシンおよびデジタル微分マシンも搭載しています。

全てのADCコマンドおよびセルフ・テスト・コマンド(ADAX およびADSTATを除く)は、デジタル冗長化と並行して実行できます。これに該当するのは、ADCV、ADOW、CVST、ADOL、ADAXD、AXOW、AXST、ADSTATD、STATST、ADCVAX、ADCVSCです。A/D変換を冗長化と同時に実行する場合、アナログ変調器はそのビット・ストリームを主要デジタル・マシンと冗長デジタル・マシンの両方に送信します。

Rev. 0

26

詳細:www.analog.com

変換が終了すると、2つのマシンからの結果が比較されます。一致しなかった場合は、0xFF0X (≥ 6.528V)という値が結果レジスタに書き込まれます。この値はADCのクランプ範囲外であり、ホストはこれを障害の兆候として識別します。最後の4ビットは、結果値のどのニブルが一致しなかったを示すために使用されます。

| 結果                    | 意味                    |

|-----------------------|-----------------------|

| 0b1111_1111_0000_0XXX | ビット15~12には障害が検出されなかった |

| 0b1111_1111_0000_1XXX | ビット15~12に障害が検出された     |

| 0b1111_1111_0000_X0XX | ビット11~8には障害が検出されなかった  |

| 0b1111_1111_0000_X1XX | ビット11~8に障害が検出された      |

| 0b1111_1111_0000_XX0X | ビット7~4には障害が検出されなかった   |

| 0b1111_1111_0000_XX1X | ビット7~4に障害が検出された       |

| 0b1111_1111_0000_XXX0 | ビット3~0には障害が検出されなかった   |

| 0b1111_1111_0000_XXX1 | ビット3~0に障害が検出された       |

|                       |                       |

存在する冗長デジタル・マシンは1つなので、冗長化を一度に適用できるADCは1つだけです。デフォルトでは、LTC6812-1はADC経路の冗長化を自動的に選択します。ただし、構成レジスタ・グループBのPS[1:0]ビットに書き込むことにより、ADCの冗長化経路を選択できます。

ADC経路の冗長化について可能性のある全ての選択肢を表10に示します。

構成レジスタ・グループBのFDRFビットに1を書き込むと、その後のA/D変換の間はデジタル冗長化の比較が機能しなくなります。

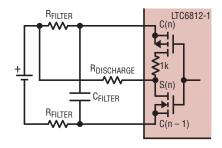

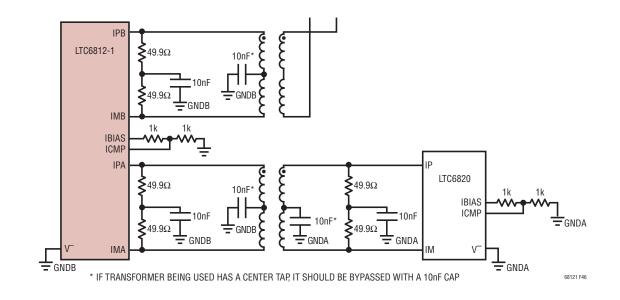

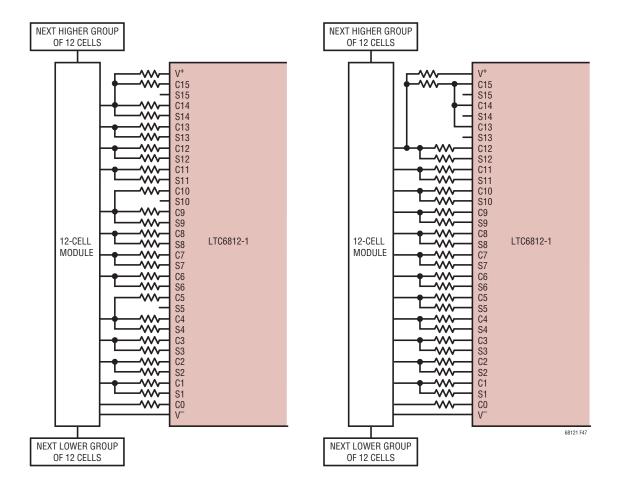

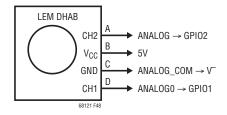

# セル電圧とセル電圧合計の測定(ADCVSCコマンド)