# 4ポートIEEE 802.3bt PoE PSE コントローラ

## 特長

- 4つのPSEポート

- ポート当たり2つのパワー・チャンネル

- IEEE 802.3bt タイプ 3 および 4 PSE 規格に完全に準拠

- タイプ1、2、3、および4PDをサポート

- チャンネル当たりの電力経路損失が小さい

- 検出抵抗:150mΩ

- MOSFET R<sub>DS(ON)</sub>:30mΩ以下

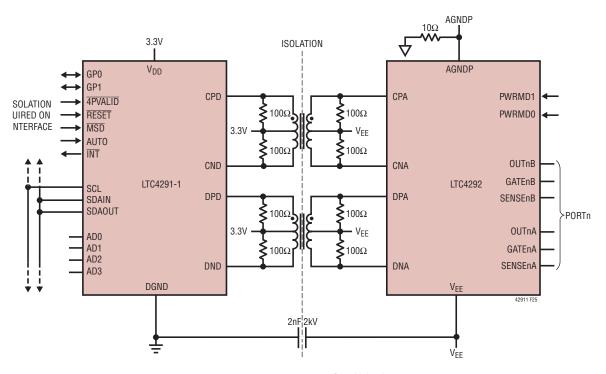

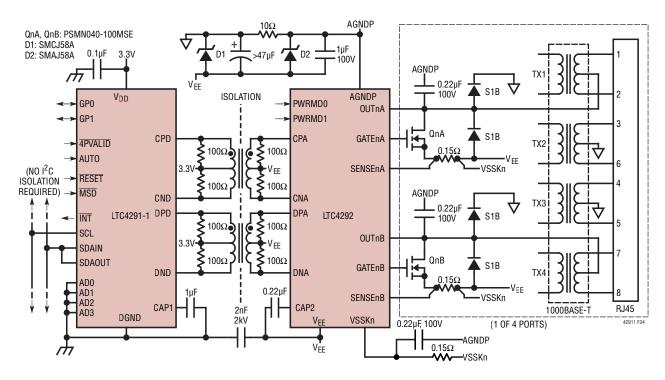

- チップセット構成で電気的に絶縁

- フォトカプラおよび3.3V絶縁型電源は不要

- 非常に信頼性の高いマルチポイントPD検出

- 接続チェックによりシングル・シグネチャPDと デュアル・シグネチャPDを自動識別

- 専用機能により継続的にポートごとの電力と電流を モニタリング

- ポートごとの電力ポリシング

- 1MHz I<sup>2</sup>C 互換のシリアル制御インターフェース

- ピンまたはI<sup>2</sup>Cで設定可能な最大71.3WのPD電源

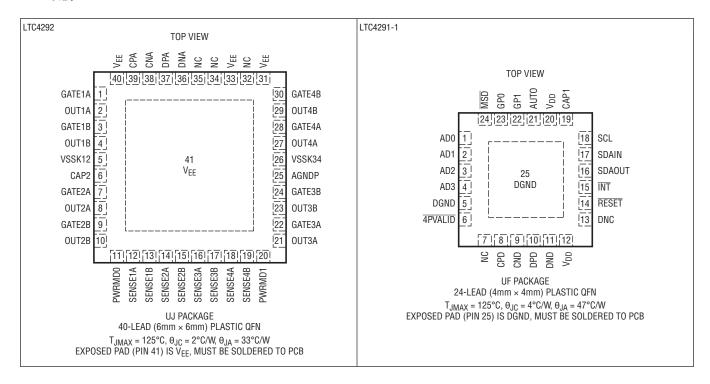

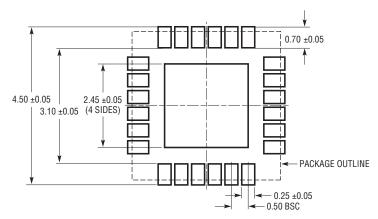

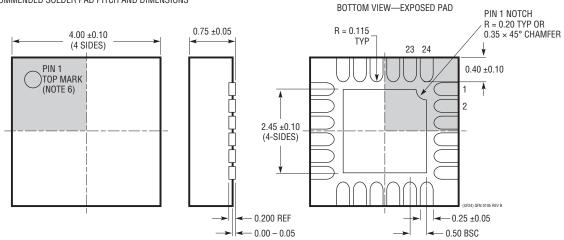

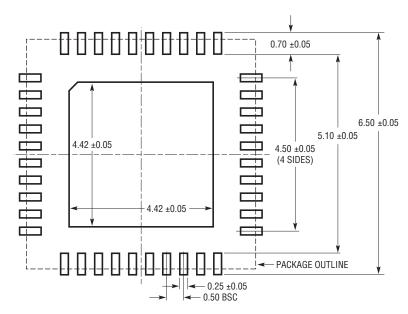

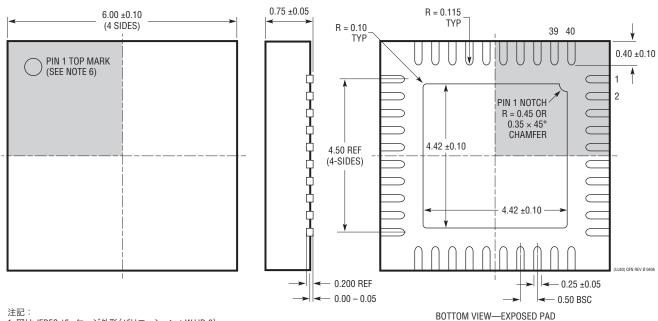

- 40 ピン 6mm×6mm (LTC4292)と24 ピン 4mm×4mm (LTC4291-1)の QFN パッケージで提供

# アプリケーション

- PoE PSEスイッチ/ルーター

- PoE PSE ミッドスパン

### 概要

LTC® 4291-1/LTC4292 チップセットは、IEEE 802.3bt タイプ3および4準拠のPoE (Power over Ethernet) システム向け4ポートPSE (Power Sourcing Equipment) コントローラです。LTC4291-1/LTC4292 は、802.3af、802.3at、および802.3bt 準拠のPDに電力を供給するように設計されています。LTC4291-1/LTC4292 チップセットは、パワー・チャンネルごとに低 $R_{DS(ON)}$ の外付けMOSFET と0.15 $\Omega$ の検出抵抗を利用することで業界で最も小さい熱損失を実現しています。高価なフォトカプラと複雑な3.3V 絶縁型電源をトランス絶縁型の通信プロトコルに置き換えることで、部品コストを大幅に低減します。

高度なパワー・マネージメント機能には、ポートごとの14 ビット電流モニタリング、プログラマブルな電流制限、事前に選択したポートの多目的高速シャットダウンが含まれます。高度なパワー・マネージメントのためのホスト・ソフトウェアは無償ライセンス版が用意されています。独自のマルチポイント検出機構を備えたPD検出機能によって、PDの誤識別を防止します。オートクラスと5イベント物理分類をサポートしています。LTC4291-1/LTC4292は、最大1MHzで動作可能なI<sup>2</sup>Cシリアル・インターフェースを内蔵しています。LTC4291-1/LTC4292は、ピンまたはI<sup>2</sup>Cを使ってPD供給電力を最大71.3Wまで設定できます。

全ての登録商標および商標の所有権は、それぞれの所有者に帰属します。

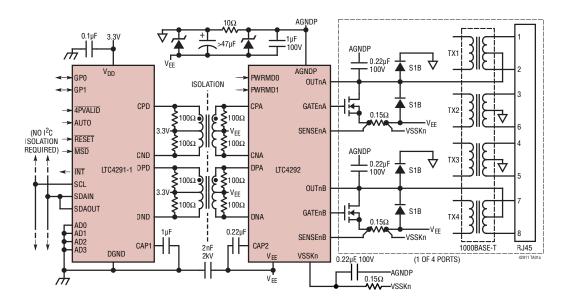

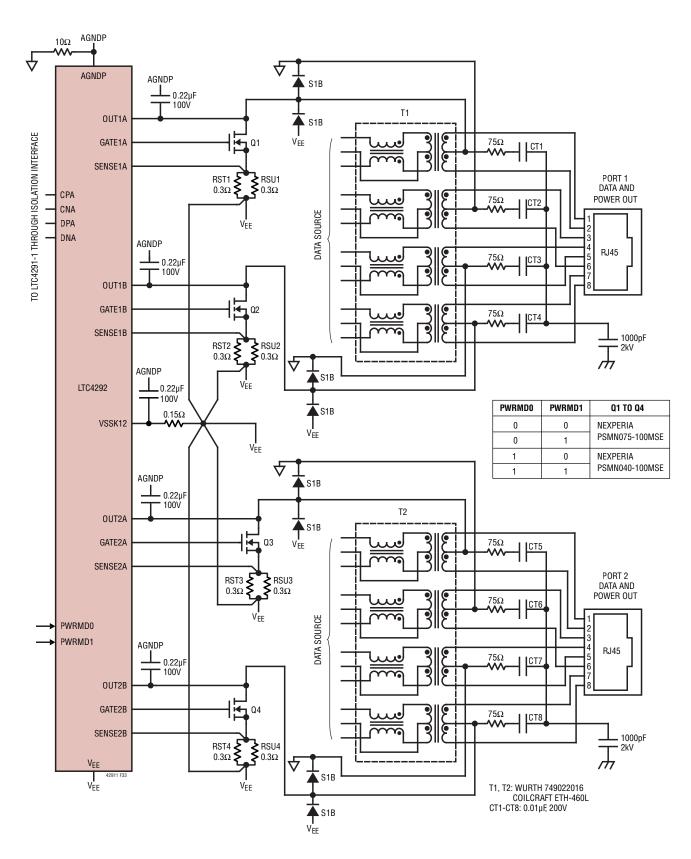

# 標準的応用例

# LTC4291-1/LTC4292

# 絶対最大定格

#### (Notes 1, 4)

#

保存温度範囲.....-65°C~150°C

#### (Note 1)

#### LTC4291-1

| 電源電圧                                                                     |

|--------------------------------------------------------------------------|

| V <sub>DD</sub> − DGND−0.3V~3.6V                                         |

| デジタル・ピン                                                                  |

| SCL、SDAIN、SDAOUT、INT、RESET、MSD、ADn、AUTO、                                 |

| $\overline{4PVALID}$ , GPn (DGND – 0.3V) $\sim$ (V <sub>DD</sub> + 0.3V) |

| アナログ・ピン                                                                  |

| CAP1 (Note 13)0.3V~(DGND + 2V)                                           |

| CPD, CND, DPD, DND (DGND – 0.3V) $\sim$ (V <sub>DD</sub> + 0.3V)         |

| 動作周囲温度範囲                                                                 |

| LTC4291I-140°C~85°C                                                      |

| ジャンクション温度(Note 2)125°C                                                   |

| 保存温度範囲65°C~150°C                                                         |

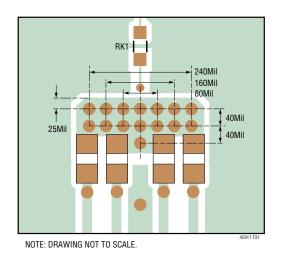

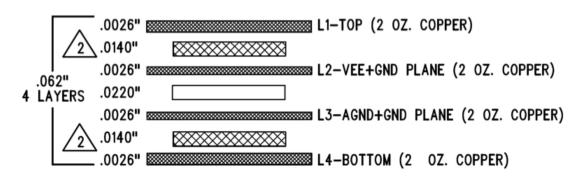

## ピン配置

# 発注情報

| 鉛フリー仕上げ          | テープ&リール            | 製品マーキング   | パッケージ                           | 温度範囲          |

|------------------|--------------------|-----------|---------------------------------|---------------|

| LTC4291IUF-1#PBF | LTC4291IUF-1#TRPBF | 42911     | 24-Lead (4mm × 4mm) Plastic QFN | -40°C to 85°C |

| LTC4292IUJ#PBF   | LTC4292IUJ#TRPBF   | LTC4292UJ | 40-Lead (6mm × 6mm) Plastic QFN | -40°C to 85°C |

更に広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。 テープ&リールの仕様。一部のパッケージは、#TRMPBF接尾部の付いた指定の販売経路を通じて500個入りのリールで供給可能です。

# 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外はT<sub>A</sub> = 25°Cでの値。注記がない限り、AGNDP – V<sub>EE</sub> = 54VおよびV<sub>DD</sub> – DGND = 3.3V (Note 3 および 4)。

| SYMBOL            | PARAMETER                                        | CONDITIONS                                                                                      |   | MIN        | TYP        | MAX        | UNITS                    |

|-------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------|---|------------|------------|------------|--------------------------|

|                   | Main PoE Supply Voltage                          | AGNDP – V <sub>EE</sub> For IEEE Type 3 Compliant Output For IEEE Type 4 Compliant Output       | • | 51<br>53   |            | 57<br>57   | V<br>V                   |

|                   | Undervoltage Lock-Out                            | AGNDP – V <sub>EE</sub>                                                                         | • | 20         | 25         | 30         | V                        |

| $V_{DD}$          | V <sub>DD</sub> Supply Voltage                   | V <sub>DD</sub> – DGND                                                                          | • | 3.0        | 3.3        | 3.6        | V                        |

|                   | Undervoltage Lock-Out                            | V <sub>DD</sub> – DGND                                                                          |   |            | 2.7        |            | V                        |

| V <sub>CAP1</sub> | Internal Regulator Supply Voltage                | V <sub>CAP1</sub> – DGND                                                                        |   |            | 1.84       |            | V                        |

| V <sub>CAP2</sub> | Internal Regulator Supply Voltage                | V <sub>CAP2</sub> – V <sub>EE</sub>                                                             |   |            | 4.3        |            | V                        |

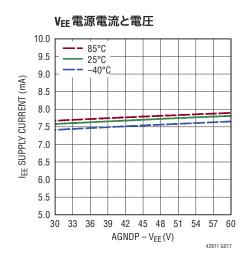

| I <sub>EE</sub>   | V <sub>EE</sub> Supply Current                   | $(AGNDP - V_{EE}) = 55V$                                                                        | • |            | 9          | 15         | mA                       |

| R <sub>EE</sub>   | V <sub>EE</sub> Supply Resistance                | $(AGNDP - V_{EE}) < 15V$                                                                        | • |            |            | 12         | kΩ                       |

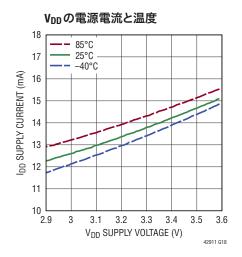

| I <sub>DD</sub>   | V <sub>DD</sub> Supply Current                   | $(V_{DD} - DGND) = 3.3V$                                                                        | • |            | 10         | 15         | mA                       |

| 検出/接続             | チェック                                             |                                                                                                 |   |            |            |            |                          |

|                   | Forced Current                                   | First Point, AGNDP – V <sub>OUTnM</sub> = 9V<br>Second Point, AGNDP – V <sub>OUTnM</sub> = 3.5V | • | 220<br>143 | 240<br>160 | 260<br>180 | μ <b>Α</b><br>μ <b>Α</b> |

|                   | Forced Voltage                                   | AGNDP – $V_{OUTnM}$ , $5\mu A \le I_{OUTnM} \le 500\mu A$ First Point Second Point              | • | 7 3        | 8<br>4     | 9<br>5     | V<br>V                   |

|                   | Detection/Connection Check Current<br>Compliance | AGNDP – V <sub>OUTnM</sub> = 0V                                                                 | • |            | 0.8        | 0.9        | mA                       |

| V <sub>OC</sub>   | Detection/Connection Check Voltage<br>Compliance | AGNDP – V <sub>OUTnM</sub> , Open Port                                                          | • |            | 10.4       | 12         | V                        |

|                   | Detection/Connection Check Voltage Slew<br>Rate  | AGNDP – V <sub>OUTnM</sub> , C <sub>PORT</sub> = 0.15μF (Note 7)                                | • |            |            | 0.01       | V/µs                     |

|                   | Min. Valid Signature Resistance                  |                                                                                                 | • | 15.5       | 17         | 18.5       | kΩ                       |

|                   | Max. Valid Signature Resistance                  |                                                                                                 | • | 27.5       | 29.7       | 32         | kΩ                       |

●は全動作温度範囲での規格値を意味する。それ以外はT<sub>A</sub> = 25°Cでの値。注記がない限り、AGNDP - V<sub>EE</sub> = 54VおよびV<sub>DD</sub> - DGND = 3.3V (Note 3 および 4)。

| SYMBOL                 | PARAMETER                                                           | CONDITIONS                                                                                                                                                                                                                                                                    |   | MIN                                                       | TYP                                                       | MAX                                                        | UNITS                            |

|------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------|----------------------------------|

| 分類                     |                                                                     |                                                                                                                                                                                                                                                                               |   |                                                           |                                                           | '                                                          |                                  |

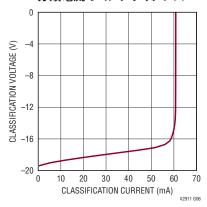

| V <sub>CLASS</sub>     | Classification Voltage                                              | $AGNDP - V_{OUTnM},  0mA \leq I_{OUTnM} \leq 50mA$                                                                                                                                                                                                                            | • | 16.0                                                      |                                                           | 20.5                                                       | V                                |

|                        | Classification Current Compliance                                   | V <sub>OUTnM</sub> = AGNDP                                                                                                                                                                                                                                                    | • | 53                                                        | 61                                                        | 67                                                         | mA                               |

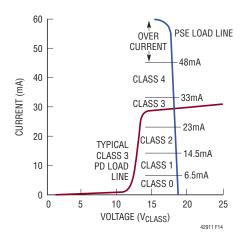

|                        | Classification Threshold Current                                    | Class Signature 0 – 1 Class Signature 1 – 2 Class Signature 2 – 3 Class Signature 3 – 4 Class Signature 4 – Overcurrent                                                                                                                                                       | • | 5.5<br>13.5<br>21.5<br>31.5<br>45.2                       | 6.5<br>14.5<br>23<br>33<br>48                             | 7.5<br>15.5<br>24.5<br>34.9<br>50.8                        | mA<br>mA<br>mA<br>mA             |

| V <sub>MARK</sub>      | Classification Mark State Voltage                                   | $AGNDP - V_{OUTnM}, \ 0.1 mA \le I_{CLASS} \le 5 mA$                                                                                                                                                                                                                          | • | 7.5                                                       | 9                                                         | 10                                                         | V                                |

|                        | Mark State Current Compliance                                       | $V_{OUTnM} = AGNDP$                                                                                                                                                                                                                                                           | • | 53                                                        | 61                                                        | 67                                                         | mA                               |

| ゲート・ドラー                | イバ                                                                  |                                                                                                                                                                                                                                                                               |   |                                                           |                                                           |                                                            |                                  |

|                        | GATE Pin Pull-Down Current                                          | Port Off, V <sub>GATEnM</sub> = V <sub>EE</sub> + 5V<br>Port Off, V <sub>GATEnM</sub> = V <sub>EE</sub> + 1V                                                                                                                                                                  | • | 0.4<br>0.08                                               | 0.12                                                      |                                                            | mA<br>mA                         |

|                        | GATE Pin Fast Pull-Down Current                                     | V <sub>GATEnM</sub> = V <sub>EE</sub> + 5V                                                                                                                                                                                                                                    |   |                                                           | 30                                                        |                                                            | mA                               |

|                        | GATE Pin On Voltage                                                 | V <sub>GATEnM</sub> - V <sub>EE</sub> , I <sub>GATEnM</sub> = 1μA                                                                                                                                                                                                             | • | 8                                                         | 12                                                        | 14                                                         | V                                |

| 出力電圧検出                 | 出                                                                   |                                                                                                                                                                                                                                                                               |   |                                                           |                                                           | '                                                          |                                  |

| V <sub>PG</sub>        | Power Good Threshold Voltage                                        | V <sub>OUTnM</sub> — V <sub>EE</sub>                                                                                                                                                                                                                                          | • | 2                                                         | 2.4                                                       | 2.8                                                        | V                                |

|                        | OUT Pin Pull-Up Resistance to AGNDP                                 | $0V \le (AGNDP - V_{OUTnM}) \le 5V$                                                                                                                                                                                                                                           | • | 300                                                       | 500                                                       | 700                                                        | kΩ                               |

| 電流検出                   |                                                                     |                                                                                                                                                                                                                                                                               | - |                                                           |                                                           |                                                            |                                  |

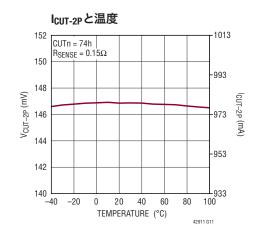

| Vcut-2P                | Overcurrent Sense Voltage,<br>Single-Signature PD                   | Vsensenm — Vsskn Class 1, CUTn[6:0] = 45h Class 2, CUTn[6:0] = 48h Class 3, CUTn[6:0] = 52h Class 4, CUTn[6:0] = 62h Class 5, CUTn[6:0] = 5Fh Class 6, CUTn[6:0] = 67h Class 7, CUTn[6:0] = 6Ch Class 8, CUTn[6:0] = 74h (Note 12)                                            | • | 13.5<br>21.6<br>47.5<br>92.0<br>84.0<br>105<br>119<br>140 | 14.1<br>22.5<br>50.5<br>96.0<br>87.0<br>110<br>124<br>146 | 14.6<br>23.4<br>53.5<br>100.0<br>91.0<br>114<br>129<br>152 | mV<br>mV<br>mV<br>mV<br>mV<br>mV |

| VIIIM OD               | Overcurrent Sense Voltage, Dual-Signature PD  Active Current Limit, | V <sub>SENSEnM</sub> – VSSKn<br>Class 1, CUT <i>n</i> [6:0] = 45h<br>Class 2, CUT <i>n</i> [6:0] = 48h<br>Class 3, CUT <i>n</i> [6:0] = 52h<br>Class 4, CUT <i>n</i> [6:0] = 62h<br>Class 5, CUT <i>n</i> [6:0] = 74h (Note 12)<br>V <sub>OUTnM</sub> – V <sub>EE</sub> < 10V | • | 13.5<br>21.6<br>47.5<br>92.0<br>140                       | 14.1<br>22.5<br>50.5<br>96.0<br>146                       | 14.6<br>23.4<br>53.5<br>100.0<br>152                       | mV<br>mV<br>mV<br>mV             |

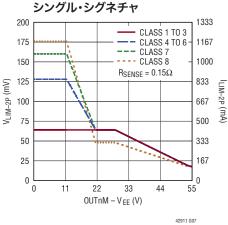

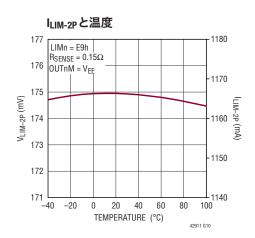

| V <sub>LIM-2P</sub>    | Single-Signature PD                                                 | Class 1 – Class 3, LIM $n$ = 80h<br>Class 4 – Class 6, LIM $n$ = C0h<br>Class 7, LIM $n$ = D0h<br>Class 8, LIM $n$ = E9h (Note 12)                                                                                                                                            | • | 61.2<br>122<br>153<br>168                                 | 63.6<br>128<br>159<br>175                                 | 67.3<br>135<br>169<br>185                                  | mV<br>mV<br>mV                   |

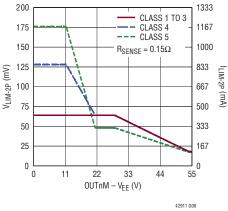

|                        | Active Current Limit,<br>Dual-Signature PD                          | $V_{OUTnM} - V_{EE} < 10V$<br>Class 1 - Class 3, LIM $n = 80h$<br>Class 4, LIM $n = C0h$<br>Class 5, LIM $n = E9h$ (Note 12)                                                                                                                                                  | • | 61.2<br>122<br>168                                        | 63.6<br>128<br>175                                        | 67.3<br>135<br>185                                         | mV<br>mV<br>mV                   |

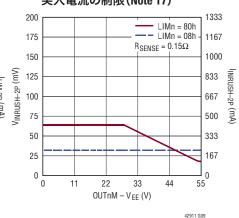

| V <sub>INRUSH-2P</sub> | Active Current Limit, Inrush                                        | AGNDP - V <sub>OUTnM</sub> > 30V (Note 17)<br>LIMn = 80h<br>LIMn = 08h                                                                                                                                                                                                        | • | 61.2<br>30.6                                              | 63.6<br>31.8                                              | 67.3<br>33.7                                               | mV<br>mV                         |

| V <sub>HOLD-2P</sub>   | DC Disconnect Sense Voltage                                         | $V_{SENSEnM} - VSSKn$<br>CUTn[7] (Dis) Bit = 0<br>CUTn[7] (Dis) Bit = 1 (Note 12)                                                                                                                                                                                             | • | 0.31<br>0.76                                              | 0.53<br>1.13                                              | 0.74<br>1.49                                               | mV<br>mV                         |

●は全動作温度範囲での規格値を意味する。それ以外はT<sub>A</sub> = 25°Cでの値。注記がない限り、AGNDP - V<sub>EE</sub> = 54VおよびV<sub>DD</sub> - DGND = 3.3V。 (Notes3 および 4)

| SYMBOL                   | PARAMETER                                              | CONDITIONS                                                                                             |   | MIN      | ТҮР         | MAX        | UNITS                |

|--------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------|---|----------|-------------|------------|----------------------|

| V <sub>SC</sub>          | Short-Circuit Sense                                    | V <sub>SENSEnM</sub> - V <sub>EE</sub> - V <sub>LIM</sub>                                              | • | 20       | 50          | 80         | mV                   |

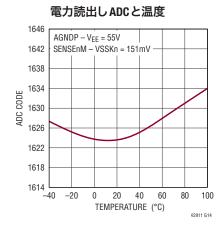

| ポート電流の                   | D読出し                                                   |                                                                                                        |   |          |             |            |                      |

|                          | Full-Scale Range                                       | (Note 7、15、16)                                                                                         |   |          | 1.018       |            | V                    |

|                          | LSB Weight                                             | V <sub>SENSEnM</sub> – VSSKn, VSSKn = V <sub>EE</sub> (Note 15)                                        | • | 61.0     | 62.1        | 63.5       | μV/LSB               |

|                          | Averaging Period                                       | FILTER_TYPE Bit = 1<br>FILTER_TYPE Bit = 0 (Note 7)                                                    |   |          | 100<br>1000 |            | ms<br>ms             |

|                          | Update Interval                                        | (Note 7)                                                                                               |   |          | 100         |            | ms                   |

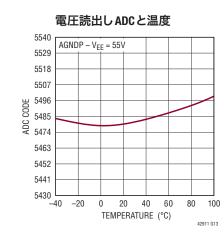

| ポート電力の                   | <br>D読出し                                               |                                                                                                        |   | <u> </u> |             |            | <u> </u>             |

|                          | Full-Scale Range                                       | (Note 7, 15, 16)                                                                                       |   |          | 83.8        |            | V <sup>2</sup>       |

|                          | LSB Weight                                             | (V <sub>SENSEnM</sub> - VSSKn) × (AGNDP - V <sub>EE</sub> )<br>VSSKn = V <sub>EE</sub> (Note 15)       | • | 4.992    | 5.115       | 5.235      | mV <sup>2</sup> /LSB |

|                          | Averaging Period                                       | FILTER_TYPE Bit = 1<br>FILTER_TYPE Bit = 0 (Note 7)                                                    |   |          | 100<br>1000 |            | ms<br>ms             |

|                          | Update Interval                                        | (Note 7)                                                                                               |   |          | 100         |            | ms                   |

| システム電圧                   |                                                        |                                                                                                        |   |          |             |            |                      |

|                          | Full-Scale Range                                       | (Note 7)                                                                                               |   |          | 82          |            | V                    |

|                          | LSB Weight                                             | AGNDP – V <sub>EE</sub>                                                                                | • | 9.8      | 10.1        | 10.3       | mV/LSB               |

|                          | Averaging Period                                       | FILTER_TYPE Bit = 1<br>FILTER_TYPE Bit = 0 (Note 7)                                                    |   |          | 100<br>1000 |            | ms<br>ms             |

|                          | Update Interval                                        | (Note 7)                                                                                               |   |          | 100         |            | ms                   |

| デジタル・イ                   | ンターフェース                                                |                                                                                                        |   |          |             |            |                      |

| V <sub>ILD</sub>         | Digital Input Low Voltage                              | ADn, RESET, MSD, GPn, AUTO, 4PVALID (Note 6)                                                           | • |          |             | 0.8        | ٧                    |

|                          | I <sup>2</sup> C Input Low Voltage                     | SCL, SDAIN (Note 6)                                                                                    | • |          |             | 1.0        | V                    |

| V <sub>IHD</sub>         | Digital Input High Voltage                             | (Note 6)                                                                                               | • | 2.2      |             |            | V                    |

|                          | Digital Output Voltage Low                             | I <sub>SDAOUT</sub> = 3mA, I <sub>INT</sub> = 3mA<br>I <sub>SDAOUT</sub> = 5mA, I <sub>INT</sub> = 5mA | • |          |             | 0.4<br>0.7 | V                    |

|                          | Internal Pull-Up to V <sub>DD</sub>                    | AD <i>n</i> , RESET, MSD, GP <i>n</i>                                                                  |   |          | 50          |            | kΩ                   |

|                          | Internal Pull-Down to DGND                             | AUTO, 4PVALID                                                                                          |   |          | 50          |            | kΩ                   |

| PWRMD                    |                                                        |                                                                                                        |   |          |             |            |                      |

|                          | PWRMD Digital Input Low Voltage                        | V <sub>PWRMDn</sub> — V <sub>EE</sub>                                                                  | • |          |             | 0.8        | V                    |

|                          | PWRMD Digital Input High Voltage                       | V <sub>PWRMDn</sub> — V <sub>EE</sub>                                                                  | • | 3.4      |             |            | V                    |

|                          | Internal Pull Up to CAP2                               | PWRMD0, PWRMD1                                                                                         |   |          | 50          |            | kΩ                   |

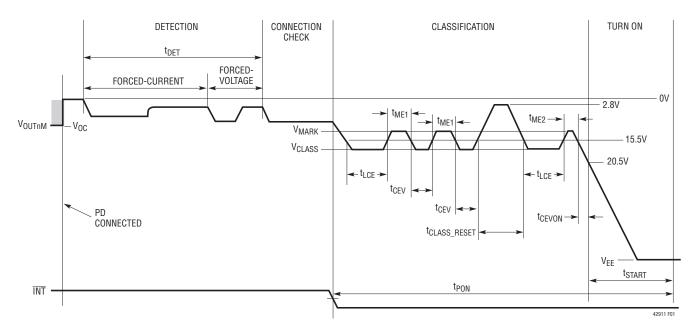

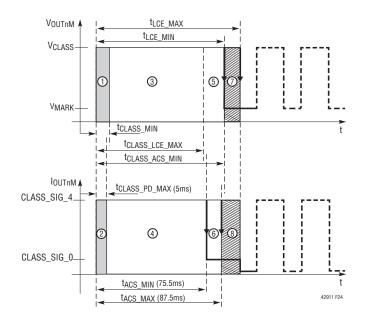

| PSEのタイミ                  | ング特性(Note 7)                                           |                                                                                                        |   |          |             |            |                      |

| t <sub>DET</sub>         | Detection Time                                         | Beginning to End of Detection                                                                          | • |          | 320         | 500        | ms                   |

| t <sub>CLASS_RESET</sub> | Classification Reset Duration                          |                                                                                                        | • | 15       |             |            | ms                   |

| t <sub>CEV</sub>         | Class Event Duration                                   |                                                                                                        | • | 6        | 12          | 20         | ms                   |

| t <sub>CEVON</sub>       | Class Event Turn On Duration                           | C <sub>PORT</sub> = 0.6μF                                                                              | • |          |             | 0.1        | ms                   |

| t <sub>LCE</sub>         | Long Class Event Duration                              |                                                                                                        | • | 88       |             | 105        | ms                   |

| t <sub>CLASS</sub>       | Class Event I <sub>CLASS</sub> Measurement Timing      |                                                                                                        | • | 6        |             |            | ms                   |

| t <sub>CLASS_LCE</sub>   | Long Class Event I <sub>CLASS</sub> Measurement Timing |                                                                                                        | • | 6        |             | 75         | ms                   |

| tclass_acs               | Autoclass I <sub>CLASS</sub> Measurement Timing        |                                                                                                        | • | 88       |             |            | ms                   |

●は全動作温度範囲での規格値を意味する。それ以外はT<sub>A</sub> = 25°Cでの値。注記がない限り、AGNDP - V<sub>EE</sub> = 54VおよびV<sub>DD</sub> - DGND = 3.3V (Notes3 および 4)。

| SYMBOL                | PARAMETER                                                 | CONDITIONS                                                              |   | MIN     | TYP     | MAX      | UNITS    |

|-----------------------|-----------------------------------------------------------|-------------------------------------------------------------------------|---|---------|---------|----------|----------|

| t <sub>ME1</sub>      | Mark Event Duration (Except Last Mark Event)              | (Note 11)                                                               | • | 6       | 8.6     | 12       | ms       |

| t <sub>ME2</sub>      | Last Mark Event Duration                                  | (Note 11)                                                               | • | 6       | 20      |          | ms       |

| t <sub>PON</sub>      | Power On Delay, Auto Mode                                 | From End of Valid Detect to End of Valid Inrush (Note 14)               | • |         |         | 400      | ms       |

| tauto_pse1            | Autoclass Power Measurement Start                         | From End of Inrush to Beginning of Autoclass Power Measurement          | • | 1.4     |         | 1.6      | S        |

| tauto_pse2            | Autoclass Power Measurement End                           | From End of Inrush to End of Autoclass Power<br>Measurement             | • | 3.1     |         | 3.5      | S        |

| tauto_window          | Autoclass Average Power Sliding Window                    |                                                                         | • | 0.15    | 0.2     | 0.3      | s        |

| t <sub>ED</sub>       | Fault Delay                                               | From Power On Fault to Next Detect                                      | • | 1.0     | 1.3     | 1.5      | S        |

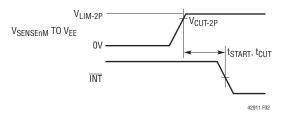

| tstart                | Maximum Current Limit Duration During Inrush              |                                                                         | • | 52      | 59      | 66       | ms       |

| t <sub>CUT</sub>      | Maximum Overcurrent Duration After Inrush                 |                                                                         | • | 52      | 59      | 66       | ms       |

|                       | Maximum Overcurrent Duty Cycle                            |                                                                         | • | 5.8     | 6.3     | 6.7      | %        |

| t <sub>LIM</sub>      | Maximum Current Limit Duration After Inrush               | (Note 12) Type 3, t <sub>LIMn</sub> = 8h Type 4, t <sub>LIMn</sub> = 5h | • | 10<br>6 | 12<br>8 | 14<br>10 | ms<br>ms |

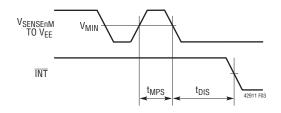

| t <sub>MPS</sub>      | Maintain Power Signature (MPS) Pulse<br>Width Sensitivity | Current Pulse Width to Reset Disconnect Timer (Note 8)                  | • | 1.6     |         | 3.6      | ms       |

| t <sub>DIS</sub>      | Maintain Power Signature (MPS) Dropout Time               | (Note 5)                                                                | • | 320     | 350     | 380      | ms       |

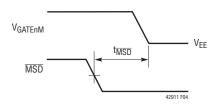

| tMSD                  | Masked Shut Down Delay                                    |                                                                         |   |         |         | 6.5      | μs       |

|                       | I <sup>2</sup> C Watchdog Timer Duration                  |                                                                         | • | 1.5     | 2       | 3        | S        |

|                       | Minimum Pulse Width for Masked Shut<br>Down               |                                                                         | • | 3       |         |          | μs       |

|                       | Minimum Pulse Width for RESET                             |                                                                         | • | 4.5     |         |          | μs       |

| I <sup>2</sup> Cのタイミン | グ(Note 7)                                                 |                                                                         |   |         |         |          |          |

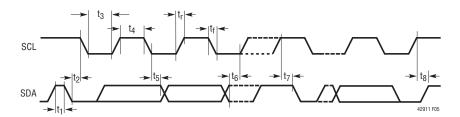

| f <sub>SCLK</sub>     | Clock Frequency                                           |                                                                         | • |         |         | 1        | MHz      |

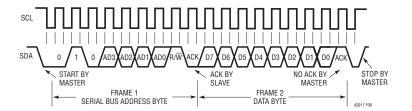

| t <sub>1</sub>        | Bus Free Time                                             | Figure 5(Note 9)                                                        | • | 480     |         |          | ns       |

| t <sub>2</sub>        | Start Hold Time                                           | Figure 5(Note 9)                                                        | • | 240     |         |          | ns       |

| t <sub>3</sub>        | SCL Low Time                                              | Figure 5(Note 9)                                                        | • | 480     |         |          | ns       |

| t <sub>4</sub>        | SCL High Time                                             | Figure 5(Note 9)                                                        | • | 240     |         |          | ns       |

| t <sub>5</sub>        | SDAIN Data Hold Time                                      | Figure 5(Note 9)                                                        | • | 60      |         |          | ns       |

| t <sub>5</sub>        | Data Clock to SDAOUT Valid                                | Figure 5(Note 9)                                                        | • |         |         | 130      | ns       |

| t <sub>6</sub>        | Data Set-Up Time                                          | Figure 5(Note 9)                                                        | • | 80      |         |          | ns       |

| t <sub>7</sub>        | Start Set-Up Time                                         | Figure 5(Note 9)                                                        | • | 240     |         |          | ns       |

| t <sub>8</sub>        | Stop Set-Up Time                                          | Figure 5(Note 9)                                                        | • | 240     |         |          | ns       |

| t <sub>r</sub>        | SCL, SDAIN Rise Time                                      | Figure 5(Note 9)                                                        | • |         |         | 120      | ns       |

| t <sub>f</sub>        | SCL, SDAIN Fall Time                                      | Figure 5(Note 9)                                                        | • |         |         | 60       | ns       |

|                       | Fault Present to INT Pin Low                              | (Notes 9, 10)                                                           | • |         |         | 150      | ns       |

|                       | Stop Condition to INT Pin Low                             | (Notes 9, 10)                                                           | • |         |         | 1.5      | μs       |

●は全動作温度範囲での規格値を意味する。それ以外はT<sub>A</sub> = 25°Cでの値。注記がない限り、AGNDP - V<sub>EE</sub> = 54VおよびV<sub>DD</sub> - DGND = 3.3V (Notes3 および 4)。

| SYMBOL | PARAMETER                | CONDITIONS |   | MIN | TYP | MAX | UNITS |

|--------|--------------------------|------------|---|-----|-----|-----|-------|

|        | ARA to INT Pin High Time | (Note 9)   | • |     |     | 1.5 | μѕ    |

|        | SCL Fall to ACK Low      | (Note 9)   | • |     |     | 130 | ns    |

Note 1: 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。また、 $(V_{DD}$  – DGND) を除き、長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える恐れがある。

Note 2: このデバイスには、短時間の過負荷状態の間デバイスを保護するための過熱保護機能が備わっている。過熱保護機能がアクティブなときジャンクション温度は140°Cを超える。規定された最大動作ジャンクション温度を超えた状態で動作が継続すると、デバイスの信頼性を損なう恐れがある。

Note 3: デバイスのピンに流れ込む電流は全て正。デバイスのピンから流れ出す電流は全て色

**Note 4:** LTC4292は(AGNDPを基準にして)負電源電圧で動作する。混乱を避けるため、このデータシートの電圧は絶対値を単位としている。

Note 5:t<sub>DIS</sub>はIEEE 802.3で定義されたt<sub>MPDO</sub>と同じ。

**Note 6:**LTC4291-1 デジタル・インターフェースは DGND を基準にして動作する。全てのロジック・レベルは DGND を基準に測定される。

Note 7: 設計上の性能は確保されているが、テストされない。

Note 8: IEEE 802.3 規格では、PDを切り離すことなく、PDがその Maintain Power Signature (MPS)を断続的に出力できる。電力供給を受け続けるには、PDは t<sub>MPD0</sub> の時間範囲内で t<sub>MPS</sub> の間 MPS を出力する必要がある。

Note 9: V<sub>ILD</sub> および V<sub>IHD</sub> で測定した値。

Note 10:  $I^2$ Cトランザクション中に障害状態が発生した場合、 $I^2$ Cバスに停止条件が生じるまで $\overline{\text{INT}}$ ピンの電圧は低下しない。

Note 11:マーク時のLTC4292の負荷特性: 7V < (AGNDP – V<sub>OUTnM</sub>) < 10V or I<sub>OUTnM</sub> < 50μA。

**Note 12:** シリアル・バスの使用法、デバイスの設定、およびステータス・レジスタについては、LTC4291 Software Programming 技術文書を参照。

Note 13: CAP1 および CAP2 に対しては、電流を流し出すことも流し込むこともしてはならない。

Note 14: シングル・シグネチャPDの場合、 $t_{PON}$ は、一方のパワー・チャンネルでの有効な検出の終了時から測定される。 デュアル・シグネチャPDの場合、 $t_{PON}$ は、同じパワー・チャンネルでの有効な検出の終了時から測定される。

Note 15: ポート電流とポート電力の測定値は、検出抵抗の値 (代表値:  $0.15\Omega$ )により異なる。詳細については、外付け部品の選択を参照。

Note 16: パワー・チャンネルごとのフルスケール・レンジは、ポートのフルスケール・レンジの半分。

Note 17: 突入電流閾値の選択については、突入電流の制御を参照。

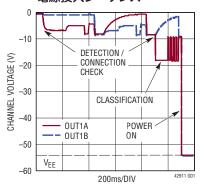

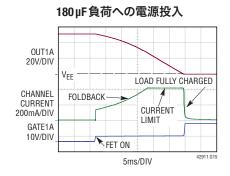

# 代表的な性能特性

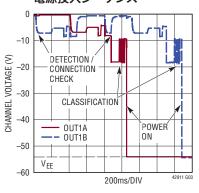

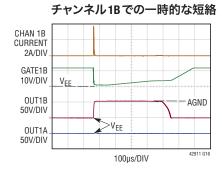

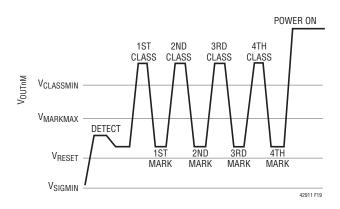

802.3btシングル・シグネチャの 電源投入シーケンス

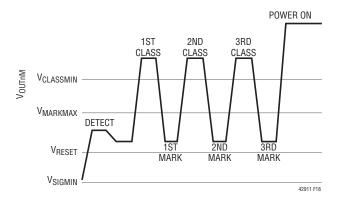

802.3btシングル・シグネチャの 分類と電源投入

802.3bt デュアル・シグネチャの 電源投入シーケンス

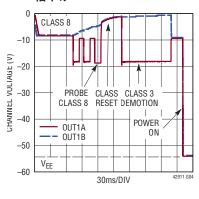

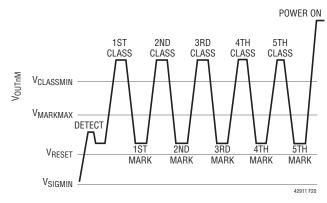

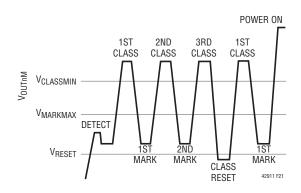

802.3btシングル・シグネチャの クラス・プローブおよびクラス 格下げ

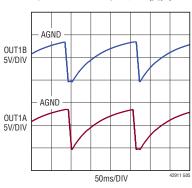

オープン・サーキットの検出

分類電流のコンプライアンス

電源投入時の電流制限シングル・シグネチャ

電源投入時の電流制限 デュアル・シグネチャ

突入電流の制限(Note 17)

Rev 0

8

詳細:www.analog.com

# 代表的な性能特性

電流読出しADCと温度

2456

2451

2446

2441

3 2436

2421

2416

2411

2416

2411

20 40

TEMPERATURE (°C)

2406

-40 -20

80 100

42911 G12

Rev 0

9

# 代表的な性能特性

# テストのタイミング図

図1. 自動モードまたは半自動モードでの検出、分類、ターンオンのタイミング

10

詳細:www.analog.com

# テストのタイミング図

図2. 電流制限のタイミング

図3.DC切り離しのタイミング

図4. シャットダウン遅延のタイミング

図5. I<sup>2</sup>Cインターフェースのタイミング

# I<sup>2</sup>Cタイミング図

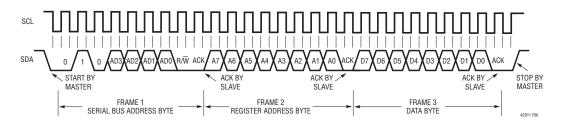

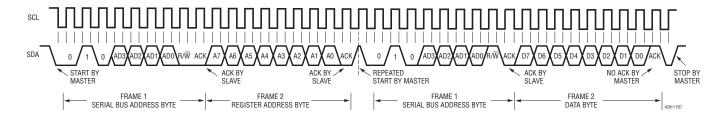

図6. レジスタへの書込み

図7. レジスタからの読出し

図8.割込みレジスタからの読出し(省略形式)

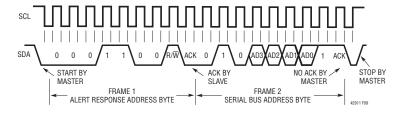

図9. アラート応答アドレスからの読出し

Rev 0

12

## ピン機能

#### LTC4292

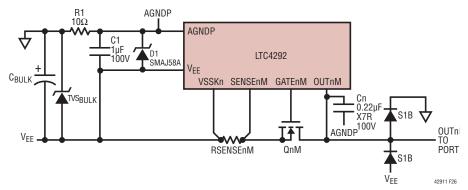

**V<sub>EE</sub>(ピン31、33、40、露出パッド・ピン41):**PoEの主電源入力。AGNDPを基準にして-51V~-57Vの電源に接続します。電圧はPSEタイプ(タイプ3または4)により異なります。

GATEnM(ピン1、3、7、9、22、24、28、30): ゲート駆動、ポートn、チャンネルM。GATEnMは、ポートn、チャンネルMの外付けMOSFETのゲートに接続します。MOSFETがオンすると、ゲート電圧は $V_{EE}$ より12V(代表値)高い電圧まで上昇します。電流制限状態の間は、GATEnMの電圧が減少して、外付けMOSFETに一定の電流が流れるよう維持します。障害タイマーの期限が切れると、GATEnMはローになり、MOSFETをオフにして、ポートnの障害イベントを生成します。チャンネルを使用しない場合は、該当のGATEnMピンをフロート状態にする必要があります。

OUTnM(ピン2、4、8、10、21、23、27、29):出力電圧モニタ、ポートn、チャンネルM。OUTnMは出力チャンネルに接続します。ドレイン/ソース間電圧が10Vを超えると、電流制限フォールドバック回路は、電流制限閾値を低くすることによって外付けMOSFETの消費電力を制限します。OUTnMからVEEまでの電圧が2.4V(代表値)より小さくなると、ポートnのパワーグッド・イベントが生成されます。チャンネルがアイドル状態のときは、OUTnMとAGNDPの間に内部で500kの抵抗が接続されます。チャンネルを使用しない場合は、該当のOUTnMピンをフロート状態にする必要があります。

**CAP2(ピン6)**: 4.3V の内部アナログ電源のバイパス・コンデンサ。 $V_{EE}$ との間に $0.22\mu$ Fのセラミック・コンデンサを接続します。

PWRMDn(ピン11、20):最大電力モードの入力。 $V_{EE} \sim V_{EE} + 4.3 \text{V}$  の範囲のロジック入力信号で、自動モードでの最大出力電力をポートごとに設定するために使用します。自動モードでのPSEの最大電力のセクションを参照してください。内部でCAP2にプルアップされています。

SENSEnM(ピン12、13、14、15、16、17、18、19):電流検出入力、ポートn、チャンネルM。SENSEnMは、SENSEnMは、SENSEnMとVSSKnの間にある $0.15\Omega$ の検出抵抗を介して外付けMOSFETの電流をモニタします。検出抵抗両端の電圧が過電流検出閾値 $V_{CUT-2P}$ を超えると、電流制限障害タイマーが計数します。検出抵抗両端の電圧が電流制限閾値 $V_{LIM-2P}$ に達すると、GATEnMピンの電圧が低下して、外付けMOSFETを流れる電流を一定に維持します。詳細については、アプリケーション情報を参照してください。チャンネルを使用しない場合は、該当のSENSEnMピンを $V_{EE}$ に接続する必要があります。

**AGNDP(ピン25)**: アナログ・グラウンド。 AGNDPは、 $10\Omega$ の 抵抗を介して $V_{EE}$ 電源の帰還路に接続します。

**DNA(ピン36)**: データ・トランシーバーの負の入出力(アナログ)。 データ・トランスを介して DND に接続します。

**DPA(ピン37)**: データ・トランシーバーの正の入出力(アナログ)。 データ・トランスを介してDPDに接続します。

**CNA(ピン38)**: クロック・トランシーバーの負の入出力(アナログ)。 データ・トランスを介して CND に接続します。

**CPA(ピン39)**: クロック・トランシーバーの正の入出力(アナログ)。 データ・トランスを介して CPD に接続します。

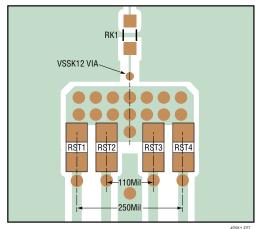

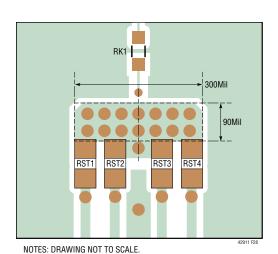

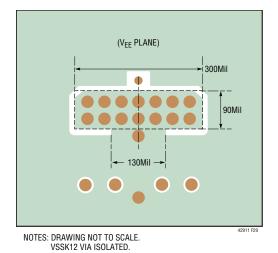

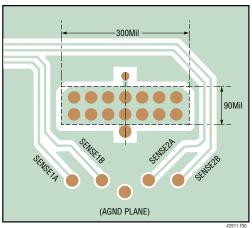

**VSSK12(ピン5)**:  $V_{EE}$ のケルビン検出ピン。ポート1および2の検出抵抗共通ノードに0.15 $\Omega$ の抵抗を介して接続します。0.22 $\mu$ F、100Vのコンデンサを介してAGNDPに接続します。 $V_{EE}$ プレーンには直接接続しないでください。レイアウト条件を参照してください。

**VSSK34(ピン26)**:  $V_{EE}$ のケルビン・センス。ポート3および4の検出抵抗共通ノードに0.15 $\Omega$ の抵抗を介して接続します。0.22  $\mu$ F、100Vのコンデンサを介してAGNDPに接続します。 $V_{EE}$ プレーンには直接接続しないでください。レイアウト条件を参照してください。

#### 共通ピン

**NC、DNC (LTC4291-1はピン7、13。LTC4292はピン32、34、35):**「NC」または「DNC」で識別される全てのピンは、未接続のままにしておく必要があります。

#### LTC4291-1

**AD0(ピン1)**: アドレス・ビット0。アドレス・ピンをハイまたはローに接続して、LTC4291-1の応答先にする $I^2$ Cシリアル・アドレスを設定します。アドレスは( $010A_3A_2A_1A_0$ )bになります。内部で $V_{DD}$ にプルアップされています。

AD1(ピン2):アドレス・ビット1。AD0を参照してください。

AD2(ピン3):アドレス・ビット2。AD0を参照してください。

AD3(ピン4):アドレス・ビット3。AD0を参照してください。

**4PVALID**(ピン6):4対の有効入力、アクティブ・ロー。ローの場合、両方のペアセットが有効なシグネチャを示さない限り、LTC4291-1/LTC4292はポートに電力を供給しません。ハイの場合、LTC4291-1/LTC4292は他のペアセットに関係なく、有効なシグネチャを示すどのペアセットにも電力を供給します。内部でDGNDにプルダウンされています。

# ピン機能

**CPD(ピン8)**:クロック・トランシーバーの正の入出力(デジタル)。データ・トランスを介して CPA に接続します。

**CND(ピン9)**: クロック・トランシーバーの負の入出力(デジタル)。 データ・トランスを介して CNA に接続します。

**DPD(ピン10)**: データ・トランシーバーの正の入出力(デジタル)。 データ・トランスを介して DPA に接続します。

**DND(ピン11)**: データ・トランシーバーの負の入出力(デジタル)。 データ・トランスを介して DNA に接続します。

$V_{DD}$ (ピン12、20):  $V_{DD}$  IOの電源電圧。 DGNDを基準にして 3.3Vの電源に接続します。 LTC4291-1の近くに $0.1\mu$ F以上の コンデンサを接続して、 $V_{DD}$ をDGNDにバイパスする必要が あります。

RESET (ピン14): リセット入力、アクティブ・ロー。RESET をローにすると、LTC4291-1/LTC4292 は、全てのポートがオフになり、全ての内部レジスタがリセットされた不動作状態に保持されます。RESETをハイにすると、LTC4291-1/LTC4292は通常動作を開始します。RESET は外付けコンデンサまたはRCネットワークに接続して、ターンオン遅延を設けることができます。RESETの内部フィルタリングにより、幅が1 $\mu$ sより短いグリッチでLTC4291-1/LTC4292がリセットされることはありません。内部で $V_{DD}$ にプルアップされています。

$\overline{\text{INT}}$ (ピン15):割込み出力、オープンドレイン。LTC4291-1でいくつかのイベントのいずれかが発生すると、 $\overline{\text{INT}}$  はローになります。Reset PB レジスタ(1Ah)でビット6または7を設定すると、このピンは高インピーダンスに戻ります。 $\overline{\text{INT}}$  信号を使用してホスト・プロセッサに対する割込みを発生させ、連続したソフトウェア・ポーリングを不要にすることができます。個々の $\overline{\text{INT}}$  イベントは、 $\overline{\text{INT}}$  Mask レジスタ(01h)を使用して無効化できます。詳細については、LTC4291 Software Programming技術文書を参照してください。 $\overline{\text{INT}}$ が更新されるのは、 $\Gamma^2$ Cトランザクション間だけです。

**SDAOUT (ピン16)**: シリアル・データ出力、 $I^2$ Cシリアル・インターフェース・バスのオープンドレイン・データ出力。 LTC4291-1は2つのピンを使用して双方向 SDA機能を実行し、 $I^2$ Cバスの光絶縁を簡略化します。標準的な双方向 SDAピンを実装するには、SDAOUT と SDAINを互いに接続します。詳細については、アプリケーション情報を参照してください。 SDAIN (ピン17): シリアル・データ入力。 $I^2$ Cシリアル・インターフェース・バスの高インピーダンス・データ出力。LTC4291-1は2つのピンを使用して双方向 SDA 機能を実装し、 $I^2$ Cバスの光絶縁を簡略化します。標準的な双方向 SDA ピンを実装するには、SDAOUT と SDAIN を互いに接続します。詳細については、アプリケーション情報を参照してください。

**SCL(ピン18)**:シリアル・クロック入力。 $I^2$ Cシリアル・インターフェース・バスの高インピーダンス・クロック入力。SCLピンは、 $I^2$ C SCLバス・ラインに直接接続します。 $I^2$ Cシリアル・インターフェース・バスを使用しない場合は、SCLをハイに接続する必要があります。

**CAP1(ピン19)**:コア電源のバイパス・コンデンサ。1.8Vの内部レギュレータのバイパス・コンデンサとして1μFの容量をDGNDとの間に接続します。コンデンサに他の値は使用しないでください。

AUTO(ピン21):自動モード入力、アクティブ・ハイ。ハイの場合、LTC4291-1は有効なPDの検出、分類、および起動を、ホストと対話せずに実行します。AUTOは、LTC4291-1がリセットされるか、UVLO状態から抜け出したときに、内部レジスタの状態を判別します(LTC4291 Software Programming 技術文書を参照)。これらのレジスタ・ビットの状態は、I<sup>2</sup>Cインターフェースを介して後で変更できます。内部でDGNDにプルダウンされています。

**GP1(ピン22)**: お客様のアプリケーション用の汎用デジタル入出力。DGNDを基準にしています。

**GPO(ピン23)**: お客様のアプリケーション用の汎用デジタル入出力。DGNDを基準にしています。

MSD (ピン24): マスク可能なシャットダウン入力、アクティブ・ロー。ローにすると、対応するマスク・ビットがmconfレジスタ(17h)に設定されている全てのポートがリセットされます。 $\overline{MSD}$ ピンの内部フィルタリングにより、幅が1 $\mu$ sより短いグリッチでポートがリセットされることはありません。MSDPin Modeレジスタは、 $\overline{MSD}$ ピンの極性を設定できます。内部で $V_{DD}$ にプルアップされています。

**DGND(ピン5、露出パッドのピン25)**: デジタル・グラウンド。 DGNDはV<sub>DD</sub>電源からの帰還路に接続してください。

#### 概要

Power over Ethernet (PoE)は、銅線のイーサネット・データ配線を介してDC電力を送信する標準プロトコルです。802.3 イーサネット・データ規格を管理しているIEEEグループは、PoE給電機能を2003年に追加しました。この最初のPoE規格は802.3afとして知られ、最大13Wで48VのDC電力が可能でした。802.3afは広く普及していましたが、13Wはアプリケーションによっては十分ではありませんでした。2009年に、IEEEは802.3at (PoE+)として知られる新規格を公開し、電圧と電流の条件を高めて25.5Wの供給電力を規定しました。

また、IEEE規格では、PoEの用語も定義しています。ネットワークに電力を供給するデバイスは給電装置(PSE)として知られるのに対して、ネットワークから電力を引き出すデバイスは受電装置(PD)として知られます。PSEには次の2種類があります。1つはエンドポイント(代表的なのはネットワーク・スイッチやルーター)で、データと電力を供給します。もう1つはミッドスパンで、電力は供給しますが、データは通り抜けます。ミッドスパンは、通常は既存の非PoEネットワークにPoE機能を追加する目的で使用されます。PDの代表的なデバイスは、IP電話、無線アクセス・ポイント、防犯カメラなどです。

### PoE++の進化

IEEE 802.3at (PoE+)の25.5W 規格の策定中ですら、25.5W を超える供給電力を求める声が高まりつつあることが明らかになっていました。2013年には、増大しているPD供給電力に対応できる標準を策定するための802.3btタスク・フォースが結成されました。

タスク・フォースの主な目的は、802.3atで利用されている2対の電源に相対するものとして、4対のイーサネット・ケーブル全てを使用することです。4対全部を使用することにより、既存のイーサネット・ケーブルを介した供給電力の2倍以上が対応可能になります。更に、(ペアセットとして知られる)2対当たりの電流量が増加しながら、イーサネットのデータ信号の完全性は維持されます。802.3btでは、PD供給電力が25.5Wから71.3Wに増加し、IEEE準拠の大電力PDアプリケーションが可能になります。

LTC4291-1/LTC4292は、2つのパワー・チャンネルを介して電力を供給します。各ペアセットは専用のパワー・チャンネルにより駆動されます。このデータシートでは、「チャンネル」という用語は、対応するペアセットに割り当てられたPSE回路のことを指します。この技術文書の目的から、チャンネルとペアセットという用語は互いに交換できるとみなしてかまいません。

加えて、IEEE 802.3btではMaintain Power Signature (MPS) 電流を大幅に低減できるので、待機時の消費電力は大幅に減少します。これにより、政府や産業界の新たな待機電力規制を、標準的なPoE部品を使用して満たすことができます。

#### LTC4291-1/LTC4292の製品概要

LTC4291-1/LTC4292は第5世代のPSEコントローラで、エンドポイント・アプリケーションまたはミッドスパン・アプリケーションで4つのPSEポートを実装します。IEEE 802.3bt 準拠のPSE設計を実装するために必要な全ての回路を実質的に内蔵しており、必要なのは、1ポートにつき1対の外付けパワーMOSFETと検出抵抗だけです。これにより、MOSFET内蔵型の代替設計案と比較して電力損失が最小限に抑えられ、システムの信頼性が向上します。

LTC4291-1/LTC4292チップセットでは、チップ間通信に独自の絶縁方式を実装しています。このアーキテクチャでは、費用のかかる光アイソレータや絶縁電源を1個の低価格トランスで置き換えることにより、部品の費用が大幅に削減されます。

LTC4291-1/LTC4292は、先進の第5世代PSE機能を備えています。この機能は、ポートごとのイベントでトリガされる設定可能な割込み信号、チャンネルごとの電源投入制御と障害遠隔測定、ポートごとの電流モニタリング、VEEのモニタリング、1秒の回転電流、電圧、ポート電力の平均化、2つの汎用入出力ピンなどです。

VEEとポート電流の測定は同時に行われ、完全にコヒーレントなポート電力計算を実現します。報告されるポート電力計算により、コヒーレントで高精度なポートごとの電力モニタリングが可能です。

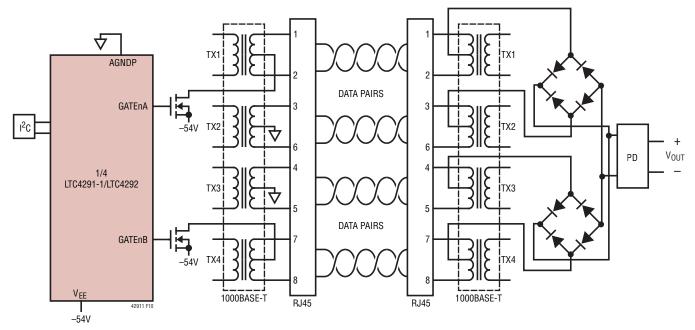

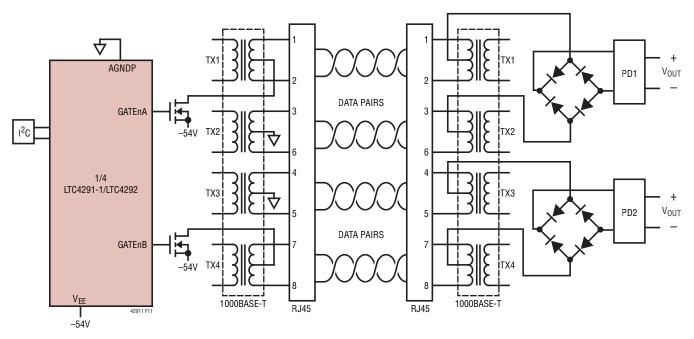

#### PoEの基礎

一般的なイーサネット・データ接続は、2本または4本のツイスト・ペア銅線(通称イーサネット・ケーブル)で構成され、それぞれの端をトランスで結合してグラウンド・ループを防止しています。PoEシステムは、この結合配置を利用して、データ・トランスのセンター・タップ間に電圧を加えることにより、データ伝送に影響することなく、PSEからPDへ電力を伝送します。PoEシステムの概略回路図を図10および11に示します。

DC電圧の印加を想定していない旧式のデータ装置が損傷しないように、PoE 規格では、PSEによる電源の投入および遮断が可能かどうかを判別するプロトコルを規定しています。有効なPDは、その入力に特定の25kコモンモード抵抗が必要です。こうしたPDをケーブルに接続すると、PSEはこのシグネチャ抵抗を検出して、電源を投入します。その後、PDを切り離すと、PSEはオープン・サーキットを検出して、電源を遮断します。また、PSEは電流障害や短絡が発生した場合にも電源を遮断します。

PDが検出されると、PSEは、PDで消費する最大電力をPSE に通知する分類シグネチャを探します。PSEはこの情報を使用していくつかのポートに電力を割り振るか、PDの消費電流を規制するか、PSEが供給できる電力より多くの電力を消費するPDを拒否します。

#### 802.3btの新機能

802.3btのドラフトでは、次に示すいくつかの新機能を導入しています。

- タイプ3およびタイプ4のPSEは、接続されているPDの特性に応じて、4対全部(両方のペアセット)を介して電力を供給できます。

- タイプ3およびタイプ4のPDは、4対全部(両方のペアセット)を介して電力を受け取ることができる必要があります。

- タイプ3およびタイプ4のPDは、シングル・シグネチャPD またはデュアル・シグネチャPDとして構成できます。シン グル・シグネチャPDは、有効な同じシグネチャ抵抗を両 方のペアセットに対して同時に示します。デュアル・シグネ チャPDは、完全に独立した2つの有効な検出シグネチャ を、各ペアセットに対して1つ示します。

- タイプ3のシングル・シグネチャPDは、次の6種類の電力 レベル(3.84W、6.49W、13W、25.5W、40W、51W)のいず れか1種類を厳密に要求します。

- タイプ3のデュアル・シグネチャPDは、各ペアセットで次の 4種類の電力レベル(3.84W、6.49W、13W、25.5W)のい ずれか1種類を厳密に要求します。PDの全要求電力は、 各ペアセットでの要求電力の合計です。

- タイプ3のPDクラスは、タイプ3の追加機能セットをより 低い電力レベルで提供するために、タイプ1および2のク ラスと重複します。

- タイプ4のシングル・シグネチャPDは、次の2種類の電力 レベル(62Wまたは71.3W)のいずれかを厳密に要求し ます。

- タイプ4のデュアル・シグネチャPDは、少なくとも一方のペアセットで厳密に35.6Wを要求し、もう一方のペアセットで次の5種類の電力レベル(3.84W、6.49W、13W、25.5W、35.6W)のいずれかを厳密に要求します。PDの全要求電力は、各ペアセットでの要求電力の合計です。

- 分類は、最大5つのクラス・イベントに拡張されます。 追加 イベントは、既存のPDクラスと新しいPDクラスを一意に 識別できます。

- タイプ3と4のPSEは、長い最初のクラス・イベントを発行して、タイプ3と4の機能サポートを接続先のPDに通知します。

- 少ない待機電力を有効にするには、Maintain Power Signatureパルスの長さを短くします(短縮MPS)。PDのデューティ・サイクルは約23%から約2%に低下します。PSEが長い最初のクラス・イベントを発行した場合、PDは短縮MPSを出力できます。

- パワー・マネージメントはAutoclass (802.3btのPSEおよびPD向けのオプション機能)によって強化されます。 Autoclassシステムでは、PDの最大電力が測定されてPSEホストに報告され、PDアプリケーションで使用されなかった出力電圧とイーサネット・ケーブル配線での損失をPSEが取り戻すことができます(表1)。詳細については、Autoclassのセクションと、LTC4291 Software Programming 技術文書を参照してください。

Rev 0

16

詳細:www.analog.com

図10. Power over Ethernet シングル・シグネチャ PD システムの回路図

図11. Power over Ethernet デュアル・シグネチャPD システムの回路図

表 1. IEEE が仕様化した電力の割り当て、シングル・シグネチャPD

| PD クラス | PSE の出力電力 | 割り当てられた<br>配線損失 | PDの入力電力 |

|--------|-----------|-----------------|---------|

| 1      | 4W        | 0.16W           | 3.84W   |

| 2      | 6.7W      | 0.21W           | 6.49W   |

| 3      | 14W       | 1W              | 13W     |

| 4      | 30W       | 4.5W            | 25.5W   |

| 5      | 45W       | 5W              | 40W     |

| 6      | 60W       | 9W              | 51W     |

| 7      | 75W       | 13W             | 62W     |

| 8      | 90W       | 18.7W           | 71.3W   |

|        |           |                 |         |

#### 後方互換性

LTC4291-1/LTC4292は、802.3bt 準拠のPSE (タイプ3またはタイプ4)として設定できます。802.3bt PSEは 802.3at タイプ1またはタイプ2 PSEとしては識別できませんが、PSEの機能は失われません。802.3bt 準拠の全てのPSEは、表2に示すように、既存の802.3at タイプ1およびタイプ2 PDと完全に後方互換です。802.3bt PSEは、完全な互換性に加えて、(PDアプリケーションによってサポートされているように)低待機電力、強化された電流制限タイミング機能、全てのPDタイプに対する動的パワー・マネージメントへのサポートが拡張されています。

表2. PSEの最大供給電力、1ポート当たり

| デバイス |         |     | PSE     |        |         |       |  |

|------|---------|-----|---------|--------|---------|-------|--|

|      | 標準規格    |     | 802.3at |        | 802.3bt |       |  |

|      |         | タイプ | 1       | 2      | 3       | 4     |  |

|      | 802.3at | 1   | 13W     | 13W    | 13W     | 13W   |  |

| PD   | 002.381 | 2   | 13W*    | 25.5W  | 25.5W   | 25.5W |  |

| ן אי | 000 06+ | 3   | 13W*    | 25.5W* | 51W     | 51W   |  |

|      | 802.3bt | 4   | 13W*    | 25.5W* | 51W*    | 71.3W |  |

\*PDが要求より少ない電力を割り当てたことを示す。

LTC4266およびLTC4271ベースのPSEとのソフトウェア・レジスタ・マップ互換性は、可能な範囲で維持されています。 LTC4291ベースのPSEは、2チャンネルを使用して1つのPSEポートを制御します。このチャンネル・ステータスと制御の多様性により、既存のレジスタ・マップへの拡張が必要です。

レジスタ・マップの詳細について確認したい場合は、LTC4291 Software Programming 技術文書をアナログ・デバイセズに請求してください。

#### 特殊な互換性モードに関する注記

- 前の世代と同様に、各I<sup>2</sup>Cアドレスは4つのPoEポートに対してステータスと制御を与えます。ポート・レジスタの各スライスは、チャンネルA対Bの制御およびステータスと同様に、ポートの制御およびステータスを与えます。

- 特定のステータス・レジスタ(例えばPort Status やPower Status)は、チャンネルの状態に関係します。これはポート状態とは対照的であり、3つの部分(汎用のポート状態、チャンネルAの状態、チャンネルBの状態)に分かれています。

- 特定のコマンド・レジスタ(例えば、電源投入押しボタン) も同様に、チャンネルごとの制御ができるように2つの部 分に分かれています。

#### 動作モード

LTC4291-1/LTC4292は、独立した4つのポートを内蔵しており、それぞれが3つのモード(手動、半自動、自動)のいずれかで動作できます。4番目のモード(シャットダウン)は、ポートをディスエーブルします(表3参照)。

表3.動作モード

| モード       | AUTO<br>ピン | OPMD | 検出/<br>分類               | 起動            | 閾値の<br>自動割り当て |

|-----------|------------|------|-------------------------|---------------|---------------|

| Auto      | 1          | 11b  | Enabled<br>at Reset     | Automatically | Yes           |

| Auto      | 0          | 11b  | Host<br>Enabled         | Automatically | Yes           |

| Semi-auto | 0          | 10b  | Host<br>Enabled         | Upon Request  | No            |

| Manual    | 0          | 01b  | Once<br>Upon<br>Request | Upon Request  | No            |

| Shutdown  | 0          | 00b  | Disabled                | Disabled      | No            |

手動モードでは、ポートはホスト・システムからの命令を待ってから動作します。ポートは、ホストによって命令されると、検出(検出と分類のサイクル)を1回実行し、その結果をPort Statusレジスタで報告します。ホスト・システムは電源の投入または遮断をポートにいつでも命令できます。

半自動モードでは、ポートは、接続されている全てのPDの検出と分類を繰り返し試行します。ポートはこれらの試行のステータスをホストに報告し、ホストからの命令を待ってからポートに電源を投入します。ホストは検出と分類を有効にする必要があります。

自動モードは半自動モードと同じ動作ですが、検出と分類が正常だった場合にポートの電源を自動的に投入することだけが異なります。自動モードでは、ICUT-2P、ILIM-2P、PCUT-4Pの値が分類結果に基づいて自律的に設定されます。この動作モードにするには、リセット時にAUTOをハイに設定するか、OPMDの状態をAutoに変更します。自動モードでのPSEの最大電力のセクションを参照してください。

シャットダウン・モードでは、ポートはディスエーブルされ、 PDの検出も電源投入も行いません。

LTC4291-1/LTC4292は、現在のモードに関係なく、障害が発生したポートあるいはチャンネルの電源を、必要に応じて自動的に遮断します。また、切り離しの検出が有効になっている場合、切り離しイベントが発生したポート/チャンネルの電源も自動的に遮断します。また、ホスト・コントローラは電源の遮断をポートにいつでも命令できます。

#### リセットとAUTOピン

LTC4291-1/LTC4292の初期設定は、リセット時のAUTOの 状態により異なります。リセットが行われるのは、電源投入 時、RESETをローにしたとき、またはグローバルのReset All ビットを設定したときです。電源投入後にAUTOの状態を変 更しても、リセットが実行されるまでLTC4291-1/LTC4292の ポートの動作は変わりません。

LTC4291-1/LTC4292は、通常はホスト・コントローラによって能動的に管理されていますが、AUTOをハイに設定すれば、自律動作に合わせて設定することもできます。AUTOをハイにした場合、各ポートは、PDが検出されるまで検出と分類を繰り返し実行し、PSEが割り当てたクラスに従ってICUT-2P、ILIM-2P、およびPCUT-4Pを設定し、有効なPDに電源を供給して、PDが切り離されたら電源を遮断します。

PDが要求したクラスに基づいて、自動モードで自動的に設定される $I_{\text{CUT-2P}}$ 、 $I_{\text{LIM-2P}}$ 、および $P_{\text{CUT-4P}}$ の値を表4と5に示します。

表 4. 自動モードでの代表的な電源投入閾値、シングル・ シグネチャ PD

|     | チャンネ                | チャンネル当たり            |                     |  |  |

|-----|---------------------|---------------------|---------------------|--|--|

| クラス | I <sub>CUT-2P</sub> | I <sub>LIM-2P</sub> | P <sub>CUT-4P</sub> |  |  |

| 1   | 94mA                | 425mA               | 5.43W               |  |  |

| 2   | 150mA               | 425mA               | 8.69W               |  |  |

| 3   | 338mA               | 425mA               | 19.5W               |  |  |

| 4   | 638mA               | 850mA               | 36.4W               |  |  |

| 5   | 581mA               | 850mA               | 52.7W               |  |  |

| 6   | 731mA               | 850mA               | 70.0W               |  |  |

| 7   | 825mA               | 1063mA              | 87.4W               |  |  |

| 8   | 975mA               | 1167mA              | 96.6W               |  |  |

#### 表 5. 自動モードでの代表的な電源投入閾値、デュアル・ シグネチャ PD

|     | チャンネル当たり            |                     |                       |  |  |  |  |

|-----|---------------------|---------------------|-----------------------|--|--|--|--|

| クラス | I <sub>CUT-2P</sub> | I <sub>LIM-2P</sub> | P <sub>CUT-2P</sub> * |  |  |  |  |

| 1   | 94mA                | 425mA               | 5.43W                 |  |  |  |  |

| 2   | 150mA               | 425mA               | 8.69W                 |  |  |  |  |

| 3   | 338mA               | 425mA               | 19.5W                 |  |  |  |  |

| 4   | 638mA               | 850mA               | 36.4W                 |  |  |  |  |

| 5   | 975mA               | 1167mA              | 48.3W                 |  |  |  |  |

\*ポート当たりの $P_{CIIT-4P}$ 閾値には、各受電チャンネルの $P_{CIIT-2P}$ の合計が入ります。

#### 接続チェック

#### 接続チェックの概要

IEEE 802.3btは、接続チェックとして知られる新しい検出サブルーチンを導入しています。接続チェックが必要なのは、接続したPDがシングル・シグネチャPDなのか、デュアル・シグネチャPDなのか、あるいは無効な結果なのかを判定するためです。

802.3atでは、1つのPD構成だけが記述されていました。これはシングル・シグネチャPDとして知られており、図10に示します。シングル・シグネチャPDは、同じ25kの検出抵抗を両方のペアセットに対して並列に示します。

802.3btでの新項目は、図11に示すようにデュアル・シグネチャPDです。デュアル・シグネチャPDは、完全に独立した2つの25k検出シグネチャ抵抗を、各ペアセットに対して1つ示します。

PDの構成(シングルまたはデュアル)によって、それに続く検出、分類、電源投入の手順の間にPDがどのように管理されるかが決まります。このデータシートの残り全体を通して、シングル・シグネチャPDとデュアル・シグネチャPDの扱い方が異なることに対して注意が喚起されます。

最初のチャンネルでは、2回の電流測定を同じ強制電圧で行うことによって接続チェックを実施します。2番目のチャンネルでは、2回目の測定時に2番目のチャンネルに強制電流を流すことによって、アグレッサの動作がテストされます。最初のチャンネルでの2回の電流測定結果を比較することで、接続されたデバイスがシングル・シグネチャPDなのか、デュアル・シグネチャPDなのか、あるいは無効な結果なのかを分類できます。

接続チェック中にデバイスの追加や削除を行うと、無効な接続チェック結果が報告されます。

#### 検出

#### 検出の概要

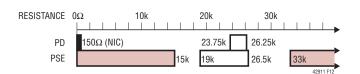

DC電圧に耐えるよう設計されていなかったネットワーク・デバイスの損傷を防ぐため、PSEは接続されたデバイスが有効なPDであることを確認してから電力を供給する必要があります。IEEE規格では、チャンネルの電圧が10V未満の条件で、有効なPDは25k±5%のコモンモード抵抗を内蔵していることが要求されます。PSEは19k~26.5kの範囲内の抵抗を合格とし、33kを超える抵抗または15k未満の抵抗(図12の網掛け領域)を不合格にする必要があります。PSEは、必須合格範囲と必須不合格範囲の間の未定義領域の抵抗を合格にするか不合格にするか選択できます。特に、PSEはコンピュータの標準的なネットワーク・インターフェース・カード(NIC)を不合格にする必要があります。これらの多くは、コモンモード終端抵抗が150Ωであり、電源が投入されると損傷します(図12の左側の黒の領域)。

図12. IEEE 802.3のシグネチャ抵抗の範囲

#### マルチポイント検出

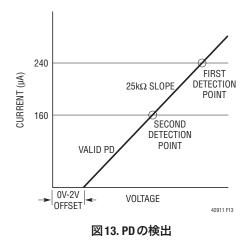

LTC4291-1/LTC4292 は、マルチポイント方式を使用してPDを検出します。強制電流測定と強制電圧測定を併用してシグネチャ抵抗をチェックすることで、誤判定検出を最小限に抑えます。

最初に、2種類のテスト電流を(OUTnMピンを介して)チャ ンネルに強制的に流し、得られた電圧を測定します。検出回 路は2つのV-I点の差をとって抵抗の傾きを求めつつ、ポー トのリーク電流や直列ダイオードに起因するオフセットを除 去します(図13参照)。強制電流検出によって有効なシグネ チャ抵抗が得られる場合は、2種類のテスト電圧をチャンネ ルに印加し、得られた電流を測定して差をとります。有効な 検出を報告するには、両方の方法で有効な抵抗が報告され る必要があります。PDシグネチャ抵抗が17k~29k(代表値) の範囲内であれば有効と検出され、対応するPort Status レ ジスタまたはChannel Statusレジスタで、適宜Detect Goodと 報告されます。また、オープン・サーキットや短絡など、この 節囲外の値も報告されます。強制電流テスト時にチャンネル が1Vより低い値を測定すると、検出サイクルはアボートして Short Circuitが報告されます。起こり得る検出結果を表6お よび7に示します。

Rev 0

#### 表 6. ポートの検出ステータス

| PDシグネチャの測定結果<br>(代表値)                                          | ポート検出結果                           |

|----------------------------------------------------------------|-----------------------------------|

| Incomplete or Not Yet Tested                                   | Detect Status Unknown             |

| V <sub>PD</sub> < 1V                                           | Short Circuit                     |

| R <sub>PD</sub> < 17k                                          | R <sub>SIG</sub> Too Low          |

| 17k < R <sub>PD</sub> < 29k                                    | Detect Good, Single-Signature PD  |

| $R_{PD} > 29k$                                                 | R <sub>SIG</sub> Too High         |

| R <sub>PD</sub> > 50k                                          | Open Circuit                      |

| V <sub>PD</sub> > 10V                                          | Port Voltage Outside Detect Range |

| Connection Check = INVALID                                     | Connection Check Invalid          |

| Connection Check = DUAL or<br>Channel Detection Results Differ | Refer to Channel Detect Results   |

#### 表7. チャンネルの検出ステータス

| PDシグネチャの測定結果<br>(代表値)                                           | チャンネル検出結果                            |

|-----------------------------------------------------------------|--------------------------------------|

| Incomplete or Not Yet Tested                                    | Detect Status Unknown                |

| V <sub>PD</sub> < 1V                                            | Short Circuit                        |

| $C_{PD} > 2.7 \mu\text{F}$                                      | C <sub>PD</sub> Too High             |

| R <sub>PD</sub> < 17k                                           | R <sub>SIG</sub> Too Low             |

| 17k < R <sub>PD</sub> < 29k                                     | Detect Good, Dual-Signature PD       |

| R <sub>PD</sub> > 29k                                           | R <sub>SIG</sub> Too High            |

| R <sub>PD</sub> > 50k                                           | Open Circuit                         |

| V <sub>PD</sub> > 10V                                           | Channel Voltage Outside Detect Range |

| Connection Check = INVALID                                      | Connection Check Invalid             |

| Connection Check = SINGLE or<br>Channel Detection Results Match | Refer to Port Detect Result          |

#### 動作モードに関するその他の情報

LTC4291-1/LTC4292が検出サイクルを実行するタイミングは、ポートの動作モードによって決まります。手動モードでは、ホストが検出サイクルを命令するまでポートはアイドル状態になります。その後、ポートは検出を実行し、結果を報告して、アイドル状態に戻って別のコマンドを待ちます。

半自動モードでは、LTC4291-1/LTC4292はポートを自律的にポーリングしてPDを探しますが、ホストが命令するまで電力は供給しません。各検出/分類サイクルの最後に、Port Statusレジスタど Channel Statusレジスタが更新されます。

半自動モードでは、有効なシグネチャ抵抗が検出されて分類が有効になると、ポートはPDも分類して、その結果を報告します。その後、ポートは100ms以上待機し、検出サイクル

を繰り返して、Port Statusレジスタ内にあるデータを更新します。

電流検出結果がDetect Goodでない限り、ポートが電源投入コマンドに応じてオンすることはありません。それ以外の検出結果では、電源投入コマンドを受け取ると、tstart障害が発生します。

自動モードでの動作は半自動モードと同様です。ただし、Detect Goodが報告されてポートが分類されると、ポートには自動的に電源が投入され、ホストが介入することはありません。自動モードでは、ICUT-2P、ILIM-2P、PCUT-4Pの各閾値が自動的に設定されます。詳細については、リセットとAUTOピンのセクションを参照してください。

ポートの検出が無効になるのは、最初にLTC4291-1/LTC4292の電源を投入するときにAUTOをローに設定していた場合、ポートがシャットダウン・モードである場合、または対応するDetect Enable ビットがクリアされている場合です。

#### レガシーPDの検出

最初のIEEE 802.3af 規格より前から存在する独自開発PDは、現在では一般にレガシーPDと呼ばれています。レガシーPDの1種に、大容量のコモンモード容量(>10 µF)を検出シグネチャとして使用するものがあります。この範囲の容量ではPDが無効と規定されているので、レガシーPDに電力を供給するPSEはIEEE 規格に準拠していないことに注意してください。LTC4291-1/LTC4292は、この種のレガシーPDを検出するよう設定できます。レガシーPDの検出はデフォルトでは無効になっていますが、ポートごとに手動で有効にすることができます。有効にした場合、ポートは、有効なIEEE PDと大容量のレガシーPDのいずれを検出した場合にもDetect Goodを報告します。レガシー・モードを無効にしている場合は、有効なIEEE PDだけが認識されます。

非標準のPDが、レガシー検出に含まれていない無効な検出シグネチャを示した場合は、検出結果に関係なく、分類または電力供給あるいはその両方を実行するようLTC4291-1/LTC4292を設定できます。このため、LTC4291-1/LTC4292は、Force Power と Class Event のポートごとのオーバーライドを導入しています。これらのオーバーライドでは、コンプライアンス・チェックを意図的に無効にしています。詳細については、LTC4291 Software Programming 技術文書を参照してください。

#### 分類

#### 802.3afでの分類

PDは、オプションで分類シグネチャをPSEに示して、動作時に消費する最大電力を通知できます。図15に示すように、IEEE規格では、PSEポートの電圧が $V_{CLASS}$ の範囲 (15.5 $V_{CLASS}$ )内に入っているときに流れる定電流としてこのシグネチャを規定しており、この電流レベルは5種類のPDシグネチャのいずれかを示しています。図14にPDの代表的な負荷線を示します。10V以下での25kシグネチャ抵抗の勾配に始まり、 $V_{CLASS}$ の範囲では分類シグネチャ電流(この場合はクラス3)に遷移します。表8kに、想定される分類の値を示します。

図14. PD の分類

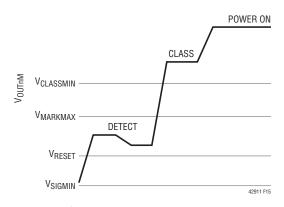

図 15. タイプ 1 PSE、1 イベント・クラスのシーケンス

表8. タイプ1およびタイプ2 PDの分類の値

| クラス     | 結果                                             |

|---------|------------------------------------------------|

| Class 0 | No Class Signature Present; Treat Like Class 3 |

| Class 1 | 3.84W                                          |

| Class 2 | 6.49W                                          |

| Class 3 | 13W                                            |

| Class 4 | 25.5W (Type 2)                                 |

分類が有効になると、PSEは正常な検出サイクルの直後にPDを分類します。PSEは、OUTnMを介してV<sub>CLASS</sub>をポートに印加し、得られた電流を測定することによってPD分類シグネチャを測定します。その後、検出したクラスを、適宜、Port Status レジスタまたは Channel Status レジスタで報告します。LTC4291-1/LTC4292 が自動モードの場合は、分類結果を補足的に使用してI<sub>CUT-2P</sub>、I<sub>LIM-2P</sub>、P<sub>CUT-4P</sub>の閾値を設定します。

ポートの分類が無効になるのは、最初にLTC4291-1/LTC4292の電源を投入するときにAUTOピンをローに設定していた場合、ポートがシャットダウン・モードである場合、または対応するClass Enable ビットがクリアされている場合です。

#### LLDP分類

802.3atで導入され、802.3btで拡張されたPoE規格は、リンク層検出プロトコル(LLDP)分類方式を規定しています。 LLDP方式では、イーサネットLLDPデータ・プロトコルに特別なフィールドを追加しています。

LTC4291-1/LTC4292はこの分類方式との互換性がありますが、データ・パスへのアクセス権がないため、LLDP分類を直接実行することはできません。LLDP分類では、ホストがPDとのLLDP通信を実行して、PDの電力割り当て量を更新できます。LTC4291-1/LTC4292は、I<sub>LIM-2P</sub>、I<sub>CUT-2P</sub>、およびP<sub>CUT-4P</sub>レベルの動的な変更をサポートしており、システムレベルのLLDPサポートが可能です。

#### 802.3atの2イベント分類

802.3atでは、802.3afの分類にタイプ1分類という名前が付いています。802.3at規格では、タイプ1分類の拡張版であるタイプ2(2イベント)分類を導入しています。タイプ2 PSE は、分類を実行することが要求されます。

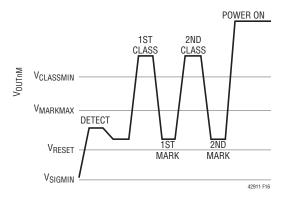

25.5Wを要求しているタイプ2 PDは、全てのクラス・イベント時にクラス・シグネチャ4を示します。供給可能な電力が25.5Wのタイプ2 PSEは、図16に示すように、最初のクラス・イベント時にクラス・シグネチャ4を認識すると、PDにV<sub>MARK</sub>(代表値9V)を印加して、一時的に停止し、2番目のクラス・イベントを発行します。2番目のクラス・イベントは、PSEが25.5Wを割り当てたことをPDに通知します。

図16. タイプ2 PSE、2イベント・クラスのシーケンス

2番目の分類イベントが実行されるのは、IEEE分類手順で必要とされる場合に限ることに注意してください。例えば、クラス0~3のシングル・シグネチャPDに発行されるのは、あらゆる状況でシングル・クラス・イベントのみです。

802.3atでは、格下げの概念が導入されています。タイプ2 PD は、供給能力がわずか13WのPSEに接続できますが、これは恐らくパワー・マネージメント上の制限が原因です。この場合、PSEは、図15に示すように1回の分類イベントを実行し、25.5Wを要求されます。電力供給能力が限られているため、PSEは2番目のイベントを発行せず、PDに直接電力を供給する段階に進みます。1回のクラス・イベントが存在することで、タイプ2 PDが13Wに格下げされていることがこのPDに通知されます。格下げされると、このPDは電力制限を受け、低減された電力モードで動作することがあります。

#### 802.3bt のマルチイベント分類

LTC4291-1/LTC4292は、802.3btで要求されているように、タイプ3分類とタイプ4分類を実装しています。タイプ3分類およびタイプ4分類は、タイプ1 PDおよびタイプ2 PDと後方互換性があります。

タイプ2(802.3at)分類はタイプ1(802.3af)分類を拡張しているのに対して、タイプ3分類とタイプ4(802.3bt)分類はタイプ1分類とタイプ2分類に取って代わるものです。タイプ1分類とタイプ2分類は、これまでのセクションで歴史的な参考情

報として説明しており、電力の格下げ、クラス・イベント、マーク・イベント、電気的パラメータなどの共通用語を定義することが目的でした。

IEEE 802.3btは、表9に示すように、シングル・シグネチャPD に対して8つのPDクラスを規定しており、デュアル・シグネチャPDに対して5つのPDクラスを規定しています。

シングル・シグネチャPDとデュアル・シグネチャPDでは、分類の扱いが異なります。以降のセクションでは、各PD構成の物理層分類を個別に説明します。

表 9. PD 構成別のタイプ 3 およびタイプ 4 PD の分類

| シングル・シグネチャPD |                | デュアル・シグネチャ PD |                                |  |

|--------------|----------------|---------------|--------------------------------|--|

| クラス          | PDが受給できる<br>電力 | クラス           | チャンネルが<br>受給できる電力 <sup>*</sup> |  |

| Class 1      | 3.84W          | Class 1       | 3.84W                          |  |

| Class 2      | 6.49W          | Class 2       | 6.49W                          |  |

| Class 3      | 13W            | Class 3       | 13W                            |  |

| Class 4      | 25.5W          | Class 4       | 25.5W                          |  |

| Class 5      | 40W            | Class 5       | 35.6W                          |  |

| Class 6      | 51W            |               |                                |  |

| Class 7      | 62W            |               |                                |  |

| Class 8      | 71.3W          |               |                                |  |

\*デュアル・シグネチャPDが受給できる全電力は、両方のチャンネルが受給できる電力の合計です。 クラス・シグネチャはポートのチャンネル間で異なる場合があります。 例えば、 クラス 3+ クラス 4= 13W+ 25.5W= 38.5W です。

#### シングル・シグネチャPDの802.3bt分類

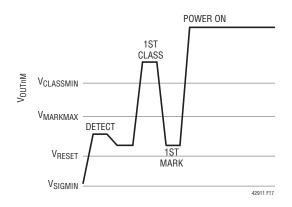

タイプ3 PSEとタイプ4 PSEは、3つのシングル・シグネチャ (SS) PDを介して1つの分類イベントをクラス0に発行します(図17参照)。クラス0~3のSS PDは、そのクラス・シグネチャをPSEに提示し、十分な電力が得られる場合は電源が投入されます。また、電力が制限された802.3bt PSEは、クラス4以上のSS PDを13Wに格下げするために、これらのPDに対して1つの分類イベントを発行できます。図17を参照してください。

タイプ3 PSEとタイプ4 PSEは、十分な電力を供給できる場合、クラス4 SS PDに対して3つの分類イベントを示します(図18参照)。クラス4のSS PDは、全てのイベントでクラス・シグネチャ4を示します。3番目のイベントでは、クラス4のSS PDが上位クラスのSS PDと区別されます。電力が制限されたIEEE 802.3bt PSEは、クラス5以上のSS PDを25.5Wに格下げするために、これらのPDに対して3つの分類イベントを発行できます。

図 17. タイプ3またはタイプ4 PSE、1イベント・クラスのシーケンス

図 19. タイプ3またはタイプ4 PSE、4イベント・クラスのシーケンス

図18. タイプ3またはタイプ4 PSE、3イベント・クラスのシーケンス

図 20. タイプ 4 PSE、5イベント・クラスのシーケンス

タイプ3 PSEとタイプ4 PSEは、十分な電力を供給できる場合、クラス5および6のSS PDに対して4つの分類イベントを示します(図19参照)。クラス5および6のSS PDは、最初の2つのイベントでクラス・シグネチャ4を示します。クラス5および6のSS PDは、後続のイベントでそれぞれクラス・シグネチャ0または1を示します。電力が制限されたPSEは、クラス7および8のSS PDを51Wに格下げするために、これらのPDに対して4つのイベントを発行できます。

タイプ4 PSEは、十分な電力を供給できる場合、クラス7および8のSS PDに対して5つの分類イベントを示します(図20参照)。クラス7および8のPDは、最初の2つのイベントでクラス・シグネチャ4を示します。クラス7および8のSS PDは、後続のイベントでそれぞれクラス・シグネチャ2または3を示します。

#### デュアル・シグネチャPDの802.3bt分類

デュアル・シグネチャ (DS) PDの各ペアセットに対する分類と電力の割り当ては、完全に独立しています。例えば、DS PDは、一方のペアセットではクラス1(3.84W)を要求し、別のペアセットではクラス4(25.5W)を要求して、PDが要求する電力の合計を29.3Wにすることができます。このため、PDとは対照的に、全ての分類はペアセットに対して実行されます。このセクションの残りの部分では、用語を互いに交換できるとみなしています。

タイプ 3 PSE とタイプ 4 PSE は、4つの DS PD を介して3つの 分類イベントを全てクラス1 に発行します(図 18 参照)。

電力が制限されたタイプ3およびタイプ4のPSEは、クラス4 および5のDS PDを13Wに格下げするために、これらのPD に対してクラスのリセットを発行できます(4PIDの理解のセクションを参照)。

Rev 0

24

詳細:www.analog.com

電力が制限されたタイプ3およびタイプ4のPSEでは、クラス5のDSPDを25.5Wに格下げするためにこれらのPDに対して発行できるイベントが、わずか3つに限られます。

タイプ4 PSEは、十分な電力を供給できる場合、クラス5のDS PDに対して4つの分類イベントを示します(図19参照)。クラス5のDS PDは、最初の2つのイベントでクラス・シグネチャ4を示し、後続のイベントでクラス・シグネチャ3を示します。

#### 4PIDの理解

4対の識別条件(4PID)とは、PDが両方のペアセットを介して同時に電力を受給できるかどうかを判定するための一連の条件を指します。

PDが両方のペアセットで有効な検出シグネチャを示し、次の条件のいずれか1つ以上を満たす場合、PSEは4対の電源で給電できます。

- PD はシングル・シグネチャ構成である。

- PD はタイプ3またはタイプ4である。

- あるペアセットを介して電源を投入すると、電源未投入の別のペアセットでPDが有効な検出シグネチャを示す。

タイプ1とタイプ2のPDに対しては、PDシグネチャ設定は定義されていませんが、タイプ3またはタイプ4のPSEは、そのようなPDをシングル・シグネチャまたはデュアル・シグネチャとして識別できます。シングル・シグネチャPDは、PDタイプに関係なく4対の電源から受電できます。802.3bt以前の一定の「デュアル・シグネチャ」PDは、4対の電源によって損傷する可能性があります。

タイプ3とタイプ4のデュアル・シグネチャPDは、同じクラスの802.3bt以前のデュアル・シグネチャPDから得た一意の分類応答を示す必要があります。デュアル・シグネチャPDの場合は、LTC4291-1/LTC4292が、分類時にPDクラスとPDタイプの両方を判別して報告します。

タイプ3、タイプ4、および802.3bt以前のクラス1~クラス4のデュアル・シグネチャPDは、最初と2回目のクラス・イベント時にクラス・シグネチャ1~4をそれぞれ示します。タイプ3とタイプ4のデュアル・シグネチャPDは、その後の全クラス・イベントでクラス・シグネチャDのPDタイプを、3番目のクラス・イベントまでに最終的に判別できます。

クラス4またはクラス5のデュアル・シグネチャPDを接続すると、問題が発生します。PDタイプを判別するために、3つのクラス・イベントが発行されます。クラス・イベントの数に基づいて、PDには25.5Wが割り当てられています。PSEがPDタイプの判別(3イベント)と13Wへの格下げ(1イベント)の両方を行う場合は、図21に示すように、クラス・リセット・イベントを発行する必要があります。

図21. クラス・シーケンス間のクラス・リセット・イベント

クラス・リセット・イベントを発行するには、少なくともtclass\_reset以上、チャンネルの電圧を2.8V未満に維持します。その後、1回のイベント分類を使用してPDを13Wに格下げします。

自動モードでは、4PID情報と4PVALIDの状態を使用して、 受電チャンネル数が自動的に割り出されます。

LLDP信号方式では、その後の任意の時点で、802.3bt以前のPDが実際に4対の電源に対応しているか確認することが可能であり、LTC4291-1/LTC4292に対して4対の電源で給電するよう命令できます。

#### 無効なマルチイベント分類の組み合わせ

802.3bt規格は、一連の有効なクラス・シグネチャの組み合わせを規定しています。最初の2回のクラス・イベントでは、全てのPDが同じ分類シグネチャを返します。タイプ3とタイプ4のPDは、その後の全クラス・イベントで分類シグネチャを変更します。例えば、シングル・シグネチャのクラス5PDは、クラス・シグネチャ4、4、0、0を使用して、それぞれクラス・イベント1、2、3、4に応答します。

クラスの電流制限値を超えている個々のクラス・シグネチャには、無効な分類結果としてのフラグが立てられます。PD の設定に基づく正しいシーケンスを表さないクラス・シグネチャのシーケンスにも、無効な分類結果としてのフラグが同様に立てられます。

#### 自動モードでのPSEの最大電力

自動モードでは、接続されている全ての有効なPDの検出、分類、および電源投入をLTC4291-1/LTC4292が自動的に実行します。このためには、最大の電力を割り当てるようにPSEを設定する必要があります。最大の電力割り当ては、電源と電力経路の能力を反映するものです。PWRMDピンを適切に設定して、PSEシステムの電力供給能力を反映させる必要があります。これらのピンはリセット時にサンプリングされます。

表10. 自動モードでの最大の電力供給能力

| PWRMD1 | PWRMD0 | ポートの最大電力<br>(シングル・シグネチャ) | ペアセットの最大電力<br>(デュアル・シグネチャ) |

|--------|--------|--------------------------|----------------------------|

| 0      | 0      | 40W                      | 13W                        |

| 0      | 1      | 51W                      | 25.5W                      |

| 1      | 0      | 62W                      | 25.5W                      |

| 1      | 1      | 71.3W                    | 35.6W                      |

#### 電力の制御

LTC4291-1/LTC4292の主な機能は、PSEポートへの電力供給を制御することです。LTC4291-1/LTC4292では、PSEポートは2つのパワー・チャンネルで構成されています。各パワー・チャンネルはペアセットを介して電力供給を制御します。このセクションでは、電力の供給と制御をチャンネルごとに定義します。

LTC4291-1/LTC4292は、外付けのパワーMOSFETのゲート 駆動電圧を制御しつつ、(外付けの検出抵抗を流れる)電流 と(OUTピン両端の)出力電圧を監視することにより、電力 を供給します。

LTC4291-1/LTC4292は、 $V_{EE}$ 電源を制御状態でPSEポートに接続し、PDの電力需要を満たすと同時に、外付けMOSFETの消費電力と $V_{EE}$ バックプレーンに対する外乱を最小限に抑えます。

#### 突入電流の制御

ポートの電源投入を命令されると、LTC4291-1/LTC4292は (命令された)一方または両方のチャンネルのGATEピンの電圧を上昇させて、外付けMOSFETのゲート電圧を制御状態で上昇させます。

通常の突入電流制御時には、外付けMOSFETが完全な 導通状態になるか、チャンネルの電流が突入電流制限値 ( $I_{INRUSH-2P}$ )に達するまで、MOSFETのゲート電圧は上 昇します。 $I_{INRUSH-2P}$ はPSEによって自動的に設定されま す。クラス0からクラス4に割り当てられているシングル・シ グネチャPDに対して、PSEが4対の電源で給電している場 合、 $I_{INRUSH-2P}$ は1チャンネルにつき212.5mA(代表値)です (LIMn = 08h)。それ以外の場合、 $I_{INRUSH-2P}$ は1チャンネルにつき425mA(代表値)です(LIMn = 80h)。

チャンネルの電流が $I_{INRUSH-2P}$ を超えるとGATEピンはサーボ制御され、電流を $I_{INRUSH-2P}$ 以内に能動的に制限します。GATEピンがサーボ制御されていない場合、最終的なVGSは 12V(代表値)になります。

突入電流制御時に、各受電チャンネルはタイマー(tSTART)を作動させます。各受電チャンネルは、tSTARTの期限が切れるまで突入電流の制御を維持します。tSTARTの期限が切れると、PSEはチャンネルの電圧および電流を検査します。PSEがPDに電力を供給しているときに、チャンネルに流れる電流がINRUSH-2P(PDの設定およびクラスに従った適切な値)より少なければ、突入電流の制御は正常です。

突入電流の制御がうまくいかないと、電源は遮断され、対応するtstart障害が設定されます。そうでない場合は、電流の遮断および制限のセクションで説明するように、ポートまたはチャンネルは、適宜、電源投入段階に進んで、事前設定の電流制限閾値が使用されます。

#### ポートの電力ポリシング

電力ポリシング閾値(PCUT-4P)は、ポートごとに、128Wまで 0.5W刻み(代表値)でモニタされます。全出力電力の1秒間 の移動平均が規定の閾値を超えると、電源がポートから遮 断され、対応するtCUT 障害が設定されます。

特に、ポートのポリシング機能を使用して、PDクラス電力の供給を確保しつつ、100Wの有限電源(LPS)条件より低い値を維持できます。

#### 電流の遮断および制限

LTC4291-1/LTC4292の各ポートには、2つの電流制限閾値 ( $I_{CUT-2P}$  および $I_{LIM-2P}$ )が組み込まれており、それぞれに対応するタイマー( $t_{CUT}$  および $t_{LIM}$ )があります。 $I_{CUT-2P}$  閾値と  $I_{LIM-2P}$  閾値の設定は、数種類の要因(PD割り当てクラス、

Rev 0

26

詳細:www.analog.com

主電源の電圧( $V_{EE}$ )、PSEタイプ(タイプ3または4)、および MOSFETのSOA)によって決まります。

1組のプログラマブル・ポート閾値ICUT-2PおよびILIM-2Pは、両方のチャンネルに共用されます。これらの閾値は、表4および表5に示すように、分類結果に基づいて設定します。デュアル・シグネチャPDによって異なるクラスが割り当てられた場合は、最も高いクラスを使用して閾値を設定します。例えば、デュアル・シグネチャPDがクラス1とクラス5を割り当てた場合は、クラス5に基づいてICUT-2PとLIM-2Pの値が決まります。

LTC4291-1/LTC4292は、IEEE 規格に従って、ポートまたはチャンネルから電源を遮断する前の限られた時間、適宜、チャンネルの電流がI<sub>CUT-2P</sub>を超えることを許容する一方で、MOSFET のゲート駆動電圧を能動的に制御して、チャンネルの電流をI<sub>LIM-2P</sub>未満に抑えます。I<sub>CUT-2P</sub>関値を超えただけでは、チャンネルは電流を制限する処置をとりませんが、t<sub>CUT</sub> タイマーは起動させます。タイマーの期限が切れる前に電流が減少してI<sub>CUT-2P</sub>関値より低くなると、t<sub>CUT</sub> タイマーはカウント・ダウンしますが、カウント・アップ時の1/16の速度です。t<sub>CUT</sub> タイマーが 59ms (代表値)に達すると、ポートまたはチャンネルは適宜オフになり、対応するt<sub>CUT</sub>障害が設定されます。これにより、デューティ・サイクルが約6%未満の断続的な過負荷信号をチャンネルは許容できます。これよりデューティ・サイクルが長い過負荷では、適宜ポートまたはチャンネルから電源が遮断されます。

ILIM-2P電流制限回路は常にイネーブルされており、チャンネ ルの電流を能動的に制限します。tLIMタイマーがイネーブル されるのは、t<sub>LIM</sub>のTimer Configurationフィールドがゼロ以 外の値に設定されている場合だけです。このため、tLIMの値 をtCUTより小さい値に設定することにより、MOSFETをより 強力に保護して、MOSFETが損傷する前にポートをオフす ることができます。tLIMタイマーは、電流がILIM-2P 閾値を超 えると始動します。tLIMタイマーの経過時間が、1.7ms(代表 値)にt<sub>LIM</sub>のTimer Configurationフィールドの値を掛けた時 間に達すると、ポートまたはチャンネルは適宜オフになり、該 当するt<sub>LIM</sub>障害が設定されます。t<sub>LIM</sub>のTimer Configuration フィールドを0に設定すると、tLIMの動作はtCUTタイマーに よって追従され、ILIM-2PとICUT-2Pの両方のイベント時にカ ウント・アップします。IEEEの準拠を維持するため、t<sub>LIM</sub>の事 前設定Timer Configurationフィールドを、LTC4291 Software Programming 技術文書に示す値に設定してください。

I<sub>CUT-2P</sub>は、通常はI<sub>LIM-2P</sub>より低い値に設定されるので、ポートは電流制限なしで軽度の障害に耐えることができます。

IEEEの準拠を維持するため、 $I_{LIM-2P}$ の事前設定値を、表4 および5に示す値に設定してください。突入電流の段階が完 了すると、 $I_{LIM-2P}$ の事前設定値が自動的に適用されます。

tcutタイマーとtLIMタイマーは、チャンネルごとに維持されます。tcutまたはtLIMの障害が発生すると、一方または両方のチャンネルをオフする判定が行われます。詳細については、ポートの障害とチャンネルの障害のセクションを参照してください。

#### ILIM-2P のフォールドバック動作

LTC4291-1/LTC4292の I<sub>LIM-2P</sub> 閾値は、チャンネルの電圧 が通常の動作電圧より低くなるとチャンネルの電流を低減 する2段階のフォールドバック回路として実装されています。これにより、MOSFETの消費電力は安全なレベルに維持されます。電流制限とフォールドバックの動作は、ポートごとに 設定できます。

LTC4291-1/LTC4292は、802.3bt 規格での最大値をはるかに超える電流レベルをサポートします。 $I_{LIM-2P}$ の値を大きくするには、大型の外付けMOSFET、ヒートシンクの追加の他に、 $t_{LIM}$ のTimer Configuration フィールドを低めの値に設定することが必要です。

#### MOSFETの障害検出

LTC4291-1/LTC4292のPSEポートは、かなりのレベルの酷使に耐えるように設計されていますが、極端な場合には外付けMOSFETが損傷する可能性があります。損傷したMOSFETはソースとドレインの間が短絡していることがあり、その場合には、本来はオフしているはずのポートがオンしているように見えます。また、この状態が原因で検出抵抗が溶断してオープンになり、ポートはオフになりますが、SENSEの電圧が異常に高くなることがあります。故障したMOSFETは、更にゲートとドレインの間を短絡させて、GATEの電圧が異常に高くなる可能性があります。OUT、SENSE、およびGATEは、最大80Vの異常電圧に耐えられ、損傷しないよう設計されています。

給電されていないポートのいずれかのチャンネル(給電されているチャンネルがない状況)でLTC4291-1/LTC4292がパワーグッド状態を認識すると、デバイスは全てのポート機能を無効にして、ポートのゲート駆動プルダウン電流を低減し、FET Bad障害を報告します。これは一般的には永続的な障害ですが、ホストはポートをリセットすることによって回復を試行できます。ポートのリセットで障害を解消できない場合には、デバイス全体をリセットします。MOSFETが実際に異常動作を示す場合、障害信号が素早く返され、ポートはそれ自体を再度ディスエーブルします。LTC4291-1/LTC4292の残りのポートは影響を受けません。

MOSFETがオープンの場合やMOSFETがないことでFET Bad 障害がトリガされることはありませんが、LTC4291-1/LTC4292がポートをオンしようとすると、tSTART 障害が発生します。

#### 切り離し

LTC4291-1/LTC4292は、給電されているチャンネルをモニタして、PDに最小規定電流が流れ続けていることを確認します。 $I_{HOLD-2P}$  閾値は、 $0.15\Omega$ の検出抵抗両端で $V_{HOLD-2P}$  閾値としてモニタされており、PDが切り離されたかどうかを調べるために使用します。

$I_{HOLD-2P}$  閾値は、自動モードでは自動的に設定され、半自動モードと手動モードではお客様に設定していただきます。 クラス 0 からクラス 4 に割り当てられているシングル・シグネチャPDに1つのチャンネルを介して電力を供給する場合は、Disconnect Configuration ビットによって  $I_{HOLD-2P}$  閾値を 7.5mA (代表値)に設定します。その他の場合は、 $I_{HOLD-2P}$  閾値を 3.5mA (代表値)に設定します。

切り離しタイマー(t<sub>DIS</sub>)は、チャンネルの電流がI<sub>HOLD-2P</sub>関値より少なくなるとカウント・アップして、PDが切り離されていることを示します。該当のt<sub>DIS</sub>タイマーが終了すると、ポートまたはチャンネル(表11)はオフになり、対応するt<sub>DIS</sub>障害が設定されます。t<sub>DIS</sub>タイマーが終了する前に電流が増加してI<sub>HOLD-2P</sub>を超えると、タイマーはリセットします。PDが最小電流レベルを超えてからt<sub>DIS</sub>タイマーが終了する限り、PDは給電されたままです。

推奨はしませんが、DC切り離し機能は、対応するDC Disconnect Enableビットをクリアすれば無効化できます。DC 切り離し機能を無効にすると、LTC4291-1/LTC4292はIEEE 規格に準拠しなくなります。給電されているポートは、PDの

取り外し後も給電されたままです。給電されたままのポートが、その後PoE非対応のデータ・デバイスに接続された場合には、損傷する可能性があります。

LTC4291-1/LTC4292は、AC切り離し回路を内蔵していません。AC切り離し機能は、802.3btのサポート対象外です。

#### ポートの障害とチャンネルの障害

tCUT、tLIM、およびtDISタイマーは、チャンネルごとに維持されます。いずれかのチャンネルのタイマーが終了すると、ポートの両方または一方のチャンネルの電源を遮断するか、どのチャンネルの電源も遮断しないかが判定されます。

シングル・シグネチャPDに障害が発生した場合、802.3bt規格によってオプションの動作が許可されています。このオプションにより、シングル・シグネチャPDは、ペアセットYで障害が発生した場合でも、ペアセットXで給電状態を維持できます。FAULT2Pnビットを設定すると、このオプション動作が可能になります。この動作は通常動作では推奨されません。PDやケーブル配線での障害は、PDの故障やケーブルの損傷にいたる直前の兆候を示すからです。

表 11. チャンネル障害がポート/チャンネル状態に与える 影響

|        |          | 障害の結果:<br>電源の遮断対象(ポートまたはチャンネル) |                  |                  |

|--------|----------|--------------------------------|------------------|------------------|

| PDの構成  | FAULT2Pn | t <sub>CUT</sub> **            | t <sub>LIM</sub> | t <sub>DIS</sub> |

| Cinalo | 0        | Port                           | Port             | Dort*            |

| Single | 1        | Channel                        | Channel          | Port*            |

| Dual   | Х        | Channel                        | Channel          | Channel          |

<sup>\*</sup>toisの期限が両方のチャンネルで切れた場合

### 障害遠隔測定

前の数セクションで説明したように、障害は一方または両方のチャンネルで発生する可能性があり、その結果、一方または両方のチャンネルで電源が遮断されます。障害イベント・レジスタは、従来からポート・レベルで実装されています。障害発生源のチャンネルにとっての障害を追跡するため、LTC4291-1/LTC4292には、障害レジスタの2番目の層(Fault Telemetry レジスタ)が追加されています。詳細については、LTC4291 Software Programming 技術文書を参照してください。

<sup>\*\*</sup>ポートの電力ポリシング(P<sub>CUT-4P</sub>)によってt<sub>CUT</sub>イベントが発生する。有効にした場合、ポートの電力ポリシングによって、FAULT2Pnの設定に関係なく、ポートの電源が遮断される。

#### **Autoclass**

IEEE 802.3btでは、新しいオプション機能であるAutoclass が導入されています。Autoclassにより、PSEは、最も厳しい動作条件で必要な電力より多くの電力を要求しているシングル・シグネチャPDからパワー・バジェットを回収できます。802.3btは、デュアル・シグネチャPDについてはAutoclassを仕様化していません。LTC4291-1/LTC4292は、Autoclassを完全にサポートしています。

802.3 PoE規格の以前のバージョンでは、最も厳しい条件でのイーサネット・ケーブル両端間のIR電圧降下および最小のPSE出力電圧に対して、最小のPSE出力電力を規定しています。ただし、過剰に割り当てられた電力をPSEが回収する方法は規定されていません。短めのイーサネット・ケーブルを使用する場合や、サポートされているPSE出力電圧が規定の最小値より高い場合、規定の最小PSE出力電力では、実質的に過剰な電力がPDに割り当てられます。

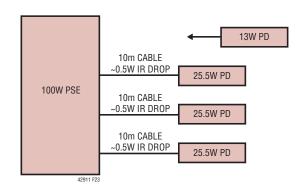

PoEシステムの例を2つのバージョンで示します。100mのケーブルを介して3つの25.5W PDに電力を供給している100Wの4ポートPSEを図22に示します。こうしたシステムでは、PSEが1つのPDにつき25.5Wを割り当て、更に100mケーブルのIR電圧降下ごとに4.5Wを割り当てることが必要です。

全電力の割り当ては次のようになります。

#### 3 Ports • (4.5W + 25.5W) = 90W

別の13W PDを4番目のPSEポートに差し込んだ場合、供給できるのはわずか10Wであり、このPDには電力を供給できません。

100m CABLE

4.5W IR DROP

25.5W PD

100m CABLE

4.5W IR DROP

25.5W PD

100m CABLE

4.5W IR DROP

25.5W PD

25.5W PD

25.5W PD

図22.100mのケーブルを使用する100WのPoEシステム

10mのケーブルを介して3つの25.5W PDに電力を供給している100Wの4ポートPSEを図23に示します。こうしたシステムでは、PSEが1つのPDにつき25.5Wを割り当て、更に10mケーブルのIR電圧降下ごとに約0.5Wを割り当てることが必要です。

Autoclassを使用しない場合、全電力の割り当ては次のようになります。

#### 3 ports • (4.5W + 25.5W) = 90W