### 概要

DS4302は、3個のプログラマブルディジタル出力付 き5ビットディジタル-アナログコンバータ(DAC)です。 DS4302は、2線式、SMBus™対応のシリアルインタ フェースを介して通信します。小型8ピンµSOPパッ ケージは、スペースが制限されたアプリケーションに 最適です。

## 特長

- ♦ SOPパッケージはMPS1251およびMPS1252の ドロップイン置換品

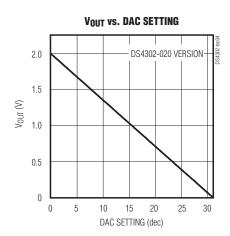

- ◆ 単一5ビットDAC (32ステップ)

- ♦ 0V~2Vおよび0V~1.9Vバージョン

- ♦ 3個のプログラマブルディジタル出力

- ◆ SMBus対応のシリアルインタフェース

- ◆ 電源電圧範囲: 4.5V~5.5V

- ◆ 8ピンSOPおよび8ピンµSOPパッケージ

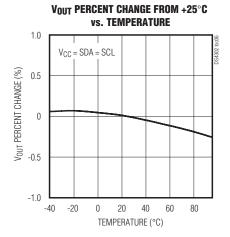

- ◆ 工業用温度範囲:-40℃~+85℃

## アプリケーション

CCFLバックライト輝度制御 電源キャリブレーション

## 型番

| PART         | V <sub>OUT</sub><br>RANGE | TOP<br>BRAND | PIN-<br>PACKAGE |  |  |

|--------------|---------------------------|--------------|-----------------|--|--|

| DS4302Z-020  | 0V to 2.0V                | 4302B        | 8 SO            |  |  |

| DS4302Z-019* | 0V to 1.9V                | 4302A        | 8 SO            |  |  |

| DS4302U-020  | 0V to 2.0V                | 4302B        | 8 µSOP          |  |  |

| DS4302U-019* | 0V to 1.9V                | 4302A        | 8 µSOP          |  |  |

テープ&リールの場合は、末尾に「/T&R」を加えてください。 \*入手性についてはお問い合わせください。

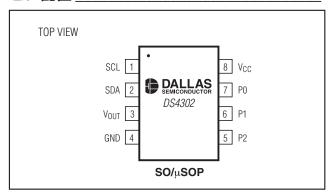

## 端子説明

| 端子 | 名称   | 機能                            |

|----|------|-------------------------------|

| 1  | SCL  | シリアルクロック入力。2線式クロック入力。         |

| 2  | SDA  | シリアルデータ入力/出力。双方向2線<br>式データ端子。 |

| 3  | Vout | DAC出力電圧                       |

| 4  | GND  | グランド                          |

| 5  | P2   |                               |

| 6  | P1   | プログラマブルディジタル出力                |

| 7  | P0   |                               |

| 8  | Vcc  | 電源入力                          |

SMBusはIntel Corp.の商標です。

#### ピン配置

# **DS4302**

#### **ABSOLUTE MAXIMUM RATINGS**

| Voltage Range on Vcc, SDA, and SCL Pins  | Storage Temperature Range55°C to +125°C                     |

|------------------------------------------|-------------------------------------------------------------|

| Relative to Ground0.5V to +6.0V          | Soldering TemperatureSee IPC/JEDEC J-STD-020A Specification |

| Operating Temperature Range40°C to +85°C |                                                             |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### RECOMMENDED DC OPERATING CONDITIONS

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C)$

| PARAMETER                | SYMBOL | CONDITIONS | MIN 7     | ГҮР МАХ        | UNITS |

|--------------------------|--------|------------|-----------|----------------|-------|

| Supply Voltage           | Vcc    | (Note 1)   | 4.5       | 5.5            | V     |

| Input Logic 1 (SDA, SCL) | VIH    |            | 2.0       | $V_{CC} + 0.3$ | V     |

| Input Logic 0 (SDA, SCL) | VIL    |            | GND - 0.3 | 0.8            | V     |

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +4.5V \text{ to } 5.5V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C.)$

| PARAMETER                               | SYMBOL           | CONDITIONS                                       | MIN                   | TYP  | MAX   | UNITS |

|-----------------------------------------|------------------|--------------------------------------------------|-----------------------|------|-------|-------|

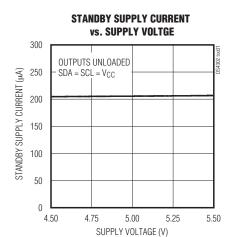

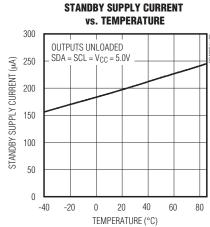

| Standby Current                         | ISTBY            | (Notes 2, 3)                                     |                       | 200  | 300   | μΑ    |

| Input Leakage                           | ΙL               | (Note 4)                                         | -1.0                  |      | +1.0  | μΑ    |

| SDA Low-Level Output Voltage            | M                | 3mA sink current                                 | 0.0                   |      | 0.4   | V     |

|                                         | V <sub>OL1</sub> | 6mA sink current                                 | 0.0                   |      | 0.6   |       |

| P0, P1, P2 Low-Level Output<br>Voltage  | V <sub>OL2</sub> | (Note 1)<br>4mA sink                             |                       |      | +0.4V | V     |

| P0, P1, P2 High-Level Output<br>Voltage | Voн              | (Note 1)<br>4mA source                           | V <sub>CC</sub> - 0.4 | 1V   |       | V     |

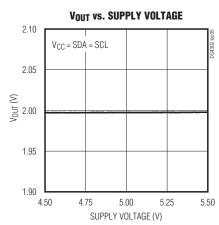

| V <sub>OUT</sub> Maximum Level (-020)   |                  | V <sub>CC</sub> = 5.0V, Data = 00000XXX (Note 3) | 1.925                 | 2.0  | 2.075 | V     |

| V <sub>OUT</sub> Minimum Level (-020)   |                  | V <sub>CC</sub> = 5.0V, Data = 11111XXX          | 0.0                   | 0.05 | 0.1   | V     |

| V <sub>OUT</sub> Maximum Level (-019)   |                  | V <sub>CC</sub> = 5.0V, Data = 00000XXX (Note 3) | 1.825                 | 1.9  | 1.975 | V     |

| V <sub>OUT</sub> Minimum Level (-019)   |                  | V <sub>CC</sub> = 5.0V, Data = 11111XXX          | 0.0                   | 0.05 | 0.1   | V     |

| Power-On Reset                          |                  |                                                  |                       | 1.7  |       | V     |

| Settling Time                           |                  |                                                  |                       | 10   |       | μs    |

| D/A Output Levels                       |                  |                                                  |                       | 32   |       | steps |

X = Don't care.

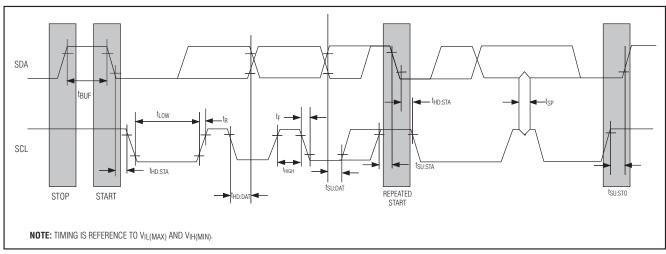

## **AC ELECTRICAL CHARACTERISTICS (Figure 3)**

$(V_{CC} = +4.5V \text{ to } 5.5V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \text{ timing referenced to } V_{IL(MAX)} \text{ and } V_{IH(MIN)}.)$

| PARAMETER                                       | SYMBOL         | CONDITIONS | MIN       | TYP | MAX | UNITS |

|-------------------------------------------------|----------------|------------|-----------|-----|-----|-------|

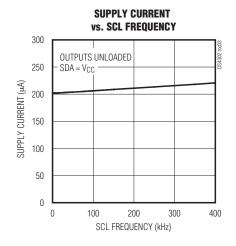

| SCL Clock Frequency                             | fscl           |            | 0         |     | 400 | kHz   |

| Bus Free Time Between STOP and START Conditions | tBUF           |            | 1.3       |     |     | μs    |

| Low Period of SCL                               | tLOW           |            | 1.3       |     |     | μs    |

| High Period of SCL                              | tHIGH          |            | 0.6       |     |     | μs    |

| Data Hold Time                                  | thd:dat        |            | 0         |     | 0.9 | μs    |

| Data Setup Time                                 | tsu:dat        |            | 100       |     |     | ns    |

| Start Setup Time                                | tsu:sta        |            | 0.6       |     |     | μs    |

| SDA and SCL Rise Time                           | t <sub>R</sub> | (Note 5)   | 20 + 0.10 | Св  | 300 | ns    |

| SDA and SCL Fall Time                           | tF             | (Note 5)   | 20 + 0.10 | Св  | 300 | ns    |

| Stop Setup Time                                 | tsu:sto        |            | 0.6       |     |     | μs    |

| SDA and SCL Capacitive Loading                  | СВ             | (Note 5)   |           |     | 400 | рF    |

**Note 1:** All voltages referenced to ground.

Note 2: I<sub>STBY</sub> specified for the inactive state measured with SDA = SCL = V<sub>CC</sub> and with V<sub>OUT</sub>, P0, P1, and P2 floating.

**Note 3:** No load on V<sub>OUT</sub>.

Note 4: The DS4302 will not obstruct the SDA and SCL lines if V<sub>CC</sub> is switched off as long as the voltages applied to these inputs does not violate their min and max input-voltage levels.

**Note 5:** C<sub>B</sub>—total capacitance of one bus line in picofarads.

## 標準動作特性

$(V_{CC} = +5.0V, T_A = +25^{\circ}C.)$

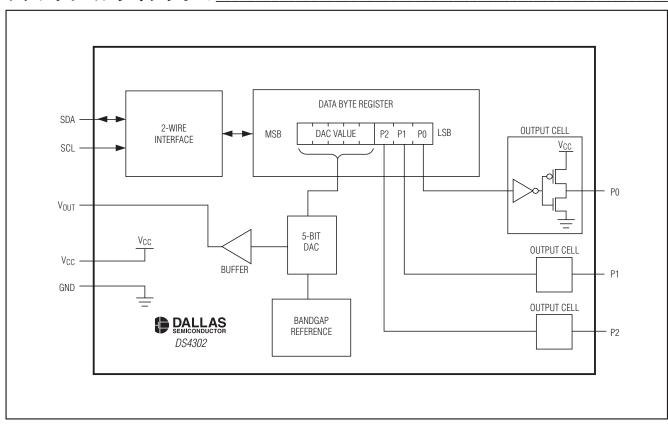

## ファンクションダイアグラム \_

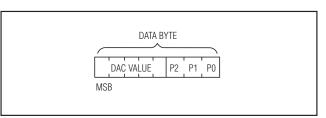

図1. データバイト構成

#### 詳細

DS4302は、5ビットのDACと3個のプログラマブルディジタル出力を備えています。DACの設定値および設定される出力レベルは1バイトのデータワードに含まれており、このデータワードは電源投入の際00hにデフォルト設定されます(データバイト構成については、図1を参照してください)。このバイトの上位5ビットはDACを設定し、VOUTに発生する電圧を制御します。1111 1XXXの設定値はDACの最小出力電圧を設定し、0000 0XXXの設定値はDACの最大出力電圧を設定します。このデータバイトの下位3ビットは、3つの出力端子PO、P1、およびP2を制御します。これらの制御ビットのいずれも0に設定すると対応する出力がローに駆動され、これらのビットを1に設定すると出力がバイに駆動されます。

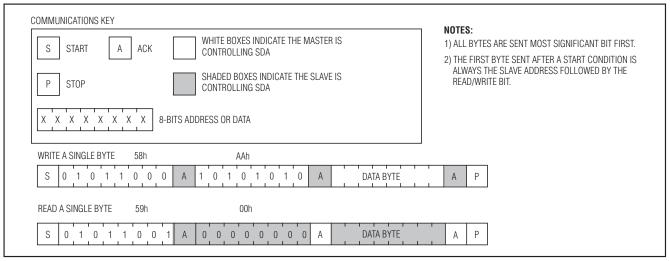

DS4302は、2線式(SMBus対応)のディジタルインタフェースを介して通信し、58hの2線式アドレスを備えています。書込みおよび読取り動作を使用して、DACおよび出力設定値へのアクセスが行われます。各動作は、2線式START条件で始まり、3バイトで構成され、2線式STOP条件で終了します(図2参照)。書込み動作を使用すると、2線式マスタは5ビットのDACを設定してVOUTの電圧を調整し、3つの出力端子PO、P1、およびP2のレベルを設定することができます。読取り動作は、プログラムされた設定値の呼出しに使用されます。

#### 2線式の定義

2線式データ転送の説明には以下の用語が一般に使用されます。

マスタデバイス:マスタデバイスは、バス上のスレーブ デバイスを制御します。マスタデバイスはSCLクロック パルス、START条件、およびSTOP条件を生成します。

スレーブデバイス: スレーブデバイスは、マスタの要求 に応じてデータを送受信します。

バスアイドルまたは非ビジー: SDAとSCLの両方が非アクティブでロジックハイ状態にあるときのSTOP条件とSTART条件の間の時間。バスはアイドル状態のときスレーブデバイスを低電力モードにします。

START条件: START条件は、スレーブとの新たなデータ 転送を開始するためにマスタによって生成されます。 SCLがハイの間にSDAがハイからローに遷移すると、 START条件が生成されます。有効なタイミングについては、図3を参照してください。

STOP条件: STOP条件は、スレーブとのデータ転送を終了するためにマスタによって生成されます。SCLがハイの間にSDAがローからハイに遷移すると、STOP条件が生成されます。有効なタイミングについては、図3を参照してください。

ビット書込み: SDAはSCLがロー状態の間に遷移する必要があります。SDAのデータは、SCLの全ハイパルス期間およびセットアップとホールドの時間要件を満たす期間中、有効かつ不変の状態を保たれなければなりません(図3参照)。データはSCLの立上りエッジの間にデバイスにシフト入力されます。

図2. 2線式通信の例

図3. 2線式のタイミング図

ビット読取り:書込み動作の最後に、マスタは、ビット 読取り中、次のSCL立上りエッジの前に適切なセット アップ時間(図3参照) SDAバスラインを解放する必要 があります。デバイスは前のSCLパルスの立下りエッジでSDAの各データビットをシフト出力し、データビットは次のSCLパルスの立上りエッジで有効になります。マスタは、スレーブからビットを読み取っているときも含め、すべてのSCLクロックパルスを生成することに 留意してください。

確認応答(ACK):確認応答(ACK)は、バイト転送中に送信される常に9番目のビットです。データを受信するデバイス(読取り中のマスタ、または書込み中のスレーブ)は、9番目のビットの間ゼロを送信することによってACKを返します。タイミングについては、図3を参照してください。ACKは、デバイスがデータを正しく受信していることの確認です。

バイト書込み:バイト書込みは、マスタからスレーブに転送(最上位ビットが先頭)される8ビットの情報と、スレーブからマスタへの1ビットの確認応答で構成されます。マスタによって送信される8ビットは、ビット書込みの定義に従って行われ、確認応答はビット読取りの定義を用いて読み取られます。

バイト読取り:バイト読取りは、スレーブからマスタへの8ビット情報転送とマスタからスレーブへの1ビットのACKからなります。スレーブからマスタに転送(最上位ビットが先頭)される8ビットの情報は、前記のビット読取りの定義を用いてマスタによって読み取られ、マスタはビット書込みの定義を用いてACKを送信し後続のデータバイトを受信します。スレーブがSDAの制御をマスタに戻すためには、マスタは最終バイト読取りに対してACKを返して通信を終了する必要があります。

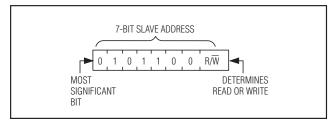

図4. スレーブアドレスとR/Wビット

スレーブアドレスとR/Wビット: 2線式バス上の各スレーブは、START条件のすぐ後に送信されるスレーブアドレスバイトに応答します。スレーブアドレスバイトは、スレーブアドレスとR/Wビットを含んでいます。スレーブアドレス(図4参照)は上位7ビットで、R/Wビットは最下位ビットです。

DS4302のスレーブアドレスは0101100X (バイナリ)です。ただし、XはR/ $\overline{W}$ ビットです。R/ $\overline{W}$ ビットが0 (01011000)であれば、マスタはスレーブにデータを書き込みます。R/ $\overline{W}$ ビットが1 (01011001)であれば、マスタはスレーブからデータを読み取ります。

メモリアドレス: 2線式書込み動作中、マスタはメモリアドレスを送信してスレーブがデータを保存するメモリ位置を指示する必要があります。メモリアドレスは、スレーブアドレスバイト(R/W = 0)に続く書込みまたは読取り動作中に送信される2番目のバイトです。書込み動作の場合、メモリアドレスは10101010 (AAh)で、読取り動作の場合、メモリアドレスは00000000 (00h)です。

# **DS4302**

## 2線式通信

スレーブへの書込み:マスタは、START条件の生成、スレーブアドレスの書込み(R/W = 0)、メモリアドレスの書込み、データバイトの書込み、STOP条件の生成を行う必要があります。マスタはすべてのバイトの書込み動作中にスレーブの確認応答を読み取る必要があります。書込みコマンドの例については、図2を参照してください。

スレーブからの読取り:スレーブからの読取りのために、マスタはSTART条件の生成、R/W = 1によるスレーブアドレスの書込み、スレーブからのACKの受信、スレーブからの00hのメモリアドレスの読取り、スレーブへのACKの送信、データバイトの読取り、転送の終了を示すACKの送信、およびSTOP条件の生成を行います。読取りコマンドの例については、図2を参照してください。

## アプリケーション情報

### 電源のデカップリング

DS4302を使用する際、最良の結果を得るためには  $0.01\mu$ Fまたは $0.1\mu$ Fのコンデンサで電源をデカップル してください。高品質のセラミック表面実装コンデンサを使用し、これらをDS4302の $V_{CC}$ とGNDの各端子のできる限り近くに取り付けてリードインダクタンスを最小限に抑えてください。

#### SDAおよびSCLプルアップ抵抗器

AC ELECTRICAL CHARACTERISTICS (AC電気的特性) に記載された立上りおよび立下り時間が規定値内になるように、SDAとSCLのプルアップ抵抗値を選択する必要があります。

## チップ情報

TRANSISTOR COUNT: 2428

SUBSTRATE CONNECTED TO GROUND

## パッケージ \_\_\_

最新のパッケージ情報は、japan.maxim-ic.com/DallasPackInfoをご参照ください。

# マキシム・ジャパン株式会社

〒169-0051東京都新宿区西早稲田3-30-16(ホリゾン1ビル) TEL. (03)3232-6141 FAX. (03)3232-6149

マキシムは完全にマキシム製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。マキシムは随時予告なく回路及び仕様を変更する権利を留保します。

8 \_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600