#### 概要

DS1972は、耐久性の高いiButton®パッケージ内に各 256ビットの4ページのメモリページとして構成される、 1024ビットの1-Wire® EEPROMチップです。データは 8バイトのスクラッチパッドに書き込まれ、検証された 後に、EEPROMメモリにコピーされます。特別機能と して、4ページの各メモリページを個別に書込み保護 するか、またはEPROMエミュレーションモードに設定 することができます。このエミュレーションモードでは、 各ビットを1から0の状態にのみ変更することができます。 DS1972は、導線が1本の1-Wireバスを通じて通信し ます。この通信は、標準の1-Wireプロトコルに準拠して います。各デバイスは、出荷時にレーザで書き込まれた 変更不可能なそれぞれ固有の64ビットROM登録番号を 備えています。この登録番号を使って、マルチドロップ 1-Wireネット環境でデバイスのアドレスを指定すること ができます。

#### アプリケーション

アクセス制御/パーキングメータ 仕掛品(WIP)追跡 ツール管理 在庫管理 保守/検査データストレージ

#### アクセサリ例

| PART     | ACCESSORY               |

|----------|-------------------------|

| DS9096P  | Self-Stick Adhesive Pad |

| DS9101   | Multipurpose Clip       |

| DS9093RA | Mounting Lock Ring      |

| DS9093A  | Snap-In Fob             |

| DS9092   | <u>i</u> Button Probe   |

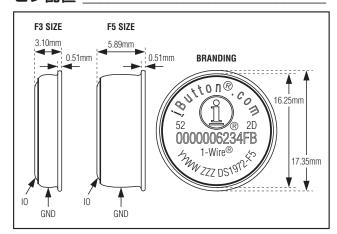

#### ピン配置

1-WireおよびiButtonはMaxim Integrated Products, Inc.の 登録商標です。

#### 特長

- ♦ 各256ビットの4ページに分割された1024ビットの EEPROMメモリ

- ◆ 各メモリページに対する永久的な書込み保護、 またはEPROMエミュレーションモード(「Write to 0 (0の書込み)」)の設定が可能

- ♦ スイッチポイントヒステリシスとフィルタリングに よってノイズ環境における性能を最適化

- ◆ IEC 1000-4-2レベル4のESD保護(±8kV接触放電、 ±15kV空中放電、typ)

- ◆ 2.8V~5.25V (-40℃~+85℃)の広い電圧範囲での 読取りと書込み

- ◆ 1-Wireプロトコルを使用して15.4kbpsまたは 125kbpsの速度で単一ディジタル信号によって ホストと通信

#### 共通のiButtonの特長

- ◆ 出荷時にレーザで書き込まれた固有の64ビット登録 番号によって同一製品が存在しないため、エラーの ないデバイス選択と絶対追跡を実現

- ◆ 1-Wireネット用マルチドロップコントローラ内蔵

- ♦ チップベースのデータキャリアが、堅牢な ステンレススチールケース内に保護され、 ディジタルIDおよび情報を保存

- ♦ 対象物に取り付けられた状態で、データにアクセス 可能

- ♦ ボタン形状はカップ形状プローブと自己整合

- ◆ 自己接着する粘着性背面、フランジによるラッチ、 またはリングをリムに押し付けロックによって 取付けが容易

- ◆ 読取り器が最初に電圧を印加するときプレゼンス 検出器が認知

| PART       | TEMP RANGE     | PIN-PACKAGE        |

|------------|----------------|--------------------|

| DS1972-F5+ | -40°C to +85°C | F5 <u>i</u> Button |

| DS1972-F3+ | -40°C to +85°C | F3 <u>i</u> Button |

+は鉛(Pb)フリー/RoHS準拠パッケージを表します。

MIXIM

#### **ABSOLUTE MAXIMUM RATINGS**

| IO Voltage Range to GND0.5V to +6V       | Junction Temperature+150°C              |

|------------------------------------------|-----------------------------------------|

| IO Sink Current20mA                      | Storage Temperature Range55°C to +125°C |

| Operating Temperature Range40°C to +85°C |                                         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.}) \text{ (Note 1)}$

| PARAMETER                       | SYMBOL            | CONDITIONS                                                             | MIN                | TYP | MAX                    | UNITS |

|---------------------------------|-------------------|------------------------------------------------------------------------|--------------------|-----|------------------------|-------|

| IO PIN: GENERAL DATA            | ,                 |                                                                        |                    |     |                        |       |

| 1-Wire Pullup Voltage           | V <sub>PUP</sub>  | (Note 2)                                                               | 2.8                |     | 5.25                   | V     |

| 1-Wire Pullup Resistance        | R <sub>PUP</sub>  | (Notes 2, 3)                                                           | 0.3                |     | 2.2                    | kΩ    |

| Input Capacitance               | Cio               | (Notes 4, 5)                                                           |                    |     | 1000                   | рF    |

| Input Load Current              | ΙL                | IO pin at V <sub>PUP</sub>                                             | 0.05               |     | 6.7                    | μΑ    |

| High-to-Low Switching Threshold | V <sub>T</sub> L  | (Notes 5, 6, 7)                                                        | 0.5                |     | V <sub>PUP</sub> - 1.8 | V     |

| Input Low Voltage               | VIL               | (Notes 2, 8)                                                           |                    |     | 0.5                    | V     |

| Low-to-High Switching Threshold | V <sub>TH</sub>   | (Notes 5, 6, 9)                                                        | 1.0                |     | V <sub>PUP</sub> - 1.0 | V     |

| Switching Hysteresis            | V <sub>H</sub> Y  | (Notes 5, 6, 10)                                                       | 0.21               |     | 1.70                   | V     |

| Output Low Voltage              | V <sub>OL</sub>   | At 4mA (Note 11)                                                       |                    |     | 0.4                    | V     |

|                                 | t <sub>REC</sub>  | Standard speed, $R_{PUP} = 2.2 k\Omega$                                | 5                  |     |                        |       |

| Recovery Time                   |                   | Overdrive speed, $R_{PUP} = 2.2k\Omega$ 2                              |                    |     |                        |       |

| (Notes 2, 12)                   |                   | Overdrive speed, directly prior to reset pulse; $R_{PUP} = 2.2k\Omega$ | 5                  |     |                        | - µs  |

| Rising-Edge Hold-Off Time       | <b>4</b>          | Standard speed                                                         |                    |     | 5.0                    |       |

| (Notes 5, 13)                   | <sup>t</sup> REH  | Overdrive speed                                                        | Not applicable (0) |     | (0)                    | μs    |

| Time Slot Duration              | touer             | Standard speed                                                         | 65                 |     |                        | 110   |

| (Notes 2, 14)                   | tslot             | Overdrive speed                                                        | 8                  |     |                        | μs    |

| IO PIN: 1-Wire RESET, PRESEN    | CE-DETECT         | CYCLE                                                                  |                    |     |                        |       |

| Donat Low Time (Note 2)         | toon              | Standard speed                                                         | lard speed 480     |     | 640                    |       |

| Reset Low Time (Note 2)         | <sup>t</sup> RSTL | Overdrive speed                                                        | 48                 |     | 80                     | μs    |

| Presence-Detect High Time       | too               | Standard speed                                                         | 15                 |     | 60                     |       |

| Fresence-Detect Fight Time      | t <sub>PDH</sub>  | Overdrive speed                                                        | 2 6                |     | 6                      | - µs  |

| Presence-Detect Low Time        | topi              | Standard speed                                                         | 60                 |     | 240                    | 110   |

| Tresence-Detect Low Tille       | t <sub>PDL</sub>  | Overdrive speed                                                        | 8                  |     | 24                     | μs    |

| Presence-Detect Sample Time     | twon              | Standard speed                                                         | 60                 |     | 75                     | μs    |

| (Notes 2, 15)                   | tMSP              | Overdrive speed                                                        | 6                  |     | 10                     | μο    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(T_A = -40$ °C to +85°C, unless otherwise noted.) (Note 1)

| PARAMETER                                | SYMBOL           | CONDITIONS                               | MIN T             | YP MAX | UNITS |  |

|------------------------------------------|------------------|------------------------------------------|-------------------|--------|-------|--|

| IO PIN: 1-Wire WRITE                     |                  |                                          | ·                 |        |       |  |

| W. 7 . T.                                |                  | Standard speed                           | 60                | 120    |       |  |

| Write-Zero Low Time<br>(Notes 2, 16, 17) | twoL             | Overdrive speed, V <sub>PUP</sub> > 4.5V | 5                 | 15.5   | μs    |  |

|                                          |                  | Overdrive speed                          | 6                 | 15.5   |       |  |

| Write-One Low Time                       | t                | Standard speed                           | 1                 | 15     | 110   |  |

| (Notes 2, 17)                            | t <sub>W1L</sub> | Overdrive speed                          | 1                 | 2      | μs    |  |

| IO PIN: 1-Wire READ                      |                  |                                          |                   |        |       |  |

| Read Low Time                            | to               | Standard speed                           | 5                 | 15 - δ | 0     |  |

| (Notes 2, 18)                            | t <sub>RL</sub>  | Overdrive speed                          | 1                 | 2 - δ  | μs    |  |

| Read Sample Time                         | tuon             | Standard speed                           | $t_{RL} + \delta$ | 15     | 110   |  |

| (Notes 2, 18)                            | IMSR             | t <sub>MSR</sub> Overdrive speed         |                   | 2      | μs    |  |

| EEPROM                                   |                  |                                          |                   |        |       |  |

| Programming Current                      | IPROG            | (Notes 5, 19)                            |                   | 0.8    | mA    |  |

| Programming Time                         | tprog            | (Note 20)                                |                   | 10     | ms    |  |

| Write/Erase Cycles (Endurance)           | Nov              | At +25°C                                 | 200k              |        |       |  |

| (Notes 21, 22)                           | NCY              | At +85°C (worst case)                    | 50k               |        | _     |  |

| Data Retention<br>(Notes 23, 24, 25)     | t <sub>DR</sub>  | At +85°C (worst case)                    | 40                |        | Years |  |

- Note 1: Specifications at T<sub>A</sub> = -40°C are guaranteed by design only and not production tested.

- Note 2: System requirement.

- **Note 3:** Maximum allowable pullup resistance is a function of the number of 1-Wire devices in the system and 1-Wire recovery times. The specified value here applies to systems with only one device and with the minimum 1-Wire recovery times. For more heavily loaded systems, an active pullup such as that found in the DS2482-x00, DS2480B, or DS2490 may be required.

- Note 4: Maximum value represents the internal parasite capacitance when V<sub>PUP</sub> is first applied. If a 2.2kΩ resistor is used to pull up the data line, 2.5μs after V<sub>PUP</sub> has been applied, the parasite capacitance does not affect normal communications.

- Note 5: Guaranteed by design, characterization, and/or simulation only. Not production tested.

- **Note 6:** V<sub>TL</sub>, V<sub>TH</sub>, and V<sub>HY</sub> are a function of the internal supply voltage, which is a function of V<sub>PUP</sub>, R<sub>PUP</sub>, 1-Wire timing, and capacitive loading on IO. Lower V<sub>PUP</sub>, higher R<sub>PUP</sub>, shorter t<sub>REC</sub>, and heavier capacitive loading all lead to lower values of V<sub>TL</sub>, V<sub>TH</sub>, and V<sub>HY</sub>.

- **Note 7:** Voltage below which, during a falling edge on IO, a logic 0 is detected.

- Note 8: The voltage on IO must be less than or equal to VILMAX at all times the master is driving IO to a logic 0 level.

- Note 9: Voltage above which, during a rising edge on IO, a logic 1 is detected.

- Note 10: After V<sub>TH</sub> is crossed during a rising edge on IO, the voltage on IO must drop by at least V<sub>HY</sub> to be detected as logic 0.

- Note 11: The I-V characteristic is linear for voltages less than 1V.

- Note 12: Applies to a single device attached to a 1-Wire line.

- Note 13: The earliest recognition of a negative edge is possible at tREH after VTH has been reached on the preceding rising edge.

- Note 14: Defines maximum possible bit rate. Equal to twoLMIN + trecmin.

- Note 15: Interval after t<sub>RSTL</sub> during which a bus master is guaranteed to sample a logic 0 on IO if there is a DS1972 present. Minimum limit is t<sub>PDHMAX</sub>; maximum limit is t<sub>PDHMIN</sub> + t<sub>PDLMIN</sub>.

- Note 16: Numbers in **bold** are **not** in compliance with legacy 1-Wire product standards. See the *Comparison Table*.

- **Note 17:**  $\epsilon$  in Figure 11 represents the time required for the pullup circuitry to pull the voltage on IO up from  $V_{IL}$  to  $V_{TH}$ . The actual maximum duration for the master to pull the line low is  $t_{W1LMAX} + t_F \epsilon$  and  $t_{W0LMAX} + t_F \epsilon$ , respectively.

- **Note 18:** δ in Figure 11 represents the time required for the pullup circuitry to pull the voltage on IO up from V<sub>IL</sub> to the input-high threshold of the bus master. The actual maximum duration for the master to pull the line low is t<sub>RL MAX</sub> + t<sub>F</sub>.

- **Note 19:** Current drawn from IO during the EEPROM programming interval. The pullup circuit on IO during the programming interval should be such that the voltage at IO is greater than or equal to V<sub>PUPMIN</sub>. If V<sub>PUP</sub> in the system is close to V<sub>PUPMIN</sub>, a low-impedance bypass of R<sub>PUP</sub>, which can be activated during programming, may need to be added.

- **Note 20:** Interval begins t<sub>REHMAX</sub> after the trailing rising edge on IO for the last time slot of the E/S byte for a valid Copy Scratchpad sequence. Interval ends once the device's self-timed EEPROM programming cycle is complete and the current drawn by the device has returned from I<sub>PROG</sub> to I<sub>L</sub>.

- Note 21: Write-cycle endurance is degraded as TA increases.

- Note 22: Not 100% production tested; guaranteed by reliability monitor sampling.

- Note 23: Data retention is degraded as TA increases.

- **Note 24:** Guaranteed by 100% production test at elevated temperature for a shorter time; equivalence of this production test to the data sheet limit at operating temperature range is established by reliability testing.

- **Note 25:** EEPROM writes can become nonfunctional after the data-retention time is exceeded. Long-term storage at elevated temperatures is not recommended; the device can lose its write capability after 10 years at +125°C or 40 years at +85°C.

#### **COMPARISON TABLE**

|                                                 |                     | LEGACY      | VALUES                  |             | DS1972 VALUES |                 |                         |             |  |

|-------------------------------------------------|---------------------|-------------|-------------------------|-------------|---------------|-----------------|-------------------------|-------------|--|

| PARAMETER                                       | STANDARD SPEED (µs) |             | OVERDRIVE SPEED<br>(µs) |             | _             | RD SPEED<br>is) | OVERDRIVE SPEED<br>(µs) |             |  |

|                                                 | MIN                 | MAX         | MIN                     | MAX         | MIN           | MAX             | MIN                     | MAX         |  |

| t <sub>SLOT</sub> (including t <sub>REC</sub> ) | 61                  | (undefined) | 7                       | (undefined) | 65*           | (undefined)     | 8*                      | (undefined) |  |

| trstl                                           | 480                 | (undefined) | 48                      | 80          | 480           | 640             | 48                      | 80          |  |

| tPDH                                            | 15                  | 60          | 2                       | 6           | 15            | 60              | 2                       | 6           |  |

| tPDL                                            | 60                  | 240         | 8                       | 24          | 60            | 240             | 8                       | 24          |  |

| twoL                                            | 60                  | 120         | 6                       | 16          | 60            | 120             | 6                       | 15.5        |  |

<sup>\*</sup>意図的な変更。回復時間が長くなったのは、1-Wireフロントエンドの改良によります。

注:太字の数値は、従来の1-Wire製品の規格に準拠していません。

#### 詳細

DS1972は、1024ビットのEEPROM、最大7バイトの ユーザ用読取り/書込みバイトを備える8バイトのレジスタ/ 制御ページ、およびフル機能の1-Wireインタフェース を耐久性の高いiButtonパッケージ内に統合しています。 各DS1972は固有の64ビットROM登録番号を持って います。この登録番号は出荷時にレーザで書き込まれ、 絶対追跡を保証する固有のIDを提供します。データは 1-Wireプロトコルを通じてシリアル転送されます。これ には1つのデータ接点とグランドリターンしか必要あり ません。DS1972は、メインメモリまたはレジスタ ページへの書込み時にバッファとして機能するスクラッチ パッドと呼ばれる追加メモリ領域を備えています。データ はまずスクラッチパッドに書き込まれ、そこからデータ を読み戻すことができます。データが検証された後に、 Copy Scratchpadコマンドによって、そのデータは 最終メモリ位置に転送されます。DS1972のアプリケー ションには、アクセス制御/パーキングメータ、仕掛品 (WIP)追跡、ツール管理、在庫管理、および保守/検査 データストレージなどがあります。DS1972との通信用 のソフトウェアは、japan.maxim-ic.com/ibuttonから 無料ダウンロードして、入手することができます。

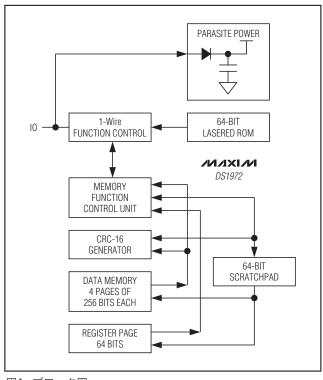

#### 概要

図1のブロック図は、DS1972の主な制御セクションとメモリセクションの関係を示しています。DS1972は、1) 64ビットのレーザ書込みROM、2) 64ビットのスクラッチパッド、3) 4 x 32バイトページのEEPROM、および4) 64ビットのレジスタページの4つの主要なデータ構成要素から構成されています。

図1. ブロック図

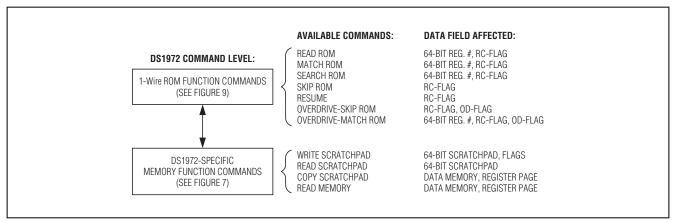

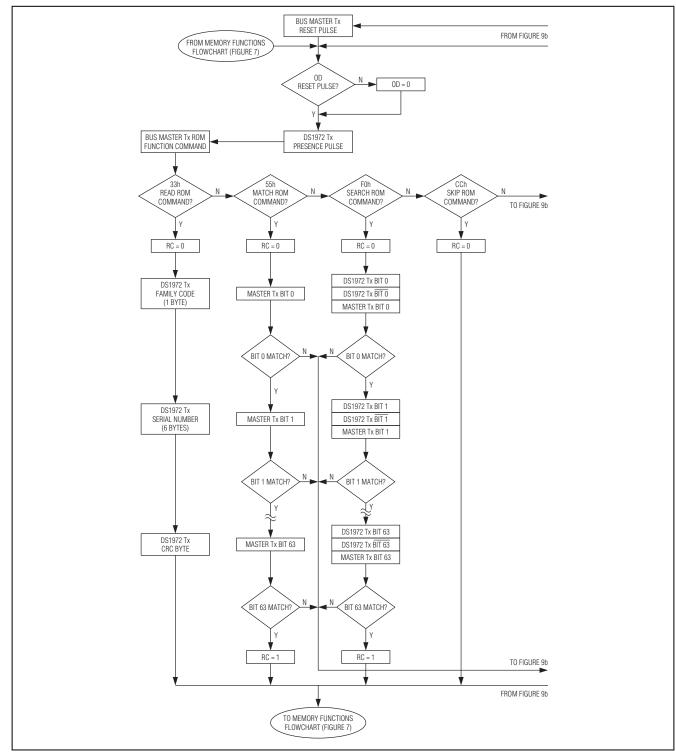

1-Wireプロトコルの階層構造は、図2に示されています。 バスマスターはまず、以下の7つのROM機能コマンドの いずれか1つを送出する必要があります。1) Read ROM (ROM読取り)、2) Match ROM (ROM一致)、3) Search ROM (ROM検索)、4) Skip ROM (ROMスキップ)、5) Resume (再開)、6) Overdrive-Skip ROM (ROMオー バードライブスキップ)、または7) Overdrive-Match ROM (ROMオーバードライブ一致)。標準速度で実行さ

図2. 1-Wireプロトコルの階層構造

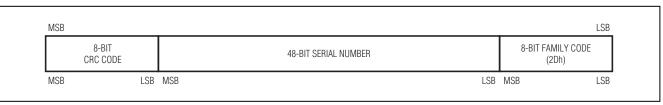

図3.64ビットレーザ書込みROM

図4. 1-Wire CRC生成器

れる、Overdrive-Skip ROMコマンドまたはOverdrive-Match ROMコマンドバイトが終了すると、デバイスはオーバードライブモードに移行し、このモードでは以後の通信はすべて標準速度より高い速度で行われます。これらのROM機能コマンドに要求されるプロトコルは、図9に記載されています。ROM機能コマンドが正常に実行されると、メモリ機能へのアクセスが可能になり、マスターは4つのメモリ機能コマンドのいずれか1つを送出することができます。これらのメモリ機能コマンドのプロトコルは、図7に記載されています。すべてのデータは、最下位ビットを先頭に読取りと書込みが行われます。

#### 64ビットレーザ書込みROM

各DS1972は、64ビット長の固有のROMコードを備えています。先頭からの8ビットは、1-Wireのファミリコードです。その次の48ビットは、固有のシリアル

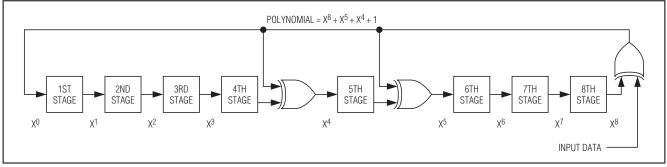

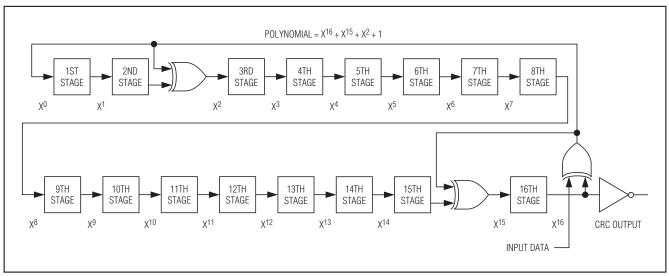

番号です。最後の8ビットは、先頭から56ビットのCRC (巡回冗長検査)です。詳細については図3を参照してください。図4に示されるように、シフトレジスタとXOR ゲートから構成される生成多項式によって1-Wire CRC が生成されます。この多項式は、 $X^8+X^5+X^4+1$ です。1-Wire CRCに関する詳細は、アプリケーションノート27 「マキシムのiButton製品に用いる巡回冗長検査(CRC)の理解と用法」に記載されています。

シフトレジスタの各ビットは、Oに初期化されます。次にファミリコードの最下位ビットから始まり、1度に1ビットずつシフトインされます。ファミリコードの8番目のビットが入力されると、シリアル番号が入力されます。シリアル番号の最後のビットが入力されると、シフトレジスタはCRCの値を備えています。CRCの8ビットをシフトインすると、シフトレジスタはすべて0に戻ります。

#### メモリアクセス

データメモリとレジスタは、図5に示すようにリニアア ドレス空間内にあります。データメモリとレジスタは、 無制限に読取りアクセスすることができます。DS1972 のEEPROMアレイは、各8バイトの18列で構成されます。 最初の16列は、4メモリページ(ページ当り32バイト)に 均等に分割されています。これら4ページは一次データ メモリです。レジスタ列内の対応する保護バイトを設定 して、各ページをオープン(非保護)、書込み保護、または EPROMモードに個別に設定することができます。最後 の2列は、保護レジスタと予備バイトで構成されます。 レジスタ列は、4バイトの保護制御バイト、1バイトの コピー防止バイト、ファクトリバイト、および2バイト のユーザバイト/製造メーカーIDバイトで構成されます。 製造メーカーIDは、ユーザ設定のIDコードでもかまいま せん。アプリケーションソフトウェアでこのIDコードを 使用すると、DS1972が使われている製品を識別するの

に役立ちます。カスタムの製造メーカーIDの設定と登録については、お問い合わせください。最終列は予備です。この最終列はR/W機能に関して未定義であり、使用しないでください。

メインEEPROMアレイのほかに、8バイトの揮発性スクラッチパッドも内蔵しています。EEPROMアレイへの書込みは、2段階のプロセスで行われます。データはまずスクラッチパッドに書き込まれ、続いてメインアレイにコピーされます。このプロセスによって、メインアレイにコピーされる前に、まずスクラッチパッドに書き込まれたデータを検証することができます。このデバイスは、全列(8バイト)のコピー動作のみをサポートします。スクラッチパッドのデータがコピー動作に適合するようにするには、Write Scratchpadコマンドと共に与えられるアドレスが列の境界で始まり、全8バイトのデータがスクラッチパッドに書き込まれる必要があります。

| ADDRESS RANGE  | TYPE  | DESCRIPTION                    | PROTECTION CODES                                                                |

|----------------|-------|--------------------------------|---------------------------------------------------------------------------------|

| 0000h to 001Fh | R/(W) | Data Memory Page 0             | _                                                                               |

| 0020h to 003Fh | R/(W) | Data Memory Page 1             | _                                                                               |

| 0040h to 005Fh | R/(W) | Data Memory Page 2             | _                                                                               |

| 0060h to 007Fh | R/(W) | Data Memory Page 3             | _                                                                               |

| 0080h*         | R/(W) | Protection-Control Byte Page 0 | 55h: Write Protect P0; AAh: EPROM Mode P0; 55h or AAh: Write Protect 80h        |

| 0081h*         | R/(W) | Protection-Control Byte Page 1 | 55h: Write Protect P1; AAh: EPROM Mode P1; 55h or AAh: Write Protect 81h        |

| 0082h*         | R/(W) | Protection-Control Byte Page 2 | 55h: Write Protect P2; AAh: EPROM Mode P2; 55h or AAh: Write Protect 82h        |

| 0083h*         | R/(W) | Protection-Control Byte Page 3 | 55h: Write Protect P3; AAh: EPROM Mode P3; 55h or AAh: Write Protect 83h        |

| 0084h*         | R/(W) | Copy Protection Byte           | 55h or AAh: Copy Protect 0080h:008Fh, and Any Write-Protected Pages             |

| 0085h          | R     | Factory Byte. Set at Factory.  | AAh: Write Protect 85h, 86h, 87h;<br>55h: Write Protect 85h; Unprotect 86h, 87h |

| 0086h          | R/(W) | User Byte/Manufacturer ID      | _                                                                               |

| 0087h          | R/(W) | User Byte/Manufacturer ID      | _                                                                               |

| 0088h to 008Fh | _     | Reserved                       | _                                                                               |

<sup>\*</sup>このアドレスはAAhまたは55hに設定されると、読取り専用になります。他のどのコードも保存することができますが、アドレスは書込み保護されず、また機能も作動しません。

図5. メモリマップ

保護制御レジスタは、Write Scratchpadコマンドで受信データがスクラッチパッドにロードされる方法を決定します。55hの保護設定(書込み保護)によって、受信データは無視され、宛先アドレスのメインメモリデータがスクラッチパッドにロードされます。AAhの保護設定(EPROMモード)によって、受信データと宛先アドレスのメインメモリデータとの論理積がスクラッチパッドにロードされます。保護制御レジスタのその他の設定によって、対応するメモリページはオープンのままとなり、無制限にアクセスして書き込むことができます。また、55hまたはAAhの保護制御バイト設定は保護制御バイト設定は保護制御バイトの書込み保護も行います。55hの保護制御バイト設定によって、コピーは阻止されません。このため、書込み保護されたデータをデバイス内でリフレッシュすることができます(すなわち最新データで再設定可能)。

コピー防止バイトは高度なセキュリティ用に使用され、他のすべての保護制御バイト、ユーザバイト、および書込み保護ページが各々の最終値に設定された場合に限り、コピー防止バイトを使用してください。コピー防止バイトを55hまたはAAhに設定すると、レジスタ列とユーザバイト列へのコピーの試みはすべて阻止されます。また、書込み保護されたメインメモリページへのコピーの試み(すなわちリフレッシュ)はすべて阻止されます。

#### アドレスレジスタおよび転送ステータス

DS1972は、TA1、TA2、およびE/Sの3つのアドレスレジスタを使用します(図6)。これらのレジスタは他の多くの1-Wireデバイスと共通していますが、DS1972では動作が少し異なります。レジスタTA1およびTA2には、データの書込み先やデータの読取り元の宛先アドレスをロードする必要があります。レジスタE/Sは読取り専用の転送ステータスレジスタであり、書込みコマンドによるデータ完全性を検証するために使用されます。E/SビットE[2:0]にはWrite Scratchpadコマンドで受信され

るT[2:0]がロードされ、後続のデータバイトごとにイン クリメントされます。これは、事実上、8バイトスク ラッチパッド内のバイト終了オフセットカウンタです。 PFと呼ばれるE/Sレジスタのビット5は、スクラッチパッド 内のデータが電源喪失によって無効の場合や、マスター が送信するバイト数がスクラッチパッドの最後に達する のに必要なバイト数よりも少ない場合は、ロジック1と なります。スクラッチパッドへの書込みを有効にする には、T[2:0]が0である必要があり、マスターは8データ バイトを送信済みである必要があります。ビット3、4、 および6には機能がありません。これらのビットは常に 0を読み取ります。AAまたは認証承認(Authorization Accepted)と呼ばれるE/Sレジスタの最上位ビットは、 スクラッチパッドに保存されたデータが宛先メモリアド レスに既にコピー済みであることを示すフラグとして 機能します。スクラッチパッドにデータを書き込むと、 このフラグはクリアされます。

#### 書込みと検証

データをDS1972に書き込むには、スクラッチパッド を中間記憶として使用する必要があります。まず、 マスターがWrite Scratchpadコマンドを送出して、 所望の宛先アドレスを指定します。これに続いて、 スクラッチパッドに書き込むデータが送出されます。 なお、Copy Scratchpadコマンドは、8バイト境界で 実行される必要があります。すなわち、宛先アドレス (T2、T1、T0)の3つのLSBは000bである必要があり ます。非ゼロ値のT[2:0]が送信されると、コピー機能が 阻止されます。特定の条件下(「Write Scratchpad [OFh]」 の項を参照)では、マスターはWrite Scratchpadコマンド シーケンスの最後にコマンド、アドレス(送信された実際 のアドレス)、およびデータの反転CRC-16を受信する ことになります。マスターはこのCRCの値を知り、その 値をマスターが自ら計算した値と照合して、通信が成功 したかどうかを判定し、Copy Scratchpadコマンドに

| BIT#                                                    | 7   | 6   | 5   | 4   | 3   | 2   | 1  | 0  |

|---------------------------------------------------------|-----|-----|-----|-----|-----|-----|----|----|

| TARGET ADDRESS (TA1)                                    | Т7  | T6  | T5  | T4  | Т3  | T2  | T1 | TO |

| TARGET ADDRESS (TA2)                                    | T15 | T14 | T13 | T12 | T11 | T10 | Т9 | Т8 |

| ENDING ADDRESS WITH<br>DATA STATUS (E/S)<br>(READ ONLY) | AA  | 0   | PF  | 0   | 0   | E2  | E1 | E0 |

図6. アドレスレジスタ

進むことができます。マスターがCRC-16を受け取ることができない場合は、Read Scratchpadコマンドを送信してデータ完全性を検証する必要があります。DS1972は、スクラッチパッドデータのプリアンブルとして宛先アドレスTA1およびTA2を繰り返し、E/Sレジスタの内容を送信します。PFフラグがセットされている場合は、データがスクラッチパッドに正常に到達しなかったか、またはデータが最後にスクラッチパッドに書き込まれた以降に電源喪失があったことになります。この場合、マスターは読取りを続ける必要はありません。マスターはデータをスクラッチパッドに書き込む新たな試行を開始することができます。同様に、AAフラグがセットされ、かつPFフラグがクリアされている場合は、デバイスがWrite Scratchpadコマンドを認識しなかったことを示します。

すべてが正しく実行されると、両フラグがクリアされます。この場合、マスターは全データバイトの読取りと検証を続けることができます。マスターがデータを検証した後に、Copy Scratchpadコマンドなどを送出することができます。このコマンドの後には、TA1、TA2、およびE/Sという3つのアドレスレジスタのデータが正しく続く必要があります。マスターは、スクラッチパッドを読み取って、これらのレジスタの内容を取得する必要があります。

#### メモリ機能コマンド

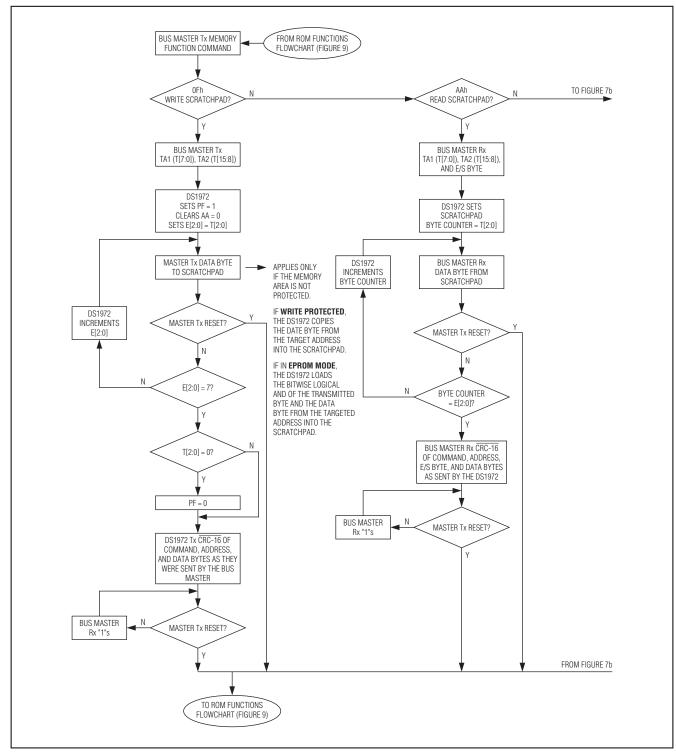

「メモリ機能のフローチャート」(図7)は、DS1972のメモリにアクセスするのに必要なプロトコルを示しています。これらの機能を使って、デバイスを読み書きする方法例は、「メモリ機能の例」の項に記載されています。マスターとDS1972間の通信は、標準速度(デフォルト、OD = 0)、またはオーバードライブ速度(OD = 1)のいずれかで行われます。オーバードライブモードに明確に設定されていない場合は、DS1972は標準速度で動作します。

#### Write Scratchpad [0Fh]

Write Scratchpadコマンドは、データメモリと、レジスタページの書込み可能なアドレスに適用されます。スクラッチパッドデータをアレイへのコピーが可能なデータにするには、正しい列境界で始まる8バイトのWrite Scratchpadコマンドを実行する必要があります。Write Scratchpadコマンドは、無効なアドレスおよび一部の列を受取り可能ですが、後続のCopy Scratchpadコマンドは阻止されます。

マスターはWrite Scratchpadコマンドを送出した後に、まず2バイトの宛先アドレス、それに続いてスクラッチパッドに書き込まれるデータを送出する必要があります。

そのデータは、T[2:0]のバイトオフセットからスクラッチパッドに書き込まれます。E/SビットE[2:0]には先頭バイトオフセットがロードされ、後続のバイトごとにインクリメントされます。実質的に、E[2:0]はスクラッチパッドに書き込まれた最終フルバイトのバイトオフセットを表しています。フルデータバイトのみが受け入れられます。

Write Scratchpadコマンドを実行すると、DS1972内のCRC生成器(図13参照)は、コマンドコードから始まり、マスターから送出される最後のデータバイトで終了するデータストリーム全体のCRCを計算します。まずCRC生成器をクリアしてから、Write Scratchpadコマンドのコマンドコード(OFh)、宛先アドレス(TA1およびTA2)、および全データバイトをシフトインすることによって、このCRCがCRC-16多項式を使って生成されます。なお、CRC-16の計算は、マスターが送信する実際のTA1とTA2およびデータを使用して行われます。マスターは、いつでもWrite Scratchpadコマンドを終了することができます。ただし、スクラッチパッドの最後に達した場合(E[2:0] = 111b)は、マスターは16個の読取りタイムスロットを送出し、DS1972が生成したCRCを受け取ることができます。

Write Scratchpadコマンドが書込み保護領域に実行されようとすると、スクラッチパッドには送出データではなくメモリ内の既存データがロードされます。同様に、宛先アドレスページがEPROMモード状態の場合は、スクラッチパッドには、送出データとメモリ内の既存データのビット単位の論理積がロードされます。

#### Read Scratchpad [AAh]

Read Scratchpadコマンドを使って、宛先アドレス およびスクラッチパッドデータの完全性を検証すること ができます。マスターはこのコマンドコードを送出する と、読取りを開始します。先頭の2バイトは、宛先アド レスです。その次のバイトは終了オフセット/データ ステータスバイト(E/S)と、続いてスクラッチパッド データであり、このスクラッチパッドデータはマスター が当初送出したものと異なる場合があります。このこと は、宛先アドレスがレジスタページ内、または書込み 保護モードやEPROMモード状態のページ内にある場合 は、特に重要です。詳細については、「Write Scratchpad [OFh]]の項を参照してください。マスターは、スク ラッチパッド(E[2:0] - T[2:0] + 1バイト)をすべて読み 取る必要があります。この後に、マスターは、DS1972 から送信されたデータに基づく反転CRCを受け取ります。 マスターがCRCを受信した後に読取りを継続すると、 すべてのデータはロジック1になります。

図7a. メモリ機能のフローチャート

図7b. メモリ機能のフローチャート(続き)

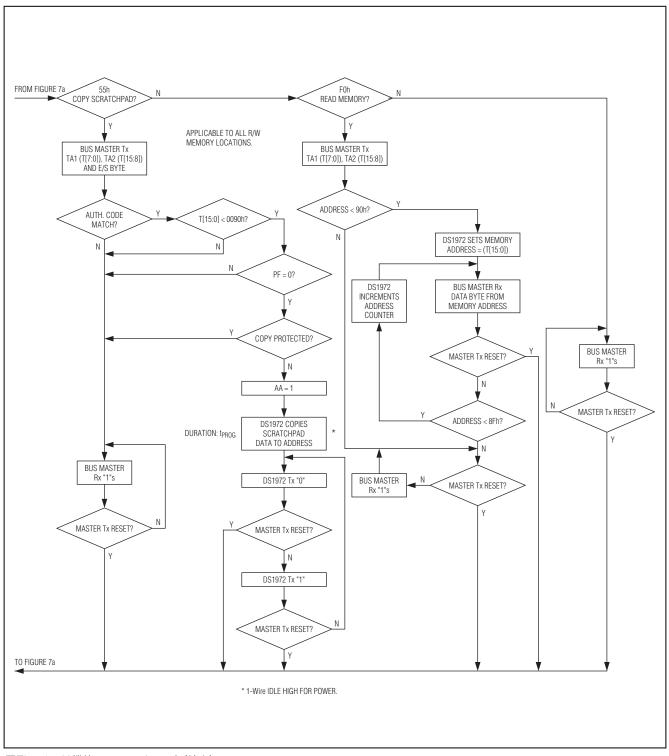

#### Copy Scratchpad [55h]

Copy Scratchpadコマンドを使って、スクラッチパッド から書込み可能メモリセクションにデータをコピーする ことができます。マスターはCopy Scratchpadコマンドを 送出した後に、3バイトの認証パターンを送出する必要 があります。このパターンは、直前のRead Scratchpad コマンドによって取得済みである必要があります。この 3バイトのパターンは、3つのアドレスレジスタ(TA1、 TA2、E/Sの順序)内のデータと完全に一致する必要が あります。パターンが一致し、宛先アドレスが有効で、 PFフラグが未設定で、宛先メモリがコピー防止されてい ない場合は、AA (認証承認)フラグがセットされ、コピー が始まります。全8バイトのスクラッチパッドの内容が、 宛先メモリ位置にコピーされます。デバイスの内部デー 夕転送時間はt<sub>PROG</sub>であり、その間は、1-Wireバス上の 電圧は2.8Vを下回ってはいけません。データがコピー されてから、マスターがリセットパルスを送出するまで、 0と1の交互のパターンが送信されます。PFフラグが セットされているか、または宛先メモリがコピー防止 状態の場合は、コピーは始まらず、AAフラグはセット されません。

コピーコマンドが電力不足やその他の理由によって妨げられた場合は、マスターは1-Wire Reset Pulseを送出するまでFFhバイトの一定ストリームを読み取ります。この場合は、宛先メモリが不完全に設定されるおそれがあり、EEPROMを適切に設定するためにWrite ScratchpadおよびCopy Scratchpadを繰り返す必要があります。このため、断続接触環境でDS1972に書き込むアプリケーションソフトウェアを設計する際には、十分検討する必要があります。

#### Read Memory [F0h]

Read Memoryコマンドは、DS1972からデータを読み取るための汎用機能です。コマンド送出後に、マスターは2バイトの宛先アドレスを送出する必要があります。この2バイトの後に、マスターは宛先アドレスから始まるデータを読み取り、アドレス008Fhまで読取りを続けることができます。マスターがさらに読取りを続行すると、その結果はロジック1になります。デバイス内部のTA1、TA2、E/S、およびスクラッチパッドの内容は、Read Memoryコマンドによって影響を受けません。

#### 1-Wireバスシステム

1-Wireバスは、単一のバスマスターと、1つまたは複数のスレーブで構成されるシステムです。いかなる場合でも、DS1972はスレーブデバイスです。バスマスターは、通常はマイクロコントローラです。このバスシステムの説明は、ハードウェア構成、トランザクション

シーケンス、および1-Wire信号方式(信号種類とタイミング)の3つのトピックに分類されます。1-Wireプロトコルでは、バスマスターからの同期パルスの立下りエッジで始まる特定タイムスロット中のバスの状態によって、バストランザクションが定義されます。

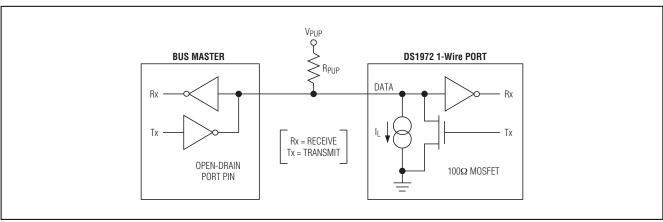

#### ハードウェア構成

1-Wireバスはその名のとおり1本の線しか備えていません。バス上の各デバイスは適時このバスを駆動可能である必要があります。これを容易にするために、1-Wireバスに接続された各デバイスの出力はオープンドレイン出力またはトライステート出力である必要があります。DS1972の1-Wireポートは、図8に示すものと等価な内部回路を備えるオープンドレインです。

マルチドロップバスは、複数のスレーブが接続された 1-Wireバスから構成されます。DS1972は、15.4kbps (max)の標準通信速度と125kbps (max)のオーバードライブ通信速度をともにサポートしています。なお、1-Wireの旧製品は、16.3kbpsの標準通信速度と142kbpsのオーバードライブ通信速度をサポートしています。DS1972の通信速度が少し低下したのは、回復時間を増加したためです。これは、1-Wireの物理的インタフェースを強化して、ノイズ耐性を向上するためでした。プルアップ抵抗の値は、主にネットワーク規模と負荷状態に依存します。DS1972には、いずれの速度でも2.2kΩ (max)のプルアップ抵抗が必要です。

1-Wireバスのアイドル状態はハイです。なんらかの理由でトランザクションを一時停止する必要がある場合は、その後トランザクションが再開するためには、バスをアイドル状態に維持する必要があります。バスをアイドル状態にせず、バスが16μs (オーバードライブ速度)、または120μs (標準速度)を超えてロー状態に維持されると、バス上の1つまたは複数のデバイスがリセットされることがあります。

### トランザクションシーケンス

1-Wireポートを通じてDS1972にアクセスするための プロトコルは、以下のとおりです。

- 初期化

- ROM機能コマンド

- メモリ機能コマンド

- トランザクション/データ

#### 初期化

1-Wireバス上のすべてのトランザクションは初期化シーケンスから始まります。初期化シーケンスは、バスマスターから送出されるリセットパルスと、それに続く

図8. ハードウェア構成

(単数または複数の)スレーブが送出する(単数または複数の)プレゼンスパルスから構成されます。プレゼンスパルスは、DS1972がバス上にあり動作可能であることをバスマスターに通知します。詳細については、「1-Wire信号方式」の項を参照してください。

#### 1-Wire ROM機能コマンド

バスマスターがプレゼンスを検出すると、DS1972が サポートする7つのROM機能コマンドのいずれか1つを 送出することができます。いずれのROM機能コマンド も8ビット長です。これらのコマンドを以下に示します (図9のフローチャートを参照)。

#### Read ROM [33h]

Read ROMコマンドを使うと、バスマスターはDS1972の8ビットファミリコード、固有の48ビットシリアル番号、および8ビットCRCを読み取ることができます。バス上のスレーブが1個の場合に限り、このコマンドを使用することができます。複数のスレーブがバス上に存在する場合は、すべてのスレーブが同時に送信しようとすると、データの衝突が発生します(オープンドレインがワイヤードANDの結果を出力)。その結果、ファミリコードと48ビットシリアル番号によって、CRCの不整合が発生します。

#### Match ROM [55h]

Match ROMコマンドとこれに続く64ビットROMシーケンスによって、バスマスターはマルチドロップバス上の特定のDS1972のアドレスを指定することができます。64ビットROMシーケンスと完全に一致するDS1972のみが、以下のメモリ機能コマンドに応答します。その他すべてのスレーブは、リセットパルスを待ちます。このコマンドは、バス上の1つまたは複数のデバイスで使用することができます。

#### Search ROM [F0h]

システムが最初に立ち上がる際に、バスマスターが 1-Wireバス上のデバイスの数やデバイスの登録番号を 知らない場合があります。バスのワイヤードAND特性 を利用することによって、マスターは消去プロセスを 使って全スレーブデバイスの登録番号を識別すること ができます。登録番号のビットごとに、最下位ビット から、バスマスターは3つ1組のタイムスロットを送出 します。最初のタイムスロットでは、検索に関わる 各スレーブデバイスは各登録番号ビットの真値を出力 します。2番目のタイムスロットでは、検索に関わる 各スレーブデバイスは各登録番号ビットの補数値を出力 します。3番目のタイムスロットでは、マスターは選択 対象のビットの真値を書き込みます。マスターが書き 込んだビットと一致しないスレーブデバイスはすべて、 検索への関わりを停止します。両方の読取りビットが ゼロの場合は、マスターは、両方のビット状態のスレーブ デバイスが存在していることを認識します。書き込む 状態を選択することによって、バスマスターはROM コードツリー内で分岐します。1回の処理が完了すると、 バスマスターは単一デバイスの登録番号を認識します。 後続の処理によって、残りのデバイスの登録番号が識別 されます。事例を含む詳細については、アプリケーション ノート187「1-Wire検索アルゴリズム」を参照してくだ さい。

#### Skip ROM [CCh]

シングルドロップバスシステムでこのコマンドを使えば、バスマスターが64ビットROMコードを送出せずにメモリ機能にアクセスすることができるようになり、時間を節約することができます。複数のスレーブがバス上にある場合、たとえば、Skip ROMコマンドに続いてReadコマンドが送出されると、複数のスレーブが同時に送信するため、データの衝突がバス上で発生します(オープンドレインのプルダウンがワイヤードANDの結果を出力)。

図9a. ROM機能のフローチャート

図9b. ROM機能のフローチャート(続き)

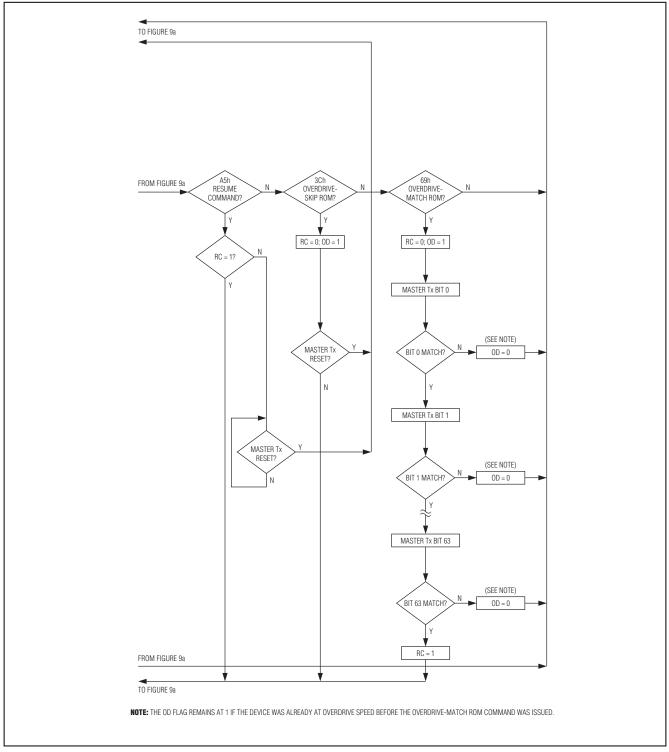

#### Resume [A5h]

マルチドロップ環境においてデータスループットを最大にするために、Resumeコマンドを利用することができます。このコマンドではRCビットの状態をチェックし、これがセットされている場合はSkip ROMコマンドと同様に、メモリ機能コマンドに直ちに制御を移します。RCビットは、Match ROM、Search ROM、またはOverdrive-Match ROMコマンドを正常に実行することによってのみセットされます。RCビットがセットされると、Resumeコマンドによってデバイスに繰返しアクセスすることができます。バス上の別のデバイスがResumeコマンドに同時に応答しないようにすることができます。

#### Overdrive-Skip ROM [3Ch]

シングルドロップバスでこのコマンドを使えば、バスマスターが64ビットROMコードを送出せずにメモリ機能にアクセスすることができるようになり、時間を節約することができます。通常のSkip ROMコマンドとは異なり、Overdrive-Skip ROMコマンドはDS1972をオーバードライブモード(OD = 1)に設定します。最小持続時間が $480\mu$ sのリセットパルスがバス上の全デバイスを標準速度(OD = 0)にリセットするまで、このコマンドに続くすべての通信はオーバードライブ速度で行われる必要があります。

このコマンドがマルチドロップバスで送出されると、オーバードライブに対応しているすべてのデバイスはオーバードライブモードに設定されます。続いて、特定のオーバードライブ対応デバイスをアドレス指定するには、オーバードライブ対応でのリセットパルスに続いて、Match ROMまたはSearch ROMコマンドシーケンスを送出する必要があります。これによって、検索プロセスの時間が短縮されます。複数のオーバードライブ対応スレーブがバス上にあり、Overdrive-Skip ROMコマンドの後にReadコマンドが続く場合は、複数のスレーブが同時に送信するため、データの衝突がバス上で発生します(オープンドレインのプルダウンがワイヤードAND結果を出力)。

#### Overdrive-Match ROM [69h]

Overdrive-Match ROMコマンドの後にオーバードライブ 速度で64ビットROMシーケンスが送出されると、バスマスターがマルチドロップバス上の特定のDS1972のアドレスを指定し、同時にオーバードライブモードに設定することができます。64ビットのROMシーケンスに完全に一致するDS1972のみが、後続のメモリ機能コマンドに応答します。前のOverdrive-Skip ROMコマンドまたは有効なOverdrive-Match ROMコマンドによってすでにオーバードライブモード状態のスレーブは、オー

バードライブモード状態を維持します。オーバードライブ対応スレーブはすべて、最小持続時間が480µsの次のリセットパルスで標準速度に戻ります。Overdrive-Match ROMコマンドは、バス上の1つまたは複数のデバイスで使用することができます。

#### 1-Wire信号方式

DS1972には、データの完全性を保証する厳密なプロトコルが必要です。このプロトコルは、1つのラインで送出される4種類の信号方式で構成されます。すなわち、リセットパルスとプレゼンスパルスによるリセットシーケンス、write-zero (0の書込み)、write-one (1の書込み)、およびread-data (データの読取り)です。プレゼンスパルスを除いて、バスマスターがすべての立下りエッジを生成します。DS1972は、標準速度とオーバードライブ速度の2種類の速度で通信することができます。DS1972は、オーバードライブモードに明確に設定されていない限り、標準速度で通信します。オーバードライブモード状態の間は、高速タイミングがすべての波形に適用されます。

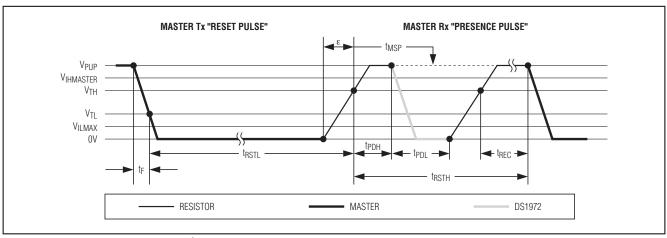

アイドル状態からアクティブに移行するには、1-Wire ライン上の電圧が $V_{PUP}$ からスレッショルド $V_{TL}$ 以下に降下する必要があります。アクティブからアイドル状態に移行するには、この電圧が $V_{ILMAX}$ からスレッショルド $V_{TH}$ 以上に上昇する必要があります。このような電圧の上昇に必要な時間は、図10に $\epsilon$ として示されています。その所要時間は、使用するプルアップ抵抗( $R_{PUP}$ )と、接続される1-Wireネットワークの容量によって決まります。電圧 $V_{ILMAX}$ は、DS1972におけるロジックレベルの決定に関係する値であり、イベントのトリガには関係しません。

図10は、DS1972との通信を開始するのに必要な初期化シーケンス示しています。リセットパルスの後にプレゼンスパルスが続くことは、適切なROMとメモリ機能コマンドが与えられる場合に、DS1972のデータ受信が可能であることを示します。バスマスターが立下りエッジでスルーレート制御を行う場合は、 $t_{RSTL}+t_{F}$ の間、ラインをプルダウンして、エッジを補償する必要があります。 $t_{RSTL}$ の持続時間が480 $\mu$ s以上の場合は、オーバードライブモードが終了し、デバイスは標準速度に戻ります。DS1972がオーバードライブモード状態にあり、 $t_{RSTL}$ が80 $\mu$ s以下の場合は、デバイスはオーバードライブモード状態で、 $t_{RSTL}$ が80 $\mu$ sの範囲内にある場合は、デバイスはリセットされますが、通信速度は決定されません。

バスマスターはラインを解放した後に、受信モードに移行します。このとき、1-Wireバスは、プルアップ抵抗によって、またはDS2482-x00やDS2480Bドライバの場合は能動回路によって、 $V_{PUP}$ にプルアップ

図10. 初期化手順: リセットおよびプレゼンスパルス

されます。スレッショルド $V_{TH}$ を超えると、DS1972は  $t_{PDH}$ の間待機してから、 $t_{PDL}$ の間ラインをローにプルダウンすることによって、プレゼンスパルスを送出します。プレゼンスパルスを検出するには、マスターは  $t_{MSP}$ の時点で1-Wireラインのロジック状態を検証する必要があります。

$t_{RSTH}$ ウィンドウは、 $t_{PDHMAX}$ 、 $t_{PDLMAX}$ 、および $t_{RECMIN}$  の総和以上でなければなりません。 $t_{RSTH}$ が経過すると直ちに、DS1972はデータ通信の準備が整います。さまざまなデバイスが存在するネットワークでは、他の1-Wireデバイスに対応するために、 $t_{RSTH}$ を標準速度で少なくとも480 $\mu$ sに、オーバードライブ速度で少なくとも48 $\mu$ sに延長する必要があります。

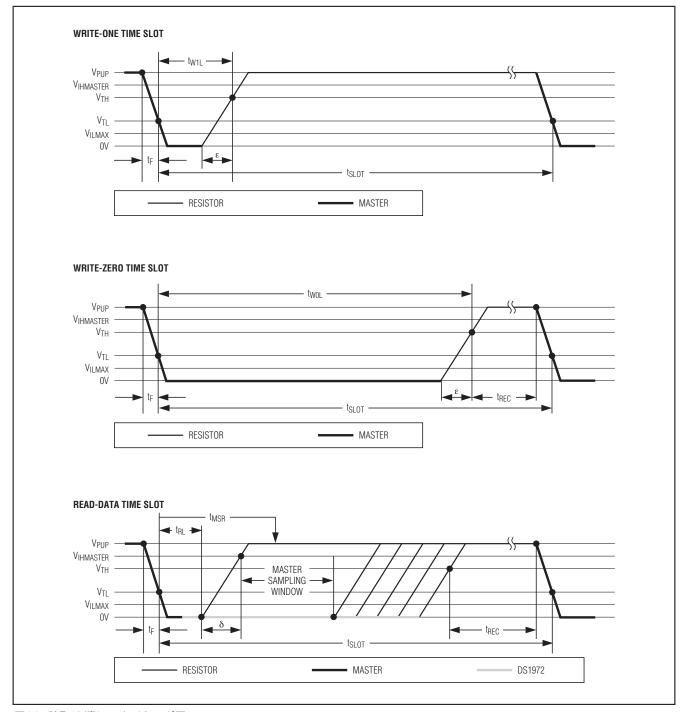

#### 読取り/書込みタイムスロット

DS1972とのデータ通信は、1ビットずつを搬送するタイムスロット(複数)で行われます。書込みタイムスロットは、データをバスマスターからスレーブに転送します。読取りタイムスロットは、データをスレーブからマスターに転送します。図11は、書込みおよび読取りタイムスロットの定義を示しています。

すべての通信は、マスターがデータラインをローにプルダウンして始まります。1-Wireライン上の電圧がスレッショルド $V_{TL}$ を下回ると、DS1972は内蔵タイミング発生器を起動します。これによって、書込みタイムスロット中にデータラインがサンプリングされる時点、および読取りタイムスロット中にデータが有効である時間が決定されます。

#### マスターからスレーブへ

**write-one**タイムスロットの場合は、write-oneのロータイム $t_{W1LMAX}$ が経過する前に、データラインの電圧が $V_{TH}$ スレッショルドを超えている必要があります。 **write-zero**タイムスロットの場合は、write-zeroのロータイム $t_{W0LMIN}$ が経過するまで、データラインの電圧が

$V_{TH}$ スレッショルドを下回っている必要があります。最も信頼性の高い通信にするには、データラインの電圧は、 $t_{WOL}$ または $t_{W1L}$ のウィンドウ全体にわたって $V_{ILMAX}$ を超えてはいけません。データラインの電圧が $V_{TH}$ スレッショルドを超えると、次のタイムスロットの用意ができるまでDS1972には回復時間 $t_{RFC}$ が必要です。

#### スレーブからマスターへ

read-dataタイムスロットは、write-oneタイムスロットと同様に始まります。データラインの電圧は、読取りロータイム $t_{RL}$ が経過するまで、 $V_{TL}$ を下回っている必要があります。DS1972は、0で応答するとき、 $t_{RL}$ ウィンドウの間にデータラインをローにプルダウンし始めます。その内部タイミング発生器は、このプルダウンを終了して電圧の再上昇を開始する時点を決定します。1で応答するとき、DS1972はデータラインをローに保持せず、 $t_{RL}$ が終了すると直ちに電圧が上昇し始めます。

一方の $t_{RI}$  +  $\delta$  (立上り時間)の合計、および他方のDS1972 の内部タイミング発生器によって、マスターのサンプ リングウィンドウ(t<sub>MSRMIN</sub>~t<sub>MSRMAX</sub>)が規定されます。 マスターは、このウィンドウ内でデータラインから読取 りを行う必要があります。最も信頼性の高い通信にする には、t<sub>RI</sub> をできる限り短くして、マスターはt<sub>MSRMAX</sub> 以内でt<sub>MSRMAX</sub>に近い時間で読み取る必要があります。 マスターはデータラインから読み取った後に、t<sub>SLOT</sub>が 経過するまで待機する必要があります。これによって、 DS1972が次のタイムスロットに備えるのに十分な回復 時間t<sub>RFC</sub>が保証されます。なお、ここで指定するt<sub>RFC</sub>は、 1-Wireラインに接続された単一のDS1972にのみ適用さ れます。複数のデバイス構成の場合は、追加の1-Wire デバイスの入力容量に対応するためにtRECを長くする 必要があります。代わりに、1-Wireラインドライバの DS2482-x00やDS2480Bなど、1-Wire回復時間の間 にアクティブプルアップを実行するインタフェースを使 用することもできます。

図11. 読取り/書込みタイミング図

#### ネットワーク動作の改善 (スイッチポイントヒステリシス)\_

1-Wire環境ではバスマスター(1-Wireドライバ)が制御 するトランジェントの間のみ、ライン終端が可能です。 このため、1-Wireネットワークはさまざまなノイズ源 からのノイズの影響を受けやすくなっています。ネット ワークの物理的サイズや構成に応じて、端点と分岐点 からの反射はある程度まで加算または相殺されること があります。こうした反射は、1-Wire通信ライン上に グリッチやリンギングとして現れます。また、外部 ノイズ源から1-Wireラインに結合されたノイズによって、 信号グリッチが発生する場合もあります。タイムスロット の立上りエッジ中のグリッチによってスレーブデバイス がマスターとの同期を失い、このためSearch ROM コマンドが停止したり、またはデバイス固有の機能 コマンドが異常終了したりするおそれがあります。 ネットワークアプリケーションの性能を改善するために、 DS1972は新しい1-Wireフロントエンドを使用し、 これによってノイズの影響を低減しています。

DS1972の1-Wireフロントエンドは、以下の3つの特性が従来のスレーブデバイスとは異なります。

- 1) タイムスロットの最初の立下りエッジを検出する回路 には、ローパスフィルタが追加されています。これ によって、高周波ノイズに対する感度が低減します。 この追加フィルタは、オーバードライブ速度では適用 されません。

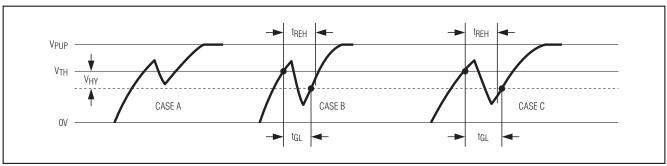

- 2) ローからハイへのスイッチングスレッショルド $V_{TH}$ に ヒステリシスがあります。負のグリッチが $V_{TH}$ を超えても、 $V_{TH}$   $V_{HY}$ を下回らない場合は、グリッチは認識されません(図12、Case A)。ヒステリシスは、いずれの1-Wire速度でも有効です。

- 3) 立上りエッジのホールドオフ時間 $t_{REH}$ によって規定される時間ウィンドウがあります。この間は、グリッチが $V_{TH}$   $V_{HY}$ のスレッショルドを下回ってもグリッチは無視されます(図12、Case B、 $t_{GL}$  <  $t_{REH}$ )。 $V_{TH}$  スレッショルドを超えた後しばらくして現れ、 $t_{REH}$

ウィンドウを超える深い電圧降下やグリッチはフィルタで取り除くことができず、新しいタイムスロットの開始として見なされます(図12、Case C、t<sub>GL</sub> ≥ t<sub>REH</sub>)。

電気的特性で規定されたパラメータ $V_{HY}$ および $t_{REH}$ を備えるデバイスは、改良型 $1-W_{II}$ でフロントエンドを採用しています。

#### CRCの生成

DS1972には、2種類のCRC (巡回冗長検査)があります。1つのCRCは8ビットタイプで、64ビットROMの最上位バイトに保存されています。バスマスターは64ビットROMの先頭の56ビットからCRCの値を計算し、この値をDS1972内に保存された値と比較して、ROMデータがエラーなしで受信されたかを判別することができます。このCRCの等価多項式関数は、 $X^8 + X^5 + X^4 + 1$ です。この8ビットCRCは、真値(非反転)形式で受け取られます。このCRCは出荷時に計算され、ROMにレーザで書き込まれます。

もう一つのCRCは16ビットタイプで、標準化された CRC-16多項式関数 $X^{16}+X^{15}+X^2+1$ に従って生成されます。このCRCを使って、スクラッチパッドとの間の読取りや書込み時に、データ転送を迅速に検証することができます。8ビットCRCとは対照的に、16ビット CRCは常に反転方式で通信されます。DS1972 iButton内のCRC生成器(図13)は、コマンドフローチャート(図7)に示されているように新しい16ビットCRCを計算します。バスマスターは、デバイスから読み取られたCRC値をデータから計算された値と比較して、動作を続行するか、またはCRCエラーのあるデータの部分を再読み取りするかを決定します。

Write Scratchpadコマンドの場合、まずCRC生成器をクリアしてから、コマンドコード、宛先アドレスTA1とTA2、およびすべてのデータバイトをバスマスターから送出されたときにシフトインすることによって、CRCが生成されます。DS1972は、E[2:0] = 111bの場合に限り、このCRCを送信します。

図12. ノイズ抑制方式

図13. CRC-16ハードウェアの説明および多項式

Read Scratchpadコマンドの場合、まずCRC生成器をクリアしてから、コマンドコード、宛先アドレスTA1とTA2、E/Sバイト、およびスクラッチパッドデータをDS1972から送出されたときにシフトインすることに

よって、CRCが生成されます。DS1972は、読取りがスクラッチパッドの最後まで続く場合に限り、このCRCを送信します。CRC値の生成に関する詳細については、アプリケーションノート27を参照してください。

#### コマンド固有の1-Wire通信プロトコルー凡例

| 記号                         | 説明                                          |

|----------------------------|---------------------------------------------|

| RST                        | マスターによって生成される1-Wireリセットパルス                  |

| PD                         | スレーブによって生成される1-Wireプレゼンスパルス                 |

| Select                     | ROM機能プロトコルを満たすコマンドとデータ                      |

| WS                         | 「Write Scratchpad」コマンド                      |

| RS                         | 「Read Scratchpad」コマンド                       |

| CPS                        | 「Copy Scratchpad」コマンド                       |

| RM                         | 「Read Memory」コマンド                           |

| TA                         | 宛先アドレスTA1、TA2                               |

| TA-E/S                     | 宛先アドレスTA1、TA2、およびE/Sバイト                     |

| <8-T[2:0] bytes>           | 指定の宛先アドレスについて、スクラッチパッドの最後に到達するのに必要な数のバイト転送  |

| <data eom="" to=""></data> | メモリの最後に到達するのに必要な数のバイト転送                     |

| CRC-16                     | 反転CRC-16の転送                                 |

| FF Loop                    | マスターがFFバイトを読み取る無限ループ                        |

| AA Loop                    | マスターがAAバイトを読み取る無限ループ                        |

| Programming                | EEPROMへのデータ転送。この時間の間、1-Wireバス上での動作は許可されません。 |

### コマンド固有の1-Wire通信プロトコル-カラーコード\_\_\_\_\_

Master to Slave Slave to Master Programming

### 1-Wire通信の例\_\_\_\_\_

Write Scratchpad (Cannot Fail)

RST PD Select WS TA <8-T[2:0] bytes> CRC-16 FF Loop

Read Scratchpad (Cannot Fail)

RST PD Select RS TA-E/S <8-T[2:0] bytes> CRC-16 FF Loop

Copy Scratchpad (Success)

RST PD Select CPS TA-E/S Programming AA Loop

Copy Scratchpad (Invalid Address or PF = 1 or Copy Protected)

RST PD Select CPS TA-E/S FF Loop

Read Memory (Success)

RST PD Select RM TA <Data to EOM> FF Loop

Read Memory (Invalid Address)

RST PD Select RM TA FF Loop

#### メモリ機能の例\_\_\_\_

メモリページ1の先頭の8バイトに書き込み、メモリ全体を読み取ります。

バスマスターにDS1972を1個だけ接続した場合、通信は以下のようになります。

| マスターモード | データ(LSB先頭)         | コメント                                |

|---------|--------------------|-------------------------------------|

| Tx      | (Reset)            | リセットパルス                             |

| Rx      | (Presence)         | プレゼンスパルス                            |

| Tx      | CCh                | 「Skip ROM」コマンドの発行                   |

| Tx      | 0Fh                | 「Write Scratchpad」コマンドの発行           |

| Tx      | 20h                | TA1、開始オフセット= 20h                    |

| Tx      | 00h                | TA2、アドレス= <u>00</u> 20h             |

| Tx      | <8 Data Bytes>     | 8バイトデータをスクラッチパッドに書込み                |

| Rx      | <2 Bytes CRC-16>   | CRCを読み込みデータ品質をチェック                  |

| Tx      | (Reset)            | リセットパルス                             |

| Rx      | (Presence)         | プレゼンスパルス                            |

| Tx      | CCh                | 「Skip ROM」コマンドの発行                   |

| Tx      | AAh                | 「Read Scratchpad」コマンドの発行            |

| Rx      | 20h                | TA1の読込み、開始オフセット= 20h                |

| Rx      | 00h                | TA2の読込み、アドレス= <u>00</u> 20h         |

| Rx      | 07h                | E/Sの読込み、終了オフセット= 111b、AA、PF = 0     |

| Rx      | <8 Data Bytes>     | スクラッチパッドデータの読込みと確認                  |

| Rx      | <2 Bytes CRC-16>   | CRCを読み込みデータ品質をチェック                  |

| Tx      | (Reset)            | リセットパルス                             |

| Rx      | (Presence)         | プレゼンスパルス                            |

| Tx      | CCh                | 「Skip ROM」コマンドの発行                   |

| Tx      | 55h                | 「Copy Scratchpad」コマンドの発行            |

| Tx      | 20h                | TA1                                 |

| Tx      | 00h                | TA2   (認証コード)                       |

| Tx      | 07h                | E/S                                 |

| _       | <1-Wire Idle High> | コピー機能が終了するまでt <sub>PROGMAX</sub> 待つ |

| Rx      | AAh                | コピーステータスの読込み、AAh = 成功               |

| Tx      | (Reset)            | リセットパルス                             |

| Rx      | (Presence)         | プレゼンスパルス                            |

| Tx      | CCh                | 「Skip ROM」コマンドの発行                   |

| Tx      | F0h                | 「Read Memory」コマンドの発行                |

| Tx      | 00h                | TA1、開始オフセット= 00h                    |

| Tx      | 00h                | TA2、アドレス= <u>00</u> 00h             |

| Rx      | <144 Data Bytes>   | 全メモリの読み込み                           |

| Tx      | (Reset)            | リセットパルス                             |

| Rx      | (Presence)         | プレゼンスパルス                            |

#### パッケージ \_

最新のパッケージ図面情報およびランドパターンは、japan.maxim-ic.com/packages を参照してください。なお、パッケージコードに含まれる[+]、「#]、または[-]はRoHS対応状況を表したものでしかありません。パッケージ図面はパッケージそのものに関するものでRoHS対応状況とは関係がなく、図面によってパッケージコードが異なることがある点を注意してください。

| パッケージタイプ           | パッケージコード | ドキュメントNo.      |

|--------------------|----------|----------------|

| F3 <u>i</u> Button | IB+3NT   | <u>21-0252</u> |

| F5 <u>i</u> Button | IB+5NT   | <u>21-0266</u> |

#### 改訂履歴 \_\_\_\_\_

| 版数 | 改訂日  | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                   | 改訂ページ |  |

|----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|

| 0  | 4/06 | 初版                                                                                                                                                                                                                                                                                                                                                                                                                                   | _     |  |

| 1  | 8/06 | UL#913の箇条書きを「UL#93 (第4版)に適合 (申請出願中)」から「UL#93 (第4版)に<br>適合するように設計」に変更                                                                                                                                                                                                                                                                                                                                                                 | 1, 2  |  |

|    |      | 「共通のiButtonの特長」の項からUL#913の箇条書きを削除                                                                                                                                                                                                                                                                                                                                                                                                    | 1     |  |

| 2  | 8/09 | 「型番」の表でRoHSパッケージを鉛(Pb)フリーパッケージに変更                                                                                                                                                                                                                                                                                                                                                                                                    |       |  |

|    |      | 「Electrical Characteristics (電気的特性)」の表でV <sub>TLMIN</sub> を0.46Vから0.5Vに変更                                                                                                                                                                                                                                                                                                                                                            | 2     |  |

| 3  | 4/10 | 「Absolute Maximum Ratings (絶対最大定格)」で、保存温度を-55℃~+125℃に変更。「Electrical Characteristics」の表でV <sub>PUP</sub> に基づいてV <sub>TH</sub> とV <sub>TL</sub> を変更、およびデータ保持を85℃で40年(min)に変更。保持の仕様に次の注を追記、すなわち「EEPROM writes can become nonfunctional after the data-retention time is exceeded. Long-term storage at elevated temperatures is not recommended; the device can lose its write capability after 10 years at +125℃ or 40 years at +85℃.」 | 2, 3  |  |

| 3  | 4/10 | 「Electrical Characteristics」の表で、V <sub>ILMAX</sub> の仕様を0.3Vから0.5Vに変更。t <sub>W1LMAX</sub> の仕様からεを削除。t <sub>W0L</sub> の仕様に注17を追記。「Electrical Characteristics」の表の注17と18を更新。注20を修正                                                                                                                                                                                                                                                       | 2, 3  |  |

|    |      | 図11のWrite-Zeroタイムスロットにεを追加                                                                                                                                                                                                                                                                                                                                                                                                           | 18    |  |

|    |      | 「パッケージ」の表を追加                                                                                                                                                                                                                                                                                                                                                                                                                         | 22    |  |

|    |      | 新しいテンプレート形式のデータシートを作成                                                                                                                                                                                                                                                                                                                                                                                                                | 全ページ  |  |

マキシム·ジャパン株式会社 〒141-0032 東京都品川区大崎1-6-4 大崎ニューシティ 4号館 20F TEL: 03-6893-6600

Maximは完全にMaxim製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。Maximは随時予告なく回路及び仕様を変更する権利を留保します。