# システム・レベルのESD信頼性を 強化したデジタル・アイソレータ

# **ADuM3100**

#### 特長

IEC 61000-4-x に準拠してシステム・レベルの ESD 性能を強化 高速データレート: DC~100 Mbps (NRZ) 3.3 V および 5.0 V 動作/レベル変換との互換性 最大 105°C までの動作温度 低消費電力動作

5 V 動作

最大 2.0 mA @ 1 Mbps 最大 5.6 mA @ 25 Mbps 最大 18 mA @ 100 Mbps

3.3 V 動作

最大 1.1 mA @ 1 Mbps 最大 4.2 mA @ 25 Mbps 最大 8.3 mA @ 50 Mbps

RoHS 準拠の 8 ピン SOIC

高いコモンモード過渡耐性: >25 kV/µs

安全規格および適用規格

UL 認定: UL 1577 に準拠して 1 分間で 2500 V rms

CSA 部品承認通知#5A VDE 適合性証明

DIN V VDE V 0884-10 (VDE V 0884-10): 2006-12

V<sub>IORM</sub> = 560 V ピーク

#### アプリケーション

デジタル・フィールドバス絶縁 光アイソレータの置換品 コンピュータと周辺機器間のインターフェース マイクロプロセッサ・システムのインターフェース 一般的な計装とデータ・アクイジション

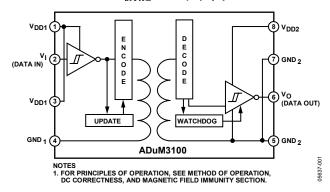

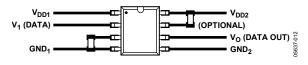

#### 機能ブロック図

図 1.

#### 概要

ADuM3100<sup>1</sup>は、アナログ・デバイセズの*i*Coupler<sup>®</sup>技術をベースとするデジタル・アイソレータです。高速CMOSおよびモノリシック・トランス技術を組み合わせたこの絶縁信号伝送素子は、フォトカプラ・デバイスなどに比べてはるかに優れた性能特性を備えています。

既存の高速フォトカプラを置き換えることができるピン互換デバイスとしての構成で、ADuM3100 は最大 25 Mbps および 100 Mbps の非常に高いデータレートに対応します。

ADuM3100 は 3.0~5.5 V の範囲の電源電圧で動作し、18 ns 以下の伝播遅延と 2 ns 以下のエッジ非対称性を備えるとともに、最大  $105^{\circ}$ C の温度で動作します。この製品は非常に低い消費電力で動作し、無負荷時電源電流(両サイドの合計)は 2.0 mA 未満、ダイナミック電流は 1 Mbps のデータレート当たり 160  $\mu$ A 未満です。ほかのフォトカプラ代替品とは異なり、ADuM3100 は出力信号を連続的に更新する特許取得済みのリフレッシュ機能によって高い DC 精度を維持します。

ADuM3100 には、2 つのグレードがあります。ADuM3100AR と ADuM3100BR は 105℃ の最大温度で動作し、それぞれ最大 25 Mbps および 100 Mbps のデータレートに対応します。

ADuM1100 デジタル・アイソレータと比較すると、ADuM3100 は各種回路およびレイアウトの変更によってシステム・レベルの IEC 61000-4- $\times$ テスト (ESD/バースト/サージ) に関連する性能 が向上しています。これらのテストにおける ADuM1100 または ADuM3100 の最終的な回路性能は、ユーザのボードまたはモジュールの設計とレイアウトに大きく左右されます。詳細については、アプリケーション・ノート AN-793 「ESD/Latch-Up Considerations with iCoupler Isolation Products」を参照してください。

<sup>1</sup> 米国特許 5,952,849、6,525,566、6,922,080、6,903,578、6,873,065、7,075,329、 および現在申請中の他の特許によって保護されています。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。 ※日本語データシートは REVISION が古い場合があります。最新の内容については、英語版をご参照ください。 ©2005-2007 Analog Devices, Inc. All rights reserved.

Rev. B

本 社/〒105-6891 東京都港区海岸 1-16-1 ニュー

# ADuM3100

# 目次

| 符長                                                                  | 1         |

|---------------------------------------------------------------------|-----------|

| アプリケーション                                                            | 1         |

| 機能ブロック図                                                             | 1         |

| 概要                                                                  | 1         |

| 改訂履歴                                                                | 2         |

| 仕様                                                                  | 3         |

| 電気的仕様、5 V 動作                                                        | 3         |

| 電気的仕様、3.3 V 動作                                                      | 4         |

| 電気的仕様、5 V/3 V または 3 V/5 V 混在動作                                      | 5         |

| パッケージ特性                                                             | 7         |

| 適用規格                                                                | 7         |

| 絶縁および安全に関連する仕様                                                      | 7         |

| DIN V VDE V 0884-10(VDE V 0884-10)絶縁特性                              | 8         |

|                                                                     |           |

| 改訂履歴                                                                |           |

| 6/07—Rev. A to Rev. B                                               |           |

| Updated VDE Certification Throughout                                | 1         |

| Changes to Note 1                                                   | 1         |

| Changes to Regulatory Information Section                           | 7         |

| Changes to Table 6                                                  | 7         |

| Changes to DIN V VDE V 0884-10 (VDE V 0884-10)                      | 0         |

| Insulation Characteristics Section                                  | 8         |

| <b>3/06—Rev. 0 to Rev. A</b> Updated Format                         | Universal |

| Changes to Product Title, Features, General Description, and Note 1 | 1         |

| Changes to Table 1                                                  | 3         |

| Changes to Table 2                                                  | 4         |

| Changes to Table 3                                                  | 5         |

| Added System-Level ESD Considerations and Enhancements Section      | 13        |

| Added Power Consumption Section                                     | 15        |

| 推奨動作条件                    | 8  |

|---------------------------|----|

| 絶対最大定格                    | 9  |

| ESD に関する注意                | 9  |

| ピン配置と機能の説明                | 10 |

| 代表的な性能特性                  | 11 |

| アプリケーション情報                | 13 |

| PC ボードのレイアウト              | 13 |

| システム・レベルの ESD に関する配慮と性能強化 | 13 |

| 伝播遅延に関連するパラメータ            | 13 |

| 素子の動作、DC 精度、磁界耐性          | 14 |

| 消費電力                      | 15 |

| 外形寸法                      | 16 |

| オーダー・ガイド                  | 16 |

10/05—Revision 0: Initial Version

## 仕様

#### 電気的仕様、5 V動作

すべての電圧は、それぞれ対応するグラウンドを基準とします。 $4.5~V \le V_{DD1} \le 5.5~V$ 、 $4.5~V \le V_{DD2} \le 5.5~V$ 。特に注記のない限り、すべての最小値/最大値の仕様は推奨の全動作範囲に適用されます。代表値の仕様はすべて、 $T_A = 25^{\circ}C$ 、 $V_{DD1} = V_{DD2} = 5~V$  における値です。

表 1.

| Parameter                                                                    | Symbol                 | Min             | Тур   | Max  | Unit    | Test Conditions                                          |

|------------------------------------------------------------------------------|------------------------|-----------------|-------|------|---------|----------------------------------------------------------|

| DC SPECIFICATIONS                                                            |                        |                 |       |      |         |                                                          |

| Input Supply Current, Quiescent                                              | $I_{DD1 (Q)}$          |                 | 1.3   | 1.8  | mA      | $V_I = 0 \text{ V or } V_{DD1}$                          |

| Output Supply Current, Quiescent                                             | $I_{DD2(Q)}$           |                 | 0.15  | 0.25 | mA      | $V_I = 0 \text{ V or } V_{DD1}$                          |

| Input Supply Current (25 Mbps)<br>(See Figure 4)                             | I <sub>DD1 (25)</sub>  |                 | 3.2   | 4.5  | mA      | 12.5 MHz logic signal freq.                              |

| Output Supply Current <sup>1</sup> (25 Mbps)<br>(See Figure 5)               | I <sub>DD2 (25)</sub>  |                 | 0.6   | 1.1  | mA      | 12.5 MHz logic signal freq.                              |

| Input Supply Current (100 Mbps)<br>(See Figure 4)                            | I <sub>DD1 (100)</sub> |                 | 10    | 15   | mA      | 50 MHz logic signal freq.                                |

| Output Supply Current <sup>1</sup> (100 Mbps)<br>(See Figure 5)              | I <sub>DD2 (100)</sub> |                 | 2.1   | 2.9  | mA      | 50 MHz logic signal freq.,<br>ADuM3100BRZonly            |

| Input Current                                                                | $I_{I}$                | -10             | +0.01 | +10  | μA      | $0 \leq V_{\rm IN} \leq V_{\rm DD1}$                     |

| Logic High Output Voltage                                                    | $V_{OH}$               | $V_{DD2} - 0.1$ | 5.0   |      | V       | $I_{O} = -20 \mu A, V_{I} = V_{IH}$                      |

|                                                                              |                        | $V_{DD2} - 0.8$ | 4.6   |      | V       | $I_O = -4 \text{ mA}, V_I = V_{IH}$                      |

| Logic Low Output Voltage                                                     | $V_{OL}$               |                 | 0.0   | 0.1  | V       | $I_{O} = 20 \mu A, V_{I} = V_{IL}$                       |

|                                                                              |                        |                 | 0.03  | 0.1  | V       | $I_{O} = 400 \ \mu A, \ V_{I} = V_{IL}$                  |

|                                                                              |                        |                 | 0.3   | 0.8  | V       | $I_O = 4 \text{ mA}, V_I = V_{IL}$                       |

| SWITCHING SPECIFICATIONS                                                     |                        |                 |       |      |         |                                                          |

| For ADuM3100AR Z                                                             |                        |                 |       |      |         |                                                          |

| Minimum Pulse Width <sup>2</sup>                                             | PW                     |                 |       | 40   | ns      | $C_L = 15 \text{ pF}$ , CMOS signal levels               |

| Maximum Data Rate <sup>3</sup>                                               |                        | 25              |       |      | Mbps    | $C_L = 15 \text{ pF}, \text{CMOS signal levels}$         |

| For ADuM3100BRZ                                                              |                        |                 |       |      |         |                                                          |

| Minimum Pulse Width <sup>3</sup>                                             | PW                     |                 | 6.7   | 10   | ns      | $C_L = 15 \text{ pF}$ , CMOS signal levels               |

| Maximum Data Rate <sup>3</sup>                                               |                        | 100             | 150   |      | Mbps    | $C_L = 15 \text{ pF}$ , CMOS signal levels               |

| For All Grades                                                               |                        |                 |       |      |         |                                                          |

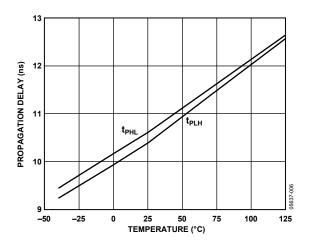

| Propagation Delay Time to Logic Low<br>Output <sup>4, 5</sup> (See Figure 6) | $t_{PHL}$              |                 | 10.5  | 18   | ns      | $C_L = 15 \text{ pF}, \text{CMOS signal levels}$         |

| Propagation Delay Time to Logic High<br>Output <sup>4,5</sup> (See Figure 6) | $t_{\rm PLH}$          |                 | 10.5  | 18   | ns      | $C_L = 15 \text{ pF}$ , CMOS signal levels               |

| Pulse-Width Distortion $ t_{PLH} - t_{PHL} ^5$                               | PWD                    |                 | 0.5   | 2    | ns      | $C_L = 15 \text{ pF}$ , CMOS signal levels               |

| Change vs. Temperature <sup>6</sup>                                          |                        |                 | 3     |      | ps/°C   | $C_L = 15 \text{ pF}$ , CMOS signal levels               |

| Propagation Delay Skew (Equal Temperature)5, 7                               | t <sub>PSK1</sub>      |                 |       | 8    | ns      | $C_L = 15 \text{ pF}$ , CMOS signal levels               |

| Propagation Delay Skew (Equal Temperature, Supplies) <sup>5, 7</sup>         | t <sub>PSK2</sub>      |                 |       | 6    | ns      | $C_L = 15 \text{ pF}$ , CMOS signal levels               |

| Output Rise/Fall Time                                                        | $t_{\rm R},t_{\rm F}$  |                 | 3     |      | ns      | $C_L = 15 \text{ pF}$ , CMOS signal levels               |

| Common-Mode Transient Immunity at Logic Low/High Output <sup>8</sup>         | $ CM_L ,  CM_H $       | 25              | 35    |      | kV/μs   | $V_{I} = 0 \text{ or } V_{DD1}, V_{CM} = 1000 \text{ V}$ |

| Input Dynamic Supply Current <sup>9</sup>                                    | $I_{DDI (D)}$          |                 | 0.09  |      | mA/Mbps |                                                          |

| Output Dynamic Supply Current <sup>9</sup>                                   | $I_{DDO (D)}$          |                 | 0.02  |      | mA/Mbps |                                                          |

<sup>6</sup>ページの注を参照してください。

Rev. B -3/16 -

### 電気的仕様、3.3 V動作

すべての電圧は、それぞれ対応するグラウンドを基準とします。  $3.0~\mathrm{V} \le \mathrm{V}_{\mathrm{DD1}} \le 3.6~\mathrm{V}$ 、  $3.0~\mathrm{V} \le \mathrm{V}_{\mathrm{DD2}} \le 3.6~\mathrm{V}$ 。特に注記のない限り、すべての最小値/最大値の仕様は推奨の全動作範囲に適用されます。代表値の仕様はすべて、 $\mathrm{T_A} = 25^{\circ}\mathrm{C}$ 、 $\mathrm{V_{DD1}} = \mathrm{V_{DD2}} = 3.3~\mathrm{V}$  における値です。

表 2.

| Parameter                                                                    | Symbol                | Min                                               | Тур   | Max | Unit    | Test Conditions                                                                       |

|------------------------------------------------------------------------------|-----------------------|---------------------------------------------------|-------|-----|---------|---------------------------------------------------------------------------------------|

| DC SPECIFICATIONS                                                            |                       |                                                   |       |     |         |                                                                                       |

| Input Supply Current, Quiescent                                              | I <sub>DD1 (Q)</sub>  |                                                   | 0.7   | 0.9 | mA      | $V_I = 0 \text{ V or } V_{DD1}$                                                       |

| Output Supply Current, Quiescent                                             | $I_{DD2(Q)}$          |                                                   | 0.1   | 0.2 | mA      | $V_I = 0 \text{ V or } V_{DD1}$                                                       |

| Input Supply Current (25 Mbps)<br>(See Figure 4)                             | I <sub>DD1 (25)</sub> |                                                   | 2.6   | 3.4 | mA      | 12.5 MHz logic signal freq.                                                           |

| Output Supply Current <sup>1</sup> (25 Mbps)<br>(See Figure 5)               | I <sub>DD2 (25)</sub> |                                                   | 0.4   | 0.8 | mA      | 12.5 MHz logic signal freq.                                                           |

| Input Supply Current (50 Mbps)<br>(See Figure 4)                             | I <sub>DD1 (50)</sub> |                                                   | 4.6   | 6.6 | mA      | 25 MHz logic signal freq.,<br>ADuM3100BRZ only                                        |

| Output Supply Current <sup>1</sup> (50 Mbps)<br>(See Figure 5)               | I <sub>DD2 (50)</sub> |                                                   | 0.7   | 1.7 | mA      | 25 MHz logic signal freq.,<br>ADuM3100BRZ only                                        |

| Input Current                                                                | $I_{\rm I}$           | -10                                               | +0.01 | +10 | μΑ      | $0 \leq V_{\rm IN} \leq V_{\rm DD1}$                                                  |

| Logic High Output Voltage                                                    | $V_{OH}$              | $\begin{array}{c} V_{\rm DD2}-\\ 0.1 \end{array}$ | 3.3   |     | V       | $I_0 = -20 \mu A, V_I = V_{IH}$                                                       |

|                                                                              |                       | $V_{\mathrm{DD2}}-0.5$                            | 3.0   |     | V       | $I_0 = -2.5 \text{ mA}, V_I = V_{IH}$                                                 |

| Logic Low Output Voltage                                                     | $V_{OL}$              |                                                   | 0.0   | 0.1 | V       | $I_O = 20 \mu A$ , $V_I = V_{IL}$                                                     |

|                                                                              |                       |                                                   | 0.04  | 0.1 | V       | $I_{O} = 400 \mu A, V_{I} = V_{IL}$                                                   |

|                                                                              |                       |                                                   | 0.3   | 0.4 | V       | $I_O = 2.5 \text{ mA}, V_I = V_{IL}$                                                  |

| SWITCHING SPECIFICATIONS                                                     |                       |                                                   |       |     |         |                                                                                       |

| For ADuM3100ARZ                                                              |                       |                                                   |       |     |         |                                                                                       |

| Minimum Pulse Width <sup>2</sup>                                             | PW                    |                                                   |       | 40  | ns      | $C_L = 15 \text{ pF}$ , CMOS signal levels                                            |

| Maximum Data Rate <sup>3</sup>                                               |                       | 25                                                |       |     | Mbps    | $C_L = 15 \text{ pF}$ , CMOS signal levels                                            |

| For ADuM3100BRZ                                                              |                       |                                                   |       |     |         |                                                                                       |

| Minimum Pulse Width <sup>2</sup>                                             | PW                    |                                                   | 10    | 20  | ns      | $C_L = 15 \text{ pF}$ , CMOS signal levels                                            |

| Maximum Data Rate <sup>3</sup>                                               |                       | 50                                                | 100   |     | Mbps    | $C_L = 15 \text{ pF}$ , CMOS signal levels                                            |

| For All Grades                                                               |                       |                                                   |       |     |         |                                                                                       |

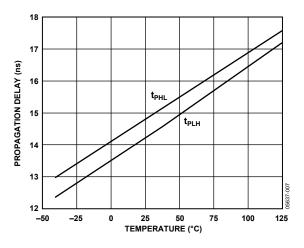

| Propagation Delay Time to Logic Low<br>Output <sup>4,5</sup> (See Figure 7)  | $t_{ m PHL}$          |                                                   | 14.5  | 28  | ns      | $C_L = 15 \text{ pF}$ , CMOS signal levels                                            |

| Propagation Delay Time to Logic High<br>Output <sup>4,5</sup> (See Figure 7) | $t_{\rm PLH}$         |                                                   | 15.0  | 28  | ns      | $C_L = 15 \text{ pF}$ , CMOS signal levels                                            |

| Pulse-Width Distortion $ t_{PLH} - t_{PHL} ^5$                               | PWD                   |                                                   | 0.5   | 3   | ns      | $C_L = 15 \text{ pF}$ , CMOS signal levels                                            |

| Change vs. Temperature <sup>6</sup>                                          |                       |                                                   | 10    |     | ps/°C   | $C_L = 15 \text{ pF}$ , CMOS signal levels                                            |

| Propagation Delay Skew (Equal Temperature) <sup>5,7</sup>                    | $t_{PSK1}$            |                                                   |       | 15  | ns      | $C_L = 15 \text{ pF}$ , CMOS signal levels                                            |

| Propagation Delay Skew (Equal Temperature, Supplies) <sup>5, 7</sup>         | $t_{\mathrm{PSK2}}$   |                                                   |       | 12  | ns      | $C_L = 15 \text{ pF}$ , CMOS signal levels                                            |

| Output Rise/Fall Time                                                        | $t_R, t_F$            |                                                   | 3     |     | ns      | $C_L = 15 \text{ pF}$ , CMOS signal levels                                            |

| Common-Mode Transient Immunity at Logic Low/High Output <sup>8</sup>         | $ CM_L ,  CM_H $      | 25                                                | 35    |     | kV/μs   | $V_{\rm I}$ = 0 or $V_{\rm DD1}$ , $V_{\rm CM}$ = 1000 V, transient magnitude = 800 V |

| Input Dynamic Supply Current <sup>9</sup>                                    | I <sub>DDI (D)</sub>  |                                                   | 0.08  |     | mA/Mbps |                                                                                       |

| Output Dynamic Supply Current <sup>9</sup>                                   | I <sub>DDO (D)</sub>  |                                                   | 0.01  |     | mA/Mbps |                                                                                       |

6ページの注を参照してください。

Rev. B — 4/16 —

#### 電気的仕様、5 V/3 Vまたは 3 V/5 V混在動作

すべての電圧は、それぞれ対応するグラウンドを基準とします。 $5\,V/3\,V$ 動作: $4.5\,V \le V_{DD1} \le 5.5\,V$ 、 $3.0\,V \le V_{DD2} \le 3.6\,V$ 。 $3\,V/5\,V$ 動作: $3.0\,V \le V_{DD1} \le 3.6\,V$ 、 $4.5\,V \le V_{DD2} \le 5.5\,V$ 。特に注記のない限り、すべての最小値/最大値の仕様は推奨の全動作範囲に適用されます。代表値の仕様はすべて、 $T_A = 25\,^{\circ}C$ 、 $V_{DD1} = 3.3\,V$ 、 $V_{DD2} = 5\,V$ 、または $V_{DD1} = 5\,V$ 、 $V_{DD2} = 3.3\,V$  における値です。

表 3.

| Parameter                                                           | Symbol                              | Min                 | Тур   | Max  | Unit | Test Conditions                                                          |

|---------------------------------------------------------------------|-------------------------------------|---------------------|-------|------|------|--------------------------------------------------------------------------|

| DC SPECIFICATIONS                                                   |                                     |                     | -     |      |      |                                                                          |

| Input Supply Current, Quiescent                                     | $I_{DDI(Q)}$                        |                     |       |      |      |                                                                          |

| 5 V/3 V Operation                                                   |                                     |                     | 1.3   | 1.8  | mA   |                                                                          |

| 3 V/5 V Operation                                                   |                                     |                     | 0.7   | 0.9  | mA   |                                                                          |

| Output Supply Current <sup>1</sup> , Quiescent                      | $I_{\mathrm{DDO(Q)}}$               |                     |       |      |      |                                                                          |

| 5 V/3 V Operation                                                   |                                     |                     | 0.1   | 0.2  | mA   |                                                                          |

| 3 V/5 V Operation                                                   |                                     |                     | 0.15  | 0.25 | mA   |                                                                          |

| Input Supply Current, 25 Mbps                                       | I <sub>DDI (25)</sub>               |                     |       |      |      |                                                                          |

| 5 V/3 V Operation                                                   |                                     |                     | 3.2   | 4.5  | mA   | 12.5 MHz logic signal freq.                                              |

| 3 V/5 V Operation                                                   |                                     |                     | 2.6   | 3.4  | mA   | 12.5 MHz logic signal freq.                                              |

| Output Supply Current <sup>1</sup> , 25 Mbps                        | I <sub>DDO (25)</sub>               |                     |       |      |      |                                                                          |

| 5 V/3 V Operation                                                   |                                     |                     | 0.4   | 0.8  | mA   | 12.5 MHz logic signal freq.                                              |

| 3 V/5 V Operation                                                   |                                     |                     | 0.6   | 1.1  | mA   | 12.5 MHz logic signal freq.                                              |

| Input Supply Current, 50 Mbps                                       | I <sub>DDI (50)</sub>               |                     |       |      |      |                                                                          |

| 5 V/3 V Operation                                                   |                                     |                     | 5.5   | 8.0  | mA   | 25 MHz logic signal freq.                                                |

| 3 V/5 V Operation                                                   |                                     |                     | 4.6   | 6.6  | mA   | 25 MHz logic signal freq.                                                |

| Output Supply Current <sup>1</sup> , 50 Mbps                        | I <sub>DDO (50)</sub>               |                     |       |      |      |                                                                          |

| 5 V/3 V Operation                                                   | === (++)                            |                     | 0.7   | 1.7  | mA   | 25 MHz logic signal freq.                                                |

| 3 V/5 V Operation                                                   |                                     |                     | 1.1   | 1.6  | mA   | 25 MHz logic signal freq.                                                |

| Input Currents                                                      | $I_{IA}$                            | -10                 | +0.01 | +10  | μΑ   | $0 \leq V_{IA}, V_{IB}, V_{IC}, V_{ID} \leq V_{DD1} \text{ or } V_{DD2}$ |

| Logic High Output Voltage, 5 V/3 V Operation                        | $V_{\mathrm{OH}}$                   | $V_{\rm DD2} - 0.1$ | 3.3   |      | V    | $I_{O} = -20 \mu A, V_{I} = V_{IH}$                                      |

|                                                                     |                                     | $V_{\rm DD2} - 0.5$ | 3.0   |      | V    | $I_0 = -2.5 \text{ mA}, V_I = V_{IH}$                                    |

| Logic Low Output Voltage, 5 V/3 V Operation                         | $V_{OL}$                            |                     | 0.0   | 0.1  | V    | $I_{O} = 20 \mu A, V_{I} = V_{IL}$                                       |

|                                                                     |                                     |                     | 0.04  | 0.1  | V    | $I_{O} = 400  \mu A,  V_{I} = V_{IL}$                                    |

|                                                                     |                                     |                     | 0.3   | 0.4  | V    | $I_0 = 2.5 \text{ mA}, V_I = V_{IL}$                                     |

| Logic High Output Voltage, 3 V/5 V Operation                        | $V_{\mathrm{OH}}$                   | $V_{\rm DD2} - 0.1$ | 5.0   |      | V    | $I_{O} = -20 \mu A, V_{I} = V_{IH}$                                      |

|                                                                     |                                     | $V_{\rm DD2} - 0.8$ | 4.6   |      | V    | $I_O = -4 \text{ mA}, V_I = V_{IH}$                                      |

| Logic Low Output Voltage, 3 V/5 V Operation                         | $V_{OL}$                            |                     | 0.0   | 0.1  | V    | $I_{O} = 20 \mu A, V_{I} = V_{IL}$                                       |

|                                                                     |                                     |                     | 0.03  | 0.1  | V    | $I_{O} = 400  \mu A,  V_{I} = V_{IL}$                                    |

|                                                                     |                                     |                     | 0.3   | 0.8  | V    | $I_O = 4 \text{ mA}, V_I = V_{IL}$                                       |

| SWITCHING SPECIFICATIONS                                            |                                     |                     |       |      |      | ·                                                                        |

| For ADuM3100AR                                                      |                                     |                     |       |      |      |                                                                          |

| Minimum Pulse Width <sup>2</sup>                                    | PW                                  |                     |       | 40   | ns   | $C_L = 15 \text{ pF}$ , CMOS signal levels                               |

| Maximum Data Rate <sup>3</sup>                                      |                                     | 25                  |       |      | Mbps | $C_L = 15 \text{ pF}$ , CMOS signal levels                               |

| For ADuM3100BR                                                      |                                     |                     |       |      |      |                                                                          |

| Minimum Pulse Width <sup>2</sup>                                    | PW                                  |                     |       | 20   | ns   | $C_L = 15 \text{ pF}$ , CMOS signal levels                               |

| Maximum Data Rate <sup>3</sup>                                      |                                     | 50                  |       |      | Mbps | $C_L = 15 \text{ pF}$ , CMOS signal levels                               |

| For All Grades                                                      |                                     |                     |       |      |      |                                                                          |

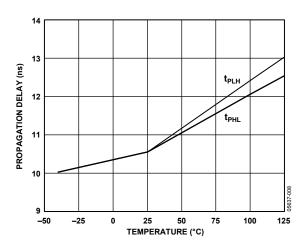

| Propagation Delay Time to Logic Low/<br>High Output <sup>4, 5</sup> | t <sub>PHL</sub> , t <sub>PLH</sub> |                     |       |      |      |                                                                          |

| 5 V/3 V Operation (See Figure 8)                                    |                                     |                     | 13    | 21   | ns   | $C_L = 15 \text{ pF}$ , CMOS signal levels                               |

| 3 V/5 V Operation (See Figure 9)                                    |                                     |                     | 16    | 26   | ns   | $C_L = 15 \text{ pF}$ , CMOS signal levels                               |

| Pulse-Width Distortion, $ t_{PLH} - t_{PHL} ^5$                     | PWD                                 |                     |       |      |      |                                                                          |

| 5 V/3 V Operation                                                   |                                     |                     | 0.5   | 2    | ns   | $C_L = 15 \text{ pF}$ , CMOS signal levels                               |

| 3 V/5 V Operation                                                   |                                     |                     | 0.5   | 3    | ns   | $C_L = 15 \text{ pF}$ , CMOS signal levels                               |

Rev. B -5/16 -

| Parameter                                                            | Symbol                | Min | Тур  | Max | Unit    | Test Conditions                                                            |

|----------------------------------------------------------------------|-----------------------|-----|------|-----|---------|----------------------------------------------------------------------------|

| Change vs. Temperature <sup>6</sup>                                  |                       |     |      |     |         |                                                                            |

| 5 V/3 V Operation                                                    |                       |     | 3    |     | ps/°C   | $C_L = 15 \text{ pF}$ , CMOS signal levels                                 |

| 3 V/5 V Operation                                                    |                       |     | 10   |     | ps/°C   | $C_L = 15 \text{ pF}$ , CMOS signal levels                                 |

| Propagation Delay Skew (Equal Temperature) <sup>5, 7</sup>           | $t_{PSK1}$            |     |      |     |         |                                                                            |

| 5 V/3 V Operation                                                    |                       |     |      | 12  | ns      | $C_L = 15 \text{ pF}$ , CMOS signal levels                                 |

| 3 V/5 V Operation                                                    |                       |     |      | 15  | ns      | $C_L = 15 \text{ pF}$ , CMOS signal levels                                 |

| Propagation Delay Skew (Equal Temperature, Supplies) <sup>5, 7</sup> | $t_{\mathrm{PSK2}}$   |     |      |     |         |                                                                            |

| 5 V/3 V Operation                                                    |                       |     |      | 9   | ns      | $C_L = 15 \text{ pF}$ , CMOS signal levels                                 |

| 3 V/5 V Operation                                                    |                       |     |      | 12  | ns      | $C_L = 15 \text{ pF}$ , CMOS signal levels                                 |

| Output Rise/Fall Time (10% to 90%)                                   | $t_{\rm R},t_{\rm f}$ |     | 3    |     | ns      | $C_L = 15 \text{ pF}$ , CMOS signal levels                                 |

| Common-Mode Transient Immunity at Logic Low/High Output <sup>8</sup> | $ CM_L ,  CM_H $      | 25  | 35   |     | kV/μs   | $V_I = 0$ or $V_{DD1}$ , $V_{CM} = 1000$ V,<br>transient magnitude = 800 V |

| Input Dynamic Supply Current per Channel <sup>9</sup>                | $I_{DDI(D)}$          |     |      |     |         |                                                                            |

| 5 V/3 V Operation                                                    |                       |     | 0.09 |     | mA/Mbps |                                                                            |

| 3 V/5 V Operation                                                    |                       |     | 0.08 |     | mA/Mbps |                                                                            |

| Output Dynamic Supply Current per Channel <sup>9</sup>               | $I_{\text{DDO (D)}}$  |     |      |     |         |                                                                            |

| 5 V/3 V Operation                                                    |                       |     | 0.01 |     | mA/Mbps |                                                                            |

| 3 V/5 V Operation                                                    |                       |     | 0.02 |     | mA/Mbps |                                                                            |

<sup>&</sup>lt;sup>1</sup> 出力側電源電流は、出力負荷が接続されていないときの値です。ロジック信号周波数の変化に伴う電源電流の変動に関しては、図4と図5を参照してください。所定のデータレートおよび出力負荷接続時の入力および出力電源電流の計算に関する指針は、「消費電力」を参照してください。

Rev. B — 6/16 —

<sup>2</sup> 最小パルス幅は、規定されたパルス幅歪みが保証される最も短いパルスです。

<sup>3</sup> 最大データレートは、規定されたパルス幅歪みが保証される最も高速のデータレートです。

$<sup>^4</sup>$   $t_{PHL}$  は、 $V_1$ 信号の立下がりエッジの 50%レベルから  $V_0$ 信号の立下がりエッジの 50%レベルまでを測定した時間です。 $t_{PLH}$  は、 $V_1$ 信号の立上がりエッジの 50%レベルから  $V_0$ 信号の立上がりエッジの 50%レベルまでを測定した時間です。

<sup>&</sup>lt;sup>5</sup> ADuM3100の入力スレッショールドは、代表的な入力信号の50%レベル以外の電圧であるため、伝播遅延とパルス幅歪みの測定値は低速の入力立上がり/立下がり時間による影響を受けることがあります。これらのパラメータに対する所定の入力立上がり/立下がり時間の影響に関しては、「システム・レベルの ESD に関する配慮と性能強化」および図 13 から図 17 までを参照してください。

$<sup>^6</sup>$ パルス幅歪み変化の温度特性は、動作温度が 1 ℃変化するときのパルス幅歪み変化の絶対値です。

$<sup>^{7}</sup>$   $t_{PSKL}$ は、推奨の動作条件範囲内において同じ動作温度と同じ出力負荷でユニット間で測定された  $t_{PHL}$ および/または  $t_{PLH}$ の最悪時の時間差です。 $t_{PSKL}$ は、推奨の動作条件範囲内において同じ動作温度、同じ電源電圧、同じ出力負荷のとき、ユニット間で測定された  $t_{PHL}$ および/または  $t_{PLH}$ の最悪時の時間差です。

$<sup>^8</sup>$  CM<sub>H</sub>は、 $V_0 > 0.8$   $V_{DD2}$  を維持しながら保つことができる最大コモンモード電圧スルーレートです。CM<sub>L</sub>は、 $V_0 < 0.8$  V を維持しながら保つことができる最大コモンモード電圧スルーレートです。このコモンモード電圧スルーレートは、立上がりエッジと立下がりエッジの両方に適用されます。過渡電圧レベルは、コモンモードがスルーなれる禁門です。

<sup>9</sup> ダイナミック電源電流は、信号データレートが 1 Mbps 増加するときに要求される電源電流の増分量です。ロジック信号周波数の変化に伴う電源電流の変動に関しては、図4と図5を参照してください。所定のデータレートおよび出力負荷接続時の入力および出力電源電流の計算に関する指針は、「消費電力」を参照してください。

#### パッケージ特性

#### 表 4.

| Parameter                                      | Symbol             | Min | Тур       | Max | Unit | Test Conditions                   |

|------------------------------------------------|--------------------|-----|-----------|-----|------|-----------------------------------|

| Resistance (Input-to-Output) <sup>1</sup>      | R <sub>I-O</sub>   |     | $10^{12}$ |     | Ω    |                                   |

| Capacitance (Input-to-Output) <sup>1</sup>     | $C_{\text{I-O}}$   |     | 1.0       |     | pF   | f = 1 MHz                         |

| Input Capacitance <sup>2</sup>                 | $C_{\rm I}$        |     | 4.0       |     | pF   |                                   |

| IC Junction-to-Case Thermal Resistance, Side 1 | $\theta_{ m JCI}$  |     | 46        |     | °C/W | Thermocouple located at center of |

| IC Junction-to-Case Thermal Resistance, Side 2 | $\theta_{\rm JCO}$ |     | 41        |     | °C/W | package underside                 |

| Package Power Dissipation                      | $P_{PD}$           |     |           | 240 | mW   |                                   |

<sup>&</sup>lt;sup>1</sup> このデバイスを 2 端子デバイスと見なして規定しています。1 番ピン、2 番ピン、3 番ピン、4 番ピンを短絡し、5 番ピン、6 番ピン、7 番ピン、8 番ピンを短絡しています。

### 適用規格

ADuM3100は、表5に記載する団体によって承認されています。

#### 表 5.

| UL                                                                        | CSA                                                                                                    | VDE                                                                              |

|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Recognized under UL 1577 Component<br>Recognition<br>Program <sup>1</sup> | Approved under CSA Component<br>Acceptance Notice #5A                                                  | Certified according to DIN V VDE V 0884-10 (VDE V 0884-10): 2006-12 <sup>2</sup> |

| Single/basic insulation, 2500 V rms isolation voltage                     | Basic insulation per CSA 60950-1-03 and IEC 60950-1,<br>400 V rms (565 V peak) maximum working voltage | Reinforced insulation, 560 V peak                                                |

| File E214100                                                              | File 205078                                                                                            | File 2471900-4880-0001                                                           |

<sup>&</sup>lt;sup>1</sup> UL 1577 に準拠して、すべての ADuM3100 には 1 秒間に≥3000 V rms の絶縁テスト電圧を印加する耐久テストが行われています(リーク電流検出限界値 = 5 μA)。

#### 絶縁および安全に関連する仕様

#### 表 6.

| Parameter                                                        | Symbol     | Value     | Unit   | Conditions                                                                           |

|------------------------------------------------------------------|------------|-----------|--------|--------------------------------------------------------------------------------------|

| Minimum External Air Gap (Clearance)                             | L(I01)     | 4.90 min  | mm     | Measured from input terminals to output terminals, shortest distance through air     |

| Minimum External Tracking (Creepage)                             | L(I02)     | 4.01 min  | mm     | Measured from input terminals to output terminals, shortest distance path along body |

| Minimum Internal Gap (Internal Clearance)                        |            | 0.017 min | mm     | Insulation distance through insulation                                               |

| Tracking Resistance (Comparative Tracking Index)                 | CTI        | >175      | V      | DIN IEC 112/VDE 0303 Part 1                                                          |

| Isolation Group                                                  |            | IIIa      |        | Material Group (DIN VDE 0110, 1/89, Table 1)                                         |

| Maximum Working Voltage Compatible with 50 Years<br>Service Life | $V_{IORM}$ | 565       | V peak | Continuous peak voltage across the isolation barrier                                 |

Rev. B — 7/16 —

$<sup>^2</sup>$  入力容量は2番ピン  $(V_I)$  で測定します。

<sup>&</sup>lt;sup>2</sup> DIN V VDE V 0884-10 に準拠して、すべての ADuM3100 には 1 秒間に≥1050 V ピークの絶縁テスト電圧を印加する耐久テストが行われています (部分放電検出限界値=5 pC)。部品にマーキングされている星印 (\*) は、DIN V VDE V 0884-10 認定品であることを示しています。

#### DIN V VDE V 0884-10 (VDE V 0884-10) 絶縁特性

このアイソレータは、安全性限界データの範囲以内でのみ使用する強化絶縁に適しています。安全データの範囲は、保護回路によって維持されます。パッケージ上にマーキングされている星印(\*)は、560 Vピークの動作電圧に対する DIN V VDE V 0884-10 の認可があることを示しています。

表 7.

| Description                                              | Conditions                                                                                       | Symbol     | Characteristic | Unit   |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------|----------------|--------|

| Installation Classification per DIN VDE 0110             |                                                                                                  |            |                |        |

| For Rated Mains Voltage ≤ 150 V rms                      |                                                                                                  |            | I to IV        |        |

| For Rated Mains Voltage ≤ 300 V rms                      |                                                                                                  |            | I to III       |        |

| For Rated Mains Voltage ≤ 400 V rms                      |                                                                                                  |            | I to II        |        |

| Climatic Classification                                  |                                                                                                  |            | 40/105/21      |        |

| Pollution Degree per DIN VDE 0110, Table 1               |                                                                                                  |            | 2              |        |

| Maximum Working Insulation Voltage                       |                                                                                                  | $V_{IORM}$ | 560            | V peak |

| Input-to-Output Test Voltage, Method B1                  | $V_{IORM} \times 1.875 = V_{PR}$ , 100% production test, $t_m$ = 1 sec, partial discharge < 5 pC | $V_{PR}$   | 1050           | V peak |

| Input-to-Output Test Voltage, Method A                   | $V_{IORM} \times 1.6 = V_{PR}$ , $t_m = 60$ sec, partial discharge < 5 pC                        | $V_{PR}$   |                |        |

| After Environmental Tests Subgroup 1                     |                                                                                                  |            | 896            | V peak |

| After Input and/or Safety Test Subgroup 2 and Subgroup 3 | $V_{IORM} \times 1.2 = V_{PR}$ , $t_m = 60$ sec, partial discharge $< 5$ pC                      |            | 672            | V peak |

| Highest Allowable Overvoltage                            | Transient overvoltage, $t_{TR} = 10$ seconds                                                     | $V_{TR}$   | 4000           | V peak |

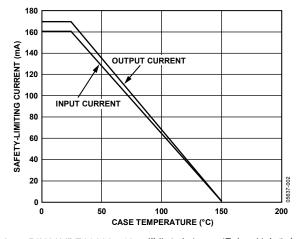

| Safety-Limiting Values                                   | Maximum value allowed in the event of a failure (see Figure 2)                                   |            |                |        |

| Case Temperature                                         |                                                                                                  | $T_{S}$    | 150            | °C     |

| Side 1 Current                                           |                                                                                                  | $I_{S1}$   | 160            | mA     |

| Side 2 Current                                           |                                                                                                  | $I_{S2}$   | 170            | mA     |

| Insulation Resistance at T <sub>S</sub>                  | $V_{IO} = 500 \text{ V}$                                                                         | $R_S$      | >109           | Ω      |

図 2. DIN V VDE V 0884-10 に準拠したケース温度に対する安全 限界値による、サーマル・ディレーティング曲線。

#### 推奨動作条件

表 8.

| Parameter                                                                                     | Symbol                                 | Min | Max       | Unit |

|-----------------------------------------------------------------------------------------------|----------------------------------------|-----|-----------|------|

| Operating Temperature                                                                         | $T_A$                                  | -40 | +105      | °C   |

| Supply Voltages <sup>1</sup>                                                                  | $V_{\mathrm{DD1}}, \ V_{\mathrm{DD2}}$ | 3.0 | 5.5       | V    |

| Logic High Input Voltage,<br>5 V Operation<br>(See Figure 10 and Figure 11)                   | $V_{IH}$                               | 2.0 | $V_{DD1}$ | V    |

| Logic Low Input Voltage,<br>5 V Operation <sup>1, 2</sup><br>(See Figure 10 and Figure 11)    | V <sub>IL</sub>                        | 0.0 | 0.8       | V    |

| Logic High Input Voltage,<br>3.3 V Operation <sup>1, 2</sup><br>(See Figure 10 and Figure 11) | $V_{IH}$                               | 1.5 | $V_{DD1}$ | V    |

| Logic Low Input Voltage,<br>3.3 V Operation <sup>1, 2</sup><br>(See Figure 10 and Figure 11)  | V <sub>IL</sub>                        | 0.0 | 0.5       | V    |

| Input Signal Rise and Fall Times                                                              |                                        |     | 1.0       | ms   |

<sup>「</sup>すべての電圧は、それぞれ対応するグラウンドを基準とします。

Rev. B — 8/16 —

<sup>2</sup> 入力スイッチング・スレッショールドのヒステリシスは 300 mV です。外部 磁界に対する耐性については、「素子の動作、DC 精度、磁界耐性」を参照 してください。

## 絶対最大定格

特に指定のない限り、周囲温度=25°C。

表 9.

| Parameter                                       | Min  | Max                      | Unit  |

|-------------------------------------------------|------|--------------------------|-------|

| Storage Temperature (T <sub>ST</sub> )          | -55  | +150                     | °C    |

| Ambient Operating Temperature (T <sub>A</sub> ) | -40  | +105                     | °C    |

| Supply Voltages $(V_{DD1}, V_{DD2})^1$          | -0.5 | +6.5                     | V     |

| Input Voltage (V <sub>I</sub> ) <sup>1</sup>    | -0.5 | $V_{\mathrm{DD1}} + 0.5$ | V     |

| Output Voltage $(V_0)^1$                        | -0.5 | $V_{\mathrm{DD2}} + 0.5$ | V     |

| Average Current, per Pin <sup>2</sup>           |      |                          |       |

| Temperature ≤ 105°C                             | -25  | +25                      | mA    |

| Common-Mode Transients <sup>3</sup>             | -100 | +100                     | kV/μs |

<sup>「</sup>すべての電圧は、それぞれの対応するグラウンドを基準とします。

左記の絶対最大定格を超えるストレスを加えると、デバイスに恒 久的な損傷を与えることがあります。この規定はストレス定格の みを指定するものであり、この仕様の動作セクションに記載する 規定値以上でのデバイス動作を定めたものではありません。デバ イスを長時間絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

#### ESDに関する注意

ESD (静電放電)の影響を受けやすいデバイスです。 電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

表 10. 真理値表(正ロジック)

| V <sub>I</sub> Input | V <sub>DD1</sub> State | V <sub>DD2</sub> State | V <sub>o</sub> Output |

|----------------------|------------------------|------------------------|-----------------------|

| Н                    | Powered                | Powered                | Н                     |

| L                    | Powered                | Powered                | L                     |

| X                    | Unpowered              | Powered                | $\mathbf{H}^{1}$      |

| X                    | Powered                | Unpowered              | $X^1$                 |

$<sup>^{1}</sup>$   $V_{O}$  は電源復帰後  $1\,\mu s$  以内に  $V_{I}$ 状態に戻ります。

Rev. B - 9/16 -

<sup>&</sup>lt;sup>2</sup> 各種温度での最大許容電流については、図 2 を参照してください。

<sup>3</sup> 絶縁バリア間で発生するコモンモード過渡電圧を示します。コモンモード過 渡電圧がその絶対最大定格を超えると、ラッチアップまたは恒久的な損傷が 発生する可能性があります。

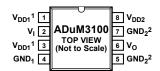

# ピン配置と機能の説明

1PIN 1 AND PIN 3 ARE INTERNALLY CONNECTED. IT IS STRONGLY RECOMMENDED THAT BOTH BE CONNECTED TO VDD1.

2PIN 5 AND PIN 7 ARE INTERNALLY CONNECTED. IT IS STRONGLY RECOMMENDED THAT BOTH BE CONNECTED TO GND2.

図 3. ピン配置

表 11. ピン機能の説明

| ピン番号 | 記号                 | 説明                |

|------|--------------------|-------------------|

| 1    | $V_{\mathrm{DD1}}$ | 入力側電源電圧、3.0~5.5 V |

| 2    | $V_{\rm I}$        | ロジック入力            |

| 3    | $V_{ m DD1}$       | 入力側電源電圧、3.0~5.5 V |

| 4    | $GND_1$            | 入力側グラウンド          |

| 5    | $GND_2$            | 出力側グラウンド          |

| 6    | $V_{0}$            | ロジック出力            |

| 7    | $GND_2$            | 出力側グラウンド          |

| 8    | VDD <sub>2</sub>   | 出力側電源電圧、3.0~5.5 V |

Rev. B — 10/16 —

## 代表的な性能特性

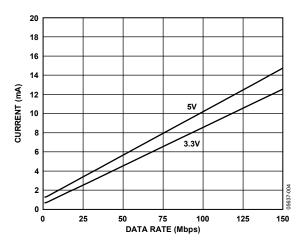

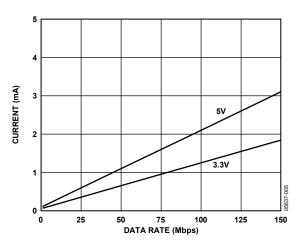

図 4. ロジック信号周波数 対 入力電源電流の特性 (5 V および 3.3 V 動作時)

図 5. ロジック信号周波数 対 出力電源電流の特性 (5 V および 3.3 V 動作時)

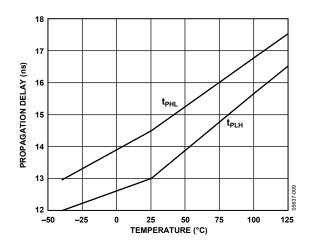

図 6. 伝播遅延の温度特性(5 V 動作時)

図7. 伝播遅延の温度特性(3.3 V 動作時)

図 8. 伝播遅延の温度特性(5 V/3 V 動作時)

図 9. 伝播遅延の温度特性(3 V/5 V 動作時)

Rev. B — 11/16 —

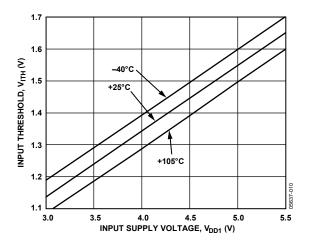

図 10. 入力電圧スイッチング・スレッショールド、 ローレベルからハイレベルへの遷移

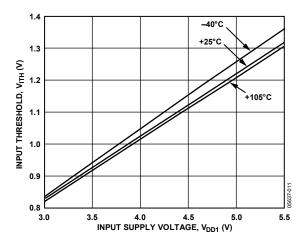

図 11. 入力電圧スイッチング・スレッショールド、 ハイレベルからローレベルへの遷移

## アプリケーション情報

#### PCボードのレイアウト

ADuM3100 デジタル・アイソレータは、ロジック・インターフェース用の外部レベル変換回路が必要ありません。入力と出力の電源ピンにバイパス・コンデンサの使用を推奨します。入力バイパス・コンデンサは、3番ピンと4番ピンの間にうまく配置することができます(図12を参照)。あるいは、1番ピンと4番ピンの間に配置することもできます。出力バイパス・コンデンサは、7番ピンと8番ピンの間、または5番ピンと8番ピンの間に接続できます。コンデンサの容量は、0.01  $\mu$ F から0.1  $\mu$ F までにしてください。コンデンサの両端から電源ピンまでのリード長は20 mmを超えないようにしてください。

図 12. PC ボードの推奨レイアウト

#### システム・レベルのESDに関する配慮と性能強化

システム・レベルの ESD 信頼性 (たとえば、IEC 61000-4-x に準拠した信頼性) は、アプリケーションによって大きく異なるシステム設計に依存しています。ESD 信頼性がシステム設計にあまり左右されないように、AduM3100 には、以下のように多くの性能強化が行われています。

- すべての入力/出力インターフェースに ESD 保護セルを追加

- パターンを太くし、ラインをビアに平行にすることにより、 重要なメタルパターン配線の抵抗を低減

- PMOS デバイスと NMOS デバイスの間にガードおよび絶縁技 術を適用し、CMOS デバイス固有の寄生 SCR 効果の影響を最 小化

- メタルパターン配線に 45°のコーナーを使用して、高電界密度 の領域を排除

- 各電源ピンとそれに対応するグラウンド間に大きい ESD クランプを接続して、電源ピンの過電圧を防止

AduM3100 はシステム・レベルの ESD 信頼性の向上に効果的ですが、耐久性の高いシステム・レベルの総合的な設計に完全に代わるものではありません。ボード・レイアウトとシステム・レベル設計に関する詳細な推奨事項については、アプリケーション・

ノート AN-793「ESD/Latch-Up Considerations with *i*Coupler Isolation Products」を参照してください。

#### 伝播遅延に関連するパラメータ

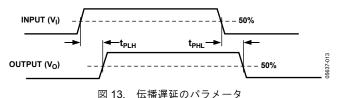

伝播遅延時間は、ロジック信号が部品を伝播する所要時間を表します。ロジック・ローレベル出力の伝播遅延時間とロジック・ハイレベル出力の伝播遅延時間は、入力信号が遷移した後でそれぞれ対応する出力信号が遷移するまでの時間を示します(図 13 を参照)。

パルス幅歪みは tplh と tphl との差の最大値であり、入力信号タイミングがデバイスの出力信号でどれほど維持されているかを表します。伝播遅延スキューは、同じ動作温度で動作し、同じ出力負荷をもつ複数の ADuM3100 製品の間の伝播遅延の最小値と最大値の差です。

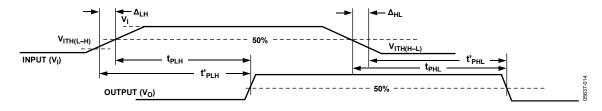

入力信号の立上がり/立下がり時間に応じて、入力の50%レベルをベースに測定された伝播遅延は、デバイスの真の伝播遅延(その入力スイッチング・スレッショールドから測定)とは異なることがあります。その理由は、よく使用されるフォトカプラの場合と同じく、入力スレッショールドの電圧レベルが入力信号の50%ポイントと異なるためです。この伝播遅延の差は、以下のように表すことができます。

$\Delta_{LH} = t'_{PLH} - t_{PLH} = (t_r/0.8 \ V_I)(0.5 \ V_I - V_{ITH \ (L-H)})$

$\Delta_{HL} = t'_{PHL} - t_{PHL} = (t_f/0.8 \ V_I)(0.5 \ V_I - V_{ITH \ (H-L)})$

ここで、

$t_{PLH}$ 、 $t_{PHL}$ は入力の 50%ポイントから測定した伝播遅延です。  $t_{PLH}$ 、 $t_{PHL}$ は入力スイッチング・スレッショールドから測定した 伝播遅延です。

$t_r$ 、 $t_f$ は入力の  $10\sim90\%$ ポイントにおける立上がり/立下がり時間です。

$V_I$ は入力信号の振幅 ( $0 \sim V_I$ のレベルを想定) です。

$V_{ITH(L-H)}$ 、 $V_{ITH(H-L)}$ は入力スイッチング・スレッショールドです。

図 14. 伝播遅延に対する入力立上がり/立下がり時間の影響

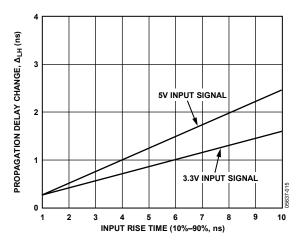

図 15. 入力立上がり時間の変動による代表的な伝播遅延の変化(V<sub>DD1</sub> = 3.3 V および 5 V 時)

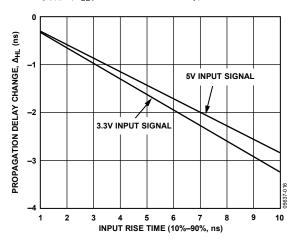

図 16. 入力立下がり時間の変動による代表的な伝播遅延の変化(V<sub>DD1</sub> = 3.3 V および 5 V 時)

入力エッジ速度の低速化も、入力の50%レベルをベースに測定したパルス幅歪みに影響を及ぼすことがあります。この影響によって、tpHL、tpLH、PWDの相対値に依存する見掛け上のパルス幅歪みが増加または減少することがあります。ここで注目するのは、パルス幅歪みを最大にする条件です。この場合の変化は、次式で表すことができます。

$\Delta_{PWD} = PWD' - PWD = \Delta_{LH} - \Delta_{HL} =$

$(t/0.8 \text{ V}_1)(V - V_{\text{ITH (L-H)}} - V_{\text{ITH (H-L)}}), (for \ t = t_r = t_f)$

ここで、

$PWD = |t_{PLH} - t_{PHL}|$

$PWD' = |t'_{PLH} - t'_{PHL}|$

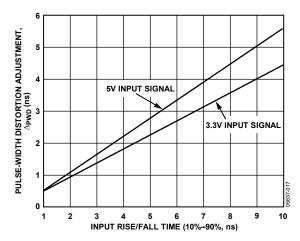

このパルス幅歪みの調整値を入力の立上がり/立下がり時間の 関数として表したものが、図 17です。

図 17. 入力立上がり/立下がり時間の変動による代表的なパルス幅歪み変化の調整値(V<sub>DD1</sub> = 3.3 V および 5 V 時)

#### 素子の動作、DC精度、磁界耐性

図1を見ると、2本のコイルがパルス・トランスとして機能しています。アイソレータ入力のロジックが正および負に遷移することによって、短いパルス(2 ns)がトランスからデコーダに送られます。デコーダは双安定性フリップフロップであるため、入力ロジックの遷移を示すパルスによってセットまたはリセットされます。約1 $\mu$ s以上経っても入力ロジックが遷移しない場合は、出力の DC 精度を維持するために、適切な極性の周期的な更新パルスが送信されます。約5 $\mu$ s以上経ってもデコーダがこれらのパルスをまったく受信しなければ、入力側に電源が印加されていないか、または機能していないと判断します。この場合、アイソレータの出力はウォッチドッグ・タイマ回路によってロジック・ハイレベルの状態に強制的に設定されます。

ADuM3100の磁界耐性の限界は、トランス受信コイルの誘導電圧が大きくなって、デコーダが誤ってセットまたはリセットされる状態が発生したときです。以下の解析は、これが発生する条件を定義するものです。この影響を最も受けやすい動作モードとして、ADuM3100の3.3 V動作条件を調べます。

トランスの出力パルスは振幅が  $1.0\,\mathrm{V}$  を超えます。デコーダのセンシング・スレッショールドは約  $0.5\,\mathrm{V}$  であるため、誘導電圧を許容できる  $0.5\,\mathrm{V}$  のノイズ・マージンを得ることができます。受信コイル間で誘導された電圧は、以下のようになります。

$V = (-d\beta/dt) \sum_{n=1}^{\infty} r_n^2, n = 1, 2, ..., N$

ここで、

βは磁束密度(ガウス)です。

Nは受信コイルの巻き数です。

$r_n$ は受信コイルのn番目の巻きの半径(cm)です。

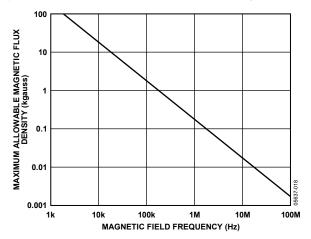

ADuM3100の受信コイルを所定の形状とし、誘導電圧が最大でもデコーダの 0.5 V マージンの 50%になるとすると、磁界の最大許容値は図 18 に示すように計算することができます。

図 18. 50%のマージンを確保できる外部磁界の最大許容値

たとえば、磁界周波数が 1 MHz のときに、磁界の最大許容値が 0.2 キロガウスであれば、受信コイルには 0.25 V の誘導電圧が生じます。これはセンシング・スレッショールドの約 50%であるため、誤って出力が遷移することはありません。同様に、このような事象がパルスの送信中に発生した場合(しかも極性が最悪時のとき)、送信パルスを 1.0 V を超える値から 0.75 V まで下げますが、それでもデコーダの 0.5 V のセンシング・スレッショールドを十分に上回っています。

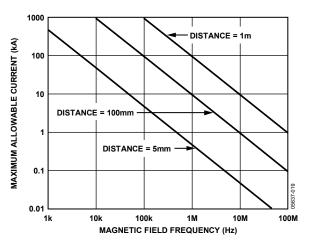

前述の磁束密度は、ADuM3100のトランスから所定の距離だけ離れた場所での特定の電流レベルに対応します。図 19には、いくつかの距離について周波数の関数となる電流レベルの許容値を示しています。この図からわかるように、ADuM3100は耐性が非常に高く、影響があるのは、高周波数の大きい電流がデバイスの非常に近く存在する場合だけです。この図に示す 1 MHz の例では、0.5 kA の電流が ADuM3100 から 5 mm離れたところにあれば、デバイスの動作に影響を及ぼしたことになります。

図 19. 電流と ADuM3100 間の距離に対する最大許容電流

ただし、強力な磁界と高い周波数が組み合わさったときは、PC ボードのパターンが作るループによって、非常に大きい誤差電圧 が誘導され、これが後続の回路のスレッショールドをトリガする ことがあります。このようなことにならないように、パターン配 線のレイアウトには注意してください。

#### 消費電力

ADuM3100 アイソレータの電源電流は、電源電圧、入力データレート、出力負荷の関数になります。

入力電源電流は、以下の式から求めることができます。

$$I_{DDI} = I_{DDI(Q)}$$

$$f \le 0.5f_r$$

$$I_{DDI} = I_{DDI(D)} \times (2f - f_r) + I_{DDI(Q)}$$

$$f > 0.5f_r$$

出力電源電流は、以下の式から求めることができます。

$$I_{DDO} = I_{DDO(Q)}$$

$f \le 0.5f_r$

$$I_{DDO} = (I_{DDO(D)} + (0.5 \times 10^{-3}) \times C_L V_{DDO}) \times (2f - f_r) + I_{DDO(Q)}$$

$f > 0.5f_r$

ここで、

$I_{DDI(D)}$ 、 $I_{DDO(D)}$ は各チャンネルごとの入力および出力のダイナミック電源電流(mA/Mbps)です。

$C_L$ は出力負荷容量(pF)です。

$V_{DDO}$ は出力電源電圧 (V) です。

fは入力ロジック信号周波数です(MHz、入力データレートの1/2、NRZシグナリング)。

frは入力段のリフレッシュ・レート (Mbps) です。

$I_{DDI(Q)}$ 、 $I_{DDO(Q)}$ は入力および出力の規定された無負荷時電源電流 (mA) です。

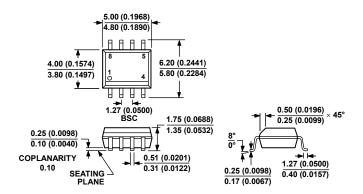

## 外形寸法

COMPLIANT TO JEDEC STANDARDS MS-012-A A CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

図 20. 8 ピン標準スモール・アウトライン・パッケージ [SOIC\_N] ナローボディ(R-8) 寸法単位:mm(インチ)

#### オーダー・ガイド

| Model                        | Temperature Range | Max Data<br>Rate (Mbps) | Minimum<br>Pulse Width (ns) | Package Description             | Package<br>Option |

|------------------------------|-------------------|-------------------------|-----------------------------|---------------------------------|-------------------|

| ADuM3100ARZ <sup>1</sup>     | -40°C to +105°C   | 25                      | 40                          | 8-Lead SOIC_N                   | R-8               |

| ADuM3100ARZ-RL7 <sup>1</sup> | −40°C to +105°C   | 25                      | 40                          | 8-Lead SOIC_N, 1,000 Piece Reel | R-8               |

| ADuM3100BRZ <sup>1</sup>     | −40°C to +105°C   | 100                     | 10                          | 8-Lead SOIC_N                   | R-8               |

| ADuM3100BRZ-RL7 <sup>1</sup> | −40°C to +105°C   | 100                     | 10                          | 8-Lead SOIC_N, 1,000 Piece Reel | R-8               |

<sup>&</sup>lt;sup>1</sup> Z = RoHS 準拠製品。

Rev. B