# マルチフォーマット SDTVビデオ・デコーダ

# **ADV7183B**

### 特長

NTSC-(M、N、4.43)、PAL-(B/D/G/H/I/M/N)、SECAM対応の マルチフォーマット・ビデオ・デコーダ

54MHz、10ビットのA/Dコンバータを3個内蔵

1個の27MHz水晶発信器でクロック駆動

ライン・ロック・クロック(LLC)と互換

アダプティブ・デジタル・ライン長トラッキング機能 (ADLLT<sup>TM</sup>)、信号処理、拡張FIFOマネジメントによりミニ TBC機能

5ライン長のアダプティブ・コムフィルタ(くし形フィルタ)を採用 VCRやチューナのようなノイズが多く、不安定な微弱ビデオ信 号源をロックする当社独自のアーキテクチャ

サブキャリア周波数ロックおよびステータス情報の出力 アダプティブ・ピーク・ホワイト・モードを備えたAGCを内蔵

Macrovision®コピー保護検出

CTI(カラー・トランジェント・インプルーブメント)

DNR(デジタル・ノイズ・リダクション)

プログラマブルな複数のアナログ入力フォーマット:

CVBS(コンポジット・ビデオ)

Sビデオ(Y/C)

YPrPbコンポーネント(VESA、MII、SMPTE、BetaCam)

12チャンネルのアナログ・ビデオ入力

NTSC/PAL/SECAMの自動識別

デジタル出力フォーマット(8ビットまたは16ビット):

ITU-R BT.656 YCrCb 4:2:2出力十HS、VS、FIELD

0.5~1.6Vのアナログ信号入力範囲

微分ゲイン: 0.5% (typ)

微分位相: 0.5°(typ)

プログラマブルなビデオ制御:

ピーク・ホワイト/色相/明度/彩度/コントラスト

ビデオ・タイミング・ジェネレータを内蔵

フリーラン・モード(入力なしで安定したビデオ出力を発生)

クローズド・キャプション(CC)、WSS、CGMS、EDTV、

Gemstar® 1×/2×対応のVBIデコード

パワーダウン・モード

2線式シリアルMPUインターフェース(I2C®互換)

アナログ電源:3.3V、デジタル・コア電源:1.8V、IO電源:3.3V

2種類の温度グレード:-25~+70℃、-40~+85℃

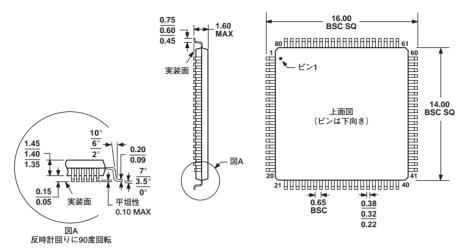

80ピンのLQFP鉛フリー・パッケージ

### アプリケーション

DVDレコーダ ビデオ・プロジェクタ HDDベースのPVR/DVDR 液晶TV セットトップ・ボックス セキュリティ・システム デジタル・テレビ

AVRレシーバ

### 概要

ADV7183Bビデオ・デコーダは、世界的な標準であるNTSC、PAL、SECAM互換の標準アナログ・ベースバンド・テレビ信号を自動的に検出し、16/8ビットのCCIR601/CCIR656互換の4:2:2コンポーネント・ビデオ・データに変換します。

先進的できわめて柔軟性の高いこのビデオ・デコーダのデジタル出力は、ライン・ロック・クロックをベースにしたシステムとのインターフェースを容易にします。このため、ADV7183Bはテープ・ベースの信号源、放送用信号源、セキュリティ/監視カメラ、業務用システムなどのさまざまなアナログ・ビデオ特性を持つ広範囲なアプリケーションに最適となっています。

10ビットの高精度A/D変換は業務用品質のビデオ性能を提供し、これに並ぶものはありません。このため、8ビット出力モードで真の8ビット分解能を実現できます。

12チャンネルのアナログ入力は、標準のコンポジット信号やSビデオ信号、YPrPbビデオ信号をいろいろな組合わせで取り込むことができます。 AGC(自動ゲイン・コントロール)回路とクランプ再生回路が内蔵されて いるため、0.5~1.6Vのピークtoピーク範囲をもつビデオ信号の入力が可能になります。また、これらの回路をバイパスしてマニュアル設定することもできます。

全モードでADCとデータ・パスに対して固定の54MHzクロックが使用できるため、非常に高精度で正確なサンプリングとデジタル・フィルタリングが可能になります。ライン・ロック・クロック出力により、±5%のライン長変化があっても、出力データレート、タイミング信号、出力クロック信号を同期化、非同期化、またはラインにロックすることができます。出力制御信号は、ほとんどのアプリケーションでグルーレスなインターフェース接続を可能とします。ADV7183Bのモードは、2線式のシリアル双方向ポート(I²C互換)で設定します。

ADV7183Bは3.3V CMOSプロセスで製造されています。モノリシック CMOS構造を採用しているため、低消費電力でより多くの機能を実現しています。

ADV7183Bは鉛フリーの小型80ピンLQFPパッケージを採用しています。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいはその利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的また暗示的に許諾するものでもありません。仕様は予告なく変更する場合があります。本紀記載の商標および登録商標は、各社の所有に属します。\*日本語データシートは、REVISIONが古い場合があります。最新の内容については英語版をご参照ください。©2004 Analog Devices, Inc. All rights reserved.

REV.0

本 社/東京都港区海岸1-16-1 電話03(5402)8200 〒105-6891 ニューピア竹芝サウスタワービル

大阪営業所 / 大阪府大阪市淀川区宮原3-5-36 電話06(6350)6868(代) 〒532-0003 新大阪MTビル2号

# 目次

| 輝度信号フィルタ・・・・・・・・20                                                       |

|--------------------------------------------------------------------------|

| 色信号フィルタ・・・・・・20                                                          |

| ゲイン動作・・・・・・30                                                            |

| カラー・ドランジェント・インプルーブメント (CTI) ・・・・3:                                       |

| デジタル・ノイズ・リダクション (DNR) ・・・・・・・・・・34                                       |

| コムフィルタ(くし形フィルタ)・・・・・・・・3:                                                |

| AVコードの挿入と制御 ······3                                                      |

| 同期出力信号・・・・・・39                                                           |

| 同期処理・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                 |

| VBIデータ・デコード・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                           |

| ピクセル・ポートの設定・・・・・・・55                                                     |

| MPUポートの説明 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                           |

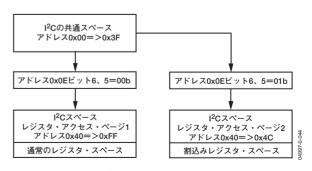

| レジスタのアクセス・・・・・・・6.                                                       |

| レジスタの設定・・・・・・・・・・・・・・・・・・6.                                              |

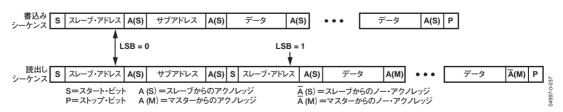

| I <sup>2</sup> Cシーケンサ6.                                                  |

| I <sup>2</sup> Cレジスタ・マップ ・・・・・・・・・・・62                                   |

| I <sup>2</sup> Cレジスタ・マップの詳細 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・         |

| I <sup>2</sup> Cのプログラミング例 ・・・・・・88                                       |

| モード1:CVBS入力(AIN5上のコンポジット・ビデオ)・・・・88                                      |

| モード2:Sビデオ入力 (AIN1上のY、AIN4上のC) ······8                                    |

| モード3:525i/625i YPrPb入力(AIN2上のY、AIN3上のPr、<br>AIN6上のPb)・・・・・・・・・・・・・・・・・89 |

| モード4:AIN4上のCVBSチューナ入力PAL専用 ······89                                      |

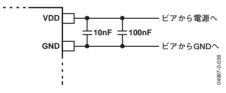

| PCボード・レイアウトの推奨事項 ・・・・・・・・90                                              |

| アナログ・インターフェース入力・・・・・・・9(                                                 |

| 電源のデカップリング・・・・・・・・・・・・・・・・・90                                            |

| PLL90                                                                    |

| デジタル出力 (データとクロックの両方) ・・・・・・・・・・・・・・9(                                    |

| デジタル入力・・・・・・・9:                                                          |

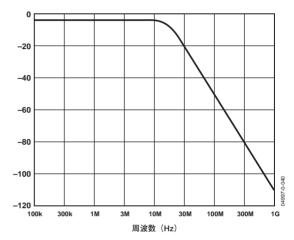

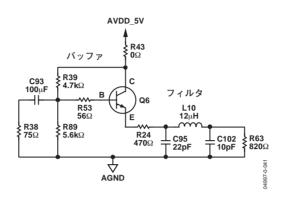

| アンチエイリアシング(折返し誤差防止)フィルタ・・・・・・・9:                                         |

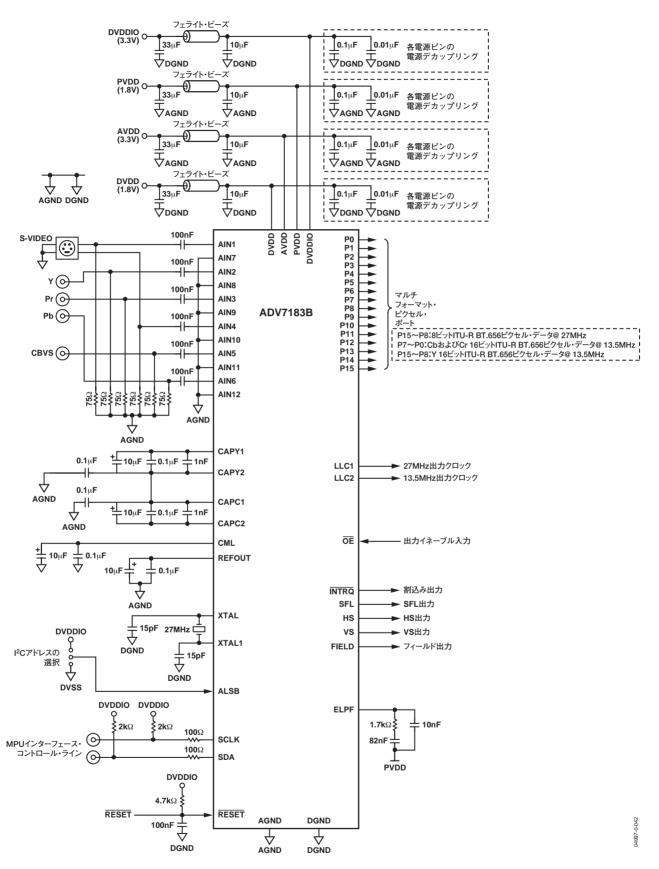

| 代表的な回路接続・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                             |

| 外形寸法・・・・・・9.                                                             |

| オーダー・ガイド・・・・・・・94                                                        |

|                                                                          |

|                                                                          |

### 改訂履歴

9/04-リビジョン0:初版

## はじめに

ADV7183Bは高品質なシングル・チップのマルチフォーマット・ビデオ・デコーダで、コンポジット、Sビデオ、コンポーネント・ビデオ形式のPAL、NTSC、SECAM標準を自動的に検出し、デジタルITU-R BT.656フォーマットに変換します。

先進的できわめて柔軟性の高いこのビデオ・デコーダのデジタル出力は、ライン・ロック・クロックをベースにしたシステムとのインターフェースを容易にします。このため、ADV7183Bはテープ・ベースの信号源、放送用信号源、セキュリティ/監視カメラ、業務用システムなどのさまざまなアナログ・ビデオ特性を持つ広範囲なアプリケーションに最適です。

### アナログ・フロントエンド

ADV7183Bのアナログ・フロントエンドは3つの10ビットA/Dコンバータ (ADC)から構成されており、ADCはアナログ・ビデオ信号をデジタル化してSDP(標準ビデオ信号処理プロセッサ)に与えます。アナログ・フロントエンドでは、ミックスド・シグナル・アプリケーションで高性能を実現するために、各ADCの入力で差動チャンネルを採用しています。

このフロントエンドには、複数のビデオ信号を入力できる12チャンネルの入力マルチプレクサも用意されています。各ADCの前には電流クランプと電圧クランプが配置されているため、ビデオ信号は必ずADCの入力範囲内に収まるようになっています。ビデオ信号微調クランピングは、ADV7183Bに内蔵されているデジタル微調クランピング機能を用いてダウンストリームで実行されます。各ADCは4倍オーバーサンプリング・モードで動作する構成になっています。

### SDP(標準ビデオ信号処理プロセッサ)

ADV7183Bは、コンポジット、Sビデオ、コンポーネントなどのフォーマットのさまざまなベースバンド・ビデオ信号をデコーディングできます。サポートするビデオ標準としては、PAL B/D/I/G/H、PAL60、PAL M、PAL N、PAL N、NTSC M/J、NTSC 4.43、SECAM B/D/G/K/Lなどがあります。ADV7183Bはビデオ標準を自動的に検出して処理できます。

ADV7183Bは5ライン、スーパーアダプティブの2Dコムフィルタ(くし形フィルタ)を内蔵しており、コンポジット・ビデオ信号をデコーディングする際に色信号と輝度信号を高精度に分離できます。このフィルタは、きわめて適合性に優れているため、ユーザが手を加えることなく、ビデオ標準と信号品質に応じて自動的に処理モードを調節します。ADV7183Bでは、明度、コントラスト、彩度、色相などのユーザによる制御も行えます。

ADV7183Bは、信号源から出力されるビデオ・ライン長の変化をトラッキングする、特許取得済みのアダプティブ・デジタル・ライン長トラッキング (ADLLT)アルゴリズムを採用しています。このADLLT機能により、ADV7183BはVCRをはじめ、ノイズの多いチューナ出力、VCDプレーヤ、ビデオ・カメラなどの通常品質のビデオ信号源をトラックし、デコードできます。ADV7183BはCTI(カラー・トランジェント・インプルーブメント)プロセッサを内蔵しており、色信号遷移のエッジをシャープにすることで、際立った垂直遷移を実現しています。

ADV7183Bは、クローズド・キャプション(CC)、ワイド・スクリーン・シグナリング(WSS)、コピー・ジェネレーション・マネジメント・システム(CGMS)、EDTV、Gemstar 1×/2×、拡張データ・サービス(XDS)などのさまざまなVBIデータ・サービスを処理できます。ADV7183Bは、Macrovision®の認定を取得しており、検出回路はType I、II、IIIの保護レベルを識別し、報告することができます。また、デコーダは、すべてのMacrovision信号入力に十分に対応できます。

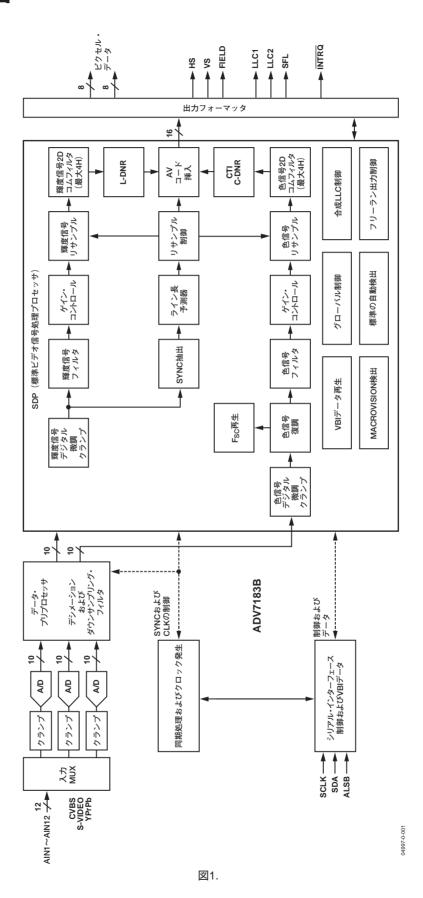

# 機能ブロック図

# 仕様

温度範囲: T<sub>MIN</sub>~T<sub>MAX</sub>、-40~+85℃。この範囲でmin/max仕様を保証。

### 電気的特性

A<sub>VDD</sub>=3.15~3.45V、D<sub>VDD</sub>=1.65~2.0V、D<sub>VDDIO</sub>=3.0~3.6V、P<sub>VDD</sub>=1.65~2.0V(特に指定のない限り、動作温度範囲)

### 表1.

| パラメータ          | 記号                 | テスト条件                      | Min  | Тур             | Max     | 単位      |

|----------------|--------------------|----------------------------|------|-----------------|---------|---------|

| 静的性能           |                    |                            |      |                 |         |         |

| 分解能(各ADC)      | N                  |                            |      |                 | 10      | ビット     |

| 積分非直線性         | INL                | 54MHzでのBSL                 |      | $-0.475/\pm0.6$ | $\pm 3$ | LSB     |

| 微分非直線性         | DNL                | 54MHzでのBSL                 |      | $-0.25/\pm0.5$  | -0.7/+2 | LSB     |

| デジタル入力         |                    |                            |      |                 |         |         |

| 入力ハイレベル電圧      | $V_{\mathrm{IH}}$  |                            | 2    |                 |         | V       |

| 入力ローレベル電圧      | $V_{ m IL}$        |                            |      |                 | 0.8     | V       |

| 入力電流           | $I_{\mathrm{IN}}$  | 注1に示すピン                    | -50  |                 | +50     | $\mu$ A |

|                |                    | その他の全ピン                    | -10  |                 | +10     | $\mu$ A |

| 入力容量           | $C_{\rm IN}$       |                            |      |                 | 10      | pF      |

| デジタル出力         |                    |                            |      |                 |         |         |

| 出力ハイレベル電圧      | V <sub>OH</sub>    | I <sub>SOURCE</sub> =0.4mA | 2.4  |                 |         | V       |

| 出力ローレベル電圧      | $V_{OL}$           | $I_{SINK}=3.2mA$           |      |                 | 0.4     | V       |

| 高インピーダンス・リーク電流 | $I_{LEAK}$         | 注2に示すピン                    |      |                 | 50      | $\mu$ A |

|                |                    | その他の全ピン                    |      |                 | 10      | $\mu$ A |

| 出力容量           | C <sub>OUT</sub>   |                            |      |                 | 20      | pF      |

| 電源条件3          |                    |                            |      |                 |         |         |

| デジタル・コア電源      | $D_{VDD}$          |                            | 1.65 | 1.8             | 2       | V       |

| デジタルI/O電源      | D <sub>VDDIO</sub> |                            | 3.0  | 3.3             | 3.6     | V       |

| PLL電源          | P <sub>VDD</sub>   |                            | 1.65 | 1.8             | 2.0     | V       |

| アナログ電源         | A <sub>VDD</sub>   |                            | 3.15 | 3.3             | 3.45    | V       |

| デジタル・コア電源電流    | $I_{DVDD}$         |                            |      | 82              |         | mA      |

| デジタルI/O電源電流    | $I_{DVDDIO}$       |                            |      | 2               |         | mA      |

| PLL電源電流        | $I_{PVDD}$         |                            |      | 10.5            |         | mA      |

| アナログ電源電流       | I <sub>AVDD</sub>  | CVBS入力 <sup>4</sup>        |      | 85              |         | mA      |

|                |                    | YPrPb入力 <sup>5</sup>       |      | 180             |         | mA      |

| パワーダウン電流       | I <sub>PWRDN</sub> |                            |      | 1.5             |         | mA      |

| パワーアップ時間       | $t_{PWRUP}$        |                            |      | 20              |         | ms      |

<sup>1</sup>ピン36、79

<sup>21、2、5、6、8、12、17、18~24、32~35、74~76、80</sup>の各ピン

<sup>3</sup> 特性評価により保証

<sup>4</sup> ADC1をパワーオン

<sup>&</sup>lt;sup>5</sup>全3個のADCをパワーオン

### ビデオ仕様

特性評価により保証。 $A_{VDD}$ =3.15~3.45V、 $D_{VDD}$ =1.65~2.0V、 $D_{VDDIO}$ =3.0~3.6V、 $P_{VDD}$ =1.65~2.0V(特に指定のない限り、動作温度範囲)

### 表2.

| パラメータ               | 記号    | テスト条件            | Min | Тур       | Max | 単位    |

|---------------------|-------|------------------|-----|-----------|-----|-------|

| 非直線性仕様              |       |                  |     |           |     |       |

| 微分位相                | DP    | CVBS I/P、変調5ステップ |     | 0.5       | 0.7 | 0     |

| 微分ゲイン               | DG    | CVBS I/P、変調5ステップ |     | 0.5       | 0.7 | %     |

| 輝度信号非直線性            | LNL   | CVBS I/P、5ステップ   |     | 0.5       | 0.7 | %     |

| ノイズ仕様               |       |                  |     |           |     |       |

| S/N比(重みなし)          |       | 輝度信号ランプ          | 54  | 56        |     | dB    |

|                     |       | 輝度信号平坦フィールド      | 58  | 60        |     | dB    |

| アナログ・フロントエンド・クロストーク |       |                  |     | 60        |     | dB    |

| ロック時間仕様             |       |                  |     |           |     |       |

| 水平ロック範囲             |       |                  | -5  |           | +5  | %     |

| 垂直ロック範囲             |       |                  | 40  |           | 70  | Hz    |

| Fscサブキャリア・ロック範囲     |       |                  |     | $\pm 1.3$ |     | Hz    |

| カラー・ロックイン時間         |       |                  |     | 60        |     | ライン   |

| Sync深さ範囲            |       |                  | 20  |           | 200 | %     |

| カラー・バースト範囲          |       |                  | 5   |           | 200 | %     |

| 垂直ロック時間             |       |                  |     | 2         |     | フィールド |

| 自動検出切替え速度           |       |                  |     | 100       |     | ライン   |

| 色信号仕様               |       |                  |     |           |     |       |

| 色相精度                | HUE   |                  |     | 1         |     | 0     |

| カラー彩度精度             | CL_AC |                  |     | 1         |     | %     |

| カラーAGC範囲            |       |                  | 5   |           | 400 | %     |

| 色信号振幅誤差             |       |                  |     | 0.5       |     | %     |

| 色信号位相誤差             |       |                  |     | 0.4       |     | ۰     |

| 色信号と輝度信号間の相互変調      |       |                  |     | 0.2       |     | %     |

| 輝度信号仕様              |       |                  |     |           |     |       |

| 輝度信号明度精度            |       | CVBS、1V I/P      |     | 1         |     | %     |

| 輝度信号コントラスト精度        |       | CVBS、1V I/P      |     | 1         |     | %     |

### タイミング仕様

特性評価により保証。 $A_{VDD}$ =3.15~3.45V、 $D_{VDD}$ =1.65~2.0V、 $D_{VDDIO}$ =3.0~3.6V、 $P_{VDD}$ =1.65~2.0V(特に指定のない限り、動作温度範囲)

### 表3.

| パラメータ                  | 記号              | テスト条件                                                                         | Min   | Тур   | Max      | 単位              |

|------------------------|-----------------|-------------------------------------------------------------------------------|-------|-------|----------|-----------------|

| システム・クロックおよび水晶発振器      |                 |                                                                               |       |       |          |                 |

| 公称周波数                  |                 |                                                                               |       | 27.00 |          | MHz             |

| 周波数安定性                 |                 |                                                                               |       |       | $\pm 50$ | ppm             |

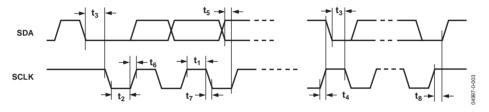

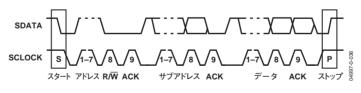

| I <sup>2</sup> Cポート    |                 |                                                                               |       |       |          |                 |

| SCLK周波数                |                 |                                                                               |       |       | 400      | kHz             |

| SCLKのハイレベル最小パルス幅       | t <sub>1</sub>  |                                                                               | 0.6   |       |          | μs              |

| SCLKのローレベルの最小パルス幅      | t <sub>2</sub>  |                                                                               | 1.3   |       |          | μs              |

| ホールド時間(スタート状態)         | t <sub>3</sub>  |                                                                               | 0.6   |       |          | μs              |

| セットアップ時間(スタート状態)       | t <sub>4</sub>  |                                                                               | 0.6   |       |          | μs              |

| SDAのセットアップ時間           | t <sub>5</sub>  |                                                                               | 100   |       |          | ns              |

| SCLKとSDAの立上がり時間        | t <sub>6</sub>  |                                                                               |       |       | 300      | ns              |

| SCLKとSDAの立下がり時間        | t <sub>7</sub>  |                                                                               |       |       | 300      | ns              |

| ストップ状態のセットアップ時間        | t <sub>8</sub>  |                                                                               |       | 0.6   |          | μs              |

| リセット機能                 |                 |                                                                               |       |       |          |                 |

| リセット・パルス幅              |                 |                                                                               | 5     |       |          | ms              |

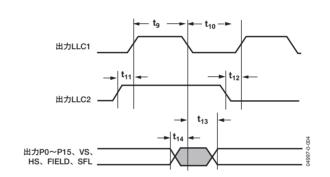

| クロック出力                 |                 |                                                                               |       |       |          |                 |

| LLC1のマーク/スペース比         | t9:t10          |                                                                               | 45:55 |       | 55:45    | %デューティ・<br>サイクル |

| LLC1の立上がりからLLC2の立上がりまで | t <sub>11</sub> |                                                                               |       | 0.5   |          | ns              |

| LLC1の立上がりからLLC2の立下がりまで | t <sub>12</sub> |                                                                               |       | 0.5   |          | ns              |

| データ出力とコントロール信号出力       |                 |                                                                               |       |       |          |                 |

| データ出力の遷移時間             | t <sub>13</sub> | 立下がりエッジから有効データの開始まで (t <sub>ACCESS</sub> =t <sub>10</sub> -t <sub>13</sub> )  |       |       | 3.4      | ns              |

| データ出力の遷移時間             | t <sub>14</sub> | 有効データの終わりから立下がりエッジまで<br>(t <sub>HOLD</sub> =t <sub>9</sub> +t <sub>14</sub> ) |       |       | 2.4      | ns              |

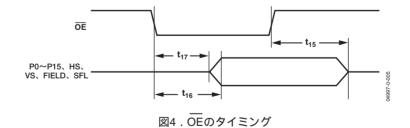

| Hi-Zまでの伝搬遅延            | t <sub>15</sub> |                                                                               |       | 6     |          | ns              |

| 出力イネーブルの最大アクセス時間       | t <sub>16</sub> |                                                                               |       | 7     |          | ns              |

| 出力イネーブルの最小アクセス時間       | t <sub>17</sub> |                                                                               |       | 4     |          | ns              |

### アナログ仕様

特性評価により保証。 $A_{VDD}$ =3.15~3.45V、 $D_{VDD}$ =1.65~2.0V、 $D_{VDDIO}$ =3.0~3.6V、 $P_{VDD}$ =1.65~2.0V (特に指定のない限り、動作温度範囲)

### 表4.

| パラメータ         | 記号 | テスト条件    | Min | Тур  | Max | 単位 |

|---------------|----|----------|-----|------|-----|----|

| クランプ回路        |    |          |     |      |     |    |

| 外付けクランプ・コンデンサ |    |          |     | 0.1  |     | μF |

| 入力インピーダンス     |    | クランプ・オフ時 |     | 10   |     | ΜΩ |

| クランプ流出大電流     |    |          |     | 0.75 |     | mA |

| クランプ流入大電流     |    |          |     | 0.75 |     | mA |

| クランプ流出小電流     |    |          |     | 60   |     | μΑ |

| クランプ流入小電流     |    |          |     | 60   |     | μΑ |

### 熱仕様

表5.

| パラメータ            | 記号          | テスト条件                  | Min | Тур  | Max | 単位   |

|------------------|-------------|------------------------|-----|------|-----|------|

| 接合部/ケース間熱抵抗      | $\theta$ JC | 全面グラウンド・プレーンを持つ4層PCボード |     | 7.6  |     | °C/W |

| 接合部/周囲間熱抵抗(自然空冷) | $\theta$ JA | 全面グラウンド・プレーンを持つ4層PCボード |     | 38.1 |     | ℃/W  |

### タイミング図

図2.I<sup>2</sup>Cのタイミング

図3.ピクセル・ポートとコントロール信号のタイミング

8

# 絶対最大定格

表6.

| パラメータ                                   | 定格                                     |

|-----------------------------------------|----------------------------------------|

| GNDに対するAvdd                             | 4V                                     |

| AGNDに対するA <sub>VDD</sub>                | 4V                                     |

| DGNDに対するD <sub>VDD</sub>                | 2.2V                                   |

| AGNDに対するP <sub>VDD</sub>                | 2.2V                                   |

| DGNDに対するD <sub>VDDIO</sub>              | 4V                                     |

| AVDDに対するD <sub>VDDIO</sub>              | $-0.3\sim+0.3V$                        |

| D <sub>VDD</sub> に対するP <sub>VDD</sub>   | $-0.3\sim+0.3V$                        |

| $D_{\mathrm{VDDIO}} - P_{\mathrm{VDD}}$ | $-0.3\sim +2V$                         |

| $D_{VDDIO} - D_{VDD}$                   | $-0.3\sim +2V$                         |

| $A_{VDD} - P_{VDD}$                     | $-0.3\sim +2V$                         |

| $A_{VDD}$ $ D_{VDD}$                    | $-0.3\sim +2V$                         |

| DGNDに対するデジタル入力電圧                        | $-0.3V\sim$ D <sub>VDDIO</sub> $+0.3V$ |

| DGNDに対するデジタル出力電圧                        | $-0.3V\sim$ D <sub>VDDIO</sub> $+0.3V$ |

| AGNDに対するアナログ入力                          | AGND $-0.3V\sim A_{VDD}+0.3V$          |

| 最大ジャンクション温度(T <sub>J</sub> max)         | 150℃                                   |

| 保存温度範囲                                  | _65~+150°C                             |

| 赤外線リフロー・ハンダ(20秒)                        | 260℃                                   |

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な 損傷を与えることがあります。この規定はストレス定格のみを指定するも のであり、この仕様の動作セクションに記載する規定値以上でのデバイ ス動作を定めたものではありません。デバイスを長時間絶対最大定格状 態に置くと、デバイスの信頼性に影響を与えることがあります。

### 注意

ESD(静電放電)の影響を受けやすいデバイスです。人体や試験機器には4,000Vもの高圧の静電気が容易に蓄積され、検知されないまま放電されることがあります。本製品は当社独自のESD保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、回復不能の損傷を生じる可能性があります。したがって、性能劣下や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

# ピン配置および機能の説明

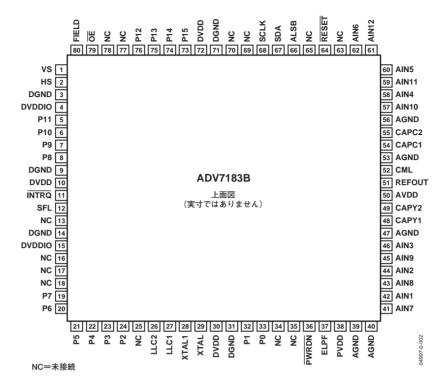

図5.80ピンLQFPのピン配置

表7. ピン機能の説明

| ピン番号                                                             | 記号         | タイプ | 機能                                                            |

|------------------------------------------------------------------|------------|-----|---------------------------------------------------------------|

| 3, 9, 14, 31, 71                                                 | DGND       | G   | デジタル・グラウンド                                                    |

| 39, 40, 47, 53, 56                                               | AGND       | G   | アナログ・グラウンド                                                    |

| 4, 15                                                            | DVDDIO     | P   | デジタルI/O電源電圧 (3.3V)                                            |

| 10, 30, 72                                                       | DVDD       | P   | デジタル·コア電源電圧(1.8V)                                             |

| 50                                                               | AVDD       | P   | アナログ電源電圧 (3.3V)                                               |

| 38                                                               | PVDD       | P   | PLL電源電圧 (1.8V)                                                |

| 42, 44, 46, 58, 60, 62, 41, 43, 45, 57, 59, 61                   | AIN1~AIN12 | I   | アナログ・ビデオ入力チャンネル                                               |

| 11                                                               | ĪNTRQ      | О   | 割込み要求出力。入力ビデオ上に一定の信号が検出されると、割込みが発生します。<br>表82の割込みレジスタ・マップを参照。 |

| 13, 16~18, 25, 34, 35, 63, 65, 69, 70, 77, 78                    | NC         |     | 未使用ピン                                                         |

| 33, 32, 24, 23, 22,<br>21, 20, 19, 8, 7, 6, 5,<br>76, 75, 74, 73 | P0∼P15     | О   | ビデオ・ピクセル出力ポート                                                 |

| 2                                                                | HS         | О   | 水平同期出力信号                                                      |

| 1                                                                | VS         | О   | 垂直同期出力信号                                                      |

| 80                                                               | FIELD      | О   | フィールド同期出力信号                                                   |

| 67                                                               | SDA        | I/O | I <sup>2</sup> Cポートのシリアル・データ入出力ピン                             |

| 68                                                               | SCLK       | I   | I <sup>2</sup> Cポートのシリアル・クロック入力(最大クロック・レート: 400kHz)           |

| 66                                                               | ALSB       | I   | このピンはADV7183BのI <sup>2</sup> Cアドレスを選択します。ALSBをローレベルに設定すると、    |

|                                                                  |            |     | 書込みアドレスが0x40に設定されます。ALSBをハイレベルに設定すると、アドレスが                    |

|                                                                  |            |     | 0x42に設定されます。                                                  |

| ピン番号   | 記号           | タイプ | 機能                                                          |

|--------|--------------|-----|-------------------------------------------------------------|

| 64     | RESET        | I   | アクティブ・ローレベルのシステム・リセット入力。ADV7183Bの回路をリセットするには、               |

|        |              |     | RESETに最小幅5msのローレベル・パルスを入力する必要があります。                         |

| 27     | LLC1         | О   | これは、ADV7183Bの出力ピクセル・データに対する、ライン・ロック出力クロックです。                |

|        |              |     | 公称27MHzですが、ビデオ・ライン長に応じて上下に変動します。                            |

| 26     | LLC2         | О   | これは、ADV7183Bの出力ピクセル・データに対する、LLC1出力クロックの2分周出力                |

|        |              |     | です。公称13.5MHzですが、ビデオ・ライン長に応じて上下に変動します。                       |

| 29     | XTAL         | I   | 27MHzの水晶発振器の入力ピンですが、外付けの3.3V、27MHzのクロック発振器から                |

|        |              |     | 駆動することもできます。水晶発振器モードでは、基本波水晶発振器を使う必要があり                     |

|        |              |     | ます。                                                         |

| 28     | XTAL1        | О   | このピンは27MHzの水晶発振器に接続します。ADV7183Bのクロックとして外付け3.3V、             |

|        |              |     | 27MHzのクロック発振器を使用する場合は、開放のままにします。水晶発振器モードで                   |

|        |              |     | は、基本波水晶発振器を使う必要があります。                                       |

| 36     | PWRDN        | I   | このピンにロジック・ローレベルを入力すると、ADV7183Bはパワーダウン・モードになり                |

|        |              |     | ます。ADV7183Bのパワーダウン・モードでのオプションについては、I <sup>2</sup> Cレジスタ・マップ |

|        |              |     | を参照してください。                                                  |

| 79     | ŌE           | I   | OE にロジック・ローレベルを入力すると、ADV7183Bのピクセル出力バス、P15~P0が              |

|        |              |     | イネーブルになります。 OE ピンにロジック・ハイレベルを入力すると、P15~P0、HS、VS、            |

|        |              |     | SFL/SYNC_OUTの各ピンは高インピーダンス状態になります。                           |

| 37     | ELPF         | I   | 推奨の外部ループ・フィルタは、このELPFピンに接続する必要があります(図45)。                   |

| 12     | SFL          | О   | サブキャリア周波数ロック。このピンにはシリアル出力ストリームが含まれています。この                   |

|        |              |     | デコーダをアナログ・デバイセズの任意のデジタル・ビデオ・エンコーダに接続するとき                    |

|        |              |     | は、これを使用してサブキャリア周波数をロックします。                                  |

| 51     | REFOUT       | О   | 内蔵電圧リファレンス出力。このピンに対する推奨コンデンサ・ネットワークについては、                   |

|        |              |     | 図45を参照してください。                                               |

| 52     | CML          | О   | CMLピンは内蔵ADCのコモン・モード・レベル出力です。このピンに対する推奨コンデン                  |

|        |              |     | サ・ネットワークについては図45を参照してください。                                  |

| 48, 49 | CAPY1, CAPY2 | I   | ADCのコンデンサ・ネットワーク。このピンに対する推奨コンデンサ・ネットワークについて                 |

|        |              |     | は図45を参照してください。                                              |

| 54, 55 | CAPC1, CAPC2 | I   | ADCのコンデンサ・ネットワーク。このピンに対する推奨コンデンサ・ネットワークについて                 |

|        |              |     | は図45を参照してください。                                              |

# アナログ・フロントエンド

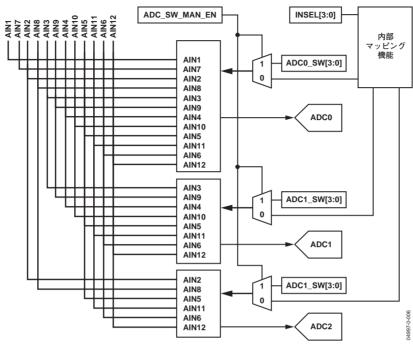

### アナログ入力のマルチプレクサ

図6.内部ピン接続

12

ADV7183Bはアナログ・マルチプレクシング部を内蔵しているため、複数のビデオ信号源をデコーダに接続できます。図6に、ADV7183Bの入力マルチプレクサの全体構成を示します。

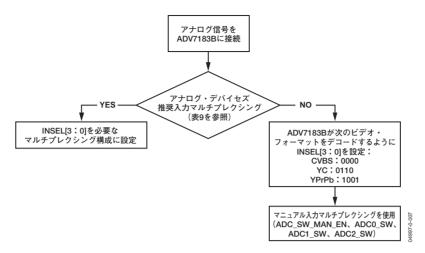

図6に示すように、アナログ入力マルチプレクシングを制御するには、2つの方法があります。ファンクショナル・レジスタ(INSEL)による方法とマニュアルによる方法です。INSEL[3:0]を使用するとマルチプレクサのセットアップが簡素化され、入力チャンネルを事前に割り当てることでチャンネル間のクロストークを最小化できます。これは、アナログ・デバイセズの推奨する入力マルチプレクシングです。

$I^2$ Cマニュアル・オーバーライド(ADC\_sw\_man\_en、ADC0\_sw、ADC1\_sw、ADC2\_sw)による制御は、予め割り当てた入力接続を使わない特別な条件(たとえば、信号の数/組合わせ)のアプリケーション向けに用意されています。これがマニュアル入力マルチプレクシングです。

ADV7183Bの入力マルチプレククシングを制御する2つの方法については、図7を参照してください。

### アナログ・デバイセズ推奨の入力マルチプレクシング

ADV7183Bでは、最大12のCVBS入力を接続し、デコードすることができます。図5からわかるように、これは信号源をICの隣接ピンに接続する必要があるということです。このため、PCボードのレイアウトは注意深く設計する必要があります(たとえば、物理的に隣接するパターン上の全信号間でのグラウンド・シールド)。

### INSEL[3:0] 入力選択、アドレス 0x00 [3:0]

INSELビットで入力チャンネルと入力フォーマットを選択できます。PCボードの接続によっては、INSELモードの一部のみが有効になります。なお、INSEL[3:0]はアナログ入力マルチプレクシングを切り替えるだけでなく、CVBS(Comp)、Sビデオ(Y/C)、コンポーネント(YPbPr)の各フォーマットを処理するようにSDPコアを設定します。

図7.入力マルチプレクシングの概要

表8. INSEL[3:0]を使用した入力チャンネルの切替え

| べる。 INOLL[3.0]を使用したパカナヤンネルの切目だ |              |            |  |  |  |  |  |

|--------------------------------|--------------|------------|--|--|--|--|--|

|                                | 説            | 明          |  |  |  |  |  |

| INSEL[3:0]                     | アナログ入力ピン     | ビデオ・フォーマット |  |  |  |  |  |

| 0000(デフォルト値)                   | CVBS1=AIN1   | コンポジット     |  |  |  |  |  |

| 0001                           | CVBS2=AIN2   | コンポジット     |  |  |  |  |  |

| 0010                           | CVBS3=AIN3   | コンポジット     |  |  |  |  |  |

| 0011                           | CVBS4=AIN4   | コンポジット     |  |  |  |  |  |

| 0100                           | CVBS5=AIN5   | コンポジット     |  |  |  |  |  |

| 0101                           | CVBS6=AIN6   | コンポジット     |  |  |  |  |  |

| 0110                           | Y1=AIN1      | YC         |  |  |  |  |  |

|                                | C1=AIN4      | YC         |  |  |  |  |  |

| 0111                           | Y2=AIN2      | YC         |  |  |  |  |  |

|                                | C2=AIN5      | YC         |  |  |  |  |  |

| 1000                           | Y3=AIN3      | YC         |  |  |  |  |  |

|                                | C3=AIN6      | YC         |  |  |  |  |  |

| 1001                           | Y1=AIN1      | YPrPb      |  |  |  |  |  |

|                                | PR1=AIN4     | YPrPb      |  |  |  |  |  |

|                                | PB1=AIN5     | YPrPb      |  |  |  |  |  |

| 1010                           | Y2=AIN2      | YPrPb      |  |  |  |  |  |

|                                | PR2=AIN3     | YPrPb      |  |  |  |  |  |

|                                | PB2=AIN6     | YPrPb      |  |  |  |  |  |

| 1011                           | CVBS7=AIN7   | コンポジット     |  |  |  |  |  |

| 1100                           | CVBS8=AIN8   | コンポジット     |  |  |  |  |  |

| 1101                           | CVBS9=AIN9   | コンポジット     |  |  |  |  |  |

| 1110                           | CVBS10=AIN10 | コンポジット     |  |  |  |  |  |

| 1111                           | CVBS11=AIN11 | コンポジット     |  |  |  |  |  |

表9. 入力チャンネルの割当て

| 入力<br>チャンネル | ピン<br>番号 | アナログ・デバイセズ推奨の入力マルチプレクシング制御<br>INSEL[3:0] |       |           |  |  |  |

|-------------|----------|------------------------------------------|-------|-----------|--|--|--|

| AIN7        | 41       | CVBS7                                    |       |           |  |  |  |

| AIN1        | 42       | CVBS1                                    | YC1-Y | YPrPb1-Y  |  |  |  |

| AIN8        | 43       | CVBS8                                    |       |           |  |  |  |

| AIN2        | 44       | CVBS2                                    | YC2-Y | YPrPb2-Y  |  |  |  |

| AIN9        | 45       | CVBS9                                    |       |           |  |  |  |

| AIN3        | 46       | CVBS3                                    | YC3-Y | YPrPb2-Pb |  |  |  |

| AIN10       | 57       | CVBS10                                   |       |           |  |  |  |

| AIN4        | 58       | CVBS4                                    | YC1-C | YPrPb1-Pb |  |  |  |

| AIN11       | 59       | CVBS11                                   |       |           |  |  |  |

| AIN5        | 60       | CVBS5                                    | YC2-C | YPrPb1-Pr |  |  |  |

| AIN12       | 61       | 使用不可                                     |       |           |  |  |  |

| AIN6        | 62       | CVBS6                                    | ҮС3-С | YPrPb2-Pr |  |  |  |

アナログ・デバイセズ推奨の入力マルチプレクシングは、信号チャンネル間のクロストークを最小化し、最高レベルの信号の完全性が得られるように設計されています。表9に、PCボードのレイアウトを使ったADV7183Bへのアナログ・ビデオ信号の接続方法を示します。

未使用のアナログ入力ピンは、AGNDに接続してシールドとして使うことを強く推奨します。

6本の入力チャンネルのみを使う場合は、入力AIN7~AIN11を必ず AGNDに接続します。こうするとチャンネル間のアイソレーションが改善 されるため、サンプリングの品質が向上します。

AIN12は、INSEL[3:0]では制御できません。これは、マニュアル・マルチプレクシングによってのみ、ADC0/ADC1/ADC2に接続できます。詳細は、表10を参照してください。

### マニュアル入力マルチプレクシング

ADV7183Bのアナログ入力マルチプレクサは、マニュアル・オーバーライド・マルチプレクシング・レジスタにアクセスすることにより直接制御できます。これは、マニュアル入力マルチプレクシングと呼びます。

マニュアル入力マルチプレクシングは、他の入力マルチプレクシング制御ビット(たとえば、INSEL)より優先されます。

ADC\_SW\_MAN\_ENビットを設定すると、マニュアル・マルチプレクシングが有効になります。これで影響を受けるのは、ADCの前にあるアナログ・スイッチのみです。これは、INSELの設定とマニュアル入力マルチプレクシング・レジスタ(ADC0/ADC1/ADC2\_sw)の設定が互いに矛盾している場合は、ADC0/ADC1/ADC2\_swの設定が採用され、INSELが無視されることを意味します。

マニュアル入力マルチプレクシングは、アナログ入力マルチプレクサのみを制御します。後段のブロックがビデオ・データを正しいフォーマットで処理できるように、INSEL[3:0]も設定する必要があります。つまり、INSELを使用して、入力信号のフォーマットがコンポーネント、YC、CVBSのいずれであるかをADV7183Bに知らせる必要があるということです。

IC内部のアナログ信号のルーティングに起因して、チャンネル・ルーティングに制約があります。すなわち、各入力ピンは各ADCに接続することができません。チップ内部のルーティング機能の概要については、図6を参照してください。3つのマルチプレクサ・セクションは、予備の制御信号バスADC0/ADC1/ADC2\_sw[3:0]で制御することができます。表10に、使用する制御ワードを示します。

# SETADC\_sw\_man\_en、マニュアル入力マルチプレクシング・イネーブル、アドレス0xC4[7]

ADC0\_sw[3:0]、ADC0マルチプレクサ設定、アドレス0xC3[3:0] ADC1\_sw[3:0]、ADC1マルチプレクサ設定、アドレス0xC3[7:4] ADC2 sw[3:0]、ADC2マルチプレクサ設定、アドレス0xC4[3:0]

表10. すべてのADCに対するマニュアル・マルチプレクサの設定(SETADC\_sw\_man\_en = 1)

| ADC0_sw[3:0] | ADCOの接続 | ADC1_sw[3:0] | ADC1の接続 | ADC2_sw[3:0] | ADC2の接続 |

|--------------|---------|--------------|---------|--------------|---------|

| 0000         | 未接続     | 0000         | 未接続     | 0000         | 未接続     |

| 0001         | AIN1    | 0001         | 未接続     | 0001         | 未接続     |

| 0010         | AIN2    | 0010         | 未接続     | 0010         | AIN2    |

| 0011         | AIN3    | 0011         | AIN3    | 0011         | 未接続     |

| 0100         | AIN4    | 0100         | AIN4    | 0100         | 未接続     |

| 0101         | AIN5    | 0101         | AIN5    | 0101         | AIN5    |

| 0110         | AIN6    | 0110         | AIN6    | 0110         | AIN6    |

| 0111         | 未接続     | 0111         | 未接続     | 0111         | 未接続     |

| 1000         | 未接続     | 1000         | 未接続     | 1000         | 未接続     |

| 1001         | AIN7    | 1001         | 未接続     | 1001         | 未接続     |

| 1010         | AIN8    | 1010         | 未接続     | 1010         | AIN8    |

| 1011         | AIN9    | 1011         | AIN9    | 1011         | 未接続     |

| 1100         | AIN10   | 1100         | AIN10   | 1100         | 未接続     |

| 1101         | AIN11   | 1101         | AIN11   | 1101         | AIN11   |

| 1110         | AIN12   | 1110         | AIN12   | 1110         | AIN12   |

| 1111         | 未接続     | 1111         | 未接続     | 1111         | 未接続     |

# グローバル・コントロール・レジスタ

ここに記載するレジスタ制御ビットはチップ全体に影響を与えます。

### パワー・セーブ・モード

### パワーダウン

### PDBP、アドレス0x0F [2]

ADV7183Bのデジタル・コアをシャットダウンするには、ピン(PWRDN)を使用する方法とビット(PWRDN下記参照)を使用する方法があります。PDBPはこの2つの方法の優先順位を制御します。デフォルトではピン(PWRDN)が優先されます。この機能により、デフォルトでADV7183Bをパワーダウンできます。

PDBDが0(デフォルト)のとき、PWRDN ピンによりデジタル・コア電源は制御されます(ビットは無視されます)。

PDBDが1のとき、ビットが優先されます(ピンが無視されます)。

### PWRDN、アドレス0x0F [5]

PWRDNビットをセットすると、ADV7183Bのチップ全体がパワーダウン・モードになります。パワーダウンでは、チップのデジタル部へのクロック入力が停止されるため、動作がフリーズします。パワーダウン時にPCビットが失われることはありません。PWRDNビットはアナログ・ブロックにも影響を与え、それらを低電流モードに切り替えます。I<sup>2</sup>Cインターフェース自体は影響を受けず、パワーダウン・モードでも動作を続けます。

PWRDNビットが0に設定された場合 ( ${

m PC}$ 経由)、またはデバイス全体がリセットされた場合 ( ${

m RESET}$  ピン使用)、ADV7183Bはパワーダウン状態から抜け出します。

なお、PWRDNビットでADV7183Bをパワーダウンさせるには、PDBPを1に設定する必要があります。

PWRDNが0(デフォルト)のとき、チップは動作状態です。

PWRDNが1のとき、ADV7183Bはチップ全体がパワーダウンします。

### ADCパワーダウン制御

ADV7183Bには、3個の10ビットADC (ADC 0、ADC 1、ADC 2)が内蔵されています。必要に応じて、各ADCを個別にパワーダウンできます。

ADCをパワーダウンする必要がある時:

- CVBSモード: 消費電力を節約するため、ADC 1とADC 2をパワーダウンします。

- Sビデオ・モード: 消費電力を節約するため、ADC 2をパワーダウンします。

### PWRDN\_ADC\_0、アドレス0x3A[3]

PWRDN\_ADC\_0が0(デフォルト)のとき、ADCは通常動作になります。 PWRDN\_ADC\_0が1のとき、ADC 0はパワーダウンします。

### PWRDN ADC 1、アドレス0x3A [2]

PWRDN\_ADC\_1が0(デフォルト)のとき、ADCは通常動作になります。 PWRDN\_ADC\_1が1のとき、ADC 1はパワーダウンします。

### PWRDN ADC\_2、アドレス0x3A [1]

PWRDN\_ADC\_2が0(デフォルト)のとき、ADCは通常動作になります。 PWRDN ADC 2が1のとき、ADC 2はパワーダウンします。

### リセット制御

### チップ・リセット(RES)、アドレス0x0F[7]

このビットをセットすると、RESET ピンと同じ機能を持ち、ADV7183Bチップ全体がリセットされます。すべてのI<sup>2</sup>Cレジスタがデフォルト値にリセットされます(リセット値が指定されていないレジスタ・ビットもあります。これらのビットは直前に書き込まれた値を保持します。レジスタの表ではリセット値をxで表示してあります)。リセット・シーケンス後、デバイスは直ちにビデオ信号の受信を開始します。

RESビットをセットした後(またはピンでリセットを開始後)、デバイスはプライマリ動作モードに関してデフォルトの動作モードに戻ります。すべてのI<sup>2</sup>Cビットにデフォルト値がロードされるため、このビットはクリアされます。

ソフトウェア・リセットの実行には約2msを要します。しかし、I<sup>2</sup>Cに対する 書込みは5ms待ってから行うことを推奨します。

チップ・リセットを実行すると、I<sup>2</sup>Cマスター・コントローラは9番目のクロック・サイクルでノー・アクノレッジ状態を受信します。「MPUポートの説明」の項を参照してください。

RESが0(デフォルト値)のとき、通常動作になります。

RESが1のとき、リセット・シーケンスを開始します。

### グローバル・ピンの制御

### スリーステート出力ドライバ

TOD、アドレス0x03[6]

このビットは、ADV7183Bの出力ドライバをスリーステートにすることができます。

TODビットをセットすると、P15~P0、HS、VS、FIELD、SFLの各ピンはスリーステートになります。

タイミング・ピン(HS/VS/FIELD)は、TIM\_OEビットで強制的にアクティブにできます。スリーステート制御の詳細は、「スリーステートLLCドライバ」と「タイミング信号出力イネーブル」の項を参照してください。

個々の駆動強度の制御は、DR STR XXビットを使って行います。

ADV7183Bは専用ピンでスリーステートをサポートしています。ハイレベルに設定すると、OE ピンはP15~P0、HS、VS、FIELD、SFLの出力ドライバをスリーステートにします。TODビットまたはOE ピンがハイレベルに設定されると、出力ドライバはスリーステートになります。

TOD が0(デフォルト値)のとき、出力ドライバはイネーブルになります。

TOD が1のとき、出力ドライバはスリーステートになります。

### スリーステートLLCドライバ

### TRI\_LLC、アドレス0x1D[7]

このビットにより、ADV7183BのLLC1ピンとLLC2ピンの出力ドライバが スリーステートになります。スリーステート制御の詳細は、「スリーステート 出力ドライバ」と「タイミング信号出力イネーブル」の項を参照してくだ さい。

個々の駆動強度の制御は、DR STR XXビットを使って行います。

TRI\_LLCが0(デフォルト値)のとき、LLCピンのドライバはDR\_STR\_C [1:0]の設定に従って動作します(ピン・イネーブル時)。

TRI\_LLCが1のとき、LLCピン・ドライバはスリーステートになります。

### タイミング信号出力イネーブル

TIM\_OE、アドレス0x04 [3]

TIM\_OEビットは、TODビットに対する追加ビットとみなすことができます。ハイレベルに設定すると、TODビットがセットされている場合でも、HS、VS、FIELDの出力ドライバは強制的にアクティブ状態(すなわち駆動状態)になります。ローレベルに設定されると、TODビットに応じて、HS、VS、FIELDの各ピンはスリーステートになります。デコーダをタイミング・ジェネレータとしてのみ使用する場合には、この機能が便利です。このようなケースとしては、受信信号からタイミング信号だけを抽出する場合、またはデバイスがフリーラン・モードになり、別のチップがたとえば会社のロゴなどを出力できるようになった場合があります。

スリーステート制御の詳細は、「スリーステート出力ドライバ」と「スリーステートLLCドライバ」の項を参照してください。

個々の駆動強度の制御は、DR STR XXビットを使って行います。

TIM\_OEが 0(デフォルト値)のとき、HS、VS、FIELDはTODビットに応じてスリーステートになります。

TIM\_OEが 1のとき、HS、VS、FIELDは常時アクティブになります。

### 駆動強度選択(データ)

DR\_STR[1:0]、アドレス0xF4[5:4]

出力ドライバの駆動強度は、EMCとクロストークのために調節したほうがいい場合があります。DR\_STR[1:0]ビットは、P[15:0]出力ドライバを調節します。

スリーステート制御の詳細は、「駆動強度選択(クロック)」と「駆動強度 選択(同期)」の項を参照してください。

表11. DR\_STRの機能

| DR_STR [1:0] | 説明          |

|--------------|-------------|

| 00           | 駆動強度:低(1×)  |

| 01(デフォルト値)   | 駆動強度:中低(2×) |

| 10           | 駆動強度:中高(3×) |

| 11           | 駆動強度:高(4×)  |

### 駆動強度選択(クロック)

DR\_STR\_C[1:0]、アドレス0xF4 [3:2]

DR\_STR\_C[1:0]ビットにより、クロック信号出力ドライバ(LLCピン)の強度を選択できます。詳細は、「駆動強度選択(同期)」と「駆動強度選択(データ) | の項を参照してください。

### 表12. DR\_STR\_Cの機能

| DR_STR_C[1:0] | 説明          |

|---------------|-------------|

| 00            | 駆動強度:低(1×)  |

| 01(デフォルト値)    | 駆動強度:中低(2×) |

| 10            | 駆動強度:中高(3×) |

| 11            | 駆動強度:高(4×)  |

### 駆動強度選択(同期)

DR\_STR\_S[1:0]、アドレス0xF4[1:0]

DR\_STR\_S[1:0]ビットにより、HS、VS、Fを駆動する同期信号の強度を選択します。詳細は、「駆動強度選択(クロック)」と「駆動強度選択(データ)」の項を参照してください。

### 表13. DR\_STR\_Sの機能

| DR_STR_S[1:0] | 説明          |

|---------------|-------------|

| 00            | 駆動強度:低(1×)  |

| 01 (デフォルト値)   | 駆動強度:中低(2×) |

| 10            | 駆動強度:中高(3×) |

| 11            | 駆動強度:高(4×)  |

### イネーブル・サブキャリア周波数ロック・ピン

EN\_SFL\_PIN、アドレス0x04 [1]

EN\_SFL\_PINビットは、デコーダの後ろにエンコーダを接続(または、エンコーダの後ろにデコーダを接続)する場合に、ADV7183Bからエンコーダに対するサブキャリア・ロック情報(GenLockともいう)の出力をイネーブルにします。

EN\_SFL\_PINが0(デフォルト値)のとき、サブキャリア周波数ロック出力はディスエーブルになります。

EN\_SFL\_PIN が1のとき、サブキャリア周波数ロック情報はSFLピンに出力されます。

### 極性LLCピン

PCLK、アドレス0x37 [0]

PCLKビットにより、ADV7183BのLLC1ピンとLLC2ピンから出力される クロックの極性を反転できます。

LLCクロック出力の極性は、後段チップのセットアップ時間よびホールド時間に合わせて変更を必要とする場合があります。

このビットはLLC2クロックの極性も反転します。

PCLKが0のとき、LLC出力極性は反転します。

PCLKが 1(デフォルト値)のとき、LLC出力極性は(タイミング図に書いてある通り)通常のままです。

# グローバル・ステータス・レジスタ

ビデオ・デコーダの情報を提供するレジスタは4個あります。IDENTレジスタは、ADV7183Bのリビジョン・コードを識別します。他の3個のレジスタにはIC動作に関するステータス・ビットが格納されます。

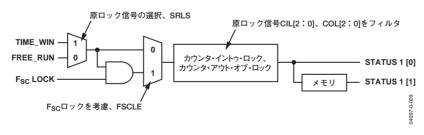

Status[0]ビットとStatus[1]ビットは、FSCLEビットの設定に応じて、水平タイミング情報のみか、または水平タイミングとカラー・サブキャリアのロック・ステータスをベースにします。FSCLE(Fscロック・イネーブル)、アドレス0x51[7]を参照してください。

### 識別

### IDENT[7:0]、アドレス0x11 [7:0]

このレジスタはADV7183Bのリビジョンを識別します。

0x11はADV7183のリリース時の識別番号を表します。

0x13はADV7183Bの識別番号を表します。

### STATUS 1

### STATUS\_1[7:0], アドレス0x10[7:0]

この読出し専用レジスタは、ADV7183Bの内部ステータスの情報を提供します。

タイミング情報については、CIL[2:0](カウント・イントゥ・ロック)、アドレス 0x51 [2:0]、およびCOL[2:0](カウント・アウト・オブ・ロック)、アドレス 0x51[5:3]を参照してください。

### 自動検出結果

### AD RESULT[2:0]、アドレス0x10[6:4]

AD\_RESULT[2:0]ビットは、自動検出ブロックの結果を報告します。自動検出ブロックのイネーブルについては「全体的なセットアップ」を、設定方法については「SDモードの自動検出」を参照してください。

表14. AD\_RESULTの機能

| AD_RESULT[2:0] | 説明                |

|----------------|-------------------|

| 000            | NTSM-MJ           |

| 001            | NTSC-443          |

| 010            | PAL-M             |

| 011            | PAL-60            |

| 100            | PAL-BGHID         |

| 101            | SECAM             |

| 110            | PAL-Combination N |

| 111            | SECAM 525         |

### 表15. STATUS 1の機能

| STATUS 1 [7:0] | ビット名        | 説明                      |

|----------------|-------------|-------------------------|

| 0              | IN_LOCK     | ロック中(現在)                |

| 1              | LOST_LOCK   | ロック喪失(このレジスタの最後の読出し以降)  |

| 2              | FSC_LOCK    | Fscロック中(現在)             |

| 3              | FOLLOW_PW   | ピーク・ホワイト・アルゴリズムを考慮したAGC |

| 4              | AD_RESULT.0 | 自動検出結果                  |

| 5              | AD_RESULT.1 | 自動検出結果                  |

| 6              | AD_RESULT.2 | 自動検出結果                  |

| 7              | COL_KILL    | カラーキルがアクティブ             |

### STATUS 2

STATUS\_2[7:0], アドレス0x12[7:0]

表16. STATUS 2の機能

| STATUS 2 [7:0] | ビット名       | 説明                                                         |

|----------------|------------|------------------------------------------------------------|

| 0              | MVCS DET   | Macrovisionカラー・ストライプを検出                                    |

| 1              | MVCS T3    | Macrovisionカラー・ストライプ保護。Type 3 (ハイレベルの場合)とType 2 (ローレベルの場合) |

|                |            | に準拠                                                        |

| 2              | MV_PS DET  | Macrovision擬似同期パルスを検出                                      |

| 3              | MV_AGC DET | Macrovision AGCパルスを検出                                      |

| 4              | LL_NSTD    | ライン長が非標準                                                   |

| 5              | FSC_NSTD   | Fsc周波数が非標準                                                 |

| 6              | 予備         |                                                            |

| 7              | 予備         |                                                            |

### STATUS 3

STATUS\_3[7:0]、アドレス0x13[7:0]

表17. STATUS 3の機能

| STATUS 3 [7:0] | ビット名         | 説明                                 |

|----------------|--------------|------------------------------------|

| 0              | INST_HLOCK   | 水平ロック表示(瞬時)                        |

| 1              | GEMD         | Gemstarデータ検出                       |

| 2              | SD_OP_50HZ   | 出力に現れる50Hzか60Hzのフラグ                |

| 3              |              | 予備                                 |

| 4              | FREE_RUN_ACT | ブルー・スクリーンを出力(「DEF_VAL_AUTO_EN」を参照) |

| 5              | STD_FLD_LEN  | フィールド長が現在選択中のビデオ標準に一致              |

| 6              | INTERLACED   | インターレース・ビデオを検出(フィールド・シーケンスを検出)     |

| 7              | PAL_SW_LOCK  | スウィンギング・バーストの確実なシーケンスを検出           |

# SDP(標準ビデオ信号処理プロセッサ)

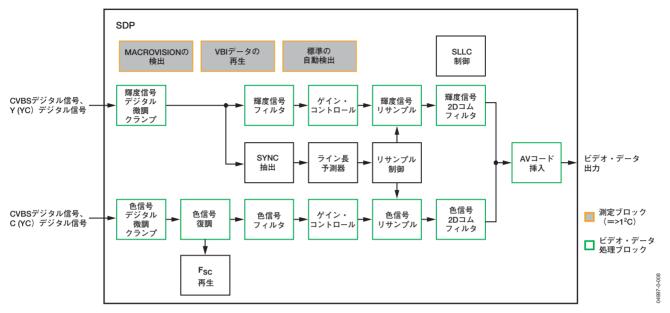

図8.SDPのブロック図

ADV7183BのSDPのブロック図を図8に示します。

SDPブロックは、CVBS、YC、YPrPbの各フォーマットの標準ビデオを処理できます。ブロックは輝度信号パスと色信号パスに分割できます。入力ビデオがコンポジット・タイプ(CVBS)の場合、CVBS入力は両方の処理パスに渡されます。

### 輝度信号パス

入力信号は次のブロックで処理されます。

- デジタル微調クランプ:このブロックは高精度アルゴリズムを使用して、 ビデオ信号をクランプします。

- ●輝度信号フィルタ・ブロック:このブロックには、固定応答を持つ輝度信号デシメーション・フィルタ(YAA)と、選択可能な応答を持つ複数のシェイピング・フィルタ(YSH)が含まれています。

- ●輝度ゲイン・コントロール: 自動ゲイン・コントロール(AGC)は、水平同期パルスの深さに基づくゲイン、ピーク・ホワイト・モード、固定マニュアル・ゲインなど、さまざまなモードで動作できます。

- ●輝度信号リサンプル:ライン長誤差やダイナミック・ライン長変化を修正するため、データをデジタル的にリサンプルします。

- ●輝度信号2Dコム:2次元コムフィルタによりYC分離を行います。

- AVコード挿入:この時点で、デコードされた輝度(Y)信号と色信号値が統合されます。AVコード(ITU-R BT.656準拠)を挿入できます。

### 色信号パス

入力信号は次のブロックで処理されます。

- デジタル微調クランプ:このブロックは高精度アルゴリズムを使用して、 ビデオ信号をクランプします。

- ●色信号復調:このブロックは、カラー・サブキャリア(Fsc)再生ユニット を使用し、任意の色信号変調方式でカラー・サブキャリアを再発生し ます。次に、PALとNTSCに対してはAM復調を、SECAMに対しては FM復調を行います。

- ●色信号フィルタ・ブロック:このブロックには、固定応答を持つ色信号 デシメーション・フィルタ(CAA)と、選択可能な応答を持つ複数のシェイピング・フィルタ(CSH)が含まれています。

- ゲイン・コントロール:自動ゲイン・コントロール(AGC)は、カラー・サブ キャリアの振幅に基づくゲイン、輝度信号チャンネルの水平同期パル スの深さに基づくゲイン、または固定マニュアル・ゲインなど、さまざま なモードで動作できます。

- ●色信号リサンプル:色信号データは輝度信号データと位置がぴったり合うように、デジタル的にリサンプルされます。リサンプリングは、受信ビデオ信号のスタティック・ライン長エラーとダイナミック・ライン長誤差を修正するために行われます。

- ●色信号2Dコムフィルタ:2次元5ラインのスーパーアダプティブ・コムフィルタは、入力信号がCVBSの場合に高品質のYC分離を行います。

- AVコード挿入:この時点で、復調された色信号(CrとCb)と輝度値が 統合されます。AVコード(ITU-R BT.656準拠)を挿入できます。

### 同期処理

AD7183Bは、ビデオ・データ・ストリームに埋めこまれた同期信号を取り出します。現在、外部HS/VS入力には対応していません。同期抽出機能は、不完全なビデオ信号源(たとえば、ヘッド切替えのビデオカセット・レコーダ)にも対応できるように最適化されています。使用している実際のアルゴリズムでは、スレッショールド交差に基づく粗い検出と、それに続くアダプティブ・インターポレーション・アルゴリズムを使用した密な検出を採用しています。原同期情報は、ライン長計測および予測ブロックに送られます。このブロックの出力はデジタル・リサンプリング・ブロックに入力され、AD7183Bが確実に1ライン当たり720個のアクティブ・ピクセルを出力するようにします。

また、ADV7183Bの同期処理には、デジタル化されたアナログ・ビデオから原同期情報を取り出し、そのフィルタリングおよびコンデショニングを行う、2つの特別なポスト・プロセシング・ブロックが含まれています。

- VSYNCプロセッサ:このブロックは、検出されたVSYNCをさらにフィルタリングして垂直ロック機能を改善します。

- ●HSYNCプロセッサ:HSYNCプロセッサは、ノイズで壊れた入力 HSYNCをフィルタリングするように設計されているため、タイム・ベー スは安定していてもS/N比が悪いビデオ信号の性能をさらに改善し ます。

### VBIデータの再生

ADV7183Bは、入力ビデオから次の情報を取り出します。

- ワイド・スクリーン・シグナリング (WSS)

- コピー・ジェネレーション・マネジメント・システム(CGMS)

- クローズド・キャプション(CC)

- Macrovision保護の有無

- EDTVデータ

- Gemstar互換データのスライシング

また、ADV7183Bは受信するビデオ標準について、自動的に次の検出が行えます。

- カラー・サブキャリア 周波数

- フィールド・レート

- ライン・レート

さらに、PAL-BGHID、PAL-M/N、PALコンビネーションN、NTSC-M、NTSC-J、SECAM 50Hz/60Hz、NTSC4.43、PAL60に対応するように構成できます。

### 全体的なセットアップ

### ビデオ標準の選択

VID\_SEL[3:0]ビットにより、デジタル・コアを特定のビデオ標準用に強制的に設定できます。通常は、この機能は必要ありません。 VID\_SEL[3:0]ビットは、デフォルトでPAL、NTSC、SECAM、およびこれらの派生に対応する自動検出モードに設定されています。自動検出システムについては、次の項を参照してください。

### 自動検出

自動検出システムを制御するため、サポートしているビデオ標準ごとに個別のイネーブル・ビットが用意されています。該当するビットを0に設定すると、その標準の自動検出が停止され、代わりにシステムはイネーブルになっている標準の中で最も近いものを選択します。自動検出結果は、ステータス・レジスタから読み出すことができます。詳細は、「グローバル・ステータス・レジスタ」を参照してください。

VID\_SEL[3:0]、アドレス0x00[7:4]

表18. VID SELの機能

| VID SEL      | 説明                          |

|--------------|-----------------------------|

| 0000(デフォルト値) | 自動検出 (PAL BGHID) <-> NTSC J |

|              | (ペデスタルなし)、SECAM             |

| 0001         | 自動検出(PAL BGHID)<-> NTSC M   |

|              | (ペデスタル)、SECAM               |

| 0010         | 自動検出(PAL N)(ペデスタル)<->       |

|              | NTSC J (ペデスタルなし)、SECAM      |

| 0011         | 自動検出(PAL N)(ペデスタル)<->       |

|              | NTSC M(ペデスタル)、SECAM         |

| 0100         | NTSC J (1)                  |

| 0101         | NTSC M (1)                  |

| 0110         | PAL 60                      |

| 0111         | NTSC 4.43 (1)               |

| 1000         | PAL BGHID                   |

| 1001         | PAL N (=PAL BGHID(ペデスタルあり)) |

| 1010         | PAL M (ペデスタルなし)             |

| 1011         | PAL M                       |

| 1100         | PALコンビネーションN                |

| 1101         | PALコンビネーションN (ペデスタルあり)      |

| 1110         | SECAM                       |

| 1111         | SECAM (ペデスタルあり)             |

AD\_SEC525\_EN (SECAM 525ライン・ビデオの自動検出イネーブル)、アドレス0x07 [7]

AD\_SEC525\_ENを0(デフォルト値)に設定すると、SECAM型FM変調カラー・コンポーネントを持つ525ライン・システムの自動検出がディスエーブルになります。

AD\_SEC525\_EN を1に設定すると、検出がイネーブルになります。

AD\_SECAM\_EN (SECAMの自動検出イネーブル)、アドレス0x07 [6] AD\_SECAM\_ENを0に設定すると、SECAMの自動検出がディスエーブルになります。

AD\_SECAM\_ENを1(デフォルト値)に設定すると 検出がイネーブル になります。

AD\_N443\_EN (NTSC 443の自動検出イネーブル)、アドレス0x07 [5] AD\_N443\_EN を0に設定すると、4.43MHzカラー・サブキャリアを持つ NTSCシステムの自動検出がディスエーブルになります。

AD\_N443\_EN を1(デフォルト値)に設定すると、検出がイネーブルになります。

### AD\_P60\_EN (PAL60の自動検出イネーブル)、アドレス0x07 [4]

AD\_P60\_EN を0に設定すると、60Hzのフィールド・レートを持つPALシステムの自動検出がディスエーブルになります。

AD\_P60\_EN を1(デフォルト値)に設定すると、検出がイネーブルになります。

### AD PALN EN(PAL Nの自動検出イネーブル)、アドレス0x07[3]

AD\_PALN\_ENを0に設定すると、PAL N標準の検出がディスエーブルになります。

AD\_PALN\_ENを1(デフォルト値)に設定すると、検出がイネーブルになります。

### AD\_PALM\_EN (PAL Mの自動検出イネーブル)、アドレス0x07 [2]

AD\_PALM\_ENを0に設定すると、PAL Mの自動検出がディスエーブルになります。

AD\_PALM\_ENを1(デフォルト値)に設定すると、検出がイネーブルになります。

### AD\_NTSC\_EN (NTSCの自動検出イネーブル)、アドレス0x07 [1]

AD\_NTSC\_ENを0に設定すると、標準NTSCの検出がディスエーブルになります。

AD\_NTSC\_ENを1(デフォルト値)に設定すると、検出がイネーブルになります。

### AD\_PAL\_EN (PALの自動検出イネーブル)、アドレス0x07 [0]

AD\_PAL\_ENをOに設定すると、標準PALの検出がディスエーブルになります。

AD\_PAL\_ENを1(デフォルト値)に設定すると、検出がイネーブルになります。

### SFL INV(サブキャリア周波数ロックの反転)

このビットは、SFL (GenLock Telegram)データ・ストリーム内のPALスイッチ・ビットの動作を制御します。ビデオ・エンコーダとの互換性の問題を解消するためにあり、次の2つの問題を解消します。

- 1. PALスイッチ・ビットはPALでのみ意味を持ちます。 エンコーダによっては(アナログ・デバイセズのエンコーダも含む)、NTSCでのこのビットの状態を見るものもあります。

- 2. アナログ・デバイセズのエンコーダADV717x~ADV719xで設計上の変更がありました。旧バージョンではSFL(GenLock Telegram)ビットをそのまま使用しましたが、新バージョンでは使用する前にビットを反転します。この理由は、反転によってSFL(GenLock Telegram) 転送の1ライン遅延を補償するためです。

結果として、ADV717xエンコーダでは、NTSCを動作させるためSFL (GenLock Telegram)内のPALスイッチ・ビットを1にする必要があります。ADV7190/ADV7191/ADV7194エンコーダでは、NTSCで動作するためにSFL内のPALスイッチ・ビットを0にする必要があります。

PALスイッチ・ビットの状態が正しくないと、180°の位相シフトが発生します。

デコーダとエンコーダを隣り合わせて接続するシステム(SFLを使用)では、使用する特定のエンコーダに合わせてこのビットを設定する必要があります。

### SFL INV、アドレス0x41 [6]

SFL\_INVを0に設定すると、SFLはADV7190/ADV7191/ADV7194エンコーダと互換性があります。

SFL\_INVを1(デフォルト値)に設定すると、SFLはADV717x/ADV7173x エンコーダと互換があります。

### ロック関連の制御

ロック情報は、STATUS 1レジスタのビット[1:0]に表示されます。「STATUS\_1[7:0]、アドレス0x10[7:0]」を参照してください。図9に、ロック・ステータス情報の発生方法を変更する際に使用可能な信号フローと制御の概要を示します。

図9. ロック関連の信号パス

22

### SRLS (原ロック信号の選択)、アドレス0x51 [6]

SRLSビットにより、次の2つの信号源のどちらでロック・ステータス (STATUS 1レジスタのビット[1:0])を決定するのか選択します。

- time\_win信号は、受信ビデオの水平同期パルスのライン毎の評価に基づきます。非常に速く応答します。

- free\_run信号は複数のフィールドについて受信ビデオの特性を評価し、垂直同期情報も考慮します。

SRLSを0(デフォルト値)に設定すると、free run信号が選択されます。

SRLSを1に設定すると、time\_win信号が選択されます。

### FSCLE (Fscロック・イネーブル)、アドレス0x51 [7]

FSCLEビットにより、全体のロック・ステータスが決定され、STATUS 1 レジスタのビット[1:0]に表示される際に、カラー・サブキャリア・ループのステータスを考慮するか否かを選択できます。信頼性の高いHLOCKステータス・ビットを発生させるために、YPrPbコンポーネント・モードのときは、このビットを0に設定する必要があります。

FSCLEを0に設定すると、全体ロック・ステータスが水平同期ロックのみに依存します。

FSCLEを1(デフォルト値)に設定すると、全体ロック・ステータスが水平同期ロックとFscロックに依存します。

### CIL[2:0] (カウント・イントゥ・ロック)、アドレス0x51[2:0]

CIL[2:0]は、システムがロック状態に切り替わる前のロック引込み状態の連続するライン数を決定し、これをSTATUS 0 [1:0]に報告します。ビデオ・ライン数で表します。

表19. CILの機能

| CIL[2:0]    | 説明(ビデオ・ライン数) |

|-------------|--------------|

| 000         | 1            |

| 001         | 2            |

| 010         | 5            |

| 011         | 10           |

| 100(デフォルト値) | 100          |

| 101         | 500          |

| 110         | 1000         |

| 111         | 100000       |

### COL[2:0] (カウント・アウト・オブ・ロック)、アドレス0x51 [5:3]

COL[2:0]は、システムがアンロック状態に切り替わる前のアンロック状態の連続するライン数を決定し、これをSTATUS 0 [1:0]に報告すします。 ビデオ・ライン数で表します。

表20. COLの機能

| COL[2:0]    | 説明(ビデオ・ライン数) |

|-------------|--------------|

| 000         | 1            |

| 001         | 2            |

| 010         | 5            |

| 011         | 10           |

| 100(デフォルト値) | 100          |

| 101         | 500          |

| 110         | 1000         |

| 111         | 100000       |

### カラー制御

これらのレジスタにより、ビデオ喪失時のアクティブ・データの制御など、画像表示を制御できます。カラー制御は、他の制御とは無関係に行われます。たとえば、明度制御はピクチャ・クランピングの制御から独立していますが、両方の制御とも信号のDCレベルに影響を与えます。

### CON[7:0](コントラスト調節)、アドレス0x08[7:0]

このレジスタでピクチャのコントラストを調整できます。

表21. CONの機能

| CON[7:0]     | 説明              |

|--------------|-----------------|

| 0x80(デフォルト値) | 輝度信号チャンネルのゲイン=1 |

| 0x00         | 輝度信号チャンネルのゲイン=0 |

| 0xFF         | 輝度信号チャンネルのゲイン=2 |

SD\_SAT\_Cb[7:0] (CbチャンネルのSD彩度)、アドレス0xE3 [7:0] このレジスタにより、Cbチャンネルのみのゲインを制御できます。ピクチャの彩度を調整できます。

表22. SD SAT Cbの機能

| SD_SAT_Cb[7:0] | 説明                |

|----------------|-------------------|

| 0x80(デフォルト値)   | Cbチャンネルのゲイン=0dB   |

| 0x00           | Cbチャンネルのゲイン=-42dB |

| 0xFF           | Cbチャンネルのゲイン=+6dB  |

### SD\_SAT\_Cr[7:0] (CrチャンネルのSD彩度)、アドレス0xE4[7:0]

このレジスタにより、Crチャンネルのみのゲインを制御できます。ピクチャの彩度を調整できます。

### 表23. SD SAT Crの機能

| SD_SAT_Cr[7:0] | 説明                |

|----------------|-------------------|

| 0x80(デフォルト値)   | Crチャンネルのゲイン=0dB   |

| 0x00           | Crチャンネルのゲイン=-42dB |

| 0xFF           | Crチャンネルのゲイン=+6dB  |

# SD\_OFF\_Cb[7:0] (CbチャンネルのSDオフセット)、アドレス0xE1 [7:0] このレジスタにより、Cbチャンネルのデータに限りオフセットを選択し、ピクチャの色相を調整できます。HUE [7:0]レジスタと重複する機能があります。

### 表24. SD\_OFF\_Cbの機能

| SD_OFF_Cb[7:0] | 説明                    |

|----------------|-----------------------|

| 0x80(デフォルト値)   | CbチャンネルにOVのオフセットを印加   |

| 0x00           | Cbチャンネルにー312mVのオフセットを |

|                | 印加                    |

| 0xFF           | Cbチャンネルに+312mVのオフセットを |

|                | 印加                    |

# SD\_OFF\_Cr[7:0](CrチャンネルのSDオフセット)、アドレス0xE2[7:0] このレジスタにより、Crチャンネルのデータに限りオフセットを選択し、ピクチャの色相を調整できます。HUE [7:0]レジスタと重複する機能があります。

### 表25. SD\_OFF\_Crの機能

| SD_OFF_Cr[7:0] | 説明                    |

|----------------|-----------------------|

| 0x80(デフォルト値)   | CrチャンネルにOVのオフセットを印加   |

| 0x00           | Crチャンネルにー312mVのオフセットを |

|                | 印加                    |

| 0xFF           | Crチャンネルに+312mVのオフセットを |

|                | 印加                    |

### BRI[7:0](明度調節)、アドレス0x0A [7:0]

このレジスタにより、ビデオ信号の明度を制御します。ピクチャの明度を 調節できます。

### 表26. BRIの機能

| BRI[7:0]     | 説明                     |

|--------------|------------------------|

| 0x00(デフォルト値) | 輝度信号チャンネルのオフセット=0IRE   |

| 0x7F         | 輝度信号チャンネルのオフセット=100IRE |

| 0xFF         | 輝度信号チャンネルのオフセット=       |

|              | -100IRE                |

### HUE[7:0](色相調節)、アドレス0x0B[7:0]

このレジスタは、色相調整値を格納します。ピクチャの色相を調整できます。

HUE[7:0]は $\pm 90^{\circ}$ の範囲を持ち、0x00は $0^{\circ}$ の調整に該当します。 HUE[7:0]の分解能は1ビット $=0.7^{\circ}$ です。

色相調整値は、AMカラー復調ブロックに渡されます。したがって、AM変調されたキャリア形式 (CVBSまたは、PALもしくはNTSCのY/C) で色信号情報を持つビデオ信号に対してのみ使用されます。SECAMに対しては無効で、コンポーネント・ビデオ入力 (YPrPb) に対しては動作しません。

### 表27. HUEの機能

| HUE[7:0]     | 説明          |

|--------------|-------------|

| 0x00(デフォルト値) | 色信号の位相=0°   |

| 0x7F         | 色信号の位相=-90° |

| 0x80         | 色信号の位相=+90° |

### DEF\_Y [5:0] (デフォルト値Y)、アドレス0x0C [7:2]

ADV7183Bが入力ビデオ信号のロックを失った場合、または入力信号がない場合、DEF\_Y[5:0]ビットで、出力するデフォルトの輝度信号値を指定できます。この値は次の条件下で使用します。

- DEF\_VAL\_AUTO\_ENビットがハイレベルに設定され、かつ ADV7183Bが入力ビデオ信号のロックを失った場合。これは自動モードとなっています。

- ビデオ・デコーダのロック状態とは無関係にDEF\_VAL\_ENビットがセットされたとき。これは設定時に使用すると便利な強制モードです。

DEF\_Y[5:0]値は、出力ビデオの上位6ビットを指定します。残りの下位 ビットには0が設定されます。たとえば、8ビット・モードでは、出力はY[7:0]={DEF\_Y[5:0],0,0}となります。

$DEF_Y[5:0]$ のデフォルト値は0x0D(ブルー)で、Yに対応します。

0x0Cレジスタのデフォルト値は0x36です。

### DEF\_C[7:0](デフォルト値C)、アドレス0x0D [7:0]

DEF\_C[7:0]レジスタは、DEF\_Y [5:0]値を補足します。次の場合に、このレジスタは出力するCr値とCb値の上位4ビットを指定します。

- ●DEF\_VAL\_AUTO\_ENビットがハイレベルに設定され、かつ ADV7183Bが入力ビデオ信号にロックできない場合(自動モード)

- DEF\_VAL\_ENビットがハイレベルに設定されている場合(強制出力)

ADV7183Bの色信号側に最終的に出力されるデータは、Cr[7:0]= {DEF\_C[7:4], 0, 0, 0, 0}、Cb[7:0]= {DEF\_C[3:0], 0, 0, 0, 0, 0}になります。

DEF\_C[7:0]のデフォルト値は0x7C(ブルー)で、CrとCbに対応します。

### DEF\_VAL\_EN(デフォルト値のイネーブル)、アドレス0x0C [0]

このビットは、Y、Cr、Cbに対してデフォルト値の使用を強制します。詳細は、DEF\_YとDEF\_Cの説明を参照してください。また、デコーダはこのモードで安定した27MHzクロック、HS、VSも出力します。

DEF\_VAL\_ENを0(デフォルト値)に設定すると、デコーダがフリーラン・モードのとき、ユーザ設定のY、Cr、Cb値で決定されるカラー・スクリーンを出力します。フリーラン・モードのオン/オフは、DEF\_VAL\_EN DEF\_VAL\_AUTO\_ENビットで行います。

DEF\_VAL\_ENを1に設定すると、ユーザ設定のY、Cr、Cb値で決定されるカラー・スクリーンを強制出力します。デコーダがロックされていても、ピクチャ・データが上書きされます。

### DEF\_VAL\_AUTO\_EN (デフォルト値の自動イネーブル)、 アドレス0x0C [1]

このビットにより、ADV7183Bがビデオ信号にロックできない場合に、Y、Cr、Cbのデフォルト値を自動的に使用できるようにします。

DEF\_VAL\_AUTO\_ENを0に設定すると、フリーラン・モードがディスエーブルになります。デコーダがアンロックの場合、ノイズを出力します。

DEF\_VAL\_AUTO\_ENを1(デフォルト値)に設定すると、フリーラン・モードがイネーブルになります。デコーダがロックを失った場合に、ユーザ設定のY、Cr、Cb値により設定されるカラー・スクリーンが表示されます。

### クランプ動作

入力ビデオはACカップリングでADV7183Bに入力されます。そのため、DC値を再生する必要があります。この処理はビデオのクランピングと呼ばれます。ここでは、ADV7183Bのクランピングの全体的な処理について説明し、その動作を設定するさまざまな方法を紹介します。

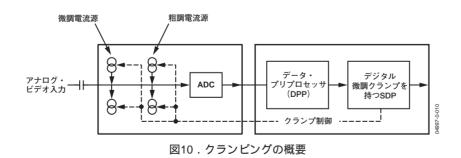

ADV7183Bでは、クランピングには、電流源とデジタル処理ブロックの組合わせを使用しています(図10)。図のアナログ処理チャンネルは、IC内部の3箇所で使用されています。CVBS信号に対しては1信号チャンネルのみ(ADCも1個のみ)必要ですが、YC(S-VHS)形式の信号に対しては独立した2チャンネルが、コンポーネント信号(YPrPb)に対しては独立した3チャンネルが必要です。

クランピング機能は、次の2つの部分に分割できます。

- ADCの前で行うクランピング (アナログ領域):電流源

- ADCの後で行うクランピング (デジタル領域): デジタル処理ブロック

入力信号がADCの入力電圧範囲1.6V以内にある場合にのみ、ADCは 入力信号をデジタル化できます。入力信号は、DCレベルが過大か過小 の場合、ADC範囲の上限または下限にクリップされてしまいます。

アナログ・クランピング回路の主な機能は、A/D変換を可能にするために、ビデオ信号が有効なADC入力ウィンドウ内に留まるようにすることです。ビデオ信号がADCの範囲内に収まる限り、アナログ領域できわめて高度な精度で入力信号をクランプする必要はありません。

デジタル化した後、デジタル微調クランプ・ブロックが残りのDCレベルの変動を補正します。入力ビデオ信号のDCレベルは、送信されるピクチャの明度を直接基準とするため、高精度に微調クランプを行うことが重要です。そうしないと、明度の変動が発生します。さらに、DCレベルの動的変動は、ほとんどの場合好ましくないノイズになるので、防止する必要があります。

クランピング方式では、全く未知のDCレベルを持つビデオ信号が新しく接続されても入力できること、および通常動作時にDCレベルを維持できること、という2つの動作が不可欠です。

未知のビデオ信号の高速な入力に対しては、大電流クランプが使用されます(このポイントでのビデオ信号の振幅は公称値を仮定しています)。 粗調電流クランプと微調電流クランプのパラメータ制御は、デコーダが自動的に行います。

標準ビデオ信号は大きなノイズを持っていることがあります。特に、地上放送で送信されてチューナで復調されるCVBS信号は、一般に非常に大きなレベルのノイズを持っています(>100mV)。このタイプのビデオ信号には、電圧クランプは適しません。代わりに、ADV7183Bでは4個の電流源セットを採用し、ビデオ信号が通過する高インピーダンス・ノードに、この4個の電流源から粗調電流(>0.5mA)と微調電流(<0.1mA)を流しています(図10参照)。

25

以下に、ADV7183Bのクランピング動作を変更する際に使用できるI<sup>2</sup>C 信号について説明します。

ADV7183Bの前バージョンでは、粗調電流源 (fast)と微調電流源をオンにするクランプ長さの設定が制御可能でした (FACL/FICL、粗調および 微調クランプ長)。しかし、ADV7183B-FTではこれらの制御がなくなり、代わりに、アダプティブ方式を採用しています。

### CCLEN(電流クランプ・イネーブル)、アドレス0x14[4]

電流クランプ・イネーブル・ビットにより、アナログ・フロントエンドの電流源 をすべてまとめてオフにすることができます。この機能は、受信アナログ・ ビデオ信号を外部でクランプする場合に便利です。

CCLENが0のとき、電流源はオフになります。

CCLENが1(デフォルト値)のとき、電流源はイネーブルになります。

### DCT[1:0](デジタル・クランプ・タイミング)、アドレス0x15[6:5]

クランプ・タイミング・レジスタは、デジタル微調クランプ回路の時定数を決定します。デジタル微調クランプはアクティブ・ラインの残留DCレベル誤差を直ちに補正することになっているので、迅速に応答できることが重要です。デジタル微調クランプの時定数は、アナログ・ブロックの時定数よりはるかに高速でなければなりません。

デジタル微調クランプの時定数は、デフォルトで接続中の入力信号に合わせて動作させながら調整します。

### 表28. DCTの機能

| DCT[1:0]   | 説明              |

|------------|-----------------|

| 00         | 低速(TC=1秒)       |

| 01         | 中速(TC=0.5秒)     |

| 10(デフォルト値) | 高速(TC=0.1秒)     |

| 11         | 入力ビデオ・パラメータに応じて |

|            | ADV7183Bが決定     |

### DCFE (デジタル・クランプ・フリーズ・イネーブル)、アドレス0x15 [4]

このレジスタ・ビットにより、デジタル・クランプ・ループをいつでもフリーズできます。これは、ユーザ独自のクランピング機能を使いたい場合に使用します。該当するレジスタ・ビットでアナログ・クランピング用電流源をディスエーブルにし、デジタル・クランプ・ループが安定するまで待った後、DCFEビットを使ってフリーズさせます。

DCFEが0(デフォルト値)のとき、デジタル・クランプが動作します。

DCFEが1のとき、デジタル・クランプ・ループがフリーズします。

### 輝度信号フィルタ

デジタル微調クランプ・ブロックから出力されるデータは、次の3セットのフィルタを使って処理されます。このポイントでのデータ・フォーマットは、CVBS入力の場合はCVBS、Y/CおよびYPrPb入力フォーマットの場合のみ輝度信号です。

- ●輝度信号アンチエイリアス(折返し誤差防止)フィルタ(YAA): ADV7183Bのビデオ受信レートは27MHzです。4倍オーバーサンプルのビデオの場合、ADCサンプルは54MHzで、最初のデシメーションはDPPフィルタ内で実行されます。このため、SDPコアに入力されるデータレートは常に27MHzになります。ITU-R BT.601はサンプリング周波数13.5MHzを勧告しています。輝度信号アンチエイリアス・フィルタは、輝度信号を通過させると同時に、帯域外成分を減衰させる高品質なリニア位相のローパス・フィルタを使用して、オーバーサンプルしたビデオをデシメーションします。輝度信号アンチエイリアス・フィルタ(YAA)は固定の応答を持っています。

- 輝度信号シェイピング・フィルタ(YSH):このシェイピング・フィルタ・ブロックはプログラマブルなローパス・フィルタで、多様な応答を持っています。このフィルタを使用し、輝度ビデオ信号の帯域幅を選択的に減少させることができます(たとえば、スケーリングの前に必要)。高周波数ノイズを含むビデオ信号源に対しては、輝度信号の帯域幅を低減すると画質が改善されることがあります。ビデオ信号をローパス・フィルタ処理すると、後段のビデオ圧縮段での効果が大きくなります。

ADV7183Bでは、シェイピング・フィルタの応答として、高品質CVBS、コンポーネント、S-VHS型の信号源に適する応答と、非標準CVBS信号に適する応答の2種類を選択できます。

また、YSHフィルタ応答にはPAL用とNTSC用のノッチも含まれています。ただし、YC分離にはコムフィルタの使用を推奨します。

● デジタル・リサンプリング・フィルタ。このブロックでビデオ信号のダイナミック・リサンプリングを行い、ビデオ・ラインのタイム・ベースなどのパラメータを変更できます。基本的には、リサンプラはローパス・フィルタのセットで構成されます。実際の応答はシステムが選択するため、ユーザの介入は不要です。

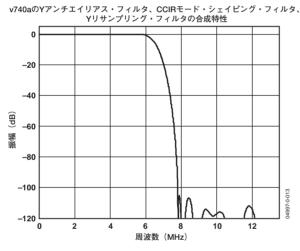

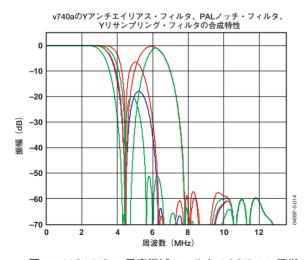

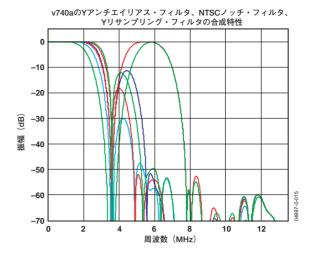

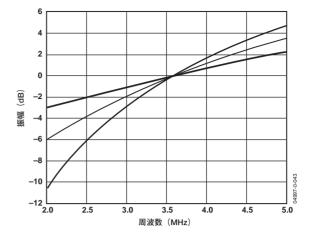

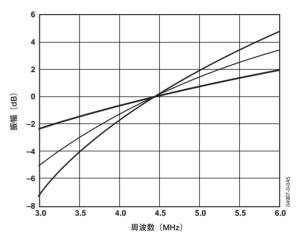

図12~15に、すべてのフィルタを通過させた全体応答を示します。特に指定のない限り、フィルタは代表的な広帯域モードに設定されています。

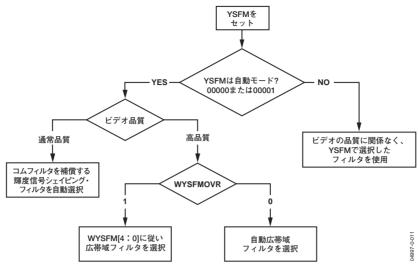

### Yシェイピング・フィルタ

CVBSフォーマットの入力信号に対して、輝度信号シェイピング・フィルタはコンポジット信号から色信号成分を除去するのに重要な役割を持ちます。YC分離ではクロストークの削減と同時に、可能な限り帯域幅(輝度信号成分は特に)を広く維持することが必要です。高品質なYC分離は、ADV7183Bの内蔵コムフィルタを使用することで実現できます。ただし、コムフィルタは、輝度信号成分(ビデオ・ライン・レートの倍数)とカラー・サブキャリア(Fsc)との間の周波数関係に依存しています。高品質のCVBS信号ではこの関係はよく知られており、コムフィルタ・アルゴリズムを使用して輝度信号と色信号を高い精度で分離できます。

非標準ビデオ信号の場合は、周波数関係が乱れるため、コムフィルタは シェイピング・フィルタ・ブロックの助けを借りないと、すべてのクロストーク・ノイズを最適な方法で除去できなくなります。

自動モードが用意されています。ここでは、ADV7183Bが入力ビデオ信号の品質を評価し、信号品質とビデオ標準に基づいてフィルタ応答を選択します。YFSM、WYSFMOVR、WYSFMを使用し、自動判定の一部または全部をマニュアルで上書きできます。

輝度信号シェイピング・フィルタには、次の3個のコントロール・レジスタがあります。

- YSFM[4:0]レジスタは、シェイピング・フィルタ・モード(全ビデオ信号 に適用)のマニュアル選択または自動選択のイネーブル(ビデオ品質 とビデオ標準に依存)が可能です。

- ◆WYSFMOVRレジスタは、WYSFMの判定をマニュアルで上書きできます。

- WYSFM[4:0]レジスタは、高品質のCVBS、コンポーネント(YPrPb)、 S-VHS(YC)の各入力信号に対して別のシェイピング・フィルタ・モードを選択できます。

自動モードでは、システムはYPrPb信号源とYC信号源(これらはコムフィルタ処理が不要)の輝度信号成分に対してはもちろん、高品質CVBS信号源(コムフィルタ処理済み)に対しても、最大限の帯域幅を維持します。通常品質に対しては、システムはノイズを削減するためにコムフィルタ動作を補完する当社独自のシェイピング・フィルタ応答から適切なフィルタ選択します。

コントロール・ロジックのフローチャートを図11に示します。

### YSFM[4:0](Yシェイピング・フィルタ・モード)、アドレス0x17[4:0]

Yシェイピング・フィルタ・モード・ビットにより、広範なローパス・フィルタと ノッチ・フィルタから選択できます。自動モードに切り替えると、他のレジスタ選択(たとえば、検出されたビデオ標準)や入力ビデオ自体から取り出した属性(たとえば、品質、タイム・ベースの安定性)に基づいてフィルタが選択されます。自動選択は、入力されたビデオに対して常に最大限可能な帯域幅を与えます。

YSFM設定でフィルタが指定されている場合(すなわち、YSFM が 00000または00001以外の値に設定されている場合)、選択されたフィルタは品質とは無関係に全ビデオに適用されます。

自動選択モードでは、通常品質ビデオ信号にはノッチ・フィルタのみ使用されます。その他のすべてのビデオ信号には、広帯域フィルタが使用されます。

# WYSFMOVR (広帯域Yシェイピング・フィルタ・モード上書き)、アドレス0x18 [7]

WYSFMOVRビットをセットすると、高品質ビデオ信号に対してWYSFM[4:0]を設定できます。詳細は、「Yシェイピング・フィルタ」の輝度信号シェイピング・フィルタの一般的な説明と図11のフローチャートを参照してください。

WYSFMOVRが0のとき、良品質ビデオ信号に対するシェイピング・フィルタを自動的に選択します。

WYSFMOVR を1(デフォルト値)に設定すると、WYSFM[4:0]でマニュアル上書きがイネーブルになります。

図11. YSFMとWYSFMの制御フローチャート

表29. YSFMの機能

| YSFM[4:0]      | 説明                       |

|----------------|--------------------------|

| 0'0000         | 広いノッチ応答(PAL/NTSC/SECAM)を |

|                | 含む自動選択                   |

| 0'0001(デフォルト値) | 狭いノッチ応答(PAL/NTSC/SECAM)を |

|                | 含む自動選択                   |

| 0'0010         | SVHS 1                   |

| 0'0011         | SVHS 2                   |

| 0'0100         | SVHS 3                   |

| 0'0101         | SVHS 4                   |

| 0'0110         | SVHS 5                   |

| 0'0111         | SVHS 6                   |

| 0'1000         | SVHS 7                   |

| 0'1001         | SVHS 8                   |

| 0'1010         | SVHS 9                   |

| 0'1011         | SVHS 10                  |

| 0'1100         | SVHS 11                  |

| 0'1101         | SVHS 12                  |

| 0'1110         | SVHS 13                  |

| 0'1111         | SVHS 14                  |

| 1'0000         | SVHS 15                  |

| 1'0001         | SVHS 16                  |

| 1'0010         | SVHS 17                  |

| 1'0011         | SVHS 18 (CCIR 601)       |

| 1'0100         | PAL NN 1                 |

| 1'0101         | PAL NN 2                 |

| 1'0110         | PAL NN 3                 |

| 1'0111         | PAL WN 1                 |

| 1'1000         | PAL WN 2                 |

| 1'1001         | NTSC NN 1                |

| 1'1010         | NTSC NN 2                |

| 1'1011         | NTSC NN 3                |

| 1'1100         | NTSC WN 1                |

| 1'1101         | NTSC WN 2                |

| 1'1110         | NTSC WN 3                |

| 1'1111         | 予備                       |

WYSFM[4:0](広帯域Yシェイピング・フィルタ・モード)、 アドレス0x18 [4:0]

WYSFM[4:0]ビットにより、高品質ビデオ信号(たとえば、安定したタイム・ベースを持つCVBS、YPrPb輝度信号成分、YC輝度信号成分)に対してシェイピング・フィルタをマニュアルで選択できます。WYSFMOVRビットを1に設定している場合にのみ、WYSFMビットがアクティブになります。「Yシェイピング・フィルタ」のシェイピング・フィルタ設定の一般的な説明を参照してください。

表30. WYSFMの機能

| WYSFM[4:0]     | 説明                 |

|----------------|--------------------|

| 0'0000         | 使用不可               |

| 0'0001         | 使用不可               |

| 0'0010         | SVHS 1             |

| 0'0011         | SVHS 2             |

| 0'0100         | SVHS 3             |

| 0'0101         | SVHS 4             |

| 0'0110         | SVHS 5             |

| 0'0111         | SVHS 6             |

| 0'1000         | SVHS 7             |

| 0'1001         | SVHS 8             |

| 0'1010         | SVHS 9             |

| 0'1011         | SVHS 10            |

| 0'1100         | SVHS 11            |

| 0'1101         | SVHS 12            |

| 0'1110         | SVHS 13            |

| 0'1111         | SVHS 14            |

| 1'0000         | SVHS 15            |

| 1'0001         | SVHS 16            |

| 1'0010         | SVHS 17            |

| 1'0011(デフォルト値) | SVHS 18 (CCIR 601) |

| 1'0100~1'1111  | 使用不可               |

# v740aのYアンチエイリアス・フィルタ、S-VHSローパス・フィルタ、 Yリサンプリング・フィルタの合成特性 0 -10 -20 -20 -50 -60 -70 0 2 4 6 8 10 12

図12. Y S-VHSの合成応答

図12のフィルタ・プロットは、S-VHS 1(最小幅)~S-VHS 18(最大幅)のシェイピング・フィルタの設定を表わしています。図14に、PALノッチ・フィルタの応答を示します。NTSC互換ノッチ・フィルタの応答は図15に示します。

図13. Y S-VHS 18最広帯域フィルタ (CCIR 601準拠)

図14. Y S-VHS 18最広帯域フィルタ ( CCIR 601準拠 )

図15. Y S-VHS 18最広帯域フィルタ(601)

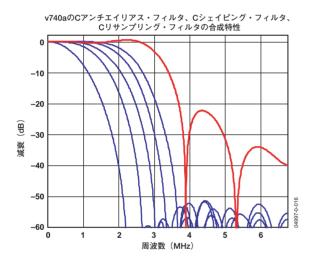

### 色信号フィルタ

デジタル微調クランプ・ブロックから出力されるデータは、次の3セットのフィルタで処理されます。このポイントでのデータ・フォーマットはCVBS入力の場合はCVBSで、Y/C、またはYPrPb入力フォーマットのU/Vインターリーブの場合のみ色信号です。

- ●色信号アンチエイリアス・フィルタ(CAA): ADV7183BはCVBSを2倍で、色信号/PrPbを4倍でオーバーサンプルします。デシメーション・フィルタ(CAA)を使用し、アクティブ・ビデオ帯域を維持し、帯域外成分を除去します。CAAフィルタは固定応答です。

- ●色信号シェイピング・フィルタ(CSH):シェイピング・フィルタ・ブロック (CSH)は、多様なローパス応答を実行するように設定できます。スケーリングまたは圧縮用に色信号の帯域幅を選択的に削減する際に使用できます。

- デジタル・リサンプリング・フィルタ:このブロックを使用しビデオ信号のダイナミック・リサンプリングを行い、ビデオ・ラインのタイム・ベースなどのパラメータを変更できます。リサンプラは基本的にローパス・フィルタで構成されます。実際の応答はシステムが選択するため、ユーザの介入は不要です。

図16のプロットは、すべてのフィルタを通過させた全体応答を示します。

### CSFM[2:0](Cシェイピング・フィルタ・モード)、アドレス0x17[7]

Cシェイピング・フィルタ・モード・ビットを使用すると、色信号用に広範なローパス・フィルタから選択することができます。自動モードに切り替えると、ビデオ標準/フォーマットとユーザの選択に基づいて最も広いフィルタが選択されます(表31の000と001の設定を参照)。

表31. CSFMの機能

| CSFM[2:0]   | 説明              |

|-------------|-----------------|

| 000(デフォルト値) | 1.5MHz帯域幅を自動選択  |

| 001         | 2.17MHz帯域幅を自動選択 |

| 010         | SH1             |

| 011         | SH2             |

| 100         | SH3             |

| 101         | SH4             |

| 110         | SH5             |

| 111         | 広帯域モード          |

図16.色信号シェイピング・フィルタの応答

図16に、SH1(最小幅)~SH5(最大幅)の応答と広帯域モードの応答 (赤)を示します。

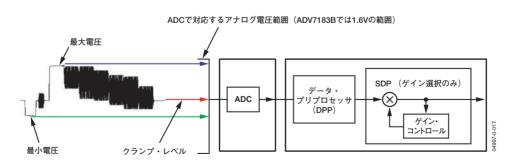

### ゲイン動作

ADV7183B内のゲイン・コントロールは、純粋にデジタル的に実行されます。入力ADCは10ビットで、1.6Vのアナログ電圧範囲に対応します。ゲイン補正はデジタル化の後にデジタル乗算の形で実行されます。

ADCの前でPGA (プログラマブル・ゲイン・アンプ)を使う一般的な方法に対して、このアーキテクチャにはいくつかの利点があります。とりわけ、ゲインが電源、温度、プロセスの変動に全く依存しなくなることです。

図17に示すように、ADV7183Bはビデオ信号がADCの入力範囲内にある限りデコードできます。ビデオ信号は入力信号の振幅とDCレベルの2つ成分から構成されています。DCレベルはクランピング回路で設定されます(「クランプ動作」を参照)。

アナログ・ビデオ信号の振幅が大き過ぎると、クリッピングが発生し、ノイズとして見えるようになります。ADCのアナログ入力範囲はクランプ・レベルとともに、対応するビデオ信号の最大振幅を決定します。

対応する入力ビデオ信号の最小振幅は、ADV7183Bの水平タイミングと垂直タイミングを再現する能力と、カラー・バースト(存在する場合)にロックする能力によって決定されます。

輝度信号データと色信号データそれぞれに1個ずつ、ゲイン・コントロール・ユニットがあります。どちらも互いに独立して動作します。ただし、色信号ユニットは輝度信号パスからゲイン値を取ることもできます。

複数のAGCモードを表32に示します。

自動ゲイン・コントロール・ループは、フリーズさせることができます。この機能は、ループに更新をフリーズさせます。ループのフリーズが解除されるか、またはゲイン動作モードが変更されるまで、フリーズ時点でAGCが決定したゲインがアクティブのままになります。

すべてのモードでアクティブ中のゲインをリードバックできます。「輝度信号ゲイン」および「色信号ゲイン」の項で扱った2つのマニュアル・ゲイン・レジスタ、すなわちLG[11:0](輝度信号ゲイン)レジスタおよび CG[11:0](色信号ゲイン)レジスタの説明を参照してください。

図17. ゲイン・コントロールの概要

表32. AGCモード

| 入力ビデオ・タイプ | 輝度信号ゲイン       | 色信号ゲイン                    |

|-----------|---------------|---------------------------|

| 任意        | マニュアル・ゲイン輝度信号 | マニュアル・ゲイン色信号              |

| CVBS      | 水平同期の深さに依存    | カラー・バーストの振幅に依存。輝度信号パスから取得 |

|           | ピーク・ホワイト      | カラー・バーストの振幅に依存。輝度信号パスから取得 |

| Y/C       | 水平同期の深さに依存    | カラー・バーストの振幅に依存。輝度信号パスから取得 |

|           | ピーク・ホワイト      | カラー・バーストの振幅に依存。輝度信号パスから取得 |

| YPrPb     | 水平同期の深さに依存    | 輝度信号パスから取得                |

### 輝度信号ゲイン

LAGC[2:0](輝度信号自動ゲイン・コントロール)、アドレス0x2C[6:4] 輝度信号自動ゲイン・コントロール・モード・ビットは、輝度信号パスでのゲイン・コントロールの動作モードを選択します。

ピーク・ホワイト・ゲイン・コントロールをカスタマイズする内部パラメータがあります。詳細は、お問い合わせください。

表33. LAGCの機能

| LAGC[2:0]   | 説明                       |  |

|-------------|--------------------------|--|

| 000         | マニュアル固定ゲイン(LMG[11:0]を使用) |  |

| 001         | AGC(ブランク・レベルから同期ティップ)。   |  |

|             | ピーク・ホワイトによる上書きなし         |  |

| 010(デフォルト値) | AGC(ブランク・レベルから同期ティップ)。   |  |

|             | ピーク・ホワイトにより自動上書き         |  |

| 011         | 予備                       |  |

| 100         | 予備                       |  |

| 101         | 予備                       |  |

| 110         | 予備                       |  |

| 111         | ゲイン・フリーズ                 |  |

### LAGT[1:0](輝度信号自動ゲイン・タイミング)、アドレス0x2F [7:6]

輝度信号自動ゲイン・タイミング・レジスタを使用し、輝度信号自動ゲイン・コントロールのトラッキング速度を変更できます。LAGC[2:0]レジスタに001、010、011、または100が設定されている場合にのみ(自動ゲイン・コントロール・モード)、このレジスタが有効であることに注意してください。

ピーク・ホワイトAGCがイネーブルでアクティブの場合(STATUS\_1[7:0]、アドレス0x10 [7:0]を参照)、実際のゲイン更新速度はピーク・ホワイトAGCループによって決定されるため、このLAGT設定は無効になります。デバイスがピーク・ホワイトAGCから抜け出ると、直ちにLAGTゲインが有効になります。

ピーク・ホワイト・アルゴリズムの更新速度は、内部パラメータを使ってカスタマイズできます。詳細は、お問い合わせください。

表34. LAGTの機能

| LAGT[1:0]  | 説明          |

|------------|-------------|

| 00         | 低速(TC=2秒)   |

| 01         | 中速(TC=1秒)   |

| 10         | 高速(TC=0.2秒) |

| 11(デフォルト値) | アダプティブ      |

LG[11:0](輝度信号ゲイン)、アドレス0x2F[3:0];アドレス0x30[7:0] LMG[11:0](輝度信号マニュアル・ゲイン)、アドレス0x2F[3:0]; アドレス0x30[7:0]

輝度信号ゲイン[11:0]レジスタには次の2つの機能があります。書込みを行うと、必要なマニュアル輝度信号ゲインを設定できます。LAGC[2:0]モードがマニュアル固定ゲインに切り替えられると、このゲインがアクティブになります。式1は必要なゲインの計算方法を示します。

リードバックを行うと、このレジスタは現在のゲイン値を返します。 LAGC[2:0]ビットの設定に応じて、次のどちらかの値になります。

- 輝度信号マニュアル・ゲイン値(LAGC[2:0]を輝度信号マニュアル・ゲイン・モードに設定)

- 輝度信号自動ゲイン値(LAGC[2:0]をいずれかの自動モードに設定)

表35. LG/LMGの機能

| LG[11:0]/<br>LMG[11:0] | 読出し/<br>書込み | 説明               |

|------------------------|-------------|------------------|

| LMG[11:0]=X            | 書込み         | 輝度信号パスに対するマニュアル・ |

|                        |             | ゲイン              |

| LG[11:0]               | 読出し         | 実際に使用されているゲイン    |

輝度信号ゲイン =

$$\frac{(0 < LG \le 4095)}{2048} = 0...2$$

(1)

たとえば、ADV7183Bを希望するゲイン=0.89でマニュアル固定ゲイン・ モードに設定します。

- 1. 式1を用いてゲインを変換します。 0.89×2048=1822.72

- 2. 整数値に丸めます。 1822.72=1822

- 3. 16進に変換します。 1822d=0x71E

- 4. 2個のレジスタに分けて、書き込みます。 輝度ゲイン・コントロール1 [3:0]=0x7 輝度ゲイン・コントロール2 [7:0]=0x1E

- 5. マニュアル固定ゲイン・モードをイネーブルにします。 LAGC[2:0]を000に設定

### BETACAM (Betacamレベルのイネーブル)、アドレス0x01 [5]

YPrPbデータがADV7183Bを経由して接続される場合、表42に示すように、自動ゲイン・コントロール・モードは複数のビデオ入力レベルを対象とすることができます。入力モードがYPrPb(コンポーネント)の場合のみ、BETACAMビットが有効であることに注意してください。BETACAMビットはAGC動作の目標値を設定します。

以下を見直してください。

- コンポーネント・ビデオ(YPrPb)をADV7183B経由で接続する方法については、INSEL[3:0](入力選択)、アドレス0x00[3:0]。

- ◆ さまざまな標準(たとえば、ペデスタルの有無)の選択については、ビデオ標準選択。

自動ゲイン・コントロール(AGC)アルゴリズムは、BETACAMビットの設定に基づいてレベルを調節します(表36)。

### 表36. BETACAMの機能

| BETACAM   | 説明                           |

|-----------|------------------------------|

| 0(デフォルト値) | 入力フォーマットとしてYPrPbの選択を想定       |

|           | ペデスタルありPALを選択すると、MIIを選択      |

|           | ペデスタルなしPALを選択すると、SMPTEを選択    |

|           | ペデスタルありNTSCを選択すると、MIIを選択     |

|           | ペデスタルなしNTSCを選択すると、SMPTEを選択   |

| 1         | 入力フォーマットとしてYPrPbの選択を想定       |

|           | ペデスタルありPALを選択すると、BETACAMを選択  |

|           | ペデスタルなしPALを選択すると、BETACAM派生を  |

|           | 選択                           |

|           | ペデスタルありNTSCを選択すると、BETACAMを選択 |

|           | ペデスタルなしNTSCを選択すると、BETACAM派生  |

|           | を選択                          |

### PW\_UPD(ピーク・ホワイト更新)、アドレス0x2B[0]

ピーク・ホワイトと平均ビデオ・アルゴリズムは、アクティブ・ビデオの計測値に基づいてゲインを決定します。PW\_UPDビットはゲイン変化レートを決定します。ピーク・ホワイト・モードまたは平均ビデオ・モードを最初にイネーブルにするには、LAGC[2:0]を該当するモードに設定する必要があります。詳細は、LAGC[2:0](輝度信号自動ゲイン・コントロール)、アドレス0x30 [7:0]を参照してください。

PW\_UPDを0に設定すると、ビデオ・ライン毎にゲインを更新します。

PW\_UPDを1(デフォルト値)に設定すると、フィールド毎にゲインを更新します。

### 色信号ゲイン

CAGC[1:0](**色信号自動ゲイン・コントロール**)、アドレス0x2C[1:0] カラー自動ゲイン・コントロール・モードのこの2ビットは、色信号パスでの 自動ゲイン・コントロールの基本動作モードを選択します。

### 表37. CAGCの機能

| CAGC[1:0]  | 説明                       |

|------------|--------------------------|

| 00         | マニュアル固定ゲイン(CMG[11:0]を使用) |

| 01         | 色信号に対して輝度信号ゲインを使用        |

| 10(デフォルト値) | 自動ゲイン(カラー・バーストに基づく)      |

| 11         | 色信号ゲインをフリーズ              |

### CAGT[1:0](色信号自動ゲイン・タイミング)、アドレス0x2D[7:6]

色信号自動ゲイン・タイミング・レジスタを使用し、色信号自動ゲイン・コントロールのトラッキング速度を変更することができます。CAGC[1:0]レジスタが10に設定されている場合にのみ(自動ゲイン)、このレジスタは有効となります。

### 表38. CAGTの機能

| CAGT[1:0]  | 説明          |

|------------|-------------|

| 00         | 低速(TC=2秒)   |

| 01         | 中速(TC=1秒)   |

| 10         | 高速(TC=0.2秒) |

| 11(デフォルト値) | アダプティブ      |

### 表39. Betacamレベル

| 名前       | Betacam (mV)         | Betacam派生(mV)    | SMPTE(mV)        | MII(mV)              |

|----------|----------------------|------------------|------------------|----------------------|

| Yの範囲     | 0~714 (7.5%ペデスタルを含む) | 0~714            | 0~700            | 0~700 (7.5%ペデスタルを含む) |

| PbとPrの範囲 | -467~+467            | $-505 \sim +505$ | $-350 \sim +350$ | $-324 \sim +324$     |

| 同期の深さ    | 286                  | 286              | 300              | 300                  |

### CG[11:0](色信号ゲイン)、アドレス0x2D[3:0];アドレス0x2E[7:0] CMG[11:0](色信号マニュアル・ゲイン)、アドレス0x2D[3:0]; アドレス0x2E [7:0]

色信号ゲイン[11:0]レジスタには次の2つの機能があります。書込みを 行うと、必要なマニュアル色信号ゲインを設定できます。CAGC[1:0]モ ードがマニュアル固定ゲインに切り替えられると、このゲインがアクティ ブになります。希望するゲインの計算方法については、式2を参照してく ださい。リードバックを行うと、このレジスタは現在のゲイン値を返します。 CAGC[1:0]ビットの設定に応じて、次のいずれかの値になります。

- 色信号マニュアル・ゲイン値(CAGC[1:0]を色信号マニュアル・ゲイ ン・モードに設定)

- 色信号自動ゲイン値(CAGC[1:0]をいずれかの自動モードに設定)

### 表40. CG/CMGの機能

| CG[11:0]/<br>CMG[11:0] | 読出し/<br>書込み | 説明              |

|------------------------|-------------|-----------------|

| CMG[11:0]              | 書込み         | 色信号パスに対するマニュアル・ |

|                        |             | ゲイン             |

| CG[11:0]               | 読出し         | 現在のゲイン          |

色信号ゲイン =

$$\frac{(0 < CG \le 4095)}{1024} = 0...4$$

(2)

たとえば、自動ゲイン・ループをフリーズさせ、CG[11:0]レジスタを読み 出すと、0x47Aの値が得られます。

- 1. リードバック値を10進に変換します。 0x47A = 1146d

- 2. 式2を用いてリードバック値を変換します。 1146/1024 = 1.12

### CKE (カラーキル・イネーブル)、アドレス0x2B [6]

カラーキル・イネーブル・ビットを使用し、オプションのカラーキル機能を オンまたはオフに切り替えることができます。

OAMベースのビデオ標準 (PALとNTSC)とFMベースのシステム (SECAM)の場合は、CKILLTHR[2:0]ビットによりカラーキル判定のス レッショールドを選択できます。

カラーキルがイネーブルになり、かつ連続する128のビデオ・ラインの間、 入力ビデオ信号のカラー・キャリアがスレッショールドを下回る場合、カ ラー処理はオフに切り替えられます(白黒出力になります)。カラー処理 をオンに戻すには、スレッショールドを超えるカラー・バーストを持つライ ンがさらに128連続する必要があります。

カラーキル・オプションは、変調された色信号を持つ入力信号に対して のみ有効です。コンポーネント入力 (YPrPb) に対しては、カラーキル機能 はありません。

CKEを0に設定すると、カラーキルがディスエーブルになります。

CKEを1(デフォルト値)に設定すると、カラーキルがイネーブルになり ます。

CKILLTHR[2:0](カラーキル・スレッショールド)、アドレス0x3D[6:4] CKILLTHR[2:0]ビットを使用し、カラーキル機能のスレッショールドを選 択できます。このスレッショールドは、OAMベースの(NTSCとPAL)ビデ オ標準またはFM変調された(SECAM)ビデオ標準に対してのみ適用さ れます。

カラーキル機能をイネーブルにするには、必ずCKEビットをセットします。 000、001、010、011に設定すると、ADV7183B内の色信号復調は通常 品質入力ビデオ信号に対して十分に動作しません。

表41. CKILLTHRの機能

|               | 説明         |            |

|---------------|------------|------------|

| CKILLTHR[2:0] | SECAM      | NTSC, PAL  |

| 000           | カラーキルなし    | 0.5%未満でキル  |

| 001           | 5%未満でキル    | 1.5%未満でキル  |

| 010           | 7%未満でキル    | 2.5%未満でキル  |

| 011           | 8%未満でキル    | 4.0%未満でキル  |

| 100(デフォルト値)   | 9.5%未満でキル  | 8.5%未満でキル  |

| 101           | 15%未満でキル   | 16.0%未満でキル |

| 110           | 32%未満でキル   | 32.0%未満でキル |

| 111           | アナログ・デバイセズ | 用の予備。選択不可。 |

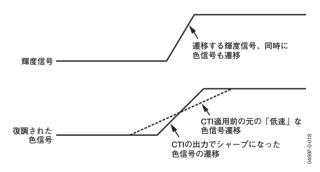

### カラー・トランジェント・インプルーブメント(CTI)

色信号に割り当てられる信号帯域幅は一般に、輝度信号の帯域幅より はるかに狭くなっています。人間の視覚は輝度に比べ色への反応が鈍 いため、以前は、このように色信号を与えられた帯域内で用いることは 有効な方法でした。

しかし、帯域幅が不均等であると、シャープなカラー遷移にノイズが現 れるようになります。2本のカラー・バーの境界で、輝度信号と色信号の 両成分が同時に変化します(図18)。輝度信号成分は帯域幅が広いた め、その遷移は一般に色信号成分の遷移よりシャープです。最悪の場 合、カラー・エッジは数ピクセルにわたってぼやけてしまいます。

図18. CTI輝度信号 / 色信号の遷移

33

カラー・トランジェント・インプルーブメント・ブロックは入力ビデオ・データを調べ、色信号の遷移を検出します。さらに、失われたカラー帯域幅を回復するために、色信号エッジを「シャープにする」ように設定できます。ただし、CTIブロックは、ノイズも一緒に強調しないように一定のスレッショールドを超えるエッジに対してのみ動作します。また、エッジのリンギングや不要な彩度歪みまたは色相歪みが発生しないように注意することも必要です。

カラー・トランジェント・インプルーブメントは、おもに色信号の帯域幅制限の影響が大きい信号に対して必要です。このタイプの信号に対しては、 CTI ENを使ってCTIブロックをイネーブルすることを強く推奨します。

# CTI\_EN (カラー・トランジェント・インプルーブメント・イネーブル)、アドレス 0x4D [0]

CTI\_ENビットは、CTI機能をイネーブルにします。0に設定すると、CTIブロックが非アクティブになり、カラー・トランジェントはそのまま何の影響も受けません。

CTI ENを0に設定すると、CTIブロックがディスエーブルになります。

CTI\_ENを1(デフォルト値)に設定すると、CTIブロックがイネーブルになります。

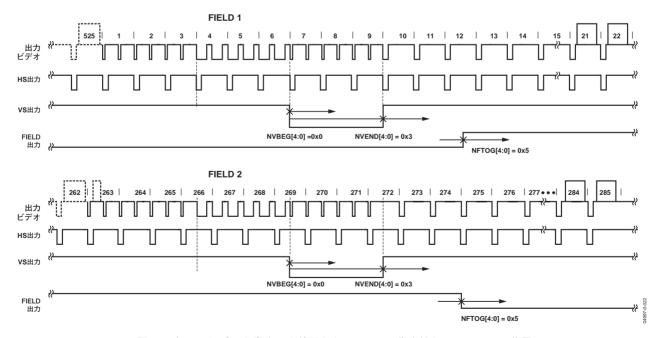

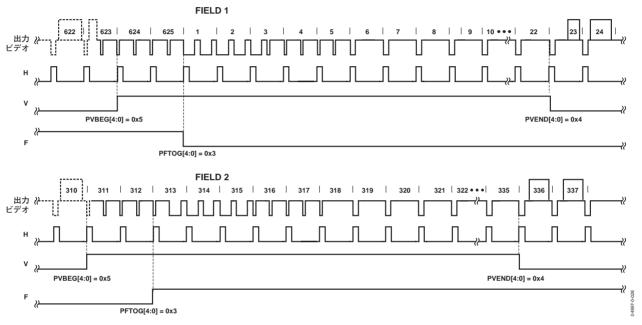

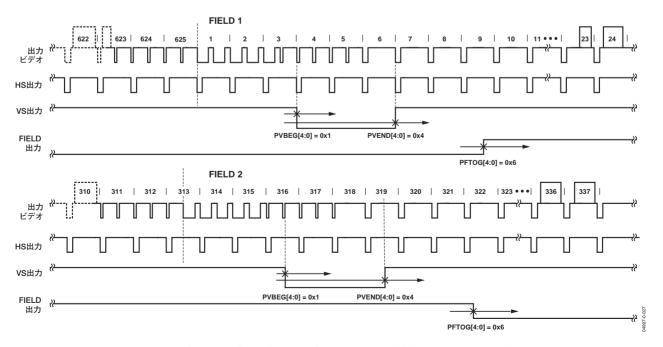

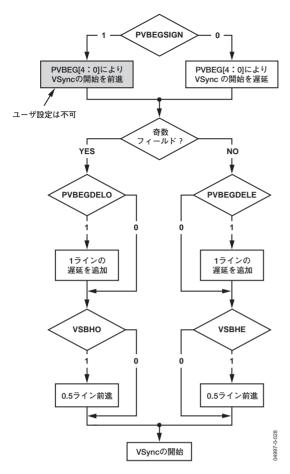

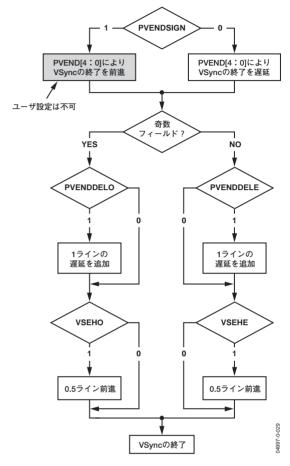

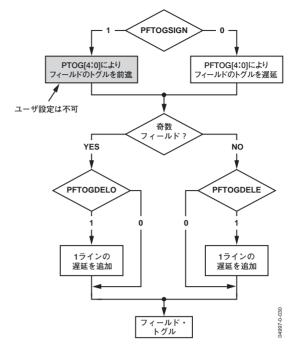

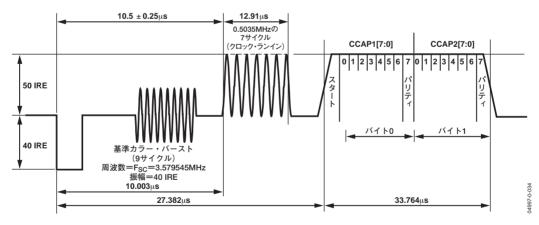

# CTI\_AB\_EN (カラー・トランジェント・インプルーブメント・アルファ・ブレンド・イネーブル)、アドレス0x4D [1]