# Blackfin 組込み型プロセッサ

# ADSP-BF534/ADSP-BF536/ADSP-BF537

#### 特長

最大600 MHzの高性能Blackfinプロセッサ

16ビットMACを2個、40ビットALUを2個、8ビット・ビデオ ALUを4個、40ビット・シフタを内蔵

RISCライクなレジスタおよび命令モデルを採用しているため、プログラミングが容易でかつコンパイラ・フレンドリなサポートが可能

高度なデバッグ機能、トレース機能、パフォーマンスモニタ ー機能をサポート

広い動作温度範囲(動作条件参照)

プログラマブルな電圧レギュレータを内蔵

182ボールおよび208ボールのCSP BGAパッケージを採用

#### メモリ

最大132Kバイトの内蔵メモリ

命令SRAM/キャッシュと命令SRAM

データSRAM/キャッシュと専用データSRAM

スクラッチパッドSRAM (メモリ構成については表1参照)

外部メモリ・コントローラにより、外付け部品なしでSDRAM および非同期8ビットと16ビット・メモリのサポートが可 能

外部フラッシュ、SPIメモリとTWIメモリ、またはSPI、TWI、 UARTの各ホスト・デバイスからの柔軟なブート・オプション メモリ・マネジメント・ユニット(MMU)によるメモリ保護

#### ペリフェラル

IEEE 802.3準拠の10/100イーサネットMAC (ADSP-BF536と ADSP-BF537の場合)

コントローラ・エリア・ネットワーク(CAN) 2.0Bインターフェース

ITU-R 656ビデオ・データ・フォーマットをサポートするパラレル・ペリフェラル・インターフェース(PPI)

2系統の2チャンネル全二重同期シリアル・ポート(SPORT) により、8チャンネルのステレオl<sup>2</sup>Sをサポート

12個のペリフェラルDMA、2個はイーサネットMACのマスタ

外部要求ラインを使用する2個のメモリ間DMA 32本の割込み入力によるイベント・ハンドラシリアル・ペリフェラル・インターフェース(SPI)に互換IrDAをサポートする2系統のUART 2線式インターフェース(TWI)コントローラPWMをサポートする32ビット・タイマ/カウンタ×8リアルタイム・クロック(RTC)とウォッチドッグ・タイマ 32ビット・コア・タイマ

48本の汎用I/O (GPIO)、8本は高電流ドライバを内蔵 0.5~64倍の周波数を生成できるオンチップPLL デバッグ/JTAGインターフェース

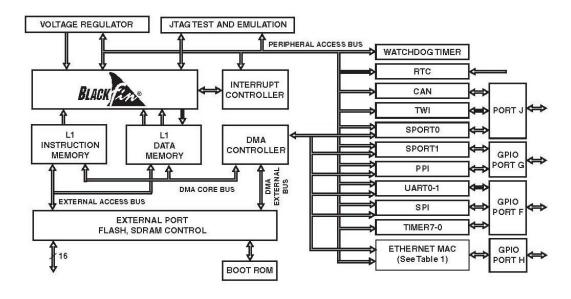

図1 機能ブロック図

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。 ※日本語データシートは REVISION が古い場合があります。最新の内容については、英語版をご参照ください。 ©2009 Analog Devices, Inc. All rights reserved.

Rev. G

本 社/〒105-6891

東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 電話 03(5402)8200

大阪営業所/〒532-0003

大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 電話 06 (6350) 6868

# 目次

| 特長                            | 1  |

|-------------------------------|----|

| メモリ                           | 1  |

| ペリフェラル                        | 1  |

| 目次                            | 2  |

| 改訂履歴                          | 2  |

| 概要                            | 3  |

| ポータブルな低消費電力アーキテクチャ            | 3  |

| システム・インテグレーション                |    |

| Blackfinプロセッサ・ペリフェラル          |    |

| Blackfinプロセッサ・コア              | 4  |

| メモリ・アーキテクチャ                   | 5  |

| DMAコントローラ                     | 8  |

| リアルタイム・クロック                   | 9  |

| ウォッチドッグ・タイマ                   | 9  |

| タイマ                           | 9  |

| シリアル・ポート(SPORT)               | 10 |

| シリアル・ペリフェラル・インターフェース(SPI)ポート. | 10 |

| UARTポート                       | 10 |

| コントローラ・エリア・ネットワーク(CAN)        | 11 |

| TWIコントローラ・インターフェース            | 11 |

| 10/100 イーサネットMAC              | 11 |

| ポート                           | 12 |

| パラレル・ペリフェラル・インターフェース(PPI)     | 12 |

| ダイナミック・パワー・マネジメント             |    |

| ディープ・スリープ動作モード―最高の省電力         |    |

|                               |    |

| 電圧レギュレーション             | 14 |

|------------------------|----|

| クロック信号                 | 15 |

| ブーティング・モード             | 16 |

| 命令セットの説明               | 17 |

| 開発ツール                  |    |

| エミュレータ互換プロセッサ・ボードのデザイン | 18 |

| 関連ドキュメント               | 18 |

| ピン説明                   | 19 |

| 仕様                     | 23 |

| 動作条件                   | 23 |

| 電気的特性                  | 25 |

| 絶対最大定格                 | 29 |

| ESD感受性                 | 29 |

| パッケージ情報                | 29 |

| タイミング仕様                | 30 |

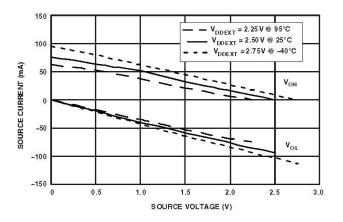

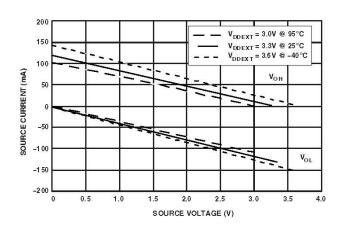

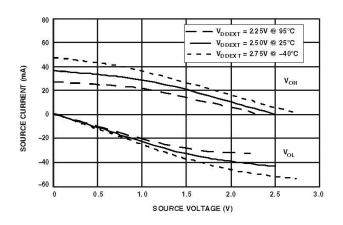

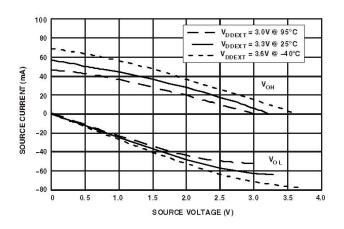

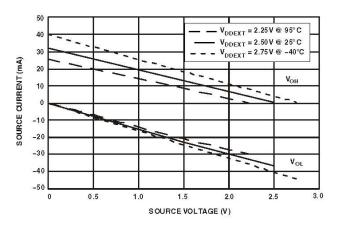

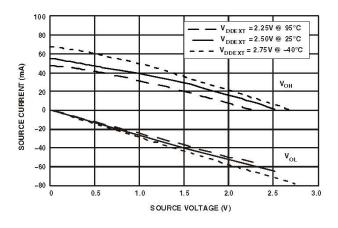

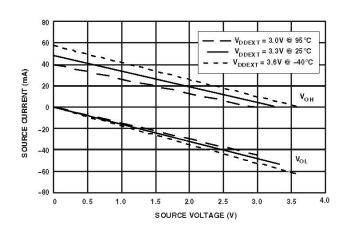

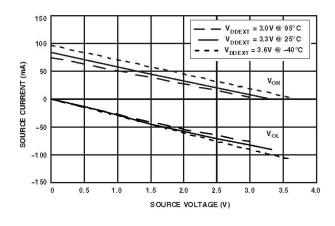

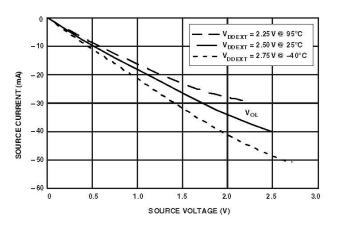

| 出力駆動電流                 | 51 |

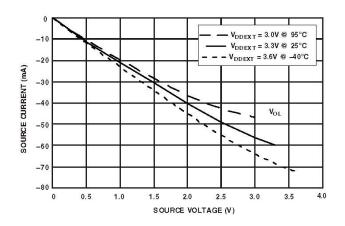

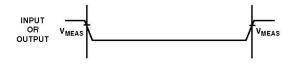

| テスト条件                  | 53 |

| 熱特性                    | 56 |

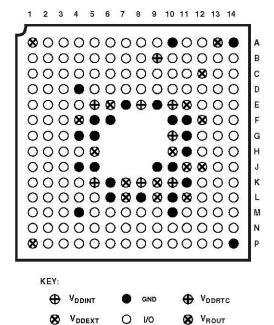

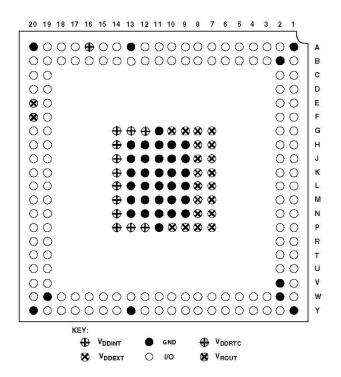

| 182 ボールCSP_BGAのボール配置   | 57 |

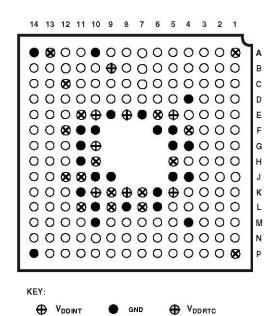

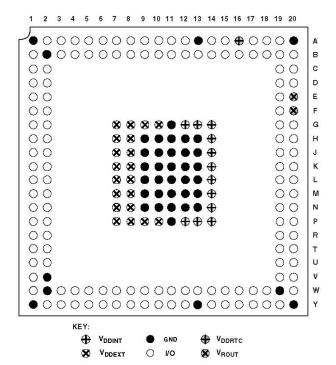

| 208 ボールCSP_BGAのボール配置   | 60 |

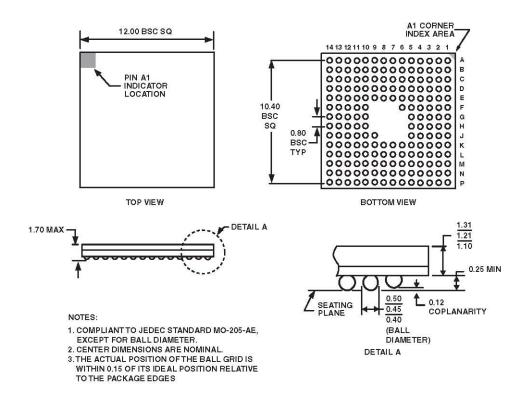

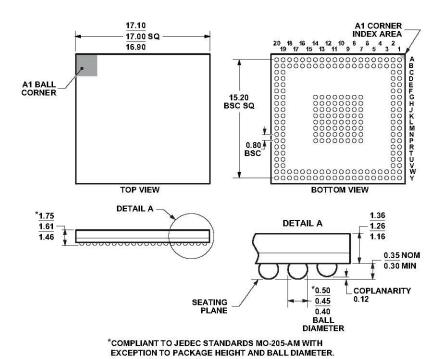

| 外形寸法                   | 63 |

| 表面実装デザイン               | 64 |

| 車載製品                   |    |

| オーダー・ガイド               | 65 |

## 改訂履歴

2/09—Rev. E to Rev. G

The revision F data sheet was never released publicly. The following revisions include those from both revision E to F and from revision F to G.

| Revised the I <sub>DDSLEEP</sub> , I <sub>DDDEEPSLEEP</sub> , and I <sub>DDINT</sub> specifications.S Electrical Characteristics             |     |

|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Removed the Power Dissipation section.See Estimating Pow for the ADSP-BF534/BF536/BF537 Blackfin Processors (EE-29 and Table 16 and Table 15 | 97) |

| Added $t_{NOBOOT}$ specification to Clock and Reset Timing 3                                                                                 | 30  |

| Removed DATA15–0 from footnote 1 in Asynchronous Memo<br>Write Cycle Timing                                                                  | -   |

| Revised SDRAM t <sub>ENSDAT</sub> specification.See SDRAM Interf<br>Timing                                          |    |

|---------------------------------------------------------------------------------------------------------------------|----|

| Revised serial ports internal clock timing specifications t <sub>SFSI</sub> and t <sub>SDRI</sub> .See Serial Ports | 39 |

| Revised SPI master timing specifications and diagram. See Serial Peripheral Interface Port—Master Timing            | 42 |

| Revised SPI slave timing specifications and diagram.  See Serial Peripheral Interface Port—Slave Timing             | 43 |

| Revised timer cycle timing specifications t <sub>TIS</sub> and t <sub>TOD</sub> .See Tin<br>Cycle Timing            |    |

| Revised Figure 61 and Figure 62 (added NC pin).                                                                     | 59 |

|                                                                                                                     |    |

## 概要

ADSP-BF534/ADSP-BF536/ADSP-BF537 は Blackfin <sup>®</sup>製品ファミリに属し、アナログ・デバイセズ/インテル・マイクロ・シグナル・アーキテクチャ(MSA)を採用しています。

Blackfin プロセッサは、2 系統の MAC を内蔵する最新の信号 処理エンジン、直交性の優れた RISC ライクなマイクロプロセッサ命令セットの利点、シングル命令マルチプル・データ (SIMD)マルチメディア機能を1つの命令セット・アーキテクチャに統合したものです。

ADSP-BF534/ADSP-BF536/ADSP-BF537 の各プロセッサは、 完全なコード互換性とピン互換性を持っています。性能、内 蔵メモリ、イーサネットMACモジュールの有無が異なってい ます。仕様性能、メモリ、機能構成を表1 に示します。

表1 プロセッサの比較

| Features                             |                              | ADSP-BF534           | ADSP-BF536           | ADSP-BF537           |

|--------------------------------------|------------------------------|----------------------|----------------------|----------------------|

| Ethernet MAC                         |                              | _                    | 1                    | 1                    |

| CAN                                  |                              | 1                    | 1                    | 1                    |

| TWI                                  |                              | 1                    | 1                    | 1                    |

| SPORTs                               |                              | 2                    | 2                    | 2                    |

| UARTs                                |                              | 2                    | 2                    | 2                    |

| SPI                                  |                              | 1                    | 1                    | 1                    |

| GP Timers                            |                              | 8                    | 8                    | 8                    |

| Watchdog Time                        | rs                           | 1                    | 1                    | 1                    |

| RTC                                  |                              | 1                    | 1                    | 1                    |

| Parallel Peripher                    | ral Interface                | 1                    | 1                    | 1                    |

| GPIOs                                |                              | 48                   | 48                   | 48                   |

|                                      | L1 Instruction<br>SRAM/Cache | 16K bytes            | 16K bytes            | 16K bytes            |

|                                      | L1 Instruction<br>SRAM       | 48K bytes            | 48K bytes            | 48K bytes            |

| Memory<br>Configuration              | L1 Data<br>SRAM/Cache        | 32K bytes            | 32K bytes            | 32K bytes            |

|                                      | L1 Data SRAM                 | 32K bytes            | _                    | 32K bytes            |

|                                      | L1 Scratchpad                | 4K bytes             | 4K bytes             | 4K bytes             |

|                                      | L3 Boot ROM                  | 2K bytes             | 2K bytes             | 2K bytes             |

| Maximum Speed                        | d Grade                      | 500 MHz              | 400 MHz              | 600 MHz              |

| Package Option<br>CSP_BGA<br>CSP_BGA | s:                           | 208-Ball<br>182-Ball | 208-Ball<br>182-Ball | 208-Ball<br>182-Ball |

Blackfin プロセッサは、業界をリードするシステム・ペリフェラルとメモリの豊富なセットを統合することにより、次世代アプリケーションに対する最適なプラットフォームになっています。次世代アプリケーションでは、RISC ライクなプログラマブル性、マルチメディアのサポート、最先端の信号処理を1つのパッケージに統合することが必要とされています。

#### ポータブルな低消費電力アーキテクチャ

Blackfin プロセッサは、ワールド・クラスのパワー・マネジメントと性能を提供します。これらのプロセッサは低消費電力および低電圧デザイン技術を使って製造されており、動作電圧と動作周波数を変更できるダイナミック・パワー・マネジメント機能を持つため、全体の消費電力を大幅に削減することができます。この機能により、動作周波数だけを変える場合に比較して大幅な消費電力削減が可能になります。このため、ポータブル・アプリケーションでバッテリ寿命を延ばすことができます。

#### システム・インテグレーション

Blackfin プロセッサは、次世代ネットワーク接続アプリケーションを対象とする高集積度のシステム・オン・チップ・ソリューションです。この業界標準のインターフェースと高性能信号処理コアとの組み合わせにより、コスト・パフオーマンスの優れたアプリケーションを高価な外付け部品なしで迅速に開発することができます。システム・ペリフェラルとしては、IEEE 準拠802.3 10/100 イーサネット MAC (ADSP-BF536と ADSP-BF537の場合)、CAN 2.0B コントローラ、TWI コントローラ、2 個の UART ポート、SPI ポート、2 個のシリアル・ポート(SPORT)、9 個の汎用32 ビット・タイマ(8 個は PWM機能付き)、リアルタイム・クロック、ウォッチドッグ・タイマ、パラレル・ペリフェラル・インターフェース(PPI)などがあります。

#### Blackfinプロセッサ・ペリフェラル

ADSP-BF534/ADSP-BF536/ADSP-BF537 プロセッサには複数の広帯域バスを介してコアに接続された豊富なペリフェラル・セットが内蔵されており、システム構成の柔軟性と優れた全体システム性能を提供します (図1 参照)。このプロセッサは、専用ネットワーク通信モジュール、高速なシリアルおよびパラレル・ポート、内蔵ペリフェラルまたは外部ソースからの割込みを柔軟に管理する割込みコントローラ、多様なアプリケーションに応じてプロセッサとシステムの性能と消費電力特性を調節するパワー・マネジメント制御機能を内蔵しています。

汎用 I/O、CAN、TWI、リアルタイム・クロック、タイマを除くすべてのペリフェラルで、柔軟な DMA 構造がサポートされています。外付けの SDRAM と非同期メモリを含むプロセッサの種々のメモリ空間の間でのデータ転送用に個別のメモリ DMA チャンネルも用意されています。最大 133 MHz で動作する複数のオンチップ・バスは、プロセッサ・コアがすべての内蔵ペリフェラルおよび外部ペリフェラルと動作するための十分な帯域幅を提供しています。

Blackfin プロセッサは、ダイナミック・パワー・マネジメント機能をサポートするために電圧レギュレータを内蔵しています。この電圧レギュレータは、VDDEXTを使用した場合、広範囲なコア電圧レベルを提供します。この電圧レギュレータは、ユーザの指定によりバイパスすることができます。

Rev. G - 3/65 -

#### Blackfinプロセッサ・コア

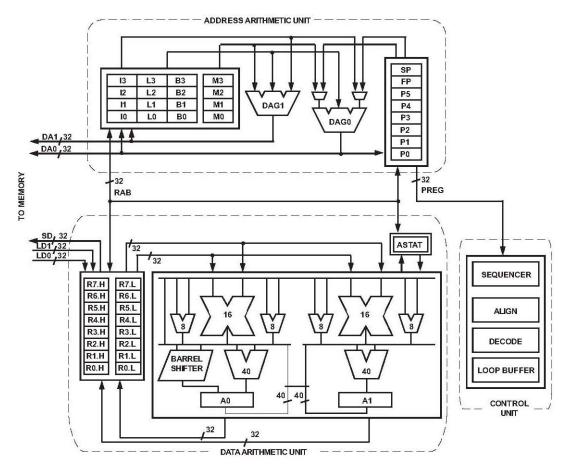

図 2 に示すように、Blackfinプロセッサ・コアは、2 個の 16 ビット乗算器、2 個の 40 ビット・アキュムレータ、2 個の 40 ビットALU、4 個のビデオALU、1 個の 40 ビット・シフタを内蔵しています。この演算ユニットは、レジスタ・ファイルにある 8 ビット、16 ビット、または 32 ビットのデータを処理します。

演算レジスタ・ファイルには、8個の32ビット・レジスタがあります。16ビットのオペランド・データに対する演算動作では、レジスタ・ファイルは16個の独立な16ビット・レジスタとして動作します。演算動作でのすべてのオペランドは、マルチポート化されたレジスタ・ファイル・フィールドと命令定数フィールドから取得されます。

各 MAC は、各サイクルで 16 ビット×16 ビットの乗算を実行して、演算結果を 40 ビットのアキュムレータにアキュムレートすることができます。 符号付きおよび符号なしフォーマット、まるめ処理、飽和処理をサポートしています。

ALU は、16 ビットまたは 32 ビットのデータに対する算術演算および論理演算の従来型セットを実行します。さらに、種々の信号処理タスクを加速させる多くの特殊命令を持っています。これらには、フィールド抽出およびポピュレーション・カウントなどのビット操作、モジュロ 2<sup>32</sup> の乗算、除算プリ

ミティブ、飽和処理、まるめ処理、符号/指数部の検出などが含まれます。ビデオ命令のセットには、バイト・アライメントおよびパッキング操作、クリッピング機能を持つ16ビットおよび8ビットの加算、8ビット平均処理、8ビットの減算/絶対値/アキュムレート(SAA)命令が含まれています。コンペア/セレクト命令とベクター・サーチ命令も用意されています。

命令によっては、2つの16ビットALU演算をレジスタ対(上位16ビットと下位16ビットの演算レジスタ)に対して同時に実行することができるものもあります。2つ目のALUを使用して、4つの16ビット演算を行うこともできます。

**40** ビット・シフタはシフトおよびローテイトを実行することができ、正規化、フィールドの抽出、フィールドの設定を行う命令をサポートするときに使います。

プログラム・シーケンサは、命令のアライメントやデコーディングなどの命令実行フローを制御します。プログラム・フロー制御に対しては、シーケンサは PC 相対および間接の条件付きジャンプ(静的分岐予測)とサブルーチン呼び出しをサポートしています。ゼロ・オーバーヘッド・ループ機能をサポートするためのハードウェアも用意されています。このアーキテクチャは完全にインターロックされています。すなわち、データ依存性を持つ命令を実行する際にプログラマはパイプラインを管理する必要がありません。

図2 Blackfinプロセッサ・コア

アドレス演算ユニットは 2 個のアドレスを提供するため、2 つの同時メモリ・フェッチが可能です。4 組の 32 ビットのインデックス・レジスタ、モデファイ・レジスタ、レングス・レジスタ、ベース・レジスタ(循環バッファ用)から構成されているマルチポート化されたレジスタ・ファイル、さらに 8 個の 32 ビット・ポインタ・レジスタ(C タイプのインデックス・スタック操作用)が含まれています。

Blackfin プロセッサは、修正ハーバード・アーキテクチャと 階層的メモリ構造の組み合わせをサポートしています。レベル1 (L1)メモリは、ほとんどレイテンシがない最高プロセッサ速度で動作するメモリです。L1 レベルでは、命令メモリは命令のみを保持します。2 つのデータ・メモリはデータを保持し、専用のスクラッチパッド・データ・メモリはスタック情報とローカル変数情報を格納します。

さらに、複数のL1メモリ・ブロックが用意されているため、SRAMとキャッシュのミックス構成が可能です。メモリ・マネジメント・ユニット(MMU)は、コア上で動作可能な個々のタスクに対してメモリ保護機能を提供し、意図しないアクセスからシステム・レジスタを保護します。

このアーキテクチャでは、ユーザ・モード、スーパーバイザ・モード、エミュレーション・モードの3種類の動作モードを提供しています。ユーザ・モードでは、ある種のシステム・リソースに対するアクセスを制限しているため、保護されたソフトウェア環境を提供しています。スーパーバイザ・モードでは、システム・リソースとコア・リソースに対するアクセス制限はありません。

Blackfin プロセッサの命令セットは、16 ビット・オペコード が最も頻繁に使用される命令となるように最適化されている ため、優れたコンパイル済みコード密度が得られます。複雑な DSP 命令は 32 ビット・オペコードにエンコードされて、フル機能のマルチファンクション命令になっています。 Blackfin プロセッサでは制限付きの並列発行機能をサポートしています。すなわち、2 つの 16 ビット命令と並列に、32 ビット命令を発行することができるため、多くのコア・リソースを1命令サイクルで使用することができます。

Blackfin プロセッサのアセンブリ言語では、代数式構文を採用しているためコードの読み書きが容易です。このアーキテクチャは C/C++コンパイラの使用に対して最適化されているため、高速かつ効率良いソフトウェアを作成することができます。

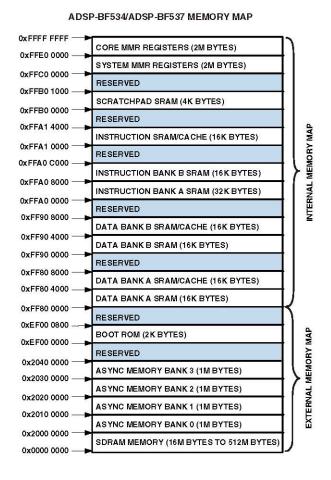

#### メモリ・アーキテクチャ

ADSP-BF534/ADSP-BF536/ADSP-BF537 プロセッサは、メモリを32 ビット・アドレスを使う1 つの連続した4Gバイトのアドレス空間として見ます。内部メモリ、外部メモリ、I/Oコントロール・レジスタなどのすべてのリソースは、この共通アドレス空間の一部を占有します。このアドレス空間のメモリ部分は階層的に構成されているため、キャッシュまたはSRAMとしての非常に高速で低レイテンシのオンチップ・メモリと、大容量で低価格かつ低性能のオフチップ・メモリ・システムとの間でコスト/パフォーマンスを均衡させることができます。(図3参照)。

内蔵 L1 メモリ・システムは、Blackfin プロセッサから使用可能な最高性能のメモリです。外部バス・インターフェース・ユニット(EBIU)を介してアクセスするオフチップ・メモリ・システムは、SDRAM、フラッシュ・メモリ、SRAM の拡張を提供し、最大 516 M バイトまでの物理メモリをアクセスすることができます。

メモリ DMA コントローラは、広帯域のデータ転送機能を提供します。内部メモリ空間と外部メモリ空間との間のコードまたはデータのブロック転送を実行することができます。

#### 内部(オンチップ)メモリ

ADSP-BF534/ADSP-BF536/ADSP-BF537 プロセッサは、3 つの ブロックのオンチップ・メモリを持っており、コアに対する 高速なアクセスを提供します。

1 つ目は L1 命令メモリであり、64K バイトの SRAM で構成 されており、その内の 16K バイトは 4 ウェイ・セット・アソ シアティブ・キャッシュとして設定することができます。こ のメモリは最高プロセッサ速度でアクセスすることができま す。

2 つ目のオンチップ・メモリ・ブロックは L1 データ・メモリ であり、各々最大 32K バイトの最大 2 バンクで構成されています。各メモリ・バンクは設定可能で、キャッシュ機能と SRAM 機能を選択できます。このメモリ・ブロックは最高プロセッサ速度でアクセスすることができます。

3 つ目のメモリ・ブロックは 4K バイトのスクラッチパッド SRAM であり、L1 メモリと同じ速度で動作しますが、データ SRAM としてのみアクセス可能で、キャッシュ・メモリとして設定することはできません。

#### 外部(オフチップ)メモリ

外部メモリは EBIU を介してアクセスします。この 16 ビット・インターフェースは、同期 DRAM (SDRAM)のバンクや、フラッシュ、EPROM、ROM、SRAM、メモリ・マップド I/O デバイスなどの最大 4 バンクの同期メモリ・デバイスに対して外付け部品不要な接続を提供します。

PC133 準拠の SDRAM コントローラは、最大 512 M バイトの SDRAM とインターフェースするように設定することができます。 SDRAM コントローラは最大 4 個の内部 SDRAM バンクをサポートし、各 SDRAM 内部バンクに対して別々に行をオープンすることができるため、全体性能が向上します。

非同期メモリ・コントローラは、非常に柔軟なタイミング・パラメータを持つ最大 4 バンクのデバイスを制御するように設定することができ、広範囲なデバイスをサポートすることができます。各バンクは使用するデバイスのサイズに無関係に 1M バイト・セグメントを占有します。したがって、各々が 1M バイトのメモリで使用された場合にのみ、これらのバンクが連続になります。

#### I/Oメモリ空間

ADSP-BF534/ADSP-BF536/ADSP-BF537 プロセッサには、I/O 空間は別に存在しません。すべてのリソースが均一な32 ビット・アドレス空間にマップされます。オンチップ I/O デバイスには固有のコントロール・レジスタがあり、4G バイト・アドレス空間の先頭近くのアドレスにあるメモリ・マップド・レジスタ(MMR)にマップされています。これらは2つの小さなブロックに分けられます。一方にはすべてのコア機能に対するコントロール MMR が、他方にはコアの外側にあるオンチップ・ペリフェラルの設定と制御に必要なレジスタが、それぞれ配置されています。この MMR はスーパーバイザ・モードでのみアクセス可能で、内蔵ペリフェラルに対しては予約済み空間として表示されます。

#### ADSP-BE536 MEMORY MAP 0xFFFF FFFF CORE MMR REGISTERS (2M BYTES) 0xFFE0 0000 SYSTEM MMR REGISTERS (2M BYTES) 0xFFC0 0000 RESERVED 0xFFB0 1000 SCRATCHPAD SRAM (4K BYTES) 0xFFB0 0000 INTERNAL MEMORY MAP RESERVED 0xFFA1 4000 INSTRUCTION SRAWCACHE (16K BYTES) 0xFFA1 0000 RESERVED 0xFFA0 C000 INSTRUCTION BANK B SRAM (16K BYTES) 0xFFA0 8000 INSTRUCTION BANK A SRAM (32K BYTES) 0xFFA0 0000 RESERVED 0xFF90 8000 DATA BANK B SRAM/CACHE (16K BYTES) 0xFF90 4000 RESERVED 0xFF90 0000 RESERVED 0xFF80 8000 DATA BANK A SRAM/CACHE (16K BYTES) 0xFF80 4000 RESERVED 0xFF80 0000 RESERVED 0xEF00 0800 BOOT ROM (2K BYTES) 0xEF00 0000 RESERVED **EXTERNAL MEMORY** 0x2040 0000 ASYNC MEMORY BANK 3 (1M BYTES) 0x2030 0000 ASYNC MEMORY BANK 2 (1M BYTES) 0x2020 0000 ASYNC MEMORY BANK 1 (1M BYTES) 0x2010 0000

図3 ADSP-BF534/ADSP-BF536/ADSP-BF537 のメモリ・マップ

0x2000 0000

0x0000 0000

#### ブート

Blackfinプロセッサには小さいブート・カーネルが内蔵されて おり、これがペリフェラルをブート用に設定します。Blackfin プロセッサがROMメモリ空間からブートするように設定さ れた場合、プロセッサはオンチップ・ブートROMから実行を 開始します。詳細については、ブーティング・モードを参照 してください。

#### イベント処理

Blackfin プロセッサのイベント・コントローラは、プロセッ サに対するすべての非同期イベントおよび同期イベントを処 理します。Blackfin プロセッサは、ネスティングと優先順位 付けをサポートするイベント処理を提供します。ネスティン グ機能を使うと、複数のイベント・サービス・ルーチンを同 時に起動することができます。優先順位付け機能により、高 い優先順位のイベントが低い優先順位のイベントより先にサ ービスされることが保証されます。このコントローラは、次 の5種類のタイプのイベントをサポートします。

- ·エミュレーション-エミュレーション・イベントが発生す ると、プロセッサはエミュレーション・モードになり、プ ロセッサのコマンドと制御が JTAG インターフェースを経 由するようになります。

- ・リセット-このイベントが発生すると、プロセッサがリセ ットされます。

・マスク不能割込み(NMI)—ソフトウェア・ウォッチドッグ・ タイマまたはプロセッサに対するNMI入力信号により、NMI イベントが発生されます。NMI イベントはパワーダウン インジケータとして頻繁に使用され、システムのシャット ダウン手順を起動します。

ASYNC MEMORY BANK 0 (1M BYTES)

SDRAM MEMORY (16M BYTES TO 512M BYTES

- ・例外—プログラム・フローに同期して発生するイベント(す なわち、命令が完了する前に例外が処理されます)。デ タ・アライメント違反や未定義命令のような条件で例外が 発生します。

- 割込み―プログラム・フローに対して非同期に発生するイ ベント。入力ピン、タイマ、その他のペリフェラル、さら に特定のソフトウェア命令により発生されます。

各イベント・タイプはリターン・アドレスを保持するレジス タと対応する return-from-event 命令を持っています。イベン トが発生すると、プロセッサの状態はスーパーバイザ・スタ ックに待避させられます。

Blackfin プロセッサのイベント・コントローラは、コア・イ ベント・コントローラ(CEC)とシステム割込みコントローラ (SIC)の2ステージから構成されています。コア・イベント・ コントローラはシステム割込みコントローラと一緒に動作し て、全システム・イベントの優先付けと制御を行います。概 念的には、ペリフェラルからの割込みが SIC に入力されて、 CEC の汎用割込みに直接接続されます。

Rev. G -6/65-

#### コア・イベント・コントローラ(CEC)

CECは、専用割込みと例外イベントの他に9個の汎用割込み (IVG15~7)をサポートしています。これらの汎用割込みの内、低優先順位の割込み(IVG15~14)はソフトウェア割込みハンドラ用に、残りの7つの優先順位の割込み入力はBlackfinプロセッサのペリフェラルのサポートに、それぞれ使用することが推奨されます。表2 に、CECに対する入力、イベント・ベクター・テーブル(EVT)内の識別名、それぞれの優先順位を示します。

表2 コア・イベント・コントローラ(CEC)

| Priority       | ( <u>)                                    </u> |           |

|----------------|------------------------------------------------|-----------|

| (0 Is Highest) | Event Class                                    | EVT Entry |

| 0              | Emulation/Test Control                         | EMU       |

| 1              | Reset                                          | RST       |

| 2              | Nonmaskable Interrupt                          | NMI       |

| 3              | Exception                                      | EVX       |

| 4              | Reserved                                       | _         |

| 5              | Hardware Error                                 | IVHW      |

| 6              | Core Timer                                     | IVTMR     |

| 7              | General-Purpose Interrupt 7                    | IVG7      |

| 8              | General-Purpose Interrupt 8                    | IVG8      |

| 9              | General-Purpose Interrupt 9                    | IVG9      |

| 10             | General-Purpose Interrupt 10                   | IVG10     |

| 11             | General-Purpose Interrupt 11                   | IVG11     |

| 12             | General-Purpose Interrupt 12                   | IVG12     |

| 13             | General-Purpose Interrupt 13                   | IVG13     |

| 14             | General-Purpose Interrupt 14                   | IVG14     |

| 15             | General-Purpose Interrupt 15                   | IVG15     |

#### システム割込みコントローラ(SIC)

システム割込みコントローラは、多くのペリフェラル割込み源から発生するイベントと優先順位付けされたCECの汎用割込み入力との間の対応と接続を提供します。プロセッサはデフォルトの対応を提供しますが、ユーザは割込み割り当てレジスタ(IAR)に該当する値を書き込むことにより、割込みイベントの対応と優先順位を変更することができます。表3に、SICに対する入力とCECに対するデフォルトの対応を示します。

#### イベント制御

Blackfin プロセッサはイベントの処理を制御する非常に柔軟なメカニズムを提供します。CECでは、3個のレジスタを使って、イベントの制御を行います。各レジスタは16ビット幅です。

CEC 割込みラッチ・レジスタ(ILAT)—イベントがラッチされたタイミングを表示します。プロセッサがイベントをラッチしたとき、該当するビットがセットされ、イベントがシステムに受理されたとき、クリアされます。このレジスタはコントローラから自動的に更新されますが、対応するIMASK ビットがクリアされているときにのみ、書込みが可能です。

表3 システム割込みコントローラ(SIC)

| 衣の ラバチ 自由 起のコントロー                                              | 5 (010)            |                            |

|----------------------------------------------------------------|--------------------|----------------------------|

| Peripheral Interrupt Event                                     | Default<br>Mapping | Peripheral<br>Interrupt ID |

| PLL Wakeup                                                     | IVG7               | 0                          |

| DMA Error (Generic)                                            | IVG7               | 1                          |

| DMAR0 Block Interrupt                                          | IVG7               | 1                          |

| DMAR1 Block Interrupt                                          | IVG7               | 1                          |

| DMAR0 Overflow Error                                           | IVG7               | 1                          |

| DMAR1 Overflow Error                                           | IVG7               | 1                          |

| CAN Error                                                      | IVG7               | 2                          |

| Ethernet Error (ADSP-BF536 and ADSP-BF537 only)                | IVG7               | 2                          |

| SPORT 0 Error                                                  | IVG7               | 2                          |

| SPORT 1 Error                                                  | IVG7               | 2                          |

| PPI Error                                                      | IVG7               | 2                          |

| SPI Error                                                      | IVG7               | 2                          |

| UART0 Error                                                    | IVG7               | 2                          |

| UART1 Error                                                    | IVG7               | 2                          |

| Real-Time Clock                                                | IVG8               | 3                          |

| DMA Channel 0 (PPI)                                            | IVG8               | 4                          |

| DMA Channel 3 (SPORT 0 Rx)                                     | IVG9               | 5                          |

| DMA Channel 4 (SPORT 0 Tx)                                     | IVG9               | 6                          |

| DMA Channel 5 (SPORT 1 Rx)                                     | IVG9               | 7                          |

| DMA Channel 6 (SPORT 1 Tx)                                     | IVG9               | 8                          |

| TWI                                                            | IVG10              | 9                          |

| DMA Channel 7 (SPI)                                            | IVG10              | 10                         |

| DMA Channel 8 (UART0 Rx)                                       | IVG10              | 11                         |

| DMA Channel 9 (UART0 Tx)                                       | IVG10              | 12                         |

| DMA Channel 10 (UART1 Rx)                                      | IVG10              | 13                         |

| DMA Channel 11 (UART1 Tx)                                      | IVG10              | 14                         |

| CAN Rx                                                         | IVG11              | 15                         |

| CAN Tx                                                         | IVG11              | 16                         |

| DMA Channel 1 (Ethernet Rx,<br>ADSP-BF536 and ADSP-BF537 only) | IVG11              | 17                         |

| Port H Interrupt A                                             | IVG11              | 17                         |

| DMA Channel 2 (Ethernet Tx,<br>ADSP-BF536 and ADSP-BF537 only) | IVG11              | 18                         |

| Port H Interrupt B                                             | IVG11              | 18                         |

| Timer 0                                                        | IVG12              | 19                         |

| Timer 1                                                        | IVG12              | 20                         |

| Timer 2                                                        | IVG12              | 21                         |

| Timer 3                                                        | IVG12              | 22                         |

| Timer 4                                                        | IVG12              | 23                         |

| Timer 5                                                        | IVG12              | 24                         |

| Timer 6                                                        | IVG12              | 25                         |

| Timer 7                                                        | IVG12              | 26                         |

| Port F, G Interrupt A                                          | IVG12              | 27                         |

| Port G Interrupt B                                             | IVG12              | 28                         |

Rev. G - 7/65 -

#### 表 1 システム割込みコントローラ(SIC) (続き)

| Peripheral Interrupt Event                      | Default<br>Mapping | Peripheral<br>Interrupt ID |

|-------------------------------------------------|--------------------|----------------------------|

| DMA Channels 12 and 13<br>(Memory DMA Stream 0) | IVG13              | 29                         |

| DMA Channels 14 and 15<br>(Memory DMA Stream 1) | IVG13              | 30                         |

| Software Watchdog Timer                         | IVG13              | 31                         |

| Port F Interrupt B                              | IVG13              | 31                         |

- ・CEC 割込みマスク・レジスタ(IMASK)—各イベントのマスク/アンマスクを制御します。IMASK レジスタ内でビットがセットされると、イベントがアンマスクされて、アサートされたときに CEC が処理します。IMASK レジスタ内のビットがクリアされると、イベントがマスクされて、ILATレジスタにイベントがラッチされても、プロセッサによるサービスが禁止されます。このレジスタはスーパーバイザ・モードで読み書きが可能です(汎用割込みは、STI命令と CLI 命令を使って、それぞれグローバルにイネーブルおよびディスエーブルすることができることに注意してください)。

- ・CEC 割込みペンディング・レジスタ(IPEND)—IPEND レジスタはネストされたすべてのイベントを記録します。 IPEND レジスタ内でビットがセットされると、イベントがアクティブであること、またはあるレベルでネストされていることを表します。このレジスタはコントローラから自動的に更新されますが、スーパーバイザ・モードでのみ読み出し可能です。

SICは3個の32ビットの割込みコントロールおよびステータス・レジスタを提供することにより、さらに詳細なイベント処理制御を可能にします。各レジスタには、表3に示す各ペリフェラル割込みイベントに対応するビットが配置されています。

- ・SIC 割込みマスク・レジスタ(SIC\_IMASK)—各ペリフェラル割込みイベントのマスク/アンマスクを制御します。レジスタ内でビットがセットされると、対応するペリフェラル・イベントがアンマスクされて、イベントのアサート時にシステムが処理します。レジスタ内でビットがクリアされると、対応するペリフェラル・イベントがマスクされて、プロセッサによるイベントのサービスが禁止されます。

- ・SIC 割込みステータス・レジスタ(SIC\_ISR)—複数のペリフェラルを 1 つのイベントに対応させることができるため、ソフトウェアはこのレジスタを使って、割込みを発生したペリフェラル・イベント・ソースを探します。ビットがセットされているとき、該当するペリフェラルが割込み発生中であることを表し、ビットがクリアされているとき、ペリフェラルはイベントを発生していないことを表します。

- ・SIC割込みウェイクアップ・イネーブル・レジスタ (SIC\_IWR)—このレジスタの対応するビットをイネーブルすると、該当するペリフェラルがプロセッサをウェイクアップするペリフェラルに設定されます。イベントが発生すると、プロセッサはスリープ(パワーダウン)モードからウェイクアップします(詳細については、ダイナミック・パワー・マネジメントを参照してください)。

複数の割込み源を1つの汎用割込みに対応させることができるため、この割込み入力で検出された割込みイベントを処理する前または処理中に、さらに複数のパルスが同時にアサートされることがあります。SIC は割込みアクノリッジとして、IPEND レジスタ値を監視します。

割込みの立ち上がりエッジが検出されると(検出にはコア・クロックで2サイクル必要)、ILAT レジスタの該当するビットがセットされます。IPEND レジスタのビットがセットされると、該当するビットがクリアされます。IPEND ビットは、イベントがプロセッサのパイプラインに入力されたことを表示します。この時点で、CEC は対応するイベント入力上の、次の立ち上がりエッジ・イベントを認識し、キューに接続します。汎用割込みの立ち上がりエッジ変化から IPEND 出力のアサートまでの最小レイテンシは、コア・クロックで3サイクルですが、内部動作とプロセッサの状態に応じて、レイテンシはこれより長くなることがあります。

#### DMAコントローラ

Blackfin プロセッサは独立した複数の DMA コントローラを内蔵しており、自動データ転送をサポートしてプロセッサ・コアのオーバーヘッドを少なくします。DMA 転送は、プロセッサの内部メモリと DMA 機能を持つペリフェラルとの間で可能です。さらに、DMA 転送は任意の DMA 機能を持つペリフェラルと外部メモリ・インターフェースに接続された外部デバイス(SDRAM コントローラや同期メモリ・コントローラなど)との間でも可能です。DMA 機能を持つペリフェラルとしては、イーサネット MAC (ADSP-BF536 と ADSP-BF537の場合)、SPORT、SPI ポート、UART、PPI などがあります。DMA 機能を持つ各ペリフェラルは少なくとも 1 つの専用DMA チャンネルを持っています。

DMA コントローラは、1 次元(1D)と 2 次元(2D)の DMA 転送 をサポートしています。 DMA 転送の初期化は、レジスタまたはディスクリプタ・ブロックと呼ばれるパラメータのセットを使って行います。

2D DMA 機能は、最大 64K エレメント×64K エレメントまでの任意の行および列サイズをサポートし、さらに最大±32K エレメントまでの任意の行および列ステップ・サイズをサポートしています。また、行ステップ・サイズより小さい列ステップ・サイズを許容するため、インターリーブされたデータ・ストリームが可能です。この機能は、特に、即座にデータのインターリーブ解除が必要とされるビデオ・アプリケーションで役立ちます。

DMA コントローラがサポートする DMA タイプの例を次に示します。

- ・完了時に停止するシングル・リニア・バッファ

- ・バッファがフルまたは部分的フル毎に割込みを発生する自 己リフレッシュ循環バッファ

- ・ディスクリプタのリンクされたリストを使用する 1D または 2D の DMA

- ・共通ページ内のベース DMA アドレスのみを指定する、ディスクリプタのアレイを使用する 2D DMA

専用ペリフェラル DMA チャンネルの他に、2 つのメモリ DMA チャンネルがあり、プロセッサ・システムの種々のメモリ間の転送に使用されます。この機能を使うと、最小のプロセッサ介入で、任意のメモリ(外部 SDRAM、ROM、SRAM、フラッシュ・メモリなど)間でのデータ・ブロックの転送が可能になります。メモリ DMA 転送は、非常に柔軟なディスクリプタ・ベースの方法、または標準的なレジスタ・ベースの自動バッファ・メカニズムを使って制御することができます。

Rev. G - 8/65 -

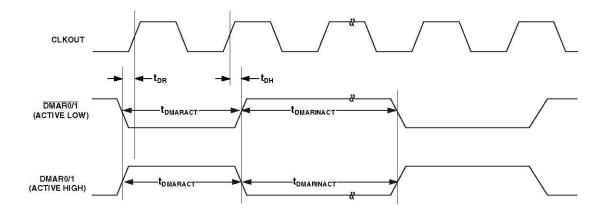

また、ADSP-BF534/ADSP-BF536/ADSP-BF537 プロセッサには、外部バス・インターフェース・ユニット(EBIU)と組み合わせて使用する場合、2 本の外部 DMA 要求ピンを使用した外部 DMA コントローラ機能もあります。この機能は、外部FIFOやUSB 2.0のような広帯域通信ペリフェラルに対して高速インターフェースが必要な場合に使うことができます。この機能を使うと、メモリ DMA の多数のデータ転送を制御することができます。エッジあたりの転送数は、設定することができます。メモリ DMA のコアに対する外部バスの優先順位を上げるように、この機能を使って設定することができます。

#### リアルタイム・クロック

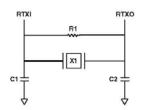

リアルタイム・クロック(RTC)は、時刻、ストップウォッチ、アラームを含むデジタル時計機能を提供します。RTCは、プロセッサ外部の32.768 kHz 水晶からクロック駆動されます。RTCペリフェラルは専用電源ピンを持っているため、プロセッサの他の部分が低消費電力状態にあるときでも、パワーアップ状態を維持することができます。RTCは、秒、分、時間または日毎の割込み、プログラマブルなストップウォッチ・カウントダウンでの割込み、設定したアラーム時刻での割込みなど、複数のプログラマブルな割込みオプションを提供します。

32.768 kHz の入力クロック周波数は、プリスケーラにより 1 Hz 信号まで分周されます。タイマのカウンタ機能は、60 秒カウンタ、60 分カウンタ、24 時間カウンタ、32,768 日カウンタの 4 つのカウンタから構成されています。

アラーム機能がイネーブルされると、タイマ出力がアラーム・コントロール・レジスタ内に設定された値に一致したとき、割込みが発生されます。アラームは2種類あり、最初のアラームは日単位です。2つ目のアラームは日時単位です。

ストップウォッチ機能では、設定した値から秒分解能でカウントダウンします。ストップウォッチがイネーブルされて、かつカウンタがアンダーフローすると、割込みが発生されます。

他のペリフェラルと同様に、RTC は任意の RTC ウェイクアップ・イベントが発生したときに、プロセッサをスリープ・モードからウェイクアップさせることができます。さらに、RTC ウェイクアップ・イベントはディープ・スリープ・モードからプロセッサをウェイクアップさせることができ、内蔵電圧レギュレータをハイバネート動作モードからウェイクアップさせることができます。

RTCピンのRTXIとRTXOを外付け部品と 図 4 のように接続してください。

#### ウォッチドッグ・タイマ

ADSP-BF534/ADSP-BF536/ADSP-BF537 プロセッサは、32 ビット・タイマを内蔵しています。このタイマはソフトウェア・ウォッチドッグ機能を構成するときに使うことができます。ソフトウェア・ウォッチドッグがソフトウェアからリセットされる前にタイマがタイムアウトすると、システム・リセット、マスク不能割込み(NMI)、または汎用割込みが発生して、プロセッサを強制的に既知状態に設定します。このためシス

テムの可用性を向上させることができます。プログラマがタイマのカウント値を初期化し、該当する割込みをイネーブルして、タイマをイネーブルします。その後、カウントが設定値からゼロに到達する前に、ソフトウェアからカウンタを再設定するようにします。外部ノイズまたはソフトウェア・エラーに起因してこのソフトウェアが停止すると、タイマをリセットすることができなくなるので、システムが未知の状態に留まってしまうことを防止します。

SUGGESTED COMPONENTS:

ECLIPTEK EC38J (THROUGH-HOLE PACKAGE)

EPSON MC405 12pF LOAD (SURFACE-MOUNT PACKAGE)

C1 = 22pF

C2 = 22pF

R1 = 10MΩ

NOTE: C1 AND C2 ARE SPECIFIC TO CRYSTAL SPECIFIED FOR X1.

CONTACT CRYSTAL MANUFACTURER FOR DETAILS, C1 AND C2

SPECIFICATIONS ASSUME BOARD TRACE CAPACITANCE OF 3pF.

#### 図4 RTCの外付け部品

ハードウェア・リセットを発生するように設定すると、ウォッチドッグ・タイマはコアとプロセッサ・ペリフェラルの両方をリセットします。リセットの後、ソフトウェアはウォッチドッグ・タイマ・コントロール・レジスタのステータス・ビットを調べることにより、ハードウェア・リセットの原因はウォッチドッグであったか否かを知ることができます。

このタイマは、最大周波数 f<sub>SCLK</sub>のシステム・クロック(SCLK) によりクロック駆動されます。

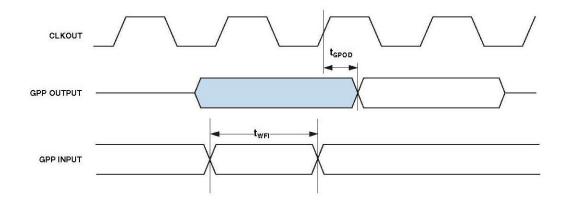

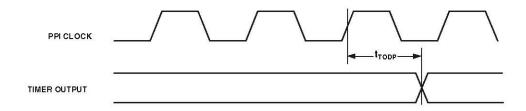

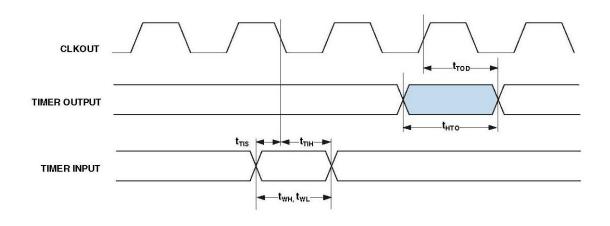

#### タイマ

このプロセッサには、9個の汎用プログラマブル・タイマ・ユニットがあります。8個のタイマには外部ピンがあり、パルス幅変調器(PWM)またはタイマ出力として、またはタイマを駆動するクロック入力として、または外部イベントのパルス幅と周期を測定するメカニズムとして、設定することができます。これらのタイマは、他の複数の対応するPFピンの外部クロック入力、PPI\_CLK入力ピンへの外部クロック入力、または内部SCLKに同期させることができます。

タイマ・ユニットを 2 個の UART および CAN コントローラ と組み合わせて使用し、データ・ストリーム内のパルス幅を 計測して、それぞれのシリアル・チャンネルのソフトウェア 自動ボーレート検出機能を実現することができます。

タイマはプロセッサ・コアに対して割込みを発生して、システム・クロックまたは外部信号のカウントに対する同期用の 周期イベントを提供することができます。

8個の汎用プログラマブル・タイマの他に、9個目のタイマも用意されています。このタイマは内部プロセッサ・クロックから駆動され、オペレーティング・システムの周期割込みの発生に使用されるシステム・ティック・クロックとして使用されます。

Rev. G - 9/65 -

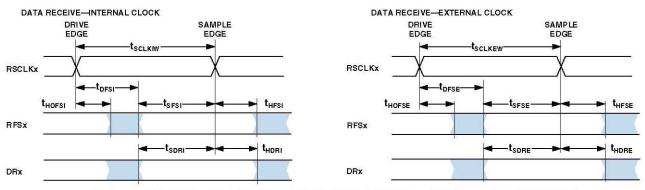

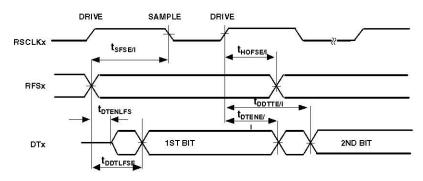

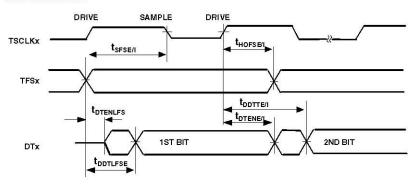

### シリアル・ポート(SPORT)

ADSP-BF534/ADSP-BF536/ADSP-BF537 プロセッサは、シリアル通信とマルチプロセッサ通信用に2個のデュアル・チャンネル同期シリアル・ポート(SPORT0とSPORT1)を内蔵しています。SPORT は次の機能をサポートしています。

- · I2S 動作

- ・双方向動作—各 SPORT は 2組の独立した送信ピンと受信ピンを持っているため、8 チャンネルの  $I^2S$  ステレオ・オーディオが可能です。

- ・バッファ付き(深さ 8)送信および受信ポート―各ポートは他のプロセッサ・デバイスに対するデータ・ワードの入出力用にデータ・レジスタを内蔵し、データ・レジスタに対してデータをシフト入出力するシフトレジスタを内蔵しています。

- ・クロック 各送信および受信ポートは周波数範囲  $(f_{SCLK}/131,070)$  Hz~ $(f_{SCLK}/2)$  Hz の外部シリアル・クロック または内部クロックを使うことができます。

- ワード・レングス―各 SPORT は 3~32 ビット長のシリアル・データ・ワードをサポートし、MSB ファーストまたはLSB ファーストで転送されます。

- ・フレーミング―各送信および受信ポートは、各データ・ワードに対するフレーム同期信号有りまたは無しで動作することができます。フレーム同期信号は内部または外部で発生することができ、アクティブ・ハイまたはロー、さらに2パルス幅分の進みまたは遅れフレーム同期が可能です。

- ・ハードウェアによる圧伸—各 SPORT は ITU 勧告 G.711 に準拠する A 則または  $\mu$  則の圧伸を実行することができます。 圧伸は SPORT の送信チャンネルおよび/または受信チャンネルに対して選択でき、レイテンシの増加はありません。

- ・シングル・サイクル・オーバーヘッドの DMA 動作—各 SPORT はメモリ・データの複数のバッファを自動的に受信 および送信することができます。プロセッサは、SPORT と メモリの間の DMA 転送シーケンスをリンクまたはチェー ンすることができます。

- ・割込み―各送信および受信ポートは、データ・ワードの転送完了またはデータ・バッファ全体または複数のバッファを DMA を使って転送した後に割込みを発生します。

- ・マルチチャンネル機能—各 SPORT は 1024 のチャンネル・ ウインドウの中から 128 のチャンネルをサポートし、H.100、 H.110、MVIP90、HMVIP の各標準と互換性を持っています。

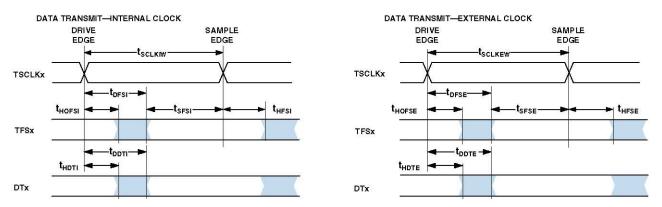

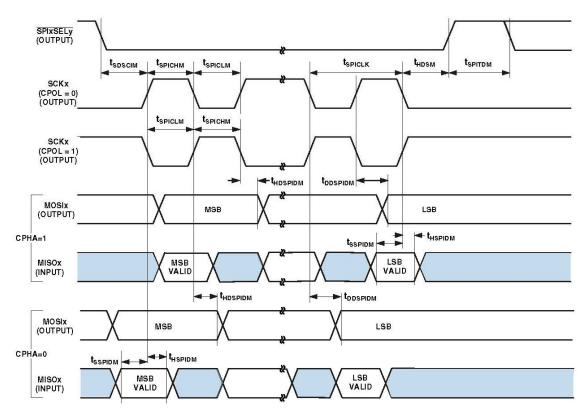

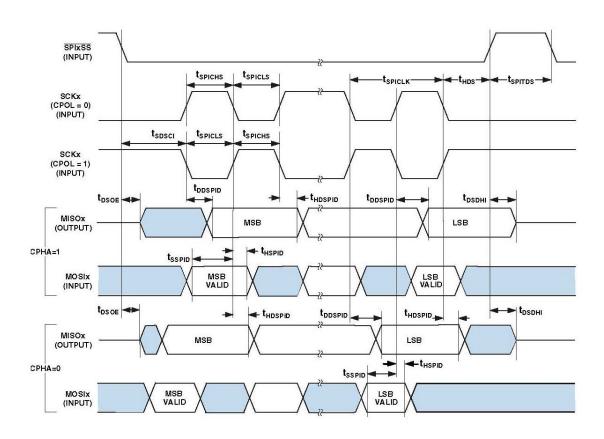

## シリアル・ペリフェラル・インターフェース(SPI) ポート

ADSP-BF534/ADSP-BF536/ADSP-BF537 プロセッサは、複数の SPI 互換デバイスと通信できるようにする SPI 互換ポートを内蔵しています。

SPI インターフェースは、2 本のデータ・ピン(マスター出力スレーブ入力 MOSI とマスター入力スレーブ出力 MISO)とクロック・ピン(シリアル・クロック SCK)の 3 本のピンを使ってデータを転送します。SPI チップ・セレクト入力ピン(SPISS)を使うと、他の SPI デバイスからこのプロセッサを選択することができ、7 本の SPI チップ・セレクト出力ピン(SPISEL7~1)を使うと、このプロセッサから他の SPI デバイスを選択することができます。SPI セレクト・ピンは再設定されたプログラマブル・フラグ・ピンです。これらのピンを使って、SPI ポートはマスター/スレーブ・モードとマルチマスタ環境をサポートする全二重同期シリアル・インターフェースを提供します。

SPI ポートのボーレートとクロック位相/極性はプログラマブルであり、データ・ストリームの送信または受信をサポートするように設定可能な DMA コントローラを内蔵しています。SPI の DMA コントローラは、同時に単方向アクセスしかサービスできません。

SPIポート・クロック・レートは次のように計算されます。

$$SPI Clock Rate = \frac{f_{SCLK}}{2 \times SPI\_BAUD}$$

ここで、16 ビット SPI\_BAUD レジスタの値は 2~65,535 です。 転送時、SPI ポートは 2 本のシリアル・データ・ライン上で データをシリアルにシフトして送信と受信を同時に行います。 シリアル・クロック・ラインは、2 本のシリアル・データ・ ライン上のデータのシフトとサンプリングを同期化します。

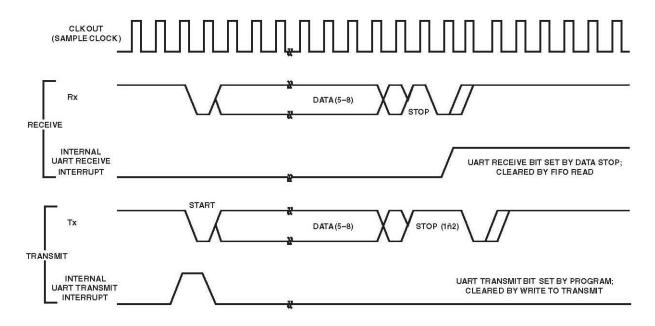

#### UARTポート

ADSP-BF534/ADSP-BF536/ADSP-BF537 プロセッサは、PC 標準 UART と互換性を持つ2個の全二重ユニバーサル非同期レシーバ/トランスミッタ(UART)ポートを内蔵しています。各 UART ポートは他のペリフェラルまたはホストに対するシンプルな UART インターフェースを提供し、全二重、DMA、シリアル・データの同期転送をサポートしています。この UART ポートは、5~8 ビットのデータ・ビット、1 ビットまたは 2 ビット幅のストップ・ビット、パリティ(偶数、奇数または無し)をサポートしています。各 UART ポートは次の 2 つの動作モードをサポートしています。

- ・PIO (プログラムド I/O)—プロセッサは I/O マップド UART レジスタに対して書き込みまたは読み出しを行うことにより、データを送信または受信します。データは送信と受信でダブル・バッファされています。

- ・DMA (ダイレクト・メモリ・アクセス)—DMA コントローラが送信データと受信データを転送します。この方法は、メモリに対するデータ転送に必要とされる割込みの回数と頻度を減らします。UART は、送信と受信に対して各 1 個の専用 DMA チャンネルを持っています。これらの DMA チャンネルはサービス・レートが相対的に低いため、大部分の DMA チャンネルより低いデフォルト優先順位を持っています。

各 UART ポートのボーレート、シリアル・データ・フォーマット、エラー・コードの発生とステータス、割込みは次のように設定することができます。

- ・毎秒(f<sub>SCLK</sub>/1,048,576)~(f<sub>SCLK</sub>/16)ビットの範囲のビット・レートをサポート

- 1 フレーム当たり 7~12 ビットのデータ・フォーマットを サポート

- ・送信動作と受信動作でプロセッサに対するマスク可能な割 込みを発生するように設定可能

UART ポート・クロック・レートは次のように計算されます。

$$UART\ Clock\ Rate\ =\ \frac{f_{SCLK}}{16\times UARTx\_Divisor}$$

ここで、16 ビット *UARTx\_Divisor* は、UARTx\_DLH レジスタ (上位 8 ビット)と UARTx\_DLL レジスタ(下位 8 ビット)から取得します。

Rev. G - 10/65 -

汎用タイマの機能との組み合わせにより、自動ボーレート検 出機能をサポートします。

UART ポートは、Infrared Data Association(IrDA®)のシリアル赤外線物理層リンク仕様(SIR)プロトコルに対応するように機能拡張されています。

### コントローラ・エリア・ネットワーク(CAN)

ADSP-BF534/ADSP-BF536/ADSP-BF537 プロセッサは、CANコントローラを提供しています。これは、CAN 2.0B (アクティブ)プロトコルを採用した通信コントローラです。このプロトコルは非同期通信プロトコルで、工業制御システムと車載制御システムで使用されています。CANプロトコルは CRCチェック・メッセージ・エラー・トラッキング機能と故障ノードの隔離機能を採用しているため、ネットワークを介する信頼度の高い通信機能を持ち、制御アプリケーションに適しています。

CANコントローラは次の機能を提供しています。

- ・32 個のメールボックス(受信専用が 8 個、送信専用が 8 個、 受信または送信に設定可能が 16 個)。

- ・各メールボックスに対する専用着信マスク。

- ・先頭の2バイトのデータ・フィルタ機能の追加。

- ・標準(11 ビット)および拡張(29 ビット)の識別子(ID)メッセージ・フォーマットのサポート。

- ・リモート・フレームのサポート。

- アクティブまたはパッシブ・ネットワーク・サポート。

- ・ハイバネート・モード(最小スタティック消費電力モード) からの CAN ウェイクアップ。

- ・Tx 完了、Rx 完了、エラー、グローバルなどの割込み。 各ネットワーク接続の電気的特性が非常に厳しいため、CAN インターフェースは一般に、コントローラとトランシーバの 2 つの部分に分かれています。このため、1 つのコントローラ で、さまざまなドライバと CAN ネットワークをサポートす ることができます。CAN モジュールとは、インターフェース のコントローラ・デバイスを意味します。このコントローラ・ インターフェースは、3.3 V の高速なフォルト・トレラントな 1 線式トランシーバに対する接続をサポートしています。

#### TWIコントローラ・インターフェース

ADSP-BF534/ADSP-BF536/ADSP-BF537 プロセッサは、複数のデバイス間で制御データを交換するシンプルな方法を提供する 2 線式インターフェース(TWI)モジュールを内蔵しています。TWI は、広く採用されている  $I^2C^{\otimes}$ バス規格と互換性を持ってます。この TWI モジュールは、マスターとスレーブの同時動作機能を提供し、7 ビット・アドレシング機能とマルチメディア・データ調停をサポートしています。TWI インターフェースは 2 本のピンを使って、クロック(SCL)とデータ(SDA)を転送し、最大 400 kbps の速度でプロトコルをサポートします。TWI インターフェース・ピンは、5 V のロジック・レベルと互換性を持っています。

さらに、このプロセッサの TWI モジュールは、シリアル・カメラ・コントロール・バス(SCCB)機能と互換性を持っているため、種々の CMOS カメラ・センサー・デバイスの制御が容易です。

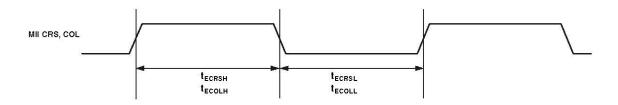

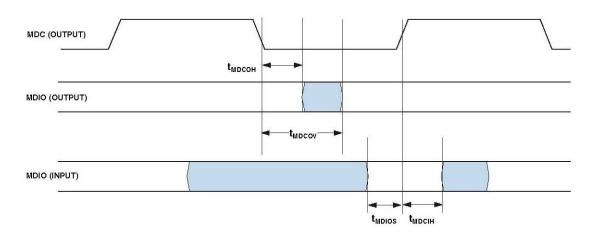

#### 10/100 イーサネットMAC

ADSP-BF536 プロセッサと ADSP-BF537 プロセッサは、10-BaseT (10 Mbps)動作と 100-BaseT (100 Mbps)動作をサポートする高速イーサネット・メディア・アクセス・コントローラ(MAC)を内蔵することにより、ネットワークに対する直接接続機能を提供しています。10/100 イーサネット MAC ペリフェラルは IEEE 802.3-2002 規格と完全な互換性を持ち、プロセッサ・システムの他の部分による監視、バス使用、またはメッセージ処理を最小にするようにデザインされたプログラマブルな機能を提供します。

標準機能には次の機能が含まれます。

- ・外部 PHY の MII プロトコルと RMII プロトコルのサポート

- ・全二重モードと半二重モード。

- ・データのフレーミングとカプセル化:プリアンブル、レングス・パッディング、FCSの生成と検出。

- ・メディア・アクセス・マネジメント(半二重動作の場合):衝 突フレームの再送とバックオフ・タイミングの制御などの、 衝突と輻輳の処理。

- ・フロー制御(全二重動作の場合): PAUSE フレームの生成と 検出。

- ・ステーション・マネジメント: PHY レジスタに対する読み/ 書き込みアクセス用 MDC/MDIO フレームの生成。

- ・ 最低 25 MHz までの SCLK 動作範囲(アクティブ動作モード とスリープ動作モード)。

- · Tx から Rx への内部ループバック。

拡張機能には次が含まれます。

- ・シングル水晶システムのサポートを可能にする外部 PHY へのバッファ付き水晶出力。

- ・IP ヘッダーと Rx フレームの IP ペイロード・フィールドの 自動チェックサム計算。

- ・32 ビット・ディスクリプタ駆動の独立な Rx および Tx DMA チャンネル。

- ・ソフトウェアでの効率の良いバッファ・キュー管理を可能にする、フレーム完了セマフォなどの、DMAを使ったメモリに対するフレーム・ステータスの送信。

- ・Tx DMA での、MAC ヘッダーとペイロードの個別ディスク リプタのサポート、バッファ・コピー動作が不要になりま す。

- 14 バイト MAC ヘッダーの後ろで、カプセル化 Rx または Tx IP パケット・データのメモリ内偶数 32 ビット・アライメントをサポートする便利なフレーム・アライメント・モード

- ・次の任意の組み合わせをサポートするプログラマブルなイーサネット・イベント割込み

- ・選択した任意のRxまたはTxフレーム・ステータス条件。

- · PHY 割込み条件。

- ウェイクアップ・ピンの機能

- ・ハーフ・フルで、選択した任意の MAC マネジメント・カ ウンタ

- · DMA ディスクリプタ・エラー。

- ・選択可能なクリア・オン・リード動作を行い、最大値の 1/2 でプログラマブルな割込みを行う 47 個の MAC マネジメント統計カウンタ。

- マルチキャスト・フレームおよび/またはユニキャスト・フレームの64ビット・アドレス・ハッシュ・テーブルを含み、ブロードキャスト、マルチキャスト、ユニキャスト、コントロール、ダメージの各フレームに対するフィルタ・モードを設定可能な、プログラマブルなRxアドレス・フィルタ。

- ・低消費電力スリープ・モードで DMA を使用した外部メモリとの間の Rx フレーム、Tx フレーム、ステータスの介入不要な転送をサポートする高度なパワー・マネジメント。

- ・マジック・パケットまたは4種類のユーザ定義ウェイクアップ・フレーム・フィルタによるスリープ動作モードからのシステム・ウェイクアップ。

- ・802.3Q タグ付き VLAN フレームのサポート。

- ・プログラマブルな MDC クロック・レートとプリアンブル 抑圧。

- ・RMII 動作で、7本の未使用ピンを他の用途の GPIO ピンとして設定可能。

#### ポート

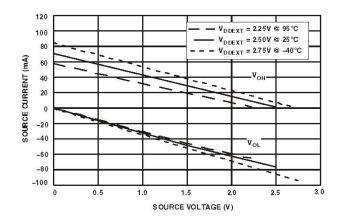

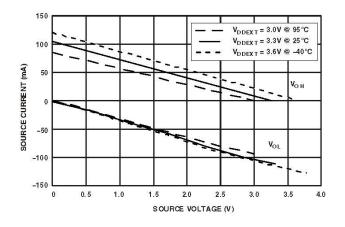

ADSP-BF534/ADSP-BF536/ADSP-BF537 プロセッサでは、多くのペリフェラル信号を 4 ポート(ポート F、ポート G、ポート H、ポート J)にグループ化しています。対応するピンの大部分は複数の信号間で共用されています。ポートは、マルチプレクサ制御として機能します。 8 本のピン(ポート  $F7\sim0$ )は、高ソース/高シンク電流能力を提供します。

#### 汎用I/O (GPIO)

このプロセッサには、48本の双方向汎用 I/O (GPIO)ピンがあり、3個の GPIO モジュールに割り当てられています (PORTFIO、PORTGIO、PORTHIOに、それぞれポートF、ポートG、ポートHが対応)。ポートJには GPIO 機能がありません。各 GPIO ピンは、他のプロセッサ・ペリフェラルと機能を共用していますが、GPIO 機能がデバイス・パワーアップ時のデフォルト状態になります。 GPIO の出力ドライバも入力ドライバもデフォルトではアクティブになりません。各汎用ポート・ピンは、次のようにポートのコントロール・レジスタ、ステータス・レジスタ、割込みレジスタを操作することにより、個別に制御することができます。

- ・GPIO ディレクション・コントロール・レジスター各 GPIO ピンの方向(入力または出力)を指定します。

- ・GPIO コントロール・レジスタおよびステータス・レジスタープロセッサでは、"write one to modify"方式を採用しています。この方式では、GPIO ピンの任意の組み合わせを1回の命令で変更し、かつ変更しない GPIO ピンのレベルに影響を与えないようにすることができます。4個のコントロール・レジスタが用意されています。ピンの値をセットするときに書き込むレジスタ、ピンの値をトグルするときに書き込むレジスタ、ピンの値をトグルするときに書き込むレジスタがあります。GPIO ステータス・レジスタを読み出すと、ソフトウェアからピンの状態を調べることができます。

- ・GPIO 割込みマスク・レジスター2 個の GPIO 割込みマスク・レジスタにより、各 GPIO ピンがプロセッサへの割込みとして機能するように設定することができます。各 GPIO ピン値のセットおよびクリアに使う 2 個の GPIO コントロール・レジスタと同様に、一方の GPIO 割込みマスク・レジスタはビットをセットして割込み機能をイネーブルし、他方の割込みマスク・レジスタはビットをクリアして割込み機能をディスエーブルします。入力として定義された GPIO ピンはハードウェア割込みを発生するように設定することができ、出力ピンはソフトウェア割込みによりトリガーすることができます。

- ・GPIO 割込み検出レジスタ—2 個の GPIO 割込み検出レジスタは、各ピンをレベル検出にするかまたはエッジ検出にするかを指定します。さらに、立ち下がり検出を指定した場合、信号の単に立ち上がりエッジだけを検出するか、あるいは立ち上がりと立ち下がりの両エッジを検出するかも指定します。一方のレジスタは検出タイプを指定し、他方のレジスタはエッジ検出で有効とするエッジを指定します。

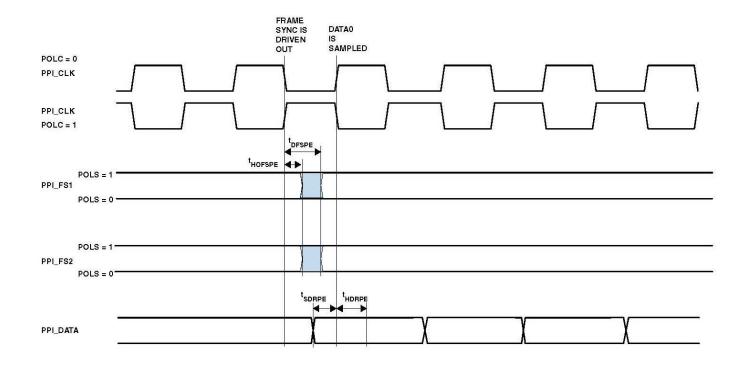

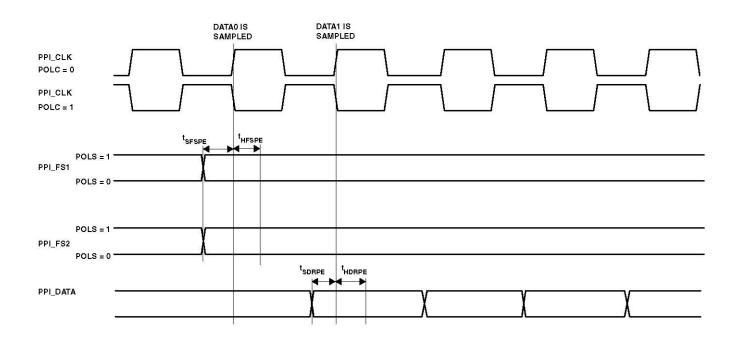

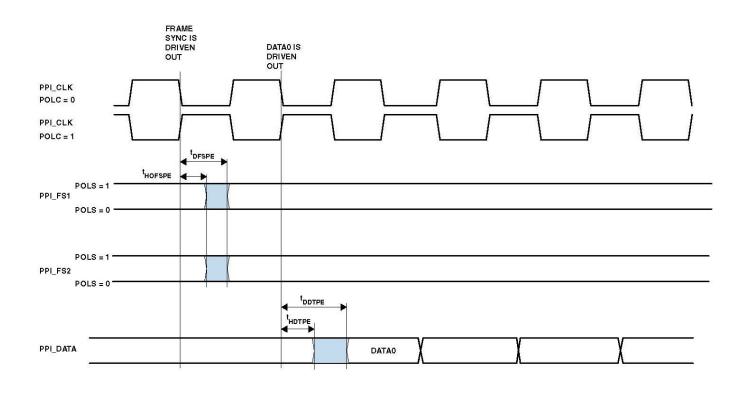

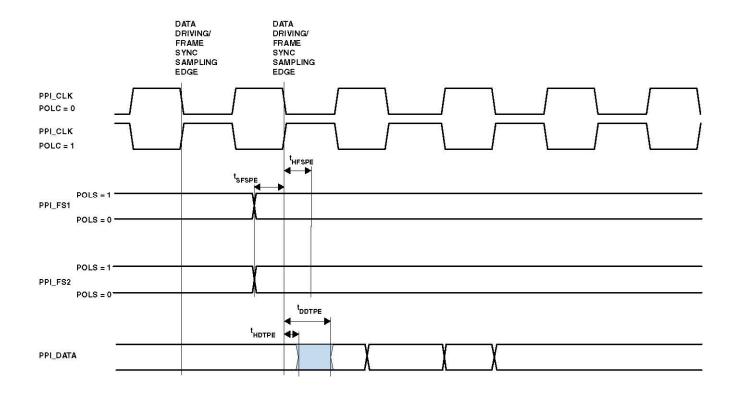

#### パラレル・ペリフェラル・インターフェース(PPI)

このプロセッサは、パラレル ADC および DAC、ビデオ・エンコーダおよびデコーダ、その他の汎用ペリフェラルに直接接続できるようにするパラレル・ペリフェラル・インターフェース(PPI)を内蔵しています。この PPI は、専用の入力クロック・ピン、最大3本までのフレーム同期ピン、最大16本までのデータ・ピンから構成されます。入力クロックではシステム・クロックの最大1/2までのパラレル・データ・レートをサポートし、同期信号は入力または出力に設定することができます。

PPI はさまざまな汎用動作モードと ITU-R 656 動作モードをサポートしています。汎用モードでは、PPI は最大 16 ビットのデータに対する半二重双方向データ転送を提供します。最大 3 フレームの同期信号もサポートします。ITU-R 656 モードでは、PPI は 8 ビットまたは 10 ビットのビデオ・データに対する半二重双方向転送を提供します。さらに、組み込まれた start-of-line (SOL)および start-of-field (SOF)プリアンブル・パケットのオンチップ・デコードもサポートしています。

#### 汎用モードの説明

PPI の汎用モードは、多様なデータ・キャプチャ・アプリケーションとデータ転送アプリケーション向けに用意されています。次の3種類のサブモードがサポートされています。

- 1.入力モード—フレーム同期とデータは PPI に対する入力になります。

- 2.フレーム・キャプチャ・モード—フレーム同期は PPI からの出力に、データは入力に、それぞれなります。

- 3.出力モード—フレーム同期とデータは PPI からの出力 になります。

#### 入力モード

入力モードは、ADC アプリケーションやハードウェア・シグナリングを持つビデオ通信向けに用意されています。最もシンプルな形式では、PPI\_FS1 はデータを読み込むタイミングを制御する外部フレーム同期入力になります。PPI\_DELAY MMR を使うと、このフレーム同期の受信とデータ読み込み開始との間の遅延(PPI\_CLK サイクル数)が可能になります。入力データ・サンプル数はユーザ設定可能で、PPI\_COUNTレジスタの値により決定されます。8、10~16 ビットのデータ幅がサポートされており、PPI\_CONTROL レジスタにより設定します。

#### フレーム・キャプチャ・モード

このモードを使うと、ビデオ・ソースがスレーブ(たとえば、フレーム・キャプチャの場合)として機能できるようになります。ADSP-BF534/ADSP-BF536/ADSP-BF537 プロセッサは、ビデオ・ソースから読み出すタイミングを制御します。PPI\_FS1 は H 同期出力に、PPI\_FS2 は V 同期出力に、それぞれなります。

#### 出力モード

このモードは、最大3個の出力フレーム同期を持つビデオまたはその他のデータの送信に使用されます。一般に、データ・コンバータ・アプリケーションに対しては1フレーム同期が適していますが、ハードウェア・シグナリングを持つビデオの送信を行うときは2または3フレーム同期を使います。

#### ITU-R 656 モードの説明

PPIのITU-R 656 モードは、さまざまなビデオのキャプチャ、 処理、転送アプリケーション向けに用意されています。次の 3 種類のサブモードがサポートされています。

- 1. アクティブ・ビデオ専用モード

- 2. 垂直ブランキング専用モード

- 3. 全体フィールド・モード

#### アクティブ・ビデオ・モード

このモードは、フィールドのアクティブ・ビデオ部分のみを対象とし、かつブランキング区間は対象にしないときに使います。PPIは、アクティブ・ビデオ終了(EAV)プリアンブル・シンボルとアクティブ・ビデオ開始(SAV)プリアンブル・シンボルとの間のデータ、または垂直ブランキング区間のデータを読み込みません。このモードでは、コントロール・バイト・シーケンスはメモリに保存されず、PPIによりフィルタされます。フィールド1の開始に同期した後、PPIはSAVコードまでの受信サンプルを無視します。1フレーム当たりのアクティブ・ビデオ・ライン数は、ユーザが指定します(PPI COUNT レジスタ)。

#### 垂直ブランキング区間モード

このモードでは、PPI は垂直ブランキング区間(VBI)データのみを転送します。

#### 全体フィールド・モード

このモードでは、受信ビット・ストリーム全体が PPI から読み込まれます。これには、アクティブ・ビデオ、コントロール・プリアンブル・シーケンス、水平ブランキング区間および垂直ブランキング区間に組込まれている補助データが含まれます。データ転送はフィールド1に対する同期後、直ちに開始されます。プロセッサ・コアから自立して動作する8個の DMA エンジンを使って、データが同期チャンネルとの間で転送されます。

#### ダイナミック・パワー・マネジメント

ADSP-BF534/ADSP-BF536/ADSP-BF537 プロセッサには 5 種類の動作モードがあり、各々は異なる性能と消費電力特性を持っています。その他に、ダイナミック・パワー・マネジメントはプロセッサ・コア電源電圧をダイナミックに変更する制御機能を提供して、さらに消費電力を減らすことができます。各ペリフェラルに対するクロックの制御によっても、消

費電力を減らすことができます。各モードに対する消費電力の設定を 表 4 にまとめます。表 16 、表 15 、表 17 を参照してください。

#### Full-On動作モード—最大性能

Full-On モードでは PLL がイネーブルされ、かつバイパスされないので、最大動作周波数で動作することができます。これはパワーアップ時のデフォルト実行状態であり、最大性能が得られます。プロセッサ・コアとイネーブルされた全ペリフェラルが最大速度で動作します。

#### アクティブ動作モード―中程度のダイナミック省電力

アクティブ・モードでは、PLL はイネーブルされていますが、バイパスされます。PLL がバイパスされているため、プロセッサ・コア・クロック(CCLK)とシステム・クロック(SCLK)は入力クロック(CLKIN)周波数で動作します。このモードでは、CLKIN 対 CCLK 乗算器の比率を変更することができます。ただし、変更は Full-On モードになるまで有効になりません。適切に設定された L1 メモリに対して、DMA アクセスを使用することができます。

アクティブ・モードでは、PLL コントロール・レジスタ (PLL\_CTL)を使って、PLL をディスエーブルすることができます。PLL をディスエーブルした場合、Full-On モードまたはスリープ・モードに入る前に PLL を再イネーブルする必要があります。

#### スリープ動作モード―高い省電力

スリープ・モードでは、プロセッサ・コアに対するクロック (CCLK)をディスエーブルしてダイナミック消費電力を削減します。ただし、PLLとシステム・クロック(SCLK)は動作を維持します。一般に、外部イベントまたはRTCの動作により、プロセッサがウェイクアップします。スリープ・モードでは、ウェイクアップ信号がアサートされると、プロセッサはPLLコントロール・レジスタ(PLL\_CTL)内のBYPASS ビットを調べます。BYPASS がディスエーブルされている場合、プロセッサは Full-On モードになります。BYPASS がイネーブルされている場合には、プロセッサはアクティブ・モードになります。

スリープ・モード内では、L1メモリに対するシステム DMA アクセスはサポートされていません。

表4 電源設定

| Mode       | PLL                  | PLL<br>Bypassed | Core<br>Clock<br>(CCLK) | System<br>Clock<br>(SCLK) | Internal<br>Power<br>(V <sub>DDINT</sub> ) |

|------------|----------------------|-----------------|-------------------------|---------------------------|--------------------------------------------|

| Full On    | Enabled              | No              | Enabled                 | Enabled                   | On                                         |

| Active     | Enabled/<br>Disabled | Yes             | Enabled                 | Enabled                   | On                                         |

| Sleep      | Enabled              | _               | Disabled                | Enabled                   | On                                         |

| Deep Sleep | Disabled             | _               | Disabled                | Disabled                  | On                                         |

| Hibernate  | Disabled             | _               | Disabled                | Disabled                  | Off                                        |

#### ディープ・スリープ動作モード―最高の省電力

ディープ・スリープ・モードでは、プロセッサ・コアに対するクロック(CCLK)と全同期ペリフェラルに対するクロック(SCLK)をディスエーブルすることにより、最高のダイナミッ

ク消費電力削減が得られます。RTCのような非同期システムは動作を続けますが、内部リソースまたは外部メモリをアクセスすることはできません。このパワーダウン・モードは、リセット割込み(RESET)またはRTCから発生される同期割込みによってのみ開始することができます。ディープ・スリープ・モード内で、RTC非同期割込みがアサートされると、プロセッサはアクティブ・モードになります。ディープ・スリープ・モード内で、RESETがアサートされると、プロセッサはFull-Onモードになります。

#### ハイバネート状態―最大静的消費電力削減

ハイバネート状態では、プロセッサ・コアに対する電圧とクロック(CCLK)、さらに全同期ペリフェラルに対するクロック(SCLK)をディスエーブルすることにより、最高の消費電力削減が得られます。 $VR\_CTL$  レジスタの FREQ ビットに b#00を書き込むことにより、プロセッサの内部電圧レギュレータをシャットオフすることができます。これにより、CCLK と SCLK がディスエーブルされます。さらにこの設定では、内部電源電圧( $V_{DDINT}$ )を 0 V に設定して、最小の消費電力にします。内部で保存されるクリティカルな情報(メモリ内容、レジスタ値など)は、プロセッサ状態を保持する場合には電源を切る前に不揮発性ストレージ・デバイスに書き込む必要があります。

この状態では $V_{\text{DDEXT}}$ が供給されているため、他に注記がない限り、すべての外部ピンはスリー・ステートになります。この機能を使うと、プロセッサに接続できる他のデバイスの電源を不要な電流なしで接続したままにすることができます。

イーサネット・モジュールまたは CAN モジュールは、内蔵電源レギュレータをウェイクアップさせることができます。 PH6 ピンを PHYINT 信号として外部 PHY デバイスに接続しない場合は、このピンを他のデバイスからロー・レベルに駆動してプロセッサをウェイクアップさせることができます。レギュレータは、リアルタイム・クロック・ウェイクアップ・イベントまたは RESET ピンのアサートによって、ウェイクアップさせることができます。すべてのハイバネート・ウェイクアップ・イベントにより、ハードウェア・リセット・シーケンスが起動されます。各々の割込みソースは、 $VR\_CTL$  レジスタを使ってイネーブルされます。

VR\_CTL レジスタと RTC レジスタ以外のすべての内部レジスタとメモリは、ハイバネート状態で値が失われます。状態変数は、外部 SRAM または SDRAM に保持することができます。VR\_CTL レジスタの SCKELOW ビットは、SDRAM がセルフ・リフレッシュ・モードで動作するか否かを制御します。このモードにより、プロセッサのリセット時に値を保持することが可能になります。

#### 省電力

表5 に示す3種類の電源ドメインをサポートしているため、業界標準や規則に準拠したまま、最大の柔軟性が得られます。プロセッサの内部ロジックを1つの電源ドメインにまとめて、RTCを他のI/Oから分離すると、RTCまたは他のI/Oデバイスに影響を与えることなく、プロセッサはダイナミック・パワー・マネジメントを利用することができるようになります。種々の電力ドメインに対するシーケンシング条件はありません。

表5 電源ドメイン

| X                                  |                       |  |  |

|------------------------------------|-----------------------|--|--|

| Power Domain                       | V <sub>DD</sub> Range |  |  |

| All internal logic, except RTC     | V <sub>DDINT</sub>    |  |  |

| RTC internal logic and crystal I/O | $V_{\text{DDRTC}}$    |  |  |

| All other I/O                      | $V_{\text{DDEXT}}$    |  |  |

プロセッサのダイナミック・パワー・マネジメント機能を使うと、プロセッサの入力電圧(V<sub>DDINT</sub>)とクロック周波数(f<sub>CCLK</sub>)の両方をダイナミックに制御することができます。

プロセッサの消費電力は、プロセッサのクロック周波数と動作電圧の二乗の関数になります。たとえば、クロック周波数を25%低下させると、消費電力は25%削減され、電圧を25%低下させると、消費電力は40%以上削減されます。さらに次式に示すように、これらの消費電力削減は加算的であり、クロック周波数と電源電圧の両方を低下させると、消費電力の削減は非常に大きくなります。

消費電力削減ファクタ(PSF)は次のように計算されます。

$$PSF = \frac{f_{CCLKRED}}{f_{CCLKNOM}} \times \left(\frac{V_{DDINTRED}}{V_{DDINTNOM}}\right)^2 \times \left(\frac{t_{RED}}{t_{NOM}}\right)$$

ここで、

fcclknomは公称コア・クロック周波数

fcclkredは削減されたコア・クロック周波数

VDDINTNOMは公称内部電源電圧

VDDINTREDは削減された内部電源電圧

$t_{NOM}$ は $f_{CCLKNOM}$ で動作する時間  $t_{RED}$ は $f_{CCLKRED}$ で動作する時間 パーセント消費電力削減は次のように計算されます。  $p_{DOWer}$  savings =  $(1-PSF) \times 100\%$

#### 電圧レギュレーション

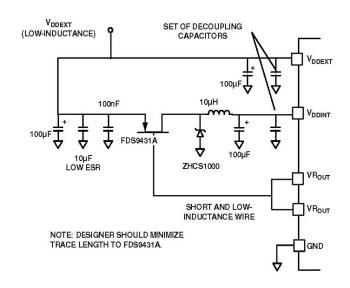

ADSP-BF534/ADSP-BF536/ADSP-BF537プロセッサは、 $V_{\text{DDEXT}}$ 電源から内部電圧レベル $V_{\text{DDINT}}$ を発生する電圧レギュレータを内蔵しています。特定のモデルのレギュレータ偏差と許容 $V_{\text{DDEXT}}$ 範囲については、動作条件を参照してください。

図5 電圧レギュレータ回路

図5 に、パワー・マネジメント・システムに必要な代表的な 外付け部品を示します。このレギュレータは内部ロジック電

Rev. G - 14/65 -

圧レベルを制御し、電圧レギュレータ・コントロール・レジスタ (VR\_CTL) を使って50 mV単位で設定することができます。スタンバイ消費電力を削減するため、I/O電源を維持したままプロセッサ・コアの電源を切るように内部電圧レギュレータを設定することができます。休眠状態では、 $V_{DDEXT}$ が維持されたままなので、外部バッファが不要になります。 $\overline{RESET}$ のアサートにより、電圧レギュレータをこのパワーダウン状態から起動することができ、ブート・シーケンスが開始されます。このレギュレータはユーザ指定により、ディスエーブルしてバイパスすることもできます。電圧レギュレーションについては、 $[Switching\ Regulator\ Design\ Considerations\ for\ the\ ADSP-BF533\ Blackfin\ Processors\ (EE-228)]を参照してください。$

#### クロック信号

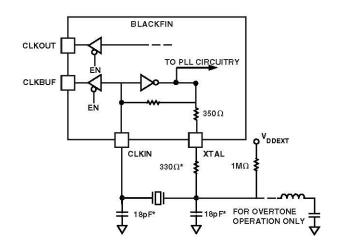

ADSP-BF534/ADSP-BF536/ADSP-BF537 プロセッサのクロックは、外部クリスタル・オシレータ、正弦波入力、または外部クロック発振器から出力される、バッファされ整形されたクロックにより駆動することができます。

外部クロックを使用する場合には TTL 互換信号を使い、通常動作時には仕様周波数未満で、停止、変更、動作させないでください。この信号はプロセッサの CLKIN ピンに接続されます。外付け水晶を使う場合は、XTAL ピンは解放のままにしてください。

あるいは、プロセッサは発振器回路を内蔵しているため、外部水晶を使うことができます。基本波周波数動作の場合、図6の回路を使用してください。並列共振で基本周波数のマイクロプロセッサ・グレードの水晶をCLKINピンとXTALピンの間に接続します。CLKINピンとXTALピンとの間の内蔵抵抗は、500 kΩ範囲です。さらに並列抵抗を追加することは推奨されません。図6に示す2個のコンデンサと直列抵抗は、正弦周波数の位相と振幅を微調整します。

図 6 に示すコンデンサと抵抗の値はtyp値です。コンデンサ値は、水晶メーカーの推奨負荷容量とPCBレイアウトに依存します。抵抗値は、水晶メーカーが規定する駆動レベルに依存します。許容温度範囲での複数デバイスについての慎重な調査に基づいて、カスタム化した値を確認する必要があります。

3 次高調波水晶は、25 MHzを超える周波数で使用することができます。図 6 に示すようにチューニングしたインダクタ回路を追加して、回路を 3 次高調波水晶動作用に変更します。3 次高調波動作のデザイン手順は、アプリケーション・ノート [Using Third Overtone Crystals with the ADSP-218x DSP (EE-168)]に記載してあります。

CLKBUF ピンに出力されるクロックは、内部クロックをバッファしたものです。このピンは、システム内で必要とされるクロック・ソース数を制限する際にイーサネット・アプリケーションで特に便利です。このタイプのアプリケーションでは、1個の25 MHz または50 MHz 水晶を直接プロセッサに接続することができます。CLKBUFの25 MHz または50 MHz 出力は、外部イーサネット MII または RMII PHY デバイスへ接続することができます。

デフォルトの逓倍比は 10 倍であるため、50 MHz の CLKIN を入力すると、低速グレードの推奨動作条件を超えます。この制限のため、50 MHz のクロック入力を必要とする RMII PHY は、低速グレードで CLKBUF ピンから直接駆動することはできません。この場合は、別の 50 MHz クロック・ソースを使うか、あるいは 25 MHz クロック入力オプションを持つ RMII PHY を使います。CLKBUF 出力はデフォルトでアク

ティブになっていますが、省電力のために VR\_CTL レジスタを使ってディスエーブルすることができます。

NOTE: VALUES MARKED WITH \* MUST BE CUSTOMIZED DEPENDING ON THE CRYSTAL AND LAYOUT. PLEASE ANALYZE CAREFULLY

#### 図6 外部水晶接続

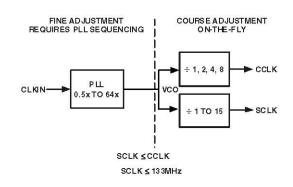

Blackfinコアは、内蔵ペリフェラルと異なるクロック・レートで動作します。図 7 に示すように、コア・クロック(CCLK)とシステム・ペリフェラル・クロック(SCLK)は入力クロック(CLKIN)信号から発生されます。オンチップPLLはプログラマブルな 0.5 倍~64 倍の倍率でCLKIN信号を逓倍することができます(VCO周波数の最小および最大規定値で制限されます)。デフォルトの倍率は 10 倍ですが、PLL\_CTLレジスタを使いソフトウェア命令シーケンスにより変更することができます。

PLL\_DIV レジスタに書き込みを行うだけで、CCLK と SCLK の周波数を即座に変更することができます。CCLK と SCLK の最大許容レートは  $V_{DDINT}$  と  $V_{DDEXT}$  に入力される電圧に依存しますが、VCO は常にデバイスのスピード・グレードで規定された周波数まで動作します。CLKOUT ピンは、チップ外部への SCLK 周波数を反映しています。このピンは SDRAM インターフェースに属しますが、他のタイミング仕様でも基準信号として機能します。デフォルトでアクティブですが、EBIU\_SDGCTL レジスタと EBIU\_AMGCTL レジスタを使ってディスエーブルすることができます。

図7 周波数変更方法

Rev. G - 15/65 -

すべての内蔵ペリフェラルは、システム・クロック(SCLK)によりクロック駆動されます。システム・クロック周波数は、PLL\_DIVレジスタのSSEL3~0 ビットを使って設定することができます。SSELフィールドに設定された値が、PLL出力(VCO)とシステム・クロックとの間の分周比を決定します。SCLK分周比の値は1~15です。表6に、代表的なシステム・クロック分周比を示します。

分周比は、システム・クロック周波数が最大値  $f_{SCLK}$  を超えないように選択する必要があることに注意してください。 SSELの値は、PLL 分周比レジスタ(PLL\_DIV)に該当する値を書き込むことにより、PLL ロック・レイテンシなしでダイナミックに変更することができます。

表6 システム・クロック比の例

| Signal Name | Divider Ratio | Example Frequency Ratios<br>(MHz) |      |

|-------------|---------------|-----------------------------------|------|

| SSEL3-0     | VCO:SCLK      | vco                               | SCLK |

| 0001        | 1:1           | 100                               | 100  |

| 0110        | 6:1           | 300                               | 50   |

| 1010        | 10:1          | 500                               | 50   |

コア・クロック(CCLK)周波数も、PLL\_DIVレジスタのCSEL1 ~0 ビットを使ってダイナミックに変更することができます。サポートしているCCLK分周比は、1、2、4、8 です(表 7 )。このプログラマブルなコア・クロック機能は、素早くコア周波数を変更するときに役立ちます。

表7 コア・クロック比

| Signal Name | Divider Ratio   | Example Frequency Ratio<br>(MHz) |      |

|-------------|-----------------|----------------------------------|------|

| CSEL1-0     | SEL1-0 VCO:CCLK | vco                              | CCLK |

| 00          | 1:1             | 300                              | 300  |

| 01          | 2:1             | 300                              | 150  |

| 10          | 4:1             | 500                              | 125  |

| 11          | 8:1             | 200                              | 25   |

最大CCLK周波数はデバイスのスピード・グレードだけでなく(オーダー・ガイドを参照)、入力される $V_{DDINT}$ 電圧にも依存します(表 10、表 11、表 12 参照)。最大システム・クロック・レート(SCLK)は、on theチップ・パッケージと入力される $V_{DDEXT}$ 電圧に依存します(表 14 参照)。

#### ブーティング・モード

ADSP-BF534/ADSP-BF536/ADSP-BF537プロセッサは、リセット後に内部メモリおよび外部メモリを自動的にローディングする6種類のメカニズムを持っています(表8)。7種類目のモードはブート・シーケンスをバイパスして、外部メモリから実行するために用意されています。

表8 ブーティング・モード

| BMODE2 - 0 | Description                                          |

|------------|------------------------------------------------------|

| 000        | Execute from 16bit external memory (bypass boot ROM) |

| 001        | Boot from 8bit or 16-bit memory (EPROM/flash)        |

| 010        | Reserved                                             |

| 011        | Boot from serial SPI memory (EEPROM/flash)           |

| 100        | Boot from SPI host (slave mode)                      |

| 101        | Boot from serial TWI memory (EEPROM/flash)           |

| 110        | Boot from TWI host (slave mode)                      |

| 111        | Boot from UART host (slave mode)                     |

リセット設定レジスタの BMODE ピンがパワーオン・リセット時とソフトウェア起動のリセット時にサンプルされて、次のモードが実行されます。

- ・16 ビットの外部メモリからの実行—16 ビット・パッキング のアドレス 0x2000 0000 から実行が開始されます。このモードでは、ブート ROM がバイパスされます。すべての構成の設定値は最低速デバイスに合わせて設定されます(3 サイクル・ホールド・タイム; 15 サイクル R/W アクセス・タイム; 4 サイクル・セットアップ)。

- ・8 ビットと 16 ビット外部フラッシュ・メモリからのブートーブート ROM メモリ空間に配置されている 8 ビットまたは 16 ビット・フラッシュ・ブート・ルーチンが非同期メモリ・バンク 0 を使って設定されます。すべての設定は、最低デバイス速度(3 サイクルのホールド・タイム、15 サイクルの R/W アクセス・タイム、4 サイクルのセットアップ)に設定されます。ブート ROM は、アドレス 0x2000 0000 のブート・ストリームの先頭バイトを調べます。値が 0x40 の場合、8 ビット・ブートを実行します。0x60 バイトでは、16 ビット・メモリ・デバイスと見なして 8 ビット DMA を実行します。0x20 バイトでも、16 ビット・メモリと見なしますが、16 ビット DMA を実行します。

- ・シリアルSPIメモリ(EEPROMまたはフラッシュ)すなわち8、16、または24ビット・アドレスのデバイスからのブートをサポートしています。また、Atmel 社の AT45DB041、AT45DB081、AT45DB161、AT45DB321、AT45DB642、AT45DB1282 の各 DataFlash®デバイスからのブートもサポートしています。SPIはPF10/SPISSEL1出力ピンを使って1個のSPIEEPROM/フラッシュ・デバイスを選択して、読み出しコマンドと連続アドレス・バイト(0x00)を発行し、有効な8、16、または24ビット、またはAtmel社のアドレサブル・デバイスが検出されると、プロセッサへのデータのクロック駆動を開始します。

- ・SPI ホスト・デバイスからのブート—Blackfin プロセッサは SPI スレーブ・モードで動作し、SPI ホスト(マスター)エー ジェントから.LDR ファイルのバイトを受信するように設定されます。ブート ROM がビジーのときホスト・デバイスからの送信を停止させるため、Blackfin プロセッサはホスト・ウエイト(HWAIT)と呼ばれる GPIO ピンをアサートして、フラグのアサートが解除されるまでバイトをさらに送信しないようにホスト・デバイスに通知します。フラグはユーザが選択し、この情報が FLAG ヘッダーのビット[10:5]を介して Blackfin プロセッサへ転送されます。

- ・UART からのブート―自動ボー・ハンドシェーク・シーケンスを使用して、ブート・ストリーム・フォーマットのプログラムがホストによりダウンロードされます。ホスト・

Rev. G - 16/65 -

エージェントは、UART のクロック能力内でボーレートを 選択します。自動ボーの実行時には、UART はビット・レートを決めるために、RXD ピンで"@"(boot stream)文字(8 ビット・データ、1 スタート・ビット、1 ストップ・ビット、 パリティなしビット)の受信を期待します。これに対してアクノリッジで応答します。このアクノリッジは、0xBF、 UART\_DLL 値、UART\_DLH 値、0x00 の 4 バイトで構成されています。ホストはこれでブート・ストリームをダウンロードできるようになります。プロセッサがホストを待たせる必要があるとき、CTS のアサートを解除します。このため、ホストはこの信号を監視している必要があります。

- ・シリアル TWI メモリ(EEPROM/フラッシュ)からのブート —Blackfin プロセッサはマスター・モードで動作し、独自 ID 0xA0 を持つ TWI スレーブを選択します。2 バイトの内 部アドレス 0x0000 から開始されるメモリ・デバイスに対し て連続読み出しコマンドを発行し、プロセッサへのデータ 入力を開始します。TWI メモリ・デバイスは Philips 社の I<sup>2</sup>C バス仕様バージョン 2.1 に準拠し、かつメモリ・デバイス の値をシーケンシャルに読み出せるように、内部アドレス・カウンタの自動インクリメント機能を持つ必要があります。

- ・TWI ホストからのブート—TWI ホスト・エージェントは、独自な ID 0x5F を持つスレーブを選択します。プロセッサはアクノリッジで応答すると、ホストはブート・ストリームをダウンロードできるようになります。TWI ホスト・エージェントは Philips 社の  $I^2C$  バス仕様バージョン 2.1 に準拠する必要があります。1 個の TWI から複数のプロセッサをブートさせるときは、 $I^2C$  マルチプレクサを使用して、プロセッサを 1 個ずつ選択することができます。

各ブート・モードで、外部メモリ・デバイスから 10 バイトの ヘッダーが最初に読み込まれます。このヘッダーは、転送バイト数とメモリ・ディステネーション・アドレスを指定します。どのブート・シーケンスでも、複数のメモリ・ブロックにロードすることができます。すべてのブロックをロードした後、L1 命令 SRAM の先頭からプログラムの実行が開始されます。

さらに、リセット設定レジスタのビット4をアプリケーション・コードから設定して、ソフトウェア・リセット時に通常のブート・シーケンスをバイパスすることもできます。このケースの場合、プロセッサは L1 命令メモリの先頭に直接ジャンプします。

ブート・モードを強化するため、その他のブーティング・メカニズムを提供する2つ目のソフトウェア・ローダを追加することができます。この2つ目のローダは、フラッシュ、可変ボーレート、その他のソースからのブートを可能にする機能を提供します。バイパス以外のすべてのブート・モードで、プログラムの実行は内蔵 L1 メモリ・アドレス 0xFFA0 0000から開始されます。

#### 命令セットの説明

Blackfin プロセッサ・ファミリのアセンブリ言語命令セットでは、代数式構文を採用しているためコードの読み書きが容易です。命令は、柔軟かつ高密度でエンコードされた命令セットを提供し、コンパイル後に最小のメモリ・サイズになるように特別に最適化されています。また、この命令セットは、1つの命令で多くのプロセッサ・コア・リソースを使用可能にするフル機能のマルチファンクション命令を提供します。この命令セットはマイクロコントローラで使用されている多くの機能との組み合わせにより、CおよびC++ソース・コードをコンパイルする際に非常に効率の良いものになります。さらに、このアーキテクチャでは、ユーザ動作モード(アルゴ

リズム/アプリケーション・コード)とスーパーバイザ動作モード(O/S カーネル、デバイス・ドライバ、デバッガ、ISR)を提供するため、コア・プロセッサ・リソースに対する複数レベルのアクセスが可能です。

プロセッサの独自なアーキテクチャを利用するアセンブリ言 語は次の利点を持っています。

- ・シームレスに統合された DSP/MCU 機能は、8 ビット動作と 16 ビット動作に対して最適化されています。

- ・1 サイクルあたり、2 個の 16 ビット MAC または 4 個の 8 ビット ALU + 2 個のロード/ストア+2 個のポインタ更新をサポートする並列発行ロード/ストア修正型ハーバード・アーキテクチャ

- ・全レジスタ、I/O、メモリが連続な4Gバイト・メモリ空間 にマップされているため、プログラミング・モデルが簡素

- ・任意のビットおよびビット・フィールドの操作、挿入、取り出しなどのようなマイクロコントローラ機能; 8 ビット、16 ビット、32 ビットのデータ型に対する整数演算;ユーザ・スタック・ポインタとスーパーバイザ・スタック・ポインタの分離

- ・16 ビットと 32 ビットの命令の混在(モード切り替えなし、 コード分離なし)などのコード密度の強化、使用頻度の高い 命令を 16 ビットにエンコード

#### 開発ツール

Blackfin プロセッサは、アナログ・デバイセズのエミュレータと VisualDSP++<sup>®1</sup>開発環境を含む CROSSCORE<sup>®2</sup>ソフトウェアおよびハードウェア開発ツールの完全なセットによりサポートされています。 他のアナログ・デバイセズ・プロセッサをサポートしている同じエミュレータ・ハードウェアも Blackfin プロセッサ・ファミリをエミュレートします。

VisualDSP++プロジェクト・マネジメント環境は、アプリケーションの開発とデバッグを可能にします。この環境には、代数的な構文に基づいた使い易いアセンブラ、アーカイバ(ライブラリアン/ライブラリ・ビルダ)、リンカー、ローダ、サイクルに対して正確な命令レベルのシミュレータ、C/C++コンパイラ、DSP 関数と数学関数を含む C/C++ランタイム・ライブラリが含まれています。これらのツールのキー・ポイントは C/C++コードの効率です。コンパイラは、C/C++コードを Blackfin アセンブリに効率良く変換するように開発されています。Blackfin プロセッサには、コンパイルされた C/C++コードの効率を改善するアーキテクチャ上の機能があります。

VisualDSP++デバッガは多くの重要な機能を持っています。 データ表示は、柔軟性を提供するプロッティング・パッケー ジにより機能強化されています。ユーザ・データのグラフィ ック表示により、プログラマはアルゴリズムの性能を迅速に 調べることができます。アルゴリズムが複雑になる程、この 機能設計者の開発スケジュールに大きな効果を持つことがで き、生産性を向上させます。データ・アクイジション機能は、 プログラム実行中のプロセッサの使用を最小限にします。 VisualDSP++独自のこの機能を使うと、ソフトウェア開発者 はプログラスのリアルタイム特性を損なうことなく重要なコ

はプログラムのリアルタイム特性を損なうことなく重要なコード実行の測定データを収集することができます。ソフトウェア内のボトルネックを迅速かつ効果的に特定できます。プロファイラを使うと、プログラマは性能に影響を与える領域に専念できるようになり、対策を講じることができます。

Rev. G - 17/65 -

<sup>&</sup>lt;sup>1</sup>VisualDSP++は Analog Devices, Inc.の登録商標です。 <sup>2</sup>CROSSCORE は Analog Devices, Inc.の登録商標です。

VisualDSP++デバッガを使って、C/C++プログラムとアセンブリ・プログラムをデバッグすると、プログラマは次のことが可能になります。

- ・C/C++とアセンブリ・コードの混在の表示(インターリーブ されたソースとオブジェクト情報)

- ・ブレークポイントの挿入

- ・レジスタ、メモリ、スタックへの条件付きブレークポイントの設定

- ・命令実行のトレース

- ・プログラム実行の連続的または統計的な分析

- ・メモリ内容のフィル、ダンプ、図形的表示

- ソース・レベル・デバッグの実行

- カスタム・デバッガ・ウインドウの作成

VisualDSP++ IDE を使うと、ソフトウェア開発の定義と管理が可能になります。ダイアログ・ボックスと属性ページを使うと、VisualDSP++エディタ内での色による強調表示などのすべての開発ツールの設定と管理ができます。これらの機能によりプログラマは次のことが可能になります。

・ 開発ツールによる入力の処理方法と出力の発生方法の制御 ・ツールのコマンドライン・スイッチとの1対1対応の維持 VisualDSP++カーネル(VDK)は、組込み型リアルタイム・プロ グラミングのメモリ制約とタイミング制約を解決するように 特別に作成されたスケジューリングとリソース・マネジメン トを内蔵しています。これらの機能を使うと、コードを効率 的に開発できるようになり、新しいアプリケーション・コー ドを開発する際に、最初からスタートする必要がなくなりま す。VDK の機能には、スレッド領域、クリティカル領域、未 スケジュール領域、セマフォ、イベント、デバイス・フラグ が含まれています。また、VDK は優先順位ベースの、プリエ ンプティブで協調動作的なタイムスライス・スケジューリン グ・アプローチもサポートしています。さらに、VDK はスケ ーラブルにデザインされています。アプリケーションである 特定の機能を使わない場合には、その機能をサポートするコ ードはターゲット・システムから除外されます。

VDK はライブラリであるため、開発者が使用するか否かを決めることができます。VDK は VisualDSP++開発環境に統合されていますが、標準のコマンドライン・ツールと一緒に使用することもできます。VDK を使うと、この開発環境は、多くのエラーを起こしやすいタスクについて開発者を支援し、システム・リソースの管理を支援し、種々の VDK ベースのオブジェクト生成を自動化し、VDK を使用するアプリケーションのデバッグではシステム状態を表示します。

エキスパート・リンカを使って、組込み型システムのコードとデータの配置を視覚的に操作します。メモリ使用状況は、カラー・グラフィックで表示することができます。コードとデータは、マウスのドラッグにより、プロセッサまたは外部メモリのさまざまな領域へ容易に移動することができます。ランタイム時のスタックとヒープの使用率を調べることができます。エキスパート・リンカは既存のリンカ定義ファイル(LDF)と完全な互換性を持っているため、グラフィカル環境とテキスト環境との間で移動することができます。

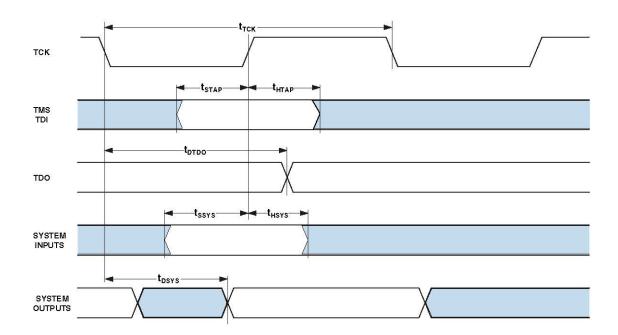

アナログ・デバイセズのエミュレータでは、Blackfin の IEEE 1149.1 JTAG テスト・アクセス・ポートを使って、エミュレーション時にターゲット・ボード・プロセッサのモニターと 制御を行っています。このエミュレータではフル速度のエミュレーションが可能なため、メモリ・スタック、レジスタ・スタック、プロセッサ・スタックの検証と変更が可能です。 プロセッサの JTAG インターフェースを使用すると、エミュレータがターゲット・システムのローディングまたはタイミ

ングに影響を与えないインサーキット・エミュレーションが 可能になります。

アナログ・デバイセズが提供するソフトウェア開発ツールとハードウェア開発ツールの他に、サード・パーティが Blackfin プロセッサ・ファミリをサポートする広範囲なツールを提供しています。サード・パーティのソフトウェア・ツールには、DSP ライブラリ、リアルタイム・オペレーティング・システム、ブロック図デザイン・ツールなどがあります。

#### EZ-KIT Lite®評価ボード

ADSP-BF534/ADSP-BF536/ADSP-BF537 プロセッサを評価する場合は、アナログ・デバイセズから提供する ADSP-BF537 EZ-KIT Lite ボードを使用してください。オーダー製品番号はADZS-BF537-EZLITE です。ボードにはエミュレーション機能が付いており、ソフトウェア開発機能が備わっています。複数のドータ・カードも提供しています。

## エミュレータ互換プロセッサ・ボードのデザイン

アナログ・デバイセズのエミュレータ・ファミリは、すべてのシステム開発者がハードウェア・システムとソフトウェア・システムをテストし、デバッグする際に必要とするツールです。アナログ・デバイセズは、各JTAGプロセッサ上でIEEE 1149.1 JTAGテスト・アクセス・ポート(TAP)を提供しています。エミュレータはこのタップを使ってプロセッサの内部機能をアクセスするため、コードのロード、ブレークポイントの設定、変数の表示、メモリの表示、レジスタの表示が可能になります。プロセッサはデータとコマンドを送信するとき停止する必要がありますが、エミュレータによる動作が完了した後に、システム・タイミングに影響を与えることなく、フル速度で動作するようにプロセッサ・システムを設定することができます。

これらのエミュレータを使うときは、ターゲット・ボードに プロセッサの JTAG ポートをエミュレータへ接続するヘッダ 一が含まれている必要があります。

機械的レイアウト、シングル・プロセッサ接続、マルチプロセッサ・スキャン・チェーン、信号バッファリング、信号終端、エミュレータ・ポッド・ロジックなどのターゲット・ボード・デザイン問題の詳細については、アナログ・デバイセズのウエブ・サイト(www.analog.com/ee-notes)にある「Analog Devices JTAG Emulation Technical Reference (EE-68)」を参照してください。エミュレータ・サポートの強化に合わせて、このドキュメントは定期的に更新されています。

#### 関連ドキュメント

ADSP-BF534/ADSP-BF536/ADSP-BF537 プロセッサ(および関連プロセッサ)について説明する次の出版物は、アナログ・デバイセズの営業または当社ウェブ・サイトに注文するすることができます。

- · Getting Started with Blackfin Processors

- · ADSP-BF537 Blackfin Processor Hardware Reference

- ADSP-BF53x/ADSP-BF56x Blackfin Processor Programming Reference

- ADSP-BF534/ADSP-BF536/ADSP-BF537 Blackfin Processor Anomaly List

## ピン説明

表9に、ADSP-BF534/ADSP-BF536/ADSP-BF537プロセッサのピン定義を示します。機能の最大化およびパッケージ・サイズとピン数を削減するため、複数の機能をマルチプレクスした共用ピンもあります。ピン機能が設定可能な場合には、デフォルト状態をテキストで示し、代替機能を斜字体で表してあります。名前の後に(\*)を付けたピンは、高ソース/高シンク電流能力を提供します。

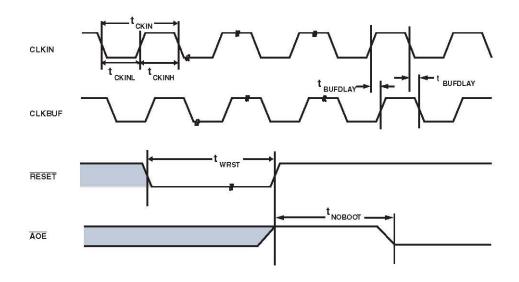

すべてのピンはリセット時とその直後にスリー・ステートになります。ただし、メモリ・インターフェース・ピン、非同期メモリ・コントロール・ピン、同期メモリ・コントロール・ピン、バッファ付き XTAL 出力ピン(CLKBUF)は除きます。

外部メモリ・インターフェースのこれらのピンはすべてハイ・レベルに駆動されますが、CLKOUT は例外でシステム・クロック・レートでトグルします。BRピンがアサートされた場合は、メモリ・ピンもスリー・ステートになります。

すべての I/O ピンの入力バッファはディスエーブルされますが、データシートでプルアップまたはプルダウンが必要と指定されたピンは例外です。

SDA (シリアル・データ)ピンと SCL (シリアル・クロック)ピンはオープン・ドレインであるため、プルアップ抵抗が必要です。正しい抵抗値については、 $I^2C$  仕様バージョン 2.1 を参照してください。

表9 ピン説明

| Pin Name                    | Туре                                                        | Function                                                    | Driver<br>Type <sup>1</sup> |  |

|-----------------------------|-------------------------------------------------------------|-------------------------------------------------------------|-----------------------------|--|

| Memory Interface            |                                                             |                                                             |                             |  |

| ADDR19-1                    | О                                                           | Address Bus for Async Access                                | A                           |  |

| DATA15-0                    | I/O                                                         | Data Bus for Async/Sync Access                              | A                           |  |

| ABE1-0/SDQM1-0              | О                                                           | Byte Enables/Data Masks for Async/Sync Access               | А                           |  |

| BR                          | 1                                                           | Bus Request (This pin should be pulled high when not used.) |                             |  |

| BG                          | О                                                           | Bus Grant                                                   | A                           |  |

| BGH                         | О                                                           | Bus Grant Hang                                              | А                           |  |

| Asynchronous Memory Control |                                                             |                                                             |                             |  |

| AMS3-0                      | 0                                                           | Bank Select                                                 | Α                           |  |

| ARDY                        | 1                                                           | Hardware Ready Control                                      |                             |  |

| AOE                         | О                                                           | Output Enable                                               | A                           |  |

| ARE                         | О                                                           | Read Enable                                                 | A                           |  |

| AWE                         | О                                                           | Write Enable                                                | А                           |  |

| Synchronous Memory Control  |                                                             |                                                             |                             |  |

| SRAS                        | О                                                           | Row Address Strobe                                          | А                           |  |

| SCAS                        | О                                                           | Column Address Strobe                                       | A                           |  |

| SWE O Write Enal            |                                                             | Write Enable                                                | A                           |  |

| SCKE                        | O Clock Enable (This pin is three-stated during hibernate.) |                                                             |                             |  |

| CLKOUT                      | О                                                           | Clock Output                                                | В                           |  |

| SA10                        | О                                                           | A10 Pin                                                     | A                           |  |

| SMS                         | О                                                           | Bank Select                                                 | A                           |  |

### 表 9.ピン説明(続き)

| Pin Name                                                                                          | Туре | Function                                                                                                                     | Driver<br>Type <sup>1</sup> |

|---------------------------------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Port F: GPIO/UART1–0/Timer7–0/SPI/<br>External DMA Request/PPI<br>(* = High Source/High Sink Pin) |      |                                                                                                                              |                             |

| PF0* – GPIO/ <i>UART0 TX/DMAR0</i>                                                                | I/O  | GPIO/UARTO Transmit/DMA Request 0                                                                                            | С                           |

| PF1* – GPIO/ <i>UARTO RX/DMAR1/TACI1</i>                                                          | I/O  | GPIO/UARTO Receive/DMA Request 1/Timer1 Alternate Input Capture                                                              | С                           |

| PF2* – GPIO/ <i>UART1 TX/TMR7</i>                                                                 | I/O  | GPIO/UART1 Transmit/Timer7                                                                                                   | С                           |

| PF3* – GPIO/ <i>UART1 RX/TMR6/TACI6</i>                                                           | I/O  | GPIO/UART1 Receive/Timer6/Timer6 Alternate Input Capture                                                                     | С                           |

| PF4* – GPIO/ <i>TMR5/SPI SSEL6</i>                                                                | I/O  | GPIO/Timer5/SPI Slave Select Enable 6                                                                                        | С                           |

| PF5* – GPIO/TMR4/SPI SSEL5                                                                        | I/O  | GPIO/Timer4/SPI Slave Select Enable 5                                                                                        | С                           |

| PF6* – GPIO/TMR3/SPI SSEL4                                                                        | I/O  | GPIO/Timer3/SPI Slave Select Enable 4                                                                                        | С                           |

| PF7* – GPIO/ <i>TMR2/PPI FS3</i>                                                                  | I/O  | GPIO/Timer2/PPI Frame Sync 3                                                                                                 | С                           |

| PF8 – GPIO/TMR1/PPI FS2                                                                           | I/O  | GPIO/Timer1/PPI Frame Sync 2                                                                                                 | С                           |

| PF9 – GPIO/ <i>TMR0/PPI FS1</i>                                                                   | I/O  | GPIO/Timer0/PPI Frame Sync 1                                                                                                 | С                           |

| PF10 – GPIO/SPI SSEL1                                                                             | I/O  | GPIO/SPI Slave Select Enable 1                                                                                               | С                           |

| PF11 – GPIO/ <i>SPI MOSI</i>                                                                      | I/O  | GPIO/SPI Master Out Slave In                                                                                                 | С                           |

| PF12 – GPIO/ <i>SPI MISO</i>                                                                      | I/O  | GPIO/SPI Master In Slave Out (This pin should be pulled high through a 4.7 k $\Omega$ resistor if booting via the SPI port.) | С                           |

| PF13 – GPIO/ <i>SPI SCK</i>                                                                       | I/O  | GPIO/SPI Clock                                                                                                               | D                           |

| PF14 – GPIO/SPI SS/TACLKO                                                                         | I/O  | GPIO/SPI Slave Select/Alternate Timer0 Clock Input                                                                           | С                           |

| PF15 – GPIO/ <i>PPI CLK/TMRCLK</i>                                                                | I/O  | GPIO/PPI Clock/External Timer Reference                                                                                      | С                           |

| Port G: GPIO/PPI/SPORT1                                                                           |      |                                                                                                                              |                             |

| PG0 – GPIO/ <i>PPI D0</i>                                                                         | I/O  | GPIO/PPI Data 0                                                                                                              | С                           |

| PG1 – GPIO/ <i>PPI D1</i>                                                                         | I/O  | GPIO/PPI Data 1                                                                                                              | С                           |

| PG2 – GPIO/ <i>PPI D2</i>                                                                         | I/O  | GPIO/PPI Data 2                                                                                                              | С                           |

| PG3 – GPIO/ <i>PPI D3</i>                                                                         | I/O  | GPIO/PPI Data 3                                                                                                              | С                           |

| PG4 – GPIO/ <i>PPI D4</i>                                                                         | I/O  | GPIO/PPI Data 4                                                                                                              | С                           |

| PG5 – GPIO/ <i>PPI D5</i>                                                                         | I/O  | GPIO/PPI Data 5                                                                                                              | С                           |

| PG6 – GPIO/ <i>PPI D6</i>                                                                         | I/O  | GPIO/PPI Data 6                                                                                                              | С                           |

| PG7 – GPIO/ <i>PPI D7</i>                                                                         | I/O  | GPIO/PPI Data 7                                                                                                              | С                           |

| PG8 – GPIO/ <i>PPI D8/DR1SEC</i>                                                                  | I/O  | GPIO/PPI Data 8/SPORT1 Receive Data Secondary                                                                                | С                           |

| PG9 – GPIO/ <i>PPI D9/DT1SEC</i>                                                                  | I/O  | GPIO/PPI Data 9/SPORT1 Transmit Data Secondary                                                                               | С                           |

| PG10 – GPIO/PPI D10/RSCLK1                                                                        | I/O  | GPIO/PPI Data 10/SPORT1 Receive Serial Clock                                                                                 | D                           |

| PG11 – GPIO/PPI D11/RFS1                                                                          | I/O  | GPIO/PPI Data 11/SPORT1 Receive Frame Sync                                                                                   | С                           |

| PG12 – GPIO/PPI D12/DR1PRI                                                                        | I/O  | GPIO/PPI Data 12/SPORT1 Receive Data Primary                                                                                 | С                           |

| PG13 – GPIO/PPI D13/TSCLK1                                                                        | I/O  | GPIO/PPI Data 13/SPORT1 Transmit Serial Clock                                                                                | D                           |

| PG14 – GPIO/PPI D14/TFS1                                                                          | I/O  | GPIO/PPI Data 14/SPORT1 Transmit Frame Sync                                                                                  | С                           |

| PG15 – GPIO/PPI D15/DT1PRI                                                                        | I/O  | GPIO/PPI Data 15/SPORT1 Transmit Data Primary                                                                                | С                           |

### 表 9.ピン説明(続き)

| Pin Name                                                                   | Туре | Function                                                                                                                          | Driver<br>Type <sup>1</sup> |

|----------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Port H: GPIO/10/100 Ethernet MAC (On ADSP-BF534, these pins are GPIO only) |      |                                                                                                                                   |                             |

| PH0 – GPIO/ <i>ETxD0</i>                                                   | I/O  | GPIO/Ethernet MII or RMII Transmit D0                                                                                             | E                           |

| PH1 – GPIO/ <i>ETxD1</i>                                                   | I/O  | GPIO/Ethernet MII or RMII Transmit D1                                                                                             | E                           |

| PH2 – GPIO/ <i>ETxD2</i>                                                   | I/O  | GPIO/Ethernet MII Transmit D2                                                                                                     | Е                           |

| PH3 – GPIO/ <i>ETxD3</i>                                                   | I/O  | GPIO/Ethernet MII Transmit D3                                                                                                     | E                           |

| PH4 – GPIO/ <i>ETxEN</i>                                                   | I/O  | GPIO/Ethernet MII or RMII Transmit Enable                                                                                         | Е                           |

| PH5 – GPIO/ <i>MII TxCLK/RMII REF_CLK</i>                                  | I/O  | GPIO/Ethernet MII Transmit Clock/RMII Reference Clock                                                                             | Е                           |

| PH6 – GPIO/MII PHYINT/RMII MDINT                                           | I/O  | GPIO/Ethernet MII PHY Interrupt/RMII Management Data Interrupt (This pin should be pulled high when used as a hibernate wake-up.) | E                           |

| PH7 – GPIO/ <i>COL</i>                                                     | I/O  | GPIO/Ethernet Collision                                                                                                           | Е                           |

| PH8 – GPIO/ <i>ERxD0</i>                                                   | I/O  | GPIO/Ethernet MII or RMII Receive D0                                                                                              | Е                           |

| PH9 – GPIO/ <i>ERxD1</i>                                                   | I/O  | GPIO/Ethernet MII or RMII Receive D1                                                                                              | Е                           |

| PH10 – GPIO/ERxD2                                                          | I/O  | GPIO/Ethernet MII Receive D2                                                                                                      | E                           |

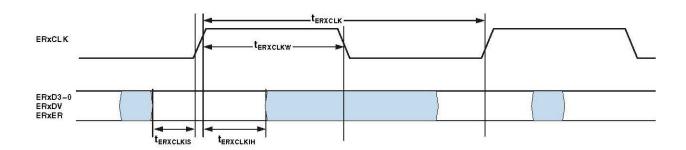

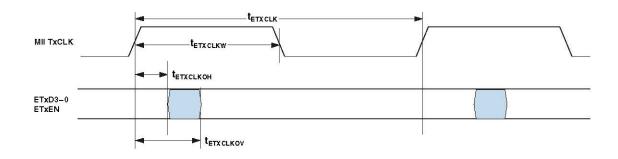

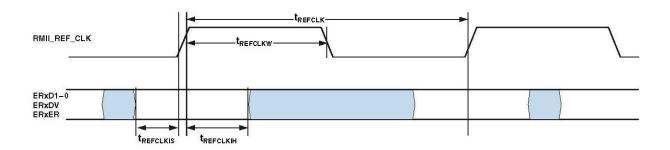

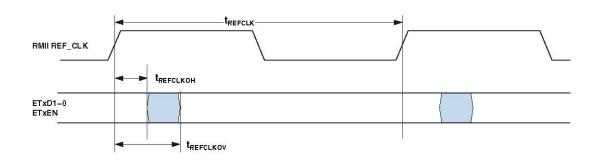

| PH11 – GPIO/ <i>ERxD3</i>                                                  | I/O  | GPIO/Ethernet MII Receive D3                                                                                                      | E                           |