# ANALOG トランス・ドライバ内蔵の高速絶縁型 DEVICES RS-485トランシーバ

# **ADM2485**

#### 特長

半二重の絶縁型RS-485トランシーバ 外部トランス用の発振器ドライバを内蔵

PROFIBUS®に準拠

ANSI/TIA/EIA RS-485-A-98とISO 8482:1987 (E)に準拠

データレート:16Mbps 5V動作または3.3V動作(V<sub>DD1</sub>) バス上のノード数:50

高コモンモード過渡耐圧:25kV/µs以上 絶縁されたDE OUT ステータス出力 サーマル・シャットダウン保護機能

安全性規格の認定:

UL認定: UL1577に準拠し1分間2500V<sub>RMS</sub>

VDE適合認定

DIN V VDE V 0884-10 (VDE V 0884-10):2006-12

絶縁を強化、V<sub>IORM</sub>=560V(ピーク)

動作温度範囲:-40~+85℃ 幅広の16ピンSOICパッケージ

## アプリケーション

絶縁型RS-485/RS-422インターフェース **PROFIBUS**ネットワーク 工業用フィールド・ネットワーク マルチポイント・データ転送システム

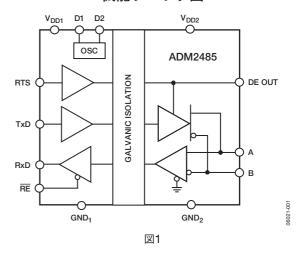

#### 機能ブロック図

#### 概要

ADM2485差動バス・トランシーバは、マルチポイント・バス の伝送ラインを使用する双方向データ通信向けにデザインされ た特殊小型トランス絶縁を内蔵したICです。平衡伝送ライン向 けにデザインされた本製品は、ANSI/TIA/EIA RS-485-A-98お よびISO 8482:1987(E)に準拠しています。

ADM2485はアナログ・デバイセズのiCoupler®技術を採用し、 3チャンネル・アイソレータ、スリーステート差動ライン・ド ライバ、差動入力レシーバをシングル・パッケージに組み込ん でいます。内蔵の発振器は外部トランスを駆動するための1対 の矩形波を出力し、外部トランスに絶縁電源を供給します。デ バイスのシステム側は5Vまたは3.3V電源で動作しますが、バ ス側はシステムから絶縁された5V電源で動作します。

ADM2485ドライバは、アクティブ・ハイのイネーブル・ピン を持っています。ドライバの差動出力とレシーバの差動入力は 内部で接続され、差動入出力ポートを構成しています(半二重)。 この入出力ポートは、ドライバがディスエーブルされたとき、 または $V_{\rm DD1}$ または $V_{\rm DD2}$ =0Vのとき、バスの負荷を最小にしま す。また、受信出力を高インピーダンス状態にするアクティ ブ・ハイのレシーバ・ディスエーブル機能も用意されていま す。

ADM2485には電流制限機能とサーマル・シャットダウン機能 があり、出力の短絡やバス競合時の過度な電力消費からデバイ スを保護します。工業用温度範囲で完全仕様規定され、16ピン のワイド幅SOICパッケージを採用しています。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の 利用に関して、あるいは利用によって生じる騙こ者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有 に属します

。 ータシートはREVISIONが古い場合があります。最新の内容については、英語版をご参照ください。 © 2007 Analog Devices, Inc. All rights reserved.

REV. A

社/ 〒105-6891

東京都港区海岸1-16-1 ニューピア竹芝サウスタワービル 電話03 (5402) 8200

大阪営業所/〒532-0003 大阪府大阪市淀川区宮原3-5-36 新大阪MTビル2号 電話06(6350)6868

# 目次

| 特長             | 代表的な性能特性       | 10 |

|----------------|----------------|----|

| アプリケーション1      | テスト回路          | 13 |

| 機能ブロック図1       | 回路の説明          | 14 |

| 概要             | 電気的絶縁          | 14 |

| 改訂履歴2          | 真理値表           | 14 |

| 仕様             | サーマル・シャットダウン   | 14 |

| タイミング仕様5       | レシーバのフェイルセーフ入力 | 14 |

| パッケージ特性6       | 磁界耐性           |    |

| 規制の情報6         | アプリケーション情報     | 16 |

| 絶縁および安全に関する仕様6 | PCボードのレイアウト    | 16 |

| VDE 0884-2絶縁仕様 | トランス電源         | 16 |

| 絶対最大定格8        | アプリケーション図      | 16 |

| ESDに関する注意8     | 外形寸法           | 17 |

| ピン配置とピン機能の説明9  | オーダー・ガイド       | 17 |

|                |                |    |

## 改訂履歴

#### 12/07—Rev. 0 to Rev. A

| 1/07—Revision 0. Initial Version                         |           |

|----------------------------------------------------------|-----------|

| Updated Outline Dimensions                               | 17        |

| Changes to PCB Section and Figure 34                     | 16        |

| Changes to VDE 0884-2 Insulation Characteristics Section | 7         |

| Changes to Table 4                                       | 6         |

| Changes to Features Section                              | 1         |

| Updated Format                                           | Jniversal |

# 仕様

特に指定のない限り、2.7 $\leq$ V<sub>DD1</sub> $\leq$ 5.5V、4.75V $\leq$ V<sub>DD2</sub> $\leq$ 5.25V、 $T_A$ = $T_{MIN}$  $\sim$  $T_{MAX}$  $\circ$

表1

| Parameter                                                    | Min                    | Тур                      | Max                                | Unit | Test Conditions/Comments                                      |

|--------------------------------------------------------------|------------------------|--------------------------|------------------------------------|------|---------------------------------------------------------------|

| DRIVER                                                       |                        |                          |                                    |      |                                                               |

| Differential Outputs                                         |                        |                          |                                    |      |                                                               |

| Differential Output Voltage, $V_{\text{OD}}$                 |                        |                          | 5                                  | V    | $R = \infty$ , see Figure 21                                  |

|                                                              | 2.1                    |                          | 5                                  | V    | $R = 50 \Omega$ (RS-422), see Figure 21                       |

|                                                              | 2.1                    |                          | 5                                  | V    | $R = 27 \Omega$ (RS-485), see Figure 21                       |

|                                                              | 2.1                    |                          | 5                                  | V    | VTST = $-7$ V to $+12$ V, $V_{DD1} \ge 4.75$ V, see Figure 22 |

| $\Delta  V_{OD} $ for Complementary Output States            |                        |                          | 0.2                                | V    | $R = 27 \Omega$ or $50 \Omega$ , see Figure 21                |

| Common-Mode Output Voltage, $V_{OC}$                         |                        |                          | 3                                  | V    | $R = 27 \Omega \text{ or } 50 \Omega, \text{ see Figure } 21$ |

| $\Delta  V_{OC} $ for Complementary Output States            |                        |                          | 0.2                                | V    | $R = 27 \Omega \text{ or } 50 \Omega, \text{ see Figure } 21$ |

| Output Short-Circuit Current, V <sub>OUT</sub> = High        | 60                     |                          | 200                                | mA   | $-7 \text{ V} \le \text{V}_{\text{OUT}} \le +12 \text{ V}$    |

| Output Short-Circuit Current, $V_{OUT} = Low$                | 60                     |                          | 200                                | mA   | $-7 \text{ V} \le \text{V}_{\text{OUT}} \le +12 \text{ V}$    |

| Bus Enable Output                                            |                        |                          |                                    |      |                                                               |

| Output High Voltage                                          | $V_{DD2} - 0.1$        |                          |                                    | V    | $I_{ODE} = 20 \mu A$                                          |

|                                                              | $V_{DD2} - 0.3$        | $V_{\mathrm{DD2}}-0.1$   |                                    | V    | $I_{ODE} = 1.6 \text{ mA}$                                    |

|                                                              | $V_{DD2} - 0.4$        | $V_{\mathrm{DD2}} - 0.2$ |                                    | V    | $I_{ODE} = 4 \text{ mA}$                                      |

| Output Low Voltage                                           |                        |                          | 0.1                                | V    | $I_{ODE} = -20 \mu A$                                         |

|                                                              |                        | 0.1                      | 0.3                                | V    | $I_{ODE} = -1.6 \text{ mA}$                                   |

|                                                              |                        | 0.2                      | 0.4                                | V    | $I_{ODE} = -4 \text{ mA}$                                     |

| Logic Inputs                                                 |                        |                          |                                    |      |                                                               |

| Input High Voltage                                           | $0.7~\mathrm{V_{DD1}}$ |                          |                                    | V    | TxD, RTS, RE                                                  |

| Input Low Voltage                                            |                        |                          | $0.25\;V_{\scriptscriptstyle DD1}$ | V    | TxD, RTS, RE                                                  |

| CMOS Logic Input Current (TxD, RTS, $\overline{\text{RE}}$ ) | -10                    | +0.01                    | +10                                | μΑ   | $TxD$ , $RTS$ , $\overline{RE} = V_{DD1}$ or $0 \text{ V}$    |

| RECEIVER                                                     |                        |                          |                                    |      |                                                               |

| Differential Inputs                                          |                        |                          |                                    |      |                                                               |

| Differential Input Threshold Voltage, $V_{TH}$               | -200                   |                          | +200                               | mV   | $-7 \text{ V} \le \text{V}_{\text{CM}} \le +12 \text{V}$      |

| Input Hysteresis                                             |                        | 70                       |                                    | mV   | $-7 \text{ V} \le \text{V}_{\text{CM}} \le +12 \text{V}$      |

| Input Resistance (A, B)                                      | 20                     | 30                       |                                    | kΩ   | $-7 \text{ V} \le \text{V}_{\text{CM}} \le +12 \text{V}$      |

| Input Current (A, B)                                         |                        |                          | 0.6                                | mA   | $V_{IN} = +12 \text{ V}$                                      |

|                                                              |                        |                          | -0.35                              | mA   | $V_{IN} = -7 \text{ V}$                                       |

| RxD Logic Output                                             |                        |                          |                                    |      |                                                               |

| Output High Voltage                                          | $V_{DD1} - 0.1$        |                          |                                    | V    | $I_{OUT} = +20 \mu A, V_A - V_B = +0.2 V$                     |

|                                                              | $V_{\rm DD1} - 0.4$    | $V_{\mathrm{DD1}}-0.2$   |                                    | V    | $I_{OUT} = +1.5 \text{ mA}, V_A - V_B = +0.2 \text{ V}$       |

| Output Low Voltage                                           |                        |                          | 0.1                                | V    | $I_{OUT} = -20 \mu A, V_A - V_B = -0.2 V$                     |

|                                                              |                        | 0.2                      | 0.4                                | V    | $I_{OUT} = -4 \text{ mA}, V_A - V_B = -0.2 \text{ V}$         |

| Output Short-Circuit Current                                 | 7                      |                          | 85                                 | mA   | $V_{OUT} = GND \text{ or } V_{CC}$                            |

| Tristate Output Leakage Current                              |                        |                          | ±1                                 | μA   | $0.4 \text{ V} \le \text{V}_{\text{OUT}} \le 2.4 \text{ V}$   |

| TRANSFORMER DRIVER                                           |                        |                          |                                    |      |                                                               |

| Oscillator Frequency                                         | 400                    | 500                      | 600                                | kHz  | $V_{\rm DD1} = 5.5 \text{ V}$                                 |

|                                                              | 230                    | 330                      | 430                                | kHz  | $V_{DD1} = 3.3 \text{ V}$                                     |

| Switch-On Resistance                                         |                        | 0.5                      | 1.5                                | Ω    |                                                               |

| Start-Up Voltage                                             |                        | 2.2                      | 2.5                                | V    |                                                               |

REV. A -3-

| Parameter                                    | Min | Тур  | Max  | Unit  | Test Conditions/Comments                                                                  |

|----------------------------------------------|-----|------|------|-------|-------------------------------------------------------------------------------------------|

| POWER SUPPLY CURRENT                         |     |      |      |       |                                                                                           |

| Logic Side                                   |     |      | 2.5  | mA    | $RTS = 0 \text{ V}, V_{DD1} = 5.5 \text{ V}$                                              |

|                                              |     | 2.3  |      | mA    | 2.5 Mbps, $V_{DD1} = 5.5 \text{ V}$ , see Figure 23                                       |

|                                              |     | 5.0  | 6.5  | mA    | 16 Mbps, $V_{DD1} = 5.5 \text{ V}$ , see Figure 23                                        |

|                                              |     | 1.26 |      | mA    | $RTS = 0 \text{ V}, \text{ V}_{DD1} = 3.3 \text{ V}$                                      |

|                                              |     | 1.5  |      | mA    | $2.5 \text{ Mbps}$ , $V_{DD1} = 3.3 \text{ V}$ , see Figure 23                            |

|                                              |     | 2.9  |      | mA    | 16 Mbps, $V_{DD1} = 3.3 \text{ V}$ , see Figure 23                                        |

| Bus Side                                     |     | 1.7  | 2.5  | mA    | RTS = 0 V                                                                                 |

|                                              |     | 49.0 |      | mA    | 2.5 Mbps, RTS = $V_{DD1}$ , see Figure 23 for load conditions                             |

|                                              |     | 55.0 | 75.0 | mA    | 16 Mbps, RTS = $V_{DD1}$ , see Figure 23 for load conditions                              |

| COMMON-MODE TRANSIENT IMMUNITY <sup>1</sup>  | 25  |      |      | kV/μs | Transient magnitude = $800 \text{ V}$ , $V_{CM} = 1 \text{ kV}$                           |

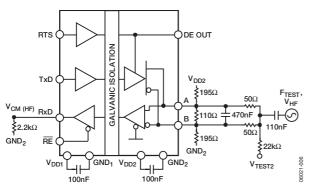

| HIGH FREQUENCY COMMON-MODE<br>NOISE IMMUNITY |     | 100  |      | mV    | $V_{HF}$ = +5 V, -2 V < $V_{TEST2}$ < +7 V,<br>1 MHz < $f_{TEST}$ < 50 MHz, see Figure 24 |

<sup>「</sup>CMは、仕様準拠動作を維持しているときのコモンモード電圧の最大スルーレートです。 $V_{CM}$ は、システム側とバス側との間のコモンモードの電位差です。過渡電圧振幅は、コモンモードの平衡が失われる範囲を表します。コモンモード電圧スルーレートは、立上がりおよび立下がりの両コモンモード電圧エッジに適用されます。

### タイミング仕様

特に指定のない限り、2.7 $\leq$ V<sub>DD1</sub> $\leq$ 5.5V、4.75V $\leq$ V<sub>DD2</sub> $\leq$ 5.25V、 $T_A$ = $T_{MIN}$  $\sim$  $T_{MAX}$  $\circ$

#### 表2

| Parameter                                                        | Min | Тур | Max | Unit | Test Conditions/Comments                                                                  |

|------------------------------------------------------------------|-----|-----|-----|------|-------------------------------------------------------------------------------------------|

| DRIVER                                                           |     |     |     |      |                                                                                           |

| Maximum Data Rate                                                | 16  |     |     | Mbps |                                                                                           |

| Propagation Delay Input-to-Output                                |     |     |     |      |                                                                                           |

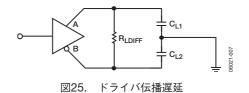

| $t_{\rm PLH},t_{\rm PHL}$                                        | 25  | 45  | 55  | ns   | $R_{LDIFF} = 54 \Omega$ , $C_{L1} = C_{L2} = 100 \text{ pF}$ , see Figure 25              |

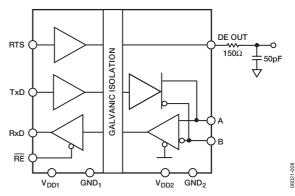

| RTS-to-DE OUT Propagation Delay                                  | 20  | 35  | 55  | ns   | See Figure 26                                                                             |

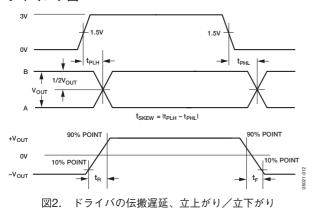

| Driver Output-to- $\overline{\text{Output}}$ , $t_{\text{SKEW}}$ |     | 2   | 5   | ns   | $R_{LDIFF} = 54 \Omega$ , $C_{L1} = C_{L2} = 100 \text{ pF}$ , see Figure 2 and Figure 25 |

| Rise/Fall Time, $t_R$ , $t_F$                                    |     | 5   | 15  | ns   | $R_{LDIFF} = 54 \Omega$ , $C_{L1} = C_{L2} = 100 \text{ pF}$ , see Figure 2 and Figure 25 |

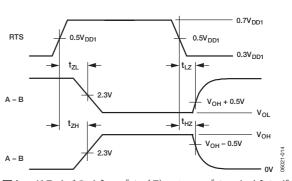

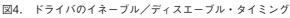

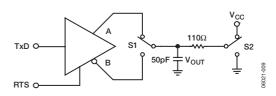

| Enable Time                                                      |     | 43  | 53  | ns   | See Figure 4 and Figure 27                                                                |

| Disable Time                                                     |     | 43  | 55  | ns   | See Figure 4 and Figure 27                                                                |

| Enable Skew, $ t_{AZH} - t_{BZL} $ , $ t_{AZL} - t_{BZH} $       |     | 1   | 3   | ns   | See Figure 4 and Figure 27                                                                |

| Disable Skew, $ t_{AZH} - t_{BZL} $ , $ t_{AZL} - t_{BZH} $      |     | 2   | 5   | ns   | See Figure 4 and Figure 27                                                                |

| RECEIVER                                                         |     |     |     |      |                                                                                           |

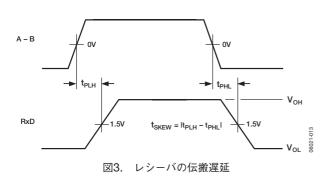

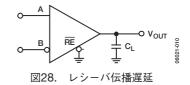

| Propagation Delay, t <sub>PLH</sub> , t <sub>PHL</sub>           | 25  | 45  | 55  | ns   | $C_L = 15 \text{ pF}$ , see Figure 3 and Figure 28                                        |

| Differential Skew, t <sub>SKEW</sub>                             |     |     | 5   | ns   | $C_L = 15 \text{ pF}$ , see Figure 3 and Figure 28                                        |

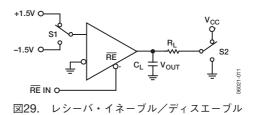

| Enable Time                                                      |     | 3   | 13  | ns   | $R_L = 1 \text{ k}\Omega$ , $C_L = 15 \text{ pF}$ , see Figure 5 and Figure 29            |

| Disable Time                                                     |     | 3   | 13  | ns   | $R_L = 1 \text{ k}\Omega$ , $C_L = 15 \text{ pF}$ , see Figure 5 and Figure 29            |

#### タイミング図

図5. レシーバのイネーブル/ディスエーブル・タイミング

REV. A — 5 —

# パッケージ特性

#### 表3

| Parameter                                     | Symbol            | Min Typ | Max | Unit | Test Conditions                                     |

|-----------------------------------------------|-------------------|---------|-----|------|-----------------------------------------------------|

| Resistance (Input-to-Output) <sup>1</sup>     | R <sub>I-O</sub>  | 1012    |     | Ω    |                                                     |

| Capacitance (Input-to-Output) <sup>1</sup>    | $C_{\text{I-O}}$  | 3       |     | pF   | f = 1  MHz                                          |

| Input Capacitance <sup>2</sup>                | $C_{I}$           | 4       |     | pF   |                                                     |

| Input IC Junction-to-Case Thermal Resistance  | $\theta_{ m JCI}$ | 33      |     | °C/W | Thermocouple located at center of package underside |

| Output IC Junction-to-Case Thermal Resistance | $\theta_{ m JCO}$ | 28      |     | °C/W | Thermocouple located at center of package underside |

<sup>1</sup> デバイスは2端子デバイスと見なします。ピン1~8を相互接続し、ピン9~16を相互接続します。 2 入力容量は、任意の入力データ・ピンとグラウンド間の容量です。

## 規制の情報

#### 表4. ADM2485の認定

| Organization | Approval Type                                                                         | Notes                                                                                                                                                                                   |

|--------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UL           | Recognized under the Component Recognition Program of Underwriters Laboratories, Inc. | In accordance with UL 1577, each ADM2485 is proof tested by applying an insulation test voltage ≥ 3000 V rms for 1 second                                                               |

|              |                                                                                       | (current leakage detection limit = $5 \mu A$ ).                                                                                                                                         |

| VDE          | Certified according to DIN V VDE V 0884-10 (VDE V 0884-10): 2006-12                   | In accordance with DIN V VDE V 0884-10, each ADM2485 is proof tested by applying an insulation test voltage $\geq$ 1050 V peak for 1 second (partial discharge detection limit = 5 pC). |

# 絶縁および安全に関する仕様

#### 表5

| Parameter                                        | Symbol | Value     | Unit  | Conditions                                                                       |

|--------------------------------------------------|--------|-----------|-------|----------------------------------------------------------------------------------|

| Rated Dielectric Insulation Voltage              |        | 2500      | V rms | 1-minute duration                                                                |

| Minimum External Air Gap (External Clearance)    | L(I01) | 5.15 min  | mm    | Measured from input terminals to output terminals, shortest distance through air |

| Minimum External Tracking (Creepage)             | L(I02) | 5.5 min   | mm    | Measured from input terminals to output terminals, shortest distance along body  |

| Minimum Internal Gap (Internal Clearance)        |        | 0.017 min | mm    | Insulation distance through insulation                                           |

| Tracking Resistance (Comparative Tracking Index) | CTI    | >175      | V     | DIN IEC 112/VDE 0303-1                                                           |

| Isolation Group                                  |        | IIIa      |       | Material Group (DIN VDE 0110: 1989-01,<br>Table 1)                               |

## VDE 0884-2絶縁仕様

このアイソレータは、安全規定データ範囲内でのみ基本電気アイソレーションに適合します。保護回路を使用して、安全データを維持 する必要があります。

パッケージ上のアスタリスク\*は、DIN V VDE V 0884-10認定済みを表します。

#### 表6

| Description                                                                                                                       | Symbol                 | Characteristic | Unit         |

|-----------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------|--------------|

| Installation Classification per DIN VDE 0110 for Rated Mains Voltage                                                              |                        |                |              |

| ≤150 V rms                                                                                                                        |                        | I to IV        |              |

| ≤300 V rms                                                                                                                        |                        | I to III       |              |

| ≤400 V rms                                                                                                                        |                        | I to II        |              |

| Climatic Classification                                                                                                           |                        | 40/85/21       |              |

| Pollution Degree (DIN VDE 0110: 1989-01, Table 1)                                                                                 |                        | 2              |              |

| Maximum Working Insulation Voltage                                                                                                | V <sub>IORM</sub>      | 560            | V peak       |

| Input-to-Output Test Voltage                                                                                                      | V <sub>PR</sub>        |                |              |

| Method B1: $V_{IORM} \times 1.875 = V_{PR}$ , 100% Production Tested, $t_m = 1$ sec, Partial Discharge < 5 pC                     |                        | 1050           | V peak       |

| Method A (After Environmental Tests, Subgroup 1): $V_{IORM} \times 1.6 = V_{PR}$ , $t_m = 60$ sec, Partial Discharge <5 pC        |                        | 896            | V peak       |

| Method A (After Input and/or Safety Test, Subgroup 2/3): $V_{IORM} \times 1.2 = V_{PR}$ , $t_m = 60$ sec, Partial Discharge <5 pC |                        | 672            | V peak       |

| Highest Allowable Overvoltage <sup>1</sup>                                                                                        | V <sub>TR</sub>        | 4000           | V peak       |

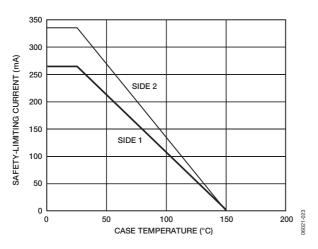

| Safety-Limiting Values <sup>2</sup>                                                                                               |                        |                |              |

| Case Temperature                                                                                                                  | T <sub>s</sub>         | 150            | $\mathbb{C}$ |

| Input Current                                                                                                                     | I <sub>S, INPUT</sub>  | 265            | mA           |

| Output Current                                                                                                                    | I <sub>S, OUTPUT</sub> | 335            | mA           |

| Insulation Resistance at T <sub>S</sub> <sup>3</sup>                                                                              | R <sub>s</sub>         | >109           | Ω            |

REV. A -7-

<sup>-</sup> 過渡過電圧、 $t_{\rm TR}$ =10sec 2 安全規定値は故障時に許容される最大値です。サーマル・デレーティング・カーブについては図14参照。 3  $V_{\rm to}$  = 500 V

# 絶対最大定格

特に指定のない限り、 $T_A=25$   $\mathbb{C}$ 。すべての電圧は、それぞれの グラウンドを基準とします。

#### 表7

| Parameter                            | Rating                                             |

|--------------------------------------|----------------------------------------------------|

| $V_{\mathrm{DD1}}$                   | -0.5 V to +6 V                                     |

| $ m V_{DD2}$                         | -0.5 V to +6 V                                     |

| Digital Input Voltage                | $-0.5 \text{ V to V}_{\text{DD1}} + 0.5 \text{ V}$ |

| (RTS, RE, TxD)                       |                                                    |

| Digital Output Voltage               |                                                    |

| RxD                                  | $-0.5 \text{ V to V}_{\text{DD1}} + 0.5 \text{ V}$ |

| DE OUT                               | $-0.5 \text{ V to V}_{DD2} + 0.5 \text{ V}$        |

| D1, D2                               | 13 V                                               |

| Driver Output/Receiver Input Voltage | −9 V to +14 V                                      |

| Operating Temperature Range          | -40°C to +85°C                                     |

| Storage Temperature Range            | -55°C to +150°C                                    |

| Average Output Current per Pin       | -35 mA to +35 mA                                   |

| $\theta_{JA}$ Thermal Impedance      | 73℃/W                                              |

| Lead Temperature                     |                                                    |

| Soldering (10 sec)                   | 300℃                                               |

| Vapor Phase (60 sec)                 | 215℃                                               |

| Infrared (15 sec)                    | 220℃                                               |

|                                      |                                                    |

左記の絶対最大定格を超えるストレスを加えると、デバイスに 恒久的な損傷を与えることがあります。この規定はストレス定 格のみを指定するものであり、この仕様の動作セクションに記 載する規定値以上でのデバイス動作を定めたものではありませ ん。デバイスを長時間絶対最大定格状態に置くと、デバイスの 信頼性に影響を与えることがあります。

#### ESDに関する注意

ESD (静電放電) の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検出されないまま放電することがあります。本製品は当社独自の特許技術であるESD保護回路を内蔵してはいますが、デバイスで高エネルギーの静電放電が発生した場合、損傷を生じる可能性があります。性能劣化や機能低下を防止するため、ESDに対して適切な予防措置をとることが推奨されます。

—8— REV. A

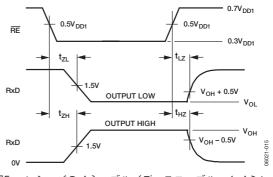

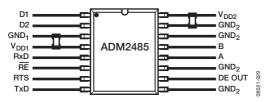

# ピン配置とピン機能の説明

表8. ピン機能の説明

| ピン番号          | 記号               | 機能                                                                                                                                                  |

|---------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | D1               | トランス・ドライバ端子1                                                                                                                                        |

| 2             | D2               | トランス・ドライバ端子2                                                                                                                                        |

| 3             | GND <sub>1</sub> | グラウンド (システム側)                                                                                                                                       |

| 4             | $V_{DD1}$        | 電源(システム側): $3.3V$ または $5V$ 。 $GND_1$ にデカップリング・コンデンサを接続します。コンデンサ値は、 $0.01\mu F \sim 0.1\mu F$ の値とします。                                                |

| 5             | RxD              | レシーバの出力データ。イネーブルの場合、 $RxD$ は $(A-B)>200mV$ のときハイ $\nu$ ベル、 $(A-B)<-200mV$ のときローレベルになります。レシーバがディスエーブルのとき、すなわち $RE$ がハイレベルに駆動されたとき、出力はスリーステート状態になります。 |

| 6             | RE               | レシーバのイネーブル入力。アクティブ・ロー入力。この入力をローレベルにするとレシーバがイネーブルされ、ハイレベルにするとレシーバがディスエーブルされます。                                                                       |

| 7             | RTS              | ドライバのイネーブル入力。この入力をハイレベルにするとドライバがイネーブルされ、ローレベルにするとドライバがディスエーブルされます。                                                                                  |

| 8             | TxD              | ドライバ入力。ドライバから送信されるデータはこのピンに入力されます。                                                                                                                  |

| 9, 11, 14, 15 | GND <sub>2</sub> | グラウンド(バス側)                                                                                                                                          |

| 10            | DE OUT           | ドライバ・イネーブル・ステータス出力                                                                                                                                  |

| 12            | A                | 非反転ドライバ出力/レシーバ入力。ドライバがディスエーブルのとき、または $V_{\rm DD1}$ がパワーダウンのとき、ピン $A$ は高インピーダンス状態になり、バスの過負荷を回避します。                                                   |

| 13            | В                | 反転ドライバ出力/レシーバ入力。ドライバがディスエーブルのとき、または $V_{DD1}$ が $V_{DD2}$ がパワーダウンのとき、ピンBは高インピーダンス状態になって、バスの過負荷を回避します。                                               |

| 16            | $V_{ m DD2}$     | 電源(バス側): $5V$ 絶縁電源。 $GND_2$ にデカップリング・コンデンサを接続します。コンデンサ値は、 $0.01\mu F \sim 0.1\mu F$ の値とします。                                                         |

REV. A — 9 —

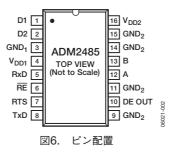

# 代表的な性能特性

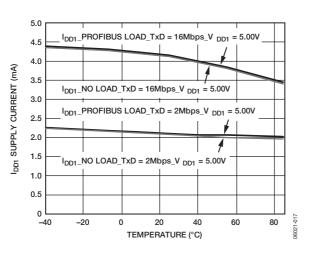

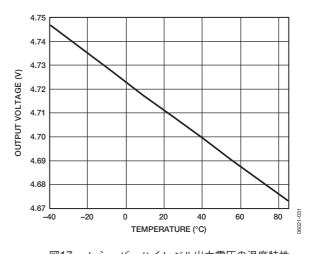

図7. 無負荷時電源電流の温度特性

図8. システム側電源電流 (I<sub>DD1</sub>=1mA) の温度特性

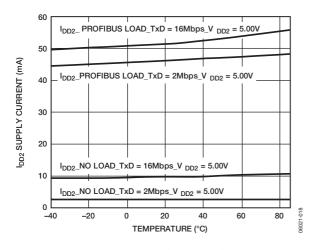

図9. バス側電源電流(I<sub>DD2</sub>=2mA)の温度特性

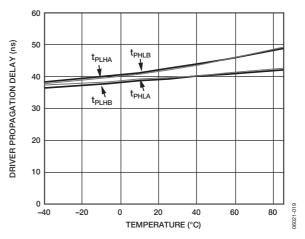

図10. ドライバ伝播遅延の温度特性

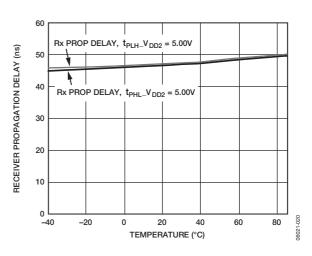

図11. レシーバ伝播遅延の温度特性

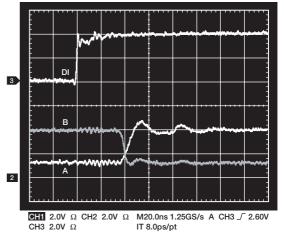

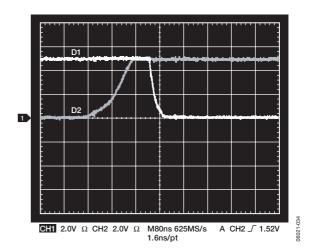

図12. ドライバ/レシーバ伝播遅延、ローレベルからハイレベル  $(R_{LDIFF}\!=\!54\Omega,\,C_{L1}\!=\!C_{L2}\!=\!100pF)$

— 10 — REV. A

図13. ドライバ/レシーバ伝播遅延、ハイレベルからローイレベル  $(R_{LDIFF}{=}54\Omega,\,C_{L1}{=}C_{L2}{=}100pF)$

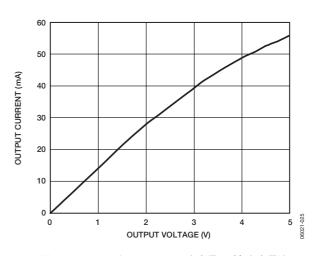

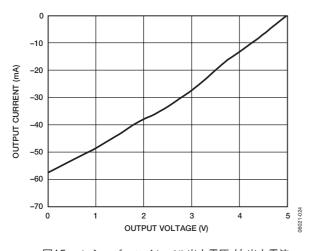

図16. レシーバ・ローレベル出力電圧 対 出力電流

図14. 熱軽減曲線、VDE 0884-2準拠の安全性限界電流 のケース温度依存性

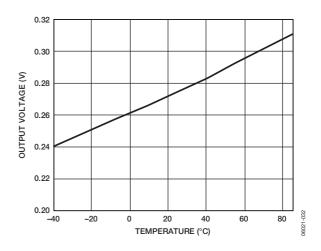

図17. レシーバ・ハイレベル出力電圧の温度特性  $(I_{DD2}=-4\text{mA})$

図15. レシーバ・ハイレベル出力電圧 対 出力電流

図18. レシーバ・ローレベル出力電圧の温度特性  $(I_{DD2} = -4mA)$

REV. A — 11 —

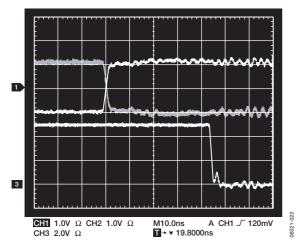

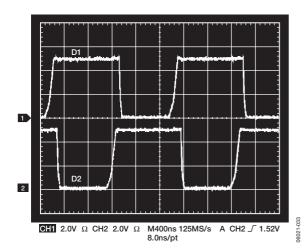

図19. スイッチング波形(D1およびD2の $V_{DD1}$ に 対する $50\Omega$ のプルアップ抵抗)

図20. スイッチング波形(ブレーク・ビフォア・メーク、 D1およびD2の $V_{DD1}$ に対する $50\Omega$ のプルアップ抵抗)

# テスト回路

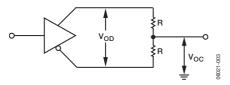

図21. ドライバ電圧測定

図22. ドライバ電圧測定

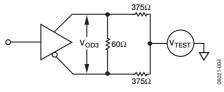

図23. 電源電流測定用のテスト回路

図24. 高周波コモンモード・ノイズ測定用のテスト回路

図26. RTSからDEまでの伝搬遅延

図27. ドライバ・イネーブル/ディスエーブル

REV. A — 13 —

## 回路の説明

#### 電気的絶縁

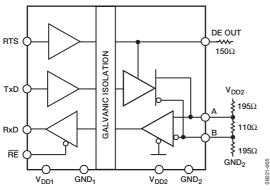

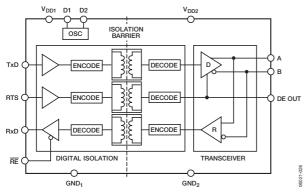

ADM2485では、インターフェースのシステム側で電気的絶縁を行っています。したがって、デバイスは主にデジタル・アイソレーション部とトランシーバ部からなります(図30参照)。 TxDピンに入力されるドライバ入力信号とDEピンに入力されるドライバ入力信号とDEピンに入力されるデータ・イネーブル信号はロジック・グラウンド(GND<sub>1</sub>)を基準としており、アイソレーション・バリアを越えて、絶縁されたグラウンド(GND<sub>2</sub>)を基準とするトランシーバ部に渡されます。同様に、トランシーバ部の絶縁されたグラウンドを基準とするレシーバ出力は、アイソレーション・バリアを越えて、ロジック・グラウンドを基準とするRxDピンに出力されます。

#### iCoupler技術

デジタル信号はiCoupler技術によってアイソレーション・バリアを越えて送信されます。この技術では、チップ・サイズのトランス巻線を使って、デジタル信号をバリアの一方から他方へ磁気的に結合します。デジタル入力は、トランスの1次巻線を励磁できる波形にエンコードされます。2次巻線では、エンコードされた波形が、送信された元のバイナリ値にデコードされます。

図30. ADM2485のデジタル・アイソレーション部と トランシーバ部

#### 真理值表

表10と表11の真理値表には、表9に示す略号を使用しています。

表9. 真理値表の略号

| Letter | Description          |

|--------|----------------------|

| Н      | High level           |

| I      | Indeterminate        |

| L      | Low level            |

| X      | Irrelevant           |

| Z      | High impedance (off) |

| NC     | Disconnected         |

表10. 送信

| Supply Status    |                  | Inputs |     |   | tputs |        |

|------------------|------------------|--------|-----|---|-------|--------|

| V <sub>DD1</sub> | V <sub>DD2</sub> | RTS    | TxD | Α | В     | DE OUT |

| On               | On               | Н      | Н   | Н | L     | Н      |

| On               | On               | Н      | L   | L | Н     | Н      |

| On               | On               | L      | X   | Z | Z     | L      |

| On               | Off              | X      | X   | Z | Z     | L      |

| Off              | On               | X      | X   | Z | Z     | L      |

| Off              | Off              | X      | X   | Z | Z     | L      |

表11. 受信

| Supply Status    |           | Input                     | Outputs |     |

|------------------|-----------|---------------------------|---------|-----|

| $V_{\text{DD1}}$ | $V_{DD2}$ | A – B                     | RE      | RxD |

| On               | On        | >+0.2 V                   | L or NC | Н   |

| On               | On        | <-0.2 V                   | L or NC | L   |

| On               | On        | -0.2  V < A - B < +0.2  V | L or NC | I   |

| On               | On        | Inputs open               | L or NC | Н   |

| On               | On        | X                         | Н       | Z   |

| On               | Off       | X                         | L or NC | Н   |

| Off              | On        | X                         | L or NC | Н   |

| Off              | Off       | X                         | L or NC | L   |

#### サーマル・シャットダウン

ADM2485はサーマル・シャットダウン回路を内蔵しており、 故障時に消費電力が大きくなり過ぎないように保護します。ド ライバ出力を低インピーダンス電源に短絡すると、大きなドラ イバ電流が流れます。温度検出回路がこの状態でのチップ温度 上昇を検出して、ドライバ出力をディスエーブルします。この 回路は、チップ温度が150℃に到達したとき、ドライバ出力を ディスエーブルします。デバイスが冷えて温度が140℃になる と、ドライバは再びイネーブルされます。

#### レシーバのフェイルセーフ入力

レシーバ入力はフェイルセーフ機能を持っているため、入力AとBがオープンまたはフロート状態になると、ロジック・ハイレベルのRxD出力を保証します。

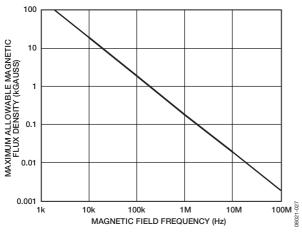

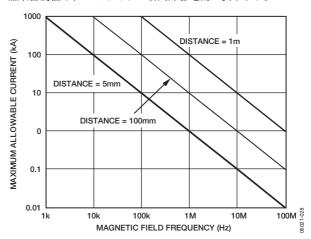

#### 磁界耐性

*i*Couplerはコアレス技術を採用しており、磁性部品がないため、コア材の磁気飽和といった問題がありません。したがって、*i*Couplerは基本的にDC磁界に対して無限の耐性があります。

しかし、iCouplerのAC磁界耐性は、次の条件によって制限されます。すなわち、受信側コイル(この場合は下側のコイル)に発生した誘導誤差電圧が大きくなって、デコーダをセットもしくはリセットさせる誤動作が発生するような場合です。次の解析でこの状態が発生する条件を求めます。ADM2485は3.3V動作が最も感受性の高い動作モードであることから、この状態を調べます。受信側コイルへの誘導電圧は次式で求められます。

$$V = \left(\frac{-d\beta}{dt}\right) \sum \pi r_n^2; n = 1, 2 \cdots N$$

(1)

ここで、トランス出力でのパルスは1.0V以上の振幅があるとします。

$\beta$ は磁束密度 (Gauss) です。

Nは受信側コイルの巻数です。

$r_n$ は受信側のn回目のコイル巻数の半径 (cm) です。

デコーダは約0.5Vの検出スレッショールドを持つため、誘導電圧に対しては0.5Vの余裕があります。

受信側コイルの形状を考え、誘導電圧がデコーダの0.5Vマージンの50%以下とすると、最大許容磁界は図31のように計算されます。

図31. 磁界周波数 対 最大許容外部磁束密度

たとえば、磁界周波数=1MHzで、最大許容磁界=0.2kGauss の場合、受信側コイルでの誘導電圧は0.25Vになります。これは検出スレッショールドの約50%であることから、出力変化の誤動作は起きません。このような条件が送信パルス内に存在し、かつ最悪時の極性であっても、受信パルスが1.0V以上から0.75Vへ減少されるため、デコーダの検出スレッショールド0.5Vに対してまだ余裕があります。

図32に、ADM2485のトランスから一定の距離をおいたときの 磁束密度値を、わかりやすい最大許容電流で表します。

図32. 電流とADM2485との間の距離を変えたときの 最大許容電流

強い磁界と高周波が組み合わされると、PCボードのパターンで 形成されるループに大きな誤差電圧が誘導され、後段回路のス レッショールドがトリガされことがあります。パターンのレイ アウトでは、このようなことが発生しないように注意が必要で す。

REV. A — 15 —

# アプリケーション情報

#### PCボードのレイアウト

絶縁型RS-485トランシーバADM2485には、ロジック・インターフェース用の外付けインターフェース回路は不要です。入力電源ピンと出力電源ピンには電源バイパスが必要です(図33参照)。

バイパス・コンデンサは $V_{\rm DD1}$ では3番ピンと4番ピンの間に、 $V_{\rm DD2}$ では15番ピンと16番ピンの間に接続するのが便利です。コンデンサの値は、 $0.01\sim0.1\mu$ Fにします。コンデンサの両端と入力電源ピンとの間の合計リード長は $20{\rm mm}$ を超えないようにします。

$V_{DD2}$ 側のグラウンド配線がパッケージのすぐ近くで接続されていない限り、9番ピンと16番ピンの間でバイパスしてください。

図33. 推奨PCボード・レイアウト

高いコモンモード過渡電圧が発生するアプリケーションでは、 絶縁バリアを越えるようなボード上での結合を最小限に抑える ように注意する必要があります。さらに、いかなる結合も部品 側のすべてのピンで等しくなるようにボード・レイアウトをデ ザインする必要があります。

この注意を怠ると、ピンとピンとの間で発生する電位差がデバイスの絶対最大定格を超えてしまい、ラッチアップまたは恒久的な損傷が発生することがあります。

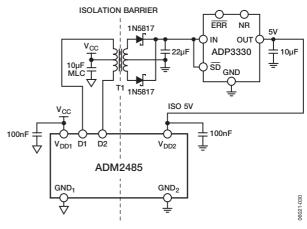

#### トランス電源

ADM2485に使われる主なトランスは、センター・タップ付きトランスです。トランスの巻数比は、予想最大負荷および最小入力電圧で最小出力電圧を提供できるように設定する必要があります。表12にADM2485のトランス電源を示します。

#### 表12. トランス電源

| Manufacturer     | Primary Voltage 3.3 V | Primary Voltage 5 V |

|------------------|-----------------------|---------------------|

| Coilcraft        | DA2304-AL             | DA2303-AL           |

| C&D Technologies | 782485/35C            | 782485/55C          |

#### アプリケーション図

ADM2485はトランス・ドライバを内蔵しています。このドライバは、外付けのトランスおよびLDOで使用され、 $V_{DD2}$ と GND $_{7}$ の間に絶縁電源電圧 $_{7}$ SVを供給します。

ADM2485のD1とD2はセンター・タップ付きトランスT1を駆動します。1対のショットキ・ダイオードと平滑化コンデンサを使って、2次巻線から整流した信号を発生します。ADP3330リニア電圧レギュレータは、ADM2485のバス側回路( $V_{DD2}$ )に5Vの安定化した電源を供給します(図34を参照)。

ADM2485をシステム側の3.3Vで駆動するときは、1CT:2.2CTトランスT1で電圧を3.3Vから6Vに上げ、十分なヘッドルームを確保してADP3330 LDOにより5Vの安定化した出力を提供できるようにします。

ADM2485をシステム側の5Vで駆動するときは、1CT:1.5CTトランス71で十分なヘッドルームを確保してADP3330 LDOにより安定化された5V出力を提供できるようにします。

図34. アプリケーション図

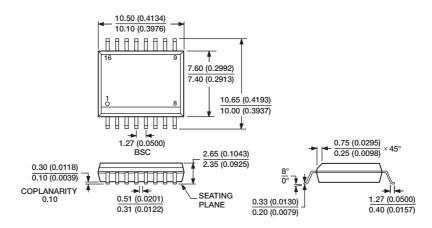

# 外形寸法

COMPLIANT TO JEDEC STANDARDS MS-013-AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

図35. 16ピン標準スモール・アウトライン・パッケージ [SOIC\_W] ワイド幅

(RW-16) 寸法単位:mm(インチ)

## オーダー・ガイド

| Model                    | Data Rate (Mbps) | Temperature Range | Package Description | Package Option |

|--------------------------|------------------|-------------------|---------------------|----------------|

| ADM2485BRWZ <sup>1</sup> | 16               | -40°C to +85°C    | 16-Lead SOIC_W      | RW-16          |

| ADM2485BRWZ-REEL71       | 16               | -40°C to +85°C    | 16-Lead SOIC_W      | RW-16          |

<sup>&</sup>lt;sup>1</sup> Z=RoHS準拠

REV. A — 17 —