## ゲイン制御範囲60dB、 10MHz~3GHz、VGA

**ADL5330**

### 特長

電圧制御アンプ/減衰器 動作周波数:10MHz~3GHz 出力パワー制御を最適化

優れた直線性: OIP3 31dBm@900MHz 出力ノイズ・フロア: -150dBm/Hz@900MHz 50Ωの入力および出力インピーダンス シングルエンド動作または差動動作

広いゲイン制御範囲: -34~+22dB@900MHz デシベル・リニアのゲイン制御機能: 20mV/dB

单電源動作: 4.75~5.25V

### アプリケーション

RFとIFでの送信および受信のパワー制御

### 概要

ADL5330は、最大周波数3GHzのアプリケーションを対象とする、高性能電圧制御VGA(可変ゲイン・アンプ)/減衰器です。信号パスの平衡構造により、歪みを最小限に抑えると同時に、低ゲインと高周波数での寄生カップリングにより発生するスプリアス混入の危険性を減らします。信号源、負荷共に平衡回路で動作させることを推奨しますが、入力がシングルエンドの場合は内部で差動に変換されます。

入力インピーダンスは、INHIとINLOとの間で $50\Omega$ です。出力は一般に、グラウンドに接続された $50\Omega$ 負荷に1:1バラン・トランスを介して接続されます。 $4.75\sim5.25$ Vの単電源が必要です。

50Ωの入力システムでは、印加された電圧を、シングルエンド信号源から駆動された場合でも高い直線性と優れた同相ノイズ除去を持つ一対の差動電流に変換します。次に、これらの信号電流は、ゲイン全体に渡って高精度を実現する、当社独自のデシベル・リニア特性を持った電圧制御減衰器に加えられます。GAINピンには、最小ゲインの0Vから最大ゲインの1.4Vまでの電圧を、スケーリング係数20mV/dBで入力することができます。

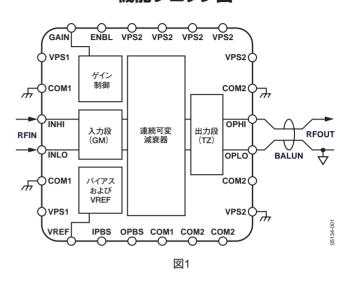

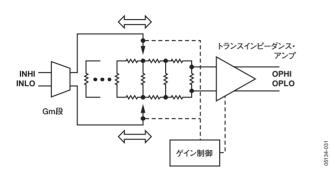

### 機能ブロック図

高精度広帯域減衰器の出力は、差動トランスインピーダンス出力段に加えられます。この出力段では $50\Omega$ の差動出力インピーダンスが設定され、OPHIピンとOPLOピンを駆動します。ADL5330にはパワーダウン機能があります。パワーダウンにするには、ENBLピンにローレベルを入力します。パワーダウン・モード時の消費電流は $250\mu$ Aです。

ADL5330は、アナログ・デバイセズ独自の高性能相補バイポーラICプロセスにより製造されています。24ピンの鉛フリーLFCSP\_VQパッケージ(4mm×4mm)を採用し、動作温度は−40~+85℃で規定されています。評価用ボードも提供しています。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいはその利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。日本語データシートは、REVISIONが古い場合があります。最新の内容については、英語版をご参照ください。©2005 Analog Devices, Inc. All rights reserved.

### 目次

| 仕様3                                               | ゲイン制御入力・・・・・・・15            |

|---------------------------------------------------|-----------------------------|

| 絶対最大定格                                            | 自動ゲイン制御・・・・・・・・・・・・・・・・・・15 |

| ESDに関する注意 ······5                                 | IQ変調器とのインターフェース17           |

| ピン配置および機能の説明 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | WCDMA送信アプリケーション・・・・・・18     |

| 代表的な性能特性 ・・・・・・・7                                 | CDMA2000送信アプリケーション・・・・・・・19 |

| 動作原理・・・・・・12                                      | ハンダ処理情報・・・・・・19             |

| アプリケーション・・・・・・13                                  | 評価用ボード・・・・・・・20             |

| 基本接続・・・・・・13                                      | 外形寸法・・・・・・24                |

| RF入力/出力インターフェース ·····14                           | オーダー・ガイド・・・・・・・24           |

### 改訂履歴

#### $6/05\mbox{---}Rev.~0$ to Rev. A

| Changes to Figure 1 · · · · · · · · · · · · · · · · · ·  |

|----------------------------------------------------------|

| Changes to Table 1                                       |

| Changes to Table 2 · · · · · · · · · · · · · · · · · ·   |

| Changes to Table 3 · · · · · · · · · · · · · · · · · ·   |

| Changes to Figure 27 · · · · · · 11                      |

| Changes to Figure 35 · · · · · · · · · · · · · · · · · · |

| Changes to the Gain Control Input Section15              |

| Changes to Figure 42 · · · · · 17                        |

4/05—Revision 0: Initial Version

## 仕様

$V_S=5V$ 、 $T_A=25$   $\mathbb{C}$ 、シングルエンドの $50\Omega$  マッチのために、入力側と出力側にM/A-COM ETC1-1-13 1:1バランを挿入

#### 表1

| パラメータ                 | 条件                                           | Min  | Тур   | Max | 単位    |

|-----------------------|----------------------------------------------|------|-------|-----|-------|

| 全体                    |                                              |      |       |     |       |

| 使用可能周波数範囲             |                                              | 0.01 |       | 3   | GHz   |

| 公称入力インピーダンス           | 1:1シングルエンド/差動変換バラン回路を使用                      |      | 50    |     | Ω     |

| 公称出力インピーダンス           | 1:1差動/シングルエンド変換バラン回路を使用                      |      | 50    |     | Ω     |

| 100MHz                |                                              |      |       |     |       |

| ゲイン制御スパン              | ±3dBゲイン則に対する整合性                              |      | 58    |     | dB    |

| 最大ゲイン                 | $V_{GAIN}=1.4V$                              |      | 23    |     | dB    |

| 最小ゲイン                 | V <sub>GAIN</sub> =0.1V                      |      | -35   |     | dB    |

| ゲイン平坦性の周波数特性          | 中心周波数±30MHz、V <sub>GAIN</sub> =1.0V(差動出力)    |      | 0.09  |     | dB    |

| ゲイン制御スロープ             |                                              |      | 20.7  |     | mV/dE |

| ゲイン制御インターセプト          | ゲイン=0dB、ゲイン=スロープ(V <sub>GAIN</sub> -インターセプト) |      | 0.88  |     | V     |

| 入力圧縮ポイント              | V <sub>GAIN</sub> =1.2V                      |      | 1.8   |     | dBm   |

| 入力圧縮ポイント              | V <sub>GAIN</sub> =1.4V                      |      | -0.3  |     | dBm   |

| 出力3次インターセプト(OIP3)     | $V_{GAIN}=1.4V$                              |      | 38    |     | dBm   |

| 出力ノイズ・フロア1            | 20MHzキャリア・オフセット、VGAIN=1.4V                   |      | -140  |     | dBm/H |

| ノイズ指数                 | $V_{GAIN}=1.4V$                              |      | 7.8   |     | dB    |

| 入力リターン損失2             | 1V <v<sub>GAIN&lt;1.4V</v<sub>               |      | -12.8 |     | dB    |

| 出力リターン損失2             |                                              |      | -15.5 |     | dB    |

| 450MHz                |                                              |      |       |     |       |

| ゲイン制御スパン              | ±3dBゲイン則に対する整合性                              |      | 57    |     | dB    |

| 最大ゲイン                 | $V_{GAIN}=1.4V$                              |      | 22    |     | dB    |

| 最小ゲイン                 | $V_{GAIN}=0.1V$                              |      | -35   |     | dB    |

| ゲイン平坦性の周波数特性          | 中心周波数±30MHz、V <sub>GAIN</sub> =1.0V(差動出力)    |      | 0.08  |     | dB    |

| ゲイン制御スロープ             |                                              |      | 20.4  |     | mV/dE |

| ゲイン制御インターセプト          | ゲイン=0dB、ゲイン=スロープ(VGAIN-インターセプト)              |      | 0.89  |     | V     |

| 入力圧縮ポイント              | $V_{GAIN}=1.2V$                              |      | 3.3   |     | dBm   |

| 入力圧縮ポイント              | $V_{GAIN}=1.4V$                              |      | 1.2   |     | dBm   |

| 出力3次インターセプト(OIP3)     | $V_{GAIN}=1.4V$                              |      | 36    |     | dBm   |

| 出力ノイズ・フロア1            | 20MHzキャリア・オフセット、VGAIN=1.4V                   |      | -146  |     | dBm/F |

| ノイズ指数                 | $V_{GAIN}=1.4V$                              |      | 8.0   |     | dB    |

| 入力リターン損失2             | 1V <v<sub>GAIN&lt;1.4V</v<sub>               |      | -19   |     | dB    |

| 出力リターン損失2             |                                              |      | -13.4 |     | dB    |

| 900MHz                |                                              |      |       |     |       |

| ゲイン制御スパン              | ±3dBゲイン則に対する整合性                              |      | 53    |     | dB    |

| 最大ゲイン                 | $V_{GAIN}=1.4V$                              |      | 21    |     | dB    |

| 最小ゲイン                 | $V_{GAIN}=0.2V$                              |      | -32   |     | dB    |

| ゲイン平坦性の周波数特性          | 中心周波数±30MHz、V <sub>GAIN</sub> =1.0V(差動出力)    |      | 0.14  |     | dB    |

| ゲイン制御スロープ             |                                              |      | 19.7  |     | mV/dE |

| ゲイン制御インターセプト          | ゲイン=0dB、ゲイン=スロープ(VGAIN-インターセプト)              |      | 0.92  |     | V     |

| 入力圧縮ポイント              | V <sub>GAIN</sub> =1.2V                      |      | 2.7   |     | dBm   |

| 入力圧縮ポイント              | $V_{GAIN}=1.4V$                              |      | 1.3   |     | dBm   |

| 出力3次インターセプト(OIP3)     | $V_{GAIN}=1.4V$                              |      | 31.5  |     | dBm   |

| 出力ノイズ・フロア1            | 20MHzキャリア・オフセット、V <sub>GAIN</sub> =1.4V      |      | -144  |     | dBm/F |

| ノイズ指数                 | $V_{GAIN}=1.4V$                              |      | 9.0   |     | dB    |

| 入力リターン損失 <sup>2</sup> | 1V <v<sub>GAIN&lt;1.4V</v<sub>               |      | -18   |     | dB    |

| 出力リターン損失2             | - STOAIN SALL                                |      | -18   |     | dB    |

| パラメータ             | 条件                                          | Min  | Тур        | Max  | 単位    |

|-------------------|---------------------------------------------|------|------------|------|-------|

| 2200MHz           |                                             |      |            |      |       |

| ゲイン制御スパン          | ±3dBゲイン則に対する整合性                             |      | 46         |      | dB    |

| 最大ゲイン             | $V_{GAIN}=1.4V$                             |      | 16         |      | dB    |

| 最小ゲイン             | $V_{GAIN}=0.6V$                             |      | -30        |      | dB    |

| ゲイン平坦性の周波数特性      | 中心周波数±30MHz、V <sub>GAIN</sub> =1.0V(差動出力)   |      | 0.23       |      | dB    |

| ゲイン制御スロープ         |                                             |      | 16.7       |      | mV/dB |

| ゲイン制御インターセプト      | ゲイン= $0dB$ 、ゲイン=スロープ ( $V_{GAIN}$ ーインターセプト) |      | 1.06       |      | V     |

| 入力圧縮ポイント          | $V_{GAIN}=1.2V$                             |      | 0.9        |      | dBm   |

| 入力圧縮ポイント          | $V_{GAIN}=1.4V$                             |      | -2.0       |      | dBm   |

| 出力3次インターセプト(OIP3) | $V_{GAIN}=1.4V$                             |      | 21.2       |      | dBm   |

| 出力ノイズ・フロア1        | 20MHzキャリア・オフセット、VGAIN=1.4V                  |      | -147       |      | dBm/H |

| ノイズ指数             | $V_{GAIN}=1.4V$                             |      | 12.5       |      | dB    |

| 入力リターン損失2         | 1V <v<sub>GAIN&lt;1.4V</v<sub>              |      | -11.7      |      | dB    |

| 出力リターン損失2         |                                             |      | -9.5       |      | dB    |

| 2700MHz           |                                             |      |            |      |       |

| ゲイン制御スパン          | ±3dBゲイン則に対する整合性                             |      | 42         |      | dB    |

| 最大ゲイン             | $V_{GAIN}=1.4V$                             |      | 10         |      | dB    |

| 最小ゲイン             | $V_{GAIN}=0.7V$                             |      | -32        |      | dB    |

| ゲイン平坦性の周波数特性      | 中心周波数±30MHz、V <sub>GAIN</sub> =1.0V(差動出力)   |      | 0.3        |      | dB    |

| ゲイン制御スロープ         |                                             |      | 16         |      | mV/dB |

| ゲイン制御インターセプト      | $f$ ゲイン=0dB、ゲイン=スロープ ( $V_{GAIN}$ ーインターセプト) |      | 1.15       |      | v     |

| 入力圧縮ポイント          | $V_{GAIN}=1.2V$                             |      | 1.2        |      | dBm   |

| 入力圧縮ポイント          | $V_{GAIN}=1.4V$                             |      | -0.9       |      | dBm   |

| 出力3次インターセプト(OIP3) | $V_{GAIN}=1.4V$                             |      | 17         |      | dBm   |

| 出力ノイズ・フロア1        | 20MHzキャリア・オフセット、VGAIN=1.4V                  |      | -152       |      | dBm/H |

| ノイズ指数             | $V_{GAIN}=1.4V$                             |      | 14.7       |      | dB    |

| 入力リターン損失2         | 1V <v<sub>GAIN&lt;1.4V</v<sub>              |      | -9.7       |      | dB    |

| 出力リターン損失2         |                                             |      | <b>-</b> 5 |      | dB    |

| ゲイン制御入力           | GAINピン                                      |      |            |      |       |

| ゲイン制御電圧範囲3        |                                             | 0    |            | 1.4  | V     |

| ゲイン制御端子の入力抵抗      | GAINピンからCOM1ピンまで                            |      | 1          |      | ΜΩ    |

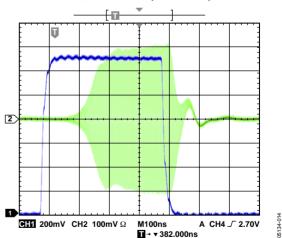

| 応答時間              | フルスケール:最終ゲインの1dB以内まで                        |      | 380        |      | ns    |

|                   | 3dBゲイン・ステップ、Pourから最終ゲインの1dB以内まで             |      | 20         |      | ns    |

| 電源                | VPS1ピン、VPS2ピン、COM1ピン、COM2ピン、ENBLピン          |      |            |      |       |

| 電圧                |                                             | 4.75 | 5          | 5.25 | v     |

| 電流、アクティブ時         | $V_{ m GN} = 0V$                            |      | 100        |      | mA    |

| •                 | $V_{GN}=1.4V$                               |      | 215        |      | mA    |

| 電流、ディスエーブル時       | ENBL=LO                                     |      | 250        |      | μΑ    |

4

<sup>1</sup>ノイズ・フロアは、出力パワー・レベルにより多少変わります。図9~13を参照。

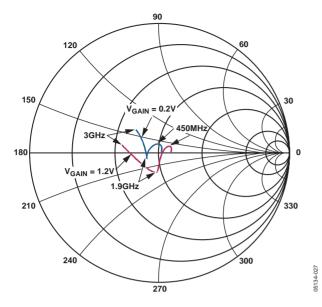

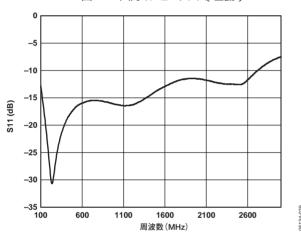

<sup>2</sup>差動入力と出力のインピーダンスについては、図27と図29を参照。

<sup>3</sup>最小ゲイン電圧は周波数により変わります。図3~7を参照。

### 絶対最大定格

#### 表2

| パラメータ                                  | 定格        |

|----------------------------------------|-----------|

| 電源電圧VPS1、VPS2                          | 5.5V      |

| 最大ゲインでのRF入力パワー                         | 50℃で5dBm  |

| OPHI, OPLO                             | 5.5V      |

| ENBL                                   | VPS1、VPS2 |

| ゲイン                                    | 2.5V      |

| 内部消費電力                                 | 1.1W      |

| $\theta_{\mathrm{JA}}$ (パッドをボードにハンダ付け) | 60℃/W     |

| 最大ジャンクション温度                            | 150℃      |

| 動作温度範囲                                 | -40~+85°C |

| 保存温度範囲                                 | -65~150°C |

| リード温度範囲(ハンダ処理、60秒)                     | 300℃      |

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な 損傷を与えることがあります。この規定はストレス定格のみを指定するも のであり、この仕様の動作セクションに記載する規定値以上でのデバイ ス動作を定めたものではありません。デバイスを長時間絶対最大定格状 態に置くと、デバイスの信頼性に影響を与えることがあります。

### 注意

ESD(静電放電)の影響を受けやすいデバイスです。人体や試験機器には4,000Vもの高圧の静電気が容易に蓄積され、検知されないまま放電されることがあります。本製品は当社独自のESD保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、回復不能の損傷を生じる可能性があります。したがって、性能劣下や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

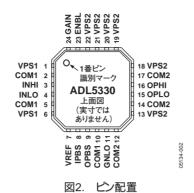

## ピン配置および機能の説明

表3 ピン機能の説明

| <br>ピン番号        | 記号         | 説明                                 |

|-----------------|------------|------------------------------------|

| 1, 6, 13, 18~22 | VPS1, VPS2 | 正側電源。公称5V。                         |

| 2, 5, 10        | COM1       | 入力段のコモン。                           |

| 3, 4            | INHI, INLO | 差動入力。ACカップリング。                     |

| 7               | VREF       | 電圧リファレンス。1.5V出力。通常、グラウンドにACカップリング。 |

| 8               | IPBS       | 入力バイアス。通常、グラウンドにACカップリング。          |

| 9               | OPBS       | 出力バイアス。グラウンドにACカップリング。             |

| 11              | GNLO       | ゲイン制御コモン。グラウンドに接続。                 |

| 12, 14, 17      | COM2       | 出力段のコモン。                           |

| 15              | OPLO       | 差動出力のローサイド。VpにRFチョークでバイアス          |

| 16              | OPHI       | 差動出力のハイサイド。VpにRFチョークでバイアス          |

| 23              | ENBL       | デバイス・イネーブル。ハイレベルで通常動作。             |

| 24              | GAIN       | ゲイン制御電圧入力。公称範囲:0~1.4V。             |

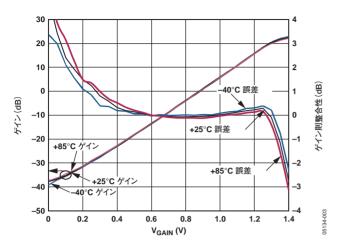

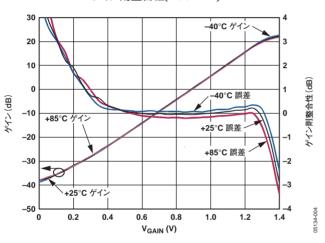

### 代表的な性能特性

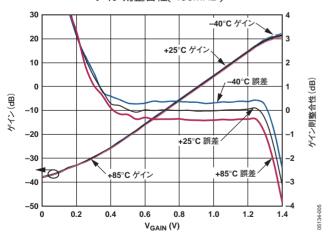

図3. 各温度におけるV<sub>GAIN</sub> 対 ゲインおよび ゲイン則整合性(100MHz)

図4. 各温度におけるV<sub>GAIN</sub> 対 ゲインおよび ゲイン則整合性(450MHz)

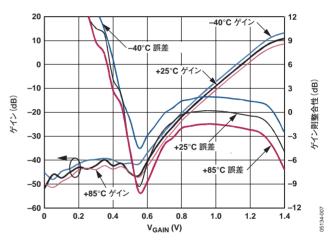

図5. 各温度におけるV<sub>GAIN</sub> 対 ゲインおよび ゲイン則整合性(900MHz)

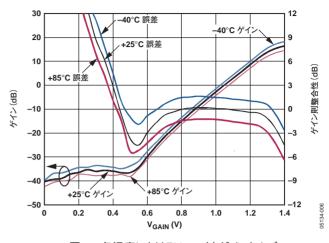

図6. 各温度におけるV<sub>GAIN</sub> 対 ゲインおよび ゲイン則整合性(2200MHz)

図7. 各温度におけるV<sub>GAIN</sub> 対 ゲインおよび ゲイン則整合性(2700MHz)

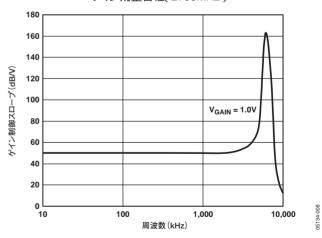

図8. ゲイン制御入力の周波数応答(キャリア周波数 = 900MHz)

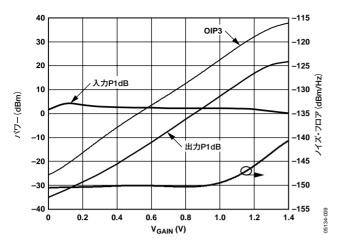

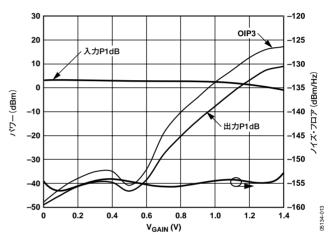

図9. V<sub>GAIN</sub> 対 入力圧縮ポイント、出力圧縮ポイント、 OIP3、ノイズ・フロア(100MHz)

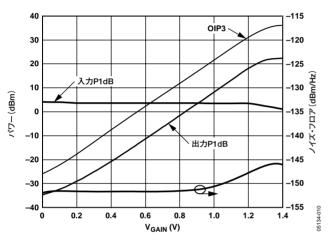

図10. V<sub>GAIN</sub> 対 入力圧縮ポイント、出力圧縮ポイント、 OIP3、ノイズ・フロア(450MHz)

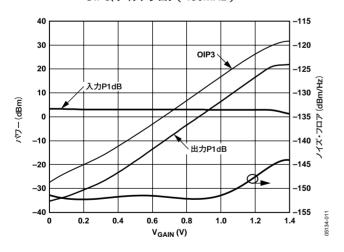

図11. V<sub>GAIN</sub> 対 入力圧縮ポイント、出力圧縮ポイント、 OIP3、ノイズ・フロア(900MHz)

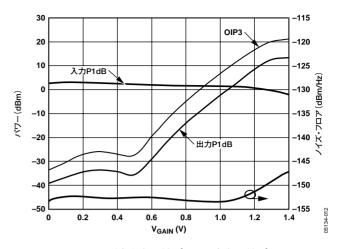

図12. V<sub>GAIN</sub> 対 入力圧縮ポイント、出力圧縮ポイント、 OIP3、ノイズ・フロア(2200MHz)

図13. V<sub>GAIN</sub> 対 入力圧縮ポイント、出力圧縮ポイント、 OIP3、ノイズ・フロア(2700MHz)

図14. ゲイン制御入力のステップ応答

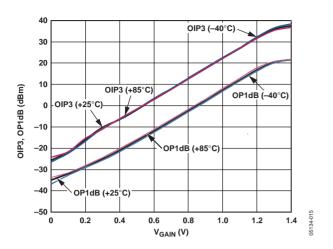

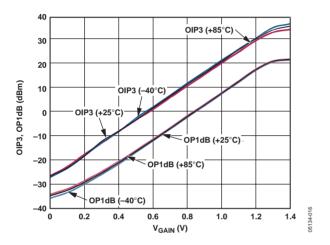

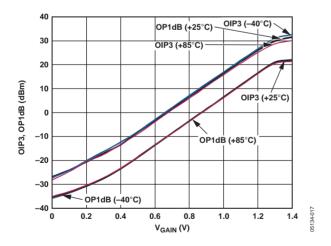

図15. 各温度におけるゲイン 対 OP1dBおよびOIP3(100MHz)

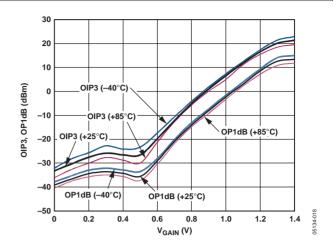

図16. 各温度におけるゲイン 対 OP1dBおよびOIP3(450MHz)

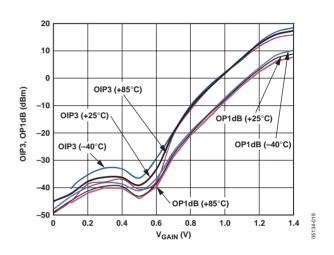

図17. 各温度におけるゲイン 対 OP1dBおよびOIP3(900MHz)

図18. 各温度におけるゲイン 対 OP1dBおよびOIP3(2200MHz)

図19. 各温度におけるゲイン 対 OP1dBおよびOIP3(2700MHz)

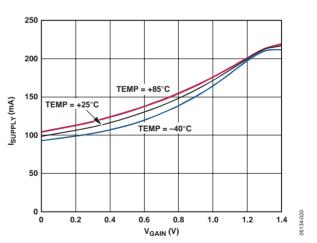

図20. 各温度におけるV<sub>GAIN</sub>対電源電流

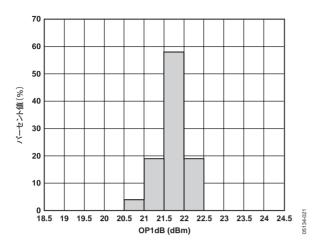

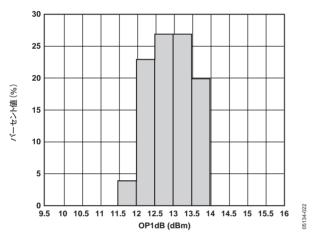

図21. 900MHz、最大ゲインでのOP1dBの分布(VGAIN = 1.4V)

図22. 2200MHz、最大ゲインでのOP1dBの分布(VGAIN = 1.4V)

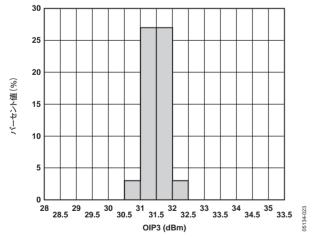

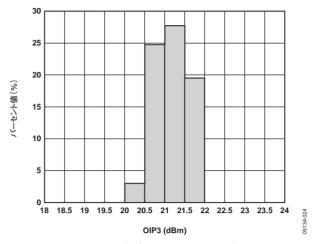

図23. 900MHz、最大ゲインでのOIP3の分布(VGAIN = 1.4V)

図24. 2200MHz、最大ゲインでのOIP3の分布(VGAIN = 1.4V)

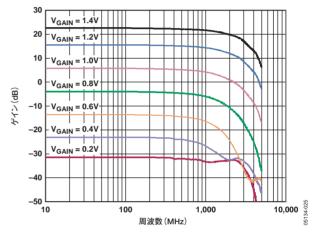

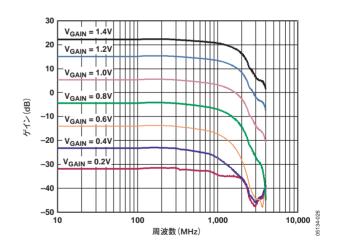

図25. ゲインの周波数特性(差動)

図26. ゲインの周波数特性(ETC1-1-13バラン回路を使用)

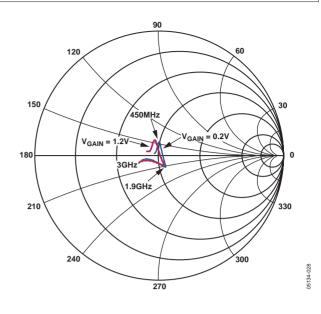

図27. 入力インピーダンス(差動)

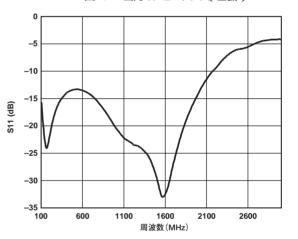

図28. 入力リターン損失(ETC1-1-13バラン回路を使用)

図29. 出力インピーダンス(差動)

図30. 出力リターン損失(ETC1-1-13バラン回路を使用)

### 動作原理

ADL5330は、最大周波数3GHzのアプリケーションを対象とする高性能電圧制御の可変ゲイン・アンプ/減衰器です。この製品は、一定の入力レベルが与えられ、かつ出力レベルを広い範囲に渡って調整したいアプリケーションで、出力可変ゲイン・アンプ(OVGA)として機能するように作られています。OVGAの1つの機能は、出力レベルをスケーリングすることで、この場合IP3とP1dB(1dB圧縮ポイント)はゲインの減少に比例して減少します。

デバイス内部の信号パスは、差動信号の一般的な利点(放射や寄生フィードスルーの削減、他の回路などからの同相信号の削減など)が得られるように、完全な差動構成になっています。図31に、ADL5330の簡略回路図を示します。

図31. 簡略回路図

入力Gm段では、(帰還回路に)パッシブとアクティブの終端技術を組み合わせることで、制御された入力インピーダンス50Ωが得られます。Gm 段の入力圧縮ポイントは、入力周波数に応じて1~3dBmです。

Gm段の入力は内部でDCレベルにバイアスされているため、一般にDC ブロッキング・コンデンサを入力に接続し、デバイスの異常動作を回避することが必要です。

Gm段からの電流は、平衡ラダー減衰器のラダー上のノードに入力されます。注入領域中心のこのノードの位置は、加えられたゲイン制御電圧に応じて変わります。ラダーへの電流注入の制御は、デシベル・リニアのゲイン制御と低歪みを可能にする当社独自の方法により実現しています。

デシベル・リニアのゲイン制御は、DC0~1.4Vの範囲の電圧をゲイン制御ピンに入力することによって、行われます。最大ゲインは最高電圧を入力したときに得られます。

ラダー減衰器の出力は、ゲインを与えかつ負荷変動に対してラダー終端インピーダンスをバッファする固定ゲインのトランスインピーダンス・アンプ (TZA)に渡されます。このTZAでは、直線性を改善し、差動出力インピーダンスを $50\Omega$ に制御するために帰還を使っています。出力アンプの静止電流はアダプティブです。すなわち、ゲイン(したがって出力パワー)が小さいときに消費電力を削減するため、静止電流はゲイン制御電圧に追従します。

ADL5330の出力では、正側電源電圧に対して外部DCバイアスが必要です。このバイアスは一般に、外付けインダクタを介して加えられます。同相ノイズを回避するために出力は差動で取り出すのがベストですが、必要に応じてシングルエンドで取り出すことも可能です。

シングル出力のみを使用する場合でも、未使用出力ピンにバイアスを加える必要があります。未使用出力ピンには同等のAC負荷を接続することを推奨します。差動出力は一般に1:1バラン回路を使って50Ω環境に取り出します。大部分の場合、出力信号パス内にDCブロッキングが必要になります。

比較的高ゲインの設定で用いる場合、ノイズ・フロアは入力段で設定されます。この場合、デバイスのノイズ指数(NF)はゲイン設定に無関係です。ただし、ゲインがある一定の値を下回ると、減衰器出力に到達する入力段ノイズは、出力段の入力換算ノイズよりかなり小さくなります。このような場合、出力ノイズは出力段そのものに支配されるため、デバイスの全体NFはdB対dBベースで悪化します。これは、ゲインが臨界値を下回るためです。図9~13に、この動作の詳細を示します。

### アプリケーション

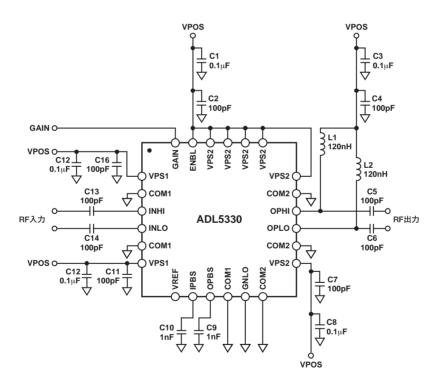

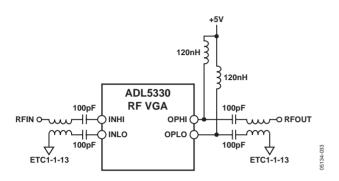

#### 基本接続

図32に、ADL5330を動作させる基本接続を示します。VPS1とVPS2の2つの正側電源があり、これらは同じ電位に接続する必要があります。COM1とCOM2の両コモン・ピンは、低インピーダンスのグラウンド・プレーンに接続します。

4.75~5.25Vの電源電圧をVPS1とVPS2に接続します。100pFと $0.1 \mu$ Fのデカップリング・コンデンサを各電源ピンの近くに接続してください。VPS2ピン(ピン18~22)は相互に隣接しているため、1対のデカップリング・コンデンサを共用できます。

ADL5330の出力OPHIとOPLOはオープン・コレクタであるため、120nH のRFチョークにより正側電源へプルアップする必要があります。ACカップリング・コンデンサとRFチョークは、低周波の動作を基本的に阻止します。たとえば、下側1MHzまでの動作では、 $0.1 \mu$ FのACカップリング・コンデンサと $1.5 \mu$ HのRFチョークを使います。状況によっては、大きなインダクタ値を使うと、発振が発生する場合があります。

差動出力は正側電源にバイアスされるため、ADL5330出力とシステム内の次の段との間に100pFのACカップリング・コンデンサを接続することが必要です。同様に、INHIピンとINLO入力ピンは、グラウンドより約3.3V高い電圧にバイアスされています。

各RF入力/出力ピンから見た公称入力インピーダンスと公称出力インピーダンスは25 $\Omega$ です。したがって、差動インピーダンスは50 $\Omega$ になります。

ADL5330をイネーブルにするには、ENBLピンをハイレベルにします。 ENBLピンをローレベルにすると、ADL5330はスリープ・モードになり、消費電流は室温で250 $\mu$ Aまで低下します。デバイスをイネーブルにする場合、ENBLピンの電圧を1.7Vより高くする必要があります。デバイスがイネーブルになると、低ゲインでは100mA、最大ゲインでは215mAが流れます。

図32. バイアス接続

### RF入出力インターフェース

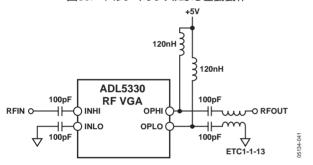

ADL5330は主に差動信号向けに設計されていますが、ADL5330をシングルエンド・アプリケーションにインターフェースさせる構成もあります。図33~35に、差動とシングルエンド間インターフェースの3つのオプションを示します。これらすべての構成では、入力と出力にACカップリング・コンデンサを、出力にRFチョークを、それぞれ使っています。

図33. バラン・トランスによる差動動作

図34. 平衡出力によるシングルエンドの駆動

図33に、バラン・トランスを使った入力と出力での差動バランスを示します。最適性能を得るためには、入力と出力共にバラン回路の使用を推奨します。ADL5330の大部分の特性評価は、入力シングルエンドと出力シングルエンドで1:1の50Ωバラン・トランスを使って実施されています。ブロードバンド・インターフェースにはM/A-COM ETC1-1-13伝送線バラン・トランスを使った動作を推奨しますが、狭い帯域幅で挿入損失

を小さくする必要があるアプリケーションに対してはナローバンド用バラン・トランスを使うことができます。

図34に示すように、シングルエンドによりデバイスを同様の性能で駆動することもできます。シングルエンド入力インターフェースは、一方の入力ピンを駆動し、未使用の入力ピンをグラウンドに接続することにより実現できます。最適性能を得るためには、出力の平衡を維持する必要があります。図34のケースでは、バラン・トランスを出力に使用しています。

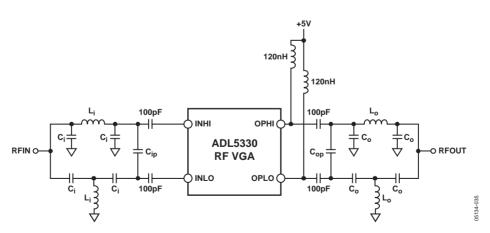

特定周波数に対しては、バラン・トランスの代わりに、パッシブなL部品と C部品で構成される集中定数バラン回路を設計することができます。図 35に、ディスクリートの集中定数バラン回路を使ったADL5330の入力と 出力での差動平衡回路を示します。この集中定数バラン回路は180°の位相差を持つと同時に、信号源から負荷へのインピーダンス変換機能およびその逆の負荷から信号源へのインピーダンス変換機能も提供します。表4に、シングルエンド・インピーダンス50Ωを使用したときの、さまざまな中心周波数に対する推奨パッシブ値を示します。Agilent社の 無料AppCAD<sup>TM</sup>プログラムを使用すると、集中定数バラン回路に対するパッシブ部品の計算を簡単に行うことができます。

集中定数バラン回路は、900MHzと2200MHzに対して、50MHzで ±0.5dBの平坦性を提供します。2.7GHzでは周波数帯域が浮遊容量により制限されます。この浮遊容量は、このような高い周波数で集中定数バラン回路内のパッシブ部品を支配します。このため、集中定数バラン回路の設計とボード・レイアウトを行うときは、PCボードの寄生容量を考慮する必要があります。

表4. 50 集中定数バラン回路に対する推奨パッシブ値 インピーダンス・マッチ

| 中心周波数     | 入力    |       |      | 出力    |       |       |

|-----------|-------|-------|------|-------|-------|-------|

| T-0/0/XXX | Ci    | Li    | Cip  | Co    | Lo    | Cop   |

| 100MHz    | 27pF  | 82nH  | 1pF  | 33pF  | 72nH  | 3.3pF |

| 900MHz    | 3.3pF | 9nH   |      | 3.9pF | 8.7nH | 0.5pF |

| 2.2GHz    | 1.5pF | 3.3nH | 16nH | 1.5pF | 3.6nH | 27nH  |

| 2.7GHz    | 1.5pF | 2.4nH |      | 1.3pF | 2.7nH | 33nH  |

図35. ディスクリートのLCバラン回路による差動動作

14

### ゲイン制御入力

VGAがイネーブルになると、GAINピンに加えられた電圧がゲインを設定します。GAINピンの入力インピーダンスは $1M\Omega$ です。

ゲイン制御電圧範囲は $0\sim+1.4$ Vで、これはゲイン範囲 (typ値)の $-38\sim+22$ dBに対応します。ゲイン制御電圧の下限は、高周波数の2.2GHzで約0.5V、2.7GHzでは約0.6Vにそれぞれ上昇します。ADL5330の電源電流は、低ゲイン制御電圧での約100mAから1.4Vでの215mAまで変化します。

1dB入力圧縮ポイントは、図9~13に示すように、ゲイン制御範囲のほぼすべてで3dBmと一定です。出力圧縮ポイントは、ゲイン設定の増加とともにdB対dBに比例して上昇します。ノイズ・フロアは1Vまで一定ですが、それを過ぎると上昇し始めます。

ゲイン制御ピンの帯域幅は約3MHzです。図14に、GAINピンでのパルス応答時間を示します。

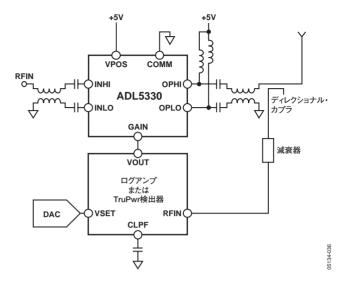

### 自動ゲイン制御(AGC)

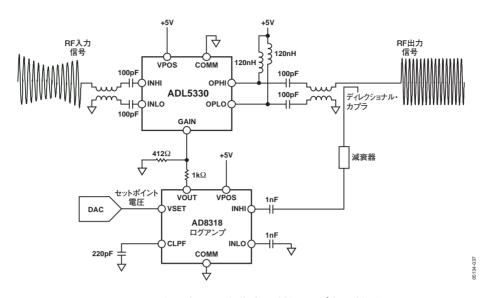

ADL5330は正確なゲイン制御を提供しますが、自動ゲイン制御 (AGC) ループを使うと、出力パワーの高精度なレギュレーションが可能になります。図36に、AGCループ内でのADL5330を示します。ログアンプ (AD8318/AD8315)または $TruPwr^{TM}$ 検出器 (AD8362)を追加すると、広い出力パワー制御範囲でAGCの温度安定性が改善されます。

AGCループ内でADL5330を動作させるときは、出力RFのサンプルを検出器に帰還させる必要があります(一般に、ディレクショナル・カプラと減衰器を追加)。検出器のVSET入力にセットポイント電圧を加え、ADL5330のGAINピンにVOUTを接続します。VOUTとRF入力信号との間の、規定された検出器のデシベル・リニアな関係に基づいて、検出器はGAINピン(検出器のVOUTピンは誤差アンプ出力)の電圧を調整し、RF入力のレベルが印加されたセットポイント電圧に対応するようにします。ゲイン設定は、検出器の入力信号レベルとセットポイント電圧との間でバランスがとれるような値に整定します。

検出器の誤差アンプは $C_{FLT}$  (グラウンド・リファレンス・コンデンサ・ピン)を使用し、誤差信号 (電流)を積分します。ループ帯域幅の設定とループ安定性のために、コンデンサを $C_{FLT}$ に接続する必要があります。

図36. AGCループ内でADL5330を使用

AD8318と組み合わせてAGCループ内でADL5330を動作させる基本接続を図37に示します。AD8318は、1MHz~8GHzの高精度復調用ログアンプです。±0.5dBの温度安定性で60dBの広い検出範囲を提供します。この構成は図36と同じです。

ADL5330のゲインは、AD8318の出力ピンによって制御されます。この電圧(VOUT)の範囲は、0V~VPOSの近辺です。オーバードライブ回復の問題を回避するため、抵抗分圧器を使用してAD8318の出力電圧をスケール・ダウンし、ADL5330の0~1.4Vのゲイン制御電圧範囲とインターフェースさせることができます。

23dBのカプラ/減衰器を使用し、VGAの最大出力パワーをAD8318のリニア動作範囲の上限(900MHzで約-5dBm)に一致させることができます。

図37. AD8318と組み合わせた自動ゲイン制御ループ内で動作するADL5330

16

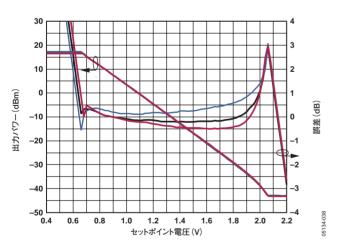

図38に、入力パワー-1.5dBmの900MHz正弦波に対する伝達関数、各温度でのVSET電圧に対する出力パワーの関係を示します。AD8318のパワー制御は負の検出を持つことに注意してください。VSETを下げると(これはADL5330からの高い信号の要求に対応)、ゲインは増加しようとします。

AGCループは、ADL5330の60dBゲイン制御範囲全域で信号を制御できます。温度性能は、最も重要な最高パワー範囲で最も正確になります。40dBの出力パワー範囲の上限では、直線性誤差は温度変化に対して±0.5dB以内になります。

図38. AD8318セットポイント電圧 対 ADL5330出力パワー (P<sub>IN</sub> = -1.5dBm)

ログアンプによって加わるブロードバンド・ノイズは無視できます。

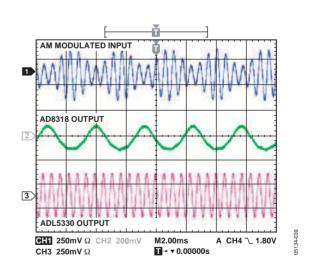

AGCループが平衡を維持するためには、AD8318がADL5330出力信号のエンベロープに追従し、ADL5330のゲイン制御入力に必要な電圧レベルを供給する必要があります。図39に、図37に示したAGCループのオシロスコープのスクリーンショットを示します。50% AM変調した100MHz正弦波をADL5330に入力しています。ADL5330の出力信号は、AD8318のセットポイント電圧1.5Vに対応したエンベロープで一定の振幅を持つ正弦波となります。また、入力エンベロープの変化に伴うAD8318によるゲイン制御応答も示しています。

図39. AM変調入力信号を示すオシロスコープのスクリーンショット

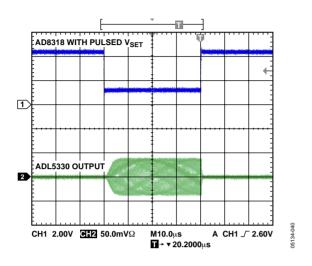

図40に、VSETパルスに対するAGC RF出力の応答を示します。VSETが1Vに減少すると、AGCループはRFバーストで応答します。応答時間と信号積分量は、AD8318 C<sub>FLT</sub>ピンの容量により制御されます。この機能は、積分アンプの周囲に使う帰還コンデンサに似ています。容量が増加すると、応答時間が遅くなります。

図40. AGCJループの応答時間を示すオシロスコープの スクリーンショット

AGCアプリケーションでAD8318を使用する方法については、AD8318の データシートを参照してください。

#### IQ変調器とのインターフェース

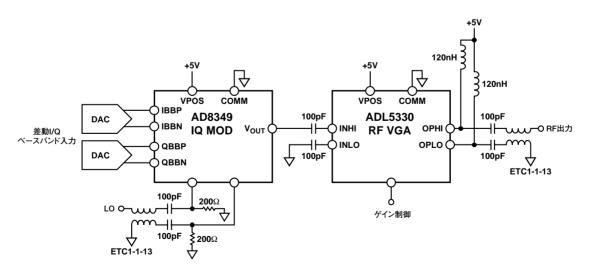

AD8349とADL5330との間のインターフェースの基本接続を図42に示します。AD8349は、出力周波数範囲700MHz~2.7GHzのRF直交変調器です。優れた位相精度と振幅バランスを提供するため、通信システムに対する高性能ダイレクトRF変調が可能になります。

AD8349の出力は $50\Omega$ 負荷を駆動するように設計されているため、ADL5330に容易にインターフェースすることができます。ADL5330の入力は、図42に示すようにシングルエンドで駆動できます。AD8345 (250MHz $\sim$ 1GHz)とAD8346 (800MHz $\sim$ 2.5GHz)の直交変調器に対しても同様の構成が可能です。

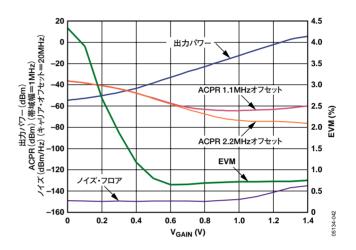

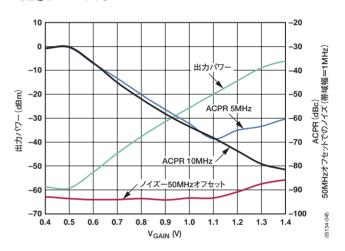

図41に、ゲイン制御電圧に対する出力パワー、EVM、ACPR、ノイズの変化を示します。 $V_{GAIN}$ は $0\sim1.4V$ の範囲で変化します。図41のプロットで、AD8349から発生された変調は、1MHzのシンボル・レートを持つ 1GHz 64 QAM波形です。ACPR値は、1.1MHzと2.2MHzのキャリア・オフセットで1MHz帯域幅を使い測定した値です。ノイズ・フロアは、20MHzキャリア・オフセットで測定した値です。

図41. 1MHzのシンボル・レートを持つ1GHz 64 QAM波形に対するV<sub>GAIN</sub> 対AD8349とADL5330の出力パワー、ACPR、EVM、ノイズ

ADL5330を駆動するAD8349の出力は、最適なEVM性能とACPR性能を提供する範囲内に制限する必要があります。システムのEVMとACPRとの間の最適な妥協点を探すための出力パワーの範囲は、AD8349の出力パワーを掃引して探します。図41に示すケースでは、AD8349の出力パワーは-15dBmに設定されています。

図42. AD8349直交変調器とADL5330とのインターフェース

### WCDMA送信アプリケーション

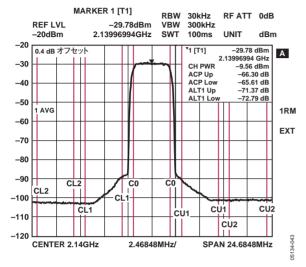

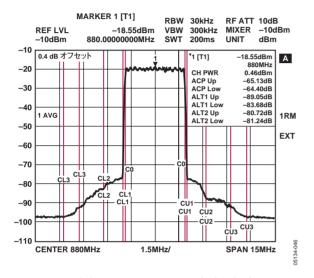

図43に、シングル・キャリアWCDMA信号(2140MHzでのテスト・モデル1-64)を送信するADL5330の出力スペクトルを示します。キャリア・パワー出力は約-9.6dBmです。ゲイン制御電圧は1.4Vで、約14.4dBのゲインを与えています。このパワー・レベルで、隣接チャンネル・パワー比ー65.61dBcを実現しています。代替チャンネル・パワー比ー71.37dBcは、ADL5330のノイズ・フロアにより支配されます。

図43. シングル・キャリアWCDMAスペクトル(2140MHz、 V<sub>GAIN</sub> = 1.4V、P<sub>IN</sub> = -23dBm)

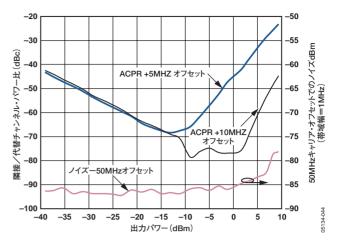

図44に、異なる入力パワー・レベルに対するACPRとノイズの変化を示します(ゲイン制御電圧は1.4Vに固定)。高いパワー・レベルで、隣接パワー比と代替チャンネル・パワー比が急増します。出力パワーが低下すると、隣接パワー比と代替チャンネル・パワー比は最小値になった後、測定値はADL5330のノイズ・フロアに支配されるようになります。このポイントで、隣接パワー比と代替チャンネル・パワー比はほぼ等しくなります。

出力パワーが低下すると、50MHzキャリア・オフセットでdBm/Hzで測定したノイズ・フロアは、最初は低下しますが、その後平坦になります。

図44. 出力パワー 対 ACPRおよびノイズ シングル・キャリアWCDMA入力 (2140MHzでのテスト・モデル1-64) V<sub>GAIN</sub> = 1.4V( 固定 )

図45に、ゲイン制御電圧に対する出力パワー、ACPR、ノイズの変化を示します。 $V_{GAIN}$ は0Vから1.4Vへ変化しますが、入力パワーは-19dBmに固定されています。

図45. V<sub>GAIN</sub> 対 出力パワー、ACPR、ノイズ、 - 19dBmの シングル・キャリアWCDMA入力 (2140MHzでのテスト・モデル1-64)

### CDMA2000送信アプリケーション

CDMA2000基地局規格への適合性をテストするため、880MHzの3キャリアCDMA2000テスト・モデル信号(3GPP2 C.S0010-B、表6.5.2.1に準拠する順方向パイロット、同期、ページング、6トラフィック)をADL5330に入力します。4.6MHz通過帯域のキャビティ調整済みフィルタを使って、デバイスに加えられる信号源から発生するノイズを削減しました。

図46に、公称条件下での出力信号のスペクトルを示します。3キャリア信号の合計P<sub>OUT</sub>は0.46dBmで、V<sub>GAIN</sub>は1.4Vです。隣接パワー比と代替チャンネル・パワー比は、それぞれ750kHzと1.98MHzのキャリア・オフセットで30kHzの帯域幅を使って測定しました。

図46. 880MHz出力スペクトル、 - 23dBm合計入力パワーの 3キャリアCDMA2000テスト・モデル、V<sub>GAIN</sub> = 1.4V、750kHzと 1.98MHzのキャリア・オフセットで測定したACPR、キャビティ調整 済みフィルタ(通過帯域 = 4.6MHz )を使って処理した入力信号

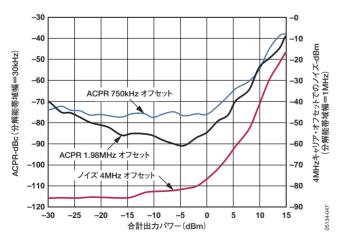

テスト中、ゲイン制御電圧を1.4Vに固定し、入力パワーを掃引しました。 図47に、合計出力パワー対ACPRおよびノイズ・フロアを示します。ノイズ・フロアは、1MHz帯域幅を使って4MHzキャリア・オフセットで測定しました。

図47. 合計出力パワー 対 ACPR 880MHz 3キャリアCDMA2000テスト・モデル、V<sub>GAIN</sub> = 1.4V( 固定 )、 750kHzと1.98MHzのキャリア・オフセットで30kHz帯域幅を使って 測定したACPR

この結果では、合計出力パワー+8dBmまで、ACPRが規格を満たしていることが示されました(750kHzで<-45dBc、1.98MHzで<-60dBc)。低い出力パワー・レベルで、1.98MHzキャリア・オフセットでのACPRは低下します。これは、ADL5330のノイズ・フロアがACPRの測定値を支配するためです。4MHzキャリア・オフセットでのノイズ測定値は、0dBm出力パワーを超ええると急速に増加し始めます。この増加はノイズが原因ではなく、キャリアによる歪みが増加するためです。出力パワーが合計0dBmを下回ると、ノイズ・フロアは-85dBmに向かって低下します。

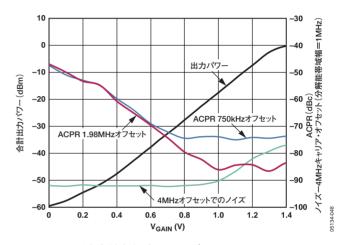

入力パワーを-23dBmに固定し、ゲイン制御入力を変えて再び出力パワーを掃引しました。V<sub>GAIN</sub>は0Vから1.4Vまで掃引されています。図48にその結果の合計出力パワー、ACPR、ノイズ・フロアを示します。

図48. V<sub>GAIN</sub> 対 合計出力パワーおよびACPR 合計入力パワー - 23dBmの880MHz 3キャリアCDMA2000 テスト・モデル、750kHzと1.98MHzのキャリア・オフセットで 30kHz帯域幅を使って測定したACPR

V<sub>GAIN</sub>=0.4Vを上回る場合でも、ACPRは規格を満たしています。ゲイン制御入力が1.0Vを下回ると、ノイズ・フロアは-90dBmを下回ります。

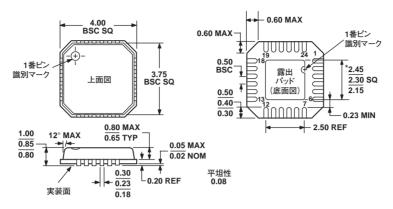

#### ハンダ処理

チップ・スケール・パッケージの裏面には、圧縮された露出パドルがあります。このパドルは内部でチップのグラウンドに接続されています。規定の電気的性能と熱放散を実現するために、パドルをPCボード上の低インピーダンスのグラウンド・プレーンにハンダ付けしてください。また、パドルの下のすべての層のグラウンド・プレーンをビアで接続し、熱抵抗を小さくすることも推奨します。

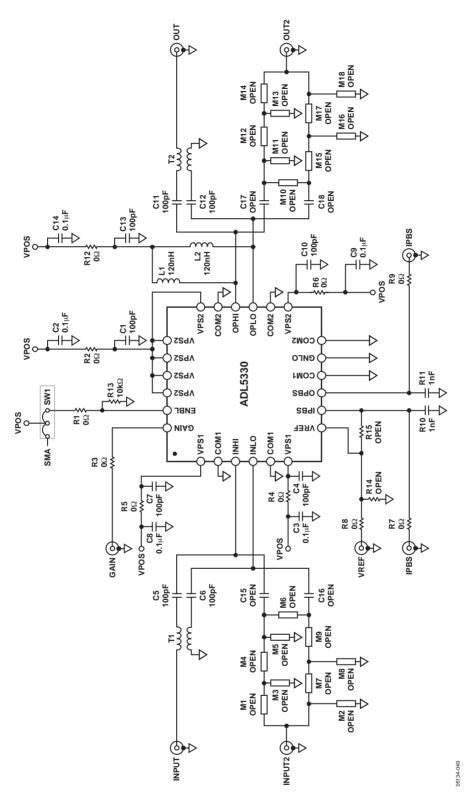

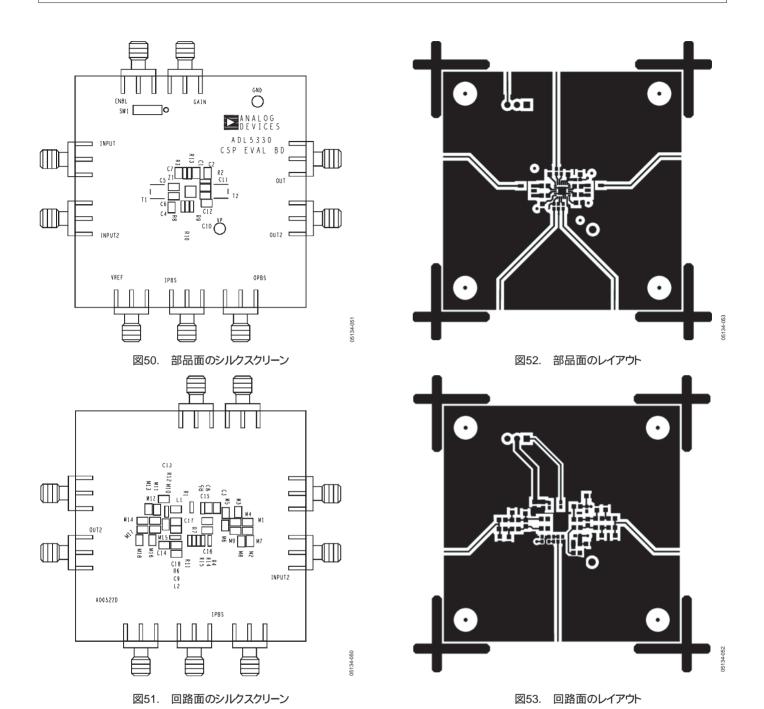

#### 評価用ボード

図49に、ADL5330評価用ボードの回路図を示します。部品面と回路面のシルクスクリーンとレイアウトを図50~53に示します。このボードには、4.75~5.25Vの範囲の単電源 (VS)を接続します。電源は100pFと 0.1 $\mu$ Fのコンデンサを各電源ピンに接続してデカップリングします。電源ピンに抵抗またはインダクタを直列接続してデカップリングを追加することもできます。表5Vに、評価用ボードのさまざまな設定オプションを示します。

ADL5330の出力ピンには、120nH RFチョークによる電源バイアスが必要です。入力ピンと出力ピンは50Ωの差動インピーダンスを持ち、ACカップリングが必要です。これらは、一対のバラン回路 (M/A-COM部品番号ETC1-1-13)を使ってシングルエンドに変換されます。

パラン・トランスの代わりに、パッシブなL部品とC部品で構成される集中 定数パラン回路を設計することもできます。部品パッドを持つ別の入力 RFパスと出力RFパスもボードの回路面に用意してあります。部品M1~ M9は入力インターフェースに、M10~M18は出力インターフェースに使 用します。100pFのDC阻止コンデンサは入力用のC15とC16、出力用のC17とC18に、それぞれ実装する必要があります。コンデンサのC5、C6、C11、C12は除去する必要があります。別セットのSMAコネクタ、INPUT2とOUT2はこの設定のために使います。

ADL5330はシングルエンドで駆動できます。この場合は、ボードの回路面にあるRF入力パスを使ってください。100pFのDCブロッキング・コンデンサをC15とC16に実装する必要がありますが、C5とC6は除去してください。INPUT2 SMAを使って、差動入力ピンの一方を駆動します。未使用ピンはグラウンドに接続します(図34)。

ADL5330をイネーブルにするには、SW1へッダのOポジションにジャンパ線を接続し、ENBLピンにハイレベル電圧を加えます。ディスエーブルにするときは、ジャンパ線を取り外します。これにより、ENBLピンが $10k\Omega$ 抵抗を介してグラウンドに接続されます。

図49. 評価用ボードの回路図

### 表5. 評価用ボードの設定オプション

| 部品                                           | 機能                                                                                                                                                                                                                                                                                                                       | デフォルト条件                                                                                                                 |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| C1~C4, C7~C10, C13, C14, R2, R4, R5, R6, R12 | 電源デカップリング。通常、電源デカップリングは、各電源ピン (VPS2ピン、18~22番ピンは隣接しているため、1対のデカップリング・コンデンサを共用)に接続した $100$ pFと $0.1$ $\mu$ Fのコンデンサから構成されます。直列インダクタまたは小さい抵抗をコンデンサの間に接続してデカップリングを強化することもできます。                                                                                                                                                 | C1、C4、C7、C10、C13 = 100pF<br>(サイズ 0603)<br>C2、C3、C8、C9、C14 = 0.1 μ F<br>(サイズ 0603)<br>R2、R4、R5、R6、R12 = 0Ω<br>(サイズ 0402) |

| T1, C5, C6                                   | 入力インターフェース。1:1バラン・トランスT1は、50Ωのシングルエンド<br>入力を50Ωの差動入力に変換します。C5とC6はDCブロッキング用です。                                                                                                                                                                                                                                            | T1 = ETC1-1-13 (M/A-COM)<br>C5、C6 = 100 pF (サイズ 0603)                                                                   |

| T2, C11, C12, L1, L2                         | 出力インターフェース。 $1:1$ バラン・トランス $T2$ は、 $50\Omega$ の差動出力を $50\Omega$ のシングルエンド出力に変換します。 $C11$ と $C2$ は $DC$ ブロッキング用です。 $L3$ と $L4$ は、出力に $DC$ バイアスを供給します。                                                                                                                                                                      | T2 = ETC1-1-13 (M/A-COM)<br>C11、C12 = 100pF(サイズ 0603)<br>L1、L2 = 120nH(サイズ 0805)                                        |

| SW1, R1, R13                                 | インターフェースのイネーブル。ADL5330をイネーブルにするには、SW1のOポジションにジャンパ線を接続し、ENBLピンにハイレベル電圧を入力します。ディスエーブルにするときは、ジャンパ線を取り外します。外部からハイレベル電圧またはローレベル電圧を加えて機能をイネーブルにするときは、SW1ヘッダの「O」と表示されたピンを使います。                                                                                                                                                  | SW1 =実装済み<br>R1 = 0 $\Omega$ (サイズ 0402)<br>R13 = 10 k $\Omega$ (サイズ 0402)                                               |

| C15~C18、M1~M18                               | 代替入出力インターフェース。評価用ボードの回路面に、別のRF入力および出力インターフェースが用意してあります。バラン・トランスを使う代わりに、L部品とC部品を使って集中定数バラン回路を構成することができます(アプリケーションの項を参照)。部品M1~M9は入力インターフェースに、M10~M18は出力インターフェースに使います。このRFパスを使うときは、DCブロッキング・コンデンサ(コンデンサC5とコンデンサC6は入力用、コンデンサC11とコンデンサC12は出力用)は接続しません。100pFのDCブロッキング・コンデンサをC15、C16、C17、C18に実装します。別のSMAコネクタ(INPUT2とOUT2)を使います。 | M1~M18 = 未実装<br>(サイズ 0603)<br>C15~C18 = 未実装<br>(サイズ 0603)                                                               |

## 外形寸法

\*JEDEC規格MO-220-VGGD-2に準拠(露出パッドの寸法を除く)

図54. 24ピン・リードフレーム・チップスケール・パッケージ[LFCSP\_VQ] 4mm×4mmボディ、超薄型クワッド (CP-24-2) 寸法単位:mm

### オーダー・ガイド

| モデル                                        | 温度範囲      | パッケージ                                | パッケージ・<br>オプション | 梱包数量  |

|--------------------------------------------|-----------|--------------------------------------|-----------------|-------|

| ADL5330ACPZ-WP <sup>1</sup> , <sup>2</sup> | -40~+85°C | 24ピン・リードフレーム・チップスケール・パッケージ(LFCSP_VQ) | CP-24-2         | 64    |

| ADL5330ACPZ-REEL7 <sup>1</sup>             | -40∼+85°C | 24ピン・リードフレーム・チップスケール・パッケージ(LFCSP_VQ) | CP-24-2         | 1,500 |

| ADL5330ACPZ-R2 <sup>1</sup>                | -40∼+85°C | 24ピン・リードフレーム・チップスケール・パッケージ(LFCSP_VQ) | CP-24-2         | 250   |

| ADL5330-EVAL                               |           | 評価用ボード                               |                 | 1     |

<sup>1</sup> Z=鉛フリー製品

<sup>2</sup> WP=ワッフル・パック