# 120dBレンジ (3nA~3mA) の デュアル・ログ・コンバータ

**ADL5310**

## 特長

フォトダイオード・インターフェースに最適化された 独立2チャンネル

6ディケードの入力ダイナミックレンジ

対数適合度:3nA~3mAで0.3dB

温度安定性にすぐれた対数出力

対数スロープ10mV/dB(200mV/dec)、

外部からのスケーリング

各インターセプトが外付け抵抗により独立して設定可能

ユーザー設定可能な出力バッファアンプ

単電源動作または両電源動作が可能

スペース効率の良い24ピン4mm×4mm のLFCSP

低消費電力:静止電流10mA以下

## アプリケーション

ゲインと吸収率の測定 マルチチャンネル・パワー・モニタリング 汎用のベースバンド対数圧縮

## 製品説明

低価格のデュアル・ログアンプADL5310\*は、広いダイナミック・レンジで入力電流をリニアなdB出力電圧に変換します。このデバイスは、レーザー、光スイッチ、減衰器、アンプの制御回路やシステム・モニタリングなどの広範囲な光通信システム・アプリケーションでの光パワー測定用に最適化されています。このデバイスは、ダイナミック・レンジを広げた(120dB)デュアルのAD8305デバイスと同等です。ADL5310は、個別に設定可能な伝達関数定数(スロープおよびインターセプト)を持つ独立した2つの信号チャンネルを内蔵していますが、消費電力とチャンネル間の一致を向上させるため、内部バイアス回路をチャンネル間で共用しています。小型のLFCSPパッケージを採用したデュアル・コンバータなので、光素子両端間のゲインまたは損失の測定でのスペース効率の良いソリューションになっています。単電源のみで動作しますが、オプションとして両電源動作も可能なため、柔軟性があります。

このADL5310は、バイポーラ・トランジスタのベース-エミッタ間電圧とコレクタ電流との間に正確な対数関係を生む最適化されたトランスリニア構造を採用しており、固有の温度依存性を補償する高精度電流による適切なスケーリング機能を持っています。入力電流ピンと基準電流ピンには3nA~3mAの範囲の電流(入力電流と基準電流の間で±60dBに制限)が流れて、VSUMの電位で決定された固定電圧に流入します。VSUMの電位は内部で500mVに設定されますが、両電源動作や、電圧入力を必要とする他のアプリケーションでは外部でグラウンドに接続できます。

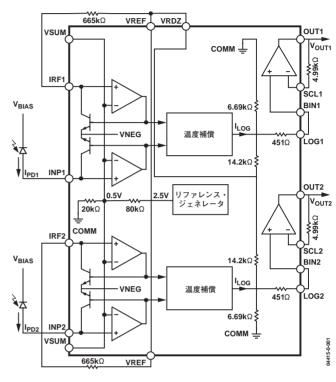

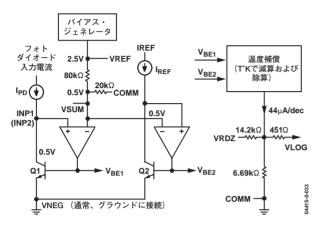

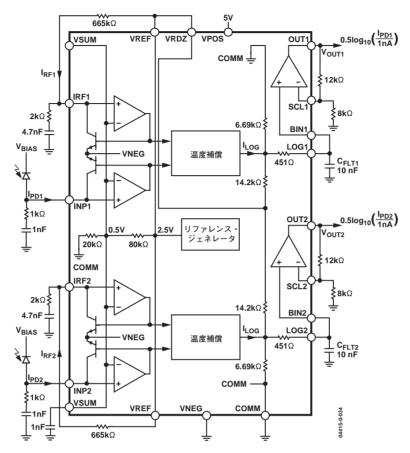

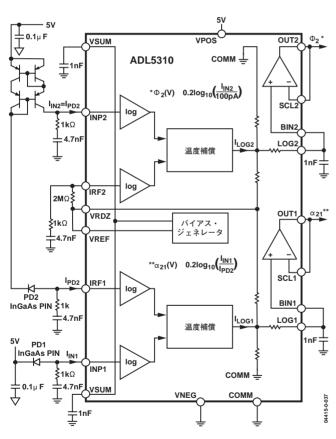

## 機能ブロック図

図1

対数スロープは公称10mV/dB(200mV/デケード)に設定されていますが、外付け抵抗と独立したバッファ・アンプを使って変更することができます。各チャンネルの対数インターセプトは各々の基準電流によって決定され、2.5VのVREFピンとIRF1およびIRF2入力の間に665k $\Omega$ の抵抗を接続して最大の入力レンジが得られるように公称3 $\mu$ Aに設定されます。VRDZをVREFに接続すると、基準電流の下側4デケードに対してxインターセプトが実質的に設定され、3 $\mu$ Aの基準電流に対して300pA(tvp)になります。

個々に最適化された基準電流を使うということは、各チャンネル入力の電流レンジ条件が異なる場合のゲインまたは吸収率の測定にADL5310を使うときに便利です。また、基準電流入力も機能的にダイナミック入力であるため、基準入力電流を分母とする対数比動作が可能です。ADL5310は、−40~+85℃で動作仕様規定されています。

\*米国特許:4,604,532、5,519,308。その他は出願中。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。本紙記載の商標および登録商標は、各社の所有に属します。

\*日本語データシートは、REVISIONが古い場合があります。最新の内容については英語版をご参照ください。 ©2003 Analog Devices, Inc. All rights reserved.

REV.0

| 本 社/東京都港区海岸1-16-1 電話03(5402)8200 〒105-6891 ニューピア竹芝サウスタワービル

## 目次

| 仕様3                          | アプリケーション・・・・・・13           |

|------------------------------|----------------------------|

| 絶対最大定格 · · · · · · 4         | キャリブレーション・・・・・・14          |

| ピン配置および機能の説明 ・・・・・・・5        | クロストークの最小化・・・・・・15         |

| 代表的な性能特性 ・・・・・・・・・・・・・・・・・・6 | 相対パワーと絶対パワーの測定・・・・・・・・・・16 |

| 一般的構造・・・・・・11                | 特性評価方法・・・・・・17             |

| 動作原理・・・・・・11                 | 評価ボード・・・・・・18              |

| インターセプトとスロープの管理・・・・・・12      | 外形寸法・・・・・・20               |

| 応答時間とノイズに対する考慮事項・・・・・・・・・・12 | オーダー・ガイド・・・・・・・・・20        |

### 改訂履歴

リビジョン0、初版

# 仕様

表1. 特に指定のない限り、V<sub>P</sub>=5V、V<sub>N</sub>=0V、T<sub>A</sub>=25°C、R<sub>REF</sub>=665kΩ、VRDZとVREFを接続。

| パラメータ         | 条件                                                                      | Min   | Тур       | Max   | 単位                               |

|---------------|-------------------------------------------------------------------------|-------|-----------|-------|----------------------------------|

| 入力インターフェース    | ピン1~6、INP1およびINP2、IRF1およびIRF2、VSUM                                      |       |           |       |                                  |

| 規定電流範囲、IPD    | INP1またはINP2ピンに流入                                                        | 3n    |           | 3m    | A                                |

| 入力電流の最小値/最大値  | INP1またはINP2ピンに流入                                                        |       |           | 10m   | A                                |

| 基準電流、IREF、範囲  | IRF1またはIRF2ピンに流入                                                        | 3n    |           | 3m    | A                                |

| 加算ノード電圧       | 内部でプリセット;ユーザー変更可能                                                       | 0.46  | 0.5       | 0.54  | V                                |

| 温度ドリフト        | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +85^{\circ}\text{C}$       |       | 0.030     |       | mV/℃                             |

| 入力オフセット電圧     | V <sub>IN</sub> -V <sub>SUM</sub> , V <sub>IREF</sub> -V <sub>SUM</sub> | -20   |           | +20   | mV                               |

| 対数出力          | ピン15および16、LOG1およびLOG2                                                   |       |           |       |                                  |

| 対数スロープ        |                                                                         | 190   | 200       | 210   | mV/dec                           |

|               | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +85^{\circ}\text{C}$       | 185   |           | 215   | mV/dec                           |

| 対数インターセプト1    |                                                                         | 165   | 300       | 535   | pA                               |

|               | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +85^{\circ}\text{C}$       | 40    |           | 1940  | pA                               |

| 対数適合度誤差       | $10\text{nA} < I_{\text{PD}} < 1\text{mA}$                              |       | 0.1       | 0.4   | dB                               |

|               | $3nA < I_{PD} < 3mA$                                                    |       | 0.3       | 0.6   | dB                               |

| 広帯域ノイズ2       | I <sub>PD</sub> > 3 μ A; 出力換算                                           |       | 0.5       |       | $\mu \text{ V}/\sqrt{\text{Hz}}$ |

| 小信号带域幅2       | $I_{PD}=3 \mu A$                                                        |       | 1.5       |       | MHz                              |

| 最大出力電圧        |                                                                         |       | 1.7       |       | V                                |

| 最小出力電圧        | V <sub>N</sub> =0Vで制限                                                   |       | 0.10      |       | V                                |

| 出力抵抗          |                                                                         | 4.375 | 5         | 5.625 | $k\Omega$                        |

| リファレンス出力      | ピン7およびピン24 (内部で短絡)、VREF                                                 |       |           |       |                                  |

| 電圧wrtグラウンド    |                                                                         | 2.45  | 2.5       | 2.55  | V                                |

|               | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +85^{\circ}\text{C}$       | 2.42  |           | 2.58  | V                                |

| 最大出力電流        | ソーシング(グラウンド接続した負荷)                                                      |       | 20        |       | mA                               |

| 出力抵抗増分        | 負荷電流< 10mA                                                              |       | 4         |       | Ω                                |

| 出力バッファ        | ピン12~14およびピン17~19: OUT2、SCL2、BIN2、BIN1、SCL1、OUT1                        |       |           |       |                                  |

| 入力オフセット電圧     |                                                                         | -20   |           | +20   | mV                               |

| 入力バイアス電流      | ピン13、14、17、18から流出                                                       |       | 0.4       |       | μΑ                               |

| 入力抵抗增分        |                                                                         |       | 35        |       | $\mathbf{M}\Omega$               |

| 出力抵抗増分        | 負荷電流<10mA;ゲイン=1                                                         |       | 0.5       |       | Ω                                |

| 出力ハイ電圧        | $R_L=1k\Omega$ (グラウンド接続)                                                |       | $V_P = 0$ | .1    | V                                |

| 出力ロー電圧        | $R_L=1k\Omega$ (グラウンド接続)                                                |       | 0.10      |       | V                                |

| ソース/シンクのピーク電流 |                                                                         |       | 30        |       | mA                               |

| 小信号带域幅        | ゲイン=1                                                                   |       | 15        |       | MHz                              |

| スルーレート        | 出力振幅0.2~4.8V                                                            |       | 15        |       | V/μ s                            |

| 電源            | ピン8および9: VPOS;ピン10、11、20: VNEG                                          |       |           |       |                                  |

| 正電源電圧         | $(V_P - V_N) \le 12V$                                                   | 3     | 5         | 12    | V                                |

| 静止電流          | 入力電流< 10 μ A                                                            |       | 9.5       | 11.5  | mA                               |

| 負電源電圧(オプション)  | $(V_P - V_N) \le 12V$                                                   | -5.5  | 0         |       | V                                |

## 絶対最大定格

表2. ADL5310のストレス定格

| パラメータ                              | 定格         |

|------------------------------------|------------|

| 電源電圧V <sub>P</sub> -V <sub>N</sub> | 12V        |

| 入力電流                               | 20mA       |

| 内部消費電力                             | 500mW      |

| heta JA                            | 35℃/W¹     |

| 最大ジャンクション温度                        | 125℃       |

| 動作温度範囲                             | -40~+85°C  |

| 保存温度範囲                             | -65∼+150°C |

| ピン温度範囲(ハンダ処理、60秒)                  | 300℃       |

絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定は、ストレス定格のみを指定するものであり、この仕様の動作に関するセクションに記載されている規定値以上でのデバイス動作を定めたものではありません。長時間デバイスを絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

#### 注意

ESD (静電放電)の影響を受けやすいデバイスです。人体や試験機器には4,000Vもの高圧の静電気が容易に蓄積され、検知されないまま放電されることがあります。本製品は当社独自のESD保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、回復不能の損傷を生じる可能性があります。したがって、性能劣下や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

REV.0

4

<sup>1.</sup> パドルをハンダ付け。

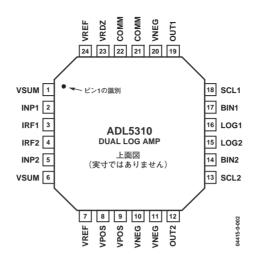

# ピン配置および機能の説明

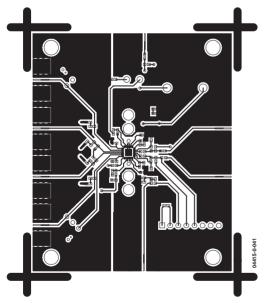

図2. 24ピンLFCSPのピン配置

表3. ピン機能の説明

| ピン番号       | 記号   | 機能                                                                                                         |

|------------|------|------------------------------------------------------------------------------------------------------------|

| 1, 6       | VSUM | ガード・ピン。INP1およびINP2入力電流ラインのシールドに使用、さらに入力加算ノード電位の調整 (オプション)に使用。ピン1とピン6は内部で短絡。                                |

| 2          | INP1 | チャンネル1の分子入力。フォトダイオード電流IPDIが流入(シンク)。通常、光電流がINP1に流入するようにフォトダイオードのアノードに接続。                                    |

| 3          | IRF1 | チャンネル1の分母入力。基準電流IRFIが流入(シンク)。                                                                              |

| 4          | IRF2 | チャンネル2の分母入力。基準電流I <sub>RF2</sub> が流入(シンク)。                                                                 |

| 5          | INP2 | チャンネル2の分子入力。フォトダイオード電流I <sub>PD2</sub> が流入(シンク)。通常、光電流がINP2に流入するようにフォトダイオードのアノードに接続。                       |

| 7, 24      | VREF | 2.5Vのリファレンス出力電圧。ピン7とピン24は内部で短絡。                                                                            |

| 8, 9       | VPOS | 正電源、(V <sub>P</sub> -V <sub>N</sub> )≤12V。両ピンは外部で接続する必要があります。                                              |

| 10, 11, 20 | VNEG | オプションの負電源 $V_{No}$ このピンは通常グラウンドに接続されます。使い方の詳細は「一般的構造」および「アプリケーション」を参照してください。すべての $VNEG$ ピンは外部で接続する必要があります。 |

| 12         | OUT2 | チャンネル2のバッファ出力                                                                                              |

| 13         | SCL2 | チャンネル2のバッファ・アンプ反転入力                                                                                        |

| 14         | BIN2 | チャンネル2のバッファ・アンプ非反転入力                                                                                       |

| 15         | LOG2 | チャンネル2の対数フロントエンドの出力                                                                                        |

| 16         | LOG1 | チャンネル1の対数フロントエンドの出力                                                                                        |

| 17         | BIN1 | チャンネル1のバッファ・アンプ非反転入力                                                                                       |

| 18         | SCL1 | チャンネル1のバッファ・アンプ反転入力                                                                                        |

| 19         | OUT1 | チャンネル1のバッファ出力                                                                                              |

| 21, 22     | COMM | アナログ・グラウンド。ピン21とピン22は内部で短絡。                                                                                |

| 23         | VRDZ | インターセプト・シフト・リファレンス入力。インターセプトの位置を決めるためにVLOGにオフセットを与える抵抗デバイダネットワークの最上部。通常、VREFに接続。バイポーラ出力が必要な場合はグラウンド接続も可能。  |

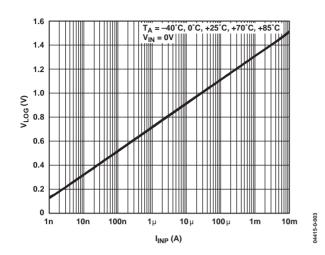

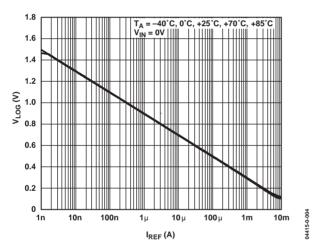

## 代表的な性能特性

特に指定のない限り、V<sub>P</sub>=5V、V<sub>N</sub>=0V、R<sub>REF</sub>=665kΩ、T<sub>A</sub>=25℃

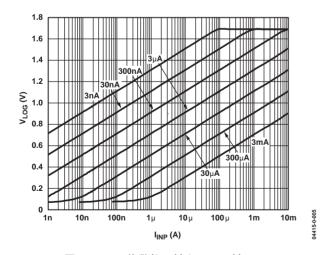

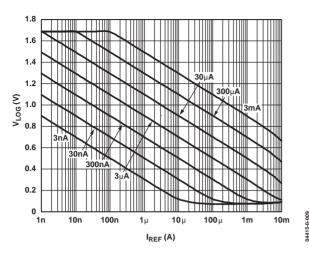

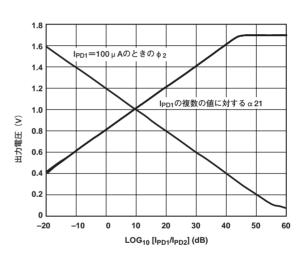

図3. VLOG対INP

図4.  $V_{LOG}$ 対 $I_{REF}$  ( $I_{INP}$ =3  $\mu$  A)

図5. I<sub>REF</sub>の複数値に対するV<sub>LOG</sub>対I<sub>INP</sub>、 3nAから3mAへのディケード変化

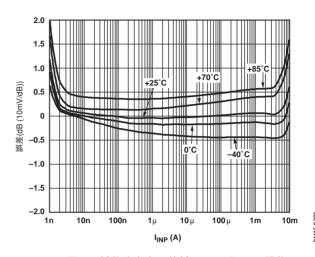

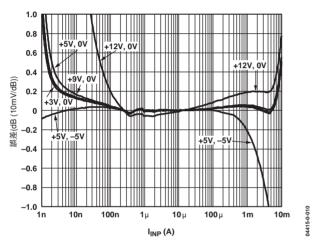

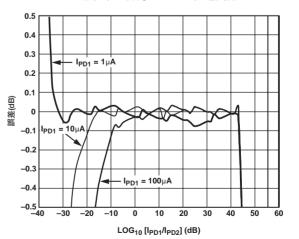

図6. 対数適合度誤差対INP、25℃に正規化

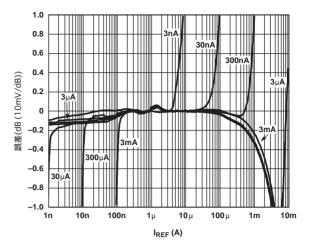

図7. 対数適合度誤差対I<sub>REF</sub>、25℃に正規化(I<sub>INP</sub>=3 μA)

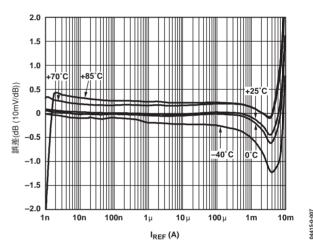

図8. I<sub>REF</sub>の複数値に対する対数適合度誤差対I<sub>INP</sub>、 3nAから3mAへのディケード変化

REV.0

6

図9. IINPの複数値に対するVLOG対IREF、 3nAから3mAへのディケード変化

図10. 種々の電源条件に対する対数適合度誤差対I<sub>INP</sub>

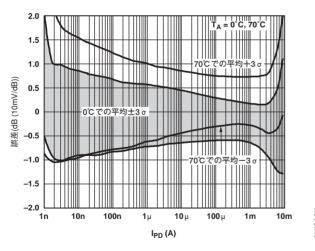

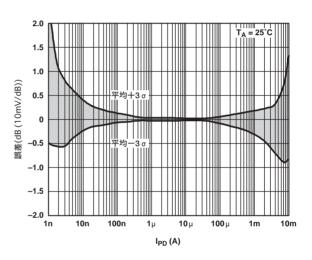

図11. 対数適合度誤差の分布(平均の両側3 $\sigma$ )

図12. I<sub>INP</sub>の複数値に対する対数適合度誤差対I<sub>REF</sub>、 3nAから3mAへのディケード変化

図13. 対数適合度誤差の分布(平均の両側3 $\sigma$ )

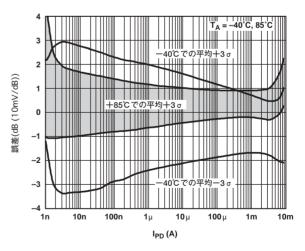

図14. 対数適合度誤差の分布(平均の両側3σ)

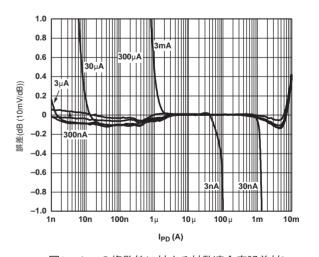

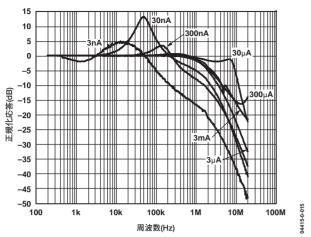

図15. 小信号AC応答、I<sub>INP</sub>からV<sub>OUT</sub> (A<sub>V</sub>=1) (5%正弦波変調、3nAから3mAへのディケード変化)

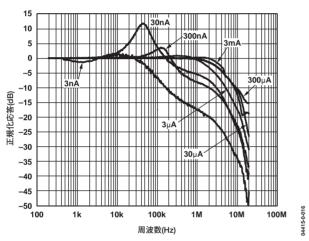

図16. 小信号AC応答、I<sub>REF</sub>からV<sub>OUT</sub> (Av=1) (5%正弦波変調、3nAから3mAへのディケード変化)

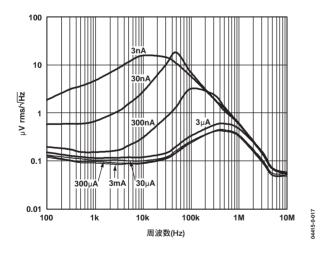

図17.  $V_{OUT}$ でのスポット・ノイズ・スペクトル密度の 周波数特性( $A_V$ =1)、 $I_{INP}$ の3nAから3mAへのディケード変化

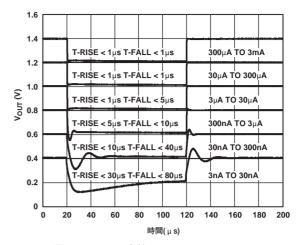

図18. パルス応答—I<sub>INP</sub>からV<sub>OUT</sub> (A<sub>V</sub>=1)、 連続1ディケード変化

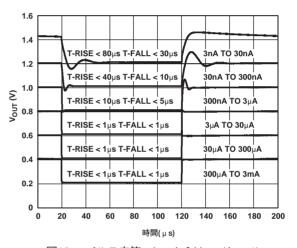

図19. パルス応答—I<sub>REF</sub>からV<sub>OUT</sub> (A<sub>V</sub>=1)、 連続1ディケード変化

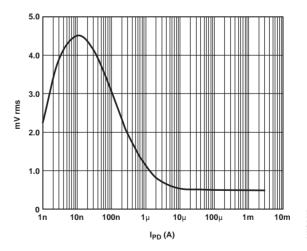

図20. V<sub>OUT</sub>での総合広帯域ノイズ電圧対I<sub>INP</sub> (A<sub>V</sub>=1)

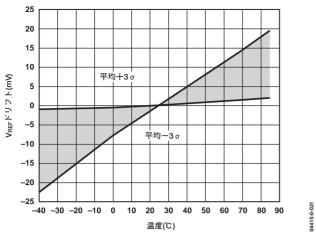

図21. V<sub>REF</sub>ドリフト対温度(平均の両側3 σ)、25℃に正規化

図24. V<sub>INPT</sub>のドリフト対温度(平均の両側3 σ)、25℃に正規化

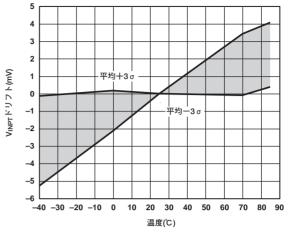

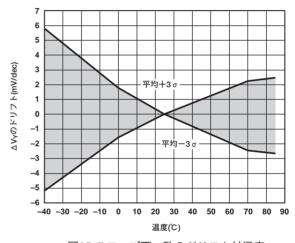

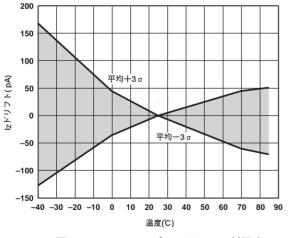

図22. スロープのドリフト対温度(平均の両側3 $\sigma$ )、25 $^{\circ}$ に正規化

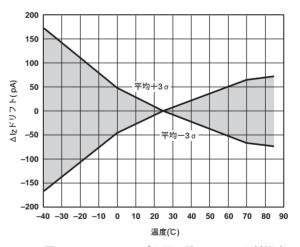

図25.スロープ不一致のドリフト対温度 (V<sub>Y1</sub>ーV<sub>Y2</sub>、平均の両側3 σ )、25℃に正規化

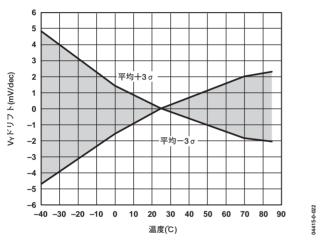

図23. インターセプトのドリフト対温度 (平均の両側3σ)、25℃に正規化

図26. インターセプト不一致のドリフト対温度 (I<sub>Z1</sub>-I<sub>Z2</sub>、平均の両側3 σ) 、25℃に正規化

REV.0

9

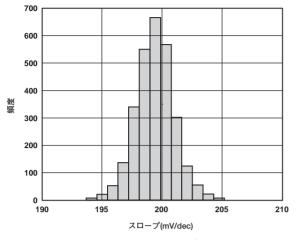

図27. 対数スロープの分布

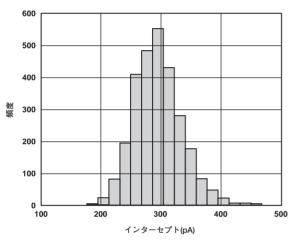

図28. 対数インターセプトの分布

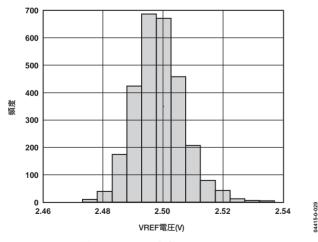

図29. V<sub>REF</sub>の分布(R<sub>L</sub>=100kΩ)

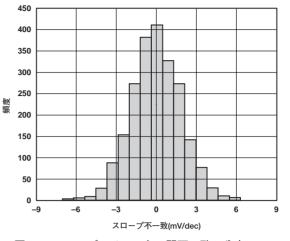

図30. スロープのチャンネル間不一致の分布(V<sub>Y1</sub>-V<sub>Y2</sub>)

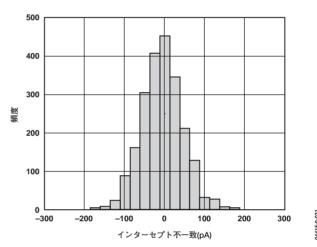

図31. インターセプトのチャンネル間不一致の分布( $I_{Z1}-I_{Z2}$ )

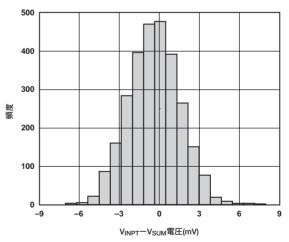

図32. オフセット電圧の分布(VINPT-VSUM)

## 全体的構造

ADL5310は光ケーブル管理システムの要求を満たす広範囲なインターフェース条件に対応しており、さらに多くの非光アプリケーションでも使用できます。以下に、このユニークなトランスリニア・ログアンプの構造について説明します。図33に、2つの同じ内蔵ログアンプの内の1つについて、主要な構成要素を示します。

図33. 1個のログアンプの簡略化した回路図

フォトダイオード電流 $I_{PD}$ は入力ピンINP1またはINP2から入力されます。これらのノードの電圧は、JFETオペアンプのオフセット電圧が小さいため、隣接するガード・ピンVSUMおよびリファレンス電流入力IRF1とIRF2の電圧にほぼ等しくなっています。トランジスタQ1は式1に示すように、 $I_{PD}$ を対応する対数電圧に変換します。単電源電圧の通常のケースの場合、 $V_{SUM}$ の正の有限値はQ1のコレクタにバイアスを与えるために必要です。これは内部で0.5Vに設定されます。この値はVREFピンに出力される2.5Vリファレンス電圧の1/9です。両VREFピンは、両VSUMピンと同様に内部で短絡されています。VSUMピンの抵抗は公称16k $\Omega$ で、一般的なバイアス源用ではありません。

また、ADL5310は、VNEGピンのオプションの負電源電圧 $V_N$ の使用もサポートしています。 $V_N$ が0.5Vかそれより負側にある場合、VSUMをグラウンドに接続することができます。そのため、INP1、INP2、IRF1、IRF2はこの電位とみなされます。これにより、片方または両方の入力に直列抵抗を接続すると、電圧入力の対数コンバータとしての動作が可能になります。インターセプト値を維持するために、各チャンネルの $I_{REF}$ を設定する抵抗を調節する必要があることに注意してください。また、Q1とQ2のコレクタ-エミッタ間電圧が大きな $V_N$ になると、自己発熱の影響によって大きな入力電流で誤差が発生することにも注意が必要です。

入力に依存するQ1の $V_{BE1}$ が、 $I_{REF}$ で動作している2番目のトランジスタQ2の基準 $V_{BE2}$ と比較されます。 $I_{REF}$ は外部で発生され、推奨値3 $\mu$ Aに設定されます。ただし、対数適合度は少し低下しますが、数ディケード範囲の他の値を使うことができます。

#### 動作原理

BJT (バイポーラ接合トランジスタ) のベース-エミッタ間電圧は、式1 で表わせます。この式は、そのまま基本的な対数の性質を表しています。

$$V_{BE} = kT/q \ln(I_C/I_S) \tag{1}$$

ここで、

Icはコレクタ電流、

$I_S$ はスケーリング電流で、通常はわずか $10^{-17}$ A、kT/qは熱電圧、絶対温度(PTAT)に比例し、300 Kで25.85mV.

Isは正確に決定されることはなく、強い温度依存性を示し、-35~+85℃の間で $10^9$ のオーダーで変化します。このため、BJTを正確な対数素子として使うには、この温度依存性の両方を消去する必要があります。

特性の一致したBJT対のベース-エミッタ間電圧の差(一方はフォトダイオード電流 $I_{PD}$ で動作し、他方は基準電流 $I_{REF}$ で動作)は、次のように表すことができます。

$$V_{BEI} - V_{BE2} = kT/q \ln(I_{PD}/I_S) - kT/q \ln(I_{REF}/I_S)$$

$$= \ln(10) kT/q \log_{10}(I_{PD}/I_{REF})$$

$$= 59.5 mV \log_{10}(I_{PD}/I_{REF}) (T = 300 K)$$

(2)

これにより、式1に含まれている不確かな、温度依存のサチレーション電流 $I_s$ が消去されます。kT/qの温度変動をなくするために、この差電圧にはアナログデバイダに特有な処理が行われます。この処理は式2に変数を1つ追加します。この処理の出力(電圧モードから電流モードへの変換も含む)は、温度補正された、中間的な電流値になります。

$$I_{LOG} = I_Y \log_{10}(I_{PD}/I_{REF}) \tag{3}$$

ここで、 $I_Y$ は温度安定性にすぐれた正確なスケーリング電流であり、関数 (ディケードごとの電流変化)のスロープを決定します。 ADL5310の場合、 $I_Y$ は44 $\mu$ Aで、 $I_{PD}$ と $I_{REF}$ のすべての値に対して、44 $\mu$ A/ディケードの温度非依存のスロープが得られます。その後、この電流は電圧モード出力 $V_{LOG}$ (スケール:200mV/ディケード)に 逆変換されます。

$I_{PD}$ = $I_{REF}$ ではこの出力がゼロになることは明らかで、入力電流がより小さい値では負側に振れることが必要です。これを回避するため、 $I_{REF}$ は $I_{PD}$ の最小値と同程度に小さい必要があります。このため、VRDZを直接VREFに接続するときは、VLOGにオフセット電圧を加えて0.8Vだけ上にシフトさせます。これにより、インターセプトが $3\,\mu$  Aから300pAへ、左に4ディケード移動します (200mV/ディケードで)。

$$I_{LOG} = I_Y \log_{10}(I_{PD}/I_{INTC}) \tag{4}$$

ここで、 $I_{INTC}$ はインターセプト電流の動作値です。 $I_{PD}$ 値<  $I_{INTC}$ 値なので $V_{LOG}$ が負になり、これに対処するには、十分な値の負電源が必要になります。

電圧 $V_{LOG}$ は、4.55 $k\Omega$ の内部抵抗に $I_{LOG}$ を流して発生させます。この内部抵抗は、グラウンドに接続した6.69 $k\Omega$ の抵抗と、VRDZピンに接続した14.2 $k\Omega$ 抵抗(一般に2.5Vのリファレンス電圧VREFに接続)との並列接続で構成されています。LOG1 (LOG2)ピンで、出力電流 $I_{LOG}$ は次の電圧を発生させます。

$$V_{LOG} = I_{LOG} \times 4.55k \Omega$$

$$= 44 \mu \text{ A} \times 4.55k \Omega \times \log_{10} (I_{PD}/I_{INTC})$$

$$= V_Y \log_{10} (I_{PD}/I_{INTC})$$

(5)

ここで、 $V_Y=200$ mV/ディケード、すなわち<math>10mV/dBです。LOG1 (LOG2)に抵抗負荷を接続すると、このスロープが小さくなり、全体にスケーリングが不確定になることに注意してください。これは、オフチップ負荷に比べてオンチップ抵抗の方が変動しやすいことに起因しています。このため、この方法はおすすめできません。

また、両電源  $(V_P \& V_N)$ を使う場合には、 $V_{LOG}$ はグラウンドの下側に振れることがあります。 $V_N \ge -0.5$ Vの場合、単にVSUMをグラウンドに接続するだけで、入力ピンINP1 (INP2)およびIRF1 (INP2)をグラウンド・レベルにすることができます。大きな負電源を使う場合は、自己発熱によって大きな電流での精度が低下するため、入力BJTデバイスでの消費電力を制限するように注意が必要です。

### インターセプトとスロープの管理

単電源を使う場合は、6デケードすべての入力電流範囲での動作を可能にするため、VRDZをVREFに直接接続する必要があります。「動作原理」で注記したように、この接続によりLOG1ピンとLOG2ピンに0.8Vの正確なオフセット電圧が加わるため(4デケードに相当)、次に示す対数伝達関数が得られます。

$$V_{LOG} = V_Y \log_{10}(10^4 \times I_{PD}/I_{REF})$$

=  $V_Y \log_{10}(I_{PD}/I_{INTC})$  (6)

ここで、 $I_{INTC}=I_{REF}/10^4$ 。

したがって、実効インターセプト電流 $I_{INTC}$ は $I_{REF}$ の1/1000で済みます。  $I_{REF}$ = $3 \mu$  Aの推奨値を使った場合、300pAに該当します。

スロープを小さくするときは、ログアンプ出力ピン(LOG1または LOG2)とグラウンドとの間に抵抗を接続します。この方法は、オンチップ抵抗と接続した抵抗の比が正しくない場合には、良くない結果になってしまいます。また、10mV/dBの基本スロープを小さくする必要はほとんどありませんが、もし必要な場合は、バッファ・アンプの低インピーダンス出力で影響を受けるようにします。このバッファ・アンプは、このようなキャリブレーション・ミスを防止して、大きなスロープの使用を可能にするために使われています。

ADL5310の各バッファはもともと、レールtoレールの出力振幅、優れた負荷駆動能力、15MHz (typ)の単位ゲイン帯域幅を持つ汎用オペアンプです。このバッファは、ゲインを提供するためや、標準の帰還ネットワークを使ってスロープ電圧 $V_Y$ を大きくする他に、高次ローパス・フィルタ、閾値検出器、その他のさまざまな機能を実現するためにも使うことができます。これらのアプリケーションの詳細は、AD8304のデータシートを参照してください。

## 応答時間とノイズに対する考慮事項

ADL5310の応答時間と出力ノイズは、基本的には信号電流 $I_{PD}$ の関数になっています。電流が小さい場合、帯域幅は $I_{PD}$ に比例します(図15)。出力の低周波電圧ノイズ・スペクトル密度も $I_{PD}$ の関数であるため(図17)、 $I_{REF}$ が小さい場合に増加します。トランスリニア・ログアンプのノイズ性能と帯域幅性能の詳細は、AD8304のデータシートを参照してください。

図34. 固定インターセプト使用時の基本接続

ADL5310は、光管理システムや、広い電流範囲を等価な対数値に変換する(すなわち、デシベル値で表す) 同様なアプリケーションで使い易くなっています。各入力で1つの電流を測定する場合の基本接続を図34に示します。図には、後で説明するように、必須でない部品もいくつか含まれています。

VREFと入力ピンINP1 (またはINP2)との間の2Vの電位差は、外付け抵抗665k $\Omega$  (R<sub>RF1</sub>とR<sub>RF2</sub>)と組み合わさって、3 $\mu$ Aの基準電流 (I<sub>RF1</sub>とI<sub>RF2</sub>)をピンIRF1とピンIRF2に流します。VRDZとVREFを接続すると、LOG1とLOG2の電圧が0.8V持ち上がり、実質的に各インターセプト電流I<sub>INTC</sub>が10<sup>4</sup>だけ低下されて、300pAになります。I<sub>REF</sub>には広範囲な値(3nA~3mA)が使用できます。このような変更の効果を図5と図8に示します。

インターセプトの安定性を評価する際には、 $R_{RF1}$  ( $R_{RF2}$ )の温度変化を考慮する必要があります。また、非常に小さい値の $I_{RF1}$  ( $I_{RF2}$ )を使用すると、全体ノイズも増えます。固定インターセプトのアプリケーションでは、大きな基準電流を使用することには何の利点もありません。これは、単電源で動作させる場合、ダイナミック・レンジの下端側電流が圧縮されるだけだからです。このノードのノイズを最小化するために、チャンネル間クロストークを小さくするために、クリーンな基準電流の発生を助けるために、VSUMとグラウンドの間にコンデンサを接続することが強く推奨されます。

さらに、各入力とリファレンス・ピン(INP1、INP2、IRF1、IRF2)には、 直列の抵抗とコンデンサで構成された補償回路が付いています。 フォトダイオードの接合容量と入力システム周辺のボード・パターン の回路容量が一緒になって極が形成され、この極は入力電流によ って広範囲に変化します。RC回路は、この極周波数を小さくすると 同時に、入力システムに固有な他の極を補償するためにゼロ点を 追加することにより、システムを安定させます。一般に、1nFと1kΩ による回路は、ほぼすべてのフォトダイオード・インターフェースを扱 うことができます。大きなアクティブ領域を持つフォトダイオードを使 う場合、または入力パターンが長い場合には、安定性を高めるため にコンデンサ値を大きくする必要があります。信号とリファレンスの 入力システムが同じでも、IRFI (IRF2)の電流範囲全体の温度限界で のリファレンス入力の安定動作を確実にするには、さらに注意が必 要です。ピンIRF1 (IRF2)とグラウンドの間に4.7nFと2kΩのフィルタ 部品を接続することが推奨されます。補償回路のようなクリティカル な場所には、常に温度安定性にすぐれた部品を使う必要がありま す。Y5Vタイプのチップ・コンデンサは温度安定性が悪いので使用 しないようにします。

LOG1 (LOG2)とグラウンドの間に接続したオプションのコンデンサは、このピンの $5k\Omega$ の抵抗との組み合わせで、1次のローパス・フィルタを構成します。たとえば、 $10nFのC_{FLT}$ を使うと、3dBコーナー周波数は3.2kHzになります。このようなフィルタは出力ノイズの削減に有効で、特に $I_{PD}$ が小さい場合に有効です。高次フィルタは、総合ノイズを抑えるのに、さらに効果的です。AD8304のデータシートに例を記載しています。

LOG1 (LOG2)での基本スケーリングは0.2V/デケードなので、バッファ出力での4Vの振幅は20デケードに相当し、レールtoレールの電圧範囲を活用するためにスロープを大きくすることは、しばしば有効です。説明のために、図34の両チャンネルでは、0.5V/ディケードの全体スロープ(25mV/dB)を使っています。このため、 $I_{REF}$ =3  $\mu$  Aを使うと、 $V_{LOG}$ は0.2V@ $I_{PD}$ =3nAから1.4V@ $I_{PD}$ =3mAまで変化します。バッファ出力は0.5Vから3.5Vまで変化し、これは120dB(電気的に。光パワーでは60dB)のダイナミックレンジに相当します。

負電源を使ったスロープとインターセプトの調節の詳細と、その他のアプリケーションはAD8305のデータシートに記載しています。

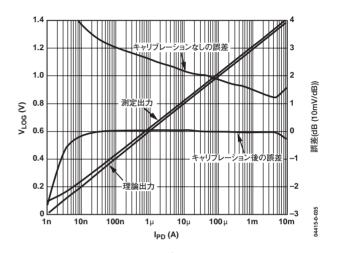

#### キャリブレーション

図34のように構成された場合、ADL5310の各チャンネルのLOG1 (LOG2)での公称スロープと公称インターセプトは、200mV/デケードと300pAになります。これらの値は調整できず、スロープだけが温度に対して7.5%まで変わることができます。このため、精度を上げるにはシンプルなキャリブレーションを行うことをお薦めします。ランダムに選択されたAD8305ログアンプ対に比べて、ADL5310のスロープとインターセプトの一致は良くなっていますが、仕様に規定した精度は各チャンネルを個別にキャリブレーションした場合にのみ実現できます。

図35. 測定精度を上げるための2ポイント・ キャリブレーションの使用

図35に、2ポイント・キャリブレーション方法を使った場合の精度の改善を示します。キャリブレーションを実行するには、 $10nA\sim1mA$ のリニアな動作範囲で2つの既知電流 $I_1$ と $I_2$ を入力します。その結果の出力 $V_1$ と出力 $V_2$ を測定して、スロープmとインターセプトbを計算します。

$$m = (V_1 - V_2)/[\log_{10}(I_1) - \log_{10}(I_2)]$$

(7)

$$b = V_I - m \times \log_{10}(I_I) \tag{8}$$

同じキャリブレーションを、2つの既知光パワー $P_1$ と $P_2$ を使って行うこともできます。この方法を使うと、測定システム全体のキャリブレーションが可能になると同時に、入射光パワーと $V_{LOG}$ 電圧の間のシンプルな関係が得られます。

$$m = (V_1 - V_2)/(P_1 - P_2) \tag{9}$$

$$b = V_l - m \times P1 \tag{10}$$

図35のキャリブレーションなしの誤差は、被測定出力のスロープが200mV/ディケード(実際には194mV/ディケード)と仮定して求めています。この不一致を補正すると、測定誤差は最大3dB小さくなります。

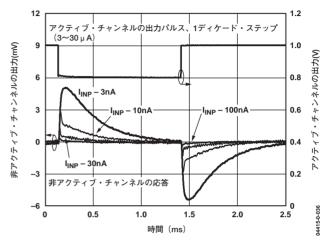

### クロストークの最小化

広いダイナミックレンジの対数コンバータ2個を1つのICに組み込むと、チャンネル間アイソレーションの問題が生じます。クロストーク性能を許容レベルに抑えるには、いくつかの領域で特別な注意が必要です。特に、一方または両方のチャンネルが非常に小さい入力電流で動作する場合には注意が必要です。クロストークを小さく抑えるには(全体の安定性にも必要)、細心の電源バイパスと注意深いボード・レイアウトが重要な第一ステップです。

バイアス回路の共用はチャンネル間一致を改善し、消費電力を削減しますが、この共用は対策が必要なクロストーク源になっています。各VSUMピン(内部で短絡)は、少なくとも1nFのコンデンサでグラウンドにバイパスする必要があります。さらに、最小電流(<30nA)で動作させるには20nFコンデンサが推奨されます。VSUMは、最初の入力が直面する小さい電流での帯域幅制限なしで、各入力システムのリファレンス電圧入力として機能するため、特に重要です。入力帯域幅内におさまっている、VSUMピンへの外乱はループによりトラッキングされ、出力に外乱を発生させません(IRF1とIRF2での電圧変動に起因する基準電流の多少の乱れは別)。

このため、 $16k\Omega(typ)$ のソース抵抗を持つVSUMでの極周波数は、入力される最小の入力電流に対する入力システム帯域幅の最小値より下側に設定する必要があります。VSUMでの低周波ノイズも、使用可能な帯域幅内でループによってトラッキングされるため、これもVSUMでの $16k\Omega$ ソース抵抗による熱ノイズの出力でのノイズ成分を減らす基準になります。

各VSUMピンの10nFのコンデンサ (等価な並列値20nF)と16k $\Omega$ のソース抵抗の組み合わせにより、500Hzに極が形成されます。これは、最小入力電流3nAに対する帯域幅より十分下側に位置します。

残留クロストークの外乱は最小電流で、特に2つの理由から問題になります。1つ目は、ループは制限された帯域幅を超える加算ノードの外乱を阻止できません。2つ目の理由は、残留外乱に対する最小電流でのセトリング応答は、1デケードまたは2デケード上の入力電流に対する応答より、はるかに低速になることです(図18)。

図36. 種々の入力電流値に対するクロストーク・パルス応答

図36に、いくつかの非アクティブ・チャンネルのDC電流値での、アクティブ・チャンネルの入力に1デケードの電流ステップを加えたときの、非アクティブ・チャンネル(DC入力)の応答の測定値を示します。一方または両方のチャンネルが非常に小さい入力電流で動作しているとき、既知の過渡現象の後で適切なセトリング・タイムを得るには、システムについて、さらなる考慮も必要です。

### 相対パワーと絶対パワーの測定

ADL5310は正しくキャリブレーションされると、正確な絶対光パワ ーの測定が可能な2つの独立したチャンネルを提供します。光アン プや可変減衰器のような光ネットワーク・エレメントの両端の相対ゲ インまたは相対吸収率を測定することが必要になることがあります。 各チャンネルの対数スロープとインターセプトが等しければ、各チ ャンネルの出力信号の差をとることで簡単に測定できます。実際に は、チャンネル間の不一致があり、補正されていない場合は、広範 囲な入力レベルで大きな誤差が発生します。信号の後処理によっ て個々のチャンネルの特性を明らかにすることができます。それに は、測定された対数電圧に対する入力レベル期待値の簡単な計算 が必要です。その後で、相対ゲインまたは相対吸収率の測定のた めに、デジタル領域で2つの信号レベルの差をとります。もっと簡単 なアナログ構成には、カレント・ミラーの使用が含まれます(図37)。 カレント・ミラーを使って、PD2のカソード光電流を複製した逆極性 の電流を、ADL5310のチャンネル2に入力します。この方法を使う と、一方のチャンネルをPD2に入射する光信号の絶対パワー・メー タとして使い、他方のチャンネルを2つの入力信号の対数比を直接 計算するために使うことができます。

図に示すカレント・ミラーは修正したWilsonミラーです。修正したWilsonミラーは安定性に優れた温度特性を提供しますが、他のカレント・ミラー回路も使うことができます。カレント・ミラーをデザインするときは、温度勾配とベータ不一致の影響を小さくするために、良く特性の一致したトランジスタ対を使うことが重要です。

図37のソリューションでは、チャンネルの不一致が問題になることはなくなっています。チャンネルのスロープ特性とインターセプト特性は、別々にキャリブレーションできるようになっています。精度は、キャリブレーションされた電流源の対を使って確認しています。図37の回路の性能を図38と図39に示します。種々のパワー・レベルでの複数の伝達関数および誤差曲線を示しています。5ディケードの範囲にわたって、精度は0.1dBより優れています。大きな $I_{IN}$ 入力電流では、ダイナミックレンジは少し減少しています。これは、VLOGピンの使用可能な振幅が制限されているためであり、入力と出力の光タップ結合比を注意深く選択することで取り戻すことができます。

図37. 修正したWilsonカレント・ミラーを使った、 絶対パワーと相対パワーの測定アプリケーション

図38. WilsonミラーとADL5310の組み合わせの、 吸収率と絶対パワーの伝達関数

図39. WilsonミラーとADL5310組み合わせの対数適合度、 10mAのチャンネル1の入力電流I<sub>IN1</sub>で正規化

### 特性評価方法

ADL5310は、高精度電流入力ログ・コンバータとして特性評価しています。これは、フォトダイオードの発光で正確な光電流を発生させるのが実用的でないためです。テスト電流は、Keithley 236のような良くキャリブレーションされた電流源、または電圧源から入力ピンへ接続した大きい値の抵抗を使って発生させました。非常に小さい入力電流を使う場合は、十分な注意が必要です。たとえば、電流ジェネレータからのトライアック出力接続はVSUMに接続されたガードと一緒に使用しました。PCボードの入力パターンは、隣接パターンをVSUMに接続して保護しました。

これらの対策は、リーク電流パスの危険性を少なくするために必要です。INP1 (INP2)ピンの公称バイアスを0.5Vとすると、グラウンドまでのリーク・パス抵抗 $1G\Omega$ によって入力から0.5nAが差し引かれるので、3nAのソース電流に対して-1.6dBの誤差になります。さらに、入力ピンの非常に高い感度と特性評価時に一般に必要とされる長いケーブルによって、60HzとRFの放射が大きな測定誤差を発生させることがあります。これらのスプリアス信号の混入を防止するには、注意深い保護技術が不可欠です。

テスト・セットアップ、その他の情報は、AD8305およびADL5306のデータシートに記載しています。

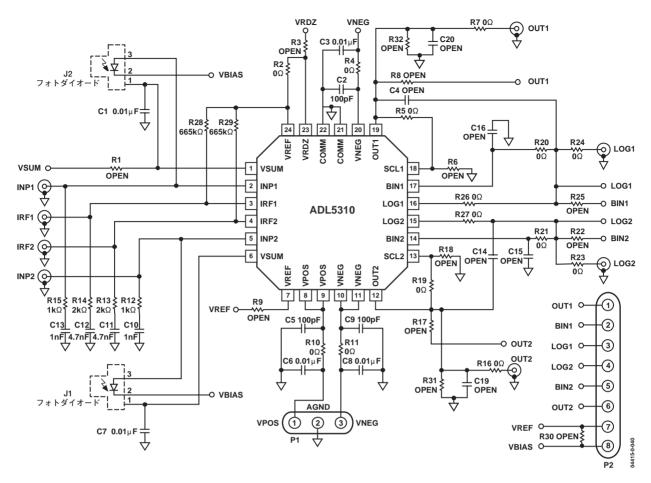

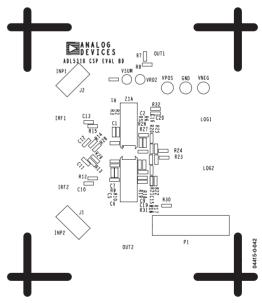

# 評価ボード

ADL5310の評価ボードを用意しています。図40に回路図を示します。評価ボードはさまざまな実験用に設定することができます。各 バッファ・アンプのゲインは出荷時に1に設定されています。スロー

プは200mV/デケードに、インターセプトは300pAに設定されています。表4に、設定オプションを示します。

表4. 評価ボードの設定オプション

| <br>部品                                                                  | 機能                                                                                                                                                                                                                            | デフォルト条件                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1                                                                      | <b>電源インターフェース</b> 。電源ピン(VNEG、COMM、VPOS)へのアクセスを提供します。                                                                                                                                                                          | P1=実装済み                                                                                                                                                                                                                                                   |

| P2、R1、R3、R8、R9、<br>R17、R22、R25、R30                                      | <b>モニター・インターフェース</b> 。R1、R3、R8、R9、R17、R22、R25 に $0\Omega$ 抵抗を追加すると、高インピーダンスのプローブを使って、VRDZ、VREF、VSUM、BIN1、BIN2、OUT1、OUT2の各ピンの電圧をモニターすることができます。VBIASを使うと、外付けバイアス電圧をJ1とJ2に加えることができます。R30= $0\Omega$ の場合は、VBIAS=VREFになります。        | P2=未実装<br>R1=R3=R8=オープン(サイズ0402)<br>R9=R17=オープン(サイズ0402)<br>R22=R25=R30=オープン(サイズ0402)                                                                                                                                                                     |

| R5、R6、R7、R16、<br>R18、R19、R20、R21、<br>R31、R32、C4、C14、<br>C15、C16、C19、C20 | <b>バッファ・アンプ/出力インターフェース</b> 。ADL5310の対数スロープは、各バッファのゲイン設定抵抗(R5とR6、およびR18とR19)を使って変更することができます。R7、R16、R31、R32、C19、C20を使うと、バッファの負荷を変えられます。R20、R21、C4、C14、C15、C16は、さまざまなフィルタ・アプリケーション用です。                                           | R5=R19=0 $\Omega$ (サイズ0402)<br>R7=R16=0 $\Omega$ (サイズ0402)<br>R20=R21=0 $\Omega$ (サイズ0402)<br>R6=R18=オープン(サイズ0402)<br>R31=R32=オープン(サイズ0402)<br>C4=C14=オープン(サイズ0402)<br>C19=C20=オープン(サイズ0402)<br>C15=C16=オープン(サイズ0402)<br>LOG1=OUT1=実装済み<br>LOG2=OUT2=実装済み |

| R2、R28、R29                                                              | <b>インターセプト調整</b> 。抵抗R28とR29の間の電圧降下が各ログアンプのインターセプト基準電流を決定し、 $665k\Omega1\%$ の抵抗を使って公称3 $\mu$ Aに設定します。R2を使って、LOG1およびLOG2出力の出力オフセット電圧を調整することができます。                                                                               | R28=R29=665kΩ (サイズ0402)<br>R2=0Ω (サイズ0402)                                                                                                                                                                                                                |

| R4、R10、R11、C2、C3、C5、C6、C8、C9                                            | 電源のデカップリング。                                                                                                                                                                                                                   | C2=C5=C9=100pF (サイズ0402)<br>C3=C6=C8=0.01 μF (サイズ0402)<br>R4=R10=R11=0Ω (サイズ0402)                                                                                                                                                                         |

| C1、C7                                                                   | VSUMのフィルタリング。                                                                                                                                                                                                                 | C1=C7=0.01 μ F (サイズ0402)                                                                                                                                                                                                                                  |

| R12、R13、R14、R15、<br>C10、C11、C12、C13                                     | <b>入力補償</b> 。INP1、INP2、IRF1、IRF2の各入力ピンで不可欠なHF<br>補償を提供します。                                                                                                                                                                    | R12=R15=1kΩ (サイズ0402)<br>R13=R14=2kΩ (サイズ0402)<br>C10=C13=1nF (サイズ0402)<br>C11=C12=4.7nF (サイズ0402)                                                                                                                                                        |

| IREF、INPT                                                               | 入力インターフェース。INP1およびINP2とラベル表示された SMAコネクタを経由してテスト・ボードに電流を入力します。光イン ターフェース用に、INP1とINP2のSMAの代わりにフォトダイオード を接続するために、スルー・ホールが用意されています。対数比アプリケーションでのADL5310の評価用に、R28 (INP2はR29)を削除して、2つ目の電流をIRF1 (INP2はIRF2)に入力することができます (SMAにも入力可能)。 | IREF=INPT=実装済み                                                                                                                                                                                                                                            |

| J1、J2                                                                   | SC型のフォトダイオード。SC型フォトダイオードの直接実装用です。                                                                                                                                                                                             | J1=J2=オープン                                                                                                                                                                                                                                                |

図40. 評価ボードの回路図

図41. 部品面のレイアウト

図42. 部品面のシルク・スクリーン

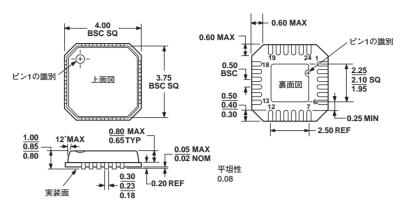

## 外形寸法

JEDEC規格SMO-220-VGGD-2に準拠

図43. 24ピン・リード・フレーム・チップ・スケール・パッケージ[LFCSP] (CP-24) 寸法単位:mm

## オーダー・ガイド

| 製品モデル            | 温度範囲      | パッケージ     | パッケージ・オプション |

|------------------|-----------|-----------|-------------|

| ADL5310ACP       | -40~+85℃  | 24ピンLFCSP | CP-24       |

| ADL5310ACP-R2    | -40~+85°C | 24ピンLFCSP | CP-24       |

| ADL5310ACP-REEL7 | -40~+85°C | 24ピンLFCSP | CP-24       |

| ADL5310-EVAL     |           | 評価ボード     |             |

C04415-0-11/03(0)-J