# 24GHz、ISM バンド 多チャンネル FMCW レーダー・ トランスミッタ

データシート

**ADF5902**

#### 特長

24GHz~24.25GHz VCO(産業、科学、医療用(ISM) 無線バンド) 8dBm 出力の 2 チャンネル 24GHz パワー・アンプ シングル・エンド出力 ミュート機能付き2チャンネル多重出力 プログラマブル出力電力 LO 出力パッファ RF 周波数範囲: 24GHz~24.25GHz パワー・コントロール・ディテクタ 補助 8 ビット ADC 高低速 FMCW ランプ生成 25 ビット固定率により、サブヘルツの周波数分解能が可能 最大 110MHz の PFD 周波数 -222dBc/Hz の正規化位相ノイズ・フロア プログラマブル・チャージ・ポンプ電流 ±5°C 温度センサ-4ワイヤ SPI

HBM : 2000V CDM : 250V

ESD 性能

オートモーティブ・アプリケーション向けの性能を評価済み

#### アプリケーション

オートモーティブ・レーダー 産業用レーダー マイクロ波レーダー・センサー

#### 概要

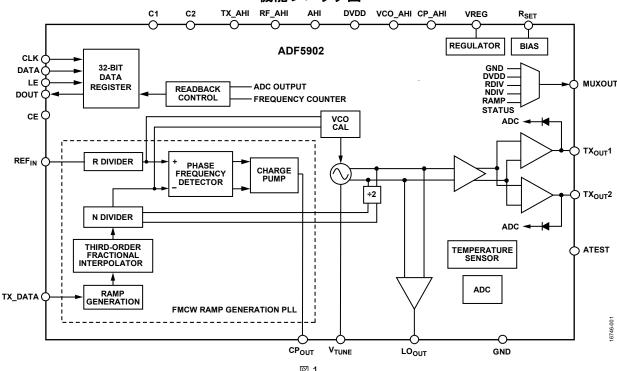

ADF5902 は、24GHz 電圧制御発振器(VCO)を内蔵した 24GHz トランスミッタ(Tx)モノリシック・マイクロ波集積回路(MMIC)です。VCO は、プログラマブル・グリッド・アレイ(PGA)とレーダー・システム用デュアル・トランスミッタ・チャンネルによる波形生成能力をもつフラクショナル N 周波数シンセサイザが特徴です。内蔵 24GHz VCO は 2 つのトランスミッタ・チャンネルとローカル発振器(LO)の出力のための24GHz 信号を生成します。各トランスミッタ・チャンネルはパワー・コントロール回路を含んでいます。また、温度センサーも1つ内蔵されています。

すべての内蔵レジスタの制御は、簡単な 4 線式シリアル・ポート・インターフェース (SPI) を介して行われます。

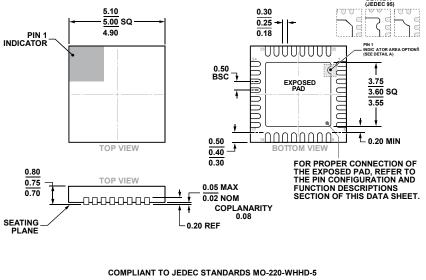

ADF5902 は、小型 32 ピン、5mm × 5mm LFCSP パッケージを採用しています。

#### 機能ブロック図

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって 生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示 的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有 者の財産です。※日本語版資料はREVISION が古い場合があります。最新の内容については、英語版をご参照ください。

©2019 Analog Devices, Inc. All rights reser

Rev 0

本 社/〒105-6891

東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 10F 雷話 03 (5402) 8200

大 阪営業所/〒532-0003

大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 10F 電話 06 (6350) 6868

名古屋営業所/〒451-6038

愛知県名古屋市西区牛島町 6-1 名古屋ルーセントタワー 38F 電話 052 (569) 6300

# データシート

# 目次

| 特長             | 1        |

|----------------|----------|

| アプリケーション       | 1        |

| 概要             | 1        |

| 機能ブロック図        | 1        |

| 改訂履歷           | 2        |

| 仕様             | 3        |

| タイミング仕様        | 5        |

| 絶対最大定格         | 6        |

| 熱抵抗            | 6        |

| ESD に関する注意     | <i>6</i> |

| ピン配置およびピン機能の説明 | 7        |

| 代表的な性能特性       | 9        |

| 動作原理           | 11       |

| リファレンス入力部      | 11       |

| RF INT 分周器     | 11       |

| INT、FRAC、R の関係 | 11       |

| R カウンタ         | 11       |

| PFD とチャージ・ポンプ  | 11       |

| 入力シフト・レジスタ     | 11       |

| プログラム・モード      | . 12     |

| レジスタ・マップ       | . 13     |

| レジスタ 0         | . 16     |

| レジスタ 1         | . 17     |

| レジスタ 2         | . 18     |

| レジスタ 3         | . 19     |

| レジスタ 4         | . 20     |

| レジスタ 5         | . 21     |

| レジスタ 6                          | 22 |

|---------------------------------|----|

| レジスタ 7                          | 23 |

| レジスタ 8                          | 24 |

| レジスタ 9                          | 24 |

| レジスタ 10                         | 25 |

| レジスタ 11                         | 25 |

| レジスタ 12                         | 26 |

| レジスタ 13                         | 27 |

| レジスタ 14                         | 28 |

| レジスタ 15                         | 29 |

| レジスタ 16                         | 30 |

| レジスタ 17                         | 30 |

| アプリケーション情報                      | 31 |

| 初期化シーケンス                        | 31 |

| 再キャリブレーション・シーケンス                | 32 |

| 温度センサー                          | 33 |

| RF 合成:実際の動作例                    | 33 |

| リファレンス・ダブラ                      | 33 |

| 周波数測定手順                         | 34 |

| 波形生成                            | 34 |

| 波形の偏差とタイミング                     | 34 |

| ランプと変調                          | 35 |

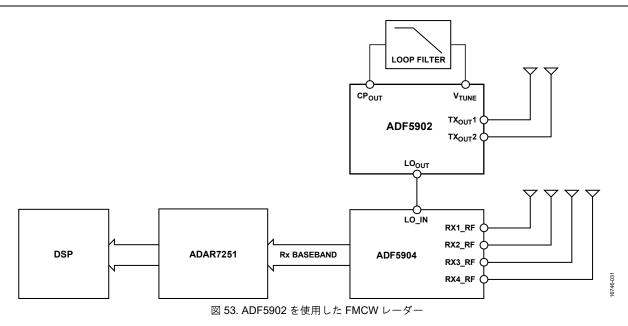

| FMCW レーダーにおける ADF5902 のアプリケーション | 37 |

| 外形寸法                            | 39 |

| オーダー・ガイド                        | 39 |

| オートモーティブ製品                      | 39 |

# 改訂履歴

11/2018—Revision 0: Initial Version

# データシート

# 目次

| 特長              |

|-----------------|

| アプリケーション        |

| 概要              |

| 機能ブロック図         |

| 改訂履歷            |

| 仕様              |

| タイミング仕様         |

| 絶対最大定格          |

| 熱抵抗             |

| ESD に関する注意      |

| ピン配置およびピン機能の説明  |

| 代表的な性能特性        |

| 動作原理1           |

| リファレンス入力部1      |

| RF INT 分周器1     |

| INT、FRAC、R の関係1 |

| R カウンタ1         |

| PFD とチャージ・ポンプ1  |

| 入力シフト・レジスタ1     |

| プログラム・モード12     |

| レジスタ・マップ1       |

| レジスタ 010        |

| レジスタ 11′        |

| レジスタ 218        |

| レジスタ 319        |

| レジスタ 420        |

| レジスタ 52         |

| レジスタ 6                          | 22 |

|---------------------------------|----|

| レジスタ 7                          | 23 |

| レジスタ 8                          | 24 |

| レジスタ 9                          | 24 |

| レジスタ 10                         | 25 |

| レジスタ 11                         | 25 |

| レジスタ 12                         | 26 |

| レジスタ 13                         | 27 |

| レジスタ 14                         | 28 |

| レジスタ 15                         | 29 |

| レジスタ 16                         | 30 |

| レジスタ 17                         | 30 |

| アプリケーション情報                      | 31 |

| 初期化シーケンス                        | 31 |

| 再キャリブレーション・シーケンス                | 32 |

| 温度センサー                          | 33 |

| RF 合成:実際の動作例                    | 33 |

| リファレンス・ダブラ                      | 33 |

| 周波数測定手順                         | 34 |

| 波形生成                            | 34 |

| 波形の偏差とタイミング                     | 34 |

| ランプと変調                          | 35 |

| FMCW レーダーにおける ADF5902 のアプリケーション | 37 |

| 外形寸法                            | 39 |

| オーダー・ガイド                        | 39 |

| オートモーティブ製品                      | 39 |

# 改訂履歴

11/2018—Revision 0: Initial Version

| Parameter                                                    | Min    | Тур     | Max  | Unit   | Test Conditions/Comments                                                                           |

|--------------------------------------------------------------|--------|---------|------|--------|----------------------------------------------------------------------------------------------------|

| NOISE CHARACTERISTICS                                        |        |         |      |        |                                                                                                    |

| Normalized Phase Noise Floor, Fractional-N Mode <sup>3</sup> |        | -222    |      | dBc/Hz | PLL loop bandwidth (BW) = 1 MHz                                                                    |

| Normalized 1/f Noise (PN <sub>1_f</sub> ) <sup>4</sup>       |        | -120    |      | dBc/Hz | Measured at 10 kHz offset, normalized to 1 GHz                                                     |

| TEMPERATURE SENSOR                                           |        |         |      |        |                                                                                                    |

| Analog Accuracy                                              |        | ±5      |      | °C     | Following one point calibration                                                                    |

| Digital Accuracy                                             |        | ±5      |      | °C     | Following one point calibration                                                                    |

| Sensitivity                                                  |        | 6.4     |      | mV/°C  |                                                                                                    |

| ANALOG-TO-DIGITAL CONVERTER (ADC)                            |        |         |      |        |                                                                                                    |

| Resolution                                                   |        | 8       |      | Bits   |                                                                                                    |

| Integral Nonlinearity (INL)                                  |        | ±1      |      | LSB    |                                                                                                    |

| Differential Nonlinearity (DNL)                              |        | $\pm 1$ |      | LSB    |                                                                                                    |

| Least Significant Bit (LSB)                                  |        | 7.4     |      | mV     |                                                                                                    |

| REF <sub>IN</sub> CHARACTERISITICS                           |        |         |      |        |                                                                                                    |

| REF <sub>IN</sub> Input Frequency                            | 10     |         | 260  | MHz    | -5 dBm minimum to +9 dBm maximum biased                                                            |

|                                                              |        |         |      |        | at AHI/2 (ac coupling ensures 1.8 ÷ 2 bias); for                                                   |

|                                                              |        |         |      |        | frequencies < 10 MHz, use a dc-coupled, CMOS-<br>compatible square wave with a slew rate > 25 V/µs |

| REF <sub>IN</sub> Input Capacitance <sup>2</sup>             |        |         | 1.2  | pF     | companie square wave with a siew rate > 25 47 µs                                                   |

| REF <sub>IN</sub> Input Current                              |        |         | ±100 | μA     |                                                                                                    |

| LOGIC INPUTS                                                 |        |         | _100 | μι     |                                                                                                    |

| Input Voltage                                                |        |         |      |        |                                                                                                    |

| High (V <sub>IH</sub> )                                      | 1.4    |         |      | V      |                                                                                                    |

| Low (V <sub>IL</sub> )                                       | 111    |         | 0.6  | v      |                                                                                                    |

| Input Current (I <sub>INH</sub> , I <sub>INL</sub> )         |        |         | ±1   | μA     |                                                                                                    |

| Input Capacitance $(C_{IN})^2$                               |        |         | 10   | pF     |                                                                                                    |

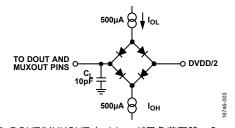

| LOGIC OUTPUTS                                                |        |         | -    | 1      |                                                                                                    |

| Output Voltage                                               |        |         |      |        |                                                                                                    |

| High (V <sub>OH</sub> ) <sup>5</sup>                         | DVDD - |         |      | V      |                                                                                                    |

| <b>5</b> ( 5)                                                | 0.4    |         |      |        |                                                                                                    |

| $Low(V_{OL})$                                                |        |         | 0.4  | V      |                                                                                                    |

| Output Current                                               |        |         |      |        |                                                                                                    |

| High (I <sub>OH</sub> )                                      |        |         | 500  | μΑ     |                                                                                                    |

| $Low(I_{OL})$                                                |        |         | 500  | μΑ     |                                                                                                    |

<sup>&</sup>lt;sup>1</sup> 初期化シーケンスのセクションで説明されている初期化シーケンスに従い、TA=25℃、AHI=3.3V、f<sub>REFIN</sub>=100MHz、およびRF=24.025GHz。

Rev. 0 - 4/39 -

<sup>2</sup> 設計により性能を確保。コンプライアンス確保のためにサンプルをテスト済み。

$<sup>^3</sup>$  この仕様はあらゆるアプリケーションの位相ノイズを計算するのに使用できます。式((正規化位相ノイズ・フロア)+ $10\log$ ( $f_{PFD}$ )+ $20\log$ N)を使用して、VCO 出力から見た帯域内位相ノイズ性能を計算します。

<sup>&</sup>lt;sup>4</sup> PLL 位相ノイズは、フリッカ(1/f)ノイズと正規化 PLL ノイズ・フロアから成ります。RF 周波数( $f_{RF}$ )およびオフセット周波数(f)での 1/f ノイズの寄与を計算する式は、 $PN = PN_{1\_f} + 10log(10kHz/f) + 20log(<math>f_{RF}/1GHz$ )で与えられます。正規化位相ノイズ・フロアとフリッカ・ノイズの両方が ADIsimPLL でモデル化されています。

<sup>&</sup>lt;sup>5</sup> DVDD は IO レベル・ビット(レジスタ 3 のビット DB11)で選択します。

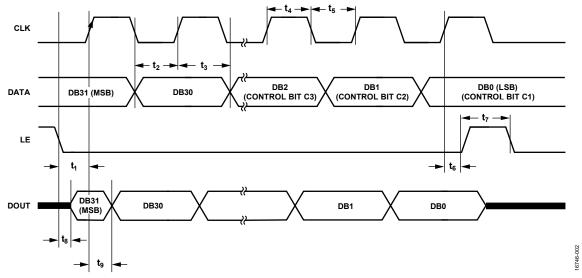

# タイミング仕様

#### 書込みタイミング仕様

特に指定のない限り、AHI = TX\_AHI = RF\_AHI = VCO\_AHI = DVDD = CP\_AHI =  $3.3V\pm5\%$ 、GND = 0V、 $50\Omega$  を基準とした dBm、 $T_A = T_{MIN} \sim T_{MAX}$ 。動作温度範囲は $-40^{\circ}C \sim +105^{\circ}C$  です。

表 2.

| Parameter      | Limit at T <sub>MIN</sub> to T <sub>MAX</sub> | Unit   | Description            |

|----------------|-----------------------------------------------|--------|------------------------|

| $t_1$          | 20                                            | ns min | LE setup time          |

| $t_2$          | 10                                            | ns min | DATA to CLK setup time |

| $t_3$          | 10                                            | ns min | DATA to CLK hold time  |

| $t_4$          | 25                                            | ns min | CLK high duration      |

| $t_5$          | 25                                            | ns min | CLK low duration       |

| $t_6$          | 10                                            | ns min | CLK to LE setup time   |

| $t_7$          | 20                                            | ns min | LE pulse width         |

| $t_8$          | 10                                            | ns max | LE setup time to DOUT  |

| t <sub>9</sub> | 15                                            | ns max | CLK setup time to DOUT |

図 2. 書込みのタイミング図

図 3. DOUT/MUXOUT タイミング用負荷回路、 $C_L$  = 10pF

Rev. 0 - 5/39 -

# 絶対最大定格

#### 表 3.

| Parameter                           | Rating                   |

|-------------------------------------|--------------------------|

| AHI to GND                          | -0.3 V to +3.9 V         |

| AHI to TX_AHI                       | -0.3 V to +0.3 V         |

| AHI to RF_AHI                       | -0.3 V to +0.3 V         |

| AHI to VCO_AHI                      | -0.3 V to +0.3 V         |

| AHI to DVDD                         | -0.3 V to +0.3 V         |

| AHI to CP_AHI                       | -0.3 V to +0.3 V         |

| $V_{TUNE}$ to GND                   | -0.3 V to +3.6 V         |

| Digital Input/Output Voltage to GND | -0.3  V to DVDD + 0.3  V |

| Operating Temperature Range         | -40°C to +105°C          |

| Storage Temperature Range           | −65°C to +150°C          |

| Maximum Junction Temperature        | 150°C                    |

| Reflow Soldering                    |                          |

| Peak Temperature                    | 260°C                    |

| Time at Peak Temperature            | 40 sec                   |

| Electrostatic Discharge (ESD)       |                          |

| Charged Device Model (CDM)          | 250 V                    |

| Human Body Model (HBM)              | 2000 V                   |

上記の絶対最大定格を超えるストレスを加えると、デバイスに 恒久的な損傷を与えることがあります。この規定はストレス定 格のみを指定するものであり、この仕様の動作のセクションに 記載する規定値以上でのデバイス動作を定めたものではありま せん。デバイスを長時間にわたり絶対最大定格状態に置くと、 デバイスの信頼性に影響を与えることがあります。 ADF5902 は、ESD 定格が 2kV の高性能 RF 集積回路で、ESD による影響を受けます。取り扱いと組み立ての際には適切な注意を払ってください。

#### 熱抵抗

熱性能は、プリント回路基板 (PCB) の設計と動作環境に直接 関連しています。PCB の熱設計には細心の注意を払う必要があ ります。

表 4. 熱抵抗

| Package Type          | $\theta_{JA}^{1}$ | $\theta_{JC}^2$ | Unit |

|-----------------------|-------------------|-----------------|------|

| CP-32-12 <sup>3</sup> | 48.18             | 26.86           | °C/W |

$<sup>^{1}</sup>$   $\theta_{\rm IA}$  は、1 立方フィートの密封容器内で測定された、自然対流下におけるジャンクションと周囲温度の間の熱抵抗です。

#### ESD に関する注意

ESD(静電放電)の影響を受けやすいデバイスです。 電荷を帯びたデバイスや回路ボードは、検知されない まま放電することがあります。本製品は当社独自の特

許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

Rev. 0 - 6/39 -

$<sup>^{2}\</sup>theta_{JC}$ は、ジャンクションとケースの間の熱抵抗です。

$<sup>^3</sup>$  テスト条件 1: 熱抵抗のシミュレーション値は、熱抵抗パッドを GND にハンダ付けした PCB を使用して測定しています。

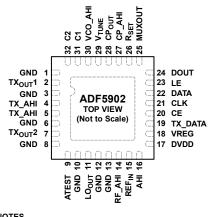

# ピン配置およびピン機能の説明

NOTES 1. THE EXPOSED PAD MUST BE CONNECTED TO GND.

図 4. ピン配置

表 5. ピン機能の説明

| ピン番号                      | 記号                  | 説明                                                                                                                                                         |

|---------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 3, 6, 8, 10,<br>12, 13 | GND                 | RF グラウンド。すべての GND ピンを互いに接続します。                                                                                                                             |

| 2                         | TX <sub>OUT</sub> 1 | 24GHz トランスミッタ出力 1。                                                                                                                                         |

| 4, 5                      | TX_AHI              | トランスミッタ部用電源。このピンのできるだけ近くで、デカップリング・コンデンサ(0.1μF、1nF、および<br>10pF)をグランド・プレーンに接続します。TX_AHI は AHI と同じ値でなければなりません。                                                |

| 7                         | TX <sub>OUT</sub> 2 | 24GHz トランスミッタ出力 2。                                                                                                                                         |

| 9                         | ATEST               | アナログ・テスト出力端子。                                                                                                                                              |

| 11                        | LO <sub>OUT</sub>   | LO出力。                                                                                                                                                      |

| 14                        | RF_AHI              | RF 部用電源。このピンのできるだけ近くで、デカップリング・コンデンサ( $0.1\mu$ F、 $1n$ F、および $10p$ F)をグランド・プレーンに接続します。RF_AHI は AHI と同じ値でなければなりません。                                          |

| 15                        | REF <sub>IN</sub>   | リファレンス入力。このピンは、公称閾値が DVDD/2 で、DC 等価入力抵抗が 100kΩの CMOS 入力です。図 17を参照。この入力は TTL または CMOS 水晶発振器から駆動するか、AC カップリングすることができます。                                      |

| 16                        | AHI                 | アナログ部用電源。このピンのできるだけ近くで、デカップリング・コンデンサ(0.1μF、1nF、および 10pF)を<br>グランド・プレーンに接続します。                                                                              |

| 17                        | DVDD                | デジタル電源。この電源の範囲は $3.135V\sim3.465V$ です。このピンのできるだけ近くで、デカップリング・コンデンサ( $0.1\mu F$ 、 $\ln F$ 、および $10pF$ )をグランド・プレーンに接続します。DVDD は AHI と同じ値でなければなりません。           |

| 18                        | VREG                | 内部 1.8V レギュレータ出力。このピンのできるだけ近くで、220nF のコンデンサをグラウンドに接続します。                                                                                                   |

| 19                        | TX_DATA             | 送信データ・ピン。このピンはランプ機能のいくつかを制御します。 $TX_DATA$ 信号の立上がりエッジを $REF_{IN}$ の立上がりエッジに同期させます。                                                                          |

| 20                        | CE                  | チップ・イネーブル。このピンをロジック・ローにすると、デバイスがパワーダウンします。このピンをハイに<br>すると、デバイスがパワーアップします。                                                                                  |

| 21                        | CLK                 | シリアル・クロック入力。このシリアル・クロック入力は、シリアル・データをレジスタにクロックインします。データは、CLK の立上がりエッジで 32 ビット・シフト・レジスタにラッチされます。この入力はハイ・インピーダンス CMOS 入力です。                                   |

| 22                        | DATA                | シリアル・データ入力。シリアル・データは、4 LSB を制御ビットとして MSB ファーストでロードされます。この入力はハイ・インピーダンス CMOS 入力です。                                                                          |

| 23                        | LE                  | ロード・イネーブル、CMOS 入力。LE がハイになると、シフト・レジスタに格納されているデータが 18 個のラッチの 1 つにロードされます。ラッチは制御ビットを介して選択します。                                                                |

| 24                        | DOUT                | シリアル・データ出力。                                                                                                                                                |

| 25                        | MUXOUT              | マルチプレクサ出力。このマルチプレクサ出力により、様々な内部信号に外部からアクセスできます。                                                                                                             |

| 26                        | R <sub>SET</sub>    | 抵抗設定ピン。このピンと GND の間に $5.1 \mathrm{k}\Omega$ の抵抗を接続すると、内部電流が設定されます。 $\mathbf{R}_{\mathrm{SET}}$ ピンの公称電位は $0.62\mathrm{V}$ です。                               |

| 27                        | CP_AHI              | チャージ・ポンプ電源。この電源の範囲は $3.135V \sim 3.465V$ です。このピンのできるだけ近くで、デカップリング・コンデンサ( $0.1\mu$ F、 $1n$ F、および $10p$ F)をグランド・プレーンに接続します。 $CP_AHI$ は $AHI$ と同じ値でなければなりません。 |

| 28                        | CP <sub>OUT</sub>   | チャージ・ポンプ出力。チャージ・ポンプをイネーブルした場合、この出力は外部ループ・フィルタに±I <sub>CP</sub> を供給し、更にこのフィルタは VCO を駆動します。                                                                  |

Rev. 0 - 7/39 -

| ピン番号 | 記号                | 説明                                                      |

|------|-------------------|---------------------------------------------------------|

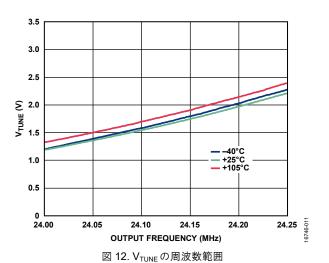

| 29   | V <sub>TUNE</sub> | VCO への制御入力。この電圧が出力を決定します。                               |

| 30   | VCO_AHI           | VCO セクション用電源。このピンのできるだけ近くで、デカップリング・コンデンサ(0.1μF、1nF、および  |

|      |                   | 10pF) をグランド・プレーンに接続します。VCO_AHI は AHI と同じ値でなければなりません。    |

| 31   | C1                | デカップリング・コンデンサ 1。このピンのできるだけ近くで 47nF のコンデンサをグラウンドに接続します。  |

| 32   | C2                | デカップリング・コンデンサ 2。このピンのできるだけ近くで 220nF のコンデンサをグラウンドに接続します。 |

|      | EP                | 露出パッド。露出パッドは GND に接続する必要があります。                          |

Rev. 0 - 8/39 -

# 代表的な性能特性

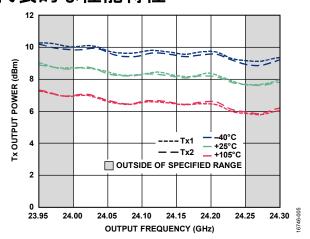

図 5. トランスミッタ (Tx) 出力電力と出力周波数の関係

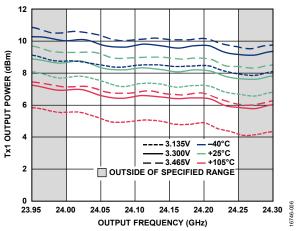

図 6. 各種の温度と電源におけるトランスミッタ 1 (Tx1) の 出力電力変動と出力周波数の関係

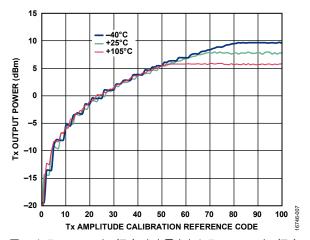

図 7. トランスミッタ(Tx)出力電力とトランスミッタ(Tx) 振幅キャリブレーション・リファレンス・コードの関係

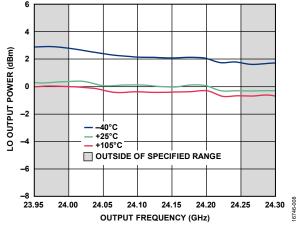

図 8. LO 出力電力と出力周波数の関係

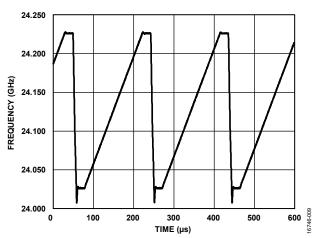

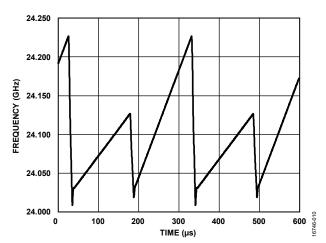

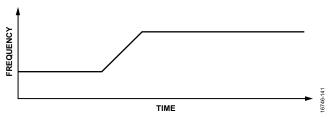

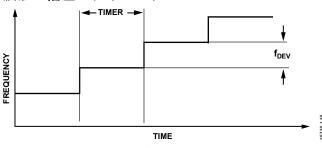

図 9. 遅延を伴う三角波ランプ

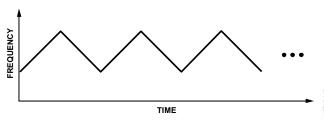

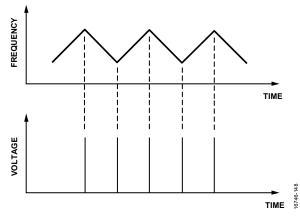

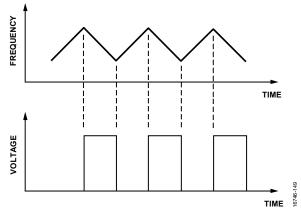

図 10. デュアル三角波ランプ

Rev. 0 – 9/39 –

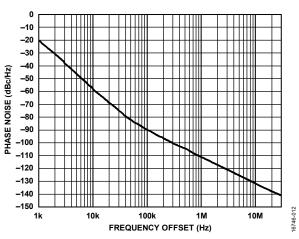

図 13. トランスミッタ 1 出力のオープンループ位相ノイズ (24.125GHz)

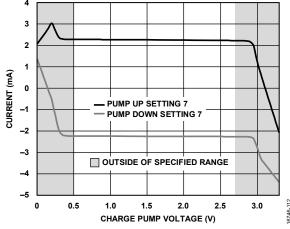

図 14. チャージ・ポンプ出力特性(25℃ で CP\_AHI = 3.3V)

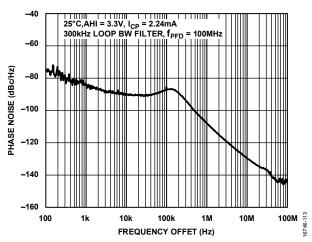

図 15. トランスミッタ 1 のクローズループ位相ノイズ (24.125GHz)

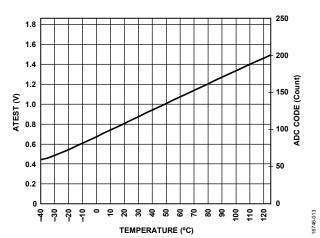

図 16. ATEST 電圧および ADC コードの温度特性

Rev. 0 - 10/39 -

# 動作原理

#### リファレンス入力部

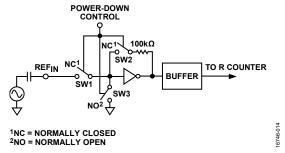

リファレンス入力段を図17に示します。SW1とSW2は通常は閉じている(ノーマル・クローズ)スイッチです。SW3は通常開いています(ノーマル・オープン)。パワーダウンが開始されると、SW3が閉じ、SW1とSW2が開きます。この構成により、パワーダウン時にREF<sub>IN</sub>ピンに負荷がかからなくなります。

図 17. リファレンス入力段

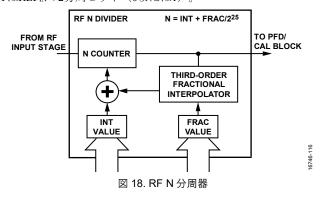

#### RF INT 分周器

RF INTカウンタにより、RFフィードバック・カウンタで分周比を設定できます。分周比には75~4095が可能です。

#### INT、FRAC、Rの関係

以下のように、INT値とFRAC値をRカウンタと組み合わせて、RF VCO周波数 (RFour) を生成します。

$$RF_{OUT} = f_{PFD} \times (INT + (FRAC/2^{25})) \times 2$$

(1)

ここで、

RFourは内部VCOの出力周波数。

fpfDは位相周波数検出器 (PFD) の周波数。

*INT*はバイナリ12ビット・カウンタのプリセット分周比(75~4095)。

FRACは分数除算の分子( $0\sim2^{25}$  - 1)。

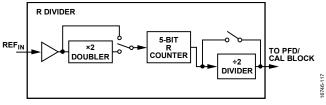

$$f_{PFD} = REF_{IN} \times \left( (1+D) / (R \times (1+T)) \right)$$

$$(2)$$

REF<sub>IN</sub>はリファレンス入力周波数。

Dは $REF_{IN}$ ダブラ・ビット(0または1)。

Rは5ビットのバイナリ・プログラマブル・リファレンス・カウンタのプリセット分周比(1 $\sim$ 32)。

TはREF<sub>IN</sub>の2分周ビット(0または1)。

図 19. リファレンス分周器

#### Rカウンタ

5ビットRカウンタにより、入力リファレンス周波数( $REF_{IN}$ )を分周してPFDおよびVCOのキャリブレーション・ブロックにリファレンス・クロックを供給できます。分周比には $1\sim32$ が可能です。

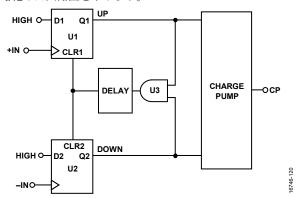

### PFD とチャージ・ポンプ

PFDはRカウンタとNカウンタから入力を受け取り、それらの位相と周波数の差に比例した出力を生成します。図20に、PFDの簡略化した回路図を示します。

図 20. PFD の簡略化した回路図

PFDには、アンチバックラッシュ・パルスの幅を設定する、Ins (代表値)の固定遅延成分が含まれています。このパルスは、PFD伝達関数内でデッド・ゾーンの発生を確実に防止し、リファレンス・スプリアス・レベルを一定にします。

#### 入力シフト・レジスタ

ADF5902のデジタル部には、5 ビットの RFR カウンタ、12 ビットの RF N カウンタ、および 25 ビットの FRAC カウンタがあります。データは、CLK の各立上がりエッジで 32 ビット入力シフト・レジスタにクロック入力されます。このデータは MSB ファーストです。データは、LE の立上がりエッジで入力シフト・レジスタから 18 個のラッチの 1 つに転送されます。ディスティネーション・ラッチは、入力シフト・レジスタの 5 つの制御ビット (C5、C4、C3、C2、C1)の状態によって決まります。図2に示すように、これらは 5 LSB(それぞれ DB4、DB3、DB2、DB1、DB0)です。これらのビットの真理値表を表 6 に示します。ラッチの設定方法の概要を図 21 と図 22 に示します。

Rev. 0 — 11/39 —

### プログラム・モード

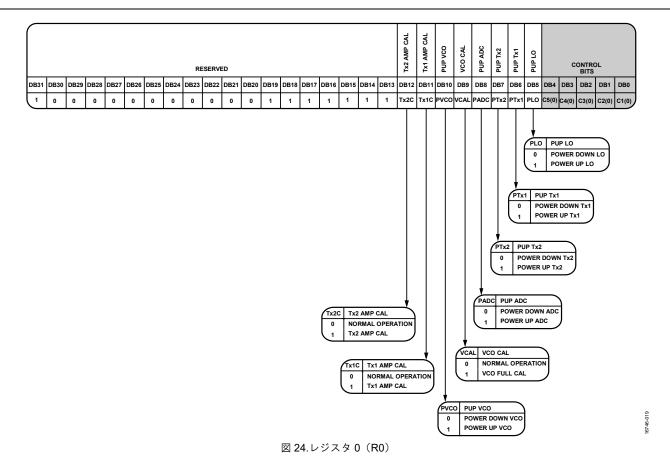

表 6 および図 24~図 42 に、ADF5902 でプログラム・モードを設定する方法を示します。

ADF5902 の設定のいくつかはダブル・バッファ付きです。これらには、LSB 小数値、R カウンタ値(R 分周器)、リファレンス・ダブラ、クロック分周器、RDIV2、MUXOUT が含まれます。ダブル・バッファ付きの場合、2 回の書込みを行った後で、設定した新しい値がデバイスで有効になります。最初に、目的のレジスタに書き込むことによって、新しい値がデバイスにラッ

チされます。更に、レジスタ R5 に別の書込みを実行する必要があります。

例えば、小数値を更新するには、レジスタR6の13 LSBビットと、レジスタR5の12 MSBビットへの書込みが必要です。最初にレジスタR6に書き込み、次にレジスタR5に書き込みます。周波数の変更は、レジスタR5への書込み後に開始されます。ダブル・バッファリングにより、レジスタR6に書き込まれたビットは、レジスタR5に書き込まれるまで有効になりません。

表 6. C5、C4、C3、C2、C1 の真理値表

|          |          | Control Bits |          |          |          |  |  |  |  |  |  |  |

|----------|----------|--------------|----------|----------|----------|--|--|--|--|--|--|--|

| C5 (DB4) | C4 (DB3) | C3 (DB2)     | C2 (DB1) | C1 (DB0) | Register |  |  |  |  |  |  |  |

| 0        | 0        | 0            | 0        | 0        | R0       |  |  |  |  |  |  |  |

| 0        | 0        | 0            | 0        | 1        | R1       |  |  |  |  |  |  |  |

| 0        | 0        | 0            | 1        | 0        | R2       |  |  |  |  |  |  |  |

| 0        | 0        | 0            | 1        | 1        | R3       |  |  |  |  |  |  |  |

| 0        | 0        | 1            | 0        | 0        | R4       |  |  |  |  |  |  |  |

| 0        | 0        | 1            | 0        | 1        | R5       |  |  |  |  |  |  |  |

| 0        | 0        | 1            | 1        | 0        | R6       |  |  |  |  |  |  |  |

| 0        | 0        | 1            | 1        | 1        | R7       |  |  |  |  |  |  |  |

| 0        | 1        | 0            | 0        | 0        | R8       |  |  |  |  |  |  |  |

| 0        | 1        | 0            | 0        | 1        | R9       |  |  |  |  |  |  |  |

| 0        | 1        | 0            | 1        | 0        | R10      |  |  |  |  |  |  |  |

| 0        | 1        | 0            | 1        | 1        | R11      |  |  |  |  |  |  |  |

| 0        | 1        | 1            | 0        | 0        | R12      |  |  |  |  |  |  |  |

| 0        | 1        | 1            | 0        | 1        | R13      |  |  |  |  |  |  |  |

| 0        | 1        | 1            | 1        | 0        | R14      |  |  |  |  |  |  |  |

| 0        | 1        | 1            | 1        | 1        | R15      |  |  |  |  |  |  |  |

| 1        | 0        | 0            | 0        | 0        | R16      |  |  |  |  |  |  |  |

| 1        | 0        | 0            | 0        | 1        | R17      |  |  |  |  |  |  |  |

データシート レジスタ・マップ **ADF5902**

#### REGISTER 0 (R0)

|     |      |      |      |      |      |      |      |      | Tx2 AMP CAL | Tx1 AMP CAL | PUP VCO | VCO CAL | PUP ADC | PUP Tx2 | PUP Tx1 | PUP LO |      | C    | ONTRO<br>BITS | DL   |      |      |      |      |      |     |       |       |       |       |       |

|-----|------|------|------|------|------|------|------|------|-------------|-------------|---------|---------|---------|---------|---------|--------|------|------|---------------|------|------|------|------|------|------|-----|-------|-------|-------|-------|-------|

| DB3 | DB30 | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22        | DB21        | DB20    | DB19    | DB18    | DB17    | DB16    | DB15   | DB14 | DB13 | DB12          | DB11 | DB10 | DB9  | DB8  | DB7  | DB6  | DB5 | DB4   | DB3   | DB2   | DB1   | DB0   |

| T   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0           | 0           | 0       | 1       | 1       | 1       | 1       | 1      | 1    | 1    | Tx2C          | Tx1C | PVCO | VCAL | PADC | PTx2 | PTx1 | PLO | C5(0) | C4(0) | C3(0) | C2(0) | C1(0) |

#### REGISTER 1 (R1)

|      |      |      |      |      |      |      |      | RESER | VED  |      |      |      |      |      |      |      |      |      |      |      | Tx AM | P CAI | REF ( | CODE |      |      |       | co    | ONTRO<br>BITS | )L    |       |

|------|------|------|------|------|------|------|------|-------|------|------|------|------|------|------|------|------|------|------|------|------|-------|-------|-------|------|------|------|-------|-------|---------------|-------|-------|

| DB31 | DB30 | DR29 | DB28 | DB27 | DB26 | DB25 |      | _     |      | DB21 | DB20 | DR19 | DR18 | DB17 | DB16 | DR15 | DB14 | DR13 | DB12 | DB11 |       |       |       |      |      | DB5  | DB4   | DB3   |               | DR1   | DB0   |

| 5531 | 2230 | 0029 | 5520 | 5521 | 5520 | 5525 | 5524 | 5525  | JJ22 | 0021 | DD20 | 5519 | 5510 | 5517 | 2310 | 2213 | 5514 |      |      |      |       |       |       |      |      |      |       |       |               |       |       |

| (1   | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1     | 1    | 1    | 1    | 0    | 1    | 1    | 1    | 1    | 1    | 1    | TAR7 | TAR6 | TAR5  | TAR4  | TAR3  | TAR2 | TAR1 | TAR0 | C5(0) | C4(0) | C3(0)         | C2(0) | C1(1) |

#### REGISTER 2 (R2)

|        |        |      |      |      |      |      | RESER | RVED |      |      |      |      |      |      |      | ADC START | AC<br>AVER |      |      |      | ADC  | CLOC | K DIVI | DER |     |     |       | c     | ONTRO<br>BITS | )L    |       |

|--------|--------|------|------|------|------|------|-------|------|------|------|------|------|------|------|------|-----------|------------|------|------|------|------|------|--------|-----|-----|-----|-------|-------|---------------|-------|-------|

| DB3    | 1 DB30 | DB29 | DB28 | DB27 | DB26 | DB25 | DB24  | DB23 | DB22 | DB21 | DB20 | DB19 | DB18 | DB17 | DB16 | DB15      | DB14       | DB13 | DB12 | DB11 | DB10 | DB9  | DB8    | DB7 | DB6 | DB5 | DB4   | DB3   | DB2           | DB1   | DB0   |

| $\Box$ | 0      | 0    | 0    | 0    | 0    | 0    | 0     | 0    | 0    | 0    | 0    | 0    | 0    | 1    | 0    | AS        | AA0        | AA0  | AC7  | AC6  | AC5  | AC4  | AC3    | AC2 | AC1 | AC0 | C5(0) | C4(0) | C3(0)         | C2(1) | C1(0) |

#### REGISTER 3 (R3)

|      |      |      |      |      |      | RI   | ESERVI | ĒD   |      |      |      |      |      |      |      |      | MUXOU | IT DBR | 1    | IO LEVEL | F    | READE | BACK ( | CONTI | ROL |     |       | C     | ONTRO<br>BITS | DL    |       |

|------|------|------|------|------|------|------|--------|------|------|------|------|------|------|------|------|------|-------|--------|------|----------|------|-------|--------|-------|-----|-----|-------|-------|---------------|-------|-------|

| DB31 | DB30 | DB29 | DB28 | DB27 | DB26 | DB25 | DB24   | DB23 | DB22 | DB21 | DB20 | DB19 | DB18 | DB17 | DB16 | DB15 | DB14  | DB13   | DB12 | DB11     | DB10 | DB9   | DB8    | DB7   | DB6 | DB5 | DB4   | DB3   | DB2           | DB1   | DB0   |

| G    | 0    | 0    | 0    | 0    | 0    | 0    | 1      | 1    | 0    | 0    | 0    | 1    | 0    | 0    | 1    | МЗ   | M2    | M1     | МО   | IOL      | RC5  | RC4   | RC3    | RC2   | RC1 | RC0 | C5(0) | C4(0) | C3(0)         | C2(1) | C1(1) |

# REGISTER 4 (R4)

|        |      |      |      |      | RESE | RVED |      |      |      |      |      |      |      |      |      | R    | AMP S | TATUS | /ANAL | OG TES | ST BUS |     |     |     |     |     |       | С     | ONTRO<br>BITS | DL    |       |

|--------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-------|-------|-------|--------|--------|-----|-----|-----|-----|-----|-------|-------|---------------|-------|-------|

| DB31   | DB30 | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18 | DB17 | DB16 | DB15 | DB14  | DB13  | DB12  | DB11   | DB10   | DB9 | DB8 | DB7 | DB6 | DB5 | DB4   | DB3   | DB2           | DB1   | DB0   |

| $\Box$ | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | AB14 | AB13 | AB12 | AB11 | AB10 | AB9   | AB8   | AB7   | AB6    | AB5    | AB4 | AB3 | AB2 | AB1 | AB0 | C5(0) | C4(0) | C3(1)         | C2(0) | C1(0) |

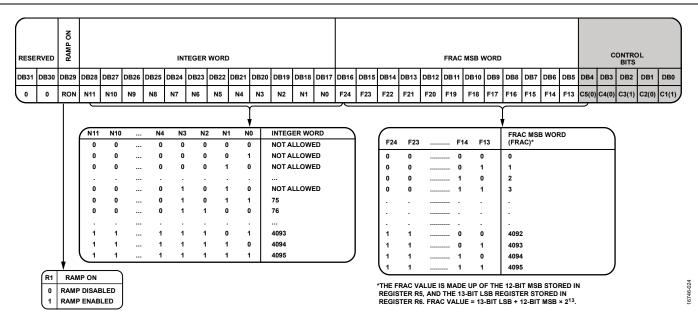

#### REGISTER 5 (R5)

| RESI | RVED | RAMP ON |      |      |      |      | IN   | TEGER | WORE | )    |      |      |      |      |      |      |      |      |      | FRAC | MSB V | WORD |     |     |     |     |       | C     | ONTRO<br>BITS | DL    |       |

|------|------|---------|------|------|------|------|------|-------|------|------|------|------|------|------|------|------|------|------|------|------|-------|------|-----|-----|-----|-----|-------|-------|---------------|-------|-------|

| DB31 | DB30 | DB29    | DB28 | DB27 | DB26 | DB25 | DB24 | DB23  | DB22 | DB21 | DB20 | DB19 | DB18 | DB17 | DB16 | DB15 | DB14 | DB13 | DB12 | DB11 | DB10  | DB9  | DB8 | DB7 | DB6 | DB5 | DB4   | DB3   | DB2           | DB1   | DB0   |

| C    | 0    | RON     | N11  | N10  | N9   | N8   | N7   | N6    | N5   | N4   | N3   | N2   | N1   | N0   | F24  | F23  | F22  | F21  | F20  | F19  | F18   | F17  | F16 | F15 | F14 | F13 | C5(0) | C4(0) | C3(1)         | C2(0) | C1(1) |

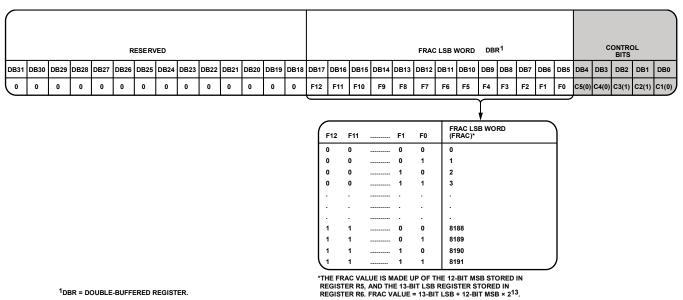

#### REGISTER 6 (R6)

|                 |        |         |      |      | F    | RESERV | /ED  |      |      |      |      |      |      |      |      |      |      |      | FRAC | C LSB V | VORD | DBF | ₹1  |     |     |     |       | С     | ONTRO<br>BITS | DL    |       |

|-----------------|--------|---------|------|------|------|--------|------|------|------|------|------|------|------|------|------|------|------|------|------|---------|------|-----|-----|-----|-----|-----|-------|-------|---------------|-------|-------|

| DB:             | 31 DB3 | 30 DB29 | DB28 | DB27 | DB26 | DB25   | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18 | DB17 | DB16 | DB15 | DB14 | DB13 | DB12 | DB11    | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4   | DB3   |               | DB1   | DB0   |

| $igcup_{\circ}$ | 0      | 0       | 0    | 0    | 0    | 0      | 0    | 0    | 0    | 0    | 0    | 0    | 0    | F12  | F11  | F10  | F9   | F8   | F7   | F6      | F5   | F4  | F3  | F2  | F1  | F0  | C5(0) | C4(0) | C3(1)         | C2(1) | C1(0) |

1DBR = DOUBLE BUFFERED REGISTER—BUFFERED BY THE WRITE TO REGISTER 5.

図 21. レジスタの一覧(レジスタ 0~レジスタ 6)

#### REGISTER 7 (R7)

|      |      | RESE | RVED |      |      | MASTER<br>RESET | RESERVED |       |       |      |      | CLOC | K DIVIE | DER  | DE   | 3R <sup>1</sup> |      |      |      | RDIV2 DBR <sup>1</sup> | REF DOUBLER<br>DBR 1 |     | R DIVI | DER | DBR | 1   |       | C     | ONTRO<br>BITS | DL    |       |

|------|------|------|------|------|------|-----------------|----------|-------|-------|------|------|------|---------|------|------|-----------------|------|------|------|------------------------|----------------------|-----|--------|-----|-----|-----|-------|-------|---------------|-------|-------|

| DB31 | DB30 | DB29 | DB28 | DB27 | DB26 | DB25            | DB24     | DB23  | DB22  | DB21 | DB20 | DB19 | DB18    | DB17 | DB16 | DB15            | DB14 | DB13 | DB12 | DB11                   | DB10                 | DB9 | DB8    | DB7 | DB6 | DB5 | DB4   | DB3   | DB2           | DB1   | DB0   |

| C    | 0    | 0    | 0    | 0    | 0    | MR              | 1        | C1D11 | C1D10 | C1D9 | C1D8 | C1D7 | C1D6    | C1D5 | C1D4 | C1D3            | C1D2 | C1D1 | C1D0 | RD2                    | RD                   | R4  | R3     | R2  | R1  | R0  | C5(0) | C4(0) | C3(1)         | C2(1) | C1(1) |

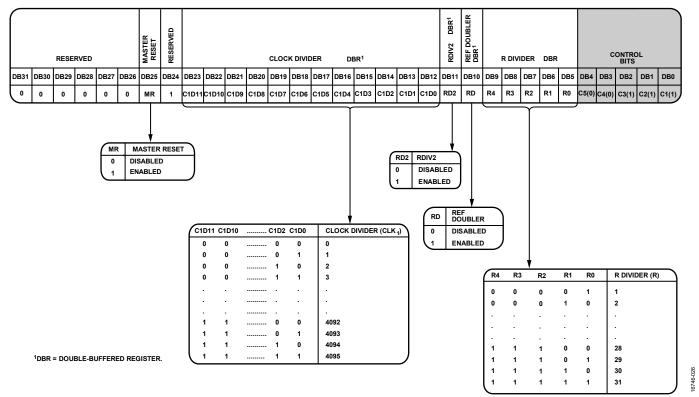

#### REGISTER 8 (R8)

|      |      |      |      |      |      |      | RE | SERVE | :D |      |      |      |      |      |      |      |      |      |      | FREQE | ENCY C | :AL DI | VIDER |     |     |     |       |       | ONTRO<br>BITS | L     |       |

|------|------|------|------|------|------|------|----|-------|----|------|------|------|------|------|------|------|------|------|------|-------|--------|--------|-------|-----|-----|-----|-------|-------|---------------|-------|-------|

| DB31 | DB30 | DB29 | DB28 | DB27 | DB26 | DB25 |    | _     |    | DB21 | DB20 | DB19 | DB18 | DB17 | DB16 | DB15 | DB14 | DB13 | DB12 | DB11  | DB10   | DB9    | DB8   | DB7 | DB6 | DB5 | DB4   | _     |               | DB1   | DB0   |

| C    | 1    | 0    | 0    | 0    | 0    | 0    | 0  | 0     | 0  | 0    | 0    | 0    | 0    | 0    | 0    | 0    | FC9  | FC8  | FC7  | FC6   | FC5    | FC4    | FC3   | FC2 | FC1 | FC0 | C5(0) | C4(1) | C3(0)         | C2(0) | C1(0) |

#### REGISTER 9 (R9)

|     |        |      |      |      |      |      |      |      |      |      |      |      |      | RESE | RVED |      |      |      |      |      |      |     |     |     |     |     |       | C     | ONTRO<br>BITS | DL    |       |

|-----|--------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-------|-------|---------------|-------|-------|

| DB3 | 1 DB30 | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18 | DB17 | DB16 | DB15 | DB14 | DB13 | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4   | DB3   | DB2           | DB1   | DB0   |

| C   | 0      | 1    | 0    | 1    | 0    | 1    | 0    | 0    | 0    | 1    | 0    | 0    | 0    | 0    | 0    | 1    | 0    | 1    | 1    | 1    | 0    | 0   | 1   | 0   | 0   | 1   | C5(0) | C4(1) | C3(0)         | C2(0) | C1(1) |

#### REGISTER 10 (R10)

|     |      |      |      |      |      |      |      |      |      |      |      |      | R    | ESER | /ED  |      |      |      |      |      |      |     |     |     |     |     |       | С     | ONTRO |       |       |

|-----|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-------|-------|-------|-------|-------|

| DB3 | DB30 | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18 | DB17 | DB16 | DB15 | DB14 | DB13 | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4   | DB3   | DB2   | DB1   | DB0   |

| 0   | 0    | 0    | 1    | 1    | 1    | 0    | 1    | 0    | 0    | 1    | 1    | 0    | 0    | 1    | 0    | 1    | 0    | 1    | 0    | 0    | 1    | 1   | 0   | 0   | 1   | 0   | C5(0) | C4(1) | C3(0) | C2(1) | C1(0) |

#### REGISTER 11 (R11)

|      |      |      |      |      |      |      |      |      | RESE | RVED |      |      |      |      |      |      |      |      |      | SD RESET | RESERVED | SING FULL<br>TRI RAMP | RAI<br>MO |     | RESERVED | CNTR |       | С     | ONTRO<br>BITS | DL    |       |

|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|----------|----------|-----------------------|-----------|-----|----------|------|-------|-------|---------------|-------|-------|

| DB31 | DB30 | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18 | DB17 | DB16 | DB15 | DB14 | DB13 | DB12 | DB11     | DB10     | DB9                   | DB8       | DB7 | DB6      | DB5  | DB4   | DB3   | DB2           | DB1   | DB0   |

| ( o  | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | SDR      | 0        | SFT                   | RM1       | RM0 | 0        | CR   | C5(0) | C4(1) | C3(0)         | C2(1) | C1(1) |

#### REGISTER 12 (R12)

|      |      |      |      | RES  | ERVE | )    |      |      |      |      | c    | DE<br>CURF |      | P    | RESERVED | CP TRISTATE<br>DBR1 |      |      |      | RES  | ERVED | )   |     |     |     |     |       | С     | ONTRO<br>BITS | DL    |       |

|------|------|------|------|------|------|------|------|------|------|------|------|------------|------|------|----------|---------------------|------|------|------|------|-------|-----|-----|-----|-----|-----|-------|-------|---------------|-------|-------|

| DB31 | DB30 | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20 | DB19       | DB18 | DB17 | DB16     | DB15                | DB14 | DB13 | DB12 | DB11 | DB10  | DB9 | DB8 | DB7 | DB6 | DB5 | DB4   | DB3   | DB2           | DB1   | DB0   |

| C    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1    | 0    | ссз  | CC2        | CC1  | CC0  | 1        | CTRI                | 0    | 0    | 0    | 0    | 0     | 0   | 0   | 0   | 0   | 0   | C5(0) | C4(1) | C3(1)         | C2(0) | C1(0) |

<sup>1</sup>DBR = DOUBLE BUFFERED REGISTER—BUFFERED BY THE WRITE TO REGISTER 5.

図 22. レジスタの一覧(レジスタ 7~レジスタ 12)

16746-018

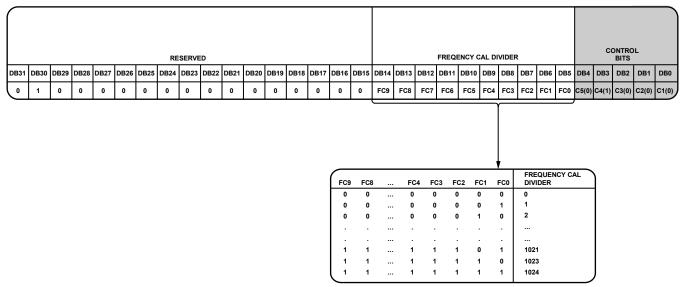

#### REGISTER 13 (R13)

|      |      |      |      | RESER | VED  |      |      |      |      | TE SET | CLK DIV | ō    |       |       |      |      |      | CLOC | C DIVID | 0ER 2 |      |      |      |      | CLK DIV | SEL  |       | C     | ONTRO<br>BITS | DL    |       |

|------|------|------|------|-------|------|------|------|------|------|--------|---------|------|-------|-------|------|------|------|------|---------|-------|------|------|------|------|---------|------|-------|-------|---------------|-------|-------|

| DB31 | DB30 | DB29 | DB28 | DB27  | DB26 | DB25 | DB24 | DB23 | DB22 | DB21   | DB20    | DB19 | DB18  | DB17  | DB16 | DB15 | DB14 | DB13 | DB12    | DB11  | DB10 | DB9  | DB8  | DB7  | DB6     | DB5  | DB4   | DB3   | DB2           | DB1   | DB0   |

| C    | 0    | 0    | 0    | 0     | 0    | 0    | 0    | 0    | 0    | LES    | CDM1    | CDM0 | C2D11 | C2D10 | C2D9 | C2D8 | C2D7 | C2D6 | C2D5    | C2D4  | C2D3 | C2D2 | C2D1 | C2D0 | CDS1    | CDS0 | C5(0) | C4(1) | C3(1)         | C2(0) | C1(1) |

#### REGISTER 14 (R14)

| Tx_DATA INV | TX RAMP CLK | RE   | ESERVE | ĒD   |      | ATION<br>EL |      | VIATIO | N OFFS | SET  |      |      |      |      |      |      | ſ    | DEVIAT | ION W | ORD  |      |     |     |     |     |     |       | С     | ONTRO<br>BITS | )L    |       |

|-------------|-------------|------|--------|------|------|-------------|------|--------|--------|------|------|------|------|------|------|------|------|--------|-------|------|------|-----|-----|-----|-----|-----|-------|-------|---------------|-------|-------|

| DB31        | DB30        | DB29 | DB28   | DB27 | DB26 | DB25        | DB24 | DB23   | DB22   | DB21 | DB20 | DB19 | DB18 | DB17 | DB16 | DB15 | DB14 | DB13   | DB12  | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4   | DB3   | DB2           | DB1   | DB0   |

| TDI         | TRC         | 0    | 0      | 0    | DS1  | DS0         | DO3  | DO2    | DO1    | DO0  | DW15 | DW14 | DW13 | DW12 | DW11 | DW10 | DW9  | DW8    | DW7   | DW6  | DW5  | DW4 | DW3 | DW2 | DW1 | DW0 | C5(0) | C4(1) | C3(1)         | C2(1) | C1(0) |

#### REGISTER 15 (R15)

|      |      |       |      |      |      |          |      |      |      |      |      |      |      |      |      | • (   | ,    |      |      |      |      |     |     |     |     |     |       |       |               |       |       |

|------|------|-------|------|------|------|----------|------|------|------|------|------|------|------|------|------|-------|------|------|------|------|------|-----|-----|-----|-----|-----|-------|-------|---------------|-------|-------|

|      | R    | ESERV | ED   |      |      | EP<br>EL |      |      |      |      |      |      |      |      | STE  | EP WO | RD   |      |      |      |      |     |     |     |     |     |       | co    | ONTRO<br>BITS | L     |       |

|      |      |       |      |      | ,    |          |      |      |      |      |      |      |      |      |      |       |      |      |      |      |      |     |     |     |     |     |       |       | Dilo          |       |       |

| DB31 | DB30 | DB29  | DB28 | DB27 | DB26 | DB25     | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18 | DB17 | DB16 | DB15  | DB14 | DB13 | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4   | DB3   | DB2           | DB1   | DB0   |

| O    | 0    | 0     | 0    | 0    | SS1  | SS0      | SW19 | SW18 | SW17 | SW16 | SW15 | SW14 | SW13 | SW12 | SW11 | SW10  | SW9  | SW8  | SW7  | SW6  | SW5  | SW4 | SW3 | SW2 | SW1 | SW0 | C5(0) | C4(1) | C3(1)         | C2(1) | C1(1) |

#### REGISTER 16 (R16)

|      |      | RE   | ESERVI | ĒD   |      |      | DEI<br>SEL |      | BESERVED |      | Tx_DATA<br>TRIGGER | RAMP DEL |      | RESERVED |      |      |      |      | DEL  | AY ST | ART W | ORD |     |     |     |     |       | C     | ONTRO<br>BITS | DL    |       |

|------|------|------|--------|------|------|------|------------|------|----------|------|--------------------|----------|------|----------|------|------|------|------|------|-------|-------|-----|-----|-----|-----|-----|-------|-------|---------------|-------|-------|

| DB31 | DB30 | DB29 | DB28   | DB27 | DB26 | DB25 | DB24       | DB23 | DB22     | DB21 | DB20               | DB19     | DB18 | DB17     | DB16 | DB15 | DB14 | DB13 | DB12 | DB11  | DB10  | DB9 | DB8 | DB7 | DB6 | DB5 | DB4   | DB3   | DB2           | DB1   | DB0   |

| 0    | 0    | 0    | 0      | 0    | 0    | 0    | DSL1       | DSL0 | 0        | 0    | TR1                | RD       | 0    | 0        | DS11 | DS10 | DS9  | DS8  | DS7  | DS6   | DS5   | DS4 | DS3 | DS2 | DS1 | DS0 | C5(1) | C4(0) | C3(0)         | C2(0) | C1(0) |

#### REGISTER 17 (R17)

|     |      |      |      |      |      |      |      |      |      |      |      |      | RESE | RVED |      |      |      |      |      |      |      |     |     |     |     |     |       | С     | ONTRO<br>BITS |       |       |   |

|-----|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-------|-------|---------------|-------|-------|---|

| DB3 | DB30 | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18 | DB17 | DB16 | DB15 | DB14 | DB13 | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4   | DB3   | DB2           | DB1   | DB0   | ĺ |

| C   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0   | 0   | 0   | 0   | 0   | C5(1) | C4(0) | C3(0)         | C2(0) | C1(1) | 1 |

図 23. レジスタの一覧(レジスタ 13~レジスタ 17)

6746-121

#### レジスタ 0

#### 制御ビット

ビット [C5:C1] に 00000 を設定すると、レジスタ R0 が設定されます。このレジスタを設定するための入力データ・フォーマットを図 24に示します。

#### 予備

ビット [DB31:DB13] は予備で、図 24 に示すように設定する必要があります。

#### トランスミッタ 2(Tx2)の振幅キャリブレーション

ビット DB12 は、Tx2 出力の振幅キャリブレーションを制御するビットです。通常動作では、このビットを 0 に設定します。このビットを 1 に設定すると、Tx2 出力の振幅キャリブレーションが実行されます。ビット DB12 は、図 24 では Tx2 AMP CALとして示されています。

#### Tx1 の振幅キャリブレーション

ビット DB11 は、Tx1 出力の振幅キャリブレーションを制御する ビットです。通常動作では、このビットを 0 に設定します。こ のビットを 1 に設定すると、Tx1 出力の振幅キャリブレーショ ンが実行されます。ビット DB11 は、図 24 では Tx1 AMP CAL として示されています。

#### VCO の起動

ビット DB10 は VCO を起動するためのビットです。このビットを 0 に設定すると、VCO が停止し、1 に設定すると、VCO が起動します。ビット DB10 は、図 24 では PUP VCO として示されています。

#### VCO のキャリブレーション

ビット DB9 は、VCO の周波数キャリブレーションを制御するビットです。通常動作では、このビットを 0 に設定します。このビットを 1 に設定すると、VCO の周波数と振幅のキャリブレーションが実行されます。ビット DB9 は、図 24 では VCO CAL として示されています。

#### ADC の起動

ビットDB8は、ADCを起動するためのビットです。このビットを0に設定すると、ADCが停止し、1に設定すると、ADCが起動します。ビットDB8は、図24ではPUP ADCとして示されています。

#### Tx2 出力の起動

ビット DB7 は、Tx2 出力を起動するためのビットです。このビットを 0 に設定すると、Tx2 出力が停止し、1 に設定すると、Tx2 出力が起動します。常に、Tx1 (DB6) または Tx2 (DB7) のどちらか一方のトランスミッタ出力しか起動できません。ビット DB7 は、 $\mathbf{Z}$  24 では PUP  $\mathbf{Z}$  2 として示されています。

#### Tx1 出力の起動

ビット DB6 は、Tx1 出力を起動するためのビットです。このビットを 0 に設定すると、Tx1 出力が停止し、1 に設定すると、Tx1 出力が起動します。常に、Tx1 (DB6) または Tx2 (DB7) のどちらか一方のトランスミッタ出力しか起動できません。ビット DB6 は、 $\mathbf{\boxtimes}$  24 では PUP Tx1 として示されています。

#### LO 出力の起動

ビット DB5 は、LO 出力を起動するためのビットです。このビットを 0 に設定すると、LO 出力が停止し、1 に設定すると、LO 出力が起動します。ビット DB5 は、24 では PUP LO として示されています。

Rev. 0 — 16/39 —

|      |      |      |      |      |      |      |      | RESE | RVED |      |      |      |      |      |      |      |                       |                                |      |               | Tx AN | IP CAI | L REF C           | ODE   |       |       |       |       | NTROI<br>BITS | L     |       |

|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----------------------|--------------------------------|------|---------------|-------|--------|-------------------|-------|-------|-------|-------|-------|---------------|-------|-------|

| DB31 | DB30 | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18 | DB17 | DB16 | DB15 | DB14                  | DB13                           | DB12 | DB11          | DB10  | DB9    | DB8 I             | DB7   | DB6   | DB5   | DB4   | DB3   | DB2           | DB1   | DB0   |

| 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 0    | 1    | 1    | 1    | 1    | 1                     | 1                              | TAR7 | TAR6          | TAR5  | TAR4   | TAR3 T            | AR2   | TAR1  | TAR0  | C5(0) | C4(0) | C3(0)         | C2(0) | C1(1) |

|      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      | 0<br>0<br>0<br>0<br>0 | 7 TAR<br>0<br>0<br>0<br>0<br>0 |      | (             | 1 (   | )      | 0<br>1<br>2<br>3  | MP CA | AL RE | F COD | E     |       |               |       |       |

|      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      | 1                     | 1                              |      |               | ) (   | )      | 252<br>253        |       |       |       |       |       |               |       |       |

|      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      | 1 1 1                 | 1<br>1<br>1                    |      | (<br><i>'</i> | 1 (   | )      | 253<br>254<br>255 |       |       |       |       | J     |               |       |       |

図 25. レジスタ 1 (R1)

### レジスタ 1

### 制御ビット

ビット [C5:C1] を 00001 に設定すると、レジスタ R1 が設定されます。このレジスタを設定するための入力データ・フォーマットを図 25 に示します。

#### 予備

ビット [DB31:DB13] は予備で、図 25 に示すように設定する必要があります。

### トランスミッタ振幅キャリブレーションの リファレンス・コード

ビット [DB12:DB5] は、キャリブレーション時の 2 つのトランスミッタ出力用に、トランスミッタ振幅キャリブレーションのリファレンス・コードを設定します。トランスミッタ振幅キャリブレーションのリファレンス・コードの設定により、トランスミッタ出力の出力電力を $-20dBm\sim8dBm$  に補正します(図 7参照)。ビット [DB12:DB5] は、図 25 では Tx AMP CAL REF CODE として示されています。

Rev. 0 – 17/39 –

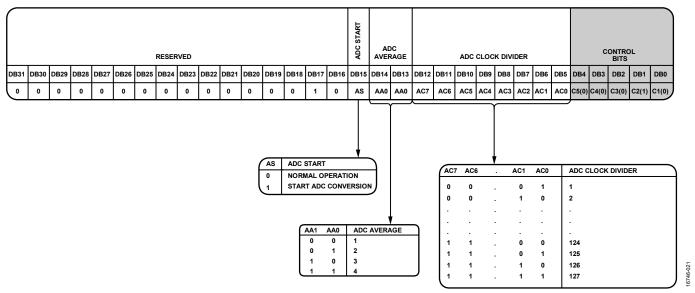

図 26. レジスタ 2(R2)

#### レジスタ2

#### 制御ビット

ビット [C5:C1] を 00010 に設定すると、レジスタ R2 が設定されます。このレジスタを設定するための入力データ・フォーマットを図 26 に示します。

#### 予備

ビット [DB31:DB16] は予備で、図 26 に示すように設定する必要があります。

#### ADC 開始

ビット DB15 は、ADC 変換を開始させます。このビットを 1 に 設定すると、ADC 変換が開始します。

#### ADC 平均

ビット [DB14:DB13] は、ADC 平均を設定します。これはADC 出力の平均数です(図 26 を参照)。

#### ADC クロック分周器

ビット [DB12:DB5] は、ADC のサンプリング・クロックとして使用されるクロック分周器を設定します(図 26 を参照)。R 分周器ブロックの出力は ADC クロック分周器をクロックします。分周値は、ADC サンプリング・クロックが 1MHz になるように設定します。

Rev. 0 — 18/39 —

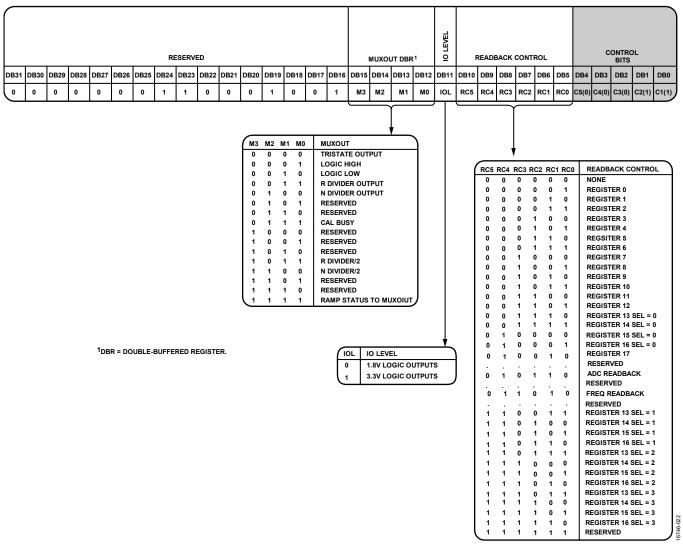

#### 図 27. レジスタ 3 (R3)

#### レジスタ3

#### 制御ビット

ビット [C5:C1] を 00011 に設定すると、レジスタ R3 が設定されます。このレジスタを設定するための入力データ・フォーマットを図 27に示します。

#### 予備

ビット [DB31:DB16] は予備で、図 27 に示すように設定する必要があります。

#### MUXOUT 制御

ビット [DB15:DB12] は、ADF5902 の内蔵マルチプレクサを制御します。真理値表については図27を参照してください。

#### 入出力(I/O)レベル

ビット DB11 は、DOUT のロジック・レベルを制御します。このビットを 0 に設定すると、DOUT のロジック・レベルが 1.8V に設定され、1 に設定すると、DOUT のロジック・レベルが 3.3V に設定されます。

#### リードバック制御

ビット [DB10:DB5] は、ADF5902 の DOUT へのリードバック・データを制御します。真理値表については図 27 を参照してください。

Rev. 0 – 19/39 –

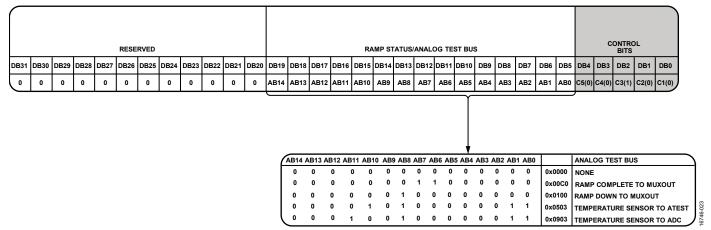

図 28. レジスタ 4(R4)

#### レジスタ 4

#### 制御ビット

ビット [C5:C1] を 00100 に設定すると、レジスタ R4 が設定されます。このレジスタを設定するための入力データ・フォーマットを図 28 に示します。

#### 予備

ビット [DB31:DB20] は予備で、図 28 に示すように設定する必要があります。

#### ランプ・ステータス/アナログ・テスト・バス

ビット [DB19:DB5] は、アナログ・テスト・バスと MUXOUT へのランプ・ステータスを制御します(図 28 参照)。

アナログ・テスト・バスにより、温度センサー用の内部テスト信号にアクセスできます。センサーは ATEST ピンまたは内部ADCに接続できます。

ビット DB [19:5] を 0 (値なし) に設定すると、ATEST ピンは ハイ・インピーダンスに設定されます。

MUXOUT のランプ・ステータス出力の場合、これらのモードに アクセスするには、レジスタ R3 の MUXOUT ビット(ビット [DB15:DB12] )を 1111 に設定する必要があります。

Rev. 0 — 20/39 —

図 29. レジスタ 5 (R5)

#### レジスタ 5

#### 制御ビット

ビット [C5:C1] を 00101 に設定すると、レジスタ R5 が設定されます。このレジスタを設定するための入力データ・フォーマットを図 29 に示します。

#### 予備

ビット [DB31:DB30] は予備で、図 29 に示すように設定する必要があります。

#### ランプ・オン

ビットDB29を1に設定すると、ランプが開始します。ビットDB29を0に設定すると、ランプ機能は無効になります。

連続ランプ・モードの場合、ビットDB29を0に設定するとランプは停止します。ランプを初期周波数で停止させる必要があるアプリケーションでは、ランプ機能を無効にする前にレジスタR6への書込みが必要です。単一ランプ・モードでは、単一ランプ機能を繰り返す前にレジスタR6への書込みが必要です。

連続ランプ・モードで、TX\_DATAピンを使用してランプ・オフをトリガすると、ランプは初期周波数で停止し、レジスタR6への書込みは不要です。単一ランプ・モードでTX\_DATAピンを使用する場合、単一ランプ機能を繰り返す前のレジスタR6への書込みは不要です。

#### 12 ビット整数値 (INT)

これらの 12 ビット(ビット [DB28:DB17] )は INT 値を設定します。これは、RF 分周係数の整数部を決定します。この INT 値は式 5 で使用されます。詳細については、RF 合成: 実際の動作例のセクションを参照してください。 $75\sim4095$  のすべての整数値を指定できます。

#### 12 ビット MSB 小数値(FRAC)

ビット [DB16:DB5] は、レジスタ R6 のビット [DB17:DB5] (FRAC LSB ワード) と共に使用して、フラクショナル・インターポレータにロードされる FRAC値を制御します。この FRAC値は、RF 分周係数全体の一部を決定します。これは式 1 でも使用されます。これらの 12 ビットは 25 ビット FRAC値の最上位ビット (MSB) であり、レジスタ R6 のビット [DB17:DB5] (FRAC LSB ワード) は最下位ビット (LSB) です。詳細については、RF 合成:実際の動作例のセクションを参照してください。

Rev. 0 — 21/39 —

<sup>1</sup>DBR = DOUBLE-BUFFERED REGISTER.

図 30. レジスタ 6 (R6)

### レジスタ 6

#### 制御ビット

ビット [C5:C1] を 00110 に設定すると、レジスタ R6 が設定さ れます。このレジスタを設定するための入力データ・フォーマ ットを図30に示します。

#### 予備

ビット [DB31:DB18] は予備で、図 30 に示すように設定する必 要があります。

#### 13 ビット LSB FRAC 値

これらの 13 ビット (ビット [DB17:DB5] ) は、レジスタ R5 の ビット [DB16:DB5] (FRAC MSB ワード) と共に使用して、フ ラクショナル・インターポレータにロードされる FRAC 値を制 御します。この FRAC 値は、RF 分周係数全体の一部を決定しま す。これは式 1 でも使用されます。これらの 13 ビットは 25 ビ ット FRAC 値の最下位ビット (LSB) であり、レジスタ R5 のビ ット [DB16:DB5] (FRAC MSB ワード) は最上位ビット (MSB) です。詳細については、RF 合成:実際の動作例のセク ションを参照してください。

16746-025

図 31. レジスタ 7(R7)

#### レジスタ7

#### 制御ビット

ビット [C5:C1] を 00111 に設定すると、レジスタ R7 が設定されます。このレジスタを設定するための入力データ・フォーマットを図 31 に示します。

#### 予備

ビット [DB31:DB26] は予備で、図 31 に示すように設定する必要があります。

#### マスタ・リセット

ビット DB25 は、デバイスをマスタ・リセットするビットです。 このビットを 1 に設定すると、デバイスとすべてのレジスタ・ マップがリセットされます。このビットを 0 に設定すると、デ バイスは通常動作に戻ります。

#### クロック分周器

ビット [DB23:DB12] は、クロック分周器 (CLK<sub>1</sub>) の値を制御します (図31を参照)。 CLK<sub>1</sub>値は、VCO周波数キャリブレーションの分周器を設定します。 PFD周波数  $(f_{PFD})$  / CLK<sub>1</sub>が25kHz以下になるように分周器を設定します。

例えば、 $f_{PFD}$  = 50MHz の場合、 $f_{PFD}$ /CLK $_1$  < 25kHz になるように CLK $_1$  = 2048 を設定します。

CLK<sub>1</sub> 値は、ランプ・モードでタイム・ステップの期間を決定するのにも使用されます。詳細については、ランプと変調のセクションを参照してください。

#### 2分周(RDIV2)

DB11 ビットを 1 に設定すると、R カウンタと VCO キャリブレーション・ブロックの間に 2 分周を行うトグル・フリップフロップが挿入されます。

#### リファレンス・ダブラ

DB10を0に設定すると、REF<sub>IN</sub>信号が直接5ビットRカウンタに入力され、ダブラがディスエーブルされます。このビットを1に設定すると、REF<sub>IN</sub>周波数が2逓倍されてから、REF<sub>IN</sub>信号が5ビットRカウンタに入力されます。ダブラがディスエーブルされると、REF<sub>IN</sub>の立下がりエッジは、フラクショナル・シンセサイザへのPFD入力のアクティブ・エッジになります。ダブラがイネーブルされると、REF<sub>IN</sub>の立上がりエッジと立下がりエッジの両方がPFD入力のアクティブ・エッジになります。

リファレンス・ダブラをイネーブルした場合、位相ノイズ性能を最適化するために、レジスタ12でチャージ・ポンプ電流設定を0b0000~0b0111、つまり0.28mA~2.24mAでのみ使用することを推奨します。この場合、最善の方法は、チャージ・ポンプ電流が1.12mAまたは1.4mAになるようにループ・フィルタを設計してから、プログラマブルなチャージ・ポンプ電流を使用して周波数応答を調整することです。

ダブラがイネーブル時の最大許容 REF<sub>IN</sub>周波数は 50MHz です。

#### 5 ビット R 分周器

5ビットRカウンタを使用すると、入力リファレンス周波数 (REF<sub>IN</sub>) を分周してVCOのキャリブレーション・ブロックに リファレンス・クロックを供給できます。分周比は $1\sim31$ が可能です。

Rev. 0 — 23/39 —

図 32. レジスタ 8 (R8)

|      |      |      |      |      |      |      |      |      |      |      |      |      |      | RESE | RVED |      |      |      |      |      |      |     |     |     |     |     |       | C     | DNTRO<br>BITS | L     |       |

|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-------|-------|---------------|-------|-------|

| DB31 | DB30 | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18 | DB17 | DB16 | DB15 | DB14 | DB13 | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4   | DB3   | DB2           | DB1   | DB0   |

| C    | 0    | 1    | 0    | 1    | 0    | 1    | 0    | 0    | 0    | 1    | 0    | 0    | 0    | 0    | 0    | 1    | 0    | 1    | 1    | 1    | 0    | 0   | 1   | 0   | 0   | 1   | C5(0) | C4(1) | C3(0)         | C2(0) | C1(1) |

図 33. レジスタ 9 (R9 0x2A20B929)

|     |      |      |      |      |      |      |      |      |      |      |      |      |      | RESE | RVED |      |      |      |      |      |      |     |     |     |     |     |       | C     | ONTRO<br>BITS | )L    |       |

|-----|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-------|-------|---------------|-------|-------|

| DB3 | DB30 | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18 | DB17 | DB16 | DB15 | DB14 | DB13 | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4   | DB3   | DB2           | DB1   | DB0   |

| C   | 0    | 1    | 0    | 1    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1    | 0    | 1    | 1    | 1    | 0    | 0   | 1   | 0   | 0   | 1   | C5(0) | C4(1) | C3(0)         | C2(0) | C1(1) |

図 34. レジスタ 9(R9 0x2800B929)

#### レジスタ8

#### 制御ビット

ビット [C5:C1] を 01000 に設定すると、レジスタ R8 が設定されます。このレジスタを設定するための入力データ・フォーマットを図 32 に示します。

#### 予備

ビット [DB31:DB15] は予備で、図 32 に示すように設定する必要があります。

### 周波数キャリブレーション分周器

ビット [DB14:DB5] は、VCO 周波数キャリブレーション・クロックの分周器を設定します。PFD 周波数 ( $f_{PFD}$ ) / 周波数キャ

リブレーション分周器が 100kHz以下になるように分周器を設定します(図 32 を参照)。

#### レジスタ9

レジスタ 9 のビットは予備で、VCO キャリブレーションを行う前に、16 進ワード 0x2A20B929 を使用して、図 33 に示すように設定する必要があります。

レジスタ 9 のビットは、通常動作では 16 進ワード 0x2800B929 を使用して、図 34 に示すように設定する必要があります。

詳細については、アプリケーション情報のセクションを参照してください。

Rev. 0

|   |     |      |      |      |      |      |      |      |      |      |      |      |      | R    | ESER\ | /ED  |      |      |      |      |      |      |     |     |     |     |     |       | С     | ONTRO<br>BITS |       |       |

|---|-----|------|------|------|------|------|------|------|------|------|------|------|------|------|-------|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-------|-------|---------------|-------|-------|

| D | 331 | DB30 | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18 | DB17  | DB16 | DB15 | DB14 | DB13 | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4   | DB3   |               | DB1   | DB0   |

|   | 0   | 0    | 0    | 1    | 1    | 1    | 0    | 1    | 0    | 0    | 1    | 1    | 0    | 0    | 1     | 0    | 1    | 0    | 1    | 0    | 0    | 1    | 1   | 0   | 0   | 1   | 0   | C5(0) | C4(1) | C3(0)         | C2(1) | C1(0) |

図 35. レジスタ 10 (R10 0x1D32A64A)

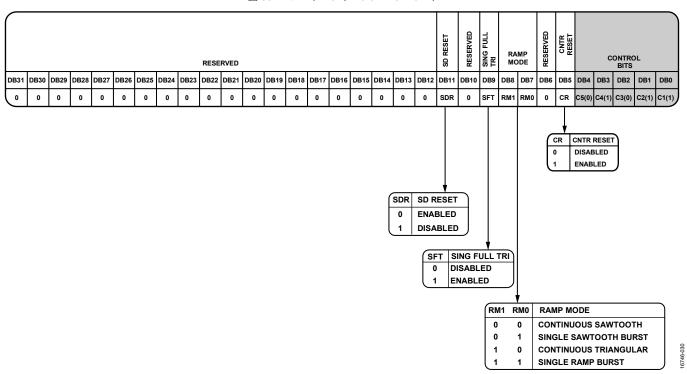

図 36. レジスタ 11 (R11)

#### レジスタ 10

レジスタ 10 のビットは予備で、16 進ワード 0x1D32A64A を使用して、図 35 に示すように設定する必要があります。

#### レジスタ 11

# 制御ビット

ビット [C5:C1] を 01011 に設定すると、レジスタ R11 が設定されます。このレジスタを設定するための入力データ・フォーマットを図 36 に示します。

#### 予備

ビット [DB31:DB12] 、ビット DB10、ビット DB6 は予備で、図 36に示すように設定する必要があります。

#### SD リセット

ほとんどのアプリケーションでは、ビット DB11 を 0 に設定します。このビットを 0 に設定すると、レジスタ R5 への書込みごとに  $\Sigma$ - $\Delta$  (SD) 変調器がリセットされます。レジスタ R5 への書込みごとに SD変調器をリセットする必要がない場合は、このビットを 1 に設定します。

#### 単一フル三角波

ビット DB9 を 1 に設定すると、単一フル三角波機能が有効になります。ビット DB9 を 0 に設定すると、この機能は無効になります。単一フル三角波機能を使用するには、ランプ・モード(レジスタ 11、ビット DB [8:7])を 0b11、単一のこぎり波バーストに設定する必要があります。詳細については、ランプと変調のセクションを参照してください。

#### ランプ・モード

ビット [DB8:DB7] は、生成される波形のタイプを決定します (図 36 を参照)。詳細については、ランプと変調のセクションを参照してください。

#### カウンタ・リセット

ビット DB5 は、カウンタ用のカウンタ・リセット・ビットです。 このビットを 1 に設定すると、デバイス・カウンタに対してカウンタ・リセットが実行されます。このビットを 0 に設定すると、デバイスは通常動作に戻ります。ビット DB5 は、図 36 では CNTR RESET として示されています。

Rev. 0 — 25/39 —

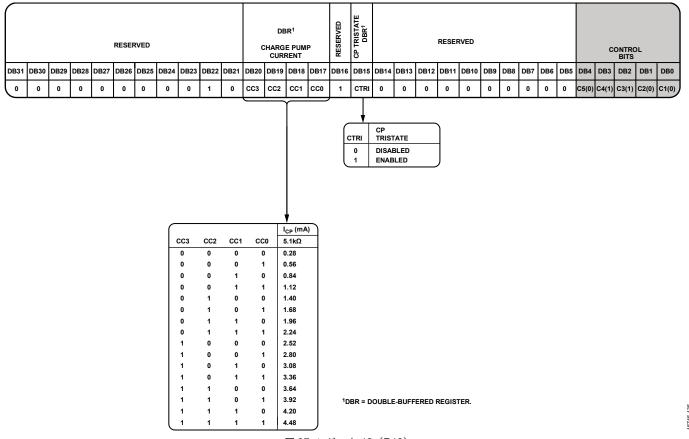

図 37. レジスタ 12 (R12)

## レジスタ 12

#### 制御ビット

ビット [C5:C1] を 01100 に設定すると、レジスタ R12 が設定されます。このレジスタを設定するための入力データ・フォーマットを図 37 に示します。

#### 予備

ビット [DB31:DB21] とビット DB16 は予備で、図 37 に示すように設定する必要があります。

#### チャージ・ポンプ電流設定

ビット [DB20:DB17] はチャージ・ポンプ電流を設定します(図37を参照)。これらのビットは、ループ・フィルタの設計に使用するチャージ・ポンプ電流を設定します。最善の方法は、チャージ・ポンプ電流が 2.24mA または 2.52mA になるようにループ・フィルタを設計してから、プログラマブルなチャージ・ポンプ電流を使用して周波数応答を調整することです。ダブラを有効にしている場合のチャージ・ポンプ電流の設定については、リファレンス・ダブラのセクションを参照してください。

#### チャージ・ポンプ・トライステート

ビット DB15 を1 に設定すると、チャージ・ポンプはトライステート・モードになります。通常のチャージ・ポンプ動作では、このビットを0に設定します。

Rev. 0 — 26/39 —

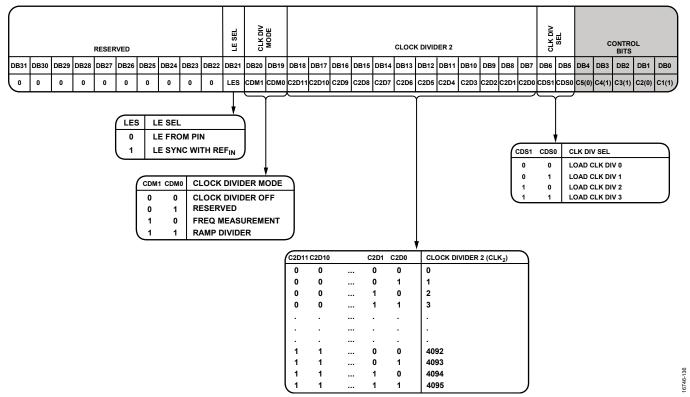

図 38. レジスタ 13 (R13)

#### レジスタ 13

#### 制御ビット

ビット [C5:C1] を 01101 に設定すると、レジスタ R13 が設定されます。このレジスタを設定するための入力データ・フォーマットを図 38 に示します。

#### 予備

ビット [DB31:DB22] は予備で、図 38 に示すように設定する必要があります。

#### LE 選択

アプリケーションによっては、LE ピンをリファレンス信号と同期させる必要があります。この同期を実行するには、ビット DB21を1に設定する必要があります。同期はデバイス内部で実行されます。

#### クロック分周器モード

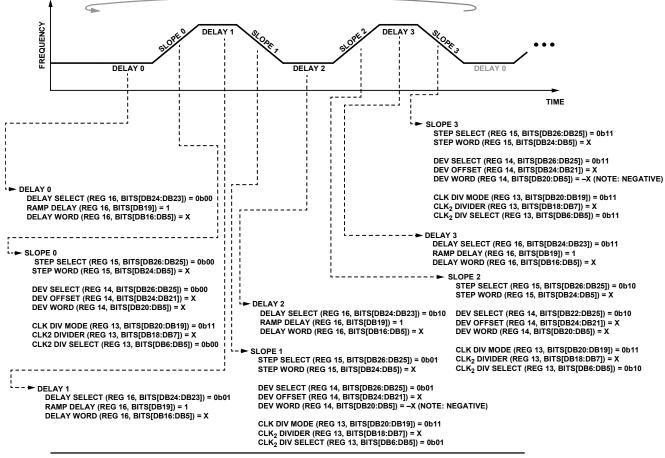

ビット [DB20;DB19] は、ランプ分周器モードを有効にするのに使用します。ランプ・モードを使用する際は、ビット [CDM1:CDM0] を 11 に設定します。それ以外の場合は、これらのビットを 0b00 に設定します。

#### 12 ビット・クロック分周器 (CLK₂) の値

デバイスがランプ・モードで動作する場合、ビット [DB18:DB7] によってクロック分周器( $CLK_2$ )のタイマを設定します(ランプと変調のセクションを参照)。

#### クロック分周器の選択

ビット [DB6:DB5] は、使用するランプ  $CLK_2$ のセグメントを選択します(図 38 を参照)。詳細については、ランプと変調のセクションを参照してください。ビット [DB6:DB5] は、図 38 では CLK DIV SEL として示されています。

Rev. 0 — 27/39 —

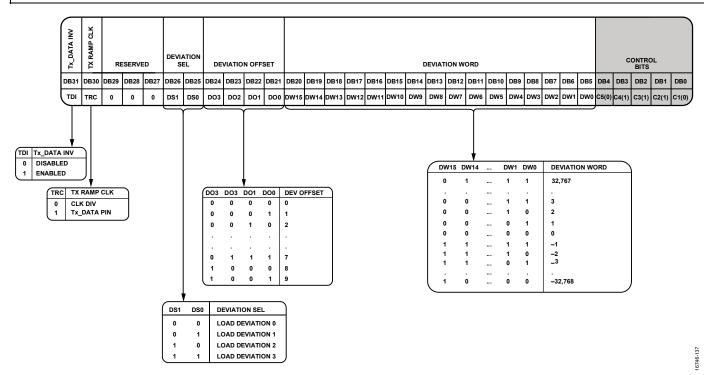

図 39. レジスタ 14(R14)

#### レジスタ 14

#### 制御ビット

ビット [C5:C1] を 01110 に設定すると、レジスタ R14 が設定されます。このレジスタを設定するための入力データ・フォーマットを図 39 に示します。

#### 予備

ビット [DB29:DB27] は予備で、図 39 に示すように設定する必要があります。

#### TX\_DATA 反転

ビット DB31 を 0 に設定すると、TX\_DATA によってトリガされるイベントは TX\_DATA パルスの立上がりエッジで発生します。ビット DB31 を 1 に設定すると、TX\_DATA によってトリガされるイベントは TX\_DATA パルスの立下がりエッジで発生します。

#### TX\_DATA ランプ・クロック

ビット DB30 を 0 に設定すると、クロック分周器クロックがランプのクロックに使用されます。ビット DB30 を 1 に設定すると、TX DATA ピンがランプのクロックに使用されます。

#### 偏差選択

ビット [DB26:DB25] は、ロードされる偏差ワードを選択します (図39を参照)。

#### 4 ビット偏差オフセット・ワード

ビット DB [24:21] は、偏差オフセット・ワードを決定します。 偏差オフセット・ワードは偏差分解能に影響します(ランプと 変調のセクションを参照)。

#### 16 ビット偏差ワード

ビット [DB20:DB5] は、2 の補数形式の符号付き偏差ワードを決定します。偏差ワードは偏差ステップを定義します(ランプと変調のセクションを参照)。

Rev. 0 — 28/39 —

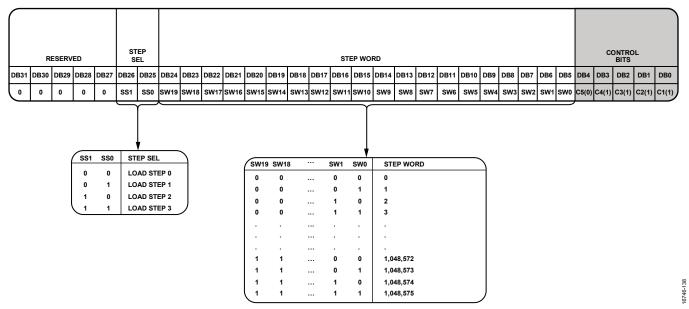

図 40. レジスタ 15 (R15)

#### レジスタ 15

#### 制御ビット

ビット [C5:C1] を 01111 に設定すると、レジスタ R15 が設定されます。このレジスタを設定するための入力データ・フォーマットを図 40 に示します。

#### 予備

ビット [DB31:DB27] は予備で、図 40 に示すように設定する必要があります。

#### ステップ選択

ビット [DB26:DB25] は、ロードされるステップ・ワードを選択します(図40を参照)。

#### 20 ビット・ステップ・ワード

ビット [DB22:DB3] はステップ・ワードを決定します。ステップ・ワードはランプのステップ数です(ランプと変調のセクションを参照)。

Rev. 0 — 29/39 —

CONTROL BITS RESERVED DB31 DB30 DB29 DB28 DB27 DB26 DB25 DB24 DB23 DB22 DB21 DB20 DB19 DB18 DB17 DB16 DB15 DB14 DB13 DB12 DB11 DB10 DB9 DB8 DB7 DB6 DB5 DB4 DB3 DB2 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 C5(1) C4(0) C3(0) C2(0) C1(1)

図 42. レジスタ 17(R17)

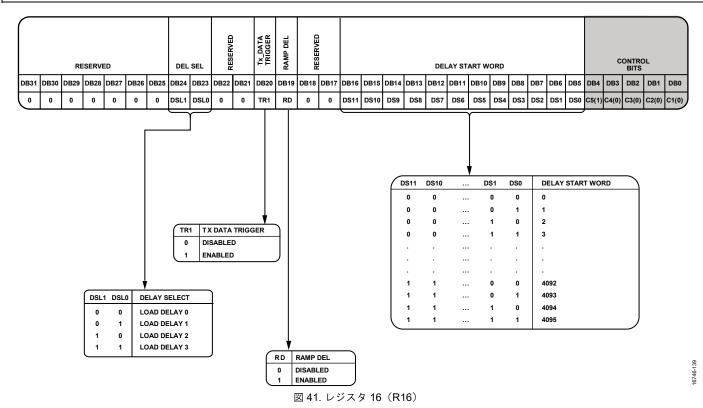

#### レジスタ 16

#### 制御ビット

ビット [C5:C1] を 10000 に設定すると、レジスタ R16 が設定されます。このレジスタを設定するための入力データ・フォーマットを図 41 に示します。

#### 予備

ビット [DB31:DB25] 、ビット [DB22:DB21] 、ビット [DB18:DB17] は予備で、図 41 に示すように設定する必要があります。

#### 遅延選択

ビット [DB24:DB23] は、ロードされる遅延ワードを選択します

#### TX\_DATA トリガ

ビットDB20を1に設定した場合、レジスタ5のビットDB29と組み合わされ、 $TX_DATA$ ピンがロジック・ハイになるとランプがアクティブになります。 $TX_DATA$ ピンに印加されるパルスのアクティブ・エッジを $REF_N$ リファレンス入力の立上がりエッジに同期させます。

$TX_DATA$ ピンに印加されるパルス幅は $4 \times 1/f_{PFD}$ の最小幅でなければなりません。ここで、 $f_{PFD}$ は位相周波数検出器(PFD)の周波数です。

ビットDB20を0に設定すると、この機能は無効になります。

連続三角波または連続のこぎり波のランプをアクティブにする場合、レジスタ5のビットDB29をハイにトグルした後にTX\_DATAピンにパルスを印加する必要があります。連続三角波または連続のこぎり波のランプを停止するには、レジスタ5のビットDB29をローにトグルした後にTX\_DATAパルスが必要です。

ビットDB20を0に設定すると、この機能は無効になります。

#### ランプ遅延

ビット DB19 を 1 に設定すると、ランプ間遅延機能が有効になります。ビット DB19 を 0 に設定すると、この機能は無効になります。

#### 12 ビット遅延ワード

ビット [DB16:DB5] は遅延ワードを決定します。遅延ワードはランプ開始遅延の期間を決定します。

#### レジスタ 17

レジスタ 17 のビットは予備で、図 42 に示すように、16 進ワード 0x00000011 を設定する必要があります。

Rev. 0 - 30/39 -

# アプリケーション情報

# 初期化シーケンス

デバイスをパワーアップした後、表 7 に示すプログラミング・シーケンスを実行します。

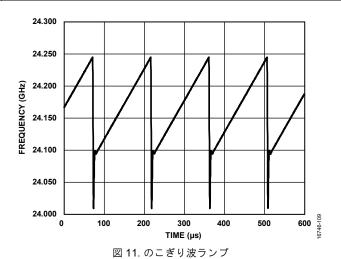

このシーケンスは、100 MHz リファレンスを使用して VCO を 24.025 GHz にロックします。上昇率は  $144 \mu s$  で 200 MHz です。下降率は  $9 \mu s$  で 200 MHz です。

#### 表 7. 初期化シーケンス

| ステップ           | レジスタ     | 16 進コード                                 | 説明                                                         |

|----------------|----------|-----------------------------------------|------------------------------------------------------------|

| 1              | R7       | 0x02000007                              | マスタ・リセット                                                   |

| 2              | R11      | 0x0000002B                              | カウンタをリセット                                                  |

| 3              | R11      | 0x0000000B                              | カウンタをイネーブル                                                 |

| 4              | R13      | 0x0018000D                              | ランプ分周器をイネーブル                                               |

| 5              | R10      | 0x1D32A64A                              | 予備                                                         |

| 6              | R9       | 0x2A20B929                              | VCOキャリブレーションの設定                                            |

| 7              | R8       | 0x40003E88                              | VCO 周波数キャリブレーション分周器のクロックを 100kHz に設定                       |

| 8              | R0       | 0x800FE520                              | デバイスと LO をパワーアップ                                           |

| 10µs の遅延       | •        | •                                       |                                                            |

| 9              | R7       | 0x01800827                              | $PFD = 50MHz$ , $CLK_1 = 2048$                             |

| 10             | R6       | 0x00000006                              | LSB FRAC = 0 に設定                                           |

| 11             | R5       | 0x01E38005                              | N = 241.175                                                |

| 12             | R4       | 0x00000004                              | ATEST ピンをハイ・インピーダンスに設定                                     |

| 13             | R3       | 0x01897803                              | I/O レベルを 3.3V に、CAL_BUSY を MUXOUT に設定                      |

| 14             | R2       | 0x00020642                              | ADC クロックを 1MHz に設定                                         |

| 15             | R1       | 0xFFF7FFE1                              | トランスミッタの振幅レベルを設定                                           |

| 16             | R0       | 0x800FE720                              | VCO 周波数キャリブレーションを開始                                        |

| 1200µs の遅延     | <u> </u> |                                         |                                                            |

| 17             | R0       | 0x800FE560                              | Tx1をオン、Tx2をオフ、LOをオン                                        |

| 18             | R0       | 0x800FED60                              | Txl 振幅キャリブレーション                                            |

| 500µs の遅延      | 1        | ******                                  | I I I I I I I I I I I I I I I I I I I                      |

| 19             | R0       | 0x800FE5A0                              | Tx1をオフ、Tx2をオン、LOをオン                                        |

| 20             | R0       | 0x800FF5A0                              | Tx2 振幅キャリブレーション                                            |

|                | 1        | *************************************** | INDIDATE COLUMN                                            |

| 21             | R17      | 0x00000011                              | 予備                                                         |

| 22             | R16      | 0x00000011                              | ランプ遅延レジスタ                                                  |

| 23             | R15      | 0x000010F                               | ステップ・レジスタに STEP_SEL = $0$ をロード、ステップ・ワードは $144$             |

| 24             | R15      | 0x0200012F                              | ステップ・レジスタに STEP SEL = $1$ をロード、ステップ・ワードは $9$               |

| 25             | R15      | 0x0400120F                              | ステップ・レジスタに STEP SEL = $2$ をロード、ステップ・ワードは 144               |

| 26             | R15      | 0x0600012F                              | ステップ・レジスタに STEP_SEL = $3$ をロード、ステップ・ワードは $9$               |

| 27             | R14      | 0x012038EE                              | 偏差レジスタに DEV SEL= $0$ 、DEV ワード= $455$ 、DEV オフセット= $9$ をロード  |

| 28             | R14      | 0x033C720E                              | 偏差レジスタに DEV SEL = 1、DEV ワード = $-1820$ 、DEV オフセット= $9$ をロード |

| 29             | R14      | 0x052038EE                              | 偏差レジスタに DEV_SEL = 2、DEV ワード = $455$ 、DEV オフセット= $9$ をロード   |

| 30             | R14      | 0x73C720E                               | 偏差レジスタに DEV SEL = 3、DEV ワード = $-1820$ 、DEV オフセット= 9をロード    |

| 31             | R13      | 0x0018050D                              | $\rho$ クロック・レジスタに CLK DIV SEL = 0、CLK2 0 = 10をロード          |

| 32             | R13      | 0x0018052D                              | クロック・レジスタに CLK DIV SEL = 1、CLK2 1 = 10 をロード                |

| 33             | R13      | 0x0018054D                              | クロック・レジスタに CLK DIV SEL = 1、CLK2 2 = 10 をロード                |

| 34             | R13      | 0x0018056D                              | クロック・レジスタに CLK DIV SEL = 3、CLK2_2 = 10 をロード                |

| 35             | R12      | 0x004F000C                              | チャージ・ポンプ電流 = 2.24mA                                        |

| 36             | R9       | 0x2800B929                              | ラヤージ・ホンノ 电 <sub>/m</sub> = 2.24mA<br>通常動作                  |

| 37             | R7       | 0x0100A027                              | 理 帝 男/丁F<br>PFD = 100MHz、CLK <sub>1</sub> = 10             |

| 38             | R6       | 0x00000006                              | PFD = 100MHZ、CLK <sub>1</sub> = 10<br>LSB FRAC = 0 に設定     |

| 39             | R5       |                                         |                                                            |

|                |          | 0x00F04005                              | INT =120、MSB FRAC = 512、24.025GHz にロック                     |

| 40             | R4       | 0x00002004                              | MUXOUTまでランプダウン                                             |

| 41<br>100 O'ET | R3       | 0x0189F803                              | I/O 電圧レベルを 3.3V                                            |

| 100μs の遅延      | D11      | 00000010D                               | ニンディートと選択                                                  |

| 42             | R11      | 0x0000010B                              | ランプ・モードを選択                                                 |

Rev. 0 - 31/39 -

# 再キャリブレーション・シーケンス

初期化シーケンスが完了してデバイスをパワーアップした後、ADF5902 を再キャリブレーションできます。再キャリブレーシ

ョン・シーケンスは、 $10^{\circ}$ の温度変化ごとに実行する必要があります。温度は、温度センサーを使用してモニタできます(温度センサーのセクションを参照)。

表 8. 再キャリブレーション・シーケンス

| 初期化シーケンスの  |          |            |                                         |

|------------|----------|------------|-----------------------------------------|

| ステップ番号     | レジスタ     | 16 進コード    | 説明                                      |

|            | R0       | 0x800FE500 | Tx1 をオフ、Tx2 をオフ、LO をオフ                  |

| 6          | R9       | 0x2A20B929 | 予備                                      |

| 9          | R7       | 0x01800827 | $PFD = 50MHz$ , $CLK_1 = 2048$          |

| 10         | R6       | 0x00000006 | LSB FRAC = 0 に設定                        |

| 11         | R5       | 0x01E38005 | N = 241.175                             |

| 12         | R4       | 0x00000004 | ATEST ピンをハイ・インピーダンスに設定                  |

| 13         | R3       | 0x01897803 | I/O レベルを 3.3V に、CAL_BUSY を MUXOUT に設    |

|            |          |            | 定                                       |

| 14         | R2       | 0x00020642 | ADC クロックを 1MHz に設定                      |

| 15         | R1       | 0xFFF7FFE1 | トランスミッタの振幅レベルを設定                        |

|            | R0       | 0x800FE700 | VCO 周波数キャリブレーションを開始                     |

| 1200μs の遅延 |          |            |                                         |

| 17         | R0       | 0x800FE560 | Tx1 をオン、Tx2 をオフ、LO をオン                  |

| 18         | R0       | 0x800FED60 | Tx1 振幅キャリブレーション                         |

| 500μs の遅延  |          |            | ·                                       |

| 19         | R0       | 0x800FE5A0 | Tx1をオフ、Tx2をオン、LOをオン                     |

| 20         | R0       | 0x800FF5A0 | Tx2 振幅キャリブレーション                         |

| 500μs の遅延  |          |            |                                         |

| 36         | R9       | 0x2800B929 | 予備                                      |

| 37         | R7       | 0x0100A027 | PFDを 100MHz、CLK_DIV1 = 10 に設定           |

| 38         | R6       | 0x00000006 | LSB FRAC = 0 に設定                        |

| 39         | R5       | 0x00F04005 | INT ワードを 120、MSB FRAC = 512、24.025GHz に |

|            |          |            | ロック                                     |

| 40         | R4       | 0x00002004 | MUXOUT までランプダウン                         |

| 41         | R3       | 0x0189F803 | I/O 電圧レベルを 3.3 V                        |

| 100μs の遅延  | <u>.</u> | <u>.</u>   |                                         |

| 42         | R11      | 0x0000010B | ランプ・モードを選択                              |

#### 温度センサー

ADF5902 は、ATEST ピンからアクセス可能な、または ADC 変換後の DOUT でデジタル・ワードとしてアクセス可能な温度センサーを内蔵しています。温度センサーは、-40 $^{\circ}$  $^{\circ}$  $^{\circ}$ 0つ動作温度範囲全体で動作します。室温で 1点キャリブレーションを実行し、結果をメモリに保存することで精度を向上できます。

アナログ・テスト・バスおよびテスト・バス上の温度センサー を ATEST ピンに接続すると (レジスタ 4 を 0x0000A064 に設定)、次式により ATEST 電圧を温度に変換できます。

Temperature (°C) =

$$\frac{\left(V_{ATEST} - V_{OFF}\right)}{V_{GAIN}}$$

(3)

ここで、

*V<sub>ATEST</sub>*は ATEST ピンの電圧。

$V_{OFF} = 0.699V$ 、オフセット電圧。

$V_{GAIN} = 6.4 \times 10^{-3}$ 、電圧ゲイン。

温度センサーの結果は、ADC を使ってデジタル・ワードに変換し、以下のシーケンスにより DOUT でリードバックできます。

- 1. レジスタ R4 に 0x00012064 を書き込んで、アナログ・テスト・バスを ADC に、温度センサーをアナログ・テスト・バスに接続します。

- 2. レジスタ R2 に 0x0002A802 を書き込んで、ADC 変換を開始します。

- レジスタ R3 に 0x0189FAC3 を書き込んで、ADC の出力データを DOUT に設定します。

- 4. DOUT をリードバックします。

- レジスタ R4 に 0x00002064 を書き込んで、レジスタ R4 を 初期値にリセットします。

- 6. レジスタ R2 に 0x00020642 を書き込んで、レジスタ R2 を 初期値にリセットします。

次式を使って、DOUTワードを温度に変換します。

Temperature (°C) =

$$\frac{\left(\left(ADC \times V_{LSB}\right) - V_{OFF}\right)}{V_{GAIN}}$$

(4)

ここで、

ADC は DOUT でリードバックされる ADC コード。

$V_{LSB} = 7.33 \text{mV}$ 、ADC の LSB 電圧。

$V_{OFF} = 0.699V$ 、オフセット電圧。

$V_{GAIN} = 6.4 \times 10^{-3}$ 、電圧ゲイン。

#### RF 合成:実際の動作例

次式は、ADF5902の設定方法を決定します。

$$RF_{OUT} = (INT + (FRAC/2^{25})) \times f_{REF} \times 2$$

(5)

ここで、

RFourはRF周波数出力。

INTは分周係数の整数部。

FRACは分周係数の分数部。

$$f_{REF} = REF_{IN} \times \left( (1+D) / (R \times (1+T)) \right)$$

(6)

ここで、

REF<sub>IN</sub>はリファレンス周波数入力。

Dはリファレンス・ダブラ・ビット、レジスタR7のDB10(0または1)。

Rはリファレンス分周係数。

*T*はリファレンス2分周指定、レジスタR7のDB11 (0または 1)。

例えば、24.125GHzのRF周波数出力(RFout)が必要で、100MHzのリファレンス周波数入力(REF<sub>IN</sub>)が利用可能なシステムでは、 $f_{REF}$ を50MHzに設定します。

式6から、

$f_{REF} = (100 \text{ MHz} \times (1+0) / (1 \times (1+1)) = 50 \text{ MHz}$ 式5から、

$24.125 \text{ GHz} = 50 \text{ MHz} \times (N + FRAC/2^{25}) \times 2$

NとFRACの値を計算します。

$$\begin{split} N &= \text{int } (RF_{OUT} / (f_{REF} \times 2) ) = 241 \\ FRAC &= F_{MSB} \times 2^{13} + F_{LSB} \\ F_{MSB} &= \text{int } ( (RF_{OUT} / (f_{REF} \times 2) ) - N) \times 2^{12} ) = 1024 \\ F_{LSB} &= \text{int } ( ( (RF_{OUT} / (f_{REF} \times 2) ) - N) \times 2^{12} ) - F_{MSB} ) \times 2^{13} ) = 0 \end{split}$$

ここで、

$F_{MSB}$ はレジスタ R5 の 12 ビット MSB FRAC 値。  $F_{LSB}$ はレジスタ R6 の 13 ビット LSB FRAC 値。 int () は括弧で囲んだ引数を整数にします。

# リファレンス・ダブラ

内蔵リファレンス・ダブラにより、入力リファレンス信号を2倍にすることができます。この倍増は、PFDの比較頻度を増やすのに役立ちます。PFD周波数を2倍にすると、通常はシステムのノイズ性能が3dB改善されます。

#### 周波数測定手順

次の手順で、ADF5902の出力ロック周波数を測定します。

- 1. レジスタ R3 で、リードバック制御ビット(ビット [DB10:DB5]) を 26 に設定します。

- 2. DOUTで周波数カウンタ値をリードバックし、この値を周 波数1として記録します(図3を参照)。

- 3. レジスタ R7 で、CLK1 ビット(ビット [DB23:DB12] )を 1808 に設定します。

- 4. レジスタ R13 で、CLK2 ビット(ビット [DB18:DB7] ) を 10 に設定します。

- レジスタ R5 で、ランプ・オン・ビット(ビット DB29)を 0 に設定します。

- 6. レジスタ R13 で、クロック分周器モード・ビット(ビット [DB20:DB19]) を 2 に設定します。

- 428μs (CLK<sub>DIV</sub>/f<sub>PFD</sub> (秒) ) の最小遅延を見込んでくださ

- 8. レジスタ R3 で、リードバック制御ビット(ビット [DB10:DB5]) を 26 に設定します。

- 9. DOUT で周波数カウンタ値をリードバックし、この値を周波数 2 として記録します。

周波数1>周波数2の場合、

周波数カウンタ値の差分= $(2^{16} - 周波数1) + 周波数2$ 。 周波数2>周波数1の場合、

周波数カウンタ値の差分= 周波数2-周波数1。

10. 次式を使用して、出力周波数を計算します。

出力周波数 = (周波数カウンタ値の差分  $CLK_{DIV}$ ) ×  $f_{PFD}$  ×  $N_{DIV}$  × 2

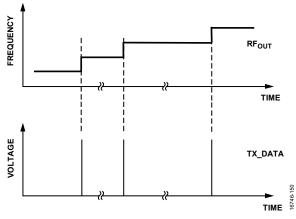

ここで、