# VCO 内蔵マイクロ波 広帯域シンセサイザ

データシート

**ADF4371**

### 特長

RF 出力周波数範囲:62.5MHz~32,000MHz フラクショナル N シンセサイザおよび インテジャーN シンセサイザ

高分解能 39 ビット・フラクショナル・モジュール

PFD スプリアス(代表値): -90dBc 積算実効値ジッタ: 38fs(1kHz~100MHz) 正規化位相ノイズ・フロア: -234dBc/Hz 位相周波数検出器(PFD)動作: 最大 250MHz

基準周波数動作:最大 600MHz

1、2、4、8、16、32、または64出力によるプログラマブルな 割り振り

RF8x および RFAUX8x で 62.5MHz~8,000MHz 出力

RF16x で 8,000MHz~16,000MHz 出力 RF32x で 16,000MHz~32,000MHz 出力

ロック時間:自動キャリブレーション使用時は約 3ms ロック時間:自動キャリブレーションをバイパスする場合は

<30µs

アナログ電源とデジタル電源:3.3V

VCO 電源: 3.3V および 5V RF 出力ミュート機能 7mm×7mm 48 ピン LGA パッケージ

# アプリケーション

ワイヤレス・インフラストラクチャ(移動通信用マルチ キャリア・グローバル・システム(MC-GSM)、5G)

式験装置/計測器 クロック生成 航空宇宙/防衛

# 概要

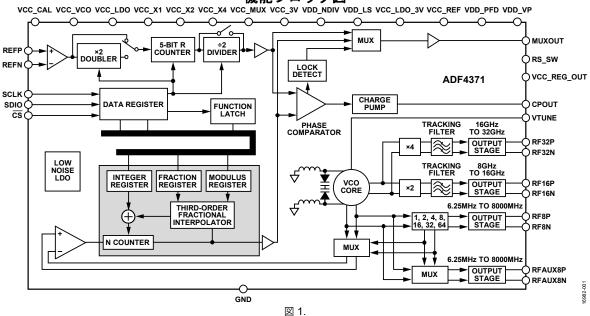

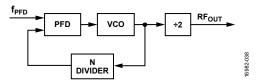

ADF4371 を外部ループ・フィルタおよび外部基準周波数と併せて使用することで、フラクショナル N またはインテジャーN フェーズ・ロック・ループ (PLL) シンセサイザが実現できます。広帯域マイクロ波の電圧制御発振器 (VCO) 設計により、62.5MHz~32GHzの周波数の生成が可能です。

ADF4371 には基本出力周波数 4000MHz~8000MHz の VCO が搭載されています。更に、VCO 周波数を結合して1、2、4、8、16、32、または 64 個の回路に割り振ることで、RF8x で 62.5MHz という低い無線周波数 (RF) の出力周波数を生成できます。周波数乗算器は、RF16x で 8GHz~16GHzの周波数を生成します。周波数 4 逓倍器は、RF32x で 16GHz~32GHz の周波数を生成します。RFAUX8x は RF8x の周波数範囲を 2 倍にする他、VCO 出力への直接アクセスを可能にします。不要な周波数逓倍積を抑えるために、乗算器と RF16x および RF32x の出力段との間には高調波フィルタがあります。

すべてのオンチップ・レジスタは、3線式インターフェースによって制御されます。ADF4371は、3.15V~3.45Vのアナログ電源とデジタル電源で動作し、VCO電源では5Vで動作します。また、ADF4371には、ハードウェアおよびソフトウェア向けのパワーダウン・モードも搭載されています。

#### 機能ブロック図

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって 生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示 的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有 者の財産です。※日本語版資料はREVISION が古い場合があります。最新の内容については、英語版をご参照ください。

©2019 Analog Devices, Inc. All rights reserved.

Rev. 0

本 社/〒105-6891

東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 10F 雷話 03 (5402) 8200

大 阪営業所/〒532-0003

大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 10F 電話 06 (6350) 6868

名古屋営業所/〒451-6038

愛知県名古屋市西区牛島町 6-1 名古屋ルーセントタワー 38F 電話 052 (569) 6300

# 目次

| 特長                   | 1  |

|----------------------|----|

| アプリケーション             | 1  |

| 概要                   | 1  |

| 機能ブロック図              | 1  |

| 改訂履歴                 | 2  |

| 仕様                   | 3  |

| タイミング仕様              | 7  |

| 絶対最大定格               | 8  |

| 熱抵抗                  | 8  |

| ESD に関する注意           | 8  |

| ピン配置およびピン機能の説明       | 9  |

| 代表的な性能特性             | 11 |

| 動作原理                 | 16 |

| RF シンセサイザ、実際例        | 16 |

| リファレンス入力感度           | 16 |

| リファレンス・ダブラとリファレンス分周器 | 17 |

| スプリアス最適化と高速ロック       | 17 |

| ジッタの最適化              | 17 |

| スプリアスのメカニズム          | 17 |

| ロック時間                | 17 |

| 回路の説明                | 19 |

| リファレンス入力             | 19 |

| RF N 分周器19                |

|---------------------------|

| PFD とチャージ・ポンプ20           |

| MUXOUT とロック検出20           |

| ダブル・バッファ20                |

| VCO                       |

| 出力段21                     |

| ダブラ21                     |

| 4 逓倍器22                   |

| 出力段のミュート22                |

| SPI                       |

| デバイス設定23                  |

| ステップ 1:SPIインターフェースの設定23   |

| ステップ 2: 初期化シーケンス23        |

| ステップ 3:周波数更新シーケンス23       |

| アプリケーション情報24              |

| 電源24                      |

| LGA パッケージの PCB 設計ガイドライン24 |

| 出力マッチング24                 |

| レジスタの一覧25                 |

| レジスタの詳細27                 |

| 外形寸法48                    |

| 1 18 18 19                |

# 改訂履歴

1/2019—Revision 0: Initial Version

# 仕様

特に指定のない限り、 $4.75V \le VCC\_VCO \le 5.25V$ 、他のすべての電源ピン  $(AV_{DD}) = 3.3V \pm 5\%$ 、GND = 0V、 $50\Omega$  を基準とする dBm、 $T_A = 全動作温度範囲。$

表 1.

| パラメータ                                | 記号                        | Min                                            | Тур       | Max                         | 単位    | テスト条件/コメント                                                                                                 |

|--------------------------------------|---------------------------|------------------------------------------------|-----------|-----------------------------|-------|------------------------------------------------------------------------------------------------------------|

| REFP AND REFN CHARACTERISTICS        |                           |                                                |           |                             |       |                                                                                                            |

| Input Frequency                      |                           |                                                |           |                             | 1     |                                                                                                            |

| Single-Ended Mode                    |                           | 10                                             |           | 500                         | MHz   | ダブラをディスエーブル                                                                                                |

| Differential Mode                    |                           | 10                                             |           | 600                         | MHz   | ダブラをディスエーブル                                                                                                |

| Single-Ended or Differential Mode    |                           | 10                                             |           | 125                         | MHz   | ダブラをイネーブル                                                                                                  |

| Input Sensitivity                    |                           |                                                |           |                             |       |                                                                                                            |

| Single-Ended Mode                    |                           | 0.4                                            |           | $\mathrm{AV}_{\mathrm{DD}}$ | V p-p | REFPを AV <sub>DD</sub> /2 でバイアス、AC カップリ                                                                    |

|                                      |                           |                                                |           |                             |       | ングにより AV <sub>DD</sub> /2 バイアスを確保                                                                          |

| Differential Mode                    |                           | 0.4                                            |           | 1.8                         | V p-p | LVDS (低電圧差動伝送) および LVPECL<br>(低電圧ポジティブ・エミッタ結合ロジック) 互換、REFP および REFN は 2.1V にバイアス、AC カップリングにより 2.1V バイアスを確保 |

| Input Capacitance                    |                           |                                                |           |                             |       |                                                                                                            |

| Single-Ended Mode                    |                           |                                                | 6.9       |                             | pF    |                                                                                                            |

| Differential Mode                    |                           |                                                | 1.4       |                             | pF    |                                                                                                            |

| Input Current                        |                           |                                                |           | ±150                        | μA    | シングルエンド・リファレンスに設定                                                                                          |

|                                      |                           |                                                |           | 300                         | μΑ    | 差動リファレンスに設定                                                                                                |

| Phase Detector Frequency             |                           |                                                |           | 160                         | MHz   | フラクショナル・モード                                                                                                |

|                                      |                           |                                                |           | 250                         | MHz   | インテジャー・モード                                                                                                 |

| CHARGE PUMP                          |                           |                                                |           |                             |       |                                                                                                            |

| Charge Pump Current, Sink and Source | $I_{CP}$                  |                                                |           |                             |       |                                                                                                            |

| High Value                           |                           |                                                | 5.6       |                             | mA    |                                                                                                            |

| Low Value                            |                           |                                                | 0.35      |                             | mA    |                                                                                                            |

| Current Matching                     |                           |                                                | 3         |                             | %     | $0.5$ V $\leq$ CPOUT ピンの電圧( $V_{CP}$ ) $\leq$ VDD_VP $-0.5$ V                                              |

| $I_{CP}$ vs. $V_{CP}$                |                           |                                                | 3         |                             | %     | $0.5V \le V_{CP} \le VDD_{VP} - 0.5V$                                                                      |

| $I_{CP}$ vs. Temperature             |                           |                                                | 1.5       |                             | %     | $V_{CP} = 2.5V$                                                                                            |

| LOGIC INPUTS                         |                           |                                                |           |                             |       | CS、SDIO、SCLK、CEは3Vロジック                                                                                     |

| Input High Voltage                   | $V_{\rm INH}$             | 1.17                                           |           |                             | V     |                                                                                                            |

| Input Low Voltage                    | $V_{INL}$                 |                                                |           | 0.63                        | V     |                                                                                                            |

| Input Current                        | $I_{\rm INH}/I_{\rm INL}$ |                                                |           | ±1                          | μΑ    |                                                                                                            |

| Input Capacitance                    | $C_{IN}$                  |                                                | 3.0       |                             | pF    |                                                                                                            |

| LOGIC OUTPUTS                        |                           |                                                |           |                             |       |                                                                                                            |

| Output High Voltage                  | $V_{OH}$                  | $\begin{array}{c} AV_{DD} \\ -0.4 \end{array}$ |           |                             | V     | 3.3V 出力を選択                                                                                                 |

|                                      |                           | 1.5                                            | 1.87<br>5 |                             | V     | 1.8V 出力を選択                                                                                                 |

| Output High Current                  | $I_{OH}$                  |                                                |           | 500                         | μΑ    |                                                                                                            |

| Output Low Voltage                   | $V_{OL}$                  |                                                |           | 0.4                         | V     | 出力ロー電流(I <sub>OL</sub> )= 500μA                                                                            |

Rev. 0 - 3/48 -

| パラメータ                                                        | 記号                          | Min   | Тур  | Max   | 単位           | テスト条件/コメント                                                                                                                                                         |

|--------------------------------------------------------------|-----------------------------|-------|------|-------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER SUPPLIES Supply Voltage (except VCO) <sup>1</sup>      | $\mathrm{AV}_{\mathrm{DD}}$ | 3.15  |      | 3.45  | V            | VCC_CAL、VCC_X4、VDD_X4、<br>VCC_X1、VDD_X1、VCC_X2、<br>VCC_MUX、VCC_3V、VDD_NDIV、<br>VDD_LS、VCC_LDO_3V、VCC_REF、<br>VDD_PFD、VDD_VP は AV <sub>DD</sub> としてグルー<br>プ化され、同電圧。 |

| Supply Voltage (except VCO)                                  | $AI_{DD}$                   |       | 190  | 260   | mA           | すべての出力をディスエーブル                                                                                                                                                     |

| Output Dividers                                              |                             |       |      |       |              |                                                                                                                                                                    |

| Divider = 2                                                  |                             |       | 14   | 20    | mA           | 2 分周ごとに 7mA 電流(代表値)を追加消費                                                                                                                                           |

| Divider = 64                                                 |                             |       | 50   | 65    | mA           |                                                                                                                                                                    |

| VCO Supply Voltage                                           | VCC_V<br>CO                 |       |      |       |              |                                                                                                                                                                    |

|                                                              |                             | 3.15  | 3.3  | 3.45  | V            | 3.3V 条件                                                                                                                                                            |

|                                                              |                             | 4.75  | 5    | 5.25  | V            | 5V 条件                                                                                                                                                              |

| VCO Supply Current                                           | $I_{VCO}$                   |       | 80   | 120   | mA           | 3.3V 条件                                                                                                                                                            |

|                                                              |                             |       | 135  | 180   | mA           | 5V 条件                                                                                                                                                              |

| RF8x Supply Current                                          |                             |       |      |       |              | RF8P と RF8N の出力段はプログラマブルであり、VCC_X1 に追加電流が流れる                                                                                                                       |

|                                                              |                             |       | 25   |       | mA           | -4dBm 設定                                                                                                                                                           |

|                                                              |                             |       | 39   |       | mA           | -1dBm 設定                                                                                                                                                           |

|                                                              |                             |       | 52   |       | mA           | 2dBm 設定                                                                                                                                                            |

|                                                              |                             |       | 65   |       | mA           | 5dBm設定                                                                                                                                                             |

| RFAUX8x Supply Current                                       |                             |       | 42   |       | mA           | -4dBm 設定                                                                                                                                                           |

|                                                              |                             |       | 56   |       | mA           | −1dBm 設定                                                                                                                                                           |

|                                                              |                             |       | 70   |       | mA           | 2dBm 設定                                                                                                                                                            |

|                                                              |                             |       | 84   |       | mA           | 5dBm 設定                                                                                                                                                            |

| RF16x Supply Current                                         |                             |       | 90   | 120   | mA           |                                                                                                                                                                    |

| RF32x Supply Current                                         |                             |       | 160  | 210   | mA           | " I'- 7 " F F F T T T T T T T T T T T T T T T T                                                                                                                    |

| Low Power Sleep Mode                                         |                             |       | 5.1  | 6.2   | mA           | ハードウェア・パワーダウン 3.3V VCO の<br>場合                                                                                                                                     |

|                                                              |                             |       | 8    | 9.5   | mA           | ハードウェア・パワーダウン 5V VCO の場合                                                                                                                                           |

|                                                              |                             |       | 21.5 | 25    | mA           | ソフトウェア・パワーダウン 3.3V VCO の<br>場合                                                                                                                                     |

|                                                              |                             |       | 23.7 | 28    | mA           | ソフトウェア・パワーダウン 5 V VCO の場合                                                                                                                                          |

| RF OUTPUT CHARACTERISTICS                                    |                             |       |      |       |              |                                                                                                                                                                    |

| VCO Frequency Range                                          |                             | 4000  |      | 8000  | MHz          | 基本波 VCO の範囲                                                                                                                                                        |

| RF8P and RF8N Output Frequency                               |                             | 62.5  |      | 8000  | MHz          |                                                                                                                                                                    |

| RFAUX8P and RFAUX8N Output Frequency                         |                             | 62.5  |      | 8000  | MHz          | a vigo III k                                                                                                                                                       |

| RF16P and RF16N Output Frequency                             |                             | 8000  |      | 16000 | MHz          | 2×VCO 出力                                                                                                                                                           |

| RF32P and RF32N Output Frequency<br>VCO Sensitivity          | V                           | 16000 |      | 32000 | MHz          | 4×VCO 出力                                                                                                                                                           |

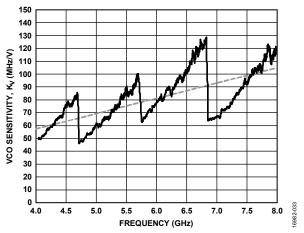

| For 5 V                                                      | $K_{V}$                     |       | 80   |       | MHz/V        | VCO 周波数 = 6GHz、K <sub>v</sub> プロットについて<br>は図 39 を参照                                                                                                                |

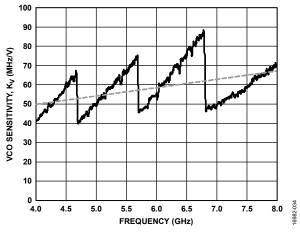

| For 3.3 V                                                    |                             |       | 60   |       | MHz/V        | VCO 周波数 = $6$ GHz、 $K_V$ プロットについて                                                                                                                                  |

| Frequency Pushing (Open-Loop)                                |                             |       | 8    |       | MHz/V        | は図 40 を参照                                                                                                                                                          |

| Frequency Pulling (Open-Loop)  Frequency Pulling (Open-Loop) |                             |       | 0.5  |       | MHz/V<br>MHz | 電圧定在波比(VSWR)=2:1 RF8P および<br>RF8N                                                                                                                                  |

|                                                              |                             |       | 30   |       | MHz          | VSWR = 2:1 RF16x                                                                                                                                                   |

| Maintain Lock Temperature Range <sup>2</sup>                 |                             |       |      | 125   | °C           | デバイスを再設定しなくともロックを維持                                                                                                                                                |

Rev. 0 - 4/48 -

| パラメータ                                                          | 記号 | Min | Тур  | Max | 単位     | テスト条件/コメント                               |

|----------------------------------------------------------------|----|-----|------|-----|--------|------------------------------------------|

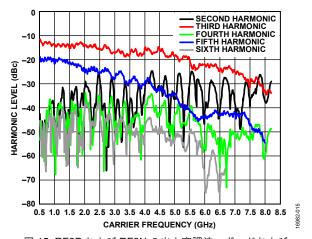

| Harmonic Content                                               |    |     |      |     |        |                                          |

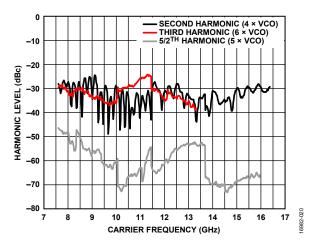

| Second Harmonic RF8P and RF8N                                  |    |     | -25  |     | dBc    | VCO基本出力(RF8P)                            |

|                                                                |    |     | -25  |     | dBc    | VCO 分周出力(RF8P)                           |

| Third Harmonic RF8P and RF8N                                   |    |     | -12  |     | dBc    | VCO基本出力(RF8P)                            |

|                                                                |    |     | -15  |     | dBc    | VCO 分周出力(RF8P)                           |

| Second Harmonic RF16P and RF16N                                |    |     | -30  |     | dBc    | 20GHz で測定                                |

| Third Harmonic RF16P and RF16N                                 |    |     | -30  |     | dBc    | 30 GHz で測定                               |

| Second Harmonic RF32P and RF32N                                |    |     | -30  |     | dBc    | 40 GHz で測定                               |

| Third Harmonic RF32P and RF32N                                 |    |     | -30  |     | dBc    | 60 GHz で測定                               |

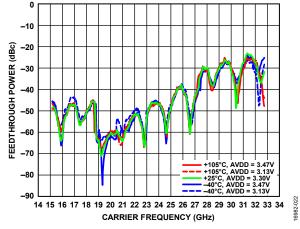

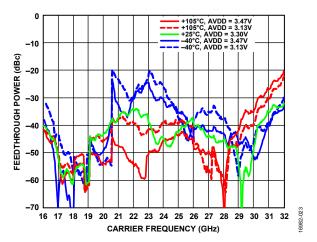

| Fundamental VCO Feedthrough                                    |    |     | -62  |     | dBc    | RF16x = 10GHz, VCO 周波数 = 5GHz            |

|                                                                |    |     | -30  |     | dBc    | RF8Pおよび RF8N = 1GHz、<br>VCO 周波数 = 4GHz   |

| RF Output Power Maximum Setting <sup>3</sup>                   |    |     | 7    |     | dBm    | RF8P = 4GHz、VCC_X1 ~ 7.5nH インダクタ         |

|                                                                |    |     | 5    |     | dBm    | RF8P = 8GHz、VCC_X1 へ 7.5nH インダクタ         |

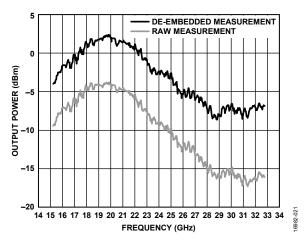

|                                                                |    |     | 0    |     | dBm    | RF16x = 8GHz                             |

|                                                                |    |     | 4    |     | dBm    | RF16x = 16GHz                            |

|                                                                |    |     | -1   |     | dBm    | RF32x = 16GHz                            |

|                                                                |    |     | -7   |     | dBm    | RF32x = 32GHz                            |

| RF Output Power Variation                                      |    |     | ±1   |     | dB     | RF8PおよびRF8N = 5GHz                       |

|                                                                |    |     | ±1   |     | dB     | RF16x = 10GHz                            |

|                                                                |    |     | ±1   |     | dB     | RF32x = 20GHz                            |

| RF Output Power Variation (over Frequency)                     |    |     | ±2   |     | dB     | RF8x および RFAUX8x = 4GHz~8GHz             |

|                                                                |    |     | ±2.5 |     | dB     | $RF16x = 8GHz \sim 16GHz$                |

|                                                                |    |     | ±5   |     | dB     | $RF32x = 16GHz \sim 32GHz$               |

| Level of Signal with RF Output Disabled                        |    |     | -50  |     | dBm    | RF8PおよびRF8N = 1GHz                       |

|                                                                |    |     | -44  |     | dBm    | RF8PおよびRF8N = 8GHz                       |

|                                                                |    |     | -41  |     | dBm    | RF8PおよびRF8N=8GHz、5V VCOの場                |

|                                                                |    |     | -75  |     | dBm    | RF16P = 8GHz                             |

|                                                                |    |     | -55  |     | dBm    | RF16P = 16GHz                            |

|                                                                |    |     | -85  |     | dBm    | RF32P = 16GHz                            |

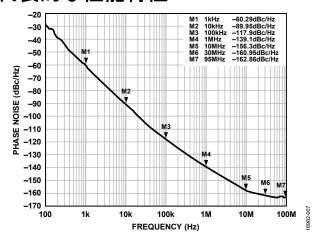

| JOISE CHARACTERISTICS                                          |    |     | -70  |     | dBm    | RF32P = 32GHz                            |

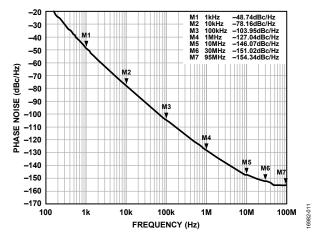

| Fundamental VCO Phase Noise Performance<br>where VCC VCO = 5 V |    |     |      |     |        | オープンループ状態での VCO ノイズ、<br>VCC_VCO = 5V     |

|                                                                |    |     | -117 |     | dBc/Hz | 4.0GHz 搬送波から 100kHz オフセット                |

|                                                                |    |     | -139 |     | dBc/Hz | 4.0GHz 搬送波から 1MHz オフセット                  |

|                                                                |    |     | -156 |     | dBc/Hz | 4.0GHz 搬送波から 10MHz オフセット                 |

|                                                                |    |     | -112 |     | dBc/Hz | 5.7GHz 搬送波から 100kHz オフセット                |

|                                                                |    |     | -136 |     | dBc/Hz | 5.7GHz 搬送波から 1MHz オフセット                  |

|                                                                |    |     | -153 |     | dBc/Hz | 5.7GHz 搬送波から 10MHz オフセット                 |

|                                                                |    |     | -109 |     | dBc/Hz | 8.0GHz 搬送波から 100kHz オフセット                |

|                                                                |    |     | -133 |     | dBc/Hz | 8.0GHz 搬送波から 1MHz オフセット                  |

|                                                                |    |     |      |     |        |                                          |

| RF16x Output Phase Noise Performance where                     |    |     | -152 |     | dBc/Hz | 8.0GHz 搬送波から 10MHz オフセット<br>VCC_VCO = 5V |

| VCC_VCO=5 V                                                    |    |     |      |     |        |                                          |

|                                                                |    |     | -106 |     | dBc/Hz | 11.4GHz 搬送波から 100kHz オフセット               |

|                                                                |    |     | -130 |     | dBc/Hz | 11.4GHz搬送波から 1MHzオフセット                   |

|                                                                |    |     | -146 |     | dBc/Hz | 11.4GHz搬送波から 10MHzオフセット                  |

|                                                                |    |     | -103 |     | dBc/Hz | 16GHz 搬送波から 100kHz オフセット                 |

|                                                                |    |     | -127 |     | dBc/Hz | 16GHz搬送波から 1MHzオフセット                     |

|                                                                |    |     | -145 |     | dBc/Hz | 16GHz搬送波から 10MHzオフセット                    |

Rev. 0 - 5/48 -

| パラメータ                                                               | 記号    | Min | Тур  | Max | 単位     | テスト条件/コメント                                                                                                                                    |

|---------------------------------------------------------------------|-------|-----|------|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| RF32x Output Phase Noise Performance where VCC_VCO = 5 V            |       |     |      |     |        | VCC_VCO = 5V                                                                                                                                  |

| _                                                                   |       |     | -100 |     | dBc/Hz | 24GHz 搬送波から 100kHz オフセット                                                                                                                      |

|                                                                     |       |     | -123 |     | dBc/Hz | 24GHz 搬送波から 1MHz オフセット                                                                                                                        |

|                                                                     |       |     | -140 |     | dBc/Hz | 24GHz 搬送波から 10MHz オフセット                                                                                                                       |

|                                                                     |       |     | -97  |     | dBc/Hz | 32GHz 搬送波から 100kHz オフセット                                                                                                                      |

|                                                                     |       |     | -121 |     | dBc/Hz | 32GHz 搬送波から 1MHz オフセット                                                                                                                        |

|                                                                     |       |     | -137 |     | dBc/Hz | 32GHz 搬送波から 10MHz オフセット                                                                                                                       |

| Fundamental VCO Phase Noise Performance<br>where<br>VCC VCO = 3.3 V |       |     |      |     |        | オープンループ状態での VCO ノイズ、<br>VCC_VCO = 3.3V                                                                                                        |

|                                                                     |       |     | -116 |     | dBc/Hz | 4.0GHz 搬送波から 100kHz オフセット                                                                                                                     |

|                                                                     |       |     | -137 |     | dBc/Hz | 4.0GHz 搬送波から 1MHz オフセット                                                                                                                       |

|                                                                     |       |     | -156 |     | dBc/Hz | 4.0GHz 搬送波から 10MHz オフセット                                                                                                                      |

|                                                                     |       |     | -111 |     | dBc/Hz | 5.7GHz 搬送波から 100kHz オフセット                                                                                                                     |

|                                                                     |       |     | -133 |     | dBc/Hz | 5.7GHz搬送波から 1MHzオフセット                                                                                                                         |

|                                                                     |       |     | -153 |     | dBc/Hz | 5.7GHz搬送波から 10MHzオフセット                                                                                                                        |

|                                                                     |       |     | -109 |     | dBc/Hz | 8.0GHz 搬送波から 100kHz オフセット                                                                                                                     |

|                                                                     |       |     | -132 |     | dBc/Hz | 8.0GHz 搬送波から 1MHz オフセット                                                                                                                       |

|                                                                     |       |     | -153 |     | dBc/Hz | 8.0GHz 搬送波から 10MHz オフセット                                                                                                                      |

| Normalized Inband Phase Noise Floor                                 |       |     |      |     |        |                                                                                                                                               |

| Fractional Channel <sup>4</sup>                                     |       |     | -233 |     | dBc/Hz |                                                                                                                                               |

| Integer Channel <sup>5</sup>                                        |       |     | -234 |     | dBc/Hz |                                                                                                                                               |

| Normalized 1/f Noise <sup>6</sup>                                   | PN1_f |     | -127 |     | dBc/Hz | 10kHz オフセット; 1GHz に正規化                                                                                                                        |

| Integrated RMS Jitter                                               |       |     | 38   |     | fs     | Wenzel オーブン制御の水晶発振器<br>(OCXO) を基準周波数入力 (REF <sub>IN</sub> ) として使用、インテジャーNモード、位相周波<br>数検出器 (PFD) = 245.76MHz、300kHzル<br>ープ・フィルタ帯域幅、1kHz~100MHz |

| Integer Boundary Spurs (Filtered)                                   |       |     | -90  |     | dBc    | インテジャー・チャンネルから 960kHz オ<br>フセット                                                                                                               |

| Inband Integer Boundary Spur (Unfiltered)                           |       |     | -55  |     | dBc    | インテジャー・チャンネルから 5kHz オフ<br>セットで測定                                                                                                              |

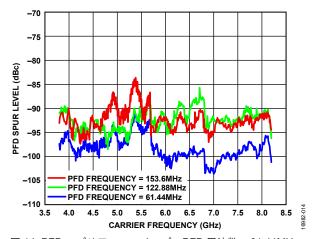

| Spurious Signals Due to PFD Frequency                               |       |     | -90  |     | dBc    |                                                                                                                                               |

| FREQUENCY LOCK TIME <sup>7</sup>                                    |       |     |      |     |        |                                                                                                                                               |

| Lock Time with Automatic Calibration                                |       |     | 3    |     | ms     |                                                                                                                                               |

| Lock Time with Automatic Calibration Bypassed                       |       |     | 30   |     | μs     |                                                                                                                                               |

$<sup>^1</sup>$   $T_A$  = 25  $^{\circ}$ C、 $AV_{DD}$  = 3.3V、 $VCC_{VCO}$  = 5.0V、プリスケーラ = 4/5、基準周波数( $f_{REFP}$ ) = 50MHz、PFD 周波数( $f_{PFD}$ ) = 50MHz、RF 周波数( $f_{RF}$ ) = 5001MHz。RF8x をイネーブル。すべての RF 出力をディスエーブル。

Rev. 0 - 6/48 -

<sup>2</sup> 設計および特性評価により確保。

<sup>&</sup>lt;sup>3</sup> EV-ADF4371SD2Z 評価用ボードの差動出力を Marki BAL-0036 バランを使用して結合し、評価用ボードとケーブルの損失を除いて、スペクトラム・アナライザで測定した RF 出力電力。 RF8P、RF8N、RFAUX8P、および RFAUX8N 用に選択された最大の電力出力。

<sup>&</sup>lt;sup>4</sup> この値を使用して、アプリケーションの位相ノイズを計算します。VCO 出力から見た帯域内位相ノイズ性能を計算するには、次式を使用します。 $-233+10\log{(f_{PPD})}+20logN$ 。求まった値は、フラクショナル・チャンネルの最低ノイズ・モードです。

$<sup>^5</sup>$ この値を使用して、アプリケーションの位相ノイズを計算します。 $^{15}$  VCO 出力から見た帯域内位相ノイズ性能を計算するには、次式を使用します。 $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{15}$   $^{1$

<sup>6</sup> PLL 位相ノイズは、1/f(フリッカ)ノイズと正規化 PLL ノイズ・フロアから構成されます。無線周波数( $f_{RF}$ )および周波数オフセット (f) での 1/f ノイズの寄与分を計算する式は、 $PN1_f+10log$ (10kHz/f) +20log(10kHz/f) で与えられます。正規化位相ノイズ・フロアとフリッカ・ノイズの両方が ADIsimPLL 設計ツールでモデル化されています。

<sup>7</sup> ロック時間は、代表的な評価用ボード構成で 100MHz ジャンプでの測定です。

# タイミング仕様

表 2.

| Parameter                                            | Symbol              | Test Conditions/Comments             | Min | Тур | Max | Unit |

|------------------------------------------------------|---------------------|--------------------------------------|-----|-----|-----|------|

| Serial Port Interface (SPI) Timing                   |                     | See Figure 2, Figure 3, and Figure 4 |     |     |     |      |

| SCLK Frequency                                       | $f_{SCLK}$          |                                      |     |     | 50  | MHz  |

| SCLK Period                                          | $t_{SCLK}$          |                                      | 20  |     |     | ns   |

| SCLK Pulse Width High                                | $t_{ m HIGH}$       |                                      | 10  |     |     | ns   |

| SCLK Pulse Width Low                                 | $t_{LOW}$           |                                      | 10  |     |     | ns   |

| SDIO Setup Time                                      | $t_{DS}$            |                                      | 2   |     |     | ns   |

| SDIO Hold Time                                       | $t_{\mathrm{DH}}$   |                                      | 2   |     |     | ns   |

| SCLK Falling Edge to SDIO Valid Propagation<br>Delay | t <sub>ACCESS</sub> |                                      | 10  |     |     | ns   |

| CS Rising Edge to SDIO High-Z                        | $t_Z$               |                                      | 10  |     |     | ns   |

| CS Fall to SCLK Rise Setup Time                      | $t_{\rm S}$         |                                      | 2   |     |     | ns   |

| SCLK Fall to CS Rise Hold Time                       | $t_{\rm H}$         |                                      | 2   |     |     | ns   |

# タイミング図

SCLK DON'T CARE

SDIO DON'T RIW A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5 D4 D3 D2 D1

図 5.3 線式、MSB ファースト、降順データ、ストリーミング

Rev. 0 - 7/48 -

# 絶対最大定格

特に指定のない限り、TA=25℃。

#### 表 3.

| Parameter                                            | Rating                                                   |

|------------------------------------------------------|----------------------------------------------------------|

| AV <sub>DD</sub> Rails to GND <sup>1</sup>           | -0.3 V to +3.6 V                                         |

| AV <sub>DD</sub> Rails to Each Other                 | -0.3 V to +0.3 V                                         |

| VCC_VCO to GND <sup>1</sup>                          | -0.3 V to +5.5 V                                         |

| VCC_VCO to AV <sub>DD</sub>                          | $-0.3 \text{ V to AV}_{DD} + 2.8 \text{ V}$              |

| CPOUT to GND <sup>1</sup>                            | $-0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$              |

| VTUNE to GND                                         | $-0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$              |

| Digital Input and Output Voltage to GND <sup>1</sup> | $-0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$              |

| Analog Input and Output Voltage to GND <sup>1</sup>  | $-0.3~\mathrm{V}$ to $\mathrm{AV_{DD}} + 0.3~\mathrm{V}$ |

| REFP and REFN to GND <sup>1</sup>                    | $-0.3 \text{ V}$ to $AV_{DD} + 0.3 \text{ V}$            |

| REFP to REFN                                         | ±2.1 V                                                   |

| Temperature                                          |                                                          |

| Operating Range                                      | -40°C to +105°C                                          |

| Storage Range                                        | −65°C to +125°C                                          |

| Maximum Junction                                     | 125 °C                                                   |

| Reflow Soldering                                     |                                                          |

| Peak                                                 | 260°C                                                    |

| Time at Peak                                         | 30 sec                                                   |

| Electrostatic Discharge (ESD)                        |                                                          |

| Charged Device Model                                 | 1.0 kV                                                   |

| Human Body Model                                     | 4.0 kV                                                   |

| Transistor Count                                     |                                                          |

| Complementary Metal-Oxide<br>Semiconductor (CMOS)    | 131439                                                   |

| Bipolar                                              | 4063                                                     |

$<sup>^{1}</sup>$  GND = 0V.

上記の絶対最大定格を超えるストレスを加えると、デバイスに 恒久的な損傷を与えることがあります。この規定はストレス定 格のみを指定するものであり、この仕様の動作のセクションに 記載する規定値以上でのデバイス動作を定めたものではありま せん。デバイスを長時間にわたり絶対最大定格状態に置くと、 デバイスの信頼性に影響を与えることがあります。

# 熱抵抗

熱性能は、プリント回路基板 (PCB) の設計と動作環境に直接 関連しています。PCB の熱設計には細心の注意が必要です。

$\theta_{1A}$  は、1 立方フィートの密封筐体内で測定された、自然対流でのジャンクションと周囲の間の熱抵抗です。 $\theta_{1C}$  は、ジャンクションとケースの間の熱抵抗です。

#### 表 4. 熱抵抗

| Package Type         | $\theta_{JA}$ | $\theta_{JC}$ | Unit |

|----------------------|---------------|---------------|------|

| CC-48-4 <sup>1</sup> | 25            | 14.4          | °C/W |

<sup>1</sup>テスト条件 1: 熱抵抗のシミュレーション値は、JESD51 規格に基づいています。

# ESD に関する注意

ESD (静電放電) の影響を受けやすいデバイスです。 電荷を帯びたデバイスや回路ボードは、検知されない

まま放電することがあります。本製品は当社独自の特許技術であるESD保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

Rev. 0 - 8/48 -

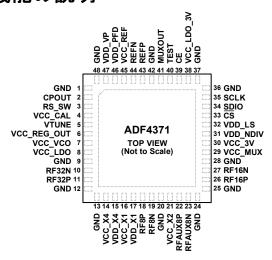

# ピン配置およびピン機能の説明

NOTES

1. THE LAND GRID ARRAY (LGA) HAS AN EXPOSED PAD THAT MUST BE SOLDERED TO A METAL PLATE ON THE PCB FOR MECHANICAL REASONS AND TO GND.

図 6. ピン配置

表 5. ピン機能の説明

| ピン番号                                               | 記号          | 説明                                                                                                                                          |

|----------------------------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 9, 12, 13, 20,<br>24, 25, 28,<br>36, 37, 42, 48 | GND         | グラウンド・リターン。                                                                                                                                 |

| 2                                                  | CPOUT       | チャージ・ポンプ出力。イネーブルすると、この出力は外部ループ・フィルタに±I <sub>CP</sub> を供給します。ループ・フィルタの出力は VTUNE に接続され、内部 VCO を駆動します。                                         |

| 3                                                  | RS_SW       | ループ・フィルタ・スイッチ。高速ロックのアプリケーションでループ・フィルタ抵抗のスイッチングに<br>使用されます。                                                                                  |

| 4                                                  | VCC_CAL     | 内部キャリブレーション・モニタ回路用電源。このピンの電圧は $3.15V\sim3.45V$ の範囲です。 VCC_CAL は $AV_{DD}$ と同じ値、すなわち、公称 $3.3V$ でなければなりません。                                   |

| 5                                                  | VTUNE       | VCO への制御入力。この電圧は出力周波数を決定し、CPOUT 出力電圧をフィルタ処理して得られます。                                                                                         |

| 6                                                  | VCC_REG_OUT | VCO 電源レギュレータ出力。VCO レギュレータの出力電源電圧はこのピンで得られ、10μF のコンデンサで GND にデカップリングし、VCC_VCO ピンに短絡する必要があります。外付け LDO レギュレータを VCC_VCO に接続する場合は、このピンをオープンにします。 |

| 7                                                  | VCC_VCO     | VCO の電源。このピンの電圧は 4.75V~5.25V の範囲です。このピンのできるだけ近くにデカップリング・コンデンサを配置し、アナログ・グランド・プレーンに接続します。最適な性能を得るために、この電源はクリーンで低ノイズでなければなりません。                |

| 8                                                  | VCC_LDO     | VCO レギュレータへの電源ピン。内部レギュレータを使用する場合は、ここから電源を VCC_LDO に接続します。このピンの電圧は 4.75V~5.25V の範囲です。外部レギュレータを使用する場合は、このピンを VCC_VCO に短絡します。                  |

| 10                                                 | RF32N       | 4 逓倍器出力。このピンは次段に AC または DC カップリングします。未使用時はこのピンをパワーオフできます。使用しない場合、このピンはオープン状態にできます。                                                          |

| 11                                                 | RF32P       | 相補4逓倍器出力。このピンは次段にACまたはDCカップリングします。未使用時はこのピンをパワーオフできます。使用しない場合、このピンはオープン状態にできます。                                                             |

| 14                                                 | VCC_X4      | 4 逓倍器 $RF$ 出力の電源。このピンの電圧は $AV_{DD}$ と同じ値でなければなりません。                                                                                         |

| 15                                                 | VDD_X4      | 4 逓倍器回路のデジタル電源。このピンの電圧は $AV_{DD}$ と同じ値でなければなりません。                                                                                           |

| 16                                                 | VCC_X1      | メイン $ m RF$ 出力の電源。このピンの電圧は $ m AV_{DD}$ と同じ値でなければなりません。                                                                                     |

| 17                                                 | VDD_X1      | メイン $RF$ 出力のデジタル電源。このピンの電圧は $AV_{DD}$ と同じ値でなければなりません。                                                                                       |

| 18                                                 | RF8P        | メイン RF 出力。次段に AC カップリングします。出力レベルはプログラマブルです。 VCO の基本出力または分周出力を取り出せます。                                                                        |

| 19                                                 | RF8N        | 相補メイン RF 出力。このピンは次段に AC カップリングします。出力レベルはプログラマブルです。<br>VCO の基本出力または分周出力を取り出せます。                                                              |

| 21                                                 | VCC_X2      | $2$ 逓倍 $RF$ 出力の電源。このピンの電圧は $AV_{DD}$ と同じ値でなければなりません。                                                                                        |

| 22                                                 | RFAUX8P     | 補助 RF 出力。次段に AC カップリングします。未使用時はこのピンをパワーオフできます。                                                                                              |

Rev. 0 - 9/48 -

|      | ÷3 P       | 5K DD                                                                                                                                                                               |

|------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ピン番号 | 記号         | 説明                                                                                                                                                                                  |

| 23   | RFAUX8N    | 相補補助 RF 出力。このピンは次段に AC カップリングします。未使用時はこのピンをパワーオフできます。                                                                                                                               |

| 26   | RF16P      | 2 逓倍 VCO 出力。このピンは次段に AC または DC カップリングします。未使用時はこのピンをパワーオフできます。使用しない場合、このピンはオープン状態にできます。                                                                                              |

| 27   | RF16N      | 相補2逓倍VCO出力。このピンは次段にACまたはDCカップリングします。未使用時はこのピンをパワーオフできます。使用しない場合、このピンはオープン状態にできます。                                                                                                   |

| 29   | VCC_MUX    | $VCO$ マルチプレクサの電源。このピンの電圧は $AV_{DD}$ と同じ値でなければなりません。                                                                                                                                 |

| 30   | VCC_3V     | アナログ電源。このピンの電圧は AV <sub>DD</sub> と同じ値でなければなりません。                                                                                                                                    |

| 31   | VDD_NDIV   | $N$ 分周器電源。このピンの電圧は $AV_{DD}$ と同じ値でなければなりません。                                                                                                                                        |

| 32   | VDD_LS     | レベル・シフタ電源。このピンの電圧は AV <sub>DD</sub> と同じ値でなければなりません。                                                                                                                                 |

| 33   | CS         | チップ・セレクト、CMOS入力。CSがハイになると、シフト・レジスタに格納されているデータが、アドレス・ビットで選択されているレジスタにロードされます。                                                                                                        |

| 34   | SDIO       | シリアル・データ入出力。この入力は高インピーダンスの CMOS 入力です。                                                                                                                                               |

| 35   | SCLK       | シリアル・クロック入力。データは、クロックの立上がり(または立下がり)エッジで24ビット・シフト・レジスタにクロック入力されます。この入力は高インピーダンスのCMOS入力です。                                                                                            |

| 38   | VCC_LDO_3V | 1.8V デジタル・ロジックのレギュレータ入力。このピンの電圧は AVDD と同じ値でなければなりません。                                                                                                                               |

| 39   | CE         | チップ・イネーブル。3.3V または AVDD に接続します。                                                                                                                                                     |

| 40   | TEST       | 工場テスト・ピン。このピンはグラウンドに接続します。                                                                                                                                                          |

| 41   | MUXOUT     | マルチプレクサ出力。マルチプレクサ出力により、デジタル・ロック検出、アナログ・ロック検出、スケーリングされた RF、またはスケーリングされた基準周波数に外部からアクセスできます。このピンは、4線式 SPI モードでレジスタ設定を出力するように設定できます。                                                    |

| 43   | REFP       | リファレンス入力。シングルエンド・リファレンスでデバイスを駆動する場合は、信号を REFP ピンに AC カップリングします。                                                                                                                     |

| 44   | REFN       | 相補リファレンス入力。使用しない場合、このピンは GND に AC カップリングします。差動で駆動する場合、REFP と REFN を AC カップリングする必要があります。シングルエンドで駆動する場合、リファレンス信号を REFP に接続し、REFN を GND に AC カップリングする必要があります。差動構成では、差動インピーダンスは 100Ωです。 |

| 45   | VCC_REF    | リファレンス・バッファへの電源。このピンの電圧は $AV_{DD}$ と同じ値でなければなりません。                                                                                                                                  |

| 46   | VDD_PFD    | $\operatorname{PFD}$ $\sim$ $\mathcal{O}$ 電源。このピンの電圧は $\operatorname{AV}_{\operatorname{DD}}$ と同じ値でなければなりません。                                                                       |

| 47   | VDD_VP     | チャージ・ポンプ電源。このピンの電圧は $AV_{DD}$ と同じ値でなければなりません。スプリアス信号を最小限に抑えるために、GND に $1μ$ F のデカップリング・コンデンサを接続する必要があります。                                                                            |

|      | EP         | 露出パッド。ランド・グリッドアレイ(LGA)には露出パッドがあり、機械的な理由により PCB の金属面にハンダ付けすると共に、GND にハンダ付けする必要があります。                                                                                                 |

Rev. 0 - 10/48 -

# 代表的な性能特性

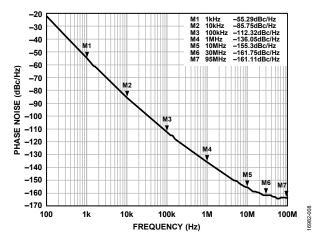

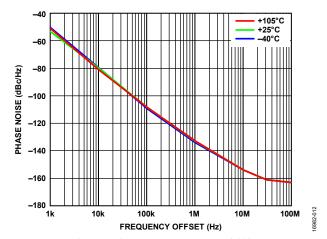

図 7. オープンループ VCO 位相ノイズ、4.0GHz、VCC\_VCO = 5V

図 8. オープンループ VCO 位相ノイズ、5.7GHz、VCC\_VCO = 5V

図 9. オープンループ VCO 位相ノイズ、8.0GHz、VCC VCO = 5V

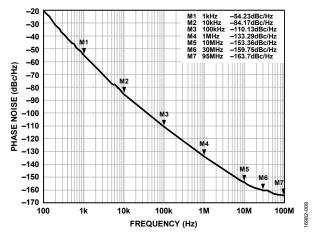

図 10. RF16x 出力でのオープンループ VCO 位相ノイズ、11.4GHz、 VCC\_VCO = 5V

図 11. RF16x 出力でのオープンループ VCO 位相ノイズ、16.0GHz、 VCC\_VCO = 5V

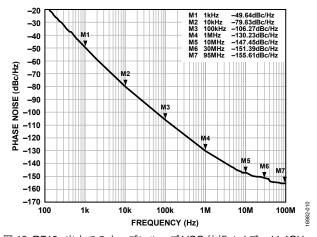

図 12. オープンループ VCO 位相ノイズの温度特性、8.0GHz、 VCC\_VCO = 5V

Rev. 0 — 11/48 —

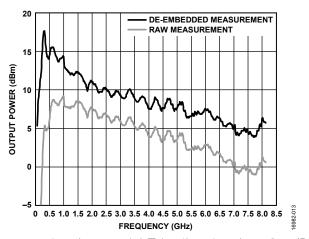

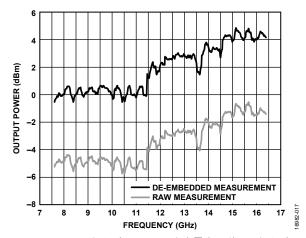

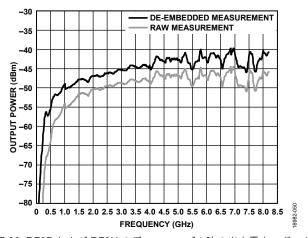

図 13. RF8P および RF8N の出力電力、ボードおよびケーブルの損失を除外、バランによる結合(7.4nH インダクタ、10pF AC カップリング・コンデンサによる低周波数での電力制限)

図 14. PFD スプリアス・スイープ、PFD 周波数 = 61.44MHz、 ループ・フィルタ帯域幅 = 100kHz

図 15. RF8P および RF8N の出力高調波、ボードおよび ケーブルの損失を除外、バランによる結合

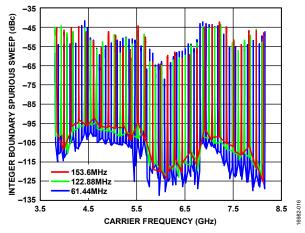

図 16. 整数境界スプリアス・スイープとコーナー周波数の関係、 PFD 周波数 = 61.44MHz、122.88MHz、および 153.6MHz、 ループ・フィルタ帯域幅 = 100kHz

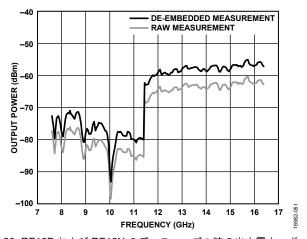

図 17. RF16P および RF16N の出力電力、ボードおよび ケーブルの損失を除外、バランによる結合

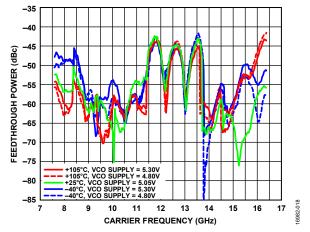

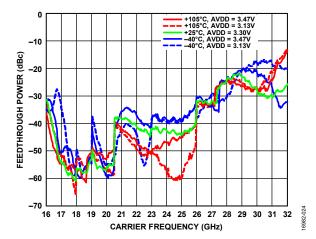

図 18. RF16P および RF16N の VCO フィードスルー、ボードおよび ケーブルの損失を除外、バランによる結合

Rev. 0 – 12/48 –

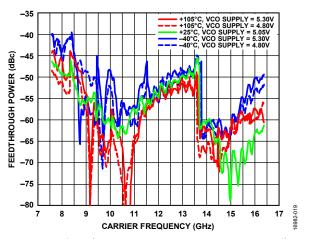

図 19. RF16P および RF16N の VCO × 3 フィードスルー、ボード およびケーブルの損失を除外、バランによる結合

図 20. RF16P および RF16N の出力高調波、ボードおよびケーブルの 損失を除外、バランによる結合

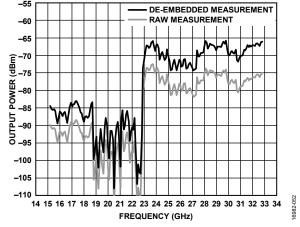

図 21. RF32P および RF32N の出力電力、ボードおよびケーブルの 損失を除外、バランによる結合

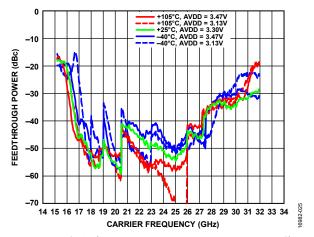

図 22. RF32P および RF32N の VCO フィードスルー、ボードおよび ケーブルの損失を除外、バランによる結合

図 23. RF32P および RF32N の VCO ×2 フィードスルー、ボード およびケーブルの損失を除外、バランによる結合

図 24. RF32P および RF32N の VCO  $\times$  3 フィードスルー、ボード およびケーブルの損失を除外、バランによる結合

Rev. 0 — 13/48 —

図 25. RF32P および RF32N の VCO  $\times$  5 フィードスルー、ボード およびケーブルの損失を除外、バランによる結合

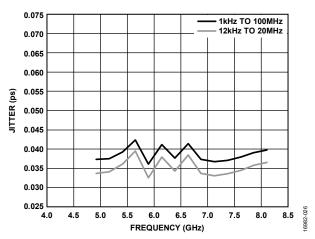

図 26. RMS ジッタ、インテジャーN、 PFD 周波数(f<sub>PFD</sub>)= 245.76MHz、 ループ・フィルタ帯域幅 = 220kHz、VCC\_VCO = 5V

図 27. RMS ジッタ、 フラクショナル N、 $f_{PFD}$  = 153.6MHz、 VCC\_VCO = 5V

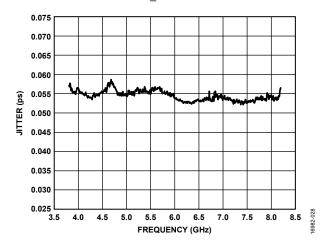

図 28. 1kHz~100MHz で積分した RMS ジッタ、フラクショナル N、  $f_{PFD}$  = 153.6MHz、VCC\_VCO = 3.3V

Rev. 0 — 14/48 —

図 29. RF8P および RF8N のディスエーブル時の出力電力、ボード およびケーブルの損失を除外、バランによる結合

図 30. RF16P および RF16N のディスエーブル時の出力電力、ボード およびケーブルの損失を除外、バランによる結合

図 31. RF32P および RF32N のディスエーブル時の出力電力、ボード およびケーブルの損失を除外、バランによる結合

Rev. 0 — 15/48 —

# 動作原理

# RF シンセサイザ、実際例

次式を使って ADF4371 シンセサイザを設定します。

$$f_{RFOUT} = INT + \frac{FRAC1 + \frac{FRAC2}{MOD2}}{MOD1} \times \frac{f_{PFD}}{RF\ Divider}$$

(1)

ここで、

freoutは RF 出力周波数。

INTはインテジャー分周係数。

FRACI はフラクショナル。

FRAC2 は補助フラクショナル。

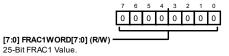

MOD1 は固定の 25 ビット・モジュラス。

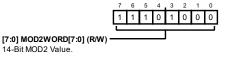

MOD2は補助モジュラス。

RF Divider は VCO 周波数を分周する出力分周比。

$$f_{PFD} = REF_{IN} \times \left( (1+D) / (R \times (1+T)) \right)$$

(2)

ここで、

REFINは基準周波数入力。

Dは REF<sub>IN</sub> ダブラ・ビット。

Rはリファレンス分周係数。

Tはリファレンス 2 分周ビット (0 または 1)。

例えば、2112.8MHzの  $f_{RFOUT}$ が必要とされるユニバーサル・モバイル・テレコミュニケーション・システム(UMTS)では、122.88MHz の  $REF_{IN}$  を使用できます。ADF4371 の VCO は 4GHz~8GHz の周波数範囲で動作します。したがって、RF を 2 分周する必要があります(VCO 周波数 = 4225.6MHz、 $RF_{OUT}$  = VCO周波数/RF分周比 = 4225.6MHz/2 = 2112.8MHz)。

フィードバック・パスも重要です。この例では、VCO 出力は出力分周器の前でフィードバックされています(図32を参照)。

この例では、122.88MHz の基準信号を 2 分周して 61.44MHz の fprD を生成します。必要なチャンネル間隔は 200kHz です。

図 32. 出力分周器の前に配置されたクローズドループ

この実際例で使用されている値は次のとおりです。

$$N = f_{VCO_OUT}/f_{PFD} = 4225.6MHz/61.44MHz = 68.7760416666666667$$

(3)

ここで、

Nは希望するフィードバック・カウンタ N の値。 $frco_{out}$ は出力 分周器を使用しない VCO 電圧制御発振器の出力周波数。fred は位相周波数検出器の周波数。

$$INT = INT (VCO 周波数f_{PFD}) = 68$$

(4)

ここで、

FRAC は N のフラクショナル部。

$$MOD1 = 33,554,432$$

(6)

$$FRAC1 = INT \quad (MOD1 \times FRAC = 26,039,637 \tag{7}$$

$$MOD2 = f_{PFD}/GCD \quad (f_{PFD}, f_{CHSP}) = 61.44MHz/GCD$$

(61.44MHz, 200kHz) = 1536 (9)

ここで、

GCD は最大公約数演算子。

$$FRAC2 =$$

$\Re$  $\times 1536 = 512$  (10)

式2から、

$$f_{PFD} = (122.88 \text{MHz} \times (1+0) /2) = 61.44 \text{MHz}$$

(11)

$$2112.8MHz = 61.44MHz \times (INT + FRAC1 +$$

$$FRAC2/MOD2) /2^{25}) ) /2$$

(12)

ここで、

$INT = 68_{\circ}$

$FRAC1 = 26,039,637_{\circ}$

$MOD2 = 1536_{\circ}$

$FRAC2 = 512_{\circ}$

RF 分周比= 2。

# リファレンス入力感度

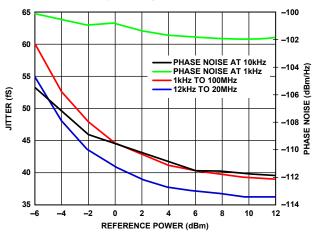

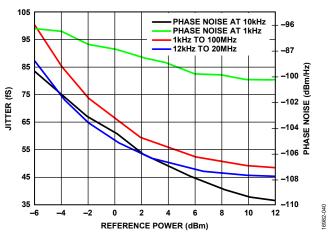

入力リファレンス信号のスルー・レートは性能に大きく影響します。このデバイスは、0.4Vp-pまでの非常に小さな振幅の信号と21V/μsのスルー・レートで機能します。ただし、最適性能は、1000V/μsもの高スルー・レートで実現されます。正弦波でこのスルー・レートを実現するには大きな振幅が必要であり、低周波数では不可能なことがあります。ADF4371のジッタと位相ノイズ性能を、PFD周波数が250MHzの場合について図33に、100MHzの場合について図34に示します。最高の性能を実現するには、リファレンス入力信号としてスルー・レートの高い高品質の方形波信号を推奨します。

図 33. ジッタと位相ノイズ、f<sub>PFD</sub> = 250MHz

Rev. 0

図 34. ジッタと位相ノイズ、f<sub>PFD</sub> = 100 MHz

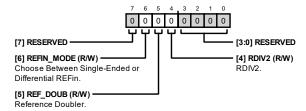

# リファレンス・ダブラとリファレンス分周器

内蔵リファレンス・ダブラにより、入力リファレンス信号を2逓倍できます。ダブラは、PFDの比較周波数を増やすのに役立ちます。システムのノイズ性能を改善するには、PFD周波数を上昇させます。PFD周波数を2倍にすると、ノイズ性能が3dB(代表値)改善されます。

リファレンス 2 分周機能によりリファレンス信号が 2 分周されるので、PFD 周波数のデューティ・サイクルは 50%になります。

# スプリアス最適化と高速ロック

ループ帯域幅を狭くすると、不要なスプリアス信号をフィルタ 処理できます。ただし、こうした帯域幅では通常はロック時間 が長くなります。ループ帯域幅が広いとロック時間は短くなりますが、ループ帯域幅内のスプリアス信号が増加する可能性が あります。

#### ジッタの最適化

ジッタを最小にしたいアプリケーションでは、PLL の帯域内ノイズの影響をできるだけ小さくするために、できるだけ高い PFD 周波数を使用します。PLL フィルタの帯域幅は、PLL の帯域内ノイズが VCO のオープンループ・ノイズと交差するように設定して、これらのノイズが全体的なノイズに及ぼす影響をできるだけ小さくできるようにします。

この作業には、ADIsimPLL設計ツールを使用します。

#### ループ・フィルタのさらなる最適化

PLL フィルタは、システム条件に応じて、リファレンス、PFD、VCO ノイズに最適な帯域幅となるように設計されます。この設計に加えて、シグマ・デルタ( $\Sigma\Delta$ )モジュレータ(SDM)をイネーブルしている場合は、SDM ノイズのフィルタ処理のために更に最適化が必要になることがあります。

# ΣΔ モジュレータのノイズ低減

フラクショナル・モードでは、SDM ノイズが明確になり始め、全体的な位相ノイズに寄与し始めます。CPOUT ピンとループ・フィルタの間に直列抵抗を接続すると、このノイズを無視できるレベルにまで低減できます。この抵抗はCPOUT ピンの近くに配置します。妥当な抵抗値であれば、設計されたループ・フィルタのループ帯域幅と位相余裕に影響を与えません。ほとんどの場合、 $91\Omega$  で最良の結果が得られます。インテジャー・モードの(SDM をイネーブルしない)場合または狭帯域ループ・フィルタを使用する(SDM ノイズが減衰される)場合、この抵抗は不要です。

### スプリアスのメカニズム

このセクションでは、フラクショナル N シンセサイザで発生する 2つの異なるスプリアスのメカニズムと、それらを ADF4371 で最小化する方法について説明します。

## 整数境界スプリアス

フラクショナル・スプリアス発生のメカニズムの 1 つは、RF VCO 周波数と基準周波数の間の相互作用です。これらの周波数が整数に関連しない場合(これがフラクショナル N シンセサイザの目的です)、スプリアス・サイドバンドはビート・ノートすなわち、リファレンスの整数倍と VCO 周波数の間の周波数差に対応するオフセット周波数で VCO 出力スペクトルに現れます。これらのスプリアスはループ・フィルタによって減衰され、差周波数がループ帯域幅の内側に入る、リファレンスの整数倍に近いチャンネルでより顕著になります。

### リファレンス・スプリアス

リファレンス・スプリアスは通常、フラクショナル N シンセサイザでは問題になりません。リファレンス・オフセットがループ帯域幅から大きく外れるためです。ただし、ループをバイパスするリファレンス・フィードスルー・メカニズムは問題を引き起こす可能性があります。低レベルの内蔵リファレンス・スイッチング・ノイズがプリスケーラを介して VCO にフィードスルーすると、リファレンス・スプリアス・レベルが最大で-100dBc になる可能性があります。

#### ロック時間

PLL ロック時間はいくつかの設定値に分割されます。周波数変更に要する合計ロック時間は、シンセサイザ・ロック、VCO帯域の選択、自動レベル・キャリブレーション(ALC)、およびPLLセトリング時間の4つの別々の時間の合計です。

# シンセサイザ・ロック

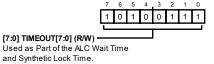

シンセサイザ・ロックのタイムアウトにより、帯域選択回路に対してVCOキャリブレーションDACがVCO調整電圧( $V_{TUNE}$ )の値を安定させることができます。 $SYNTH\_LOCK\_TIMEOUT$ と TIMEOUTは、VCO キャリブレーションのプロセスが次のフェーズ(VCO 帯域の選択)に進むまでに DAC が最終電圧に安定するための許容時間を選択するものです。

PFD 周波数はこのロジック用のクロックであり、この時間は次式を使用して設定します。

$$\frac{SYNTH\_LOCK\_TIMEEOUT \times 1024 + TIMEOUT}{f_{PFD}}$$

(13)

ここで、

SYNTH\_LOCK\_TIMEOUT は REG0033 で設定。 TIMEOUT は REG0031 と REG0032 で設定。

計算される時間は20μs以上でなければなりません。

SYNTH\_LOCK\_TIMEOUT ビットの最小値は 2、最大値は 31 です。TIMEOUT の最小値は 2、最大値は 1023 です。

Rev. 0 - 17/48 -

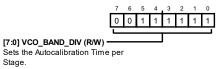

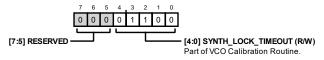

#### VCO 帯域の選択

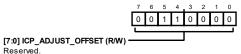

VCO 帯域選択クロックを生成するのに、次式のように VCO\_BAND\_DIV (REG0030 で設定) および PFD 周波数が使用 されます。

$$f_{BSC} = \frac{f_{PFD}}{VCO \quad BAND \quad DIV} \tag{14}$$

計算される時間は2.4MHz未満でなければなりません。

1つの VCO コアと帯域キャリブレーションのステップには 16 クロック・サイクルが必要で、全帯域の選択プロセスには 11 ステップかかるため、次式が得られます。

$$11 \times \frac{16 \times VCO\_BAND\_DIV}{f_{PFD}} \tag{15}$$

VCO BAND DIV の最小値は1、最大値は255です。

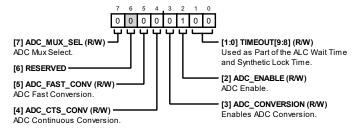

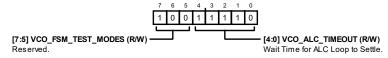

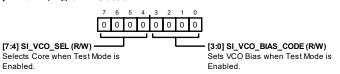

#### 自動レベル・キャリブレーション(ALC)

ALC 機能を使用して、ADF4371 の VCO コアに適切なバイアス 電流を選択します。各ステップで VCO バイアス電圧が安定する のには時間が必要で、その時間は以下の式で設定します。

$$\frac{VCO\_ALC\_TIMEOUT \times 1024 + TIMEOUT}{f_{PFD}} \tag{16}$$

ここで、

*VCO\_ALC\_TIMEOUT と Timeout* は、REG0034、REG0032、および REG0031 で設定します。

計算される時間は50μs以上でなければなりません。

ALC 全体では 63 ステップ必要です。

$$63 \times \frac{VCO\_ALC\_TIMEOUT \times 1024 + TIMEOUT}{f_{PFD}}$$

(17)

VCO ALC TIMEOUT の最小値は 2、最大値は 31 です。

#### PLL のセトリング時間

ループの安定に必要な時間は、ローパス・フィルタの帯域幅に 反比例します。セトリング時間は ADIsimPLL 設計ツールで正確 にモデル化されています。

#### ロック時間、実際例

f<sub>PFD</sub> = 61.44MHz と仮定します。

$$VCO\_BAND\_DIV = Ceiling (f_{PFD}/2,400,000) = 26$$

(18)

ここで、Ceiling () は最も近い整数に切り上げます。

$$SYNTH\_LOCK\_TIMEOUT \times 1024 + TIMEOUT > 1228.8 \tag{19}$$

$$VCO\_ALC\_TIMEOUT \times 1024 + TIMEOUT > 3072$$

(20)

これらの基準を満たす適切な値はいくつかあります。最小仕様 を考慮すると、以下の値が最適です。

- SYNTH LOCK TIMEOUT = 2 (最小值)

- VCO ALC TIMEOUT = 3

- TIMEOUT = 2

キャリブレーション・プロセスをバイパスすることによって、このデータシートに記載されている値よりもはるかに短いロック時間が可能です。詳細については、アナログ・デバイセズにお問い合わせください。

Rev. 0 — 18/48 —

# 回路の説明

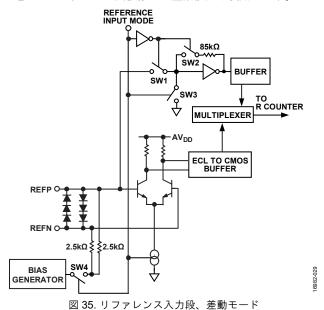

## リファレンス入力

リファレンス入力段を図 35 に示します。リファレンス入力は、シングルエンド信号と差動信号の両方に対応できます。信号を選択するには、リファレンス・モード・ビット(REG0022 のビット 6)を使用します。リファレンス入力に差動信号を使用するには、このビットをハイに設定します。この場合、SW1 とSW2が開き、SW3とSW4が閉じ、差動トランジスタのペアを駆動する電流源がオンになります。差動信号はバッファされ、CMOS コンバータへのエミッタ結合ロジック(ECL)に供給されます。

シングルエンド信号をリファレンスとして使用する場合は、リファレンス信号を REFP に接続し、REG0022 のビット 6 を 0 に設定します。この場合、SW1 と SW2 が閉じ、SW3 と SW4 が開き、差動トランジスタのペアを駆動する電流源がオフになります。

整数境界スプリアスと位相ノイズ性能を最適化するには、500MHz までのすべてのリファレンスでシングルエンド設定を使用します(差動信号を使用する場合においても)。500MHz を超えるリファレンス周波数には差動設定を使用します。

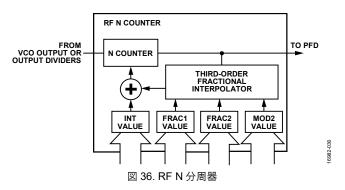

# RF N 分周器

RF N分周器により、PLLフィードバック・パスで分周比の設定が可能になります。この分周器が構成されるINT、FRAC1、FRAC2、MOD2の値で分周比を決定します。

#### INT、FRAC、MOD と R カウンタの関係

INT、FRAC1、FRAC2、MOD1、MOD2 の値を R カウンタと組み合わせると、非整数の  $f_{PFD}$  間隔を持つ出力周波数を生成できます。詳細については、RF シンセサイザの実際例のセクションを参照してください。

fvco out は次式で計算します。

$$f_{VCO\ OUT} = f_{PFD} \times N \tag{21}$$

fpfDは次式で計算します。

$$f_{PFD} = REF_{IN} \times \frac{1+D}{R \times (1+T)}$$

(22)

ここで、

REFINは基準周波数入力。

Dは $REF_{IN}$ ダブラ・ビット。

Rは 10 ビット・バイナリのプログラマブル・リファレンス・カウンタのプリセット分周比( $1\sim1023$ )。

Tは REF<sub>IN</sub> の 2 分周ビット (0 または 1)。

目的のフィードバック・カウンタ Nの値は次式で計算します。

$$N = INT + \frac{FRAC1 + \frac{FRAC2}{MOD2}}{MOD1}$$

(23)

ここで、

INT は 16 ビットのインテジャー値。インテジャー・モードの場合、4/5 プリスケーラでは  $INT = 20 \sim 32,767$ 、8/9 プリスケーラでは  $64 \sim 65,535$ 。フラクショナル・モードの場合、4/5 プリスケーラでは  $INT = 23 \sim 32,767$ 、8/9 プリスケーラでは  $75 \sim 65,535$ 。FRAC1 は 1 次モジュラスの分子( $0 \sim 33,554,431$ )。

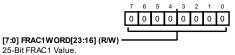

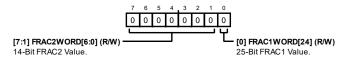

FRAC2 は 14 ビット補助モジュラスの分子(0~16,383)。

MOD2 は、プログラマブルな 14 ビット補助フラクショナル・モジュラス( $2\sim16,383$ )。

*MODI* は、 $2^{25}$  = 33,554,432 の固定値を持つ 25 ビットの 1 次モジュラス。

これらの計算により、残留周波数誤差のない非常に高い周波数 分解能が得られます。式 23 を適用するには、以下の手順を実行 します。

VCO<sub>OUT</sub>/f<sub>PFD</sub>の除算によりNを計算します。この数の整数 値がINTになります。

Rev. 0 - 19/48 -

- 2. Nの全部の値から INT を引きます。

- 3. 差に 225 を乗算します。この数の整数値が FRAC1 になり ます。

- 4. チャンネル間隔 (fcHSP) に基づく MOD2 を次式で計算します。

$$MOD2 = f_{PFD}/GCD \quad (f_{PFD}, f_{CHSP})$$

(24)

ここで、

f<sub>CHSP</sub>は目的のチャンネル間隔周波数。

*GCD (fpfD, fcHSP)* はPFD周波数とチャンネル間隔周波数の最大公約数。

5. FRAC2 を次式により計算します。

$$FRAC2 = ((N - INT) \times 2^{25} - FRAC1) \times MOD2$$

(25)

非整数の FRAC2 と MOD2 は、以下の場合にチャンネル間隔に対するゼロ周波数誤差の出力になります。

$$f_{PFD}/GCD$$

$(f_{PFD}, f_{CHSP}) = MOD2 < 16,383$  (26)

ゼロ周波数誤差が不要な場合、MOD1と MOD2 の分母は共 に作用して 39 ビットの分解能モジュラスを生成します。

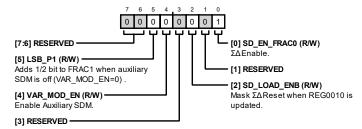

#### INTNモード

FRAC1 と FRAC2 が 0 の場合、シンセサイザはインテジャーNモードで動作します。REG002B の SD\_EN\_FRAC0 ビットを 1 に設定して SDM をディスエーブルすることを推奨します。これにより、帯域内位相ノイズが改善され、追加される  $\Sigma\Delta$  ノイズが減少します。

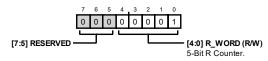

#### Rカウンタ

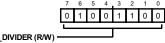

5ビットRカウンタにより、入力基準周波数(REFPとREFNへの入力)を分周して、PFDへのリファレンス・クロックを生成できます。 $1\sim1023$ の分周比が可能です。

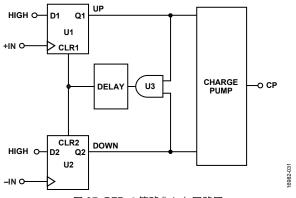

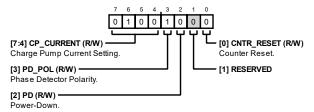

# PFD とチャージ・ポンプ

PFDはRカウンタとNカウンタから入力を受け取り、それらの位相と周波数の差に比例した出力を生成します。位相周波数検出器の簡略化した回路図を図37に示します。PFDには、バックラッシュ防止パルスの幅を設定する固定の遅延要素が含まれています。このパルスは、PFD伝達関数内でデッド・ゾーンの発生を確実に防止し、リファレンス・スプリアス・レベルを一定にします。VCOが正の調整勾配であるため、このデバイスでは位相検出器の極性を正に設定します。

図 37. PFD の簡略化した回路図

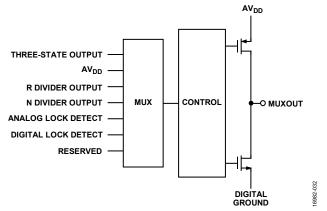

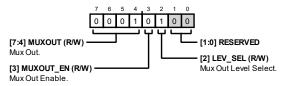

### MUXOUT とロック検出

ADF4371 の出力マルチプレクサにより、チップ上の様々な内部ポイントにアクセスできます。 MUXOUT セクションのブロック図を図 38 に示します。

図 38. MUXOUT の回路図

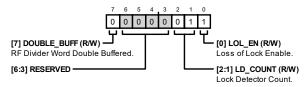

# ダブル・バッファ

ADF4371では、メイン・フラクショナル値(FRAC1)、補助モジュラス値(MOD2)、補助フラクショナル値(FRAC2)、リファレンス・ダブラ、リファレンス2分周(RDIV2)、Rカウンタ値、およびチャージ・ポンプ電流設定がダブル・バッファ付きとなっています。ADF4371がダブル・バッファ設定で新しい値を使用する前に、2つのイベントを実行する必要があります。最初に該当するレジスタへの書込みによって新しい値をデバイスにラッチさせ、次いでREG0010に新しい書込みを実行する必要があります。

例えば、モジュラス値が正しくロードされるようにするには、モジュラス値が更新されるたびに REG0010 に書き込む必要があります。

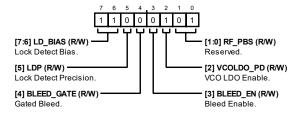

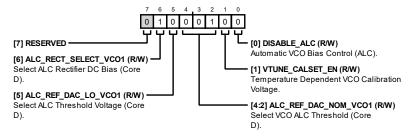

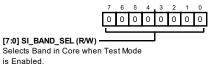

#### VCO

ADF4371 の VCO コアは、コア A、コア B、コア C、コア D の 4 つの個別の VCO コアで構成され、それぞれ 256 の重複する帯域を使用するため、VCO 感度( $K_V$ )を上げなくとも広い周波数範囲をカバーできます。その結果、位相ノイズおよびスプリアス性能の低下を防ぐことができます。

Rev. 0 — 20/48 —

REG0010 が更新されて自動キャリブレーションが有効になるたびに、VCO と帯域選択ロジックによって適切な VCO と帯域が自動的に選択されます。VTUNE はループ・フィルタの出力から切り離され、内部リファレンス電圧に接続されます。

R カウンタ出力は、帯域選択ロジック用のクロックとして使用されます。帯域選択後、通常の PLL 動作が再開されます。N 分周器が VCO 出力から駆動される場合、 $K_V$  の公称値は 50MHz/V になります。あるいは  $K_V$  値は D で除算されます。N 分周器が RF 出力分周器から駆動される場合、D は出力分周器の値です。

調整電圧 VTUNE が帯域内および帯域間で変化するのに応じて、 VCO の  $K_V$  は変動します。広い周波数範囲をカバーする(および出力分周比が変化する)広帯域アプリケーションでは、  $50MH_Z/V$  の値が平均値に最も近いため最も正確な  $K_V$  になります。  $K_V$  が基本 VCO 周波数によってどのように変化するかを、 周波数帯域の平均値と共に、図 39 と図 40 に示します。 狭帯域 設計を使用する場合は図 39 と図 40 のほうが役に立つかもしれません。

図 39. VCO 感度  $K_V$ の周波数特性、VCC\_VCO = 5V

図 40. VCO 感度  $K_V$ の周波数特性、VCC\_VCO = 3.3 V

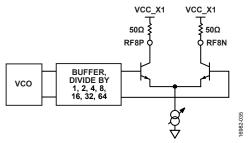

### 出力段

図 13 に示すように、ADF4371 の RF8P ピンと RF8N ピンは、 VCOのバッファ付き出力で駆動されるバイポーラ NPN 差動ペア のコレクタに接続します。ADF4371 は、VCC X1 ピンに接続さ れた 50Ω の内部抵抗を内蔵しています。消費電力と出力電力の 間の条件を最適化するために、差動ペアのテール電流は REG0025 のビット [1:0] で設定できます。4 つの電流レベルが 設定可能です。これらのレベルでは、約-4dBm、-1dBm、2dBm、 5dBm の出力電力レベルが得られます。 $50\Omega$  負荷への AC カップ リングによって、-4dBm、-1dBm、2dBmのレベルを実現できま す。5dBm レベルでは、VCC X1 に外付けのシャント・インダク タが必要です。インダクタでは 50Ω 抵抗よりも動作周波数が狭 くなります。正確な電力レベルについては、代表的な性能特性 のセクションを参照してください。電力レベルを更に高くする には外付けシャント・インダクタを追加します。この場合、内 部バイアスのみの場合よりも帯域幅が狭くなります。未使用の 相補出力は、使用する出力と同様の回路で終端します。

図 41. 出力段

2 逓倍の VCO 出力 (8GHz~16GHz) は RF16 ピンで得られ、これは次段の回路に直接接続できます。4 逓倍出力は RF32P ピンと RF32N ピンで得られ、これらも次段の回路に直接接続できます。RFAUX8P および RFAUX8N は、RF8P および RF8N 出力と同じ機能を提供しますが、必要に応じて、分周した RF8x 周波数または VCO 周波数を出力することもできます。

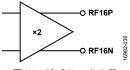

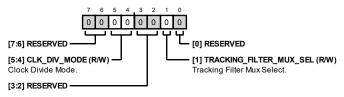

# ダブラ

VCO 周波数を 2 逓倍した周波数は RF16P ピンと RF16N ピンで得られます。未使用時はこの出力をパワーダウンさせることが可能で、その場合は RF16P ピンと RF16N ピンをオープンのままにすることができます。

図 42. ダブラの出力段

ADF4371には、VCOとその他の不要な周波数成分を抑制する自動トラッキング・フィルタが搭載されているため、2 逓倍出力が最大化され、VCOと 3×VCOの周波数が出力周波数に関係なく抑制されます。抑圧特性は代表値で50dB未満です。REG0023のビット1を使用して自動トラッキングを有効にすると、最適値が自動的に設定されます。

Rev. 0 — 21/48 —

4 逓倍器とダブラが共にイネーブルされている場合などでは、 係数を (REG0070 で) 手動で設定できます。最適な出力電力、 位相ノイズ、高調波除去の設定を表6に示します。

表 6.2 逓倍出力時のフィルタとバイアスの設定

| Frequency (GHz) | Filter | Bias |

|-----------------|--------|------|

| <8.4            | 7      | 3    |

| 8.4 to 9.4      | 6      | 3    |

| 9.4 to 10       | 5      | 3    |

| 10 to 11.5      | 4      | 3    |

| 11.5 to 12.2    | 3      | 3    |

| 12.2 to 13.7    | 2      | 3    |

| 13.7 to 14.5    | 1      | 3    |

| >14.5           | 0      | 3    |

# 4 逓倍器

図 43.4 逓倍器の出力段

VCO 周波数を 4 逓倍した周波数は RF32P ピンと RF32N ピンで得られます。未使用時はこの出力をパワーダウンさせることが可能で、その場合は RF32P ピンと RF32N ピンをオープンのままにすることができます。

ADF4371は、出力周波数に関係なく、VCO、2×VCO、3×VCO、5×VCO、およびその他の不要な周波数成分を抑制する自動トラッキング・フィルタを内蔵しています。抑圧特性は代表値で30dB未満です。自動トラッキングでは、4 逓倍出力に最適な係数は設定されません。出力電力、位相ノイズ、高調波除去を最適化するには、自動選択モード(REG0023 のビット 1)を無効にして、表7の設定を手動でREG0071にロードします。

表 7.4 逓倍出力時のフィルタとバイアスの設定

| Frequency (GHz) | Filter | Bias |

|-----------------|--------|------|

| <18             | 7      | 3    |

| 18 to 19        | 3      | 3    |

| 19 to 20.5      | 1      | 0    |

| 20.5 to 26      | 0      | 0    |

| >26             | 0      | 1    |

自動トラッキング・モード (REG0023 のビット 1) は、ダブラおよび 4 逓倍器の出力では共通です。これらを同時にイネーブルした場合は、最適な性能を得るために両方の出力のフィルタ係数とバイアス係数を手動でロードします。

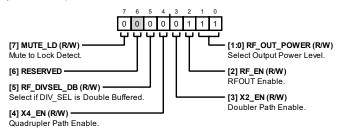

#### 出力段のミュート

ADF4371 のもう 1 つの特長は、ADF4371 がロックしたとデジタル・ロック検出回路で測定されるまで、RF8P および RF8N の出力段への供給電流をシャットダウンできることです。REG0025

のロック検出ミュート・ビット(MUTE\_LD)によって、この機能が有効になります。

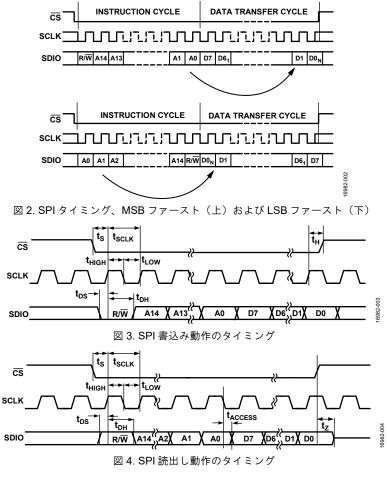

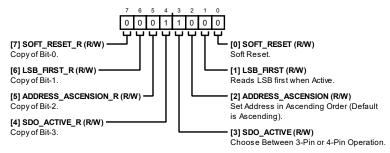

#### SPI

ADF4371 の SPI により、必要に応じて 3 線式または 4 線式の SPI ポートを介してデバイスを設定できます。このインターフェースは柔軟性を高め、カスタマイズを可能とします。シリアル・ポート・インターフェースは、4 本の制御線、すなわち、SCLK、SDIO、 $\overline{CS}$ 、 $\overline{MUXOUT}$  (3 線式 SPI では使用されない) で構成されます。SPI ポートのタイミング条件を表 2 に詳述します。

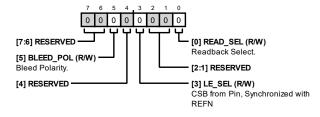

SPI プロトコルは、読み書きビットと 15 個のレジスタ・アドレス・ビット、それに続く 8 個のデータ・ビットで構成されています。アドレスとデータの両方のフィールドは、デフォルトでMSB を先頭にし LSB で終了するように構成されます。読出しのタイミングを図 3 に、書込みのタイミングを図 4 に示します。最上位 ビットの 順序 は、REG0000 レジスタの ビット 1 (LSB\_FIRST) の設定によって変更が可能で、関連するタイミング図を図 2 に示します。

書込みサイクル時の ADF4371 入力ロジック・レベルは、1.8V ロジック・レベルと互換性があります(表 1 のロジック・パラメータを参照)。読出しサイクルでは、LEV\_SEL ビットの設定により、SDIO ピンと MUXOUT ピンの両方を 1.8V(デフォルト)または 3.3V の出力レベルに設定できます。

#### SPIストリーム・モード

ADF4371 はストリーム・モードをサポートしています。このモードでは、レジスタ・アドレス(命令ワード)の書込みを行うことなく、データ・ビットがシリアルにレジスタにロードされるか、レジスタから読み出されます。このモードは、大量のデータを転送する必要があるとき、または一部のレジスタを繰り返し更新する必要があるときに、タイム・クリティカルなアプリケーションで役立ちます。

スレーブ・デバイスがこのアドレスへのデータの読書きを開始すると、CSがアサートされ、シングル・バイトの書込みが有効(REG0001 のビット 7) にならない限り継続します。スレーブ・デバイスは、アドレス拡張ビット(REG0000 のビット 2)の設定に応じて、アドレスを自動的にインクリメントまたはデクリメントします。

3バイト・ストリーミングの図を図5に示します。命令ヘッダはロジック0で始まって書込みシーケンスであることを示し、レジスタをアドレス指定します。次に、 $\overline{CS}$ がアサートされることなく、レジスタ(N,N-1,N-2)のデータが連続してロードされます。

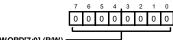

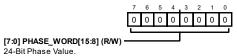

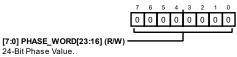

レジスタは 8 ビットで構成され、レジスタが 8 ビット以上を必要とする場合は、シーケンシャル・レジスタ・アドレスが使用されます。この構成により、ストリーム・モードの使用が可能になり、ロードが簡単になります。例えば、FRAC1WORD はREG0016、REG0015、および REG0014 (MSB から LSB) に格納されます。これらのレジスタは、図 5 に示すように、REG0016を使用し、その後 24 ビットのデータ全体を送信することによってロードできます。

Rev. 0 — 22/48 —

# デバイス設定

ADF4371を設定するための推奨手順は以下のとおりです。

- 1. SPIインターフェースを設定。

- 2. 初期化シーケンスを実行。

- 3. 周波数更新シーケンスを実行。

# ステップ1: SPI インターフェースの設定

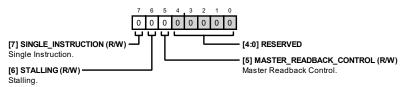

最初に SPI を初期化します。表 8 の値を REG0000 と REG0001 に 書き込みます。

#### 表 8. SPI インターフェースの設定

| アドレス | 設定   | メモ                  |

|------|------|---------------------|

| 0x00 | 0x18 | 4線式 SPI             |

| 0x01 | 0x00 | ストーリング、マスタ・リードバック制御 |

# ステップ2:初期化シーケンス

アドレス 0x7C からアドレス 0x10 への逆の順序で各レジスタに書き込みます。目的の周波数を生成するための適切な値を選択します。周波数更新シーケンスの後に、目的の出力周波数が生成されます。

# ステップ3:周波数更新シーケンス

周波数を更新するには、MOD2、FRAC1、FRAC2、および INT を更新する必要があります。したがって、更新シーケンスは以下のようになります。

- 1. REG001A (新規 MOD2WORD [13:8])

- 2. REG0019 (新規 MOD2WORD [7:0])

- 3. REG0018 (新規 FRAC2WORD [13:7])

- 4. REG0017 (新規 FRAC2WORD [6:0])

- 5. REG0016 (新規 FRAC1WORD [23:16] )

- 6. REG0015 (新規 FRAC1WORD [15:8])

- 7. REG0014 (新規 FRAC1WORD [7:0])

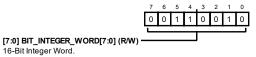

- 8. REG0011 (新規 BIT INTEGER WORD [15:8])

- 9. REG0010(新規 BIT INTEGER WORD [7:0])

周波数変更は REG0010 への書込みで実行されます。

変更しないレジスタは更新する必要はありません。例えば、インテジャーN PLL の設定(フラクション部分は未使用)の場合、手順 1 から手順 7 を省略します。この場合、必要な更新は REG0011 と REG0010 だけです。

Rev. 0 — 23/48 —

# アプリケーション情報

### 電源

ADF4371 は 4 つのマルチバンド VCO を内蔵しており、全体で 1 オクターブの周波数範囲をカバーします。 VCO 位相ノイズ性能を最適化するには、ADM7150 または LT3045 などの低ノイズ・レギュレータを VCC\_VCO ピンに接続することを推奨します。 同じレギュレータを VCC\_VCO ピンと VCC\_LDO ピンに接続します。 5V VCO 電源に  $1\mu$ F のデカップリング・コンデンサを接続することを推奨します。

他のすべての 3.3V電源ピンには、1つの ADM7150 または 1つの LT3045 レギュレータを使用します。 VDD\_VP ピンにも  $1\mu$ F を推 奨します。 他の電源ピンへの追加のデカップリングは不要です。

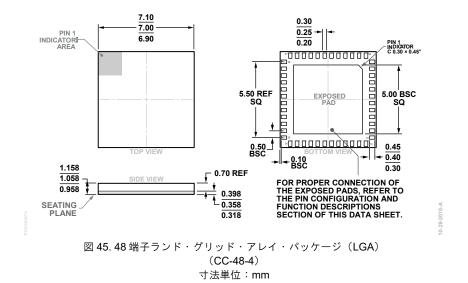

# LGA パッケージの PCB 設計ガイドライン

チップ・スケール・パッケージの底面には、中央に露出サーマル・パッドがあります。PCB上のサーマル・パッドは、少なくとも露出パッドと同じ大きさである必要があります。PCB上で、サーマル・パッドとパッド・パターンの内側の端との間に最低0.25mmの隙間が必要です。この隙間によって短絡を回避します。

パッケージの熱性能を向上させるには、PCB サーマル・パッドに サーマル・ピアを使用します。ピアを使用する場合は、それら を 1.2mm ピッチのグリッドでサーマル・パッドに組み込みます。ピア直径は 0.3mm $\sim 0.3$ 3mm とし、ピア・バレルを 1 オンスの銅でメッキしてピアに埋め込む必要があります。

ADF4371などのマイクロ波 PLLや VCO シンセサイザの場合は、ボードのスタックアップとレイアウトに注意します。FR4 材料を使用すると、3GHzを超える信号で振幅が減少するため、使用しないでください。代わりに、Rogers 4350、Rogers 4003、または Rogers 3003 の誘電体材料が適しています。

不連続性を最小限に抑え、信号の完全性を最大化するために、 RF 出力のトレースに注意します。ビアの配置と接地は重要です。

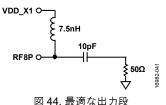

## 出力マッチング

必要に応じて、低周波出力を次段の回路に AC カップリングできます。ただし、より大きな出力電力が必要な場合は、プルアップ・インダクタを使って出力電力レベルを上昇させます。

差動出力が不要な場合は、未使用の出力を終端するか、バラン を使用して両方の出力を結合します。

1GHz より低い周波数では、RF8P ピンと RF8N ピンに 100nH のインダクタを使用することを推奨します。

RF8P ピンと RF8N ピンは差動回路を形成します。可能であれば 各出力に同じ(または類似の)部品を使用します。例えば、同じシャント・インダクタの値、バイパス・コンデンサ、および 終端を使用します。

RFAUX8P ピンと RFAUX8N ピンは実質的に RF8P と RF8N と同じであり、RF8P と RF8N について述べた方法で処理する必要があります。

RF16PピンとRF16Nピン、およびRF32PピンとRF32Nピンは、次段の回路に直接接続できます。これらのピンは内部で  $50\Omega$  に整合されており、追加のデカップリングは不要です。

Rev. 0 — 24/48 —

# レジスタの一覧

表 9. ADF4371 のレジスタの一覧