# 超低歪み電流帰還 差動ADCドライバ

## ADA4927-1/ADA4927-2

#### 特長

極めて低い高調波歪み

10 MHz で-105 dBc HD2

70 MHz で-91 dBc HD2

100 MHz で-87 dBc HD2

10 MHz で-103 dBc HD3

70 MHz で-98 dBc HD3

100 MHz で-89 dBc HD3

高いゲインで VF アンプより歪み性能が優れている

低い入力電圧ノイズ: 1.4 nV/√Hz

高速

-3 dB 帯域幅: 2.3 GHz

ゲイン平坦性: 150 MHz まで 0.1 dB

スルーレート: 25%から 75%まで 5,000 V/µs 高速なセトリング・タイム: 0.1%まで 10 ns

入力オフセット電圧: 0.3 mV (Typ)

外部調整可能なゲイン

帰還抵抗により安定性と帯域幅を制御

差動/差動動作またはシングルエンド/差動動作

調整可能な出力コモン・モード電圧

広い電源範囲: +5 V~±5 V

### アプリケーション

ADC ドライバ

シングルエンド/差動変換

IF およびベースバンドのゲイン・ブロック

差動バッファ

差動ライン・ドライバ

#### 概要

ADA4927 は、低ノイズ、超低歪み、高速、電流帰還の差動アンプであり、DC~100 MHzで 16 ビットまでの分解能を持つ高性能 ADC の駆動に最適です。必要とされる ADC 入力コモン・モード・レベルに出力コモン・モード・レベルを容易に一致させることができます。また、内部コモン・モード帰還ループは優れた出力バランスを維持し、偶数次の歪み積も抑圧します。

差動ゲイン構成は、4本の抵抗で構成される外部帰還回路を使って容易に実現できます。電流帰還アーキテクチャにより、ほぼ独立なクローズド・ループ・ゲインが実現できるため、広い帯域幅、低歪み、高いゲインでの低ノイズが実現でき、同等の電圧帰還アンプより消費電力を小さくすることができます。

ADA4927 はアナログ・デバイセズ独自のシリコン・ゲルマニウム相補バイポーラ・プロセスにより製造されているため、非常に低レベルの歪み、かつ 1.3 nV/√Hz.の小さな入力電圧ノイズを実現しています。

### 機能ブロック図

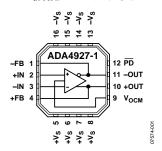

図 1.

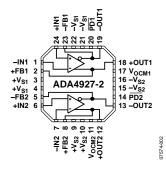

図 2.

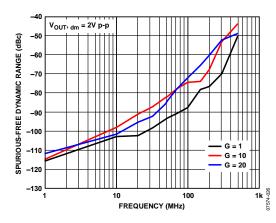

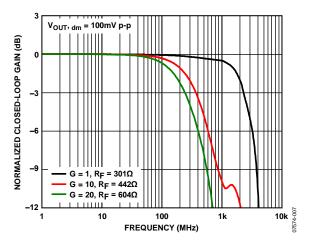

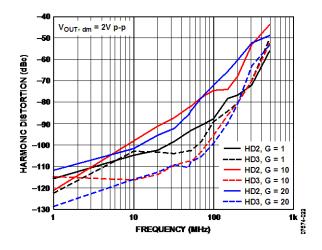

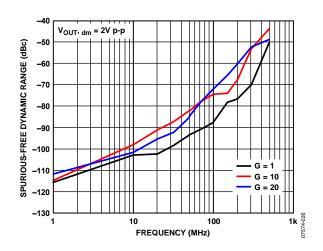

図 3.さまざまなゲインでのスプリアス・フリー・ダイナミック・レンジの周波数 特性

ADA4927 は低い DC オフセットと優れたダイナミック性能を持っため、さまざまなデータ・アクイジション・アプリケーションや信号処理アプリケーションに適しています。

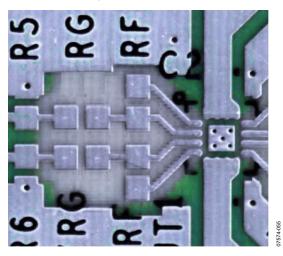

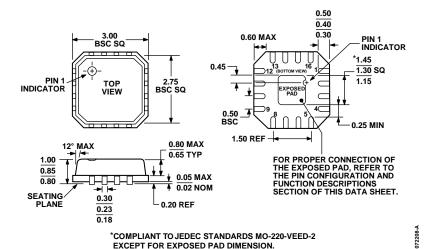

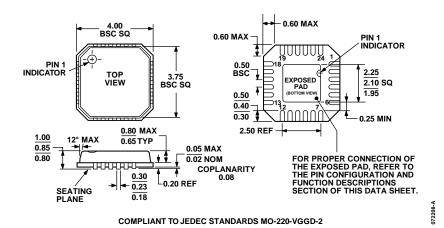

ADA4927-1 は Pb フリーの  $3 \, \text{mm} \times 3 \, \text{mm}$   $16 \, \text{ピン LFCSP}$  パッケージ を、ADA4927-2 は Pb フリーの  $4 \, \text{mm} \times 4 \, \text{mm}$   $24 \, \text{ピン LFCSP}$  パッケージを、それぞれ採用しています。 ピン配置は、PCB レイアウト と低歪み向けに最適化されています。 動作仕様は、 $-40 \, \text{°C} \sim +105 \, \text{°C}$  の温度範囲で規定されています。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。 ※日本語データシートは REVISION が古い場合があります。最新の内容については、英語版をご参照ください。 ©2008 Analog Devices, Inc. All rights reserved.

Rev. 0

本 社/〒105-6891 東京都港

東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル

電話 03(5402)8200

大阪営業所/〒532-0003 大阪府大阪市淀川区宮原 3-5-36 新大阪 MT ビル 2 号電話 06(6350)6868

# 目次

| 特長            | 1 |

|---------------|---|

| アプリケーション      | 1 |

| 概要            | 1 |

| 機能ブロック図       | 1 |

| 改訂履歴          | 2 |

| 仕様            | 3 |

| ±5 V動作        | 3 |

| +5 V動作        | 5 |

| 絶対最大定格        | 7 |

| 熱抵抗           | 7 |

| 最大消費電力        | 7 |

| ESD の注意       | 7 |

| ピン配置およびピン機能説明 | 8 |

| 代表的な性能特性      | 9 |

| テスト回路         |   |

| 動作原理          |   |

| 用語の定義                  | 16 |

|------------------------|----|

| アプリケーション情報             | 17 |

| アプリケーション回路の解析          | 17 |

| クローズド・ループ・ゲインの設定       | 17 |

| 出力ノイズ電圧の計算             | 17 |

| 帰還回路でのミスマッチの影響         | 18 |

| アプリケーション回路入力インピーダンスの計算 | 18 |

| 入力コモン・モード電圧範囲          | 20 |

| 入力と出力の容量 AC 結合         | 20 |

| 出力コモン・モード電圧の設定         | 20 |

| パワーダウン                 | 20 |

| レイアウト、グラウンド接続、バイパス     | 21 |

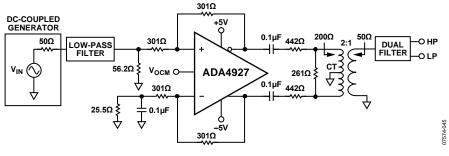

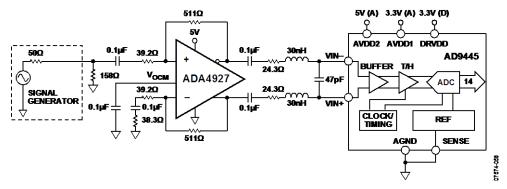

| 高性能 ADC の駆動            | 22 |

| 外形寸法                   | 23 |

| オーダー・ガイド               | 23 |

### 改訂履歴

10/08—Revision 0: Initial Version

## 仕様

### ±5 V 動作

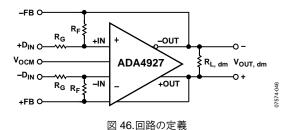

特に指定がない限り、 $T_A=25^{\circ}$ C、 $+V_S=5$  V、 $-V_S=-5$  V、 $V_{OCM}=0$  V、 $R_F=301$   $\Omega$ 、 $R_G=301$   $\Omega$ 、 $R_T=56.2$   $\Omega$  (使用時)。特に指定がない限り、すべての仕様はシングルエンド入力と差動出力を規定します。信号の定義については、図 46 を参照してください。

#### ±D<sub>IN</sub>—V<sub>OU, dm</sub> 間の性能

### 表 1.

| Parameter                       | Conditions                                                                                              | Min   | Тур  | Max   | Unit   |

|---------------------------------|---------------------------------------------------------------------------------------------------------|-------|------|-------|--------|

| DYNAMIC PERFORMANCE             |                                                                                                         |       |      |       |        |

| -3 dB Small Signal Bandwidth    | $V_{OUT, dm} = 0.1 \text{ V p-p}$                                                                       |       | 2300 |       | MHz    |

| -3 dB Large Signal Bandwidth    | $V_{OUT, dm} = 2.0 \text{ V p-p}$                                                                       |       | 1500 |       | MHz    |

| Bandwidth for 0.1 dB Flatness   | $V_{OUT, dm} = 0.1 \text{ V p-p, ADA4927-1}$                                                            |       | 150  |       | MHz    |

|                                 | $V_{OUT, dm} = 0.1 \text{ V p-p, ADA4927-2}$                                                            |       | 120  |       | MHz    |

| Slew Rate                       | $V_{OUT, dm} = 2 \text{ V step}, 25\% \text{ to } 75\%$                                                 |       | 5000 |       | V/µs   |

| Settling Time to 0.1%           | $V_{OUT, dm} = 2 V step$                                                                                |       | 10   |       | ns     |

| Overdrive Recovery Time         | $V_{IN} = 0 \text{ V to } 0.9 \text{ V step, } G = 10$                                                  |       | 10   |       | ns     |

| NOISE/HARMONIC PERFORMANCE      | See Figure 45 for distortion test circuit                                                               |       |      |       |        |

| Second Harmonic                 | $V_{OUT, dm} = 2 \text{ V p-p, } 10 \text{ MHz}$                                                        |       | -105 |       | dBc    |

|                                 | $V_{OUT, dm} = 2 \text{ V p-p}, 70 \text{ MHz}$                                                         |       | -91  |       | dBc    |

|                                 | $V_{OUT, dm} = 2 \text{ V p-p}, 100 \text{ MHz}$                                                        |       | -87  |       | dBc    |

| Third Harmonic                  | $V_{OUT, dm} = 2 \text{ V p-p}, 10 \text{ MHz}$                                                         |       | -103 |       | dBc    |

|                                 | $V_{OUT, dm} = 2 \text{ V p-p}, 70 \text{ MHz}$                                                         |       | -98  |       | dBc    |

|                                 | $V_{OUT, dm} = 2 \text{ V p-p}, 100 \text{ MHz}$                                                        |       | -89  |       | dBc    |

| IMD                             | $f_1 = 70 \text{ MHz}, f_2 = 70.1 \text{ MHz}, V_{OUT, dm} = 2 \text{ V p-p}$                           |       | -94  |       | dBc    |

|                                 | $f_1 = 140 \text{ MHz}, f_2 = 140.1 \text{ MHz}, V_{OUT, dm} = 2 \text{ V p-p}$                         |       | -85  |       | dBc    |

| Voltage Noise (RTI)             | f = 100  kHz, G = 28                                                                                    |       | 1.4  |       | nV/√Hz |

| Input Current Noise             | f = 100  kHz, G = 28                                                                                    |       | 14   |       | pA/√Hz |

| Crosstalk                       | f = 100 MHz, ADA4927-2                                                                                  |       |      |       | dB     |

| INPUT CHARACTERISTICS           |                                                                                                         |       |      |       |        |

| Offset Voltage                  | $V_{IP} = V_{IN} = V_{OCM} = 0 V$                                                                       | -1.3  | +0.3 | +1.3  | mV     |

| -                               | t <sub>MIN</sub> to t <sub>MAX</sub> variation                                                          |       | ±1.5 |       | μV/°C  |

| Input Bias Current              |                                                                                                         | -15   | +0.5 | +15   | μA     |

| •                               | t <sub>MIN</sub> to t <sub>MAX</sub> variation                                                          |       | ±0.1 |       | μΑ/°C  |

| Input Offset Current            |                                                                                                         | -10.5 | -0.6 | +10.5 | μA     |

| Input Resistance                | Differential                                                                                            |       | 14   |       | Ω      |

| •                               | Common mode                                                                                             |       | 120  |       | kΩ     |

| Input Capacitance               | Differential                                                                                            |       | 0.5  |       | pF     |

| Input Common-Mode Voltage Range |                                                                                                         | -3.5  |      | +3.5  | V      |

| CMRR                            | $\Delta V_{OUT, dm}/\Delta V_{IN, cm}$ , $\Delta V_{IN, cm} = \pm 1 \text{ V}$                          | -70   | -93  |       | dB     |

| Open-Loop Transresistance       | DC                                                                                                      | 120   | 185  |       | kΩ     |

| OUTPUT CHARACTERISTICS          |                                                                                                         |       |      |       |        |

| Output Voltage Swing            | Each single-ended output, $R_F = R_G = 10 \text{ k}\Omega$                                              | -3.8  |      | +3.8  | V      |

| Linear Output Current           |                                                                                                         |       | 65   |       | mA p-p |

| Output Balance Error            | $\Delta V_{OUT,~cm}/\Delta V_{OUT,~dm},~\Delta V_{OUT,~dm}=1~V,~10~MHz,$ see Figure 44 for test circuit |       | -65  |       | dB     |

Rev. 0 - 3/24 -

## V<sub>OCM</sub>—V<sub>OUT, cm</sub>間の性能

表 2.

| Parameter                              | Conditions                                                               |      | Тур  | Max  | Unit   |

|----------------------------------------|--------------------------------------------------------------------------|------|------|------|--------|

| V <sub>OCM</sub> DYNAMIC PERFORMANCE   |                                                                          |      |      |      |        |

| Small Signal -3 dB Bandwidth           | $V_{OUT, cm} = 100 \text{ mV p-p}$                                       |      | 1300 |      | MHz    |

| Slew Rate                              | $V_{IN} = -1.0 \text{ V to } +1.0 \text{ V}, 25\% \text{ to } 75\%$      |      | 1000 |      | V/µs   |

| Input Voltage Noise (RTI)              | f = 100  kHz                                                             |      | 15   |      | nV/√Hz |

| V <sub>OCM</sub> INPUT CHARACTERISTICS |                                                                          |      |      |      |        |

| Input Voltage Range                    |                                                                          |      | ±3.5 |      | V      |

| Input Resistance                       |                                                                          | 3.8  | 5.0  | 7.5  | kΩ     |

| Input Offset Voltage                   | $V_{OS, cm} = V_{OUT, cm}, V_{DIN+} = V_{DIN-} = +V_S/2$                 | -10  | -2   | +5.2 | mV     |

| V <sub>OCM</sub> CMRR                  | $\Delta V_{OUT, dm}/\Delta V_{OCM}$ , $\Delta V_{OCM} = \pm 1 \text{ V}$ | -70  | -97  |      | dB     |

| Gain                                   | $\Delta V_{OUT, cm}/\Delta V_{OCM}$ , $\Delta V_{OCM} = \pm 1 \text{ V}$ | 0.90 | 0.97 | 1.00 | V/V    |

### 全体性能

表 3.

| Parameter                         | Conditions                                           | Min  | Typ       | Max  | Unit  |

|-----------------------------------|------------------------------------------------------|------|-----------|------|-------|

| POWER SUPPLY                      |                                                      |      |           |      |       |

| Operating Range                   |                                                      | 4.5  |           | 11.0 | V     |

| Quiescent Current per Amplifier   |                                                      |      | 20.0      | 22.1 | mA    |

|                                   | t <sub>MIN</sub> to t <sub>MAX</sub> variation       |      | $\pm 9.0$ |      | μΑ/°C |

|                                   | Powered down                                         |      |           | 2.4  | mA    |

| Power Supply Rejection Ratio      | $\Delta V_{OUT, dm}/\Delta V_S$ , $\Delta V_S = 1 V$ | -70  | -89       |      | dB    |

| POWER-DOWN (PD)                   |                                                      |      |           |      |       |

| PD Input Voltage                  | Powered down                                         |      | <1.8      |      | V     |

|                                   | Enabled                                              |      | >3.2      |      | V     |

| Turn-Off Time                     | To 0.1%                                              |      | 15        |      | μs    |

| Turn-On Time                      | To 0.1%                                              |      | 400       |      | ns    |

| PD Pin Bias Current per Amplifier |                                                      |      |           |      |       |

| Enabled                           | $\overline{PD} = 5 \text{ V}$                        | -2   |           | +2   | μΑ    |

| Disabled                          | $\overline{PD} = 0 \text{ V}$                        | -110 |           | -90  | μΑ    |

| OPERATING TEMPERATURE RANGE       |                                                      | -40  |           | +105 | °C    |

Rev. 0 - 4/24 -

### +5 V 動作

特に指定がない限り、 $T_A=25^{\circ}$ C、 $+V_S=5$  V、 $-V_S=0$  V、 $V_{OCM}=2.5$  V、 $R_F=301$   $\Omega$ 、 $R_G=301$   $\Omega$ 、 $R_T=56.2$   $\Omega$  (使用時)、 $R_{L,dm}=1$   $k\Omega$ 。特に指定がない限り、すべての仕様はシングルエンド入力と差動出力を規定します。信号の定義については、図 46 を参照してください。

### ±D<sub>IN</sub>—V<sub>OU, dm</sub> 間の性能

表 4.

| arameter Conditions             |                                                                                                         | Min   | Typ   | Max   | Unit   |

|---------------------------------|---------------------------------------------------------------------------------------------------------|-------|-------|-------|--------|

| DYNAMIC PERFORMANCE             |                                                                                                         |       |       |       |        |

| -3 dB Small Signal Bandwidth    | $V_{OUT, dm} = 0.1 \text{ V p-p}$                                                                       |       | 2000  |       | MHz    |

| −3 dB Large Signal Bandwidth    | $V_{OUT, dm} = 2.0 \text{ V p-p}$                                                                       |       | 1300  |       | MHz    |

| Bandwidth for 0.1 dB Flatness   | $V_{OUT, dm} = 0.1 \text{ V p-p, ADA4927-1}$                                                            |       | 150   |       | MHz    |

|                                 | $V_{OUT, dm} = 0.1 \text{ V p-p, ADA4927-2}$                                                            |       | 110   |       | MHz    |

| Slew Rate                       | $V_{OUT, dm} = 2 \text{ V step}, 25\% \text{ to } 75\%$                                                 |       | 4200  |       | V/µs   |

| Settling Time to 0.1%           | $V_{OUT, dm} = 2 \text{ V step}$                                                                        |       | 10    |       | ns     |

| Overdrive Recovery Time         | $V_{IN} = 0 \text{ V to } 0.15 \text{ V step, } G = 10$                                                 |       | 10    |       | ns     |

| NOISE/HARMONIC PERFORMANCE      | See Figure 45 for distortion test circuit                                                               |       |       |       |        |

| Second Harmonic                 | $V_{OUT, dm} = 2 \text{ V p-p}, 10 \text{ MHz}$                                                         |       | -104  |       | dBc    |

|                                 | $V_{OUT, dm} = 2 \text{ V p-p}, 70 \text{ MHz}$                                                         |       | -91   |       | dBc    |

|                                 | $V_{OUT, dm} = 2 \text{ V p-p}, 100 \text{ MHz}$                                                        |       | -86   |       | dBc    |

| Third Harmonic                  | $V_{OUT, dm} = 2 \text{ V p-p}, 10 \text{ MHz}$                                                         |       | -95   |       | dBc    |

|                                 | $V_{OUT, dm} = 2 \text{ V p-p}, 70 \text{ MHz}$                                                         |       | -80   |       | dBc    |

|                                 | $V_{OUT, dm} = 2 \text{ V p-p}, 100 \text{ MHz}$                                                        |       | -76   |       | dBc    |

| IMD                             | $f_1 = 70 \text{ MHz}, f_2 = 70.1 \text{ MHz}, V_{OUT, dm} = 2 \text{ V p-p}$                           |       | -93   |       | dBc    |

|                                 | $f_1 = 140 \text{ MHz}, f_2 = 140.1 \text{ MHz}, V_{OUT, dm} = 2 \text{ V p-p}$                         |       | -84   |       | dBc    |

| Voltage Noise (RTI)             | f = 100  kHz, G = 28                                                                                    |       | 1.4   |       | nV/√Hz |

| Input Current Noise             | f = 100  kHz, G = 28                                                                                    |       | 19    |       | pA/√Hz |

| Crosstalk                       | f = 100 MHz, ADA4927-2                                                                                  |       | -75   |       | dB     |

| INPUT CHARACTERISTICS           |                                                                                                         |       |       |       |        |

| Offset Voltage                  | $V_{\rm IP} = V_{\rm IN} = V_{\rm OCM} = 0 \text{ V}$                                                   | -1.3  | +0.3  | +1.3  | mV     |

|                                 | t <sub>MIN</sub> to t <sub>MAX</sub> variation                                                          |       | ±1.5  |       | μV/°C  |

| Input Bias Current              |                                                                                                         | -30   | -12   | +4.0  | μA     |

|                                 | t <sub>MIN</sub> to t <sub>MAX</sub> variation                                                          |       | ±0.12 |       | μΑ/°C  |

| Input Offset Current            |                                                                                                         | -10.5 | -0.8  | +10.5 | μA     |

| Input Resistance                | Differential                                                                                            |       | 14    |       | Ω      |

|                                 | Common mode                                                                                             |       | 120   |       | kΩ     |

| Input Capacitance               | Differential                                                                                            |       | 0.5   |       | pF     |

| Input Common-Mode Voltage Range |                                                                                                         | 1.3   |       | 3.7   | V      |

| CMRR                            | $\Delta V_{OUT, dm}/\Delta V_{IN, cm}$ , $\Delta V_{IN, cm} = \pm 1 \text{ V}$                          | -70   | -96   |       | dB     |

| Open-Loop Transresistance       | DC                                                                                                      | 120   | 185   |       | kΩ     |

| OUTPUT CHARACTERISTICS          |                                                                                                         |       |       |       |        |

| Output Voltage Swing            | Each single-ended output                                                                                | +1.0  |       | +4.0  | V      |

| Linear Output Current           |                                                                                                         |       | 50    |       | mA p-p |

| Output Balance Error            | $\Delta V_{OUT,\;cm}/\Delta V_{OUT,\;dm},\Delta V_{OUT,\;dm}=1V,10$ MHz, see Figure 44 for test circuit |       | -65   |       | dB     |

## V<sub>OCM</sub>—V<sub>OUT, cm</sub>間の性能

表 5.

| Parameter                              | Conditions                                                        |      | Typ        | Max  | Unit   |

|----------------------------------------|-------------------------------------------------------------------|------|------------|------|--------|

| V <sub>OCM</sub> DYNAMIC PERFORMANCE   |                                                                   |      |            |      |        |

| Small signal -3 dB Bandwidth           | $V_{OUT, cm} = 100 \text{ mV p-p}$                                |      | 1300       |      | MHz    |

| Slew Rate                              | $V_{IN} = 1.5 \text{ V to } 3.5 \text{ V}, 25\% \text{ to } 75\%$ |      | 1000       |      | V/µs   |

| Input Voltage Noise (RTI)              | f = 100  kHz                                                      | 15   |            |      | nV/√Hz |

| V <sub>OCM</sub> INPUT CHARACTERISTICS |                                                                   |      |            |      |        |

| Input Voltage Range                    |                                                                   |      | 1.5 to 3.5 |      | V      |

| Input Resistance                       |                                                                   | 3.8  | 5.0        | 7.5  | kΩ     |

| Input Offset Voltage                   | $V_{OS, cm} = V_{OUT, cm}, V_{DIN+} = V_{DIN-} = +V_S/2$          | -5.0 | +2.0       | +10  | mV     |

| V <sub>OCM</sub> CMRR                  | $\Delta V_{OUT, dm}/\Delta V_{OCM}$ , $\Delta V_{OCM} = \pm 1 V$  | -70  | -100       |      | dB     |

| Gain                                   | $\Delta V_{OUT, cm}/\Delta V_{OCM}$ , $\Delta V_{OCM} = \pm 1 V$  | 0.90 | 0.97       | 1.00 | V/V    |

### 全体性能

表 6.

| Parameter                         | Conditions                                        | Min  | Typ  | Max  | Unit  |

|-----------------------------------|---------------------------------------------------|------|------|------|-------|

| POWER SUPPLY                      |                                                   |      |      |      |       |

| Operating Range                   |                                                   | 4.5  |      | 11.0 | V     |

| Quiescent Current per Amplifier   |                                                   |      | 20   | 21.6 | mA    |

|                                   | t <sub>MIN</sub> to t <sub>MAX</sub> variation    |      | ±7.0 |      | μA/°C |

|                                   | Powered down                                      |      |      | 0.6  | mA    |

| Power Supply Rejection Ratio      | $\Delta V_{OUT, dm}/\Delta V_S, \Delta V_S = 1 V$ | -70  | -89  |      | dB    |

| POWER-DOWN (PD)                   |                                                   |      |      |      |       |

| PD Input Voltage                  | Powered down                                      |      | <1.7 |      | V     |

|                                   | Enabled                                           |      | >3.0 |      | V     |

| Turn-Off Time                     |                                                   |      | 20   |      | μs    |

| Turn-On Time                      |                                                   |      | 500  |      | ns    |

| PD Pin Bias Current per Amplifier |                                                   |      |      |      |       |

| Enabled                           | $\overline{PD} = 5 \text{ V}$                     | -2   |      | +2   | μΑ    |

| Disabled                          | $\overline{PD} = 0 \text{ V}$                     | -105 |      | -95  | μΑ    |

| OPERATING TEMPERATURE RANGE       |                                                   | -40  |      | +105 | °C    |

Rev. 0 — 6/24 —

### 絶対最大定格

#### 表 7.

| Parameter                            | Rating          |

|--------------------------------------|-----------------|

| Supply Voltage                       | 11 V            |

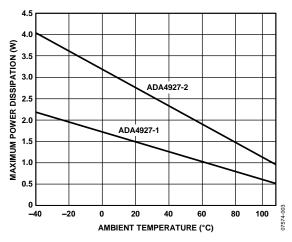

| Power Dissipation                    | See Figure 4    |

| Input Currents +IN, -IN, PD          | ±5 mA           |

| Storage Temperature Range            | −65°C to +125°C |

| Operating Temperature Range          | −40°C to +105°C |

| Lead Temperature (Soldering, 10 sec) | 300°C           |

| Junction Temperature                 | 150°C           |

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒 久的な損傷を与えることがあります。この規定はストレス定格 の規定のみを目的とするものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものでは ありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

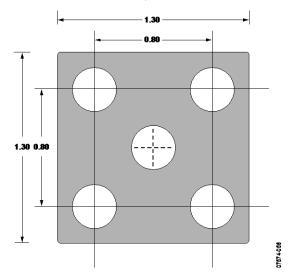

#### 熱抵抗

$\theta_{JA}$  は、デバイス(露出パッドを含む)を EIA/JESD 51-7 で規定される熱伝導性の高い 2s2p 回路ボードにハンダ付けした状態に対して規定します。

#### 表 8.

| Package Type                |    | Unit |

|-----------------------------|----|------|

| 16-Lead LFCSP (Exposed Pad) | 87 | °C/W |

| 24-Lead LFCSP (Exposed Pad) | 47 | °C/W |

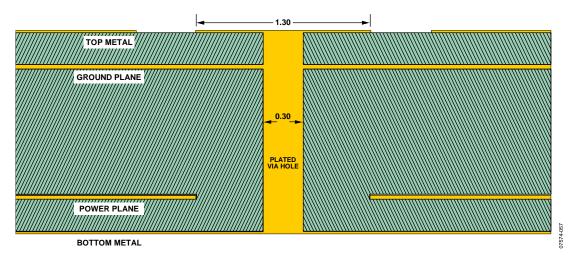

#### 最大消費電力

ADA4927 のパッケージ内での安全な最大消費電力は、チップのジャンクション温度(TJ)上昇により制限されます。約  $150^{\circ}$ C のガラス遷移温度で、プラスチックの属性が変わります。この温度規定値を一時的に超えた場合でも、パッケージからチップに加えられる応力が変化して、ADA4927 のパラメータ性能が永久的にシフトしてしまうことがあります。 $150^{\circ}$ C のジャンクション温度を長時間超えると、シリコン・デバイス内に変化が発生して、故障の原因になることがあります。

パッケージ内の消費電力( $P_D$ )は、静止消費電力と全出力での負荷駆動に起因するパッケージ内の消費電力との和になります。静止電力は、電源ピン( $V_S$ )間の電圧に静止電流( $I_S$ )を乗算して計算されます。負荷駆動に起因する消費電力は、アプリケーションに依存します。負荷駆動に起因する電力は、負荷電流とデバイスの対応する電圧降下の積として計算されます。これらの計算では RMS 電圧と RMS 電流を使用する必要があります。

強制空冷を使うと、放熱量が増えるため、実効的に  $\theta_{JA}$  が小さくなります。さらに、メタル・パターン、スルー・ホール、グラウンド・プレーン、電源プレーンとパッケージ・ピン/露出パッドが直接接触する場合、これらのメタルによっても  $\theta_{JA}$  が小さくなります。

図 4 に、パッケージの最大安全消費電力対周囲温度をシングルの 16 ピン LFCSP (87°C/W)とデュアルの 24 ピン LFCSP (47°C/W)について示します。両パッケージは、JEDEC 規格 4 層ボード上で厚いプレーンに接続されている PCB パッドに露出パッドをハンダ付けしています。

図 4.最大消費電力対周囲温度、4層ボード

#### ESD の注意

ESD (静電放電)の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

Rev. 0 - 7/24 -

## ピン配置およびピン機能説明

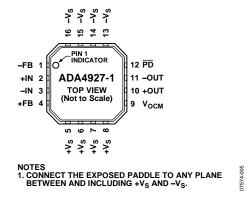

図 5.ADA4927-1 のピン配置

NOTES 1. CONNECT THE EXPOSED PADDLE TO ANY PLANE BETWEEN AND INCLUDING  $+V_S$  AND  $-V_S$ .

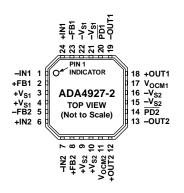

図 6.ADA4927-2 のピン配置

#### 表 9.ADA4927-1 のピン機能説明

| ピン番号      | 記号               | 説明                                                          |

|-----------|------------------|-------------------------------------------------------------|

| 1         | -FB              | 帰還部品接続の負側出力                                                 |

| 2         | +IN              | 加算ノードへの正側入力                                                 |

| 3         | -IN              | 加算ノードへの負側入力                                                 |

| 4         | +FB              | 帰還部品接続の正側出力                                                 |

| 5~8       | $+V_S$           | 正電源電圧                                                       |

| 9         | V <sub>OCM</sub> | コモン・モード電圧出力                                                 |

| 10        | +OUT             | 負荷接続の正側出力                                                   |

| 11        | -OUT             | 負荷接続の負側出力                                                   |

| 12        | PD               | パワーダウン・ピン                                                   |

| 13~16     | $-V_S$           | 負電源電圧                                                       |

| 17 (EPAD) | 露出パッド<br>(EPAD)  | 露出パッドは電圧+ $\mathbf{V}_{S}$ ~ $-\mathbf{V}_{S}$ のプレーンに接続します。 |

### 表 10.ADA4927-2 のピン機能説明

| 1       -INI       加算ノード1への負側入力         2       +FB1       帰還部品接続1の正側出力         3、4       +Vs1       正電源電圧1         5       -FB2       帰還部品接続2の負側出力         6       +IN2       加算ノード2への重側入力         7       -IN2       加算ノード2への負側入力         8       +FB2       帰還部品接続2の正側出力         9、10       +Vs2       正電源電圧2         11       VocM2       出力コモン・モード電圧2         12       +OUT2       負荷接続2の正側出力         13       -OUT2       負荷接続2の負側出力         14       PD2       パワーダウン・ピン2         15、16       -Vs2       負電源電圧2         17       VocMI       出力コモン・モード電圧1         18       +OUT1       負荷接続1の頁側出力         19       -OUT1       負荷接続1の負側出力         20       PDI       パワーダウン・ピン1         21、22       -Vs1       負電源電圧1         23       -FB1       帰還部品接続1の負側出力         24       +IN1       加算ノード1への正側入力         25 (EPAD)       露出パッドは電圧+Vs~-Vsのプレーンに接続します。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ピン番号      | 記 <del>号</del>    | 説明                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------|-------------------------------------|

| The state of   | 1         | -IN1              | 加算ノード1~の負側入力                        |

| 「FB2 帰還部品接続 2 の負側出力 加算ノード 2 への正側入力 加算ノード 2 への正側入力 加算ノード 2 への負側入力 帰還部品接続 2 の正側出力 正電源電圧 2 帰還部品接続 2 の正側出力 正電源電圧 2 出力コモン・モード電圧 2 負荷接続 2 の正側出力 13 ーOUT2 負荷接続 2 の頁側出力 パワーダウン・ピン 2 負電源電圧 2 出力コモン・モード電圧 1 負荷接続 1 の正側出力 15、16 ーVs2 負電源電圧 2 出力コモン・モード電圧 1 負荷接続 1 の正側出力 19 ーOUT1 負荷接続 1 の正側出力 20 アDI 負荷接続 1 の負側出力 パワーダウン・ピン 1 負電源電圧 1 22 ーFB1 帰還部品接続 1 の負側出力 加算ノード 1 への正側入力 24 出別コニアン・ 電側入力 露出パッドは電圧+Vs~ーVsのプレー 露出パッドは電圧+Vs~ーVsのプレー 25 (EPAD) 露出パッド 露出パッドは電圧+Vs~ーVsのプレー                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2         | +FB1              | 帰還部品接続1の正側出力                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3, 4      | $+V_{S1}$         | 正電源電圧1                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5         | -FB2              | 帰還部品接続2の負側出力                        |

| 8 +FB2 帰還部品接続2の正側出力 正電源電圧2 11 V <sub>OCM2</sub> 出力コモン・モード電圧2 12 +OUT2 負荷接続2の正側出力 13 -OUT2 負荷接続2の負側出力 14 PD2 パワーダウン・ピン2 15、16 -V <sub>S2</sub> 負電源電圧2 17 V <sub>OCMI</sub> 出力コモン・モード電圧1 18 +OUT1 負荷接続1の正側出力 19 -OUT1 負荷接続1の正側出力 20 PD1 パワーダウン・ピン1 21、22 -V <sub>S1</sub> 負電源電圧1 23 -FB1 帰還部品接続1の負側出力 24 +IN1 加算ノード1への正側入力 25 (EPAD) 露出パッド 露出パッドは電圧+V <sub>S</sub> ~-V <sub>S</sub> のプレー                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6         | +IN2              | 加算ノード2への正側入力                        |

| 9、10       +Vs2       正電源電圧 2         11       Vocm2       出力コモン・モード電圧 2         12       +OUT2       負荷接続 2 の正側出力         13       -OUT2       負荷接続 2 の負側出力         14       PD2       パワーダウン・ピン 2         15、16       -Vs2       負電源電圧 2         17       Vocm1       負荷接続 1 の正側出力         19       -OUT1       負荷接続 1 の負側出力         19       -OUT1       負荷接続 1 の負側出力         20       PD1       パワーダウン・ピン 1         21、22       -Vs1       負電源電圧 1         23       -FB1       帰還部品接続 1 の負側出力         24       +IN1       加算ノード 1 への正側入力         25 (EPAD)       露出パッド       露出パッドは電圧+Vs~ーVsのプレー                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7         | -IN2              | 加算ノード2への負側入力                        |

| Hamilton   Hamilto | 8         | +FB2              | 帰還部品接続2の正側出力                        |

| 12 +OUT2 負荷接続 2 の正側出力 13 -OUT2 負荷接続 2 の負側出力 14 PD2 パワーダウン・ピン 2 15、16 -V <sub>S2</sub> 負電源電圧 2 17 V <sub>OCMI</sub> 出力コモン・モード電圧 1 18 +OUT1 負荷接続 1 の正側出力 19 -OUT1 負荷接続 1 の負側出力 20 PDI パワーダウン・ピン 1 21、22 -V <sub>SI</sub> 負電源電圧 1 23 -FB1 帰還部品接続 1 の負側出力 24 +IN1 加算ノード 1 への正側入力 25 (EPAD) 露出パッド 露出パッドは電圧+V <sub>S</sub> ~-V <sub>S</sub> のプレー                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9、10      | $+V_{S2}$         | 正電源電圧 2                             |

| 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11        | V <sub>OCM2</sub> | 出力コモン・モード電圧 2                       |

| PD2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12        | +OUT2             | 負荷接続2の正側出力                          |

| 15、16 -V <sub>S2</sub> 負電源電圧 2 17 V <sub>OCMI</sub> 出力コモン・モード電圧 1 18 +OUT1 負荷接続 1 の正側出力 19 -OUT1 負荷接続 1 の負側出力 20 PDI パワーダウン・ピン 1 21、22 -V <sub>S1</sub> 負電源電圧 1 23 -FB1 帰還部品接続 1 の負側出力 24 +IN1 加算ノード 1 への正側入力 25 (EPAD) 露出パッド 露出パッドは電圧+V <sub>S</sub> ~-V <sub>S</sub> のプレー                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13        | -OUT2             | 負荷接続2の負側出力                          |

| Total Process   Hand Process     | 14        | PD2               | パワーダウン・ピン 2                         |

| 18 +OUT1 負荷接続1の正側出力 19 -OUT1 負荷接続1の負側出力 20 PD1 パワーダウン・ピン1 21、22 -Vs1 負電源電圧1 23 -FB1 帰還部品接続1の負側出力 24 +IN1 加算ノード1への正側入力 25 (EPAD) 露出パッド 露出パッドは電圧+Vs~-Vsのプレー                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15、16     | $-V_{S2}$         | 負電源電圧 2                             |

| 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17        | V <sub>OCM1</sub> | 出力コモン・モード電圧 1                       |

| 20     PDI     パワーダウン・ピン 1       21、22     -Vs1     負電源電圧 1       23     -FB1     帰還部品接続 1 の負側出力       24     +IN1     加算ノード 1 への正側入力       25 (EPAD)     露出パッド     露出パッドは電圧+V <sub>S</sub> ~-V <sub>S</sub> のプレー                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 18        | +OUT1             | 負荷接続1の正側出力                          |

| 21、22     -Vsi     負電源電圧 1       23     -FB1     帰還部品接続 1 の負側出力       24     +IN1     加算ノード 1 への正側入力       25 (EPAD)     露出パッド     露出パッドは電圧+V <sub>S</sub> ~-V <sub>S</sub> のプレー                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 19        | -OUT1             | 負荷接続1の負側出力                          |

| 23     -FB1     帰還部品接続1の負側出力       24     +IN1     加算ノード1への正側入力       25 (EPAD)     露出パッド     露出パッドは電圧+V <sub>S</sub> ~-V <sub>S</sub> のプレー                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20        | PD1               | パワーダウン・ピン 1                         |

| 24     +IN1     加算ノード1への正側入力       25 (EPAD)     露出パッド     露出パッドは電圧+V <sub>S</sub> ~-V <sub>S</sub> のプレー                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 21, 22    | $-V_{S1}$         | 負電源電圧1                              |

| 25 (EPAD) 露出パッド 露出パッドは電圧 $+V_S \sim -V_S$ のプレー                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23        | -FB1              | 帰還部品接続1の負側出力                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 24        | +IN1              | 加算ノード1への正側入力                        |

| (EPAD) ンに接続します。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25 (EPAD) | 露出パッド             | 露出パッドは電圧+ $V_s$ $\sim$ - $V_s$ のプレー |

| . 1-12/1/2 0 07 / 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -         | (EPAD)            | ンに接続します。                            |

Rev. 0 - 8/24 -

### 代表的な性能特性

特に指定がない限り、 $T_A=25^{\circ}$ C、 $+V_S=5$  V、 $-V_S=-5$  V、 $V_{OCM}=0$  V、 $R_G=301$   $\Omega$ 、 $R_F=301$   $\Omega$ 、 $R_T=56.2$   $\Omega$  (使用時)、 $R_{L,dm}=1$   $k\Omega$ 。基本 テスト・セットアップについては、図 43 を参照してください。信号の定義については、図 46 を参照してください。

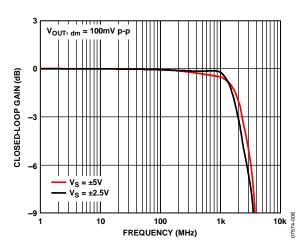

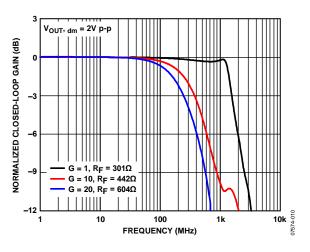

図 7.さまざまなゲインでの小信号周波数応答

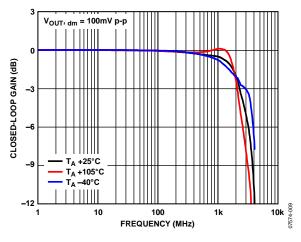

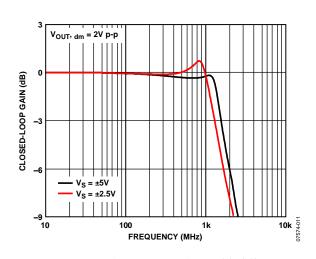

図 8.さまざまな電源での小信号周波数応答

図 9.さまざまな温度での小信号周波数応答

図 10.さまざまなゲインでの大信号周波数応答

図 11.さまざまな電源での大信号周波数応答

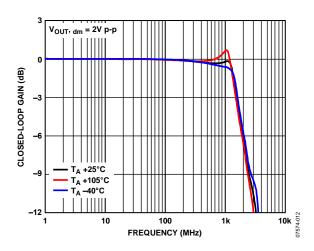

図 12.さまざまな温度での大信号周波数応答

Rev. 0

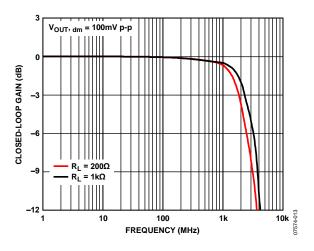

図 13.さまざまな負荷での小信号周波数応答

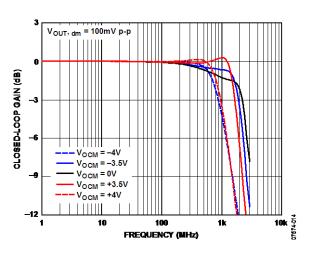

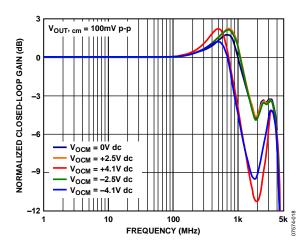

図 14.さまざまな Vocmレベルでの小信号周波数応答

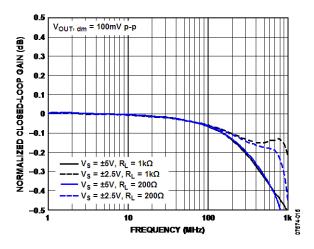

図 15.さまざまな負荷と電源での 0.1 dB 平坦性小信号周波数応答

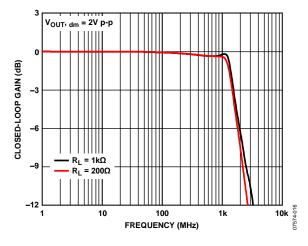

図 16.さまざまな負荷での大信号周波数応答

図 17.さまざまな Vocmレベルでの大信号周波数応答

図 18.さまざまな DC レベルの V<sub>OCM</sub> 小信号周波数応答

Rev. 0 — 10/24 —

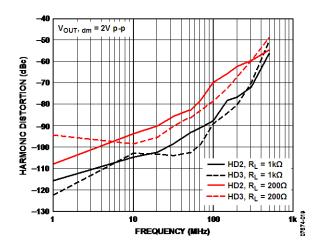

図 19.さまざまな負荷での高調波歪みの周波数特性

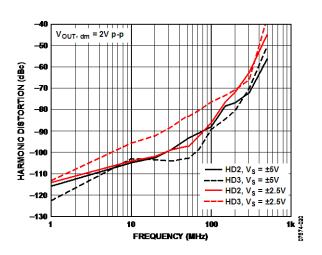

図 20.さまざまな電源での高調波歪みの周波数特性

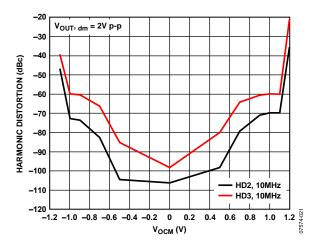

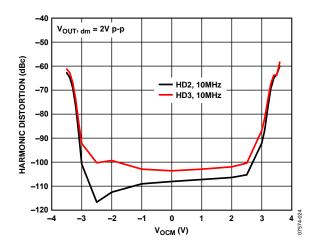

図 21.高調波歪み対 V<sub>OCM</sub>、10 MHz、±2.5 V 電源

図 22.さまざまなゲインでの高調波歪みの周波数特性

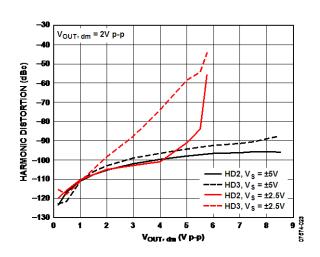

図 23.高調波歪み対  $V_{OU, dm}$  および電源電圧 f=10~MHz

図 24.高調波歪み対 V<sub>OCM</sub>、10 MHz、±5 V 電源

Rev. 0 — 11/24 —

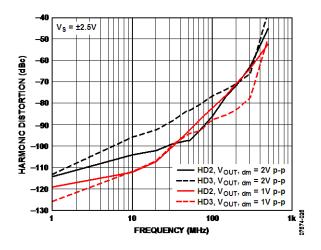

図 25.さまざまな VouT, dm での高調波歪周波数特性

図 26.さまざまなゲインでのスプリアス・フリー・ダイナミック・レンジの周波数 特性

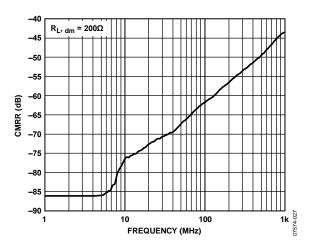

図 27.CMRR の周波数特性

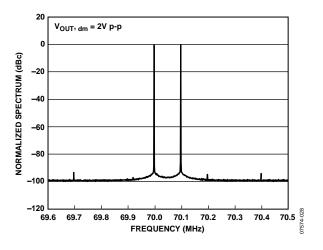

図 28.70 MHz 相互変調歪み

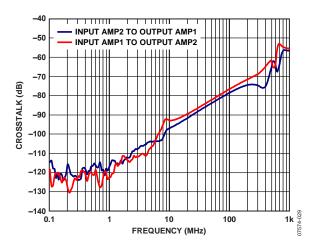

図 29.ADA4927-2 クロストークの周波数特性

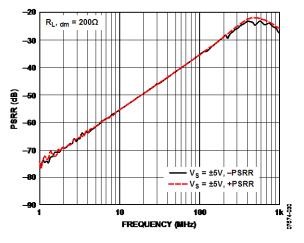

図 30.PSRR の周波数特性

Rev. 0 — 12/24 —

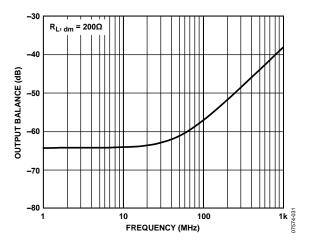

図 31.出力バランスの周波数特性

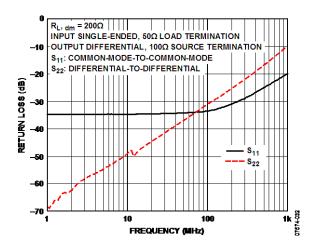

図 32.リターン損失(S11、S12)の周波数特性

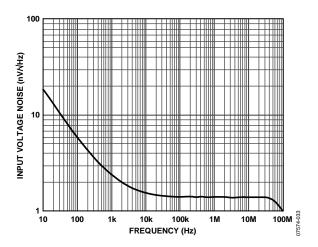

図 33.電圧ノイズ・スペクトル密度、入力換算

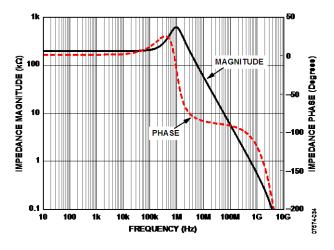

図 34.オープン・ループ相互インピーダンスと位相の周波数特性

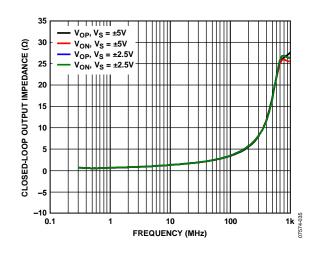

図 35.さまざまな電源電圧でのクローズド・ループ出力インピーダンスの 周波数特性、G = 1

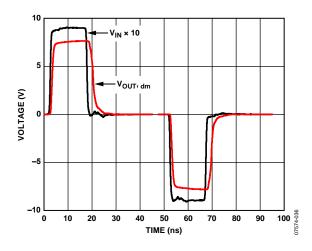

図 36.オーバードライブ回復時間、G = 10

Rev. 0 — 13/24 —

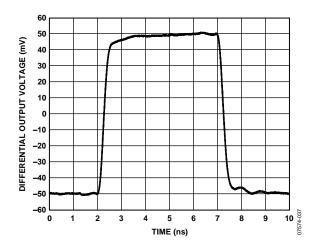

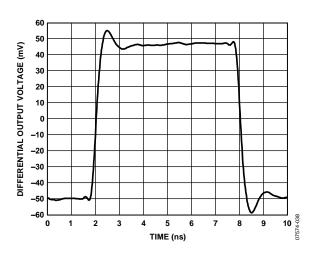

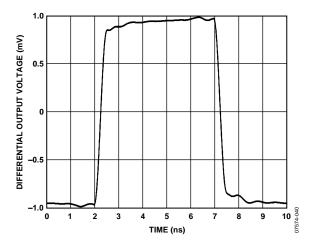

図 37.小信号パルス応答

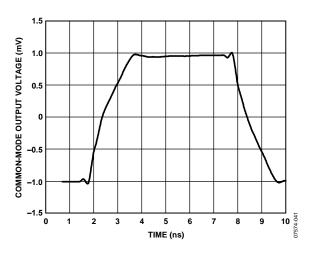

図 38.V<sub>OCM</sub> 小信号パルス応答

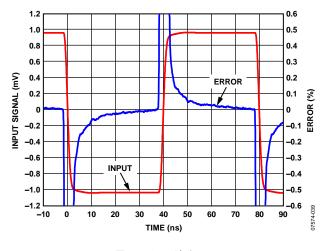

図 39.セトリング・タイム

図 40.大信号パルス応答

図 41.V<sub>OCM</sub>大信号パルス応答

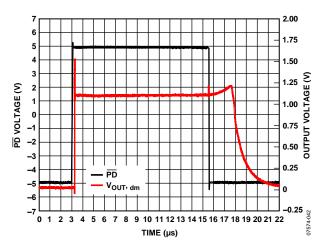

図 42.PD 応答時間

Rev. 0 — 14/24 —

## テスト回路

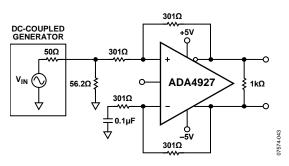

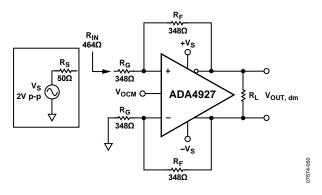

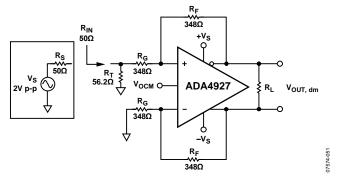

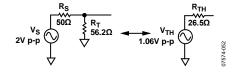

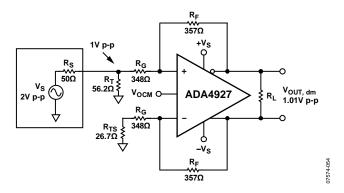

図 43.等価基本テスト回路、G = 1

図 44.出力バランスのテスト回路、CMRR

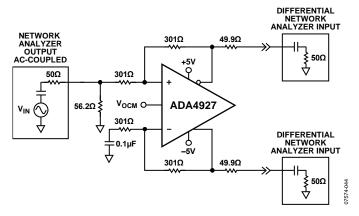

図 45.歪み測定のテスト回路

Rev. 0 — 15/24 —

### 動作原理

ADA4927 は、電圧が反対方向に動く 2 つの出力と入力  $V_{OCM}$  が 追加されている点で、従来型オペアンプと異なっています。さ らに、ADA4927 では電流帰還アーキテクチャを採用しています。 このデバイスは、従来型電流帰還オペアンプと同様に、高いオ ープン・ループ相互インピーダンス T(s)とこれらの出力を所望 の電圧にする負帰還に依存しています。ADA4927 は標準の電流 帰還オペアンプと同様に動作し、シングルエンド/差動変換、コ モン・モード・レベル・シフト、差動信号増幅の機能を持って います。また、ADA4927 は電流帰還オペアンプと同様に、低入 カインピーダンスの加算ノードを持っています。この加算ノー ドは実際にはエミッタ・フォロワ出力になっています。 ADA4927 出力は低インピーダンスであり、クローズド・ループ 出力インピーダンスはオープン・ループ出力インピーダンスを(1 +ループ・ゲイン)で除算した値です。ADA4927 は電流帰還を使 っているため、一定の公称帰還抵抗帯域幅積を持っています。 言い換えると、ADA4927 のクローズド・ループ帯域幅と安定性 は、基本的に帰還抵抗値に依存します。一般的な構成のクロー ズド・ループ・ゲインの式は、同等の電圧帰還差動アンプの式 と同じです。主な違いは、ADA4927 のダイナミック性能がノイ ズ・ゲインではなく帰還抵抗値に依存することです。このため、 帰還ループで使用する素子は安定性と十分な帯域幅を与える値 を持つ抵抗である必要があります。

2 つの帰還ループを採用して、差動モードとコモン・モードの出力電圧を制御しています。差動帰還ループでは外部抵抗を使う電流帰還アーキテクチャを採用し、差動出力電圧のみを制御します。コモン・モード帰還ループは内部にあり、電圧帰還を使い、コモン・モード出力電圧のみを制御します。このアーキテクチャにより、出力コモン・モード・レベルを規定範囲内の任意の値に容易に設定することができます。内部コモン・モード・ループにより、出力コモン・モード電圧が V<sub>OCM</sub>入力に加えられた電圧に等しくなるように維持されます。

外付け部品の厳密なマッチングなしでも、内部のコモン・モード帰還ループにより、広い周波数範囲でバランスした出力が発生されます。このために、真の同振幅と 180°の位相差に近い差動出力が得られます。

### 用語の定義

#### 差動電圧

2 つのノード電圧間の差。たとえば、出力差動電圧(または等価な出力差動モード電圧)は、次のように定義されます。

$$V_{OU, dm} = (V_{+OUT} - V_{-OUT})$$

ここで、 $V_{+OUT}$ と  $V_{-OUT}$ は+OUT ピンと-OUT ピンの電圧(共通グラウンドを基準)。同様に、差動入力電圧は次式で定義されます。

$$V_{IN.\ dm} = (+D_{IN} - (-D_{IN}))$$

#### コモン・モード電圧

コモン・モード電圧とは、2 つのノード電圧の平均を意味します(ローカル・グラウンドを基準)。出力コモン・モード電圧は次式で定義されます。

$$V_{OUT, cm} = \left(V_{+OUT} + V_{-OUT}\right)/2$$

#### バランス

出力バランスは、2 つの差動信号が同振幅と逆位相にある度合を表します。出力バランスは、一致した抵抗分圧器を差動電圧ノード間に接続し、デバイダの中点での信号振幅を差動信号の振幅と比較することにより、容易に求めることができます(図44 参照)。この定義を使うと、出力バランスは、出力コモン・モード電圧の振幅を出力差動モード電圧の振幅で除算して求められます。

$$Output \ BalanceError = \frac{\Delta V_{OUT,cm}}{\Delta V_{OUT,dm}}$$

Rev. 0 — 16/24 —

### アプリケーション情報

#### アプリケーション回路の解析

ADA4927 では、高いオープン・ループ相互インピーダンスと差動誤差電流を小さくするように差動出力電圧を制御する電流負帰還を使用しています。差動誤差電流は、2 つの差動入力(+IN と-IN)に流れる電流として定義されます(図 46 参照)。多くの場合、これらの電流はゼロと見なすことができます。+IN 入力と-IN 入力の間の電圧は内部で 0 V にブートストラップされるため、アンプ入力での電圧は一致し、電圧帰還アンプの場合と同様に外部で解析することができます。同様に、実際の出力コモン・モード電圧と  $V_{\rm OCM}$  に加えられる電圧との間の差もゼロと見なすことができます。これらの原理から、アプリケーション回路を解析することができます。

### クローズド・ループ・ゲインの設定

前述の方法を使うと、図 46 の差動モード・ゲインは次のように 求めることができます。

$$\left| \frac{V_{OUT,dm}}{V_{IN,dm}} \right| = \frac{R_F}{R_G}$$

ここでは、入力抵抗(R<sub>G</sub>)と帰還抵抗(R<sub>F</sub>)は等しいと仮定していま す。

#### 出力ノイズ電圧の計算

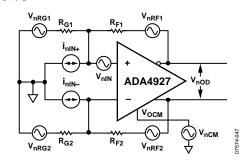

ADA4927 の差動出力ノイズは、図 47 に示すノイズ・モデルを使って計算することができます。入力換算ノイズ電圧密度  $v_{nIN}$  は差動入力としてモデル化され、ノイズ電流  $i_{nIN-}$ と  $i_{nIN+}$ は各入力とグラウンドの間で流れます。 $v_{nIN}$ に起因する出力電圧は、 $v_{nIN}$  とノイズ・ゲイン  $G_N$  ( $G_N$  の式で定義)の積として求められます。ノイズ電流は同じ 2 乗平均値と相関関係がなく、各々はノイズ電流と対応する帰還抵抗の積に等しい出力電圧を発生します。 $V_{OCM}$  ピンでのノイズ電圧密度は  $v_{nCM}$  です。多くの場合と同様に帰還回路の帰還係数が同じである場合、 $v_{nCM}$  に起因する出力ノイズはコモン・モードになります。4 本の各抵抗の寄与分は(4kTR<sub>xx</sub>)<sup>12</sup> になります。帰還抵抗からのノイズは直接出力に現れ、各ゲイン抵抗からのノイズは  $R_F/R_G$  倍されて出力に現れます。表 11 に、入力ノイズ源、乗算係数、出力換算ノイズ密度の項をまとめます。

図 47.ノイズ・モデル

#### 表 11.マッチングした帰還回路の出力ノイズ電圧密度の計算

| Input Noise Contribution           | Input Noise Term  | Input Noise<br>Voltage Density | Output<br>Multiplication Factor | Differential Output Noise<br>Voltage Density Term |

|------------------------------------|-------------------|--------------------------------|---------------------------------|---------------------------------------------------|

| Differential Input                 | V <sub>nIN</sub>  | V <sub>nIN</sub>               | $G_N$                           | $v_{nOl} = G_N(v_{nIN})$                          |

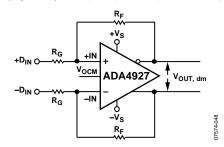

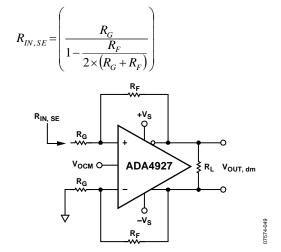

| Inverting Input                    | $i_{nIN}$         | $i_{nIN}\times(R_{F2})$        | 1                               | $v_{nO2} = (i_{nIN})(R_{F2})$                     |